Open access • Journal Article • DOI:10.1109/TASLP.2019.2931759

### Linear Multistep Discretization Methods With Variable Step-Size in Nonlinear Wave Digital Structures for Virtual Analog Modeling — Source link <a> ☑</a>

Alberto Bernardini, Paolo Maffezzoni, Augusto Sarti

Institutions: Polytechnic University of Milan

Published on: 01 Nov 2019 - IEEE Transactions on Audio, Speech, and Language Processing (IEEE)

Topics: Discretization, Iterative method, Trapezoidal rule (differential equations), Nonlinear system and Van der Pol oscillator

#### Related papers:

- · Wave digital filters: Theory and practice

- Modeling nonlinear wave digital elements using the Lambert function

- Resolving Grouped Nonlinearities in Wave Digital Filters using Iterative Techniques

- Wave-Based Analysis of Large Nonlinear Photovoltaic Arrays

- · Modeling Circuits With Arbitrary Topologies and Active Linear Multiports Using Wave Digital Filters

# Linear Multi-Step Discretization Methods with Variable Step-Size in Nonlinear Wave Digital Structures for Virtual Analog Modeling

Alberto Bernardini, *Member, IEEE*, Paolo Maffezzoni, *Senior Member, IEEE*Augusto Sarti, *Senior Member, IEEE*

Abstract—There is a growing interest in Virtual Analog modeling algorithms for musical audio processing designed in the Wave Digital (WD) domain. Such algorithms typically employ a discretization strategy based on the trapezoidal rule with fixed sampling step, though this is not the only option. In fact, alternative discretization strategies (possibly with an adaptive sampling step) can be quite advantageous, particularly when dealing with nonlinear systems characterized by stiff equations. In this article, we propose a unified approach for modeling capacitors and inductors in the WD domain using generic linear multi-step discretization methods with variable time-step size, and provide generalized adaptation conditions. We also show that the proposed approach for implementing dynamic (energystoring) elements in the WD domain is particularly suitable to be combined with a recently developed technique for efficiently solving a class of circuits with multiple one-port nonlinearities, called Scattering Iterative Method. Finally, as examples of application, we develop WD models for a Van Der Pol oscillator and a dynamic diode-based ring modulator, which use different discretization methods.

Index Terms—Wave Digital Filters, Nonlinear Audio Circuits, Virtual Analog Modeling, Reactances

#### I. INTRODUCTION

Wave Digital (WD) Filters [1], [2] have been extensively used in the audio signal processing community both for Virtual Analog modeling [3]–[9] and, combined with Digital Waveguides [10], [11], for Sound Synthesis through physical modeling [12]-[15]. WD structures have even been used for designing spatial filters in beamforming applications based on Differential Microphone Arrays [16]. It is only in the past few years, however, that Virtual Analog modeling has truly focused on the WD domain. Numerous articles, in fact, have recently appeared in the literature, proposing WD realizations of circuits containing linear and nonlinear elements such as operational amplifiers [6], [17], [18], nonlinear transformers [19], diodes [6], [20]-[23], vacuum tubes [24], [25] and transistors [26]-[30], which were not initially addressed in the original literature on WD Filters [1]. Dynamic circuits with up to one nonlinear element can be implemented using explicit (i.e. without delay-free loops) WD structures [2], [31]. This is a considerable advantage of WD modeling over Virtual Analog modeling methods [32]-[35] that work

A. Bernardini, P. Maffezzoni and A. Sarti are with the Dipartimento di Elettronica, Informazione e Bioingegneria (DEIB); Politecnico di Milano, Piazza L. Da Vinci 32, 20133 Milano, Italy (e-mail: [alberto.bernardini,paolo.maffezzoni,augusto.sarti]@polimi.it).

in the Kirchhoff domain (of voltages and currents), as they are typically characterized by sets of implicit equations and involve iterative solvers. This benefit, however, does not apply to circuits with multiple nonlinearities, as not all the delay-free loops can be removed [36], therefore we cannot avoid implicit equations. Even in these cases, however, working in the WD domain has proven beneficial. For instance, in [7] a method is introduced that allows to group all the nonlinear elements "at the root" of the WD structure, thus enabling the nonlinear part of the circuit to be separated from the linear one; then, the multi-dimensional nonlinear system of equations describing the nonlinear part is solved using the K-method with tabulation [27], [37] or multi-dimensional Newton-Raphson (NR) solvers [29]. Another iterative technique developed in [38] exploits the contractivity property of a class of WDFs for solving circuits with multiple nonlinearities making the wave signals circulate in the WD structure up to convergence. In [38] dynamic elements are accommodated introducing fictitious delays and employing the multi-dimensional WDF formalism. A different fixed-point method, known as Scattering Iterative Method (SIM), is introduced in [39], [40] for the analysis of large arrays of nonlinear photovoltaic units and later used for implementing a diode-based audio ring modulator without reactances [8]. The convergence analysis of SIM offered in [8], [39], also discusses how to properly vary the free parameters (port resistances) of the WD structure in order to speed up convergence. SIM is able to solve circuits with an arbitrary number  $N_{\rm nl}$  of 2-terminal nonlinear elements using  $N_{\rm nl}$  independent one-dimensional NR solvers instead of one  $N_{\rm nl}$ dimensional NR solver. This implies several desirable features that greatly differentiate SIM from techniques based on multidimensional iterative solvers [29], [32]: greater robustness; guaranteed convergence when working with monotonically increasing i - v nonlinearities such as diodes [8]); greater efficiency; and the possibility of solving the nonlinearities in a parallel fashion [39]. For all these reasons, SIM turns out to be particularly promising for Virtual Analog applications and it is worth extending its applicability to a wider class of nonlinear circuits. As SIM has been applied solely to circuits with no reactances, in order for it to be palatable for Virtual Analog modeling, it becomes important to extend its applicability to dynamic nonlinear circuits.

Most WD implementations of dynamic circuits presented in the literature use the trapezoidal discretization method with fixed sampling step for approximating the continuous-time derivative that appears in the constitutive equations of dynamic elements [1]. A good property of the trapezoidal method is that it is A-stable [41]. In addition, while digital implementations of dynamic linear circuits based on the trapezoidal rule generally result in implicit equations in the Kirchhoff domain [42], their WD description can be made explicit, after applying appropriate rules of adaptation [1].

Despite the excellent properties of the trapezoidal rule with fixed sampling step, alternate discretization techniques are often preferable. For example, the use of an adaptive sampling step, which is quite common in simulation software such as SPICE [42], [43], could significantly alleviate inaccuracies, particularly in the proximity of sudden signal amplitude variations, and especially when dealing with stiff systems (e.g. nonlinear relaxation oscillators); or could speed up simulations in presence of smooth signal variations. As a matter of fact, discretization methods other than the trapezoidal rule turn out to be preferable in many situations [44]. For example, the Backward Euler method can be fruitfully combined with the trapezoidal rule for implementing circuits with switches or for computing the first samples of simulations with uncertain initial conditions. Also, the use of higher-order discretization methods, such those based on the Backward Differentiation Formulas (BDF) (also known as Gear formulas) [45], are often opted for to achieve higher accuracy.

Although the idea of exploring different discretization methods in the WD domain is not new, there are surprisingly very few publications that address this topic. Some extensions of the traditional WD approach, which explore certain linear multi-step discretization methods with fixed sampling step are proposed in [46], [47], [48, pp. 33–47], and the use of passive Runge-Kutta methods in the WD domain is discussed in [49]–[52]. However, only a handful of publications [53], [54] address the problem of managing discretization methods with variable step-size in WD structures.

In this article, we propose an alternative approach to those presented in [53] and [54] for modeling dynamic nonlinear circuits in the WD domain using arbitrary Linear Multi-Step Discretization Methods (LMSDMs) with adaptive stepsize as defined in [42]. The approach is based on digital representations of dynamic elements (e.g., capacitors and inductors) through companion models, i.e., Thévenin or Norton equivalent models, which vary according to the used discretization method [42], [55]. Such representations facilitate the derivation of optimal adaptation conditions for capacitors and inductors at each sampling time. Moreover, Thévenin or Norton equivalents allow us to treat dynamic elements as time-varying resistive voltage or current sources, respectively. This fact makes the proposed modeling approach particularly suitable to be used in conjunction with SIM [8] for solving dynamic circuits with multiple one-port nonlinearities, without the need of designing fictitious delays and resorting to the multi-dimensional WDF formalism as done in [38].

The article is organized as follows. Section II provides a background on the modeling of connection networks and memoryless one-ports in WD structures. Section III presents general WD models of capacitors and inductors based on LMSDMs with variable step-size, along with their properties.

In Section IV the general WD models in Section III are applied to specific LMSDMs. Section V discusses the WD implementation of a class of nonlinear circuits employing the WD models presented in Section III. In particular, an extension of the applicability of SIM to dynamic circuits with multiple one-port nonlinearities is presented. In Section VI, WD implementations of a linear filter, a nonlinear Van Der Pol oscillator and a nonlinear ring modulator employing different LMSDMs are presented. Section VII concludes this article.

#### II. BACKGROUND ON WAVE DIGITAL STRUCTURES

In the WD domain, the topology and the elements of the reference circuit are typically modeled separately, using input/output blocks characterized by scattering relations. The derived blocks are then connected together through port connections and the WD structure is derived. In this Section, we briefly review how to compute the scattering matrices representing arbitrary reciprocal connection networks, i.e., topological interconnections possibly incorporating ideal transformers, in the WD domain [8], [39], [56], [57]. The reader who might be interested in the WD modeling of connection networks embedding both reciprocal and non-reciprocal linear elements, e.g., controlled sources, nullors or gyrators, is referred to [58]. In the following, we also briefly discuss the WD modeling of memoryless linear and nonlinear one-ports [1], [2].

#### A. Modeling Connection Networks

A N-port reciprocal connection network is characterized by the following pair of equations

$$\mathbf{v} = \mathbf{Q}^T \mathbf{v}_t \ , \quad \mathbf{j} = \mathbf{B}^T \mathbf{j}_l \ , \tag{1}$$

where the superscript  $^T$  indicates matrix/vector transposition,  $\mathbf{v} = [v_1, \dots, v_N]^T$  is the column vector of all port voltages,  $\mathbf{j} = [j_1, \dots, j_N]^T$  is the column vector of all port currents,  $\mathbf{v}_t$  is a column vector of size q,  $1 \leq q < N$ , collecting independent port voltages,  $\mathbf{j}_1$  is a column vector of size p, p = N - q, collecting independent port currents. Matrices  $\mathbf{Q}$  and  $\mathbf{B}$  are generalizations of the fundamental cut-set matrix and fundamental loop matrix, respectively, as explained in [8], [56], [57], and they satisfy the orthogonality property  $\mathbf{B}\mathbf{Q}^T = \mathbf{0}$ , where  $\mathbf{0}$  is a zero matrix of proper size. According to (1), each port voltage in  $\mathbf{v}$  is expressed as a linear combination of the q independent port voltages collected in  $\mathbf{v}_t$ , while each port current in  $\mathbf{j}$  is expressed as a linear combination of the p independent port currents collected in  $\mathbf{j}_1$  [57].

The implementation of the connection network in the WD domain is a scattering junction characterized by a scattering matrix, which in turn can be expressed as a function of  $\mathbf{Q}$  or  $\mathbf{B}$ . In order to define this scattering matrix, let us first consider the following port-wise definition of wave variables introduced by Fettweis [1]

$$\mathbf{a}_{J} = \mathbf{v} + \mathbf{Z}\mathbf{j}$$

,  $\mathbf{b}_{J} = \mathbf{v} - \mathbf{Z}\mathbf{j}$ , (2)

where  $\mathbf{a}_{J} = [a_{J1}, \dots, a_{JN}]^T$  is the vector of incident waves (entering the WD junction),  $\mathbf{b}_{J} = [b_{J1}, \dots, b_{J1}]^T$  is the vector

3

of reflected waves (exiting the WD junction), while the non-zero entries of the diagonal matrix  $\mathbf{Z} = \text{diag}[Z_1, \dots, Z_N]$  are free parameters called port resistances.

Wave variables defined in (2) are usually referred to as *voltage waves*, since their unit of measure is volt. Despite the definition in (2) is the most widespread, alternative definitions of waves, characterized by different units of measure [48], [57]–[59] and more than one free parameter per port [36], [57] have been discussed in the literature.

Incident and reflected waves are linked by the scattering relation

$$\mathbf{b}_{\mathbf{I}} = \mathbf{S}\mathbf{a}_{\mathbf{I}},\tag{3}$$

where S is a  $N \times N$  scattering matrix. As shown in [8], [39], [56], [57], S can be computed using one of the following two expressions

$$\mathbf{S} = 2\mathbf{Q}^T \left(\mathbf{Q}\mathbf{Z}^{-1}\mathbf{Q}^T\right)^{-1}\mathbf{Q}\mathbf{Z}^{-1} - \mathbf{I} , \qquad (4)$$

$$\mathbf{S} = \mathbf{I} - 2\mathbf{Z}\mathbf{B}^T \left(\mathbf{B}\mathbf{Z}\mathbf{B}^T\right)^{-1}\mathbf{B} , \qquad (5)$$

where  $\mathbf{I}$  is the  $N \times N$  identity matrix. Looking at equations (4) and (5), we notice that one of the two equations might be computationally less expensive to use, depending on whether the number of independent port voltages q is larger or smaller than the number of independent port currents p. In fact, as the sizes of the matrices  $\mathbf{Q}$  and  $\mathbf{B}$  are  $q \times N$  and  $p \times N$ , respectively, eq. (4) involves the inversion of a  $q \times q$  matrix, while eq. (5) involves the inversion of a  $p \times p$  matrix.

#### B. Modeling One-port Memoryless Circuit Elements

The mapping between the WD variables of a one-port memoryless circuit element is derived by considering its constitutive equation in the Kirchhoff domain, which describes the relation between its port voltage  $\boldsymbol{v}$  and its port current i, and then by applying the transformation

$$v = (a + b)/2$$

,  $i = (a - b)/(2Z)$ , (6)

where a is the incident voltage wave (input), b is the reflected voltage wave (output), and Z is the port resistance [1]. The following two useful hybrid relations can be easily derived from (6)

$$i = (a - v)/Z (7)$$

$$b = 2v - a (8)$$

Here are two examples of interest: the WD implementation of linear resistive voltage sources and that of nonlinear diodes.

1) Resistive voltage sources and linear resistors: The constitutive equation of a resistive voltage source is  $v = V_g + R_g i$ , where  $V_g$  is the generator and  $R_g$  is its series resistance. The corresponding wave mapping, derived according to (6), is [1]

$$b = \frac{R_{\rm g} - Z}{R_{\rm g} + Z} a + \frac{2Z}{R_{\rm g} + Z} V_{\rm g} . \tag{9}$$

If the free parameter Z is set to  $R_{\rm g}$ , the resistive voltage source is said to be *adapted*, as the instantaneous dependency between a and b is eliminated, and the wave mapping becomes simply  $b=V_{\rm g}$ . Notice that, setting  $V_{\rm g}=0$ , (9) reduces to the wave mapping of an adapted resistor with resistance  $R_{\rm g}$ .

2) Diodes: Let us consider the extended Shockley diode model presented in [8] and characterized by the nonlinear implicit equation

$$f\left(v,i\right) = I_{\rm s}\left(\exp\left(\frac{v - R_{\rm s}i}{\eta V_{\rm t}}\right) - 1\right) + \frac{v - R_{\rm s}i}{R_{\rm p}} - i = 0 \ \ (10)$$

where  $I_{\rm s}$  is the saturation current,  $\eta$  is the ideality factor,  $V_{\rm t}$  is the thermal voltage, while  $R_{\rm s}$  and  $R_{\rm p}$  are the series resistance and the shunt resistance of the p-n junction, respectively. As (10) is a transcendental equation, the derivation of a wave mapping is not straightforward. A closed-form scattering relation involving the Lambert function can be found using the approach described in [28]. Another possible efficient approach, which uses a one-dimensional Newton-Raphson (NR) solver, is explained in [8] and reported hereafter. If we substitute (7) in (10) we obtain

$$h\left(v\right) = I_{\mathrm{s}}\left(e^{\frac{v\left(Z+R_{\mathrm{s}}\right)-aR_{\mathrm{s}}}{\eta V_{\mathrm{t}}Z}}-1\right) + \frac{v\left(Z+R_{\mathrm{p}}+R_{\mathrm{s}}\right)-a\left(R_{\mathrm{p}}+R_{\mathrm{s}}\right)}{ZR_{\mathrm{p}}}$$

and its derivative h'(v) with respect to v,

$$h'(v) = \frac{I_s(Z + R_s)}{\eta V_t Z} e^{\frac{v(Z + R_s) - aR_s}{\eta V_t Z}} + \frac{Z + R_p + R_s}{ZR_p}.$$

Given a, the nonlinear equation h(v) = 0 is iteratively solved for v by applying the NR update equation

$$v^{(\iota)} = v^{(\iota-1)} - \frac{h(v^{(\iota-1)})}{h'(v^{(\iota-1)})} \quad , \tag{11}$$

where the superscript between brackets is the iteration index and  $\iota \geq 1$ . Once the convergence condition  $|v^{(\iota)}-v^{(\iota-1)}|<\epsilon_{\rm NR}$  is met,  $\epsilon_{\rm NR}$  being a small tolerance (e.g.  $\epsilon_{\rm NR}=10^{-10}$ ), the solver stops and the port voltage is set to  $v=v^{(\iota)}$ , so that the reflected wave b can be computed using (8). As the diode is nonlinear, unlike the resistive voltage source, it cannot be adapted, i.e. the instantaneous dependency between a and b cannot be eliminated [2].

## III. GENERAL WD MODELS OF DYNAMIC ELEMENTS BASED ON LMSDMS

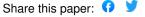

In this Section we show how to derive WD models of dynamic elements based on general LMSDMs with variable step-size [42]. The derivation is based on companion models [42], [55], also known as associated discrete circuit models [60], for dynamic elements, which are Thévenin or Norton equivalents whose parameters change at every sample. The Thévenin equivalent model is a resistive voltage source characterized by the following equation in the discrete-time domain

$$v[k] = R_{\rm e}[k]i[k] + V_{\rm e}[k]$$

(12)

where the index  $k \geq 1$  in square brackets refers to the kth sample, v[k] and i[k] are the discrete-time port signals,  $V_{\rm e}[k]$  is the generator and  $R_{\rm e}[k]$  is the series resistance. The Norton equivalent model, instead, is a current source with parallel resistor characterized by

$$i[k] = G_e[k]v[k] + I_e[k]$$

(13)

where  $I_{\rm e}[k]$  is the current generator,  $G_{\rm e}[k]$  is the Norton conductance. Thévenin and Norton equivalent models that refer to the same element are related by

$$G_{\rm e}[k] = 1/R_{\rm e}[k]$$

,  $I_{\rm e}[k] = -G_{\rm e}[k]V_{\rm e}[k]$ . (14)

Graphical representations of Thévenin and Norton equivalent models are shown in Fig. 1(a) and in Fig. 1(b), respectively.

Fig. 1. Companion models of capacitors and inductors in the discrete-time domain. Fig. 1(a): Thévenin equivalent model. Fig. 1(b): Norton equivalent model.

In the discrete-time domain, the transformation of WD port variables to Kirchhoff port variables, already defined in (6), can be rewritten as

$$v[k] = \frac{a[k] + b[k]}{2}$$

,  $i[k] = \frac{a[k] - b[k]}{2Z[k]}$  , (15)

where a[k] and b[k] are the discrete-time wave variables and Z[k] is the port resistance depending on k. The inverse transformation of (15) is given by

$$a[k] = v[k] + Z[k]i[k]$$

,  $b[k] = v[k] - Z[k]i[k]$  . (16)

Similarly to what done in Subsection II-B, substituting (15) in (12) we get the wave mapping of the Thévenin equivalent

$$b[k] = \frac{R_{\rm e}[k] - Z[k]}{R_{\rm e}[k] + Z[k]} a[k] + \frac{2Z[k]}{R_{\rm e}[k] + Z[k]} V_{\rm e}[k] . \tag{17}$$

In case of adaptation we can write

$$b[k] = V_e[k]$$

, if  $Z[k] = R_e[k]$ . (18)

Similarly, by substituting (15) in (12) we obtain the wave mapping of the Norton equivalent

$$b[k] = \frac{1 - Z[k]G_{e}[k]}{1 + Z[k]G_{e}[k]}a[k] - \frac{2Z[k]}{1 + Z[k]G_{e}[k]}I_{e}[k]$$

(19)

In case of adaptation, eq. (19) simplifies to

$$b[k] = -I_e[k]/G_e[k]$$

, if  $Z[k] = 1/G_e[k]$ . (20)

In the rest of this Section, we show how general WD models of capacitors and inductors based on a LMSDM can be derived by simply expressing the Thévenin equivalent parameters  $V_{\rm e}[k]$  and  $R_{\rm e}[k]$ , or the Norton equivalent parameters  $I_{\rm e}[k]$  and  $G_{\rm e}[k]$ , as functions of the past values of port signals, the coefficients of the discretization method, the variable step-size and the capacitance/inductance. It follows that WD realizations of capacitors and inductors based on a LMSDM can be obtained simply by implementing in the WD domain time-varying resistive voltage or current sources as those shown in Fig. 1; i.e., applying the scattering relations (17) or (19), respectively. In case of adaptation, the simplified scattering relations (18) or (20) can be directly used.

#### A. Capacitors

The constitutive equation of a capacitor of capacitance C in the continuous-time domain is

$$i(t) = C\frac{dv(t)}{dt} \tag{21}$$

where v(t) and i(t) are the continuous-time port signals, and t is the time variable in seconds. After applying a general LMSDM of order M with variable step-size [42], [60], the discrete-time version of (21) becomes

$$v[k] = \sum_{m=1}^{M} \mu_m[k]v[k-m] + \frac{h[k]}{C} \sum_{m=0}^{M} \eta_m[k]i[k-m]$$

(22)

where  $\mu_1[k], \ldots, \mu_M[k]$  and  $\eta_0[k], \eta_1[k], \ldots, \eta_M[k]$  are real coefficients, whose design depends on the chosen LMSDM. h[k] is the variable step-size, which is defined as

$$h[k] = t_k - t_{k-1} (23)$$

where  $t_k$  is the current sampling time and  $t_{k-1}$  is the previous one. Notice that, as h[k] is assumed to be variable, we could have  $h[k] \neq h[k-1]$  for each k.

Finding the Thévenin equivalent (12) of the discrete-time capacitor model (22) yields

$$R_{\rm e}[k] = \eta_0[k] \frac{h[k]}{C} ,$$

(24)

$$V_{e}[k] = \sum_{m=1}^{M} \eta_{m}[k] \frac{h[k]}{C} i[k-m] + \mu_{m}[k] v[k-m] . \quad (25)$$

The wave mapping of a WD capacitor can now be obtained by just substituting (24) and (25) in (17), or directly in (18), if the scattering relation of an adapted WD capacitor is needed.

Similarly, by equating (22) and (13) the following closedform expressions of the Norton equivalent parameters are derived

$$G_{\rm e}[k] = \frac{C}{\eta_0[k]h[k]} ,$$

(26)

$$I_{e}[k] = \frac{-1}{\eta_{0}[k]} \left( \sum_{m=1}^{M} \mu_{m}[k] \frac{C}{h[k]} v[k-m] + \eta_{m}[k] i[k-m] \right). \tag{27}$$

In this case, the wave mapping of a WD capacitor is obtained by just substituting (26) and (27) in (19), or directly in (20), if the scattering relation of an adapted WD capacitor is needed.

#### B. Inductors

The constitutive equation of an inductor with inductance L in the continuous-time domain is

$$v(t) = L\frac{di(t)}{dt} . (28)$$

After applying a general LMSDM of order M with variable step-size [42], [60], the discrete-time version of (28) becomes

$$i[k] = \sum_{m=1}^{M} \mu_m[k]i[k-m] + \frac{h[k]}{L} \sum_{m=0}^{M} \eta_m[k]v[k-m] , (29)$$

where  $\mu_1[k], \ldots, \mu_M[k]$  and  $\eta_0[k], \eta_1[k], \ldots, \eta_M[k]$  are the same real coefficients appearing in eq. (22) and the variable step-size h[k] is defined as in eq. (23).

Equating (29) and (13) the following closed-form expressions of the Thévenin equivalent parameters are obtained

$$R_{\rm e}[k] = \frac{L}{\eta_0[k]h[k]} ,$$

(30)

$$V_{e}[k] = \frac{-1}{\eta_{0}[k]} \left( \sum_{m=1}^{M} \mu_{m}[k] \frac{L}{h[k]} i[k-m] + \eta_{m}[k] v[k-m] \right). \tag{31}$$

The wave mapping of a WD inductor is obtained substituting (30) and (31) in (17), or directly in (18), if the scattering relation of an adapted WD inductor is needed.

Similarly, by equating (29) and (13) the following closedform expressions of the Norton equivalent parameters are obtained

$$G_{\rm e}[k] = \eta_0[k] \frac{h[k]}{L} ,$$

(32)

$$I_{e}[k] = \sum_{m=1}^{M} \eta_{m}[k] \frac{h[k]}{L} v[k-m] + \mu_{m}[k] i[k-m] . \quad (33)$$

The wave mapping of a WD inductor is obtained by substituting (32) and (33) in (19), or directly in (20), if the scattering relation of an adapted WD inductor is needed.

#### C. On the possibility of performing adaptation

General adaptation conditions for WD models of reactances based on LMSDMs are provided in (18) and (20). The applicability of such adaptation conditions, however, depends on the LMSDM that we are dealing with. The following two rules state when and how adaptation conditions can be set.

Rule I. If  $\eta_0[k] \neq 0$ , capacitors or inductors can be represented by Thévenin equivalents with non-zero series resistances at each sampling step; therefore, a WD realization can always be derived in which there is not an instantaneous dependency between the incident wave and the reflected wave, provided that adaptation is performed, according to eq. (18) or eq. (20).

Rule II. If  $\eta_0[k] = 0$ , capacitors do not admit a Norton representation (see eq. (26) and eq. (27)), while they admit a representation based on a Thévenin equivalent with zero series resistance, i.e., an ideal voltage source (see eq. (24) and eq. (25)); dually, inductors admit only a representation based on a Norton equivalent with zero parallel admittance, i.e., an ideal current source (see eq. (32) and eq. (33)). Therefore, when  $\eta_0[k] = 0$ , adaptation cannot be performed in either cases (capacitor or inductors).

It is worth noticing that the aforementioned rules are in line with the considerations drawn in the doctoral dissertation by Werner [48, pp. 33–47], where it is shown that capacitors and inductors can be adapted only if implicit discretization methods are used; while, when explicit discretization methods, like Forward Euler, are chosen, adaptation cannot be performed.

## IV. WD MODELS OF DYNAMIC ELEMENTS BASED ON SPECIFIC LMSDMS

#### A. LMSDMs with Fixed Step-Size

Table I presents a characterization of discrete models of capacitors and inductors based on some LMSDMs with fixed step-size, used for implementing dynamic circuit networks [42], showing their weighting coefficients. For each indicated LMSDM, all the weighting coefficients  $\eta_m[k]$  and  $\mu_m[k]$  not shown in Table I are assumed to be equal to 0. As the time-step size in Table I is assumed to be fixed, the coefficient values are fixed as well. The last column of Table I indicates whether WD models of capacitors and inductors based on a specific LMSDM can be adapted, eliminating the instantaneous dependency between the incident wave and the reflected wave. Quite naturally, the most interesting LMSDMs in our context are those that lead to WD models where adaptation can be performed. In the following, we focus on some WD models of the sort, considering the more general scenario in which the step-size is assumed to be variable.

#### B. Trapezoidal Method

The non-zero coefficients  $\eta_0[k]$ ,  $\eta_1[k]$  and  $\mu_1[k]$  of the trapezoidal method in the variable step-size scenario are the same as reported in Table I and used in the fixed step-size case [42]. It follows that the adaptation condition for a *WD* capacitor is

$$Z[k] = \frac{h[k]}{2C} . (34)$$

Hence, substituting (25) in (18) and then expressing Kirchhoff variables in terms of wave variables according to (15), the scattering relation becomes

$$b[k] = \frac{a[k-1]}{2} \left( 1 + \frac{h[k]}{h[k-1]} \right) + \frac{b[k-1]}{2} \left( 1 - \frac{h[k]}{h[k-1]} \right). \tag{35}$$

The adaptation condition for a WD inductor, instead, is

$$Z[k] = \frac{2L}{h[k]} \ . \tag{36}$$

Hence, substituting (31) in (18) and then expressing Kirchhoff variables in terms of wave variables according to (15), the scattering relation becomes

$$b[k] = \frac{a[k-1]}{-2} \left( 1 + \frac{h[k-1]}{h[k]} \right) + \frac{b[k-1]}{-2} \left( 1 - \frac{h[k-1]}{h[k]} \right). \tag{37}$$

When h[k-1] = h[k], scattering relations (35) and (37) reduce to the ones employed in traditional WD filters [1].

#### C. Backward Euler Method

The non-zero coefficients  $\eta_0[k]$  and  $\mu_1[k]$  of the Backward Euler (BE) method in the variable step-size scenario are the same reported in Table I and used in the fixed step-size case [42]. It follows that the adaptation condition for a WD capacitor is

$$Z[k] = \frac{h[k]}{C} , \qquad (38)$$

| Method            | Coefficients |             |             |             |            |            |            |            | Adaptation possible (yes/no) |

|-------------------|--------------|-------------|-------------|-------------|------------|------------|------------|------------|------------------------------|

|                   | $\eta_0[k]$  | $\eta_1[k]$ | $\eta_2[k]$ | $\eta_3[k]$ | $\mu_1[k]$ | $\mu_2[k]$ | $\mu_3[k]$ | $\mu_4[k]$ |                              |

| Backward Euler    | 1            | 0           | 0           | 0           | 1          | 0          | 0          | 0          | yes                          |

| Trapezoidal       | 1/2          | 1/2         | 0           | 0           | 1          | 0          | 0          | 0          | yes                          |

| Adams-Moulton 2   | 5/12         | 2/3         | -1/12       | 0           | 1          | 0          | 0          | 0          | yes                          |

| Adams-Moulton 3   | 3/8          | 19/24       | -5/24       | 1/24        | 1          | 0          | 0          | 0          | yes                          |

| BDF 2             | 2/3          | 0           | 0           | 0           | 4/3        | -1/3       | 0          | 0          | yes                          |

| BDF 3             | 6/11         | 0           | 0           | 0           | 18/11      | -9/11      | 2/11       | 0          | yes                          |

| BDF 4             | 12/25        | 0           | 0           | 0           | 48/25      | -36/25     | 16/25      | -3/25      | yes                          |

| Forward Euler     | 0            | 1           | 0           | 0           | 1          | 0          | 0          | 0          | no                           |

| Adams-Bashforth 2 | 0            | 1           | 0           | 0           | 3/2        | -1/2       | 0          | 0          | no                           |

| Adams-Bashforth 3 | 0            | 1           | 0           | 0           | 23/12      | -4/3       | 5/12       | 0          | no                           |

| Adams-Bashforth 4 | 0            | 1           | 0           | 0           | 55/24      | -59/24     | 37/24      | -3/8       | no                           |

TABLE I CHARACTERIZATION OF WD MODELS OF CAPACITORS AND INDUCTORS BASED ON LMSDMs WITH FIXED STEP-SIZE

and, according to (18) and (25), the scattering relation becomes

$$b[k] = \frac{a[k-1] + b[k-1]}{2} . (39)$$

The adaptation condition for a WD inductor, instead, is

$$Z[k] = \frac{L}{h[k]} \quad , \tag{40}$$

and, according to (18) and (31), the scattering relation becomes

$$b[k] = \frac{h[k-1]}{2h[k]} \left( b[k-1] - a[k-1] \right) . \tag{41}$$

#### D. Higher-Order Backward Differentiation Formulas

BDF methods of order M > 1, in the variable step-size scenario, are characterized by non-fixed coefficients depending on the actual step-sizes, hence the coefficients provided in Table I are not appropriate in this case [42]. In this Subsection, we provide general WD models of adapted capacitors and inductors based on BDF methods. Then, we derive closedform expressions for computing the coefficients needed in BDF 2, BDF 3 and BDF 4, when the step-size is assumed to be variable.

Applying a BDF of order M and setting the adaptation condition  $Z[k] = \eta_0[k]h[k]/C$ , the scattering relation of a WD capacitor becomes

$$b[k] = \sum_{m=1}^{M} \frac{\mu_m[k]}{2} \left( a[k-m] + b[k-m] \right)$$

(42)

Similarly, setting the adaptation condition Z[k] $L/(\eta_0[k]h[k])$ , the scattering relation of a WD inductor, becomes

The coefficients of a BDF of order M are computed as

$$\eta_0[k] = \frac{-1}{u_0[k]}, \quad \mu_m[k] = \eta_0[k]u_m[k] \quad \text{with } 1 \le m \le M$$

(44)

where, in accordance with the procedure presented in [42], the parameters  $u_m[k]$ , with  $0 \le m \le M$ , are given by

$$\begin{bmatrix} u_0[k] \\ u_1[k] \\ u_2[k] \\ \vdots \\ u_M[k] \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & \dots & 0 \\ 1 & 1 & 1 & \dots & 1 \\ 1 & \tau_2[k] & (\tau_2[k])^2 & \dots & (\tau_2[k])^M \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 1 & \tau_M[k] & (\tau_M[k])^2 & \dots & (\tau_M[k])^M \end{bmatrix}^{-1} \begin{bmatrix} 0 \\ 1 \\ 0 \\ \vdots \\ 0 \end{bmatrix},$$

(45)

and the further parameters  $\tau_i[k]$  are defined as

$$\tau_j[k] = \frac{h[k] + \sum_{m=1}^{j-1} h[k-m]}{h[k]}$$

, with  $1 < j \le M$ . (46)

Here follow closed-form expressions of the coefficients in the cases M=2, M=3 and M=4. It is worth saying that such closed-form expressions for BDF 3 and BDF 4 are not available in [42].

1) Coefficients for BDF 2:

$$\eta_0[k] = \frac{\tau_2[k]}{\tau_2[k] + 1} ,$$

$$\mu_1[k] = \eta_0[k] \frac{\tau_2[k]}{\tau_2[k] - 1} , \quad \mu_2[k] = \eta_0[k] \frac{1}{\tau_2[k](1 - \tau_2[k])} .$$

2) Coefficients for BDF 3:

$$\eta_0[k] = \frac{\tau_2[k]\tau_3[k]}{\tau_2[k] + \tau_3[k] + \tau_2[k]\tau_3[k]} ,$$

$$\mu_1[k] = \eta_0[k] \frac{\tau_2[k]\tau_3[k]}{(\tau_2[k] - 1)(\tau_3[k] - 1)} ,$$

$$\mu_2[k] = \eta_0[k] \frac{\tau_3[k]}{\tau_2[k](\tau_2[k] - 1)(\tau_2[k] - \tau_3[k])} ,$$

$$\mu_3[k] = \eta_0[k] \frac{\tau_2[k]}{\tau_3[k](1 - \tau_3[k])(\tau_2[k] - \tau_3[k])} .$$

$$\eta_{0}[k] = \frac{\tau_{2}[k]\tau_{3}[k]\tau_{4}[k]}{\tau_{2}[k]\tau_{3}[k] + \tau_{2}[k]\tau_{4}[k] + \tau_{3}[k]\tau_{4}[k] + \tau_{2}[k]\tau_{3}[k]\tau_{4}[k]},$$

s

$$\mu_{1}[k] = \eta_{0}[k] \frac{\tau_{2}[k]\tau_{3}[k]\tau_{4}[k]}{(\tau_{2}[k] - 1)(\tau_{3}[k] - 1)(\tau_{4}[k] - 1)},$$

$$M$$

$$\mu_{2}[k] = \eta_{0}[k] \frac{\tau_{3}[k]\tau_{4}[k]}{\tau_{2}[k](\tau_{3}[k] - \tau_{2}[k])(\tau_{2}[k] - \tau_{4}[k])(\tau_{2}[k] - 1)},$$

(44)

$$\mu_{3}[k] = \eta_{0}[k] \frac{\tau_{2}[k]\tau_{4}[k]}{\tau_{3}[k](\tau_{2}[k] - \tau_{3}[k])(\tau_{3}[k] - \tau_{4}[k])(\tau_{3}[k] - 1)} ,$$

$$\mu_{4}[k] = \eta_{0}[k] \frac{\tau_{2}[k]\tau_{3}[k]}{\tau_{4}[k](\tau_{4}[k] - \tau_{2}[k])(\tau_{3}[k] - \tau_{4}[k])(\tau_{4}[k] - 1)} .$$

#### E. Automatic Step-Size Variation

Different strategies can be used for automatically adapting the time-step size during the digital emulation of an audio circuit. The design of algorithms for the automatic change of the step-size strongly depends on the accuracy and efficiency requirements of the reference application. As a detailed discussion on the optimization criteria for step-size variation is beyond the scope of this article, here we simply mention that, algorithms that eventually change the step-size h[k+1] at each sampling step k+1 with respect to h[k], are usually based on the estimation of the Local Truncation Error (LTE) at each port connected to a dynamic element [43]. For instance, the LTE  $e_n[k]$  associated to the BE discretization formula for a capacitor with capacitance C at port n is  $e_n[k] \approx h^2[k]v_n''[k]/2$ , where  $v_n''[k]$  is the second order time derivative of the voltage across the capacitor evaluated at the time instant corresponding to the kth sample [43], and it can be approximated as  $\hat{e}_n[k] = w_n[k](i_n[k] - i_n[k-1])$ with  $w_n = h[k]/(2C)$ . However, more advanced prediction algorithms could be employed for estimating the LTEs, which depend on the used LMSDM; see, e.g., [60] and [43] for a discussion on these aspects. Depending on the magnitude of the estimated LTEs, one might decide to: increase the step-size, i.e., set  $h[k+1] = g_{inc}h[k]$ , with  $g_{inc} > 1$ , if the estimated LTEs are sufficiently low; leave the step-size unchanged, i.e., set h[k+1] = h[k]; reduce the step-size, i.e., set  $h[k+1] = g_{red}h[k]$ , with  $0 < g_{red} < 1$ ; or even repeat the computation of  $i_n[k]$  with a reduced time-step h[k], if the estimated LTEs are too large.

## V. WD IMPLEMENTATION OF NONLINEAR DYNAMIC CIRCUITS

In this Section, we discuss strategies for implementing nonlinear dynamic circuits in the WD domain. We focus our attention to circuits with one-port nonlinearities. We first revise a common efficient strategy for implementing WD structures with one nonlinear one-port, known since the publication of [2], in which all global delay-free loops are eliminated. We then show how, in the light of the results presented in the previous two Sections, the applicability of SIM [8], [39] can be extended to dynamic circuits with multiple nonlinear one-ports.

#### A. One Nonlinearity Case

Let us consider a WD multi-port junction describing the connection network of a circuit with one nonlinear element and a number of memoryless or dynamic linear elements. We also consider the scattering matrix characterizing the connection network, defined as in Section II. The free parameter (port resistance) of the junction port facing the nonlinear element is set in such a way that the corresponding diagonal entry

of the scattering matrix becomes zero. This ensures that the junction port is reflection free, which means the instantaneous dependence between the incident wave and the reflected wave at that port is eliminated [2]. We assume that all the linear elements are adapted, according to the constraints provided in the previous Sections. Then, the WD elements are virtually connected to the WD junction by first forcing the reflected waves from the junction to be equal to the incident waves to the elements and vice-versa and then setting the port resistances of the junction to be equal to the port resistances of the WD elements, in a port-wise fashion [1]. Under these assumptions all the global delay-free loops due to the interconnections of circuit elements are eliminated, as already explained in [2] and, more recently, in [36]. It follows that, if look-up tables [3] or, more conveniently, canonical piecewise linear representations of functions [23] are used for computing the nonlinear wave mapping, the reference circuit is implemented in a fully explicit fashion. Alternatively, onedimensional NR solvers can be used for solving the potentially implicit constitutive equation of the nonlinear element in the WD domain, without necessarily loosing robustness and efficiency, as explained in Subsection II-B.

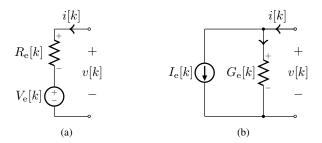

As an example, Fig. 2(b) shows a WD structure corresponding to the oscillator with one nonlinear element in Fig. 2(a). We notice that port 1 of the WD junction (a 4-port parallel adaptor) is adapted, along with all the linear elements of the WD structure.

Fig. 2. Van Der Pol oscillator circuit in Fig. 2(a) and corresponding WD structure in Fig. 2(b).

#### B. Multiple Nonlinearities Case: Scattering Iterative Method

As discussed in [36] and references therein, the presence of more than one nonlinear element in a WD structure results in unavoidable delay-free loops, i.e., a set of implicit equations involving port variables of different nonlinear elements that make the digital structure not computable without resorting to iterative solvers. In [8], [39] a relaxation method, called SIM, which efficiently solves circuits with multiple one-port nonlinearities in the WD domain is presented. However, the circuits considered in [8], [39] do not contain dynamic elements. Here we show how the approach for modeling inductors and capacitors presented in Section III and Section IV allows to easily handle dynamic nonlinear circuits using SIM.

Let us assume, without loss of generality, that the number of nonlinear elements is  $N_{\rm nl} < N$  and that they are connected

to the first  $N_{\rm nl}$  ports of the WD junction. Let us collect waves incident to and reflected from the elements in the two vectors  $\mathbf{a}[k] = [a_1[k], \dots, a_N[k]]^T$  and  $\mathbf{b}[k] = [b_1[k], \dots, b_N[k]]^T$ , respectively, where the argument k in square brackets indicates signals at kth sampling step. The connection of the elements to the junction implies that the vector of port voltages  $\mathbf{v}$  of the elements is the same defined in Subsection II-A, while the vector of port currents of the elements  $\mathbf{i}[k] = [i_1[k], \dots, i_N[k]]^T$  satisfies  $\mathbf{i}[k] = -\mathbf{j}[k]$ . It follows that  $\mathbf{a}[k] = \mathbf{b}_{\mathbf{J}}[k]$  and  $\mathbf{b}[k] = \mathbf{a}_{\mathbf{J}}[k]$ . SIM is applied at each sampling step k and it requires to perform the following four stages.

1) Initialization: each free parameter  $Z_n[k]$ , with  $1 \le n \le N$ , is set as close as possible to the slope of the tangent line passing through the actual operating point on the i-v curve of the nth one-port, i.e., the series resistance of its Thévenin equivalent.

According to the considerations in Section III, both memoryless and dynamic linear elements can be described by Thévenin (or Norton) equivalents whose parameters are independent of the coordinates of the actual operating point. It follows that in those cases free parameters can be set in an optimal fashion, i.e.  $Z_n[k] = R_{\rm en}[k]$ , where  $R_{\rm en}[k]$  is the Thévenin resistance of the linear element connected to the nth port of the junction, with  $N_{\rm nl} < n \le N$ .

Dealing with nonlinear elements, instead, the exact Thévenin equivalent parameters are not easy to derive in this stage, because they depend on the coordinates of the actual operating point. In fact, assuming each nonlinearity is characterized by a nonlinear equation  $f_n\left(v_n,i_n\right)=0$ , mathematically, the Thévenin series resistance would be given by

$$R_{\rm en}[k] = -\frac{\partial f_n(v_n[k], i_n[k]) / \partial i_n}{\partial f_n(v_n[k], i_n[k]) / \partial v_n} , \quad 1 \le n \le N_{\rm nl} . \quad (47)$$

However, the coordinates of the actual operating point,  $v_n[k]$  and  $i_n[k]$ , are unknown. Therefore, the best we can do is to perform a prediction of the desired slope  $R_{\rm en}[k]$ , based on its values at previous sampling steps.

In the light of this, an effective initialization is performed setting

$$\begin{split} \mathbf{Z}[k] &= \text{diag} \left[ R_{\text{e}1}[k-1], \dots, R_{\text{e}N_{\text{nl}}}[k-1], \\ &R_{\text{e}N_{\text{nl}}+1}[k], \dots, R_{\text{e}N}[k] \right] \;, \end{split}$$

where  $\mathbf{Z}[k]$  is the diagonal matrix of free parameters (port resistances). Vectors of port voltages and incident waves are set to initial guesses  $\mathbf{a}^{(0)}[k] = \left[a_1^{(0)}[k], \dots, a_N^{(0)}[k]\right]^T$  and  $\mathbf{v}^{(0)}[k] = \left[v_1^{(0)}[k], \dots, v_N^{(0)}[k]\right]^T$ , given by

$$\mathbf{a}^{(0)}[k] = [a_1[k-1], \dots, a_N[k-1]]^T ,$$

$$\mathbf{v}^{(0)}[k] = \frac{1}{2} \left[ 2v_1[k-1], \dots, 2v_{N_{\text{nl}}}[k-1],$$

$$a_{N_{\text{nl}}+1}[k-1] + V_{\text{e}N_{\text{nl}}+1}[k], \dots, a_N[k-1] + V_{\text{e}N}[k] \right]^T ,$$

where  $V_{\rm en}[k]$  with  $N_{\rm nl} < n \le N$  are the Thévenin voltage sources of linear elements.

2) Local Scattering Stage: the reflected wave from each memoryless or dynamic linear element is given by  $b_n[k] = V_{\rm en}[k]$  with  $N_{\rm nl} < n \leq N$ , independently of the values of incident wave. Reflected waves from nonlinear elements, instead, depend on the incident waves. It follows that the

vector of reflected waves  $\mathbf{b}^{(\gamma)}[k]$  at iteration  $\gamma \geq 1$  of SIM, where the superscript in round brackets indicates the iteration index, is given by

$$\mathbf{b}^{(\gamma)}[k] = \left[b_1^{(\gamma)}[k], \dots, b_{N_{nl}}^{(\gamma)}[k], V_{eN_{nl}+1}[k], \dots, V_{eN}[k]\right]^T$$

(48)

where, in turn,

$$b_n^{(\gamma)}[k] = 2v_n^{(\gamma)}[k] - a_n^{(\gamma-1)}[k]$$

, with  $1 \le n \le N_{\rm nl}$  . (49)

The way of computing  $v_n^{(\gamma)}[k]$  depends on the actual considered nonlinear element. For instance, if a diode characterized by the extended Shockley diode model is considered, the one-dimensional NR solver described in Subsection II-B can be used with initial guess  $v_n^{(\gamma-1)}[k]$ .

3) Global Scattering Stage: given  $\mathbf{b}^{(\gamma)} = \left[b_1^{(\gamma)}, \dots, b_N^{(\gamma)}\right]^T$ , the vector of incident waves to the elements at iteration  $\gamma$ ,  $\mathbf{a}^{(\gamma)} = \left[a_1^{(\gamma)}, \dots, a_N^{(\gamma)}\right]^T$ , is given by

$$\mathbf{a}^{(\gamma)}[k] = \mathbf{S}[k]\mathbf{b}^{(\gamma)}[k] \tag{50}$$

where S[k] indicates the scattering matrix computed according to equations provided in Subsection II-A and using the diagonal matrix of free parameters Z[k].

4) Convergence Check: if the following convergence condition is met

$$\left\| \mathbf{a}^{(\gamma)}[k] - \mathbf{a}^{(\gamma-1)}[k] \right\|_{2} < \epsilon_{\text{SIM}}$$

(51)

where  $\epsilon_{\text{SIM}}$  is a small tolerance, e.g.  $\epsilon_{\text{SIM}} = 10^{-6}$ , the output port variables of SIM at sampling step k are set as:  $\mathbf{a}[k] = \mathbf{a}^{(\gamma)}[k]$ ,  $\mathbf{b}[k] = \mathbf{b}^{(\gamma)}[k]$  and  $\mathbf{v}[k] = \mathbf{v}^{(\gamma)}[k]$ . Conversely, if condition (51) is not satisfied the iteration index  $\gamma$  is incremented by one such that the local scattering stage and the global scattering stage are performed again. The local scattering stage, the global scattering stage and the convergence check are repeated up to convergence.

Discussion on Convergence: according to the theorem presented in [39] and restated in [8], convergence of SIM applied to a memory-less circuit with nonlinear one-ports, such as diodes with a constitutive equation like (10), is guaranteed when the connection network is reciprocal, the i-v characteristic of each element is monotonically increasing and robust one-dimensional solvers are used in the local scattering stage to compute reflected waves from the WD one-port nonlinear elements. In this paper we consider more general consequences of the theorem in [39] on the analysis of nonlinear circuits with reactances. It turns out that if a discrete-time model based on LMSDM of a capacitor or an inductor can be represented as a Thévenin equivalent with positive series resistance, i.e.,  $\eta_0[k] > 0$ , the corresponding i-v characteristic at each time step k is monotonically increasing. Therefore, SIM converges when applied to circuits characterized by a reciprocal connection network, nonlinear memoryless one-ports with monotonically increasing i-vcharacteristics and linear reactive elements discretized using LMSDMs with  $\eta_0[k] > 0$ . It is worth noticing that, in practice, convergence can be achieved even when SIM is applied to nonlinear circuits for which convergence is not ensured by a theoretical analysis. As a matter of fact, convergence of other mainstream iterative solvers applied to nonlinear circuits, like multivariate NR methods, is not theoretically guaranteed in general.

#### VI. EXAMPLES OF APPLICATION

#### A. A Linear Filter

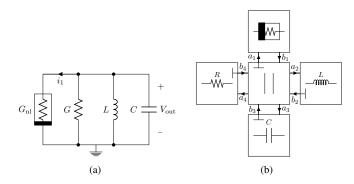

As a first example of application of the proposed approach for modeling dynamic elements, let us consider the simple first-order filter in Fig. 3(a) and its WD realization [1] in Fig. 3(b). The analysis of a linear filter like the one in Fig. 3 allows us to compare the behavior of WD models of the capacitor based on different LMSDMs with an "exact" ground truth.

Fig. 3. Linear filter circuit in Fig. 3(a) and corresponding WD structure in Fig. 3(b).

In fact, we can express the time evolution of the voltage  $V_{\rm out}$  across the resistor  $R_{\rm out}$  in closed-form. Assuming that the voltage across the capacitor at t=0 is zero, we have that

$$V_{\text{out}}(t) = V_{\text{in}} \frac{R_{\text{out}}}{R_{\text{tot}}} e^{-t/(R_{\text{tot}}C)}, \qquad (52)$$

where  $V_{\rm in}$  is a constant and  $R_{\rm tot}=R_{\rm in}+R_{\rm out}.$  We set  $V_{\rm in}=5$  V,  $R_{\rm in}=12~\Omega,~R_{\rm out}=3~\Omega$  and  $C=100~\mu{\rm F}.$

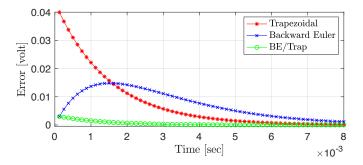

In a first experiment, the capacitor is implemented using three alternative discretization techniques: the traditional trapezoidal method, i.e., scattering relation (35) and adaptation condition (34), the BE method, i.e., scattering relation (39) and adaptation condition (38), and a combination of BE and trapezoidal in which BE is used to compute the first sample, while trapezoidal is used for the following samples. A fixed step-size  $h[k] = 1/F_s$  sec with  $F_s = 8$  kHz is employed. The errors with respect to the ground truth computed using (52) are shown in Fig. 4; the red line with asterisks refers to trapezoidal, the blue line with crosses refers to BE, while the green line with circles refers to the above combination. Despite trapezoidal is in general more accurate than BE, the error of the former at first samples is higher because the first sample is computed relying on a bad approximation of the derivative of the voltage across the capacitor at sampling time  $t_{k-1}$ . As shown in Fig. 4, a good strategy to cope with this problem is to use the BE method for computing the first sample and then switch to the trapezoidal method. In order to properly perform the switching between BE and trapezoidal maintaining adaptation, scattering relation (35) and adaptation condition (34) are used at the first sampling step, while scattering relation (39) and adaptation condition (38) are used for the following steps.

Fig. 4. WD implementations of the linear filter; comparison between three discretization methods with fixed step-size. The three lines represent the errors of the signals  $V_{\rm out}$  w.r.t. the ground truth, referred to the implementations in which the trapezoidal method, the BE method and a combination of the two (i.e., BE for the first sample and then trapezoidal) are used.

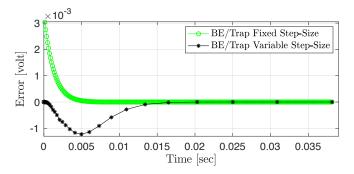

Fig. 5. WD implementation of the linear filter using a combination of BE and trapezoidal methods. A comparison between the fixed and the variable stepsize cases is presented. The two lines represent the errors of the signals  $V_{\rm out}$  w.r.t. the ground truth. The green line with circles refers to the fixed step-size case; the number of circles, i.e., 311, is the number of samples. The black line with asterisks refers to the variable step-size case; the number of asterisks, i.e., 54, is the number of samples. In both cases the MSE is  $1.6 \times 10^{-7}$ .

In a second experiment, we implement a new version of the above combination of BE and trapezoidal methods based on a variable step-size. We perform an ad hoc optimization of the step-sizes in order to match the mean squared error (MSE) of the fixed sampling step implementation considered in the previous experiment, i.e.,  $1.6 \times 10^{-7}$ . We obtain an implementation with variable step-size employing 54 samples versus the 311 samples used in the fixed step-size case to simulate the same transient from t = 0 seconds to t = 0.039seconds. This result demonstrates that the simulation of the transient can be performed almost six times faster using a variable step-size, while preserving the MSE of the fixed stepsize case. Fig. 5 shows the evolution in time of the error; the kth green circle indicates the error referred to the kth sample in the fixed step-size case, while the kth black asterisk indicates the error referred to the kth sample in the variable step-size case. Notice that in the variable step-size case asterisks are dense at the beginning of the transient and increasingly sparse as time t increases, since the signal  $V_{\rm out}$  varies less and less.

Finally, we performed Kirchhoff domain discrete-time simulations [42] of the simple circuit in Fig. 3(a), based on the same LMSDMs discussed in this Subsection, and we verified that the results are identical (up to numerical precision) to those obtained with the presented WD implementations.

#### B. Van Der Pol Oscillator

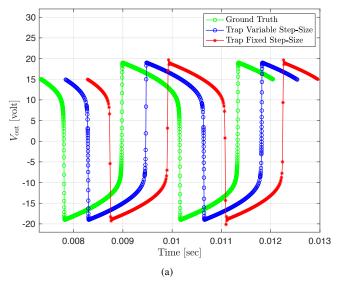

In this Subsection, we show how a variable step-size can be useful to improve the WD realization of a relaxation oscillator, like the Van Der Pol oscillator [61] in Fig. 2(a), preventing possible artifacts.

The circuit parameters are  $R=1/G=260~\Omega,~L=5.1$  mH and  $C=1.442~\mu {\rm F}.$  The nonlinear conductor  $G_{\rm nl}$  is characterized by

$$f(v,i) = i + \alpha v - \beta v^3 = 0 .$$

where  $\alpha$  and  $\beta$  are two scalar coefficients. We set  $\alpha=0.2648$  and  $\beta=0.000976$ .

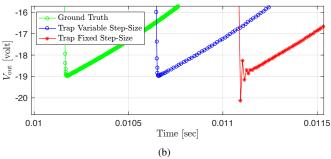

The WD structure corresponding to the nonlinear circuit in Fig. 2(a) is represented in Fig. 2(b). First, a WD implementation of the oscillator employing the trapezoidal method with fixed step-size is validated, verifying that it matches with a corresponding Kirchhoff implementation based on nodal analysis and a NR solver. These two implementations are performed with an extremely high sampling frequency, i.e.,  $F_{GT} = 1024$ kHz, in order to obtain a reliable ground truth. Then, other WD implementations with fixed sampling rate  $F_s = 96 \text{ kHz}$ and variable step-size are developed. The variable step-size is adapted according to the considerations about the estimated LTE discussed in Subsection IV-E. As a constraint in the process of adaptation of the step-size we impose that the average number of samples per period of the periodic output signal  $V_{\text{out}}$  matches the fixed step-size case, i.e., about 225 samples per period. Fig. 6(a) shows three versions of the  $V_{out}$ signal; the green line with circles refers to the ground truth, the blue line with circles refers to the WD implementation based on fixed sampling rate,  $F_s = 96$  kHz, while the red line with asterisks refers to the WD implementation based on variable step-size. A portion of Fig. 6(a) is zoomed in Fig. 6(b), which clearly shows an artifact due to the abrupt change of signal amplitude and a consequent high LTE, characterizing the fixed step-size curve. Such an artifact, instead, is highly attenuated when the adaptive step-size is used, because samples with high estimated LTE are discarded and recomputed after reducing the step-size. We deduce that it is possible to obtain a WD implementation of the oscillator with variable step-size which employs the same average number of samples per period of the fixed step-size implementation ( $F_s = 96 \text{ kHz}$ ), but does not suffer from the same artifacts due to discretization errors.

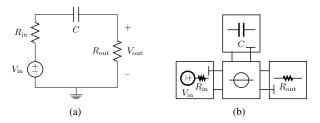

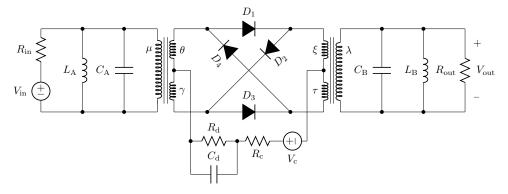

#### C. Dynamic Diode-based Ring Modulator

The dynamic digital model of the audio ring modulator circuit presented in [62], [63] is reported in Fig. 7. A WD implementation based on SIM of a similar circuit without inductors and capacitors is described in [8]. In this Subsection, we show that SIM can also be applied to the circuit in Fig. 7 containing dynamic elements and multiple nonlinear diodes, according to the considerations discussed in Subsection V-B. As in [8], the four diodes are assumed to be characterized by the nonlinear constitutive equation (10). We set the parameters of the diode model as  $I_{\rm s}=10^{-9}$  nA,  $\eta=2.19$ ,  $V_{\rm t}=26$  mV,  $R_{\rm s}=1$  m $\Omega$  and  $R_{\rm p}=100$  k $\Omega$ . The turn ratios of the ideal

Fig. 6. WD implementations of the Van Der Pol oscillator; three lines indicate different versions of the output signal  $V_{\rm out}$  (shifted in time for improving visibility). Two trapezoidal methods with fixed and variable step-size are compared in Fig. 6(a). The green line with circles indicates the ground truth. The blue line with circles refers to the variable step-size case. The red line with asterisks refers to the fixed step-size case. In both variable and fixed step-size cases the average number of samples per period is 225. Fig. 6(b) shows a zoomed detail of Fig. 6(a).

transformers are  $\theta/\mu = \gamma/\mu = \xi/\lambda = \tau/\lambda = 1/2$ , where  $\theta$ ,  $\gamma$ ,  $\mu$ ,  $\xi$ ,  $\tau$  and  $\lambda$  are the numbers of turns in each winding. The other parameters of the circuit are  $L_{\rm A} = L_{\rm B} = 0.8$  H,  $C_{\rm A} = C_{\rm B} = C_{\rm d} = 1$  nF,  $R_{\rm d} = 50~\Omega$ ,  $R_{\rm in} = 80~\Omega$ ,  $R_{\rm c} = 1~\Omega$ ,  $R_{\rm out} = 600~\Omega$ . In the following, we will assume that the input voltage signal and the carrier voltage signal are two sinusoids  $V_{\rm in}(t) = \sin(2\pi f_{\rm in}t)$  and  $V_{\rm c}(t) = \sin(2\pi f_{\rm c}t)$  with fundamental frequencies  $f_{\rm in} = 150~{\rm Hz}$  and  $f_{\rm c} = 50~{\rm Hz}$ , respectively, although other sinusoids with different parameters have been successfully tested. The output signal  $V_{\rm out}$  is the voltage across the resistor  $R_{\rm out}$ . The WD structure corresponding to the circuit in Fig. 7 is shown in Fig. 8. The 13-port WD junction in Fig. 8 is characterized by a scattering matrix  $\bf S$  which can be computed using equation (4) and setting  $\bf Q = [\bf F, \bf I]$ , where  $\bf I$  is the  $4\times 4$  identity matrix and matrix  $\bf F$  is defined as

$$\mathbf{F} = \begin{bmatrix} 0.5 & 0.5 & -0.5 & -0.5 & 1 & 0 & 1 & 0 & 0 \\ 1 & -1 & 1 & -1 & 0 & 0 & 0 & 0 & 0 \\ -0.5 & 0.5 & 0.5 & -0.5 & 0 & 1 & 0 & 1 & 0 \\ 1 & -1 & 1 & -1 & 0 & 0 & 0 & 0 & 1 \end{bmatrix}$$

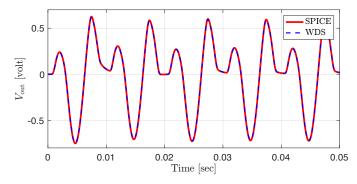

In a first implementation, WD models of capacitors and inductors employ the traditional trapezoidal discretization method

Fig. 7. Dynamic ring modulator circuit.

Fig. 8. WD structure corresponding to the circuit in Fig. 7.

Fig. 9. WD implementation based on SIM employing trapezoidal discretization method with fixed step-size vs LTspice implementation.

with fixed step-size and the sampling frequency is  $F_{\rm s}=41$  kHz. Fig. 9 shows the high matching between the output signal  $V_{\rm out}$  obtained by the WD implementation based on SIM and the same signal obtained by a LTspice software implementation.

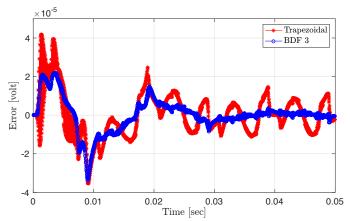

In order to test whether a LMSDM of higher order could

Fig. 10. Comparison between WD implementations of the ring modulator based on SIM employing trapezoidal method and BDF 3, both with fixed step-size. The two curves represent the errors of  $V_{\rm out}$  signals w.r.t. the ground truth. The red line with asterisks refers to the trapezoidal method. The blue line with circles refers to BDF 3.

provide better results in terms of accuracy, we performed a comparison between the already tested WD implementation employing the trapezoidal method and another WD implementation employing BDF 3, i.e., scattering relations (42) and (43) with M=3. In both implementations a fixed stepsize is used and the sampling frequency is  $F_s = 41$  kHz. A ground truth is obtained linearly interpolating the output samples of a WD implementation employing the trapezoidal method and sampling frequency  $F_{\rm GT}=512$  kHz. Two errors are computed subtracting the ground truth to the output signals  $V_{\rm out}$  of the compared WD implementations. These two errors are plotted in Fig. 10; the red line with asterisks indicates the error obtained with the trapezoidal method, while the blue line with circles indicates the error obtained with BDF 3. Fig. 10 shows that the error is generally smaller in amplitude when BDF 3 is used. In particular, the MSE referred to the 0.05 seconds of simulation in the trapezoidal case is  $1.34 \times 10^{-10}$ , while in the BDF 3 case it is  $7.28 \times 10^{-11}$ .

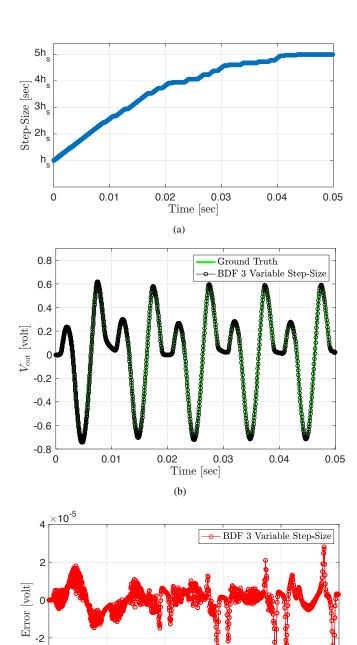

A WD implementation of the dynamic ring modulator circuit using BDF 3 with variable step-size is tested in the last experiment. An initial step-size  $h_{\rm s}=1/(2F_{\rm s})$  with  $F_{\rm s}=41$  kHz is set. The step-size is then gradually increased up to five times with respect to the initial value as shown in Fig. 11(a).

The obtained  $V_{\text{out}}$  signal is represented by the black line with circles shown in Fig. 11(b) along with the ground truth (green line) also used in the previous experiment. The corresponding error, computed subtracting the ground truth to the output signal  $V_{\text{out}}$  of the WD implementation based on BDF 3 with variable step-size, is shown in Fig. 11(c). Let us now make a comparison between the  $V_{\rm out}$  signal in the variable step-size case and the same signal in the fixed step-size case presented in the previous experiment. As far as the MSE with respect to the ground truth in the first 0.05 seconds of the simulation is concerned, we get  $5.48 \times 10^{-11}$  in the variable step-size case versus the already computed MSE in the fixed step-size case, i.e,  $7.28 \times 10^{-11}$ . Therefore, we get a comparable MSE in the two cases, while reducing the number of samples in the variable step-size case. In fact, the number of samples employed for the first 0.05 seconds of the simulation is 1286 samples in the variable step-size case, versus 2048 in the fixed step-size case.

#### VII. DISCUSSION, CONCLUSIONS AND FUTURE WORK

In this article, we presented general WD models of capacitors and inductors based on LMSDMs with variable step-size along with their general adaptation conditions. We showed that the use of LMSDMs alternative to the trapezoidal method with fixed step-size could be advantageous in various situations. The results that we presented pave the way towards the modeling of nonlinear WD structures characterized by adaptive discretization methods that change automatically according to the properties of the processed signals. In this regard, it is important to mention the fact that, when dealing with discretization methods based on variable step-size, some operations on the input and output signals of the WD structure are required for making the implementation compatible with traditional digital audio processing tools based on fixed sampling step. In fact, an interpolation of the samples of the input signals should be performed, so that an eventually non-uniform resampling operation can be executed. Similarly, the non-uniformly spaced samples of the output signals should be interpolated, so that a resampling operation at a fixed rate can be performed.

Moreover, in this article, we showed how the WD fixed-point method SIM, that we recently developed for efficiently implementing circuits with multiple one-port nonlinearities, can be extended to accommodate dynamic nonlinear circuits using the proposed general WD models of dynamic elements. SIM, therefore, proves promising for Virtual Analog modeling of increasingly complex circuits. Future research will be devoted to the application of SIM to dynamic active circuits with multiple multi-port nonlinearities. Recent developments in the convergence analysis of nonlinear delay-free loop filter networks [63], [64], in fact, could help us find new theoretical tools for studying the convergence of SIM applied to a broader class of circuits than the one considered in [8], [39] and in this article.

More generally, we showed how capacitors and inductors can be implemented like time-varying resistive voltage (or current) sources in the WD domain. It follows that the proposed WD models of dynamic elements can be readily used in

Fig. 11. WD implementation of the ring modulator based on SIM employing BDF 3 with variable step-size. Fig. 11(a) shows the variation in time of the step-size h[k]. Fig. 11(b) shows  $V_{\rm out}$  signals; the green line refers to the ground truth, while the black line with circles refers to the WD implementation employing BDF 3 with variable step-size. Fig. 11(c) shows the error of  $V_{\rm out}$  signal w.r.t. the ground truth.

(c)

Time [sec]

0.03

0.04

0.05

0.02

0

0.01

conjunction with existing methods alternative to SIM for the WD implementation of circuits with multiple nonlinearities [27], [29], [38].

The proposed approach for the WD modeling of dynamic elements could also be applied for generalizing the WD models of time-varying reactances discussed in [65] to a larger class of discretization methods.

Despite voltage waves considered in this article are the most widespread in the literature on WDFs, WD structures based on alternative types of waves, such as those characterized by different units of measure [48], [57]–[59] or two free parameters per port instead of one [36], [57], have recently proved to possess peculiar interesting properties. WD models of dynamic elements based on LMSDMs and generalized definitions of waves, including the most used as particular cases, can be straightforwardly derived combining the modeling approach used in recent publications [48], [57], [58], [65] to the results presented in this manuscript.

Finally, a systematic study on the accuracy and stability properties of specific LMSDMs with variable step-size in WD structures is postponed to future research.

#### REFERENCES

- [1] A. Fettweis, "Wave digital filters: Theory and practice," *Proc. IEEE*, vol. 74, no. 2, pp. 270–327, Feb. 1986.

- [2] K. Meerkötter and R. Scholz, "Digital simulation of nonlinear circuits by wave digital filter principles," in *IEEE Int. Symp. Circuits Syst.*, May 8–11 1989, pp. 720–723.

- [3] A. Sarti and G. De Sanctis, "Systematic methods for the implementation of nonlinear wave-digital structures," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, pp. 460–472, Feb. 2009.

- [4] G. De Sanctis and A. Sarti, "Virtual analog modeling in the wave-digital domain," *IEEE Trans. Audio, Speech, Language Process.*, vol. 18, pp. 715–727, May 2010.

- [5] J. Pakarinen and M. Karjalainen, "Enhanced wave digital triode model for real-time tube amplifier emulation," *IEEE Trans. Audio, Speech, Language Process.*, vol. 18, pp. 738–746, May 2010.

- [6] R. C. D. Paiva, S. D'Angelo, J. Pakarinen, and V. Välimäki, "Emulation of operational amplifiers and diodes in audio distortion circuits," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, pp. 688–692, Oct. 2012.

- [7] K. J. Werner, V. Nangia, J. O. Smith, and J. S. Abel, "A general and explicit formulation for wave digital filters with multiple/multiport nonlinearities and complicated topologies," in *Proc. IEEE Workshop on Applicat. of Signal Process. to Audio and Acoust. (WASPAA)*, New Paltz, NY, Oct. 18–21 2015.

- [8] A. Bernardini, K. J. Werner, P. Maffezzoni, and A. Sarti, "Wave digital modeling of the diode-based ring modulator," in *Proc. 144th Conv. Audio Eng. Soc.*, Milan, Italy, Ma 24–26 2018, conv. paper #10015.

- [9] A. Bernardini and A. Sarti, "Towards inverse virtual analog modeling," in *Proc. 22nd Conf. Digital Audio Effects (DAFx 19)*, Birmingham, UK, Sept. 2–6 2019, accepted for publication.

- [10] J. O. Smith, "Physical modeling using digital waveguides," Computer Music Journal, vol. 16, no. 4, pp. 74–91, 1992.

- [11] D. Rocchesso and J. O. Smith, "Generalized digital waveguide networks," *IEEE Trans. on Speech and Audio Process.*, vol. 11, no. 3, pp. 242–254, May 2003.

- [12] F. Pedersini, A. Sarti, and S. Tubaro, "Object-based sound synthesis for virtual environments using musical acoustics," *IEEE Signal Process. Mag.*, vol. 17, no. 6, pp. 37–51, Nov. 2000.

- [13] S. Bilbao, Wave and Scattering Methods for Numerical Simulation, 1st ed. New York: John Wiley & Sons, Oct. 2004.

- [14] R. Rabenstein, S. Petrausch, A. Sarti, G. D. Sanctis, C. Erkut, and M. Karjalainen, "Blocked-based physical modeling for digital sound synthesis," *IEEE Signal Processing Magazine*, vol. 24, no. 2, pp. 42–54, March 2007.

- [15] M. Karjalainen, "Efficient realization of wave digital components for physical modeling and sound synthesis," *IEEE Transactions on Audio, Speech, and Language Processing*, vol. 16, no. 5, pp. 947–956, July 2008.

- [16] A. Bernardini, F. Antonacci, and A. Sarti, "Wave digital implementation of robust first-order differential microphone arrays," *IEEE Signal Processing Letters*, vol. 25, no. 2, pp. 253–257, Feb 2018.

- [17] K. J. Werner, J. O. Smith, and J. S. Abel, "Wave digital filters adaptors for arbitrary topologies and multiport linear elements," in *Proc. 18th Conf. Digital Audio Effects*, Trondheim, Norway, Nov. 30 – Dec. 3 2015.

- [18] K. J. Werner, W. R. Dunkel, M. Rest, M. J. Olsen, and J. O. Smith, "Wave digital filter modeling of circuits with operational amplifiers," in *Proc. 24th European Signal Processing Conference (EUSIPCO)*, Aug. 2016, pp. 1033–1037.

- [19] R. C. D. de Paiva, J. Pakarinen, V. Välimäki, and M. Tikander, "Real-time audio transformer emulation for virtual tube amplifiers," EURASIP J. on Advances in Signal Process., Jan. 2011.

- [20] A. Bernardini, K. J. Werner, A. Sarti, and J. O. Smith, "Multi-port nonlinearities in wave digital structures," in *Proc. IEEE Int. Symp. Signals Circuits Syst.*, Iasi, Romania, July 9–10 2015.

- [21] K. J. Werner, V. Nangia, A. Bernardini, J. O. Smith III, and A. Sarti, "An improved and generalized diode clipper model for wave digital filters," in *Proc. 139th Conv. Audio Eng. Soc.*, New York, NY, Oct. 2015, conv. paper. #9360.

- [22] A. Bernardini and A. Sarti, "Dynamic adaptation of instantaneous nonlinear bipoles in wave digital networks," in *Proc. 24th European Signal Process. Conf.*, Budapest, Hungary, Aug. 29 – Sept. 2 2016.

- [23] A. Bernardini and A. Sarti, "Canonical piecewise-linear representation of curves in the wave digital domain," in *Proc. 25th European Signal Processing Conference (EUSIPCO)*, Aug 2017, pp. 1125–1129.

- [24] J. Pakarinen and M. Karjalainen, "Enhanced wave digital triode model for real-time tube amplifier emulation," *IEEE Transactions on Audio, Speech, and Language Processing*, vol. 18, no. 4, pp. 738–746, May 2010.

- [25] S. D'Angelo, J. Pakarinen, and V. Välimäki, "New family of wave-digital triode models," *IEEE Trans. Audio, Speech, Language Process.*, vol. 21, pp. 313–321, Feb. 2013.

- [26] A. Bernardini, K. J. Werner, A. Sarti, and J. O. Smith, "Modeling a class of multi-port nonlinearities in wave digital structures," in *Proc. European Signal Process. Conf.*, Nice, France, Aug. 31 – Sept. 4 2015, pp. 669–673.

- [27] K. J. Werner, V. Nangia, J. O. Smith III, and J. S. Abel, "Resolving wave digital filters with multiple/multiport nonlinearities," in *Proc. 18th Int. Conf. Digital Audio Effects*, Trondheim, Norway, Nov. 2015, pp. 387–394.

- [28] A. Bernardini, K. J. Werner, A. Sarti, and J. O. Smith III, "Modeling nonlinear wave digital elements using the Lambert function," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 8, pp. 1231–1242, Aug. 2016.

- [29] M. J. Olsen, K. J. Werner, and J. O. Smith III, "Resolving grouped nonlinearities in wave digital filters using iterative techniques," in *Proc.* 19th Int. Conf. Digital Audio Effects, Brno, Czech Republic, Sept. 2016, pp. 279–286.

- [30] D. Hernandez and J. Huang, "Emulation of junction field-effect transistors for real-time audio applications," *IEICE Electronics Express*, May 2016.

- [31] A. Sarti and G. De Poli, "Toward nonlinear wave digital filters," *IEEE Trans. Signal Process.*, vol. 47, pp. 1654–1668, June 1999.

- [32] C.-W. Ho, A. E. Ruehli, and P. A. Brennan, "The modified nodal approach to network analysis," *IEEE Trans. Circuits Syst.*, vol. 22, no. 6, pp. 504–509, June 1975.

- [33] D. T. Yeh, J. S. Abel, and J. O. Smith, "Automated physical modeling of nonlinear audio circuits for real-time audio effects - part 1: Theoretical development," *IEEE Trans. Audio, Speech, Language Process.*, vol. 18, pp. 728–737, May 2010.

- [34] M. Holters and U. Zölzer, "Physical modeling of a wah-wah effect pedal as a case study for application of the nodal dk method to circuits with variable parts," in *Proc. 14th Conf. Digital Audio Effects*, Paris, France, Sept. 19–23 2011.

- [35] A. Falaize and T. Hélie, "Passive guaranteed simulation of analog audio circuits: A port-hamiltonian approach," *Applied Sciences*, vol. 6, no. 10, 2016

- [36] A. Bernardini and A. Sarti, "Biparametric wave digital filters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 7, pp. 1826–1838, July 2017.

- [37] G. Borin, G. De Poli, and D. Rocchesso, "Elimination of delay-free loops in discrete-time models of nonlinear acoustic systems," *IEEE Trans. Speech Audio Process.*, vol. 8, no. 5, pp. 597–605, Sept. 2000.

- [38] T. Schwerdtfeger and A. Kummert, "A multidimensional approach to wave digital filters with multiple nonlinearities," in 22nd Proc. European

- Signal Process. Conf. (EUSIPCO), Lisbon, Portugal, Sept. 1–5 2014, pp. 2405–2409.

- [39] A. Bernardini, P. Maffezzoni, L. Daniel, and A. Sarti, "Wave-based analysis of large nonlinear photovoltaic arrays," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 4, pp. 1363–1376, Apr. 2018.

- [40] A. Bernardini, A. Sarti, P. Maffezzoni, and L. Daniel, "Wave digital-based variability analysis of electrical mismatch in photovoltaic arrays," in *Proc. IEEE International Symposium on Circuits and Systems (IS-CAS)*, May 2018, pp. 1–5.

- [41] G. G. Dahlquist, "A special stability problem for linear multistep methods," *BIT Numerical Mathematics*, vol. 3, no. 1, pp. 27–43, Mar. 1963.

- [42] J. Vlach and K. Singhal, Computer Methods for Circuit Analysis and Design. New York, NY: Van Nostrand Reinhold Company, 1983.

- [43] A. Vladimirescu, The SPICE Book. New York, NY: Wiley, 1994.

- [44] F. G. Germain and K. J. Werner, "Design principles for lumped model discretisation using Möbius transforms," in *Proc. 18th Int. Conf. Digital Audio Effects*, Trondheim, Norway, Nov. 2015, pp. 371–378.

- [45] C. W. Gear, Numerical Initial Value Problems in Ordinary Differential Equations. Upper Saddle River, NJ, USA: Prentice Hall PTR, 1971.

- [46] T. Felderhoff, "Simulation of nonlinear circuits with period doubling and chaotic behavior by wave digital filter principles," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 41, no. 7, pp. 485–491, Jul 1994.

- [47] D. Fränken and K. Ochs, "Improving wave digital simulation by extrapolation techniques," *AEÜ Int. J. of Electronics and Commun.*, vol. 56, no. 5, pp. 327 336, 2002.

- [48] K. J. Werner, "Virtual analog modeling of audio circuitry using wave digital filters," Ph.D. diss., Stanford Univ., CA, Dec. 2016, [Online at https://searchworks.stanford.edu/view/11891203; accessed 1-July-2019].

- [49] K. Ochs, "Passive integration methods: Fundamental theory," *AEÜ Int. J. of Electronics and Commun.*, vol. 55, no. 3, pp. 153 163, 2001.

- [50] D. Fränken and K. Ochs, "Wave digital simulation of nonlinear electrical networks by means of passive Runge-Kutta methods," in *Proc. IEEE Int. Symposium on Circuits and Systems (Cat. No.01CH37196)*, vol. 3, May 6–9 2001, pp. 469–472 vol. 2.

- [51] D. Fränken and K. Ochs, "Synthesis and design of passive Runge-Kutta methods," AEÜ - Int. J. of Electronics and Commun., vol. 55, no. 6, pp. 417–425, 2001.

- [52] D. Fränken, K. Ochs, and M. Schmidt, "A passive two-step Runge-Kutta method for the simulation of nonlinear electrical networks," in *Proc. Int. Symposium on Nonlinear Theory and its Applications*, vol. 3, Xi'an, PRC, Oct. 7–11 2001, pp. 347–350.

- [53] D. Fränken and K. Ochs, "Automatic step-size control in wave digital simulation using passive numerical integration methods," AEÜ - Int. J. Electron. Commun., vol. 58, no. 6, pp. 391–401, 2004.

- [54] M. J. Olsen, K. J. Werner, and F. G. Germain, "Network variable preserving step-size control in wave digital filters," in *Proc. 20th Int. Conf. Digital Audio Effects*, Edinburgh, UK, Sept. 2017, pp. 200–207.

- [55] D. Calahan, "Numerical considerations for implementation of a nonlinear transient circuit analysis program," *IEEE Transactions on Circuit Theory*, vol. 18, no. 1, pp. 66–73, Jan. 1971.

- [56] G. O. Martens and H. H. Lê, "Wave digital adapters for reciprocal second-order sections," *IEEE Transactions on Circuits and Systems*, vol. 25, no. 12, pp. 1077–1083, Dec 1978.

- [57] A. Bernardini, K. J. Werner, J. O. Smith, and A. Sarti, "Generalized wave digital filter realizations of arbitrary reciprocal connection networks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 2, pp. 694–707, Feb 2019.

- [58] K. J. Werner, A. Bernardini, J. O. Smith, and A. Sarti, "Modeling circuits with arbitrary topologies and active linear multiports using wave digital filters," *IEEE Transactions on Circuits and Systems I: Regular Papers*, pp. 1–14, 2018.

- [59] G. Kubin, "Wave digital filters: Voltage, current, or power waves?" in Proc. IEEE Int. Conf. Acoust., Speech, Signal Process., Tampa, FL, Apr. 26–29 1985, pp. 69–72.

- [60] L. O. Chua and P. Y. Lin, Computer-Aided Analysis of Electronic Circuits: Algorithms and Computational Techniques. Prentice Hall Professional Technical Reference, 1975.

- [61] B. Van Der Pol, "The nonlinear theory of electric oscillations," *Proceedings of the Institute of Radio Engineers*, vol. 22, no. 9, pp. 1051–1086, Sept 1934.

- [62] R. Hoffmann-Burchardi, "Digital simulation of the diode ring modulator for musical applications," in *Proc. 11th Int. Conf. Digital Audio Effects*, Espoo, Finland, September 1–4 2008, pp. 165–168.

- [63] F. Fontana and E. Bozzo, "Newton-Raphson solution of nonlinear delay-free loop filter networks," *IEEE/ACM Transactions on Audio, Speech, and Language Processing*, vol. 27, no. 10, pp. 1590–1600, Oct 2019.