### LOG-BASED TRANSACTIONAL MEMORY

by

Kevin E. Moore

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

2007

## **Abstract**

A pressing challenge in the movement to an explicitly parallel model of computing is to give programmers, compiler writers and language designers a more powerful means of synchronization. My doctoral research attacks this problem by investigating practical, high performance transactional memory systems. Transactional memory gives programmers the ability to declare the synchronization properties their programs need, without requiring that they develop a mechanism (e.g., a locking scheme) to enforce these properties. Furthermore, transactions may be nested to allow programmers to build thread-safe libraries without exposing implementation details such as locking conventions to higher levels of software.

Transactional memory systems may be implemented in software, in hardware, or in a combination of the two. Typically, transactional memory systems do not limit the amount of memory a transaction may access nor the length of time a transaction may run. Though intuitive for programmers, that model is poorly suited for direct implementation in hardware, which is limited to structures of fixed size. Ideally, an implementation of transactional memory should: (1) make the expected common case (short transactions that commit) fast; (2) defer rare and difficult-to-implement cases to software; (3) allow transactions of any size and duration; and, (4) allow programmers to nest transactions to arbitrary depths.

In my doctoral research, I developed Log-Based Transactional Memory (LogTM), a transactional memory system that combines software-based *version management* (with limited hardware support) and conservative hardware *conflict detection* to support arbitrary-size transactions with limited hardware. Version management requires maintaining multiple versions of data values: old values, the values at the start of the transaction, and new values, which are generated inside a transaction. Any memory location modified in a transaction will hold its new value if the transaction commits, and its old value if the transaction aborts. LogTM performs version management by eagerly updating memory in place during transactions and sav-

ing old values in a per-thread transaction log. No further action is needed to commit a transaction since new values are kept in place. To abort a transaction, LogTM restores saved values from the log. Fortunately, (for most workloads) aborts are rare. Because aborts are infrequent, LogTM can reduce hardware complexity by performing aborts in software without degrading performance. Conflict detection identifies overlaps between the write set of each transaction with the read set or write set of other concurrent transactions. Like other hardware transactional memory systems, LogTM detects conflicts on cached data by augmenting the cache coherence mechanism, e.g., by adding a read (R) and write (W) bit to each cache line. LogTM implementations extend this mechanism (e.g., with sticky states, which enable the directory to continue to send coherence messages to a processor for a blocks it has evicted from its cache) so that processors can conservatively detect conflicts even for blocks not present in the cache.

Before I began work on LogTM, the only published hardware transactional memory systems relied heavily on the cache. The size and associativity of the cache limited the scope of transactions. LogTM's unique log-based version management combined with innovative sticky states allow it to break this dependence on the cache without adding complex hardware. Unlike previous schemes, which relied on keeping old values in memory and storing new values in the cache, LogTM stores new and old versions in separate memory locations, which may be cached and evicted independently. Like the stack, the transaction log is a part of a thread s virtual memory and is effectively unbounded. Sticky states, although part of the coherence mechanism, break the dependence between conflict detection and caching. By allowing conflict detection on blocks after eviction, sticky states enable transactions whose read and write sets exceed the capacity or associativity of the cache. Perhaps most importantly, LogTM guarantees that transactions appear atomic to applications, but it allows some lower-level software to observe transactions. LogTM uses hardware to perform the most performance-critical tasks, tracking read and write sets and detecting conflicts, but leaves rare and complicated tasks, such as aborting transactions, to software.

## Acknowlegements

I owe the completion of this dissertation to the love, support, and guidance of my family friends, colleagues and sponsors.

First, I thank the National Science Foundation for sponsoring my research with grants CCF-0085949, CCR-0105721, EIA/CNS-020528, and CCR-03248 and Sun Microsystems and IBM for their support of my research and that of my colleagues in the Multifacet group at the University of Wisconsin.

I thank all of my colleagues and collaborators who have helped me to develop and refine the ideas in this dissertation and who have helped me develop as a researcher and as a person. Thanks especially to everyone who worked with me developing, extending and evaluating LogTM: Jayaram Bobba, Mark Hill, Ben Liblit, Michael Marty, Michelle Moravan, Mike Swift, Haris Volos, David Wood and Luke Yen. I also sincerely thank Alaa Alameldeen, Brad Beckman, Milo Martin and Min Xu for being excellent colleagues and friends and for creating the simulation infrastructure on which I relied for all of my experiments. And, I sincerely thank Dan Sorin for introducing me to Wisconsin and for being a valuable friend and mentor for many years.

Finally, I owe deepest gratitude to my parents who have encouraged my curiosity and creativity my whole life. I thank my mother for sharing with me her love of learning and for teaching me nearly all that I know about writing and language. I thank my father, who is my role model for living, for teaching me not to lose sight of what matters most, and for introducing me to computers. I am who I am because of them, their support and their love.

# Table of Contents

| Abstract                                           | 1   |

|----------------------------------------------------|-----|

| Acknowlegements                                    | iii |

| Table of Contents                                  | iv  |

| List of Figures                                    | ix  |

| List of Tables                                     | X   |

| Chapter 1 Introduction                             | 1   |

| 1.1 Motivation                                     | 1   |

| 1.2 Synchronization                                | 2   |

| 1.2.1 Serialization                                | 2   |

| 1.2.2 The Trouble with Locks                       | 3   |

| 1.2.3 Transactions                                 | 4   |

| 1.3 Transactional Memory                           | 4   |

| 1.3.1 Limitations of Software Transactional Memory | 5   |

| 1.4 Hardware Transactional Memory                  | 6   |

| 1.4.1 Implementing Hardware Transactional Memory   | 6   |

| 1.4.2 Virtualizing HTM                             | 7   |

| 1.5 Problem Statement                              | 7   |

| 1.6 LogTM                                          | 8   |

| Chapter 2 Background                               | 10  |

| 2.1 Cache-Coherent Multiprocessors                 | 10  |

| 2.2 Multi-Threaded Programming                     | 12  |

| 2.3 Transactional Programming                      | 13  |

| 2.3.1 Transactional Memory                         | 14  |

| 2.4 Concurrency Control                            | 15  |

| 2.4.1 Concurrency Control for Mutual Exclusion           | 15 |

|----------------------------------------------------------|----|

| 2.4.2 Lock-Based Concurrency Control in Database Systems | 15 |

| 2.4.3 Optimistic Concurrency Control in Database Systems | 17 |

| 2.5 Logging and Recovery in Database Systems             | 18 |

| 2.6 Transactional Memory Systems                         | 18 |

| 2.6.1 Hardware Support for Database Transactions         | 19 |

| 2.6.2 Early Hardware Transactional Memory Systems        | 19 |

| 2.6.3 Hardware Transactional Memory                      | 21 |

| 2.6.4 Recently Proposed HTMs                             | 23 |

| Chapter 3 Log-Based Transactional Memory (LogTM)         | 25 |

| 3.1 Eager Version Management                             |    |

|                                                          |    |

| 3.1.1 The Transaction Log                                | 20 |

| 3.1.2 Transaction Commit                                 | 28 |

| 3.1.3 Transaction Abort                                  | 28 |

| 3.2 Eager Conflict Detection                             | 28 |

| 3.2.1 Requirements                                       | 29 |

| 3.2.2 Example Implementation                             | 29 |

| 3.3 Conflict Resolution                                  | 31 |

| 3.4 LogTM API                                            | 31 |

| 3.5 Example                                              | 33 |

| 3.6 Discussion                                           | 35 |

| Chapter 4 Implementing LogTM                             | 38 |

| 4.1 Implementing LogTM's Eager Version Management        | 38 |

| 4.1.1 Implementation Trade-Offs                          |    |

| 4.1.2 Compiler-Supported Software Logging                | 42 |

|         |      |                                                       | vii |

|---------|------|-------------------------------------------------------|-----|

|         | 5.5  | Summary                                               | 73  |

| Chapter | :6 l | Extending LogTM                                       | 75  |

|         | 6.1  | Nested Transactions                                   | 75  |

|         |      | 6.1.1 Closed Nested Transactions (with Partial Abort) | 76  |

|         |      | 6.1.2 Open Nested Transactions                        | 78  |

|         | 6.2  | 2 Virtualizing Conflict Detection                     | 79  |

|         |      | 6.2.1 Detecting Conflicts with Signatures             | 80  |

|         |      | 6.2.2 Supporting Unbounded Nesting with Signatures    | 81  |

|         |      | 6.2.3 Thread Switching and Migration                  | 82  |

|         | 6.3  | Software Contention Management                        | 84  |

|         | 6.4  | Summary                                               | 84  |

| Chaptei | :7]  | Related Work                                          | 86  |

|         | 7.1  | Hardware Transactional Memory                         | 86  |

|         |      | 7.1.1 Unbounded Transactional Memory                  | 86  |

|         |      | 7.1.2 Transactional Memory Coherence and Consistency  | 88  |

|         | 7.2  | Software Transactional Memory                         | 89  |

|         |      | 7.2.1 Lock-Based Transactional Memory                 | 90  |

|         | 7.3  | Hardware-Software Hybrid Transactional Memory         | 91  |

|         |      | 7.3.1 Transactional Lock Removal                      | 91  |

|         |      | 7.3.2 Hybrid Transactional Memory                     | 93  |

|         |      | 7.3.3 Virtual Transactional Memory                    | 94  |

|         |      | 7.3.4 Bulk                                            | 94  |

|         |      | 7.3.5 Page-Granularity Transaction Virtualization     | 95  |

|         | 7.4  | Speculative Multithreading                            | 95  |

|         |      | 7.4.1 Software Logging in Thread-Level Speculation    | 96  |

|                      | viii |  |

|----------------------|------|--|

| Chapter 8 Conclusion | 98   |  |

| References           | 100  |  |

# List of Figures

| 1-1 | Composability of Transactions v. Locks: (a) moving an element from one hash table to another |     |  |  |

|-----|----------------------------------------------------------------------------------------------|-----|--|--|

|     | using locks, (b) using transactions.                                                         | 3   |  |  |

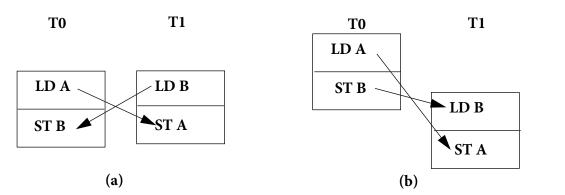

| 2-1 | Conflicting Transactions: (a) An Illegal, Non-Serial Execution, and (b) A Serial Execution.  | 17  |  |  |

| 3-1 | The Transaction Log.                                                                         | 26  |  |  |

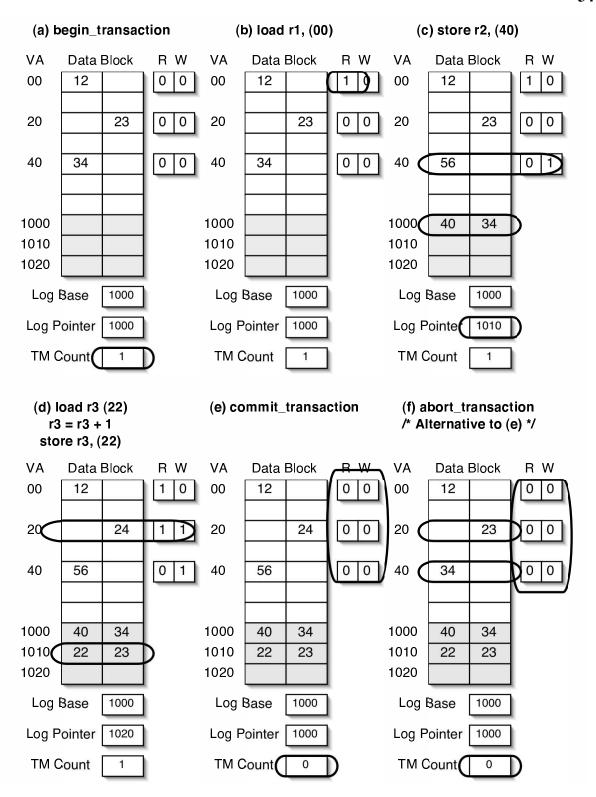

| 3-2 | Execution of a Transaction with Two Alternative Endings.                                     | 34  |  |  |

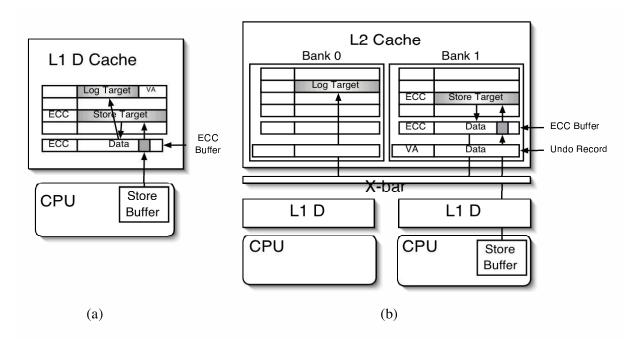

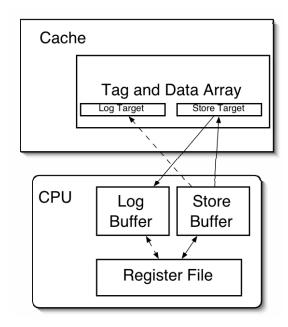

| 4-1 | In-Cache Hardware Logging. (a) Logging in the L1 Cache, (b) Logging in the L2 Cache          | 44  |  |  |

| 4-2 | Hardware/Software Hybrid Buffered Logging.                                                   | 46  |  |  |

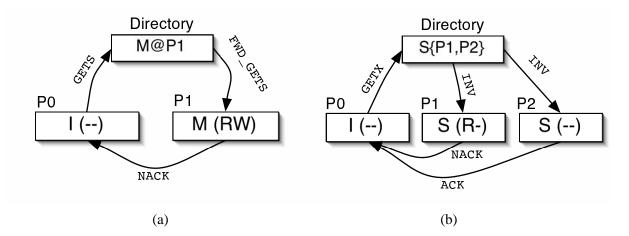

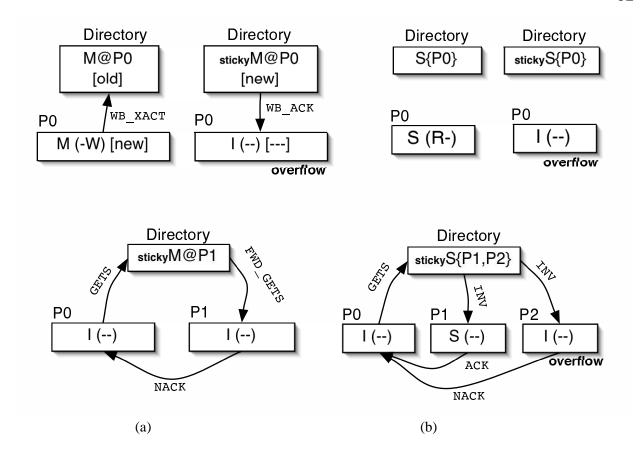

| 4-3 | In-Cache Conflict Detection in LogTM-Dir.                                                    | 50  |  |  |

| 4-4 | Conflict Detection on Un-Cached Data in LogTM-Dir Using Sticky States                        | 52  |  |  |

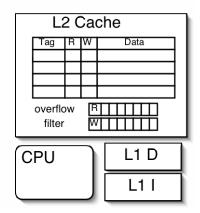

| 4-5 | LogTM-Bcast Node.                                                                            | 54  |  |  |

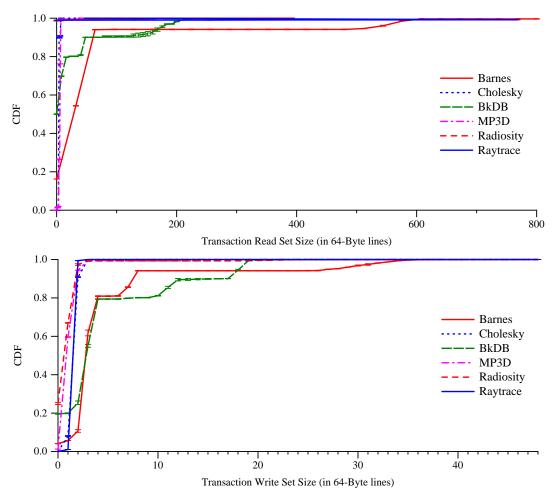

| 5-1 | Cumulative Distribution of Transaction Read Set and Write Set Sizes.                         | 63  |  |  |

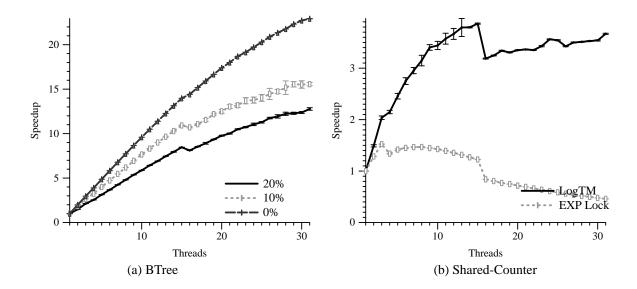

| 5-2 | Scalability of LogTM Microbenchmarks: (a) Scalability of BTree using LogTM Transactions w    | ith |  |  |

|     | 0, 10 and 20% Updates, (b) Scalability of Lock-Based and Transactional Shared-Counter        | 65  |  |  |

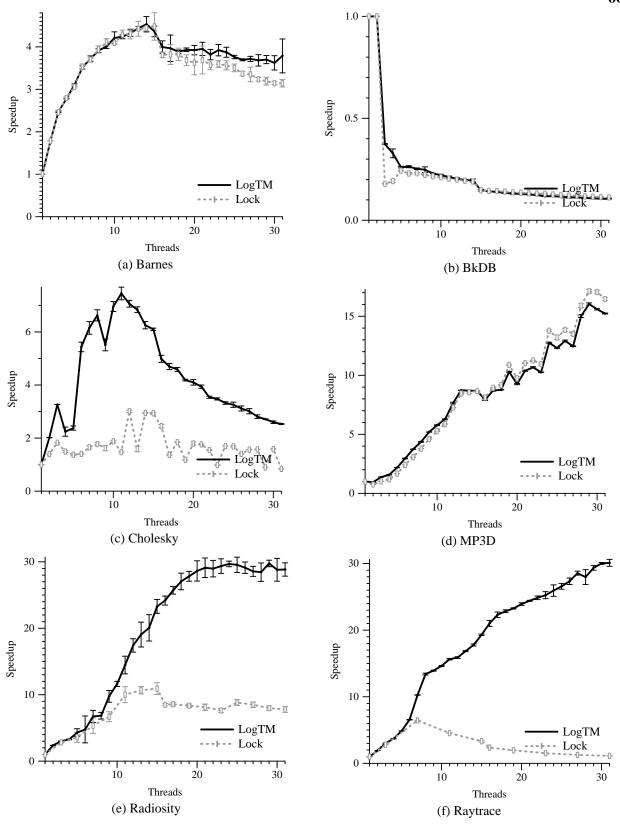

| 5-3 | Scalability of LogTM vs. Locks                                                               | 66  |  |  |

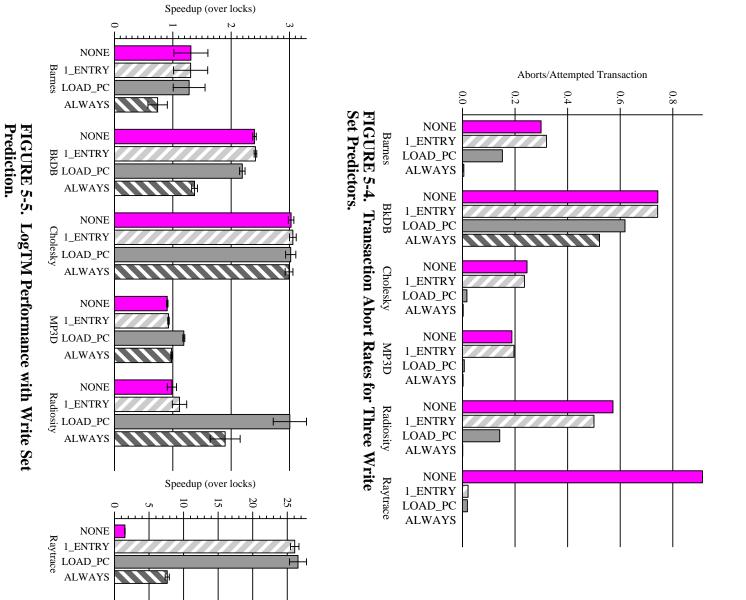

| 5-4 | Transaction Abort Rates for Three Write Set Predictors.                                      | 68  |  |  |

| 5-5 | LogTM Performance with Write Set Prediction.                                                 | 68  |  |  |

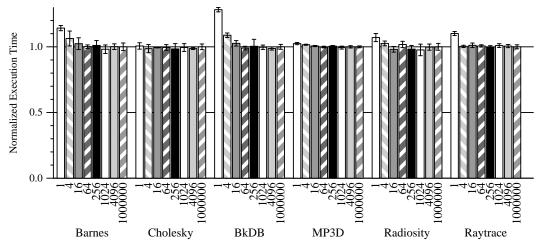

| 5-6 | Performance Impact of Buffer-Spill Stalls.                                                   | 69  |  |  |

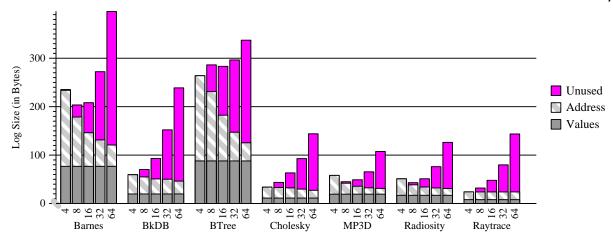

| 5-7 | Effect of Logging Granularity on Log Size.                                                   | 71  |  |  |

| 5-8 | Affect of Abort Overhead on LogTM Execution Time: (a) With LOAD_PC Write Set Prediction      | n,  |  |  |

|     | and (b) with No Write Set Prediction.                                                        | 73  |  |  |

# List of Tables

| 2-1 | A Transactional Memory Taxonomy                   | . 24 |

|-----|---------------------------------------------------|------|

| 3-1 | The LogTM Interface                               | . 32 |

| 4-1 | Write Set Predictors.                             | . 57 |

| 5-1 | System Model Parameters                           | 60   |

| 5-2 | Microbenchmarks                                   | 61   |

| 5-3 | Benchmark Inputs and Characteristics              | 62   |

| 5-4 | Log Size/Utilization at Varying Log Granularities | 70   |

| 6-1 | Nested Conflict Detection in LogTM-SE             | . 82 |

# Chapter 1

## Introduction

Parallel programming is difficult. Transactional Memory can make it less so. But, supporting transactional memory in hardware is too expensive and supporting it in software is too slow. As a result, transactional memory systems have evolved in two ways: (1) hardware systems, to which software is added to "virtualize" hardware's physical limits and (2) software systems to which some hardware is added to improve speed. Instead, LogTM takes a holistic approach—it implements unbounded transactional memory using software (with some hardware assistance) to store and recover multiple versions of data (which may require extensive state), and hardware to detect transaction conflicts (which must be performed quickly). By implementing performance-critical aspects of transactional memory in hardware and the rest in software, LogTM requires few hardware changes to implement, yet performs comparably to all-hardware implementations.

#### 1.1 Motivation

The remarkable performance gains that have fueled the computer industry for many years are today threatened by two trends that are pulling hardware and software in opposite directions. The first is an increasing emphasis on software reliability. As our society comes to rely ever more on computer systems, the cost of software failures is increasing. At the same time, the expanding role of computer systems has led to more complex software, making testing and debugging programs correspondingly more difficult. The second trend is the industry-wide shift towards thread-level parallelism. Recently, all high-performance processor makers have turned to chip multiprocessors (CMP), effectively making every computer sold today a multiprocessor. Many have also adopted multithreading, which allows each processor to execute multiple tasks concurrently. Unlike the gains in single-threaded performance, increased thread-level parallelism only speeds up parallel software. Unfortunately, the task of writing reliable software is only made more challenging with the introduction of parallelism. The chip industry's current solution, increasing performance by increasing thread-level parallelism, creates a dilemma for programmers: either ignore parallelism and face stagnant performance, or embrace parallelism and face a new class of bugs.

#### 1.2 Synchronization

In addition to the challenges of writing a correct sequential program, to write a correct parallel program, one must first divide the program's work into separate tasks, so that it may be performed in parallel by a number of *threads* of control. Next, one must ensure that each thread has access to the data on which it operates. Finally, the writer of a parallel program must coordinate these threads in some way to ensure that they access shared data structures in a consistent manner. To implement this coordination, parallel program developers use *synchronization* to impose ordering constraints on the actions of various threads. In practice, determining the synchronization needed in a program, and devising a scheme to enforce it, is often one of the most challenging aspects of parallel programs and a source of costly bugs.

#### 1.2.1 Serialization

One intuitive model for synchronization is serial execution. Accesses from each thread to a shared data structure are performed in *critical sections*. If critical sections execute serially with regard to other critical sections, programmers may perform operations that leave shared data structures in inconsistent states temporarily, without exposing those inconsistencies to other threads. Dijkstra described this problem as the *mutual exclusion* problem [19]; only one thread may execute a critical section at a time.

```

void move(T s, T d, Obj key){

LOCK(s);

LOCK(d);

tmp = s.remove(key);

d.insert(key, tmp);

UNLOCK(d);

UNLOCK(s);

}

(a)

void move(T s, T d, Obj key){

atomic {

tmp = s.remove(key);

d.insert(key, tmp);

}

tmp = s.remove(key);

d.insert(key, tmp);

}

}

```

FIGURE 1-1. Composability of Transactions v. Locks: (a) moving an element from one hash table to another using locks, (b) using transactions.

On today's hardware, ensuring mutual exclusion requires considerable effort from software. Programmers must establish and maintain a convention to record entry to and exit from critical sections and to prevent overlap between them. The current state of the art in parallel programming is to enforce mutual exclusion using *locks*, words in memory that, by software convention, represent the ability of threads to access certain data. Typically, a lock is associated with a set of data. To access a shared data structure, a thread must enter a critical section by acquiring the lock that protects that structure.

#### 1.2.2 The Trouble with Locks

When used properly, mutual exclusion via locks provides an efficient mechanism for preventing inconsistent accesses by concurrent threads. Using locks, however, is notoriously difficult, especially in large software systems built out of many separate components. Ideally, programmers should be able to compose large programs out of smaller pieces of code (e.g., reusable libraries) without knowing anything about their internal mechanisms. Locks, however, impede such composition. Consider the example in Figure 1-1, moving an item from one hash table to another. In the lock-based version (Figure 1-1-a), locks are needed to prevent other threads seeing a state where the moving object is not present in either table. While these locks may seem like a reasonable solution, even the simple example in Figure 1-1-a could result in a dead-lock. If two threads call move concurrently on the same two tables, but with the source and destination

reversed, both threads could acquire the lock on the source table, then block while trying to acquire the lock on the destination table.

Additionally, programmers using locks must balance the desire for concurrency with the overhead of acquiring and releasing many locks. Choosing fine-grain locks leads to greater concurrency, but incurs greater overhead and increases the chances of synchronization bugs. Conversely, choosing coarse-grain locks reduces lock overhead, but can reduce concurrency as more threads and processors are allocated to the program.

#### 1.2.3 Transactions

An alternative to the mutual exclusion model of synchronization is transactional programming. As developed in the database community [27], a *transaction* is defined as a transformation of state that is: atomic, consistent, isolated, and durable. Atomicity guarantees that either all of the transaction's actions will complete, or none will. Consistency means that a transaction that finds the system in any consistent state will leave the system in a (possibly different) consistent state and is the burden of the programmer. Isolation means a transaction will execute as if all other threads or processes are stopped while it is running. Finally, durability guarantees that a transaction, once completed, will not be undone, even in the event of a system failure. In transactional programming, all operations that access shared state are part of some transaction.

## 1.3 Transactional Memory

Transactional Memory [34, 44] extends the transactional programming model to shared-memory programs. In place of critical sections protected by locks, programmers specify atomic transactions. Like a database system, a transactional memory system guarantees that transactions will execute atomically and in isolation. Unlike database systems, however, transactional memory systems do not guarantee that trans-

actions are durable. Forgoing the durability guarantee allows transactional memory systems to implement transactions with much less overhead than database systems.

Compared to critical sections, transactions have several advantages. First, transactions free programmers from reasoning about the correctness and performance of their locking scheme. Second, in addition to isolation, which proper mutual exclusion ensures, transactions provide atomicity, assuring the programmer that, even in the event of a failure, shared data structures will not be left in an inconsistent state. The main advantage of transactional memory, however, is that—unlike lock-protected critical sections—transactions compose naturally. In contrast to the lock-based move method (Figure 1-1-a), the transactional move method (Figure 1-1-b), composes naturally with any internal transactions in the table class. The underlying transaction system will automatically serialize calls to move that operate on the same table without risking deadlock.

### 1.3.1 Limitations of Software Transactional Memory

Transactional memory can be implemented in hardware, software, or a combination of the two. Software Transactional Memory (STM) systems [30, 32, 69, 72], require no changes to existing hardware and are therefore the easiest to implement. Most STMs, however, suffer from two serious drawbacks, (1) poor performance and (2) weak atomicity. The fastest STM systems released to date are at best comparable to and often slower than the best lock-based algorithms for many applications [1]. More importantly, most STMs support only *weak atomicity* [8], meaning that transactions are isolated only from memory references that are part of other transactions. Weak atomicity can result in nonintuitive behavior and expose details of the STM implementation [44, 73]. As a result, supporting only weak atomicity will likely make writing and debugging more challenging, eroding the primary benefit of transactional memory. Thus far, the only high-performance STM to support strong atomicity incurs a 40% overhead over unsynchronized code [73].

Although many software developers may be willing to sacrifice performance for correctness (e.g., preventing deadlocks) the motivation for making a program run in parallel is to improve its performance.

#### 1.4 Hardware Transactional Memory

Hardware Transactional Memory (HTM) has the potential to provide both high performance and strong atomicity. HTM systems typically leverage cache coherence mechanisms to provide transactional isolation much more efficiently than STMs. HTM systems are not only more efficient than STMs, but are more efficient than lock-based synchronization for most applications. HTMs eliminate the overhead of acquiring and releasing fine-grained locks. Because HTMs typically leverage the cache coherence mechanism, they naturally check all memory references against any active transactions. Thus, they provide strong atomicity with little or no additional overhead.

#### 1.4.1 Implementing Hardware Transactional Memory

Implementing HTM primarily requires *version management* and *conflict detection*, both of which are often implemented by augmenting processor caches. *Version management* handles the simultaneous storage of both *new* data (to be visible if the transaction *commits*) and *old* data (retained if the transaction *aborts*). A common approach for version management is to use the cache to store new values, while old values remain in memory. *Conflict detection* signals an overlap between the *write set* (data written) of one transaction and the write or *read sets* (data written or read) of other concurrent transactions. Most HTMs leverage the cache coherence mechanism to perform conflict detection.

HTMs that use caches for version management and conflict detection have been shown to excel for transactions that execute for short durations and touch only small amounts of memory [29, 34, 65]. Long-running transactions that touch larger amounts of memory, however, present a challenge to such systems because both version management and conflict detection break down when data involved in a transaction leave the cache. Supporting transactions of arbitrary size and run time in hardware is difficult because hardware is constrained by the physical size of its structures. Implementing unbounded transactions with bounded physical structures requires *virtualizing* conflict detection and version management.

#### 1.4.2 Virtualizing HTM

Virtualization is the use of system software to provide the illusion of unbounded or idealized hardware to application programs. When physical resources are exhausted, software compensates, allowing applications to continue to function albeit more slowly. For example, virtual memory gives application programs the illusion of a large private memory space even when physical memory is limited and shared by many processes. It allows programmers to reason about common case memory behavior knowing that their programs may exceed the physical resources of the system so long as they do so rarely.

For transactional memory, virtualization requires abstracting the limitations of hardware structures used to perform version management and conflict detection and ensuring that transactions do not break existing virtualization mechanisms such as virtual memory and time slicing.

#### 1.5 Problem Statement

Transactional memory is an emerging programming technique that promises to ease multi-threaded programming provided that transactional memory systems can provide sufficient performance without sacrificing the convenience of the transactional model. Currently, it appears that hardware support will be necessary to implement transactional memory systems that support strong atomicity and still execute parallel programs as efficiently as lock-based synchronization. All-hardware implementations of transactional memory are not practical; they either restrict the execution model by limiting the size or duration of transactions, or introduce unnecessary expense by allocating hardware resources that are used infrequently. Therefore, an implementation of transactional memory should strive to:

- make the common case fast, namely short transactions that commit;

- defer rare and difficult-to-implement cases to software; and

- allow—through a combination of hardware and software—transactions of any size and duration.

#### 1.6 LogTM

To this end, I propose *Log-based Transactional Memory (LogTM)*, a transactional memory system that combines software-based version management (with limited hardware support) and conservative hardware conflict detection to support arbitrary-sized transactions with limited hardware. LogTM performs version management by creating a per-thread *transaction log* in cacheable virtual memory, which holds the virtual addresses and old values of all memory blocks modified during a transaction. In LogTM, a transaction commits by discarding the log (resetting a log pointer) and flash clearing some local coherence state. No other work is needed, because new values are already in place. A transaction aborts by walking the log in software to restore values.

**Contributions:** In developing LogTM, I make the following contributions:

- I develop and evaluate a transactional memory system that supports unbounded transactions with limited hardware resources.

- I develop a transactional memory system that optimizes for commit, by using eager version management to always store new values "in place," which means that no data move on commit (even if data has been replaced from a cache).

- I develop a means to extend a MESI directory protocol with *sticky states*, which enables (a) fast conflict detection on evicted blocks and (b) fast commit by lazily resetting the state of evicted blocks.

Because the log resides in virtual memory, LogTM can perform version management for transactions of any size. Hardware complexity is reduced because version management is decoupled from both proces-

sors' caches and the coherence protocol. Furthermore, the most complex component of version management, switching between old and new versions, is implemented in software. The common case, commit, is fast because memory is updated in place during transactions. Chapter 3 describes LogTM's API and general mechanisms for performing conflict detection and version management.

In Chapter 4, I discuss implementation tradeoffs in LogTM and present two implementations of LogTM's hardware conflict detection, LogTM-Dir and LogTM-Bcast. Both systems detect in-cache conflicts using an invalidation-based coherence protocol but do not require that transactional data be cached. LogTM-Dir extends directory protocols with *sticky states* to perform conflict detection even after transactional data has been replaced from caches. LogTM-Bcast performs the same task by adding Bloom filters [7] to broadcast coherence. For ease of implementation, LogTM always has the processor whose coherence request causes a conflict be the one that resolves the conflict by waiting (to reduce aborts) or aborting (if deadlock is possible).

In Chapter 5, I show that the scalability and performance of using LogTM transactions for synchronization on these systems are equal or better than those of lock-based synchronization. The remainder of Chapter 5 presents an evaluation of several of the implementation tradeoffs discussed in Chapter 4.

The evaluation in Chapter 5 demonstrates that LogTM is a viable approach for implementing transactional memory. However, the implementations described in Chapter 4 are limited in several important ways. In Chapter 6, I discuss several of those limitations and outline solutions. I discuss research related to LogTM in Chapter 7.

## Chapter 2

## Background

In this chapter, I provide background information and establish terminology used throughout this dissertation. First, I briefly describe the problem of cache coherence in shared-memory multiprocessors. Next, I discuss two alternative models for writing parallel programs on shared-memory multiprocessors, multi-threaded programming with mutual exclusion and transactional programming. Finally, I describe previously proposed transactional memory systems and their limitations, which LogTM seeks to overcome.

#### 2.1 Cache-Coherent Multiprocessors

This dissertation concerns the design and programming of cache-coherent shared-memory multiprocessors. Cache-coherent multiprocessing, which has been widely used in server systems for many years, is now ubiquitous as all high-performance microprocessors now include two or more processing cores per chip. Cache-coherent multiprocessors contain several independent processors that share a single memory system. To improve the effective access time of the shared memory, the individual processors maintain private caches. Special hardware keeps these caches *coherent*, ensuring that every load—whether it gathers its data from a cache or memory—returns the value established by the previous store to that memory location. Multiprocessors commonly enforce cache coherence using a broadcast snooping or directory-based coherence protocol.

In broadcast snooping [25] systems, all processors share a coherence bus (or other broadcast medium). When a processor attempts to access a block not present in its cache, it places a coherence request on the bus. The request may be satisfied either by the memory, or by another processor that has a valid copy of the

block in its cache. All cache requests are ordered by the sequence on which they appear on the bus, and all processors see all coherence requests.

Directory-based coherence protocols [10] reduce inter-processor bandwidth by not broadcasting coherence requests. All coherence requests are sent to the directory, which tracks the presence of the block in all caches. The exact combinations of states and messages depends on the protocol and is the subject of ongoing research. The directory relays the coherence request by sending messages to other processors and to memory, if necessary. To avoid congestion in any one node, the directory is one node (possibly a single processor or group of processors) acts as the home node for each memory block.

A common class of directory-based coherence protocols are invalidation-based MESI protocols [78]. In a MESI protocol, each block of memory resides in one of four logical states: Modified (M) the block is valid in exactly one cache and not memory; Exclusive (E) the block is valid in one cache and memory; Shared (S) the block is valid to read in one or more caches; and Invalid (I) the block is not valid in any cache. These states are also used to track the state of memory blocks in processors' caches. A processor may read a block if it is in states M, E or S, but may only write a block if it is in state M. The home node tracks the state of the block in all caches. For example, some directories record for each block either the address of one processor that holds the block in E or M or a sharers list—a list of processors that contain a shared copy of the block. When a processor executes a load to a block not valid in its cache, it requests a shared copy of the block by sending a get-shared (GETS) request to the directory. Upon receiving the request, the directory either fetches the data from memory and adds the requestor to the sharers list, or forwards the request (FWD-GETS) to the processor that has exclusive access to the block. When a processor executes a store to a block not present in the M state in its cache, it sends a get-exclusive (GETX) request to the directory. The directory then sends invalidation messages (INV) to all processors on the sharers list, instructing them to invalidate their copy or the requested block or forwards the request (FWD-GETX) to the processor that holds an exclusive copy of the block.

#### 2.2 Multi-Threaded Programming

One of the most common programming models for shared memory multiprocessors is multi-threaded programming, in which a program consists of multiple cooperating *threads* of control that share the same address space and some region of memory. In this model, a thread is an abstraction of the state of a processor. Logically, all threads execute simultaneously, sharing memory, but maintaining private processor and register state. Physically, however, the number of executing threads is limited by the number of processors available to the program. Because all threads share the same memory region and address space, there is no need for programmers to partition the program's data. In addition, threads can communicate through normal loads and stores. These conveniences and the widespread availability of shared-memory multiprocessors have contributed to the popularity of the multi-threaded programming model.

The challenge in this programming model is to coordinate accesses by multiple threads to shared objects. Consider one common data structure in multi-threaded programming, the task queue. Tasks can be placed on the queue at any time. The tasks are later executed by the next available (idle) thread. This strategy provides a simple mechanism for distributing work to a pool of a threads. Typically, each thread begins an iteration over its outer-most loop by grabbing an entry from a shared task queue. After reading the entry and removing it from the queue, the thread performs the task specified in the task queue entry. Because the task queue is shared, however, uncoordinated accesses to it by multiple threads could result in errors. For example, if the queue is implemented as a singly-linked list, threads might pull the next entry by: (1) reading the head pointer to a temporary variable, then (2) setting the head to the next entry (head->next). If two threads executed that same code simultaneously, however, both would read the head pointer and copy the address of the same task to their separate private variables. Next, both would set the shared head pointer to the next entry in the list. In the end, both threads would be set to perform the same task.

Dijkstra identified this as the mutual exclusion problem [19]. Threads sharing a memory pool alternatively execute *critical* and *non-critical* sections of program code. Only one thread at a time can be executing its

critical section and a failure of a thread executing its non-critical section cannot cause other threads to block indefinitely. If the threads in the example above access the task queue only in critical sections, mutual exclusion is sufficient to ensure that each thread safely removes tasks from the queue without interfering with other threads.

Lamport generalizes the mutual exclusion problem by observing that interactions between critical sections are defined not by their actual overlap in physical time, but by causal relationships between them [43]. In order for any critical or non-critical section to causally affect another, the two sections must operate on at least one common memory location, and one of them must update that memory location. Thus, critical sections that do not share a causal relationship may execute concurrently without violating mutual exclusion.

#### 2.3 Transactional Programming

An alternative to the multithreaded programming model described above is transactional programming. Transactional programming was first proposed in database systems as an intuitive model for application programmers to specify concurrency and durability requirements [27]. The transaction model combines the apparent serialization of critical sections with atomicity—the guarantee that a transaction will execute completely or not at all. Together, these properties guarantee that transactions will appear to execute in some serial order.

Transactions in software are analogous to the familiar concept of a business transaction. Two or more parties promise to take some action or set of actions contingent on the actions of the other parties. Either all parties fulfill their promises, or none do. Transactions in computer software work the same way; all the individual actions are completed or none are. More formally, a transaction in software is a transformation of state that is *atomic*, *consistent*, *isolated* and *durable*. Atomicity guarantees that each transaction will either complete all or none of its actions. Consistency requires that each transaction will find and leave the system in a consistent state (it is the burden of the programmer to ensure that each transaction if run inde-

pendently will leave the system in a consistent state). Isolation guarantees that each transaction will execute as if it is the only transaction running in the entire system. Effectively, this means that transactions will appear to be executed serially in some global order. Durability guarantees that, once executed, the effects of a transaction will not be undone even if the system fails.

The terminology used to describe transactional memory operations was developed in the database community. A transaction *begin* starts the execution of a transaction—the transaction becomes *active*. An active transaction can either *commit*—complete successfully—or, *abort*—terminate before completion, discarding any updates. The *read set* of a transaction is the set of objects (or memory locations) read by the transaction. Similarly, the *write set* of a transaction is the set of objects modified by the transaction.

This programming model has been widely successful in the database community and today, database mangement systems are among the most scalable commercial applications.

### 2.3.1 Transactional Memory

Transactional memory is a programming model that applies the transaction concept to memory accesses in shared-memory programs. The semantics of memory transactions are the same as that of database transactions with one exception—memory transactions are not guaranteed to be durable (memory state itself is not typically durable across system failures). The lack of a durability requirement allows memory transactions to incur much less overhead than their database equivalents. In practice, memory transactions are often used as a replacement for mutual exclusion locking in critical sections. Consequently, memory transactions are typically much shorter (in number of instructions and execution time), access less memory and contain fewer I/O operations than database transactions.

#### 2.4 Concurrency Control

Concurrency control is the method by which a particular parallel execution model is enforced. In essence, this amounts to the coordination of accesses by various concurrent threads or transactions sharing state. This section describes several concurrency control algorithms used to enforce mutual exclusion and transactional isolation.

#### 2.4.1 Concurrency Control for Mutual Exclusion

Mutual exclusion is typically enforced through the use of *locks*. A lock is simply a memory word used to coordinate access to a particular data structure or critical section. Programmers often use a lock to *protect* a shared data structure. By convention, a thread must *acquire* the lock (e.g., by setting the lock word to '1') before it accesses the data and hold the lock for the duration of its critical section. In this convention, a lock can only be held by a single thread. While the lock is held, any other threads that attempt to acquire the lock must block. threads may block by *spinning*—repeatedly testing the status of the lock—to ensure immediate notification when the lock is released, or by suspending—allowing the processor to execute other threads—to save resources and possibly prevent deadlock. After a thread finishes its critical section, it *releases* the lock (e.g., by setting the lock word back to free). If all threads follow this convention, mutual exclusion is ensured because a thread must hold the lock throughout the critical section and only thread may hold the lock at any given time.

Locks are typically acquired using atomic read-modify-write instructions. These instructions allow a thread to atomically test the lock word (to see if any thread holds the lock) and set it (to acquire the lock).

## 2.4.2 Lock-Based Concurrency Control in Database Systems

Database systems have traditionally implemented transactions using a combination of locking and logging [26]. Database locks may be shared—allowing multiple concurrent readers—or exclusive—allowing a sin-

gle writer. Database locks may be short or long. A *short lock* is a lock that is held for only one database operation. A *long lock* is a lock that is held from the time it is acquired until the end of the current transaction.

Database transactions will execute atomically if they are both *well-formed* and *two-phase*. A transaction is well-formed if it acquires at least a shared lock for each database object it reads and an exclusive lock for each object it modifies. This locking can be performed at any granularity so long as each active database object is covered by an appropriate lock. A transaction is two-phase if it acquires all of its locks before it releases any lock.

Most database systems enforce these requirements with *strict two-phase locking* and *write-ahead logging* [68]. In addition to being well-formed, strict two-phase locking requires that a process executing a transaction does not release any locks associated with that transaction until it completes (i.e. all locks are long locks). Write-ahead logging requires that the database record a log entry to stable storage for each database update before the effect of that update is recorded to stable storage. This policy ensures that the database has a record of, and the ability to undo, all updates from transactions that have not yet committed [26]. Although the transactional programming model requires that transactions appear to execute atomically, databases run many transactions in parallel in order to process transactions more quickly. Some transactions, however, *conflict* and cannot be safely overlapped. A transaction conflict occurs when two transactions access the same object and at least one of the accesses is an update (the same criteria Lamport required for a causal relationship). The transactions outlined in Figure 2-1 demonstrate a simple conflict. Both T0 and T1 access variables A and B, both of which are modified by one of the transactions.

FIGURE 2-1. Conflicting Transactions: (a) An Illegal, Non-Serial Execution, and (b) A Serial Execution.

Since the two-phase requirement prevents a running transaction from surrendering any lock on an object that it has accessed, one transaction may have to wait until another processor commits or aborts its transaction before it can continue. This waiting can lead to deadlock if two transactions are each waiting for an object held by the other. More generally, deadlock can occur any time there is a cycle in the graph of dependences between transactions. For example, in Figure 2-1 (a), both transactions T0 and T1 successfully acquire the first block in their transaction, loading A and B respectively. Once they read these variables, however, they are not allowed to release the locks held on them for the duration of the transaction. Neither transaction can proceed until the other aborts. Database systems can avoid deadlocks by aborting transactions when they attempt to block, or detect deadlocks by tracking the dependences between active transactions. Most systems allow deadlocks to form, then resolve them by aborting one of the blocked transactions [68].

## 2.4.3 Optimistic Concurrency Control in Database Systems

An alternative to strict two-phase locking in database systems is *optimistic concurrency control* [42]. Optimistic concurrency control is motivated by the observation that locking introduces an overhead that is only necessary in the worst case. Instead of using locks to prevent conflicting accesses, optimistic concurrency control mechanisms detect conflicts and abort the offending transaction. Optimistic concurrency schemes

divide transactions into three phases: read, validate and write. During the read phase, a transaction updates local copies of the modified objects. After a transaction completes its read phase, the system scans the read set to see if all the values read are still valid. A transaction T is valid unless its read set overlaps with the write set of a transaction that executed its write phase while T executed its read phase, or if T's write set overlaps the write set of another transaction that ran its write phase while T ran its write set. If T fails validation, it aborts without executing its write phase.

#### 2.5 Logging and Recovery in Database Systems

Database systems that use lock-based concurrency control typically update tuples in place during transactions for efficiency. The atomicity requirements of transactions, however, require that, if a transaction aborts, all of its updates must be undone. Many systems implement crash recovery and transaction rollback by maintaining an undo/redo log. Using the popular ARIES recovery algorithm [52], transactions add entries to a shared log for each update they make. Each log record contains the before-image (old values) and after-image (new values) of the updated record and the *LastLSN*, the log sequence number of the most recent previous log record pertaining to its transaction. Starting at the end of the log, the rollback copies the old values from the log record back to their original location (the modified tuple) and follows the LastLSN to find the next most recent log record for the transaction. Once the last LSN field is null, the undo is complete; and, all of the transactions have been undone in reverse order.

### 2.6 Transactional Memory Systems

Several transactional memory systems have been proposed with varying levels of hardware support. This section describes some particularly influential systems and characterizes several classes of transactional memory system.

#### 2.6.1 Hardware Support for Database Transactions

Some of the first proposals to add transactional semantics to the hardware interface sought to provide hardware support for the execution of database transactions. One such example is the 801 Storage system [13]. The 801 includes three architectural features designed to make database programs more efficient and easier to write: (1) large virtual storage, (2) database storage and (3) a 1-level store. Their innovative database storage includes support for database-style transactions on the one-level store with support for atomic commit, undo and recovery. Their programming interface makes storage to memory and the file system equivalent—any data structure supported in memory can be saved to disk. The transactions they envision are similar in scale to database transactions. They are long-running (thousands of instructions) and update stable storage [13].

#### 2.6.2 Early Hardware Transactional Memory Systems

To the best of my knowledge, Knight's "An Architecture for Mostly Functional Languages" [40] is the first to propose transactional operations on memory. Knight reasons that the transaction model is a convenient interface between the compiler and the hardware to automatically extract parallelism from sequential programs written in "mostly-functional" languages. Unlike in purely-functional languages, some actions are allowed to have side effects (stores), and therefore must be performed in a particular order. Knight proposes that the compiler group operations into transactional blocks, which may include many loads, but only one store.

In Knight's scheme, the hardware executes transactional blocks optimistically in parallel except for their one store. Transactional blocks are "confirmed" (committed) in program order. The hardware maintains a dependency list for all memory locations read by each transaction. As transactions are confirmed, the hardware checks the dependency list of each active transaction. Any transaction which depends on the store from the newly-confirmed transaction is aborted and re-executed. Knight outlines an implementation based

on two fully-associative caches. One cache, the dependency cache, tracks which main-memory locations have been read during the current transaction. The other, the confirm cache, holds transactional stores (although the transactional blocks in the paper are limited to only one store, the hardware would support transactions with as many stores as fit in the confirm cache). The data in the confirm cache is only written back to main memory when the transaction is confirmed [40].

Some processors provide the Load-Locked Store-Conditional (LL/SC) synchronization primitive [37, 15, 75], which allows atomic read-modify-write operations on a single memory location. LL-SC synchronization uses two separate instructions. The first, load-locked loads the value of a memory location into a processor register and begins to monitor the memory location for stores. The second, store-conditional, stores a value to the memory location only if that location has not been modified since the execution of the last load-locked instruction. LL/SC can be used to implement many common synchronization primitives such as test-and-set, fetch-and-increment/decrement, and compare and swap.

Stone et al. propose the Oklahoma Update Protocol [77], which extends the LL/SC primitive with the introduction of multiple reservations, or linked registers. The extra linked registers are combined with a different update mechanism, which allows multiple atomic stores. A "transaction" in this scheme proceeds as follows. First, the process performs one or more "Read-and-Reserve" operations, which define the read-set of the transaction. The process can speculatively update any of the locations previously read with a "Store-Contingent" operation. Finally, the process attempts to commit the transaction with a "Write-If-Reserved" action. The commit operation checks the valid bits of each reservation register, to see if any of the linked locations has been updated during the transaction. If all the reservations are still valid, the process enters the "commit phase." During the commit phase, coherence operations are deferred. The commit phase requires obtaining exclusive access to all memory locations updated by the transaction. Once the processor has obtained the proper permissions for each block updated in the transaction, all of the updates

are propagated back to the cache, any deferred requests are processed and the transaction exits successfully.

#### 2.6.3 Hardware Transactional Memory

Transactional Memory was first introduced by Herlihy and Moss introduced in their 1993 ISCA paper, "Transactional Memory: Architectural Support for Lock-Free Data Structures [34]." Their goal in designing a memory system based on atomic transactions was to support short critical sections—normally protected by locks—directly in hardware. Programmers, with the support of a compiler, designate transactional memory operations with special instructions.

Specifically, Herlihy & Moss propose the addition of four transactional instructions: *load transactional* (LT), *store transactional* (ST), *validate* and *commit* to the instruction set of a typical RISC architecture. LT and ST instructions signal to the processor that the data accessed by this load or store should be placed in the transactional cache. They also indicate that a transaction has begun if one is not already active. The validate instruction returns the status of the current transaction. The commit instruction returns a boolean value indicating whether or not the transaction succeeded (a violation of transactional semantics does not trigger a fault or trap). The programmer and compiler are free to choose the appropriate course of action in the case of a failed transaction.

They propose an implementation that uses a modified victim cache to store data accessed as part of a transaction. This transactional cache is the key mechanism in their scheme. All values accessed in a transaction are stored in a separate transactional cache. This transactional cache, they argue, should be small and fully-associative (very much like a victim cache [38]) so that the size of a transaction is not limited by worst-case cache conflicts, and so that transactional state can be cleared quickly (1 cycle in their proposal) in the case of a failed transaction. Since there is no requirement that the transactional cache hold only transactional data, unused entries in the transactional cache can be used as a victim cache for non-transactional

data. Unmodified data stored in the transactional cache can be in any of the normal cache states. Transactional stores cause the allocation of two entries in the transactional cache: the original (non-modified) data word, and the new (updated) value. The copy that represents the value modified by the transaction will survive if the transaction commits and is marked with the transactional cache state XABORT. The other, which stores the value in memory before the transaction, will persist if the transaction aborts is marked with the state XCOMMIT. If a processor aborts its current transaction, it signals the transactional cache to invalidate all entries in the XABORT state and change all entries with state XCOMMIT to normal (non-transactional) states. At the end of a transaction, the executing processor attempts to verify that no other processors have made intervening accesses to a memory location involved in the transaction. If it detects a conflicting memory action, the transaction is aborted and none of its updates are propagated to main memory. Otherwise, the transaction succeeds and all of its operations appear to take place atomically.

The cache coherence protocol proposed is based on Goodman's snooping protocol [25] (the authors also develop an adaptation based on a directory protocol in a separate technical report [33]). Non-transactional requests behave exactly the same as in the Goodman protocol. However, requests for data may be refused by a processor in the middle of a transaction (with a "busy" response) as long as the request is also made as part of a transaction. The protocol, however, does not allow a busy response for non-transactional requests from other processors. The requesting processor, upon seeing the refusal, aborts its own transaction and retries (possibly waiting to avoid repeated conflicts). A side effect of this policy is that non-transactional operations take precedence over transactional ones because non-transactional requests are always granted even if the responding processor is actively executing a transaction. This policy also violates strict two-phase locking since a non-transactional request can "steal" a block of memory away from a processor in mid-transaction. The authors preserve transactional semantics by guaranteeing that the transaction in the example above will never commit.

#### 2.6.4 Recently Proposed HTMs

The emergence of CMPs has reenergized research on transactional memory. Recently, several researchers have proposed HTMs, which differ primarily in their implementations of version management and conflict detection. Upon a store, some transactional memory systems use *eager version management* and put the new value in place. Others use *lazy version management* to (temporarily) leave the old value in place. Conflict detection is *eager* if conflicts are detected upon executing offending loads or stores and *lazy* if conflicts are detected later (e.g., when transactions commit). The taxonomy in Table 2-1 characterizes several recently proposed HTMs as to whether they use eager or lazy strategies for version management and conflict detection.

TCC. Hammond et al.'s *Transactional Memory Coherence and Consistency (TCC)* [29], like database systems that use optimistic concurrency control, uses lazy version management and lazy conflict detection. Store values are buffered at the processor's L1 cache and overwrite the L2 cache and memory only upon commit. TCC detects conflicts between transactions by broadcasting each transaction's write set on commit. Pending transactions abort if any memory location in the broadcast is a part of their write set.

LTM. Ananian et al.'s *Large Transactional Memory (LTM)* [5] uses lazy version management on cache overflows, storing new values in a hash table in uncached memory, while old values remain in place. When data fits in cache, LTM stores the new value in cache and the old value at memory. This coaxes the coherence protocol to store two different values at the same address. Repeated transactions that modify the same block, however, require a writeback of the block once per transaction. In contrast to TCC, LTM detects conflicts eagerly, checking for conflicts on each memory operation. LTM conflict detection is complex, however, due to support for the case where a processor replaces transactional data. Upon receiving a coherence request from the directory, such an LTM processor must walk an uncacheable in-memory hash table before responding (and possibly aborting).

|                      |       | Version Management                        |                                               |

|----------------------|-------|-------------------------------------------|-----------------------------------------------|

|                      |       | Lazy                                      | Eager                                         |

| lict<br>tion         | Lazy  | TCC [29]<br>(like OCC DBMSs [42])         |                                               |

| Conflic<br>Detection | Eager | LTM [5], VTM [66]<br>(on cache conflicts) | UTM [5], LogTM [new]<br>(like CCC DBMSs [21]) |

TABLE 2-1. A Transactional Memory Taxonomy

**VTM.** Rajwar et al.'s *Virtual Transactional Memory (VTM)* [66] also uses lazy version management on cache overflows with memory holding old values and an in-memory table (XADT) holding new (and a second copy of old) values. VTM does not specify version management when data fits in cache, but rather recommends other proposals [5, 29, 34, 65, 77]. VTM also uses eager conflict detection.

**UTM.** Ananian et al.'s *Unbounded Transactional Memory (UTM)* [5] proposes using both eager version management and eager conflict detection. This follows the example of the vast majority of DBMSs that use *conservative concurrency control (CCC)* [21]. UTM's implementation is complex, however, requiring substantial changes to the memory system.

# Chapter 3

## Log-Based Transactional Memory (LogTM)

LogTM is a strategy for implementing transactional memory a transactional memory system that combines software-based version management (with limited hardware support) and conservative hardware conflict detection to support arbitrary-sized transactions with limited hardware. LogTM adapts a well-known database algorithm for implementing transactions, strict two-phase locking and write-ahead logging. LogTM uses write-ahead logging to perform version management by saving old values before new values are written in place. LogTM detects conflicts eagerly, in a manner equivalent to strict two-phase locking. To balance implementation cost and performance, LogTM divides the work of providing atomicity and isolation in transactions between hardware and software. For speed, hardware detects conflicts and can aid logging; to save complexity, transaction updates are rolled back by software. The following sections describe the requirements for LogTM's version management, conflict detection and conflict resolution. The rest of the chapter describes the LogTM API and discusses the trade-offs involved in implementing the various components of transactional memory in hardware or software.

## 3.1 Eager Version Management

A defining feature of LogTM is its use of eager version management, wherein "new" values are stored in place while old values are saved in an alternate location. Specifically, in LogTM, the old values of registers are saved in a register checkpoint and old values of memory are stored in the *transaction log*, a thread-private section of the user program's virtual address space. If the transaction aborts, a software abort handler restores old values from the log and register checkpoint.

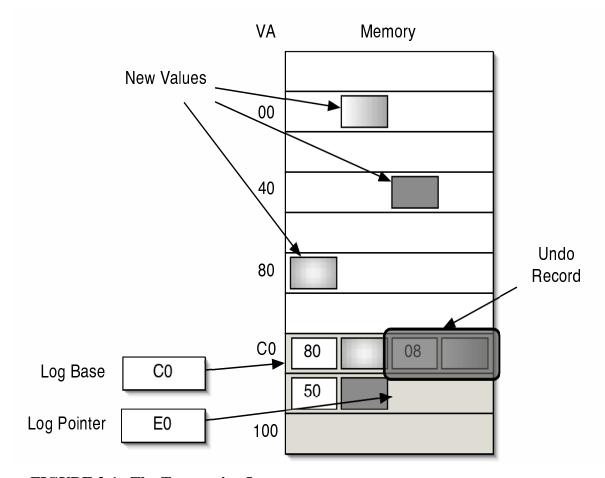

FIGURE 3-1. The Transaction Log.

## 3.1.1 The Transaction Log

The transaction log is a region of virtual memory, used by each thread to store the old values of all memory locations modified during a transaction. The base and bounds of the log are defined by two processor registers: Log Base and Log Pointer. A thread sets Log Base when it allocates space for the log—e.g., at thread creation, or when the LogTM system is initialized. The LogTM system updates Log Pointer each time it adds an entry to the log. Figure 3-1 illustrates the layout of the log in virtual memory. The main array is a representation of virtual memory, with virtual addresses shown on the left. The shaded area

(bottom of Figure 3-1) represents the transaction log for the current thread. The unshaded area represents shared memory locations, e.g., part of the heap.

A LogTM system maintains the log at a fixed granularity, logically dividing memory into fixed size blocks. Figure 3-1 shows a region of shared memory (unshaded) and the log of an active transaction that has executed three stores (shaded). The three pairs of shaded blocks in Figure 3-1 represent the old and new values of three memory blocks, each 8 bytes long. The new value of each block is stored in place, and the old value is stored in an undo record in the log. Each undo record includes the virtual address of the modified block and its old value. Because the purpose of the log is to restore pre-transaction values, a LogTM system need only log the first update to any given memory location.

In database terminology, the transaction log is an undo-only log—i.e., it does not contain sufficient information to re-execute a transaction nor to recover the state of memory in the event of a crash [52]. This is in contrast to the logging used in most database systems. In a typical database, the log is used for recovery as well as transaction rollback. Importantly, because the transaction log is not used for recovery, there is no need to store the log on disk or other stable storage. Furthermore, since the log is not needed after the commit of a transaction, unlike the log in most database systems, the transaction log in LogTM is thread private and may be discarded after a transaction completes.

The log is defined in virtual memory for which physical memory is allocated on demand. If adding a log entry exhausts the physical memory in the log, the current thread takes a page fault and uses the existing virtual memory support to allocate an additional page for the log. Because the transaction log is stored in virtual memory, it may grow arbitrarily large. Log pages may be swapped to disk without impacting LogTM's version management.

#### 3.1.2 Transaction Commit

On commit, the executing thread simply clears its transaction log by setting Log Pointer equal to the Log Base and discards its register checkpoint. No copying is needed because new values are already in place.

## 3.1.3 Transaction Abort

To maintain atomicity in the event of a transaction abort, LogTM must undo any updates from the aborting transaction by restoring the old values maintained in the transaction log and register checkpoint to their original locations in memory and processor registers. In order to save hardware complexity, LogTM performs this restoration in software. In LogTM, a transactional memory program registers an abort handler which will be called when a transaction aborts. The abort handler is expected to undo the effects of the aborted transaction using the transaction log. For example, a handler can rollback a transaction by reading the undo records in the log in last-in-first-out order, copying the old values in each record to the corresponding address. Once the handler has processed the log, it can restore the processor registers to their pre-transaction states.

## 3.2 Eager Conflict Detection

LogTM requires eager conflict detection, which means that a LogTM system must detect and resolve any conflict triggered by a memory request before that request completes. In LogTM, this detection is the responsibility of hardware. Implementations of LogTM are expected to leverage the coherence mechanism to implement conflict detection efficiently. LogTM implementations must report all true conflicts between concurrent transactions, but to reduce hardware complexity and cost, they are allowed to report false conflicts to simplify implementation.

#### 3.2.1 Requirements

LogTM's eager conflict detection is based on strict two-phase locking. In place of the shared and exclusive locks used in database systems, however, LogTM requires read and write *isolation*. Unlike locking, isolation does not prescribe any particular conflict resolution mechanism (e.g., blocking). If a block is read isolated, it cannot be written by any thread without generating a conflict. If a block is write isolated, it cannot be read or written by any thread without generating a conflict.

**Requirement 1: Transactions Must be Well Formed.** In order for a thread to read a memory location in a transaction, that thread must first obtain read isolation on that location. In order to write a location, a thread must first obtain write isolation on that location. If an attempt to acquire read or write isolation results in a transaction conflict, the system must signal a conflict before the offending memory instruction is retired.

**Requirement 2: Isolation Must be Strict Two-Phase.** Any memory location that becomes read or write isolated by being read or written in a transaction must remain isolated until the commit or abort of that transaction.

**Requirement 3: Isolation Must be Released at Transaction End.** Conflicts may prevent one or more transactions from making forward progress. In order to ensure forward progress in the system, a thread must release its isolation when it aborts or commits its transaction.

## 3.2.2 Example Implementation

For small transactions—the expected common case—the entire read and write set of the transaction remains in the private cache of the executing processor. In this case, a standard invalidation-based cache coherence protocol is well suited to detecting transaction conflicts. As discussed in Chapter 2, cache-coherent multiprocessors that use invalidation-based coherence protocols typically enforce the invariant

that every block of memory resides in one of three logical states: (I) the block is invalid in all caches, (S) one or more caches hold a valid read-only copy of the block and (M) one cache only has a writable copy of the block. Such systems already require that a processor obtain shared (read only) access to a memory location before it may be read and exclusive access (read/write permission) before it may be written. As a result, if isolation is provided by the coherence mechanism, these protocols enforce the well formed requirement by default. Additionally, these rules ensure that any memory access that hits in the local (private) cache will not trigger a transaction conflict.

Conflict detection in such a system works might work as follows: each processor tracks the read and write sets of its active transaction with two additional bits per line in its private cache. The read (R) bit indicates that the block has been read during the current transaction. The write (W) bit indicates that the block has been written during the current transaction and potentially contains data values from an uncommitted transaction. When a processor P executes a load or store, it first checks its local cache. If the corresponding block is not present, P issues a request for the block to the memory system. That request is sent to one or more other processors (e.g., via a broadcast or forwarded by a directory). Those processors check their local state (in the cache or memory controller) to detect conflicts with any transactions running there. The presence of a conflict is returned along with the coherence response. That response signals the conflict (if any) to P, which resolves the conflict. The states of any copies of the contended block in the responding processors' caches remain the same, as do the R and W bits there, until the transactions running on those processors end. This fulfills the strict two-phase requirement. Finally, at the end of a transaction, the processor flash-clears the R and W bits in its cache, fulfilling the requirement to release all read and write isolation after the transaction commits or aborts.

#### 3.3 Conflict Resolution

Detecting a transaction conflict informs a transactional memory system that its current execution schedule will violate the isolation of one or more concurrent transactions. To preserve isolation, the system must *resolve* transaction conflicts by serializing the conflicting transactions. A transactional memory system can serialize the execution of a set of transactions by aborting or stalling one or more of the transactions. Resolving conflicts by aborting transactions risks livelock if all transactions are aborted before completion. Resolving conflicts by stalling, however, risks deadlock if transactions are forced to wait indefinitely. In LogTM, transaction conflicts are resolved by the thread that makes the memory request that first causes the conflict. The requesting thread can resolve the conflict by aborting its transaction. Or, because the conflict is detected before the conflicting memory access is completed, the requesting thread can resolve the conflict by either stalling—waiting for the conflicting transaction to commit or abort. Because aborts are costly in LogTM, resolving conflicts via stalling can improve performance. Implementations that resolve conflicts by stalling, however, must take care to avoid deadlocks.

## 3.4 LogTM API

Table 3-1 presents LogTM's interface in three levels. The *user interface* (top) allows user threads to *begin*, *commit* and *abort* transactions. Compilers could translate higher level constructs such as an atomic block to LogTM's begin\_transaction and commit\_transaction calls like the Java compiler generates monitor enter and exit calls from statically scoped synchronized blocks [47]. The system/library interface (middle) lets thread packages initialize per-thread logs and register an abort handler. Upon an abort, LogTM lets the abort handler "undo" the log via a sequence of calls using the low-level interface (bottom). In the common case, the handler can restart the transaction with user-visible register and memory state

#### User Interface

begin\_transaction() Increments TM Count. If TM Count > 0, subsequent dynamic statements form a transaction. Logically saves a copy of user-visible non-memory thread state (i.e., architectural registers, condition codes, etc.).

**commit\_transaction()** Decrements TM Count. When TM Count == 1, commit ends a successful transaction. Discards any transaction state saved for potential abort.

abort\_transaction() Transfers control to a previously-registered abort handler which should undo and discard the current transaction and set TM Count to 0. A system may choose to restart the transaction or execute other code.

#### System/Library Interface

initialize\_logtm\_transactions(Thread\* thread\_struct, Address log\_base, Address log\_bound) Initiates a thread's transactional support, including allocating virtual address space for a thread's log. As for each thread's stack, page table entries and physical memory may be allocated on demand and the thread fails if it exceeds the large, but finite log size. (Other options are possible if they prove necessary.) We expect this call to wrapped with a user-level thread initiation call (e.g., for P-Threads).

register\_abort\_handler(void (\*) abort\_handler) Registers a function to be called if a transaction is aborted. Abort handlers are registered on a per-thread basis. The registered handler should assume the following pre-conditions and ensure the following post-conditions:

Abort Handler Pre-conditions: Abort has occurred. System may have restored some or all memory blocks written by the thread to their pre-transaction state. Other memory blocks written by the thread (a) have new values in (virtual) memory but these blocks are isolated and (b) have their (virtual) address and pre-write values in the log. If a block is logged more than once, its first entry pushed on the log must contain its pre-transaction value. Log also contains a record of pre-transaction user-visible non-memory thread state.

Abort Handler Post-conditions: Abort handler called undo\_log\_entry() to pop off every log entry. Abort handler then called complete\_abort\_with\_restart() or complete\_abort\_without\_restart().

#### Low-Level Interface

undo\_log\_entry() Reads a block's (virtual) address and pre-write data from the last log entry, writes the data to the address, and pops the entry off of the log. The system may end isolation on the block if is sure that pre-transaction value is now restored (i.e., there are not earlier duplicate log entries for this address).

complete\_abort\_with\_restart() End isolation on all memory blocks, restore thread's

non-memory state from last begin\_transaction(), and resume execution there.