# Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls

# Citation

Currivan-Incorvia, J. A., S. Siddiqui, S. Dutta, E. R. Evarts, J. Zhang, D. Bono, C. A. Ross, and M. A. Baldo. 2016. "Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls." Nature Communications 7 (1): 10275. doi:10.1038/ncomms10275. http://dx.doi.org/10.1038/ncomms10275.

# **Published Version**

doi:10.1038/ncomms10275

## Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:26318753

# Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

# ARTICLE

Received 30 Jun 2015 | Accepted 23 Nov 2015 | Published 12 Jan 2016

DOI: 10.1038/ncomms10275

OPEN

# Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls

J.A. Currivan-Incorvia<sup>1,2</sup>, S. Siddiqui<sup>1</sup>, S. Dutta<sup>1</sup>, E.R. Evarts<sup>3</sup>, J. Zhang<sup>4</sup>, D. Bono<sup>4</sup>, C.A. Ross<sup>4</sup> & M.A. Baldo<sup>1</sup>

Spintronic computing promises superior energy efficiency and nonvolatility compared to conventional field-effect transistor logic. But, it has proven difficult to realize spintronic circuits with a versatile, scalable device design that is adaptable to emerging material physics. Here we present prototypes of a logic device that encode information in the position of a magnetic domain wall in a ferromagnetic wire. We show that a single three-terminal device can perform inverter and buffer operations. We demonstrate one device can drive two subsequent gates and logic propagation in a circuit of three inverters. This prototype demonstration shows that magnetic domain wall logic devices have the necessary characteristics for future computing, including nonlinearity, gain, cascadability, and room temperature operation.

<sup>&</sup>lt;sup>1</sup> Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA. <sup>2</sup> Department of Physics, Harvard University, Cambridge, Massachusetts 02138, USA. <sup>3</sup> Physical Measurement Laboratory, National Institute of Standards and Technology, Boulder, Colorado 80305, USA. <sup>4</sup> Department of Materials Science and Engineering, Massachusetts Institute of Technology, Cambridge, Massachusetts 02139, USA. Correspondence and requests for materials should be addressed to J.A.C.-I. (email: incorvia@stanford.edu) or to M.A.B. (email: baldo@mit.edu)

### ARTICLE

here is great interest in encoding information in magnetic materials for future memory and logic<sup>1-6</sup>. Recent developments in perpendicular anisotropy materials<sup>7,8</sup> and spin Hall effect-assisted domain wall (DW) switching<sup>9–11</sup> have reduced the current density required to switch a magnet. Many groups are working on instantiations of magnetic logic and memory, for example, ratchet memory<sup>12</sup>, three-terminal magnetic random access memory<sup>13</sup>, majority logic gates<sup>14,15</sup>, nanomagnetic logic<sup>16</sup> and mLogic<sup>17</sup>. These devices show promise for future computing, and work has been done to simulate and build them. However, so far, little work has shown experimentally verified DW-based devices that can perform logic, be used in circuits, and have a gate-like basic element that can be used to build more complex circuits.

In this work, we present magnetic device prototypes that are capable of integration in logic circuits and easily adaptable to the continuing advances in spintronics materials and scaling. The device is a memory cell that we adapt to logic. Information is stored in the position of a DW in a short, narrow ferromagnetic wire, written using spin-torque transfer<sup>18</sup> from pulsed voltage clocks, and read out using a magnetic tunnel junction (MTJ)<sup>19</sup>. The device is nonvolatile and is predicted to scale to switching energies competitive with field-effect transistors<sup>1</sup>. We demonstrate that a single device can perform buffer and inverter operations, one device can drive two subsequent devices and three devices in series act as a circuit of three inverters. These results provide a path for realizing spintronic circuits.

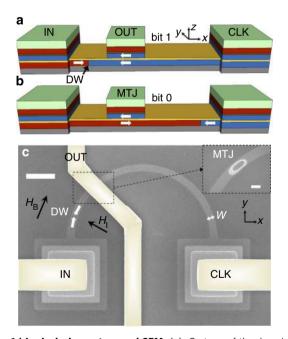

**Figure 1 | Logic device cartoon and SEM.** (**a**), Cartoon of the domain wall (DW) logic device, comprised of a magnetic wire with a DW and a magnetic tunnel junction (MTJ) to read out the DW position. Right-pointing magnetic moments are red and left-pointing are blue (grey represents Ta, brown Ru, and light green IrMn). Magnetization direction is also shown by the white arrows. The MgO tunnel barrier is shown in yellow. The device has three terminals, IN, CLK, and OUT. When the wire magnetization is parallel to the MTJ magnetization, the current at the OUT terminal is high, representing bit 1. (**b**), Cartoon showing the DW switched to the opposite side of the device, representing bit 0. (**c**), SEM image of a DW-Logic device prototype, showing the magnetic wire of width w = 400 nm and the MTJ under the center electrode with area  $1 \mu m \times 400$  nm, also shown in the inset. Electrodes are coloured in light gold. The initial DW position is shown by the white arrows. The black arrows show the orientation of the initialization field **H**<sub>I</sub> and bias field **H**<sub>B</sub>. Scale bars,  $2 \mu m$  (**c**), 400 nm (**c**, inset).

#### Results

**Domain wall logic device structure**. The prototype is shown schematically in Fig. 1a,b. It consists of two parts: a ferromagnetic wire containing a DW and a MTJ. The wire is composed of sputter-deposited thin films on a Si substrate: SiO<sub>2</sub> (200 nm)/Ta  $(3 \text{ nm})/\text{Co}_{40}\text{Fe}_{40}\text{B}_{20}$  (t=4 nm)/MgO (1 nm). The CoFeB has in-plane magnetic anisotropy; while perpendicular anisotropy will be more energy-efficient in scaled devices<sup>1,20</sup>, as explored in ref. 1, for initial prototypes the logic behaviour is independent of anisotropy type. The MTJ stack is CoFeB (2.5 nm)/Ru (0.8 nm)/CoFeB (2.5 nm)/Ir<sub>20</sub>Mn<sub>80</sub> (10 nm)/Ta (3 nm)/Ru (7 nm). There are three terminals: IN, CLK and OUT.

Figure 1c shows a scanning electron microscope (SEM) image of a fabricated device. The wire width is w = 400 nm and is shaped into a curve to allow initialization of the DW using a globally applied field **H**<sub>I</sub>. Micromagnetic simulations predict that the DW is transverse, see Supplementary Fig. 1. The MTJ sits under the center electrode. The IN and CLK terminal pads are  $5\,\mu\text{m} \times 5\,\mu\text{m}$  MTJs used to contact the magnetic wire, much larger than the center MTJ. At this size there is negligible magnetoresistance in the pads due to pinholes in the MgO layer, so their tunnel junctions are ignored. The estimated series resistance of the pads is about  $100\,\Omega$ , small compared with the wire resistance.

Device operation includes an initialization step, a write step and a read step. First,  $\mu_0 H_I = 200 \text{ mT}$  is applied to initialize the DW on the left, where  $\mu_0$  is the permeability of free space. This field is large enough to saturate the magnetic moments in  $\hat{\mathbf{H}}_{I}$ , such that when the field is removed a DW is nucleated along the field direction. By having a curved wire, we can set the initial DW position by choosing the field angle. The magnetization is parallel on either side of the MTJ, and its resistance is low (bit 1, Fig. 1a). See Supplementary Figs 2 and 3 for field-driven device characteristics. For current-driven behaviour, a 1-µs voltage pulse is applied to the IN terminal with CLK grounded. It is theoretically possible to use a three-phase sinusoidal clock to save energy<sup>1,21</sup>. If the input current,  $I_{IN}$ , is above the threshold current of the DW,  $I_{\rm T}$ , then the current can translate the DW past the MTJ using current-induced DW motion<sup>22</sup>, switching the MTJ to a high-resistance state (bit 0, Fig. 1b). Most likely, the currentinduced switching is a combination of spin transfer torque and heat-assisted depinning<sup>23</sup>.  $I_T$  depends on both intrinsic and extrinsic pinning of the DW from sources such as line edge roughness<sup>24</sup> and magnetocrystalline defects.

The device can then be read by a voltage pulse applied to CLK sunk to the input of the next device. The current at the output terminal,  $I_{OUT}$ , will be high or low depending on the position of the DW, and can be fed into the next device stage. To avoid damage to the devices at high current density, DW motion is assisted by a global bias field  $H_B$ , aligned parallel to the initial DW position. The bias field could be eliminated by using a magnetic material with lower  $I_T$ , or by scaling the devices to smaller length scales. Simulations and experiments suggest that the current density required to depin a DW decreases with wire width to sub-50 nm sizes<sup>1,22</sup>.

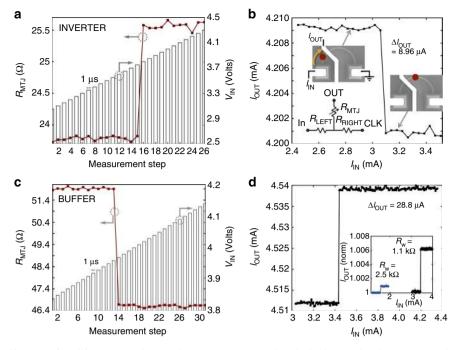

Single device behaviour as inverter and buffer gates. A single device can be used as a logic gate when the current at the input terminal,  $I_{\rm IN}$ , is the sum of multiple input currents. Figure 2a shows an example of a device acting as an inverter, which can be used to do a two-input NAND operation, with parallel MTJ resistance  $R_{\rm P} = 23.7 \,\Omega$ , antiparallel MTJ resistance  $R_{\rm AP} = 25.7 \,\Omega$ , wire resistance  $R_{\rm w} = 1.18 \,\mathrm{k}\Omega$  and tunnel magnetoresistance  $TMR = (R_{\rm AP} - R_{\rm P})/R_{\rm P} \times 100 = 8.4\%$  (ref. 25). Initialization with H<sub>I</sub> sets the MTJ initially in a parallel state (bit 1), with the DW on

**Figure 2** | Inverter and buffer operation. (a), Transient showing the MTJ resistance and applied voltage pulses between IN and CLK versus time. At 3.80 V, the device switches from low resistance (bit 1) to high resistance (bit 0). (b), Transfer characteristic of  $I_{OUT}$  through the MTJ versus  $I_{IN}$  across the wire. The SEM images show the configuration below  $I_{T}$ , with the DW position approximated by the red dot and  $I_{IN}$  electron flow direction shown by the yellow arrow, and the approximate DW position after  $I_{T}$  inset, Simple circuit diagram to represent the device, including the wire resistance and the variable tunnel junction resistance. (c), Transient behaviour showing a buffer operation, plotting  $R_{MTJ}$  and  $V_{IN}$  versus measurement step as we increase the 1-µs voltage pulse amplitude in 0.01 V steps. This device has similar  $R_w$  to the previous device, but slightly higher  $R_{MTJ}$  and TMR. At 3.97 V, the device switches from a high-resistance output to a low-resistance output. (d), Transfer characteristic for the buffer. inset, Comparison of this transfer characteristic (right black curve) to that of another device (left blue curve) with less well matched  $R_w$  and  $R_{MTJ}$ .

the left as in Fig. 1a,c. A bias field  $\mu_0 H_{\rm B} = 3.0 \,\mathrm{mT}$  is then applied parallel to the DW. We apply a series of 1-µs voltage pulses,  $V_{\rm IN}$ , increasing in 0.05 V steps, to the IN terminal. Each input pulse is followed by a 100 mV d.c. voltage applied to the CLK terminal to measure the resistance through the MTJ,  $R_{\rm MTJ}$ . Between  $V_{\rm IN} = 3.75 \,\mathrm{V}$  to 3.80 V, corresponding to an input current of  $I_{\rm T} = 3.099 \,\mathrm{mA} \pm 0.041 \,\mathrm{mA}$  (with range determined by the voltage step) and current density  $J_{\rm T} = 1.9 \times 10^{12} \,\mathrm{Am^{-2}}$ , the DW is translated across the MTJ, switching the output from  $R_{\rm P}$  (high current, bit 1) to  $R_{\rm AP}$  (low current, bit 0).

The current is calculated using the circuit in Fig. 2b (inset), with the wire resistance represented by  $R_w = R_{\text{LEFT}} + R_{\text{RIGHT}}$  and the MTJ represented by a variable resistor  $R_{\text{MTJ}}$ . For an isolated device, we define the input current as

$$I_{\rm IN} = \frac{V_{\rm IN}}{R_{\rm S} + R_{\rm LEFT} + R_{\rm RIGHT}} \tag{1}$$

where  $R_{\rm S}$  is the load resistor from the voltage supply. If we read each device using  $V_{\rm OUT}$ , then we define the output current for an isolated device as

$$I_{\rm OUT} = \frac{V_{\rm OUT}}{R_{\rm S} + R_{\rm RIGHT} + R_{\rm MTJ}}.$$

(2)

Device stages are pulsed in sequence, where in each stage a device can also have an input resistor that is tuned to put the input current in the correct range to read the data from the previous stage. Thus, if the input current originates from two logic gates, with output resistances such that the input currents sum in the subsequent gate, then that device switches from 1 to 0 only when the input current exceeds  $I_{\rm T}$ . The resulting transfer characteristic is in Fig. 2b. The change in the MTJ resistance

modulates the output current by  $\Delta I_{OUT} = 8.96 \,\mu$ A, assuming a CLK voltage pulse of 3.80 V and no external load attached to the OUT terminal.

Figure 2c shows a device instead acting as a buffer gate. The buffer is shown for a different device:  $R_{\rm P} = 46.5 \,\Omega$ ,  $R_{\rm AP} = 52.1 \,\Omega$ ,  $R_{\rm w} = 1.10 \,\mathrm{k}\Omega$ , and TMR = 12%. The device is initialized the same as previously. We program it to act as a buffer rather than an inverter by applying a higher bias field  $\mu_0 H_{\rm B} = 4.8$  mT, above the field switch of the reference layer of the MTJ but below that of the DW, initializing the MTJ in the antiparallel state (bit 0). The DW switches across the MTJ between 3.96 and 3.97 V, or  $I_T = 3.441$ mA  $\pm$  0.009 mA,  $J_{\rm T} = 2.0 \times 10^{12}$  A m<sup>-2</sup>. The output switches from high resistance (low current, bit 0) to low resistance (high current, bit 1). Across multiple devices, the transfer characteristic shows a very sharp switch between resistance states,  $\Delta V_{\rm IN} < 0.01$ V, the limit of our voltage supply. This enables stable 0 and 1 outputs even with TMR = 8-20% seen in our devices. At the switch,  $\Delta I_{OUT}/\Delta I_{IN} = 3.1$ . In Fig. 2d we plot  $I_{OUT}$  versus  $I_{IN}$  for the isolated buffer device with  $V_{OUT} = 3.97$  V. The change in current between the 0 and 1 output bits is  $\Delta I_{OUT} = 28.8 \,\mu A$ assuming no output load.

While  $\Delta I_{OUT} = 28.8 \,\mu$ A is an appreciable difference in current for stable 0 and 1 bits, the fractional output current change is  $\Delta I/I = (I_P - I_{AP})/I_{AP} = 0.3\%$  of the bit 0 output current  $I_{AP,OUT} = 4.5 \,\text{mA}$ . In an ideal device,  $\Delta I/I$  should be maximized for the best noise margin and potential fanout. Using Equation 2 with fixed  $V_{OUT}$ , and assuming that the gate drives a single subsequent ferromagnetic wire, we find

$$I_{\rm P} = I_{\rm AP} \frac{R_{\rm S} + 2R_{\rm RIGHT} + R_{\rm LEFT} + R_{\rm AP}}{R_{\rm S} + 2R_{\rm RIGHT} + R_{\rm LEFT} + R_{\rm P}}.$$

(3)

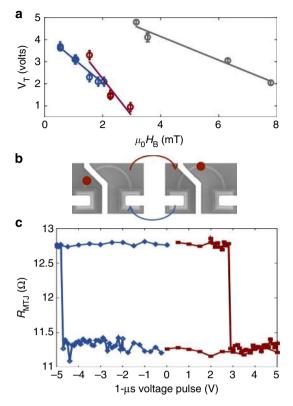

**Figure 3 | Variability and reversibility. (a)** Threshold voltage versus bias field for three different devices, where the error bars represent the depinning voltage standard deviation repeated at least  $3 \times$ , with the DW reinitialized between each. Grey = device 1, red = device 2 and blue = device 3. The lines are a linear fit. Devices 2 and 3 were fabricated together, while device 1 was fabricated at a later time on a different wafer piece. (b) SEM images showing reversibility setup, with the DW moving back and forth past the MTJ as shown by the red dots. (c)  $R_{MTJ}$  versus pulsed *V* showing reversibility of device 1's state. In the positive direction  $\mu_0 H_B = 3.3 \text{ mT}$ ; in the negative direction  $\mu_0 H_B = -6.2 \text{ mT}$ . The red dot in the SEM images is the approximate DW position at high and low  $R_{MTJ}$ , respectively.

If we define the output resistance in the parallel state  $R_{OUT} = R_P + R_{RIGHT}$  and the load resistance  $R_{LOAD} = R_{LEFT} + R_{RIGHT} + R_{S}$ , then we can define a figure of merit

$$\frac{\Delta I}{I} = \frac{TMR}{(R_{\rm OUT} + R_{\rm LOAD})/R_{\rm P}}.$$

(4)

Equation 4 shows that the highest noise margin and fanout is obtained by maximizing the *TMR* and matching the MTJ parallel resistance and the resistance of the wire.

Figure 2d (inset) compares  $I_{OUT}$  versus  $I_{IN}$  of the original buffer device (black curve) to another tested device with higher  $R_w = 2.54 \text{ k}\Omega$ ,  $R_P = 12.4 \Omega$ , and TMR = 21% (blue curve). Even though the TMR is higher, since  $(R_{OUT} + R_{LOAD})/R_P$  is also higher we find lower  $\Delta I/I = 0.1\%$ . For a given wire resistivity and MTJ resistance-area product, we can reduce the ratio between the wire and MTJ resistances by properly choosing the size of the wire and the size of the MTJ. Future devices with size optimized for resistance instead of fabrication constraints are expected to exhibit a substantially larger percent change in current. Increasing the MTJ quality to TMR = 100-600% (ref. 5) and choosing the wire and MTJ geometries to match ( $R_{OUT} + R_{LOAD}$ ) and  $R_P$  would increase  $\Delta I/I$  up to 100–600%, and implementing PMA and spin Hall-induced switching could reduce power consumption and  $J_T$  by  $100 \times$  (ref. 26).

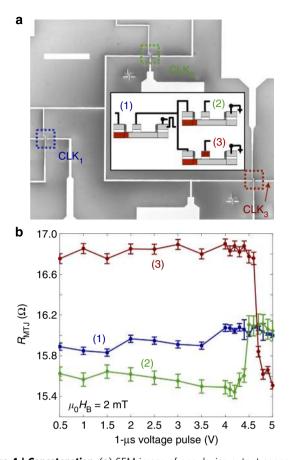

**Figure 4 | Concatenation. (a)** SEM image of one device output connecting to the inputs of two devices. Voltage pulses are applied to  $CLK_1$  with  $CLK_2$  and  $CLK_3$  grounded. Scale bar, 100  $\mu$ m. (inset) Cartoon of the initial configurations of the three devices, with the DWs initialized on the left. Red signifies magnetized right and grey signifies magnetized left. (b), Plot of MTJ resistance versus pulsed voltage applied at  $CLK_1$ , showing one device can power a switch in two subsequent devices. Here, the error bars represent the average noise fluctuation in *R* monitored for each device at each voltage step.

Device variability and reversibility. In Fig. 3a we plot the threshold voltage,  $V_{\rm T}$ , versus  $H_{\rm B}$  for three different devices to assess the variability in  $V_{\rm T} = I_{\rm T}(R_{\rm w})$  and between devices. The DW depinning voltage is repeatable within  $\pm (0.15 \pm 0.1)$  V at each bias field. This is without externally fabricated pinning, such as notches<sup>27</sup>, that can supply more repeatable depinning at the expense of higher depinning currents. There is a linear trend within a device, but variation between different devices. Devices 2 and 3 were fabricated at the same time from the same  $10 \text{ mm} \times 10 \text{ mm}$  thin-film wafer piece, while device 1 was fabricated at a different time from a separate wafer piece and shows higher device-to-device variation in the  $V_{\rm T}$  versus  $H_{\rm B}$  slope. Thus, we can conclude that the device-to-device variation seen in the prototypes arises from variations in fabrication, for example, electron-beam resist age and etching rates, and variation in the MgO thickness across the initial 3-inch diameter thin film wafer, which causes variation in TMR across the wafer.

We can estimate the zero-field current density from the linear trends: device  $1 V_T$  ( $H_B = 0$ ) = 6.27 V. Converting to I with  $R_w = 4.4 \text{ k}\Omega$ , we find  $I_T$  ( $H_B = 0$ ) = 1.4 mA and  $J_T$  ( $H_B = 0$ ) = 8.75 × 10<sup>11</sup> A m<sup>-2</sup>. This is in agreement with the current density needed to translate a DW in in-plane magnetic anisotropy wires<sup>20</sup>.

а

b

С

d

$R_{\rm MTJ}$  (normalized to  $R_{\rm P}$ ) 0.95 CLK<sub>1</sub>→CLK<sub>2</sub> CLK<sub>2</sub>→CLK<sub>3</sub> CLK<sub>3</sub>→CLK<sub>1</sub> CLK<sub>1</sub>→CLK<sub>2</sub>

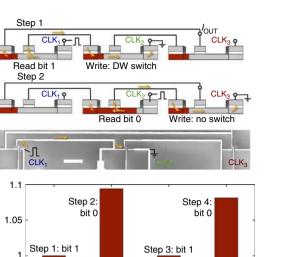

Figure 5 | Three inverters circuit. (a) Cartoon showing three devices connected in series, with the output of device 3 feeding back into the input of device 1. The devices are initialized with their domain walls (DWs) on the left and the tunnel junctions parallel. In the experiment, at Step 1 we apply a voltage pulse at CLK1 to read the state of device 1 while writing the state of device 2. The voltage pulse is applied between  $CLK_n$  and  $CLK_{n+1}$ . Yellow arrows represent electron flow direction. In this case the DW in device 2 switches. (b) Cartoon of Step 2, where we now apply a voltage pulse at CLK<sub>2</sub> to read the state of device 2 while writing the state of device 3. In this case the DW in device 3 does not switch. In Step 3 and Step 4 this is repeated at CLK<sub>3</sub> and CLK<sub>1</sub>, respectively. (c) SEM of three devices in series.  $R_{P1} = 23.8 \Omega$ ,  $R_{P2} = 19.0 \Omega$ , and  $R_{P3} = 18.4 \Omega$ . Scale bar, 50 µm. (**d**) Plot of the MTJ resistance at each step in the three inverters circuit, showing the oscillation of the DW position at each step between the parallel (low MTJ resistance, bit 1) and antiparallel (high MTJ resistance, bit 0) device states.

Figure 3b shows the reversibility behaviour of device 1. After initialization in the buffer configuration, at +2.9 V  $R_{\text{MTI}}$  switches low; reversing  $\hat{\mathbf{H}}_{B}$  we see  $R_{MTI}$  switch high again at -4.8 V.  $H_{B}$  is higher on the negative side of the loop since the field direction is less parallel to the DW.

Concatenation behaviour of multiple devices in circuits. Figure 4a is a SEM image showing three devices concatenated together, with device 1's output feeding the input of device 2 and device 3. The dotted boxes identify devices shown in Fig. 1c. The initial state is conceptualized in Fig. 4a (inset). After initialization and  $\mu_0 H_{\rm B} = 2.0 \,\mathrm{mT}$ , devices 1 and 2 are in an inverter configuration, and device 3 is a buffer. We then apply 1 µs voltage pulses to the CLK<sub>1</sub> terminal with the CLK<sub>2</sub>/CLK<sub>3</sub> terminals maintained at ground and all other terminals floating. Figure 4b shows  $R_{\text{MTJ}}$  after each pulse. The output current from device 1 switches both device 2 and device 3, at  $4.5 V \pm 0.3 V$  and  $4.7 V \pm 0.2 V$ , respectively (range is from three experiment repeats). The resistance of device 1 remains unchanged because its DW is initialized on the left side of its wire, and thus we are able to read device 1 without disturbing its logic state. This demonstrates that one gate can drive two gates, and that we can read the state of device 1 and then use that output current as the input to write devices 2 and 3. We can power more than two gates by further increasing the voltage pulse amplitude or tuning the resistance-area product of the MTJ to output higher current.

Figure 5 shows a circuit of three inverters that concatenates three devices in series. The output of device 3 is fed back into the

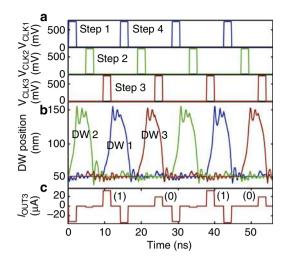

Figure 6 | Simulation of scaled three inverters circuit. Micromagnetic/ circuit simulation of transient behaviour predicted in a scaled-down device circuit with w = 15 nm and TMR = 100%. (a) 0.7 V, 2 ns clock voltages for each device applied sequentially in time. (b) Simulation of the domain wall (DW) behaviour of each device, where we can see the DW switches between the left side of the device ( $\sim$  50 nm) and the right ( $\sim$  150 nm). Once the DW switches, it oscillates about its position. (c), Current at the I<sub>OUT3</sub> node from Fig. 5a versus time. The positive current oscillates between bit 1 (32  $\mu$ A) and bit 0 (19  $\mu$ A). The negative current is from current flowing back from subsequent clock pulses, but it does not disturb the DW position in device 3.

input of device 1. We initialize all devices in the inverter configuration, depicted in Fig. 5a. To drive the logic flow, we apply sequential voltage pulses to CLK<sub>1</sub>, CLK<sub>2</sub> and then CLK<sub>3</sub>. For example, in Step 1, the voltage pulse applied to  $CLK_1$  with CLK<sub>2</sub> grounded allows us to read device 1 while writing device 2. Since the output of device 1 is high (bit 1), the current is high enough to switch the DW in device 2, changing it from a 1 bit to a 0 bit. In Step 2, Fig. 5b, we apply a voltage pulse to CLK<sub>2</sub> with CLK<sub>3</sub> grounded to read device 2 while writing device 3. Since device 2's output current is now low (bit 0), the DW in device 3 does not switch and it stays as a bit 1.

Figure 5c shows an SEM image of a fabricated three inverters circuit, initialized in the inverter configuration with  $\mu_0 H_{\rm B} = 3.0 \,\mathrm{mT}$ . In Fig. 5d, we measure  $R_{\rm MTI}$  as the information propagates around the circuit. The devices are clocked in sequence by 4.5-V pulses such that at each stage the data token is inverted. The voltage amplitude of 4.5 V is optimized for device 3, such that when device 2 is in the antiparallel state the DW of device 3 does not switch. To see the inverting operation, each resistance is normalized to its own  $R_{\rm P}$ . The output resistance at each pulse step oscillates between  $R_{\rm P}$  and  $R_{\rm AP}$  as we move around the circuit, showing oscillation between 1 and 0 bits. Operation is stopped after four steps because additional propagation requires a reset step to return all DWs to the left side. We expect that scaled down devices or materials with lower threshold currents should operate without the need of a bias field, allowing the reset to occur during reading.

In Fig. 6, we model the behaviour of a scaled three-inverter circuit using a transient micromagnetic/circuit simulation<sup>1</sup> to predict scaling, switching energy, and switching delay. For the micromagnetic simulation, we use the Object-Oriented Micromagnetic Framework<sup>28</sup> model with a current-induced DW motion extension<sup>29</sup>. We assume t = 2.5 nm, w = 15 nm, wire length 200 nm, TMR = 100%, and material properties for in-plane anisotropy CoFeB (exchange energy  $13 \times 10^{-12}$  J m<sup>-1</sup>, damping parameter  $\alpha = 0.01$ , non-adiabatic parameter  $\beta = 0.05$ ,

saturation magnetization  $M_{\rm S} = 8 \times 10^5 \,\mathrm{A \, m^{-1}}$ , and spin polarization factor P = 0.4 (ref. 18)). The simulation inputs current and outputs the new DW position in the wire. We then convert the DW position to a new  $R_{\rm MTJ}$  value, which we input into the three-terminal SPICE circuit model<sup>30</sup> shown in Fig. 2b. The circuit model calculates *I* and *V* at every node of the circuit, which we input back into the micromagnetic model. We repeat this iterative process every 0.05 ns over the timescale of interest.

Figure 6 shows the simulated transient circuit behaviour. The information flows sequentially, driven by 0.7 V, 2-ns clock pulses. At Step 1 (equivalent to Fig. 5a) we apply  $V_{\text{CLK1}}$ , shown by the blue voltage pulse. The DW position versus time plot shows that the DW of device 2 switches across the device (green curve). At Step 2 (equivalent to Fig. 5b) we apply  $V_{\text{CLK2}}$ , shown by the green voltage pulse. In the DW position versus time plot, the red curve represents the position of the DW in device 3, and we see that its DW does not switch at Step 2. This oscillatory behaviour is repeated in Step 3, Step 4 and so on. The data token is inverted every stage, meaning that the DW moves in every other device, for example, device 2 (green), device 1 (blue) and device 3 (red). The simulated circuit differs from the implementation, however, because the implementation uses a bias field. In the absence of the bias field in the scaled simulation, the logic resets itself during the read operation. By monitoring the IOUT node in the simulation, we see it oscillates between high current (bit 1, 32 µA) and low current (bit 0,  $19 \,\mu$ A) depending on the DW position of device 3. The negative pulses in the current transient occur when current is flowing backward from the next gate.

#### Discussion

We have demonstrated the capability of DW-based devices as logic gates, including inverter, buffer, and circuit operation. The DW depinning is non-linear with a sharp switching threshold  $\delta V < 0.01$  V, allowing stable 0 and 1 bits below and above the DW depinning voltage. The gates exhibit gain, one gate can drive two subsequent gates, and the three-device circuits shows that they can be cascaded into circuits. The micromagnetic/circuit simulation shows analogous switching behaviour to the experiment in further scaled devices.

While the information is encoded in the DW position, the inputs and outputs are current, maintaining compatibility with conventional field-effect transistors. The gate architecture is simple and adaptable to recent advances in magnetic materials, allowing an increase in  $\Delta I/I$  up to 100–600% and a reduction in power consumption and  $J_{\rm T}$  by 100 ×. These results show that magnetic-based logic has a realistic path to implementation, and may provide the basis for digital systems at the end of the semiconductor roadmap.

#### Methods

**Fabrication**. Thin film growth was done using UHV d.c. magnetron sputtering<sup>31</sup>. The sample was annealed *in situ* at 280 °C for 30 min with MgO exposed to vacuum to crystalize the CoFeB layer, and *ex situ* at 300 °C for 1 h in a 1-tesla field to set the IrMn exchange bias. Patterning was done using hydrogen silsesquioxane (HSQ) electron-beam resist and a Raith 150 electron-beam lithography tool. The pattern was etched into the thin film using non-reactive ion beam etching. HSQ was used as a spin-on insulator to prevent shorting of the device. A further electron-beam lithography step using polymethyl methacrylate was done to open holes on top of the three terminals for electrical contact. The darker ellipse on top of the MTJ in Fig. 1c shows a hole patterned in the SiO<sub>2</sub> insulating layer to electrically contact the MTJ top. Alignment of the hole on top of the initial size of the prototypes. Then Ta (5 nm)/Au (135 nm) electrodes were placed with an additional electron-beam lithography step.

**Resistance and current-driven measurements.** For testing, the devices were wire bonded to a chip carrier and placed in an electromagnet. A signal multiplexer

alternated the device terminal connections between a resistance measuring set-up and a pulse driving set-up.

In the resistance measuring set-up, a lock-in amplifier performed a four-point resistance measurement by forcing a sinusoidal voltage (100 mV, 6.25 Hz

quasi-DC) between one OUT terminal and the IN terminal and sensing the output voltage between a second OUT terminal and the CLK terminal. The forced current was known and kept low by a 100 k $\Omega$  ballast resistor connected in series with the measured resistance.

In the pulse driving set-up, a pulse generator provided the applied current pulse across the DW track between the IN and CLK terminals.

#### References

- Currivan, J. A., Jang, Y., Mascaro, M. D., Baldo, M. A. & Ross, C. A. Low energy magnetic domain wall logic in short, narrow, ferromagnetic wires. *IEEE Magn. Lett.* 3, 3000104 (2012).

- Nikonov, D. E. & Young, I. A. in 2012 IEEE International Electron Devices Meeting (IEDM) 25–4 (San Francisco, CA, USA 2012).

- Parkin, S. S., Hayashi, M. & Thomas, L. Magnetic domain-wall racetrack memory. *Science* 320, 190–194 (2008).

- Kim, J. et al. Spin-based computing: device concepts, current status, and a case study on a high-performance microprocessor. Proc. IEEE 103, 106–130 (2015).

- 5. Allwood, D. A. et al. Magnetic domain-wall logic. Science **309**, 1688–1692 (2005).

- Imre, A. *et al.* Majority logic gate for magnetic quantum-dot cellular automata. *Science* 311, 205–208 (2006).

- Emori, S. & Beach, G. S. D. Enhanced current-induced domain wall motion by tuning perpendicular magnetic anisotropy. *Appl. Phys. Lett.* 98, 132508 (2011).

- Wang, W.-G., Li, M., Hageman, S. & Chien, C. L. Electric-field-assisted switching in magnetic tunnel junctions. *Nat. Mater.* 11, 64–68 (2012).

- Kim, K. W., Seo, S. M., Ryu, J., Lee, K. J. & Lee, H. W. Magnetization dynamics induced by in-plane currents in ultrathin magnetic nanostructures with Rashba spin-orbit coupling. *Phys. Rev. B* 85, 180404 (2012).

- Ryu, J., Lee, K.-J. & Lee, H.-W. Current-driven domain wall motion with spin Hall effect: Reduction of threshold current density. *Appl. Phys. Lett.* 102, 172404 (2013).

- Buhrman, R. A. Spin-torque switching with the giant spin Hall effect of tantalum. Science 336, 555–558 (2012).

- Lavrijsen, R. et al. Magnetic ratchet for three-dimensional spintronic memory and logic. Nature 493, 647–650 (2013).

- 13. Fukami, S. et al. in 2009 Symposium on VLSI Technology 230-231 (Honolulu, HI, USA, 2009).

- Nikonov, D. E., Bourianoff, G. I. & Ghani, T. Proposal of a spin torque majority gate logic. *IEEE Electr. Device Lett.* 32, 1128–1130 (2011).

- Breitkreutz, S. *et al.* Majority gate for nanomagnetic logic with perpendicular magnetic anisotropy. *IEEE Trans. Magn.* 48, 4336–4339 (2012).

- Kurtz, S. et al. Non-majority magnetic logic gates: a review of experiments and future prospects for 'shape-based' logic. J. Phys. Condens. Matter. 23, 053202 (2011).

- Bromberg, D. M. et al. in 2014 International Electron Device Meeting 33.1.1–33.1.4 (San Francisco, CA, USA, 2014).

- Beach, G. S. D., Tsoi, M. & Erskine, J. L. Current-induced domain wall motion. J. Magn. Magn. Mater. 320, 1272–1281 (2008).

- Ikeda, S. et al. Tunnel magnetoresistance of 604% at 300 K by suppression of Ta diffusion in CoFeB/ MgO/ CoFeB pseudo-spin-valves annealed at high temperature. Appl. Phys. Lett. 93, 082508 (2008).

- Fukami, S., Suzuki, T., Ohshima, N., Nagahara, K. & Ishiwata, N. Micromagnetic analysis of current driven domain wall motion in nanostrips with perpendicular magnetic anisotropy. J. Appl. Phys. 103, 07E718 (2008).

- Sathe, V. S. et al. Resonant-clock design for a power-efficient, high-volume x86-64 microprocessor. IEEE J. Solid State Circuits 48, 140–149 (2013).

- Koyama, T. et al. Observation of the intrinsic pinning of a magnetic domain wall in a ferromagnetic nanowire. Nat. Mater. 10, 194–197 (2011).

- Emori, S., Umachi, C. K., Bono, D. C. & Beach, G. S. Generalized analysis of thermally activated domain-wall motion in Co/Pt multilayers. J. Magn. Magn. Mater. 378, 98–106 (2015).

- Currivan, J. A. *et al.* Polymethyl methacrylate/hydrogen silsesquioxane bilayer resist electron beam lithography process for etching 25 nm wide magnetic wires. *J. Vac. Sci. Technol. B* 32, 021601 (2014).

- Piotrowski, S. et al. Conductive atomic force microscopy of small magnetic tunnel junctions with interface anisotropy. IEEE Trans. Magn. 99, 1 (2015).

- Emori, S., Bauer, U., Ahn, S.-M., Martinez, E. & Beach, G. S. Current-driven dynamics of chiral ferromagnetic domain walls. *Nat. Mater.* 12, 611–616 (2013).

- Faulkner, C. C. Artificial domain wall nanotraps in Ni<sub>81</sub>Fe<sub>19</sub> wires. J. Appl. Phys. 95, 6717 (2004).

- Donahue, M. J. & Porter, D. G. OOMMF User's Guide, Version 1.0. Interagency Report NISTIR 6376. *National Institute of Standards and Technology*. Available at http://math.nist.gov/oommf (1999).

- 29. Vanhaverbeke, A. Spintevolve. (IBM Research, Zurich, 2008) http:// www.zurich.ibm.com/st/magnetism/spintevolve.html.

- 30. LTSpice v. 4 (Linear Technology, 2014).

- 31. Evarts, E. R. et al. Spin transfer torque switching of magnetic tunnel junctions using a conductive atomic force microscope. Appl. Phys. Lett. 95, 132510 (2009).

#### Acknowledgements

This work was supported by the National Science Foundation under contract ECCS-1101798 and the Department of Energy Office of Science Graduate Fellowship Program. We acknowledge the MIT NanoStructures Laboratory for fabrication, especially the support of Mark Mondol and James Daley.

#### Author contributions

J.A.C.-I. designed the experiment, fabricated the devices and performed the measurements and analysis. S.S. assisted with fabrication and testing. S.D. contributed to the measurement set-up and assisted with analysis. E.R.E. grew the thin films. J.Z. and D.B. contributed to the measurement set-up. C.A.R. and M.A.B. designed the experiment, planned and supervised the project and contributed to the analysis.

#### Additional information

Supplementary Information accompanies this paper at http://www.nature.com/ naturecommunications

Competing financial interests: The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/ reprintsandpermissions/

How to cite this article: Currivan-Incorvia, J. A. et al. Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls. Nat. Commun. 7:10275 doi: 10.1038/ncomms10275 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/