# LOW JITTER LOW POWER PHASE LOCKED LOOPS USING SUB-SAMPLING PHASE DETECTION

Xiang Gao

#### **Promotion Committee:**

| Chairman:           | prof.dr.ir. A. J. Mouthaan    | Universiteit Twente            |

|---------------------|-------------------------------|--------------------------------|

| Secretary:          | prof.dr.ir. A. J. Mouthaan    | Universiteit Twente            |

| Promotor:           | prof.dr.ir. B. Nauta          | Universiteit Twente            |

| Assistant Promotor: | dr.ing. E. A. M. Klumperink   | Universiteit Twente            |

| Members:            | prof.dr.ir. F. E. van Vliet   | Universiteit Twente            |

|                     | prof.ir. A. J. M. van Tuijl   | Universiteit Twente            |

|                     | prof.dr.ir. M. S. J. Steyaert | Katholieke Universiteit Leuven |

|                     | prof.dr.ir. R. B. Staszewski  | Technische Universiteit Delft  |

| Title:  | Low Jitter Low Power Phase Locked Loops Using Sub-Sampling |  |

|---------|------------------------------------------------------------|--|

|         | Phase Detection                                            |  |

| Author: | Xiang Gao                                                  |  |

| ISBN:   | 978-90-365-3022-4                                          |  |

| DOI:    | 10.3990/1.9789036530224                                    |  |

© 2010, Xiang Gao All rights reserved.

This work was supported by National Semiconductor Corporation, Santa Clara, California.

## LOW JITTER LOW POWER PHASE LOCKED LOOPS USING SUB-SAMPLING PHASE DETECTION

DISSERTATION

to obtain the degree of doctor at the University of Twente, on the authority of the rector magnificus, prof.dr. H. Brinksma, on account of the decision of the graduation committee, to be publicly defended on Wednesday 9 June 2010 at 16:45

by

Xiang Gao born on 5 June 1983 in Zhejiang, China This dissertation is approved by

the promotor, prof.dr.ir. B. Nauta

and the assistant promotor, dr.ing. E. A. M. Klumperink

"Everything should be made as simple as possible, but not simpler." – Albert Einstein

To Xiaoyan, Ruoxi and my parents

## Abstract

A periodic clock signal is required in many ICs. These clocks are for instance used to define the sampling moments in data converters; to up-convert and down-convert the wanted signals in wireless transceivers and to synchronize the data flow in wireline and optical serial data communication links. The clock timing/phase accuracy affects the overall system performance and therefore a clock generator should have low jitter/phase-noise. Moreover, a clock generator is also desired to dissipate low power to save energy.

This thesis aims to design a clock generation phase-locked loop (PLL) with low jitter as well as low power. It starts with the classical PLL phase noise and jitter analysis. Different sources of PLL phase noise are identified and analyzed. The overall PLL phase noise and output jitter are calculated and optimization methods are discussed. The scaling of the PLL jitter and power with the input frequency, output frequency and the division ratio *N* are examined and a benchmark figure-of-merit is proposed to evaluate the overall PLL jitter and power performance.

In some applications, e.g. time-interleaved ADCs and image and harmonic rejection radio transceivers, a group of clocks with multiple phases are needed. Two competing techniques to realize such clocks, one based on a shift register (SR) and the other on a delay-locked loop (DLL), are discussed. The relative merits of the two techniques are compared, primarily based on their jitter and power performance. Analysis shows that a SR is not only more flexible, but also almost always generates less jitter than a DLL for a given power, when both are realized with current mode logic. The analytical results are verified with simulation results. To generate high quality multi-phase clocks, both methods need a reference clock with low jitter. Such a reference clock can be generated using a low jitter PLL which is the main topic of this thesis.

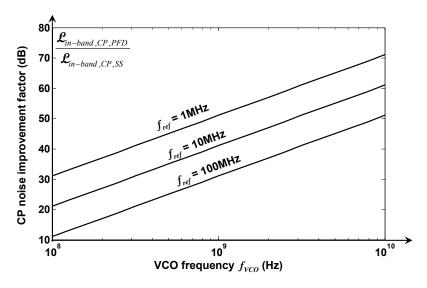

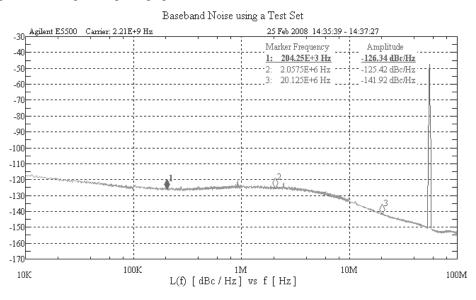

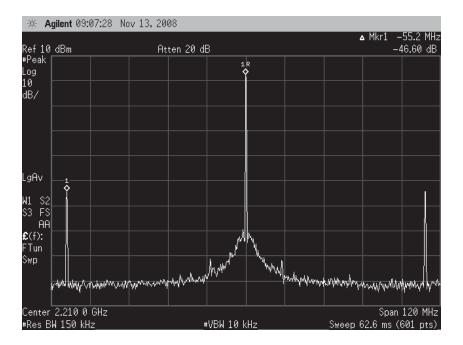

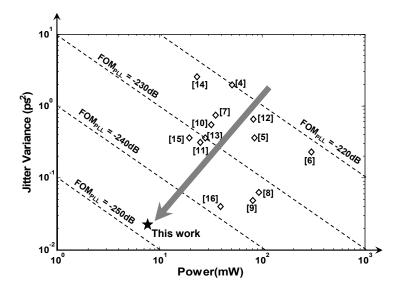

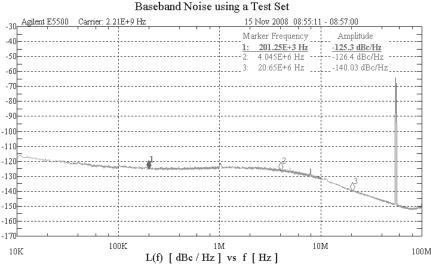

In a classical PLL, the phase detector (PD), charge pump (CP) and divider noise is multiplied by  $N^2$  due to the existence of the divide-by-N in the feedback path. This is often the bottleneck for low PLL in-band phase noise. This work proposes to use a sub-sampling PLL (SSPLL) architecture to break this bottleneck. The SSPLL exploits a sub-sampling phase detector (SSPD) that directly samples the high frequency VCO output with the low frequency reference clock and converts the VCO phase error into sampled voltage variation. The SSPLL is divider-less in the locked state and thus has no divider noise. Furthermore, analysis shows that the PD and CP noise is not multiplied by  $N^2$  in this PLL, resulting in very low in-band phase noise. To prove the concepts, a fully integrated 2.2 GHz SSPLL is implemented in 0.18-µm CMOS. It achieves -126 dBc/Hz at 200 kHz in-band phase noise, 0.15 ps rms output jitter (10 kHz to 40 MHz), -46 dBc reference spur while consuming 7.6 mW. When normalized to the same output jitter, it is an order of magnitude more power efficient than the state-of-art classical PLLs.

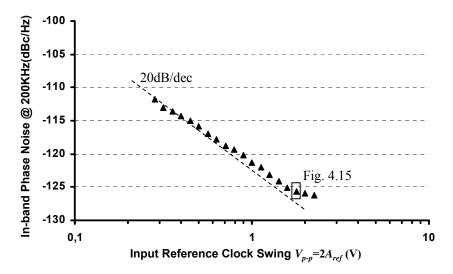

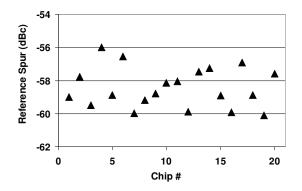

In order to improve the power efficiency of the SSPLL even further, a buffer-less direct VCO sampling scheme is proposed. No buffer is used between the VCO and SSPD while dummy samplers keep the disturbance of the SSPD sampling to the VCO low. Furthermore, a modified inverter with separate gate control for the NMOS and PMOS transistors are proposed to convert the sine-wave reference clock to a square wave in a power efficient way. By making the conduction time for the NMOS and PMOS non-overlapping, the direct current path from the supply to ground is eliminated, which eliminates the inverter short-circuit current and drastically reduces its power consumption. Measurements show that a 2.2 GHz SSPLL designed with these techniques can achieve -125 dBc/Hz in-band phase noise at 200 kHz while only dissipating 700  $\mu$ W power excluding the VCO. The whole SSPLL consumes 2.5 mW and its rms jitter is 0.16 ps (10 kHz to 100 MHz). The reference spurs measured from 20 chips are lower than -56 dBc.

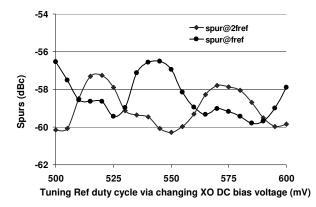

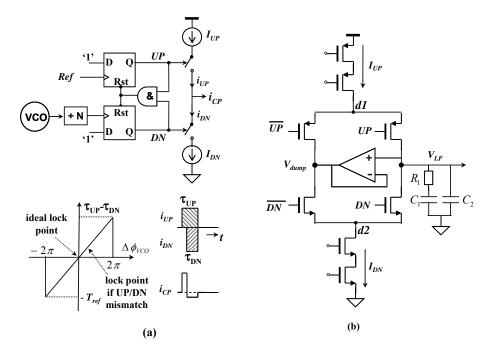

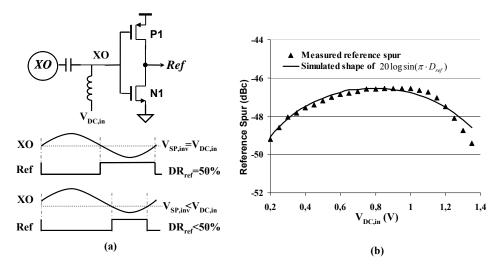

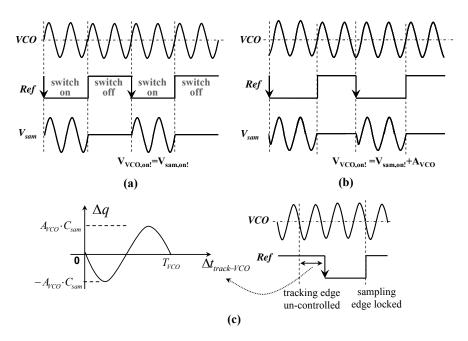

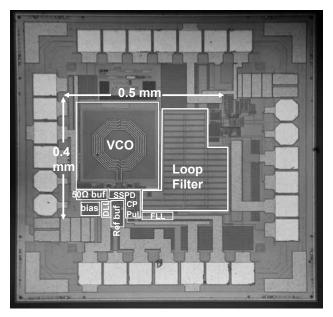

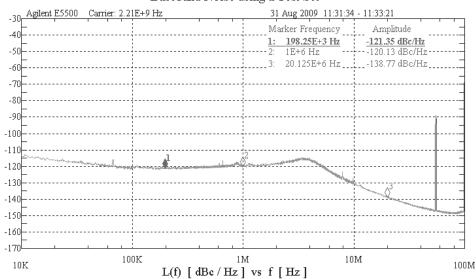

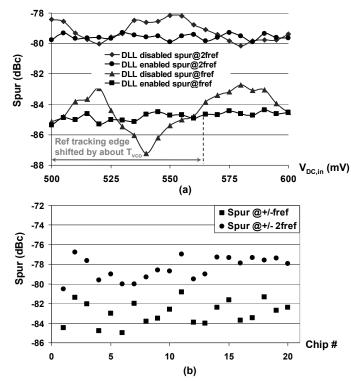

Although the previous two SSPLL designs achieve very low phase-noise/jitter with low power, the reference spurs are relatively high. In the classical PLL, the major source of spurs is usually the mismatch between the CP up- and down- current sources. In contrast, analysis reveals that the CP in the SSPLL is actually insensitive to mismatch due to its amplitude-controlled nature. Analysis reveals that the main source of the SSPLL spurs is the SSPD sampler which periodically disturbs the VCO operation via charge injection, charge sharing and frequency modulation by periodically changing the VCO capacitive load. Dummy samplers and isolation buffers are then used to minimize the disturbance of the SSPD to the VCO. A duty cycle controlled reference buffer with DLL tuning are proposed to further reduce the worst case spur. To verify the spur reduction concepts, a new SSPLL design optimizing for low spur is fabricated in 0.18-µm CMOS. While using a high loop-bandwidth-to-reference-frequency ratio of 1/20, the reference spurs measured from 20 chips are <-80 dBc. The rms output jitter is 0.3 ps (10 kHz to 100 MHz) while the power consumption is 3.8 mW.

## Samenvatting

Vele ICs (Integrated Circuits, "chips") hebben een periodiek kloksignaal nodig. Deze klok wordt bijvoorbeeld gebruikt om het moment van bemonstering ("samplen") bij data conversie te bepalen; om de frequentietranslatie in draadloze zenders en/of ontvangers vast te leggen en om datastromen over kabels en optische communicatie verbindingen te synchroniseren. De nauwkeurigheid van de timing c.q. fase van de klok beïnvloedt de haalbare systeemprestaties, zodat een klokgenerator een lage jitter en fasefout moeten hebben. Bovendien dient een klokgenerator bij voorkeur weinig vermogen te gebruiken om energie te besparen.

Het in dit proefschrift beschreven werk is erop gericht een klokgeneratie Phase Locked Loop (PLL) te ontwerpen met lage jitter. Het proefschrift analyseert eerst de faseruis en jitter in een klassieke PLL, waarbij verschillende ruisbronnen worden geïdentificeerd en gekwantificeerd. De totale faseruis en jitter van het uitgangssignaal wordt berekend en methodes om deze te optimaliseren worden besproken. De afhankelijkheid van PLL jitter en vermogensdissipatie van de frequentie van de PLL in- en uitgangssignaal en het deelgetal *N* worden onderzocht, waarbij een figure of merit (FoM) wordt voorgesteld ter evaluatie van de totale jitter in relatie tot de vermogensdissipatie van een PLL.

In sommige toepassingen, b.v. time-interleaved ADCs en ten behoeve van de spiegelonderdrukking en harmonischen onderdrukking in radiozenders en ontvangers is een groep klokken met equidistante fases nodig. Twee concurrerende technieken om dergelijke klokken te realiseren worden vergeleken, één op basis van een schuifregister (SR) en de andere op basis van een delay-locked loop (DLL). De relatieve verdiensten van de twee technieken worden vergeleken, hoofdzakelijk op basis van hun jitter en vermogensverbruik. De analyse toont aan dat een SR niet alleen flexibeler is, maar ook vrijwel altijd minder jitter produceert dan een DLL die evenveel vermogen verbruikt, veronderstellend dat beide gerealiseerd zijn in current-mode logica. De analytische resultaten zijn geverifieerd met simulatieresultaten. Om meerfasige klokken van goede kwaliteit te produceren, is een hoogfrequente referentieklok met lage jitter nodig, wat het hoofddoel van dit proefschrift is.

In een klassieke PLL worden de ruisbijdragen van fasedetector (PD), de ladingspomp (CP) en de frequentiedeler naar de uitgang vermenigvuldigd met  $N^2$ , vanwege de aanwezigheid van de deler in het terugkoppelpad. Deze ruisbijdragen vormen veelal de bottleneck voor de laagfrequente faseruis van de PLL, binnen de lusbandbreedte. In dit proefschrift wordt een sub-sampling PLL (SSPLL) architectuur voorgesteld om deze bottleneck te breken. De SSPLL exploiteert een sub-sampling fasedetector (SSPD) die de hoogfrequente VCO-uitgang direct bemonstert in het ritme van de referentieklok, waarbij de fasefout van de VCO omgezet wordt in een spanning. De SSPLL heeft geen deler en daardoor geen faseruis bijdrage van de deler. Voorts toont analyse aan dat, anders dan in de klassieke PLL, de ruis van de PD en CP niet worden vermenigvuldigd met  $N^2$  in de SSPLL, hetgeen resulteert in een zeer lage faseruis binnen de lusbandbreedte. Om de praktische waarde van de architectuur te bewijzen is een 2.2 GHz SSPLL ontworpen die volledig is geïntegreerd op een 0.18-µm CMOS chip. Metingen geven een faseruis van -126 dBc/Hz bij 200 kHz binnen de lusbandbreedte, 0.15 ps rms output jitter (van 10 kHz t/m 40 MHz), een spur van -46dBc en een vermogensverbruik van 7.6 mW. Genormeeerd naar dezelfde output jitter, is de SSPLL een grootteorde meer energie efficiënt dan de klassieke PLL.

Om het vermogensverbruik van de SSPLL nog verder te verbeteren, wordt voorgesteld om een VCO direct te bemonsteren zonder de VCO te bufferen. Door "dummy-samplers" toe te voegen, wordt de verstoring van de VCO door het sampling proces geminimaliseerd. Voorts wordt een gewijzigde referentiebuffer voorgeteld waarin de NMOS en PMOS apart wordt geschakeld om de sinus-golf op een efficiënte manier om te zetten naar een blokgolf. Door gelijktijdige geleiding van de NMOS en PMOS te vermijden, wordt het directe stroompad tussen de voeding en aarde geëlimineerd, wat het vermogensgebruik drastisch vermindert. Metingen aan een 2.2 GHz SSPLL met deze technieken geven een faseruis van -125 dBc/Hz binnen de lusbandbreedte bij 200 kHz, terwijl slechts 700  $\mu$ W vermogen wordt gebruikt door de loopcomponenten (PLL exclusief de VCO). Het totale vermogensverbruik van deze SSPLL is 2.5 mW en zijn rms jitter is 0.16 ps (van 10 kHz t/m 100 MHz). De spurs zijn <-56 dBc voor 20 gemeten chips.

Hoewel de vorige twee SSPLL ontwerpen een zeer lage faseruis en jitter hebben bij een laag vermogensgebruik, zijn de spurs nog vrij sterk. In de klassieke PLL, is de belangrijkste bron van spurs gewoonlijk de ongelijkheid van de laad- en ontlaadstroom van de CP. Uit analyse blijkt echter dat de CP in een SSPLL ongevoelig is voor deze ongelijkheid, door zijn amplitude geregelde karakter. Uit analyse blijkt dat de belangrijkste bron van spurs in de SSPLL wordt gevormd door periodieke verstoringen van de VCO door de sampling actie. Dit gebeurt via ladingsinjectie, ladingsdeling en frequentiemodulatie door de periodiek variabele capacitieve belasting. Door het gebruik van dummy samplers en isolerende buffers kan de verstoring van de VCO in de SSPD geminimaliseerd worden. Om de worst case spur te verbeteren wordt de duty-cycle het referentiebuffer signaal afgeregeld via een DLL. Om de reductie in spurs te verifiëren, is een SSPLL ontworpen in 0.18-µm CMOS. De SSPLL chip geeft bij een hoge verhouding van de lusbandbreedte en referentiefrequentie van 1/20 voor 20 chips in alle gevallen een spur <-80 dBc. De rms output jitter is 0.3 ps (van 10 kHz t/m 100 MHz) terwijl het vermogensgebruik slechts 3.8 mW is.

# Contents

| Abstract |                                                             | i   |

|----------|-------------------------------------------------------------|-----|

| Sa       | amenvatting                                                 | iii |

| L        | ist of Abbreviations                                        | ix  |

| 1        | Introduction                                                | 1   |

|          | 1.1 Low Jitter PLL: Motivation                              | 1   |

|          | 1.2 A Brief PLL Review                                      | 3   |

|          | 1.3 Research Objectives                                     | 6   |

|          | 1.4 Thesis Organization                                     | 7   |

|          | 1.5 References                                              | 8   |

|          |                                                             |     |

| 2        | Classical PLL Jitter Analysis                               | 11  |

|          | 2.1 Introduction                                            | 11  |

|          | 2.2 Classical PLL Phase Domain Model                        |     |

|          | 2.3 VCO Phase Noise and Benchmarking                        | 14  |

|          | 2.4 Loop Phase Noise and Benchmarking                       | 14  |

|          | 2.4.1 Phase Noise due to the Reference Path, Divider and PD | 15  |

|          | 2.4.2 Phase Noise due to the CP                             | 17  |

|          | 2.4.3 Loop Phase Noise Benchmarking                         | 17  |

|          | 2.5 PLL Jitter and Benchmarking                             |     |

|          | 2.5.1 PLL Output Jitter                                     |     |

|          | 2.5.2 PLL Jitter Optimization                               |     |

|          | 2.5.3 PLL Benchmarking                                      |     |

|          | 2.6 Conclusion                                              |     |

|          | 2.7 References                                              | 25  |

| 3        | Low Jitter Multi-phase Clock Generation                     | 27  |

| 3.1 Introduction                                            | 27 |

|-------------------------------------------------------------|----|

| 3.2 DLL MPCG Jitter                                         | 28 |

| 3.2.1 DLL MPCG Architecture                                 | 28 |

| 3.2.2 DLL MPCG Output Jitter                                | 29 |

| 3.3 SR MPCG JITTER                                          | 30 |

| 3.3.1 SR MPCG Architecture                                  | 30 |

| 3.3.2 SR MPCG Output Jitter                                 | 30 |

| 3.4 Comparison between DLL and SR MPCG Jitter               | 31 |

| 3.4.1 Comparing Jitter Transferred from the Reference Clock | 31 |

| 3.4.2 Comparing Jitter Generated due to Thermal Noise       | 32 |

| 3.4.3 Comparing Jitter Generated due to Mismatch            | 35 |

| 3.4.4 Discussion                                            | 36 |

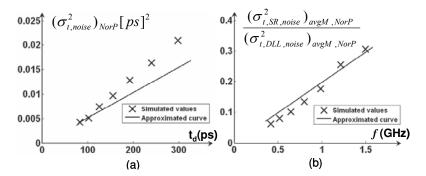

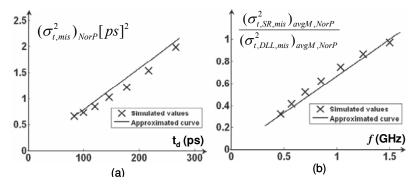

| 3.5 Simulation Results                                      | 38 |

| 3.6 Conclusion                                              | 38 |

| 3.7 References                                              | 39 |

|                                                             |    |

| Low Jitter Sub-Sampling PLL 4                               | 41 |

| 4.1 Introduction                                            | 41 |

| 4.2 Low Noise Phase Detection                               | 42 |

| 4.2 Low Noise Phase Detection        |    |

|--------------------------------------|----|

| 4.2.1 Classical 3-state PFD/CP       | 43 |

| 4.2.2 Proposed Sub-Sampling PD/CP    | 44 |

| 4.2.3 CP Noise Comparison            | 47 |

| 4.3 Sub-Sampling PLL                 |    |

| 4.3.1 Modeling and Noise Analysis    |    |

| 4.3.2 Chip Area Considerations       |    |

| 4.3.3 SSPD/CP with Gain Control      |    |

| 4.3.4 Frequency Locking              | 53 |

| 4.4 Design and Implementation        | 54 |

| 4.4.1 VCO and Measurement Buffer     | 54 |

| 4.4.2 Phase Detector and Charge Pump |    |

| 4.4.3 3-state PFD/CP with Dead Zone  |    |

| 4.5 Experimental Results             | 58 |

4

| 4.6 Conclusion | 63 |

|----------------|----|

| 4.7 References |    |

## 5 Power Reduction Techniques for SSPLI

| Power Reduction Techniques for SSPLL | 67 |

|--------------------------------------|----|

| 5.1 Introduction                     |    |

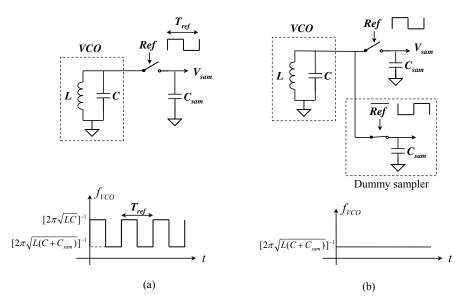

| 5.2 Buffer-less Direct VCO Sampling  |    |

| 5.3 Low Power Ref Buffer             |    |

| 5.4 Design and Implementation        |    |

| 5.5 Experimental Results             | 74 |

| 5.6 Conclusion                       | 77 |

| 5.7 References                       |    |

| 6 | Spur Reduction Techniques for SSPLL                      | 81  |

|---|----------------------------------------------------------|-----|

|   | 6.1 Introduction                                         | 81  |

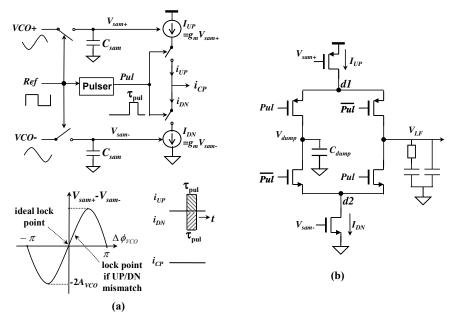

|   | 6.2 Spur due to Charge Pump                              | 83  |

|   | 6.2.1 Conventional CP                                    | 83  |

|   | 6.2.2 Low Spur CP Using Sub-sampling                     | 84  |

|   | 6.3 Spur due to VCO Sampling and Techniques to Reduce It | 86  |

|   | 6.3.1 BFSK Effect                                        | 87  |

|   | 6.3.2 Charge Sharing/Injection                           | 89  |

|   | 6.3.3 Low Spur SSPLL Architecture                        | 91  |

|   | 6.4 Design and Implementation                            | 92  |

|   | 6.4.1 VCO                                                |     |

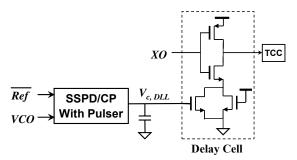

|   | 6.4.2 SSPD/CP with Pulser                                | 94  |

|   | 6.4.3 SSDLL                                              | 94  |

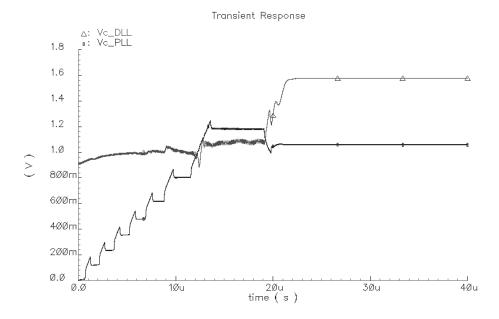

|   | 6.4.4 Settling Behavior                                  | 95  |

|   | 6.5 Experimental Results                                 | 97  |

|   | 6.6 Conclusion                                           | 100 |

|   | 6.7 References                                           | 101 |

|   |                                                          |     |

| 7 | Conclusions                 | 103   |

|---|-----------------------------|-------|

|   | 7.1 Summary and Conclusions | . 103 |

| 7.2 Original Contributions          |     |

|-------------------------------------|-----|

| 7.3 Recommendations for Future Work |     |

| 7.4 References                      |     |

| List of Publications                | 111 |

| Acknowledgements                    | 115 |

| About the Author                    | 117 |

# List of Abbreviations

| ADC   | Analog-to-Digital Converter             |

|-------|-----------------------------------------|

| BFSK  | Binary Frequency Shift Keying           |

| СР    | Charge Pump                             |

| CML   | Current Mode Logic                      |

| CMOS  | Complementary Metal-Oxide-Semiconductor |

| DCO   | Digitally Controlled Oscillator         |

| DFF   | D Flip-Flop                             |

| DLL   | Delay-Locked Loop                       |

| DU    | Delay Unit                              |

| DZ    | Dead Zone                               |

| FLL   | Frequency-Locked Loop                   |

| FOM   | Figure-of-Merit                         |

| IC    | Integrated Circuit                      |

| LF    | Loop Filter                             |

| MPCG  | Multi-Phase Clock Generator             |

| PD    | Phase Detector                          |

| PFD   | Phase-Frequency Detector                |

| PLL   | Phase-Locked Loop                       |

| rms   | Root-Mean-Square                        |

| SNR   | Signal-to-Noise Ratio                   |

| SSPD  | Sub-Sampling Phase Detector             |

| SSPLL | Sub-Sampling PLL                        |

| TDC   | Time-to-Digital Converter               |

| VCDL  | Voltage-Controlled Delay Line           |

| VCO   | Voltage-Controlled Oscillator           |

| XO    | Crystal Oscillator                      |

|       |                                         |

## Chapter 1

## Introduction

#### **1.1 Low Jitter PLL: Motivation**

The integrated circuit (IC) has enjoyed an exponential growth in the last half century since it was invented in 1959 [1], [2]. Following the famous Moore's law [3], the number of transistors in an IC or "chip" has doubled approximately every two years and reached more than two billion in 2009 [4]. IC products are now ubiquitous and universal in everyday life.

A periodic clock signal is required in many ICs. These clocks are for instance used to define the sampling moments in analog-to-digital or digital-or-analog data converters; to up-convert and down-convert the wanted signals in wireless transceivers; to synchronize the data flow in wireline and optical serial data communication links, and last but certainly not least, as a metronome to coordinate the actions of internal circuits in digital ICs.

An ideal clock is a periodic signal with a constant frequency. It delivers edge transitions or zero-crossings at precise time intervals. In reality, the frequency of the clock signal fluctuates around its mean value due to e.g. the thermal noise in the electronic devices in the clock generator. In the time domain, the inaccuracies lead to a deviation of the edge transitions of the practical clock to that of the ideal clock, called jitter or timing jitter. In the frequency domain, clock inaccuracies result in spectral components at frequencies other than the desired frequency, referred to as phase noise or spurious signals ("spurs" for short). Jitter and phase noise are related and linked with mathematical equations [5] since they characterize the inaccuracies of the same clock in the time and frequency domain.

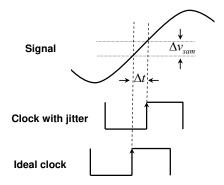

In general, the jitter or phase noise on the clock signal results in a degradation of the signal-to-noise ratio (SNR) of the signals clocked by or mixed with it. Therefore, the clock source must exhibit very low levels of jitter or phase noise in high performance ICs. One critical example is a high speed high resolution analog-to-digital converter (ADC). Fig. 1.1 shows a simple model of the sampling process in an ADC, where a sine-wave signal with frequency  $f_{sig}$  and amplitude  $A_{sig}$  is sampled by a clock. The signal voltage is sampled at the rising edge of the clock and later converted to digital by a quantizer in the ADC. Due to

Figure 1.1. Sampling process in an ADC.

jitter in the clock, the actual sampling moment deviates from the ideal one by  $\Delta t$ , resulting in an error in the sampled voltage:

$$\Delta v_{sam} = A_{sig} \cdot 2\pi f_{sig} \cdot \Delta t \cdot \cos(2\pi f_{sig} t) \,. \tag{1.1}$$

As a result of this sampled voltage error, the SNR of the ADC is degraded. Defining  $\sigma_t$  as the root-mean-square (rms) value of the clock jitter  $\Delta t$ , the achievable ADC SNR can be calculated to be [6]:

$$SNR_{jitter} = 20\log(\frac{1}{2\pi f_{sig} \cdot \sigma_t}) \cdot$$

(1.2)

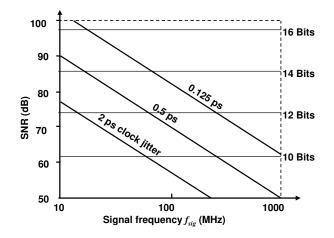

The achievable SNR of the ADC is limited by (1.2) even if the quantizer is perfect. Fig. 1.2 plots the ADC SNR and the corresponding effective number of bits for different input signal frequency limited by a certain amount of sampling clock jitter. We see that for an ADC with a higher resolution and higher frequency, the requirement on the sampling clock jitter is more stringent. In order to realize a high performance ADC, a sampling clock with low jitter thus must be available.

Crystal oscillators (XOs) can provide very accurate and stable clocks due to the high quality factor (in the range of  $10^4$  to  $10^6$ ) of the quartz crystal. However, the frequency of a practical crystal is often limited to tens-of-MHz [7]. For frequencies as needed on chip, which are typically in the GHz-range, no crystal is available. The frequency of the XO thus should be multiplied up before it can be used. The most common way of realizing frequency multiplication is using a phase-locked loop (PLL). A delay-locked loop (DLL) with an edge combiner can also be used as a frequency multiplier. However, its jitter performance for a given power budget is worse than for a PLL [8], especially when an LC oscillator is used in the PLL. This thesis focuses on the design of frequency multiplication PLLs for applications that require high speed clocks with very low jitter such as high performance ADCs.

Figure 1.2. Achievable ADC SNR with certain signal frequency and sampling clock jitter.

#### **1.2 A Brief PLL Review**

A PLL is a feedback system in which the feedback signal is used to lock the frequency and phase of the output signal to the frequency and phase of an input signal. The earliest concept of a PLL was provided by de Bellescize in 1932 [9]. However, the PLL did not fall into widespread use until the IC technology had advanced enough. The first integrated PLL debuted in ISSCC in 1969 [10] and one of the earliest use of a feedback divider in a PLL for frequency multiplication appeared in 1970 [11]. Since then the PLL has become a ubiquitous component in modern ICs due to its versatility. Apart from frequency multiplication and clock generation, PLLs can for instance also be used for frequency synthesis, frequency modulation and demodulation, clock and data recovery, synchronization, skew compensation and spread spectrum signal generation.

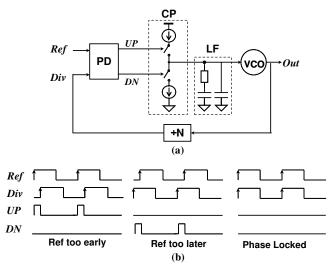

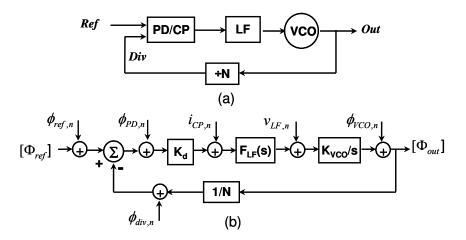

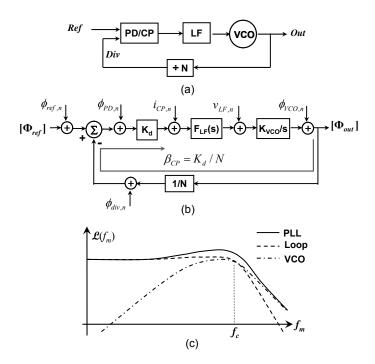

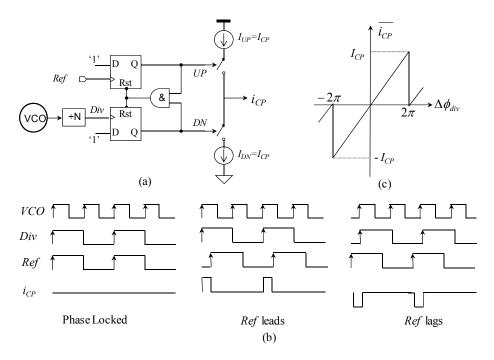

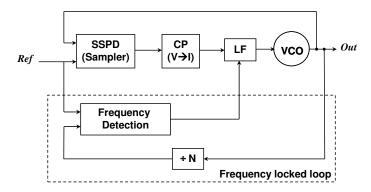

To the present time, many different PLL architectures [12-15] have been developed. The one shown in Fig. 1.3(a) is probably the most popular architecture. It consists of an input reference clock Ref, a phase detector (PD) or phase-frequency-detector, a charge pump (CP), a loop filter (LF), a voltage controlled oscillator (VCO) which creates an output frequency and a frequency divider with division ratio N ( $\div$ N). The basic operation of the PLL is as follows. The PD compares its two input signals and generates two signals UP and DN with the pulse width proportional to the amount of phase difference at the input, see Fig. 1.3(b). The CP consists of two current sources switched by UP and DN, driving a low pass filter. The filter output is used to drive the VCO and adjusts its oscillation frequency. The frequency divider reduces the VCO frequency by N times and feeds it back to the input of the PD, producing a negative feedback loop. When the loop reaches steady state, the reference clock and the divider output have the same phase and phase locking is achieved.

Figure 1.3. Classical charge pump PLL (a) schematic; (b) timing diagram.

The reference clock and the divider output then also have the same frequency since frequency is the first derivative of phase. In other words, the VCO frequency is equal to N times the reference frequency and frequency multiplication is achieved. Although the implementation of individual blocks may be different, most of the modern PLLs [16-25] have the same architecture as the one in Fig. 1.3(a). Therefore, we will refer to it as the "classical PLL" architecture.

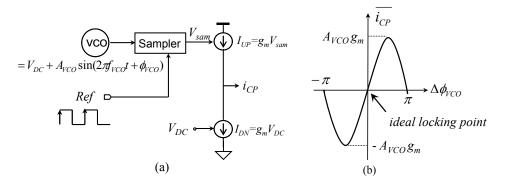

In addition to the PD described in Fig. 1.3, other types of PD like a mixer and sampleand-hold also exist. For example, the sampling or sample-and-hold PD [12] uses one input to sample another input similar to the case in Fig. 1.1. The sampled voltage value represents the phase difference between the two input signals. It will be described in more detail in Chapter 4 and we will see that a sub-sampling PD derived from the sample-and-hold PD can bring significant phase noise benefits.

The PD (and the succeeding CP, LF) can also be implemented digitally, resulting in a digital PLL. Digital PLLs [26-28] are recently becoming popular because they benefit from the shrinking transistor size and have better programmability and portability over different processes. Since oscillators are inherently analog and the phase information is continuous, a time-to-digital converter (TDC) and a digitally controlled oscillator (DCO) are often used to interface the analog and digital world. Both the limited resolution of the TDC and the DCO contribute to quantization noise or limit cycle within the loop, which results in either phase noise or spurs at the PLL output. The resolution of the TDC and DCO improves with the advance of technology. However, the jitter performance of the digital PLL is still fundamentally limited by the inherent noise of the analog components in the TDC and DCO.

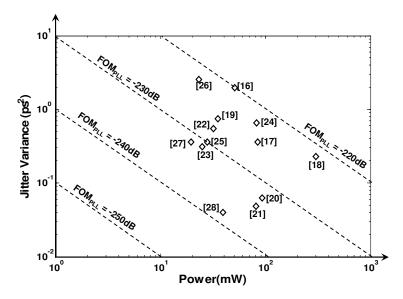

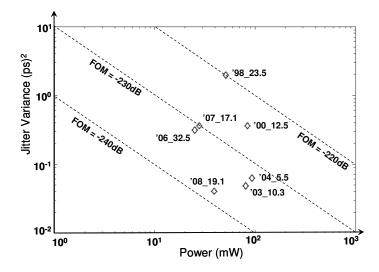

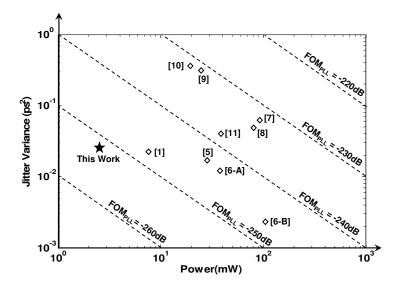

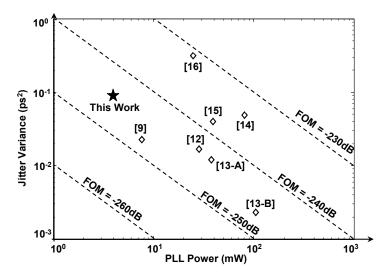

Figure 1.4. Jitter and power performance of state-of-art classical PLLs in literature.

For clock generation PLLs, two of the most important parameters are jitter  $\sigma_t$  and power *P*. As we will see from Chapter 2, the PLL performance can be characterized using a figure-of-merit (FOM) defined as:

$$FOM_{PLL} = 10\log[(\frac{\sigma_t}{ls})^2 \cdot \frac{P}{lmW}].$$

(1.3)

A smaller  $FOM_{PLL}$  corresponds to a better PLL design. Fig. 1.4 plots the performance of state-of-the-art classical PLLs in literature [16-28]. We see that they typically output more than 0.2 ps rms jitter while consuming tens-of-mW, which may not be good enough in applications that require very low jitter as well as low power consumption.

#### **1.3 Research Objectives**

The main objective of this PhD work is to explore the performance limits of existing PLLs and provide solutions to overcome these limits. We focus on the area of clock multiplication for applications that require high speed clocks with very low jitter such as high performance data links and ADCs, making the integer-*N* structure a great candidate due to its simplicity.

Apart from low jitter, a clock generator is also desired to dissipate low power. This is especially important in portable applications, such as cellular phones where lower power consumption leads to longer talk time and a longer battery life. Power dissipated by the PLL may be a small fraction of the total active power in the system. However, during sleep modes where the PLL must remain in lock, it can be a significant fraction of dissipated power. The low power requirement makes the design of low jitter PLL even more challenging due to the fundamental trade-off between power and noise.

In order to design a low jitter PLL, a deep understanding of the PLL noise mechanisms is needed. One of the first goals of this thesis is thus to study the phase noise and jitter of the classical PLL. We will analyze different PLL noise sources and their relative impacts. A relation between jitter, phase noise, power consumption and loop bandwidth will be derived and jitter optimization methods will be described. Based on the insights developed, a benchmark FOM relating jitter and power will be defined, which stimulates the design of power efficient PLLs.

In some applications e.g. time-interleaved ADCs [29], clocks with more than one phase are needed. Therefore, we will study two common multi-phase clock generation methods, one using a delay-locked loop (DLL) and the other a shift register (SR). The jitter and power performance of the two methods will be analyzed and their relative merits will be compared.

The ultimate goal of our research is to develop a fully integrated PLL with low jitter (on the order of 100 fs) with low power consumption (on the order of 10 mW). The title of the thesis refers to this goal. The term "sub-sampling phase detection" refers to the phase detection technique we used in this work. In the end we will demonstrate several PLL designs which meet the target and have >10 times less power dissipation than the PLLs in Fig. 1.5 when normalized to the same amount of output jitter.

From the implementation aspects, we will focus on the complementary metal-oxidesemiconductor (CMOS) technology. In CMOS technology, both the digital and analog parts of a complete system can be integrated on the same die, leading to smaller size and cost but also reduced power dissipation for instance by eliminating power consuming chip-to-chip interfacing.

#### **1.4 Thesis Organization**

The rest of the thesis is organized as follows.

Chapter 2 describes the classical PLL architecture and analyzes its phase noise performance using the small signal phase domain model. Different sources of PLL phase noise and power consumption are identified and analyzed. The overall PLL output jitter is calculated and jitter optimization methods are discussed. The scaling of the PLL jitter and power with the input frequency, output frequency and the division ratio *N* are examined. Based on the insights developed, a benchmark figure-of-merit to evaluate PLL jitter performance in relation to the consumed power is proposed [30].

Chapter 3 deals with low jitter multi-phase clock generation. Such clocks are for instance needed for time-interleaved ADCs and for image and harmonic rejection radio transceivers exploiting multiple clock phases. Two competing techniques to realize such clocks, one based on a shift register (SR) and the other on a DLL, are discussed [31], [32]. The relative merits of the two techniques are compared, primarily based on their jitter generation and power consumption. Analysis shows that a SR is not only more flexible, but also almost always generates less jitter than a DLL for a given power, assuming both are realized with current mode logic circuits. The analytical results are verified with simulation results. To generate high frequency multi-phase clocks, both methods need a low jitter high frequency reference clock, which can be generated from a crystal oscillator using a clock multiplying PLL. A PLL design with very low jitter is discussed in Chapter 4.

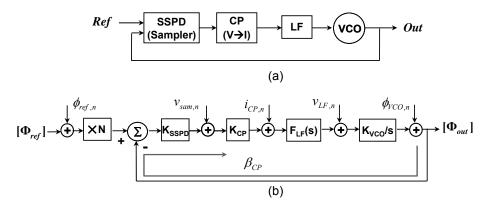

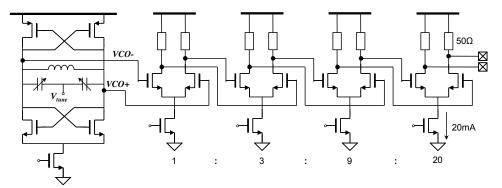

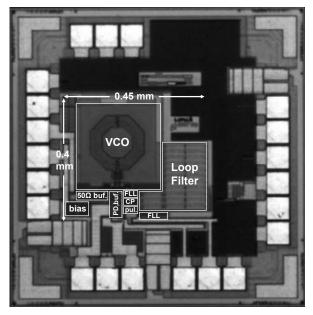

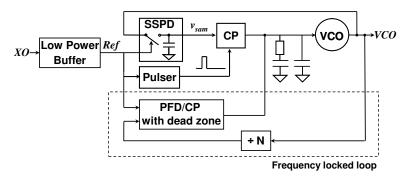

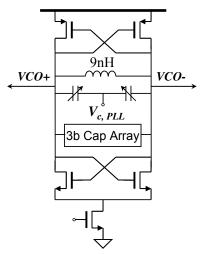

One important conclusion from Chapter 2 is that the PD, CP and divider noise is multiplied by  $N^2$  in a classical PLL due to the divide-by-N in the feedback path. This is often the bottleneck for a classical PLL to achieve low phase noise. Chapter 4 proposes a new sub-sampling based PLL architecture which can break this bottleneck [33], [34]. It uses a PD that sub-samples the VCO output with the reference clock. No divider is needed in the locked state and hence divider noise and power can be eliminated. Moreover, analyses shows that the PD and CP noise is not multiplied by  $N^2$  in this sub-sampling PLL (SSPLL), resulting in a low noise contribution from the PD and CP. To prove the concept, a 2.2 GHz SSPLL with a frequency division ratio of 40 is implemented in a standard 0.18- $\mu$ m CMOS process. The in-band phase noise at 200 kHz offset is measured to be -126 dBc/Hz. The reference spur is -46 dBc. The SSPLL has an rms output jitter of 0.15 ps (integrated over 10 kHz to 40 MHz) while consuming 5.8 mW on the loop-components and 1.8 mW on the VCO. When normalized to the same output jitter, this SSPLL is an order of magnitude more power efficient than the state-of-art classical PLLs.

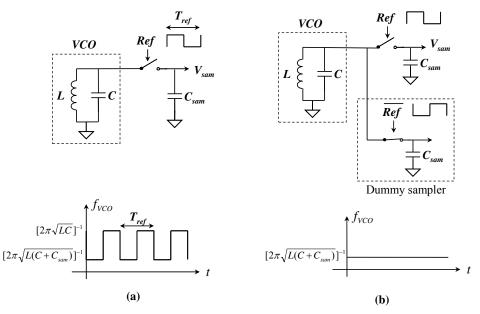

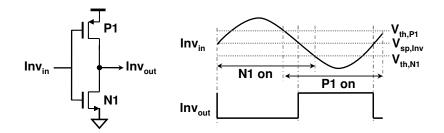

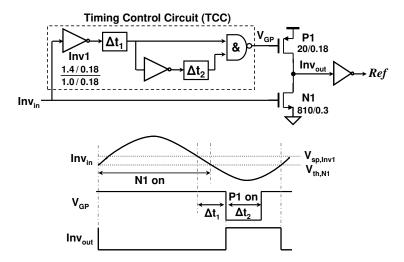

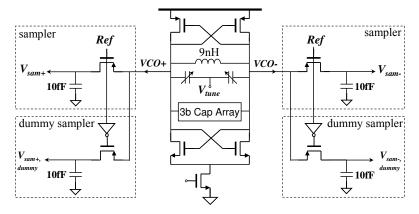

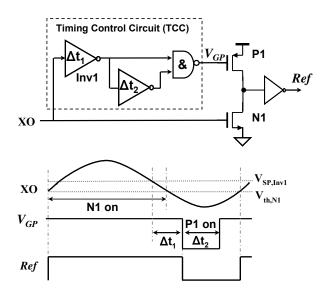

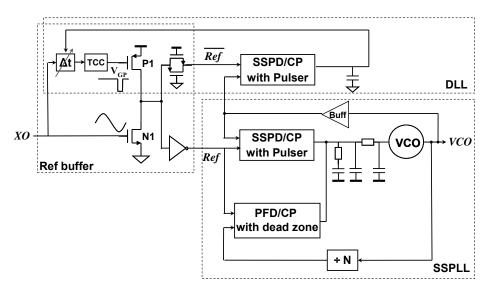

Chapter 5 elaborates design techniques that can boost the power efficiency of the SSPLL even further [35]. We aim to reduce the loop-components power of the SSPLL in Chapter 4 by an order of magnitude while keeping its superior in-band phase noise performance. To this end, a buffer-less direct VCO sampling scheme is proposed which eliminates the power hungry VCO buffer. Dummy samplers are added to keep the disturbance of the SSPD sampling to the VCO low. A modified inverter with separate gate control for the NMOS and PMOS transistors are used as a power efficient reference clock buffer. By making the conduction time for the NMOS and PMOS non-overlapping, direct current path from the supply to ground is eliminated, thereby eliminating the inverter short-circuit current. Measurements show that a 2.2 GHz SSPLL designed with these techniques can achieve - 125 dBc/Hz in-band phase noise at 200 kHz with only 700  $\mu$ W loop-components power. The whole SSPLL consumes 2.5 mW while the rms jitter is 0.16 ps (10 kHz to 100 MHz). The reference spurs measured from 20 samples are lower than -56 dBc.

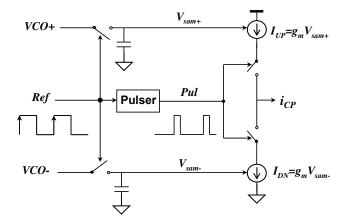

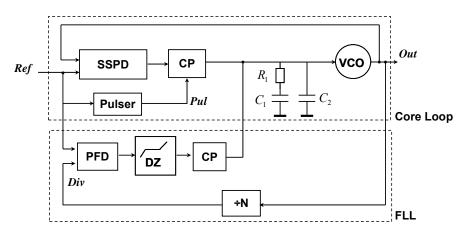

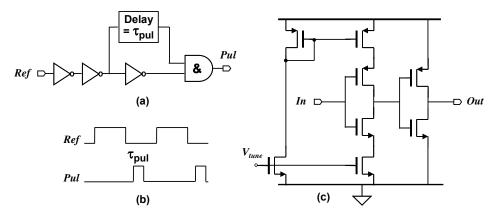

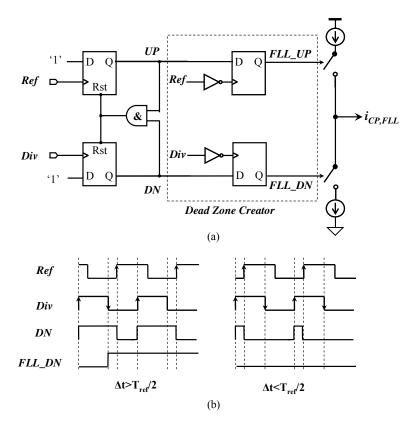

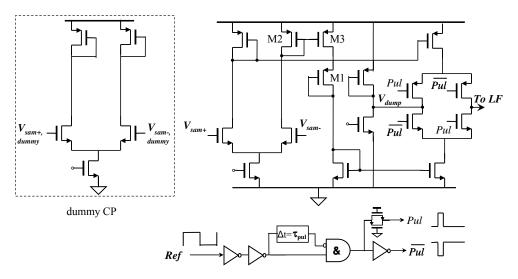

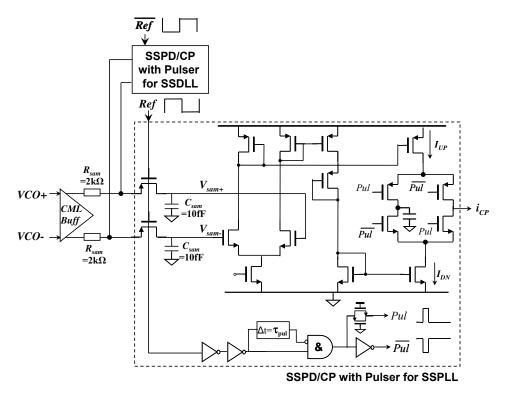

Although the SSPLLs in Chapter 4 and 5 achieve very low phase-noise/jitter with low power, the measured reference spurs are relatively high. Chapter 6 analyzes the SSPLL spur mechanisms and proposes design techniques to drastically reduce the spur level [37], [38]. It is discovered that the amplitude-controlled CP in the SSPLL is actually insensitive to mismatch and generates low ripple. The main source of the SSPLL spur is the SSPD sampler which periodically disturbs the VCO operation via charge injection, charge sharing and frequency modulation by periodically changing the VCO capacitive load. A DLL/PLL dual loop architecture and a duty-cycle controlled reference buffer is then proposed which suppresses all the SSPD spur mechanisms. To verify the spur reduction concepts, a new SSPLL design is fabricated in 0.18-µm CMOS. The prototype generates 0.3 ps (10 kHz to 100 MHz) rms jitter while consuming 3.8 mW. The reference spurs measured from 20 randomly selected chips are <-80 dBc.

Finally, Chapter 7 summarizes the most important conclusions that were drawn in this thesis, gives an overview of the original contributions and recommends some future work directions.

#### **1.5 References**

- [1] J. S. Kilby, "Miniaturized electronic circuits," U.S. patent 3138743, filed Feb. 6, 1959.

- [2] R. N. Noyce, "Semiconductor device-and-lead structure," U.S. patent 2981877, filed July 30, 1959.

- [3] G. E. Moore, "Cramming more components onto integrated circuits", *Electronics*, vol. 38, no. 8, pp. 114-117, Apr. 1965.

- [4] S. Rusu, S. Tam, H. Muljono, J. Stinson, D. Ayers, J. Chang, R. Varada, M. Ratta and S. Kottapalli, "A 45nm 8-Core Enterprise Xeon® Processor", *IEEE Int. Solid-State Circuits Conf. (ISSCC)*, pp. 56-57, Feb. 2009.

- [5] D. C. Lee, "Analysis of jitter in phase-locked loops," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 704–711, Nov.2002.

- [6] National Semiconductor, Clock Conditioner Owner's Manual, 2006. Accessed on Mar. 20<sup>th</sup>, 2010 http://www.national.com/appinfo/interface/files/clk\_conditioner\_owners\_manual.pdf

- [7] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*. New York, NY: Cambridge University Press, 1998.

- [8] R. C. H. van de Beek, E. Klumperink, C. S. Vaucher and B. Nauta, "Low-jitter clock multiplication: a comparison between PLLs and DLLs," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 555-566, Aug. 2002.

- [9] H. de Bellescize, "La Reception Synchrone," Onde Electr, Vol. 11, pp. 230-240, Jun. 1932.

- [10] A. B. Grebene and H. R. Camenzind, "Phase Locking as a New Approach for Tuned Integrated Circuits," *IEEE Int. Solid-State Circuits Conf. (ISSCC)*, vol. XII, pp. 100-101, Feb. 1969.

- [11] R. B. Sepe and R. I. Johnston, "Frequency multiplier and frequency waveform generator," U.S. patent 3551826, Dec. 1970.

- [12] V. F. Kroupa, Frequency Synthesis: Theory, Design and Applications. London, U.K.: Griffin, 1973.

- [13] J. A. Crawford, Frequency Synthesizer Design Handbook. Boston, MA: Artech House, 1994.

- [14] W. F. Egan, *Frequency Synthesis By Phase Lock.* 2nd ed., New York: Wiley Interscience, 2000.

- [15] C. S. Vaucher, Architectures for RF Frequency Synthesizers. Boston, MA: Kluwer, 2002.

- [16] J. Craninckx and M. Steyaert, "A Fully Integrated CMOS DCS-1800 Frequency Synthesizer," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 372-373, Feb.1998.

- [17] L. Lin and P. R. Gray, "A 1.4 GHz differential low-noise CMOS frequency synthesizer using a wideband PLL architecture," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp. 204–205, Feb. 2000.

- [18] H. Cong, S. M. Logan, M. J. Loinaz, K. J. O'Brien, E. E. Perry, G. D. Polhemus, J. E. Scoggins, K. P. Snowdon and M. G. Ward, "A 10-Gb/s 16:1 multiplexer and 10-GHz clock synthesizer in 0.25-um SiGe BiCMOS," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1946–1953, Sep. 2001.

- [19] N. Da Dalt and C. Sandner, "A subpicosecond jitter PLL for clock generation in 0.12 µm digital CMOS," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1275–1278, Jul. 2003.

- [20] A. M. Terrovitis, M. Mack, K. Singh and M. Zargari, "A 3.2 to 4 GHz, 0.25 um CMOS frequency synthesizer for IEEE 802.11a/b/g WLAN," *IEEE ISSCC Dig. Tech. Papers*, pp. 98–99, Feb. 2004.

- [21] R. C. H. van de Beek, C. S. Vaucher, D. M. W. Leenaerts, E. A. M. Klumperink and B. Nauta, "A 2.5–10-GHz clock multiplier unit with 0.22-ps RMS jitter in standard 0.18µm CMOS," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1862–1872, Nov. 2004.

- [22] R. Nonis, N. Da Dalt, P. Palestri and L. Selmi, "Modeling, design and characterization of a new low-jitter analog dual tuning LC-VCO PLL architecture," *IEEE J. Solid-State Circuits*, vol. 40, pp. 1303-1309, Jun. 2005.

- [23] R. Gu, A. Yee, Y. Xie and W. Lee, "A 6.25GHz 1V LC-PLL in 0.13µm CMOS," IEEE Int. Solid-State Circuits Conf. (ISSCC), pp. 594-595, Feb. 2006.

- [24] A. L. S. Loke, R. K. Barnes, T. T. Wee, M. M. Oshima, C. E. Moore, R. R. Kennedy and M. J. Gilsdorf, "A versatile 90-nm CMOS charge-pump PLL for SerDes transmitter clocking," *IEEE J. Solid-State Circuits*, vol. 41, pp. 1894-1907, Aug. 2006.

- [25] A. Swaminathan, K. J. Wang and I. Galton, "A Wide-Bandwidth 2.4 GHz ISM Band Fractional-N PLL With Adaptive Phase Noise Cancellation," *IEEE J. Solid-State Circuits*, vol. 42, pp. 2639-2650, Dec. 2007.

- [26] R. B. Staszewski, J. L. Wallberg, S. Rezeq, C.-M. Hung, O. E. Eliezer, S. Vemulapalli, K.C. Fernando, K. Maggio, R. Staszewski, N. Barton, M.-C. Lee, P. Cruise, M. Entezari, K. Muhammad and D. Leipold, "All-digital PLL and transmitter for mobile phone," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005.

- [27] N. Da Dalt, E. Thaller, P. Gregorius and L. Gazsi, "A Compact Triple-Band Low-Jitter Digital LC PLL With Programmable Coil in 130-nm CMOS," *IEEE J. Solid-State Circuits*, Vol. 40, No. 7, pp.1482-1490, Jul. 2005.

- [28] C. Hsu, M. Z. Straayer and M. H. Perrott, "A Low-Noise, Wide-BW 3.6GHz Digital ∆∑ Fractional-N Frequency Synthesizer with a Noise- Shaping Time-to-Digital Converter and Quantization Noise Cancellation," *IEEE Int. Solid-State Circuits Conf.* (ISSCC), pp. 340-341, Feb. 2008.

- [29] W. C. Black and D. A. Hodges, "Time interleaved converter arrays," *IEEE J. Solid-State Circuits*, vol.15, no. 6, pp. 1022–1029, Dec. 1980.

- [30] X. Gao, E. Klumperink, P. J. F. Geraedts and B. Nauta, "Jitter Analysis and a Benchmarking Figure-of-Merit for Phase-Locked Loops," *IEEE Trans. Circuits Syst. II*, vol. 56, no.2, pp. 117-121, Feb. 2009.

- [31] X. Gao, E. Klumperink, and B. Nauta, "Low-Jitter Multi-phase Clock Generation: A Comparison between DLLs and Shift Registers," *IEEE Int. Symp. Circuits Syst.* (ISCAS), pp. 2854–2857, May 2007.

- [32] X. Gao, E. Klumperink and B. Nauta, "Advantages of Shift Registers Over DLLs for Flexible Low Jitter Multiphase Clock Generation," *IEEE Trans. Circuits Syst. II*, vol. 55, no.3, pp. 244-248, Mar. 2008.

- [33] X. Gao, E. Klumperink, M. Bohsali and B. Nauta, "A 2.2GHz 7.6-mW Sub-Sampling PLL with -126dBc/Hz In-band Phase Noise and 0.15ps<sub>rms</sub> Jitter in 0.18-μm CMOS," *IEEE Int. Solid-State Circuits Conf. (ISSCC)*, pp. 392-393, Feb. 2009.

- [34] X. Gao, E. Klumperink, M. Bohsali and B. Nauta, "A Low Noise Sub-Sampling PLL in Which Divider Noise is Eliminated and PD/CP Noise is not Multiplied by N<sup>2</sup>," *IEEE J. Solid-State Circuits (JSSC)*, vol. 44, no.12, pp. 3253-3263, Dec. 2009.

- [35] X. Gao, E. Klumperink, G. Socci, M. Bohsali and B. Nauta, "A 2.2GHz Sub-Sampling PLL with 0.16ps<sub>rms</sub> Jitter and -125dBc/Hz In-band Phase Noise at 700μW Loop-Components Power," *IEEE Symposium on VLSI Circuits*, paper 14.1, Jun. 2010.

- [36] X. Gao, E. Klumperink, G. Socci, M. Bohsali and B. Nauta, "Spur Reduction Techniques for Phase-Locked Loops Using Sub-Sampling Phase Detection," *IEEE Int. Solid-State Circuits Conf. (ISSCC)*, pp. 474-475, Feb. 2010.

- [37] X. Gao, E. Klumperink, G. Socci, M. Bohsali and B. Nauta, "Spur Reduction Techniques for Phase-Locked Loops Exploiting a Sub-Sampling Phase Detector," accepted to *IEEE J. Solid-State Circuits (JSSC)*.

## Chapter 2

## **Classical PLL Jitter Analysis**

#### **2.1 Introduction**

In the previous chapter, we explained that the goal of this thesis is to design a low jitter phase-locked loop (PLL) with low power. In order to reach this goal, a deep understanding of the PLL noise mechanisms is needed. Of the many known PLL architectures [1-4], the one shown in Fig. 2.1(a) is perhaps the most widely-used one which we call the "classical PLL" architecture. It consists of a voltage controlled oscillator (VCO) which is locked to a reference clock by a feedback loop with the following "loop components": a phase detector (PD) combined with a charge pump (CP), a loop filter (LF) and a frequency divider with division ratio N ( $\div$ N). In this chapter, we will study the classical PLL architecture and analyze its phase noise and jitter performance.

The PLL jitter has been the topic of numerous studies [5-8]. Different from previous work, we focus on finding a systematic relation between the PLL jitter and key design parameters like the reference frequency, output frequency, loop bandwidth and power consumption. As we will see from the analytical results, changing these parameters largely affects the timing error in a systematic way. It thus makes sense to define a benchmark figure-of-merit (FOM) that normalizes for this systematic dependency. A well defined FOM makes it possible to compare different PLL designs and get an indication of their relative merits, in a similar way as for ADCs [9] or VCOs [10], [11], and can stimulate the development of power efficient high performance PLLs.

Following this introduction, Section 2.2 describes the classical PLL phase domain model and the noise transfer functions for different building blocks. Section 2.3 estimates the noise contribution and power consumption of the VCO and Section 2.4 does this for the loop components. Section 2.5 discusses the PLL output jitter and how it can be optimized. Based on the insights developed, a benchmark FOM to evaluate PLL jitter performance in relation to consumed power is proposed. Section 2.6 draws conclusions.

Figure 2.1. Classical PLL (a) architecture; (b) phase domain model.

#### 2.2 Classical PLL Phase Domain Model

The transient response of a PLL is generally a nonlinear process that cannot be formulated easily. Nevertheless, once phase locking is achieved, a linear approximation can be used to gain intuition. A linear phase-domain model for the classical PLL is shown in Fig. 2.1(b) [4], where  $K_d$  is the PD/CP detection gain,  $F_{LF}(s)$  the loop filter trans-impedance transfer function and  $K_{VCO}$  the VCO tuning gain in rad/V. Various noise sources are also shown. The noise transfer function from the VCO to the PLL output can be calculated as

$$H_{VCO}(s) = \frac{1}{1 + \frac{1}{N} \cdot K_d \cdot F_{LF}(s) \cdot \frac{K_{VCO}}{s}} = \frac{1}{1 + G(s)}$$

(2.1)

where G(s) is the PLL open loop transfer function and  $s=j2\pi f$ .

The rest of the noise all originates from the loop components and is therefore called the loop phase noise. When referred to the divider input<sup>1</sup>, the loop phase noise can be calculated as

$$\mathcal{L}_{loop} \approx \frac{S_{\phi loop,n}}{2} = \frac{1}{2} \cdot N^2 \cdot (S_{\phi ref,n} + S_{\phi div,n} + S_{\phi PD,n} + \frac{S_{iCP,n}}{K_d^2})$$

(2.2)

where the phase noise is expressed with the often used single-side-band noise power to

<sup>&</sup>lt;sup>1</sup> Here the loop phase noise is referred to the divider input (not to the PD input!), so that its level can be directly measured at the PLL output.

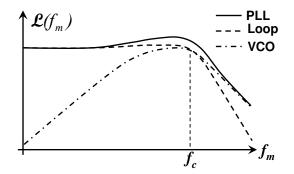

Figure 2.2. Overall PLL output phase noise originating from the loop-components and VCO, with 1/f noise neglected.

carrier power ratio  $\mathcal{L}$ , which is approximately half of the phase noise power spectral density under practical conditions [12]. In (2.2), we neglected the loop filter noise since it should be made negligible in a well designed low noise PLL. This can be done without adding power, by either properly sizing the filter components [13] or lowering  $K_{VCO}$  by design [14]. The reference clock is commonly generated by crystal oscillators whose phase noise is usually also negligible. The reference phase noise  $S_{\phi ref,n}$  is mainly contributed by reference dividers or reference clock buffers.

The noise transfer function from the (divider input referred) loop phase noise to the PLL output can be easily calculated as

$$H_{loop}(s) = \frac{G(s)}{1 + G(s)} = 1 - H_{VCO}(s) \cdot$$

(2.3)

Comparing (2.1) and (2.3), the VCO phase noise is high pass filtered while the loop phase noise is low pass filtered. Moreover, the 3-dB bandwidth for the two transfer functions is the same and determined by G(s). We define their 3-dB bandwidth as the PLL bandwidth  $f_c$ .

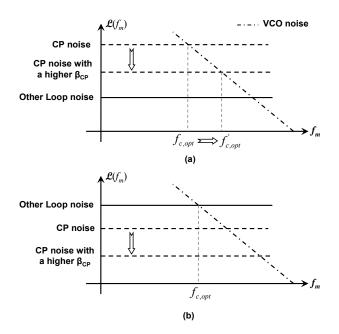

In the following noise analysis, we assume the PLL is implemented with CMOS which is the technology of interest in this thesis. We will focus on the fundamental limitation due to thermal noise and neglect 1/f noise, with similar arguments as in [6] and [7]. In most PLL designs, 1/f noise doesn't contribute much to the output jitter. The VCO 1/f noise is suppressed by the PLL loop since the 1/f corner frequency is normally lower than  $f_c$ . The contribution of the 1/f noise in the loop components is also not significant when the 1/f corner frequency is small compared with the PLL bandwidth<sup>2</sup>. With the 1/f noise neglected, the spectrum of the loop phase noise is flat. The VCO phase noise has a  $1/f^2$  shape due to the integration of white noise. Fig. 2.2 shows the overall PLL output phase noise when a first order low pass loop filter is used. Outside the loop bandwidth (offset frequency  $f_m > f_c$ ) the  $1/f^2$  shape of the VCO noise is visible, as VCO phase noise is hardly affected there by the loop filter. Within the loop bandwidth, for  $f_m < f_c$ , the filtering suppresses the VCO noise and the loop noise dominates. As this happens inside the loop bandwidth, the loop phase noise is sometimes also referred to as PLL in-band phase noise.

#### 2.3 VCO Phase Noise and Benchmarking

The VCO phase noise has been the topic of several studies, e.g. [11], [15-17]. It is found that the phase noise of a VCO in some respects is systematically dependent on design parameters like the oscillation frequency  $f_{VCO}$ , power dissipation  $P_{VCO}$  and the offset frequency  $f_m$  at which the phase noise is measured. To compare the quality of VCO designs, the following benchmark FOM [10], [11] is widely used:

$$FOM_{VCO} = 10\log(\mathcal{L}_{VCO}(f_m) \cdot \frac{f_m^2}{f_{VCO}^2} \cdot \frac{P_{VCO}}{\mathrm{ImW}}) \cdot$$

(2.4)

The unit of  $FOM_{VCO}$  is dBc/Hz ( $\mathcal{L} \cdot$  dimensionless factor). A smaller  $FOM_{VCO}$ , i.e. a more negative number, corresponds to a better VCO design<sup>3</sup>. The VCO phase noise can thus be expressed using  $FOM_{VCO}$  as

$$\mathcal{L}_{VCO}(f_m) = \frac{10^{FOM_{VCO}/10}}{P_{VCO}/1\text{mW}} \cdot \frac{f_{VCO}^2}{f_m^2} \,.$$

(2.5)

#### 2.4 Loop Phase Noise and Benchmarking

In [18], Banerjee found that the classical PLL (in-band) loop phase noise is related to N and the phase detector frequency  $f_{PD}$  as

$$\mathcal{L}_{loop} \propto N^2 \cdot f_{PD} \,. \tag{2.6}$$

To eliminate this dependence, he proposed a normalized phase noise floor  $PN_{IHz}$  to benchmark the quality of a loop design, defined as

<sup>&</sup>lt;sup>2</sup> For example, if the 1/f corner frequency is 100kHz and loop bandwidth is 1MHz, and jitter is integrated over a wide region of [1kHz, 100MHz], calculation shows that 1/f noise contributes only about 10% of the total jitter.

<sup>&</sup>lt;sup>3</sup> Sometimes the negative of (2.4), i.e., a  $FOM_{VCO}$  with plus sign is used [11], but this leads to very strange units for  $FOM_{VCO}$ .

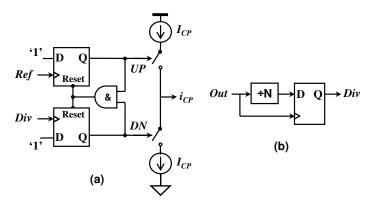

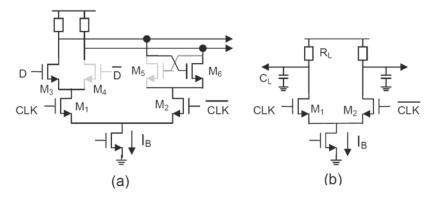

Figure 2.3. Schematic of (a) 3-state PFD/CP; (b) divider with synchronization.

$$PN_{1Hz} = \frac{\mathcal{L}_{loop}}{N^2 \cdot f_{PD}} \cdot$$

(2.7)

The Banerjee model was applied to a wide range of PLL IC's in industry and was supported by measurement results [18]. However, the theoretical basis for (2.6) is not clear in [18]. Moreover, (2.6) does not take into account the power consumption while phase noise performance is known to be strongly related to power consumption. The analysis below addresses these issues.

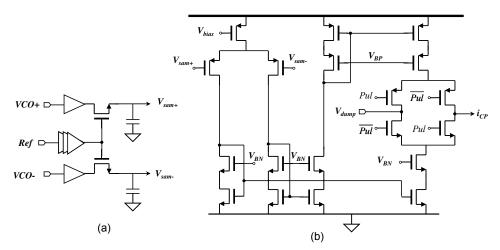

To analyze the loop phase noise, we assume the popular 3-state phase-frequency-detector (PFD) and CP combination as shown in Fig. 2.3(a) is used. For the divider design, synchronization is often used in low noise designs [19], as shown in Fig. 2.3(b). The only noise source of the divider is then the retiming D flip-flop (DFF). The divide-by-N block only acts as an edge selector and does *not* contribute to noise. Its power consumption can thus be progressively scaled down [19]. As we aim to model the power needed to meet a certain phase-noise/jitter requirement, we will ignore the divide-by-N block hereafter and only model the power of the retiming DFF<sup>4</sup> in the divider.

#### 2.4.1 Phase Noise due to the Reference Path, Divider and PD

Among the loop noise sources,  $S_{\phi ref,n}$ ,  $S_{\phi div,n}$  and  $S_{\phi PD,n}$ , are caused by circuits like the reference buffer, divider retiming DFF and the 3-state PFD, which all (effectively) run at frequency  $f_{PD}$ . These circuits all respond to zero-crossings at their inputs by producing zero-crossings at their outputs. This time discrete behavior causes sampling of the phase of the output signal at the operation frequency  $f_{PD}$ . The sampling process folds back any noise

<sup>&</sup>lt;sup>4</sup> There can be occasions where the power of the divide-by-*N* block becomes significant, e.g. in order to make it fast enough to cover very high VCO frequencies. However, this is not because of jitter or noise requirements.

component at frequency higher than  $f_{PD}/2$  and the phase noise spectrum is thus defined in the Nyquist band between 0 and  $f_{PD}/2$ . With the white noise assumption, the output phase noise of the circuit is then related to the absolute output jitter  $\sigma_t$  as [19]

$$S_{\phi,n} = 8\pi^2 \cdot f_{PD} \cdot \sigma_t^2. \tag{2.8}$$

The output jitter of circuits like DFFs or inverters is related to the output noise voltage  $\overline{v_n^2}$  and the slew rate  $SR_{out}$  of the output voltage at its zero crossing as [19], [20]

$$\sigma_t^2 = \frac{\overline{v_n^2}}{SR_{out}^2} = \frac{F_n \cdot kT / C_{out}}{SR_{out}^2}$$

(2.9)

where  $F_n$  is the noise factor and  $C_{out}$  is the capacitance at the output node.

Assuming the minimum power needed is the dynamic power, the circuit power consumption P can be calculated as

$$P \approx P_{dynamic} = f_{PD} \cdot C_{tot} \cdot V_{dd}^2 \tag{2.10}$$

where  $C_{tot}$  is the total capacitance of the circuit.

Combining (2.9) and (2.10), we get

$$\sigma_t^2 = \frac{f_{PD}}{P} \cdot \left\{ \frac{F_n \cdot kT \cdot V_{dd}^2 \cdot C_{tot} / C_{out}}{SR_{out}^2} \right\} \cdot$$

(2.11)

In order to minimize the output jitter, designers can optimize the circuit by choosing the relative sizes of components e.g. to maximize  $SR_{out}$ . Once this optimization has been done, jitter can always be reduced on system level via admittance level scaling [21]. Admittance level scaling puts *n* identical circuits in parallel. As a result, power consumption is *n* times higher and  $\overline{v_n^2}$  is *n* times lower while the voltage slope at every node does not change [21]. Thus  $C_{tot}/C_{out}$ ,  $F_n$  as well as  $SR_{out}$  remains the same as all nodes' admittances scale together. Therefore, on the system level, we can treat the bracketed part in (2.11) as a design dependent constant<sup>5</sup> and we get

$$\sigma_t^2 \propto f_{PD} / P \,. \tag{2.12}$$

For loop noise  $S_{\phi ref,n}$ ,  $S_{\phi div,n}$  and  $S_{\phi PD,n}$ , we can conclude with (2.8) and (2.12) that

$$S_{\phi ref,n} \propto f_{PD}^2 / P_{ref}; \qquad (2.13)$$

<sup>&</sup>lt;sup>5</sup> It is assumed (like in [19], [20]) that  $SR_{out}$  is independent of input rise time and frequency (e.g. the inputs are high-slope signals or square-waves).

$$S_{\phi div,n} \propto f_{PD}^2 / P_{div}; \qquad (2.14)$$

$$S_{\phi PD,n} \propto f_{PD}^2 / P_{PD}.$$

(2.15)

where  $P_{ref}$ ,  $P_{div}$  and  $P_{PD}$ , are respectively the power consumption of the reference buffer, divider and PD.

#### 2.4.2 Phase Noise due to the CP

Different from the circuits in section 2.4.1, the CP outputs current/charge instead of crossings moments. Assuming for simplicity that the CP up- and down-current sources have the same properties, the power spectral density of the (thermal) noise current generated by the CP is

$$S_{i,n} = 2 \times 4kT \gamma \cdot g_{m,CP} = 8kT \gamma \cdot (\alpha I_{CP} / V_{eff,CP})$$

(2.16)

where  $\gamma$  and  $V_{eff,CP}$  are respectively the noise factor and effective gate voltage of the transistors in the current sources,  $I_{CP}$  is the CP current,  $\alpha$  is the transistor model parameter which is equal to 2 for the square-law model, and  $\alpha I/V_{eff}$  represents the transconductance  $g_m$ .

In steady state, the CP is switched on only for a fraction of time  $\tau_{PD}$  of each period  $T_{PD}$  to avoid the dead zone. The equivalent CP (thermal) noise current can be calculated as [8]

$$S_{iCP,n} = S_{i,n} \cdot (\tau_{PD} / T_{PD}).$$

(2.17)

The minimum power needed by a CP is related to the charge delivered in steady state:

$$P_{CP} = I_{CP} V_{dd} \cdot (\tau_{PD} / T_{PD}) = I_{CP} V_{dd} \tau_{PD} \cdot f_{PD} .$$

(2.18)

For a 3-state PFD/CP, it is well known that  $K_d = I_{CP}/2\pi$ . With (2.16)-(2.18) and some manipulations, we get

$$\frac{S_{iCP,n}}{K_d^2} = \frac{f_{PD}^2}{P_{CP}} \cdot \{\tau_{PD}^2 \cdot \frac{32\pi^2 \alpha \gamma \cdot kT \cdot V_{dd}}{V_{eff,CP}}\} \propto \frac{f_{PD}^2}{P_{CP}}$$

(2.19)

where the bracketed part is treated as a design and process dependent constant.

#### 2.4.3 Loop Phase Noise Benchmarking

The overall power consumption of the PLL loop  $P_{loop}$  is the sum of  $P_{ref}$ ,  $P_{div}$ ,  $P_{PD}$  and  $P_{CP}$ . There should be an optimal way to distribute the total loop-components power  $P_{loop}$  into different blocks. Once the optimization has been done,  $P_{ref}$ ,  $P_{div}$ ,  $P_{PD}$  and  $P_{CP}$  remains a constant portion of  $P_{loop}$  when the admittance level scaling is applied to the whole loop.

With this assumption, we can derive from (2.13-2.15) and (2.19) that:

$$S_{\phi ref,n} \propto f_{PD}^2 / P_{loop}; \qquad (2.20)$$

$$S_{\phi div,n} \propto f_{PD}^2 / P_{loop}; \qquad (2.21)$$

$$S_{\phi PD,n} \propto f_{PD}^2 / P_{loop}; \qquad (2.22)$$

$$\frac{S_{iCP,n}}{K_d^2} \propto f_{PD}^2 / P_{loop}$$

(2.23)

Based on (2.2), and (2.20-2.23) we can conclude that

$$\mathcal{L}_{loop} \propto N^2 \cdot f_{PD} \cdot \frac{f_{PD}}{P_{loop}} = \frac{f_{out}^2}{P_{loop}} \cdot$$

(2.24)

Note that we assumed dynamic power consumption, i.e.  $P_{loop}$  scales with  $f_{PD}$ , so (2.24) shows the same proportionality as the Banerjee model in (2.6). In addition to (2.6), (2.24) also takes into account the power dissipation. For a given  $f_{out}$ , using a larger  $f_{PD}$  reduces the (in-band) loop phase noise but also increases the power consumption.

Based on (2.24), we propose to define a benchmark FOM for PLL loop designs as

$$FOM_{loop} = 10\log[\mathcal{L}_{loop} \cdot (\frac{1\text{Hz}}{f_{out}})^2 \cdot \frac{P_{loop}}{1\text{mW}}]$$

(2.25)

where  $f_{out}$  and  $P_{loop}$  are normalized to 1 Hz and 1 mW respectively so that the unit of  $FOM_{loop}$  is again dBc/Hz, the same as for  $FOM_{VCO}$ . The normalization to 1 mW is practical and similar to what is used for  $FOM_{VCO}$ , as the power consumption of circuits is typically expressed in mW, while signal power is RF circuits is often expressed in decibel milliwatts, again with 1 mW as reference [21]. A smaller  $FOM_{loop}$  (more negative values in dBc/Hz) again corresponds to a better loop design. The loop phase noise can now be expressed with  $FOM_{loop}$  as

$$\mathcal{L}_{loop} = 10^{FOM_{loop}/10} \cdot \left(\frac{f_{out}}{1\text{Hz}}\right)^2 \cdot \frac{1\text{mW}}{P_{loop}} \cdot$$

(2.26)

#### 2.5 PLL Jitter and Benchmarking

#### 2.5.1 PLL Output Jitter

Jitter can be characterized in several different ways [5]. This work chooses to use absolute jitter as it is often used in PLL design literature. The relation with other jitter

measures can be found in [5]. The variance of the long term PLL absolute jitter is related to the phase noise as

$$\sigma_{t,PLL}^{2} = \frac{2\int_{0}^{\infty} \boldsymbol{\mathcal{L}}_{PLL}(f_{m})df_{m}}{(2\pi f_{out})^{2}} = \frac{1}{2\pi^{2}f_{out}^{2}} \cdot \int_{0}^{\infty} \boldsymbol{\mathcal{L}}_{PLL}(f_{m})df_{m} \cdot$$

(2.27)

The PLL output jitter variance  $\sigma_{t,PLL}^2$  is the sum of the jitter variance caused by the VCO  $\sigma_{t,VCO}^2$  and the loop  $\sigma_{t,loop}^2$ . The jitter variance due to the VCO can be calculated as

$$\sigma_{t,VCO}^{2} = \frac{1}{2\pi^{2} f_{out}^{2}} \cdot \int_{0}^{\infty} \mathcal{L}_{VCO}(f_{m}) \cdot |H_{VCO}(j2\pi f_{m})|^{2} df_{m} \cdot$$

(2.28)

The value of (2.28) is dependent on the bandwidth and shape (related to phase margin) of  $H_{VCO}(s)$ . Assuming a given open loop transfer function  $G_0(s)$  which results in a close loop transfer function  $H_{VCO,0}(s)$  with a 3-dB bandwidth of  $f_{c,0}$ , scaling the bandwidth to  $f_c$  while keeping the same shape (thus the phase margin) results in a new transfer function [22]:

$$H_{VCO}(s) = H_{VCO,0}(s \cdot \frac{f_{c,0}}{f_c}) \cdot$$

(2.29)

Substituting (2.29) into (2.28) yields

$$\sigma_{t,VCO}^{2} = \frac{1}{2\pi^{2} f_{out}^{2}} \cdot \int_{0}^{\infty} \mathcal{L}_{VCO}(f_{m}) \cdot |H_{VCO,0}(j2\pi f_{m} \cdot \frac{f_{c,0}}{f_{c}})|^{2} df_{m} \cdot$$

(2.30)

Since the VCO phase noise has a  $1/f^2$  shape, it can also be expressed as

$$\mathcal{L}_{VCO}(f_m) = \frac{\mathcal{L}_{VCO}(f_r) \cdot f_r^2}{f_m^2}$$

(2.31)

where  $\mathcal{L}_{VCO}(f_r)$  is the VCO phase noise measured at a certain offset frequency  $f_r$ . We can then re-write (2.30) as

$$\sigma_{t,VCO}^{2} = \frac{\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}}{2\pi^{2} f_{out}^{2}} \cdot \int_{0}^{\infty} |H_{VCO,0}(j2\pi f_{m} \cdot \frac{f_{c,0}}{f_{c}})|^{2} \frac{df_{m}}{f_{m}^{2}}$$

$$= \frac{\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}}{2\pi^{2} f_{out}^{2}} \cdot \frac{f_{c,0}}{f_{c}} \cdot \int_{0}^{\infty} |H_{VCO,0}(j2\pi f)|^{2} \frac{df}{f^{2}} \cdot$$

(2.32)

Substituting (2.1) into (2.32) and using  $s=j2\pi f$  yields

$$\sigma_{t,VCO}^{2} = \frac{f_{c,0}}{f_{c}} \cdot \frac{2\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}}{f_{out}^{2}} \cdot \int_{0}^{\infty} |\frac{1}{s \cdot [1 + G_{0}(s)]}|^{2} df \cdot$$

(2.33)

Using similar analysis as for the VCO, the PLL output jitter variance due to the loop can

be calculated as

$$\sigma_{t,loop}^{2} = \frac{f_{c}}{f_{c,0}} \cdot \frac{\mathcal{L}_{loop}}{2\pi^{2} f_{out}^{2}} \cdot \int_{0}^{\infty} |\frac{G_{0}(s)}{1 + G_{0}(s)}|^{2} df$$

(2.34)

Therefore, the overall PLL output jitter can be calculated with (2.33) and (2.34) as

$$\sigma_{t,PLL}^{2} = \sigma_{t,VCO}^{2} + \sigma_{t,loop}^{2} = \frac{f_{c,0}}{f_{c}} \cdot \frac{2\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}}{f_{out}^{2}} \cdot \int_{0}^{\infty} \left|\frac{1}{s \cdot [1 + G_{0}(s)]}\right|^{2} df + \frac{f_{c}}{f_{c,0}} \cdot \frac{\mathcal{L}_{loop}}{2\pi^{2} f_{out}^{2}} \cdot \int_{0}^{\infty} \left|\frac{G_{0}(s)}{1 + G_{0}(s)}\right|^{2} df \cdot$$

(2.35)

#### 2.5.2 PLL Jitter Optimization

It is clear from (2.33) and (2.34) that a larger value of  $f_c$  will lower the output jitter due to the VCO while raising the jitter contribution of the loop. The optimum PLL bandwidth  $f_{c,opt}$  which gives the minimum PLL output jitter is calculated with (2.35) as

$$f_{c,opt} = \sqrt{\frac{\mathcal{L}_{VCO}(f_r) \cdot f_r^2}{\mathcal{L}_{loop}}} \cdot 2\pi \cdot \sqrt{f_{c,0}^2 \cdot \frac{\int_0^\infty |\frac{1}{s \cdot [1 + G_0(s)]}|^2 df}{\int_0^\infty |\frac{G_0(s)}{1 + G_0(s)}|^2 df}}$$

(2.36)

Substituting (2.36) into (2.31) yields:

$$\mathcal{L}_{VCO}(f_{c,opt}) = \mathcal{L}_{loop} \cdot \frac{1}{4\pi^2 \cdot f_{c,0}^2} \cdot \frac{\int_0^\infty |\frac{G_0(s)}{1+G_0(s)}|^2 df}{\int_0^\infty |\frac{1}{s \cdot [1+G_0(s)]}|^2 df}$$

(2.37)

In (2.37), the results of the integrations are related to the design of the loop filter and the phase margin of the loop transfer function. In a second-order type-II PLL with a simple RC filter, a large phase margin is preferred for less jitter peaking [7]. Since a second-order PLL with a large phase margin (i.e. an over-damped second-order PLL) can be approximated with a first-order loop [7], we can re-write (2.37) as:

$$\mathcal{L}_{VCO}(f_{c,opt}) \approx \mathcal{L}_{loop} \cdot \frac{1}{4\pi^2 \cdot f_{c,0}^2} \cdot \frac{\int_0^\infty |\frac{2\pi f_{c,0}^2 / s}{1 + 2\pi f_{c,0}^2 / s}|^2 df}{\int_0^\infty |\frac{1}{s \cdot [1 + 2\pi f_{c,0}^2 / s]}|^2 df} = \mathcal{L}_{loop}$$

(2.38)

which means that  $f_{c,opt}$  is approximately where the spectrum of the VCO and the loop noise

intersects. This conclusion is the same as the one drawn in [4].

The jitter variance due to the VCO and loop at  $f_{c,opt}$  can be calculated by substituting (2.36) into (2.33) and (2.34):

$$\sigma_{t,VCO,opt}^{2} = \frac{\sqrt{\mathcal{L}_{loop}\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}} \cdot \sqrt{\int_{0}^{\infty} |\frac{G_{0}(s)}{1 + G_{0}(s)}|^{2} df \cdot \int_{0}^{\infty} |\frac{1}{s \cdot [1 + G_{0}(s)]}|^{2} df}}{\pi \cdot f_{out}^{2}}, \qquad (2.39)$$

$$\sigma_{t,loop,opt}^{2} = \frac{\sqrt{\mathcal{L}_{loop}\mathcal{L}_{VCO}(f_{r}) \cdot f_{r}^{2}} \cdot \sqrt{\int_{0}^{\infty} |\frac{1}{s \cdot [1 + G_{0}(s)]}|^{2} df \cdot \int_{0}^{\infty} |\frac{G_{0}(s)}{1 + G_{0}(s)}|^{2} df}}{\pi \cdot f_{out}^{2}}.$$

(2.40)

We get  $\sigma_{t,VCO,opt}^2 = \sigma_{t,loop,opt}^2$ , meaning that the VCO and the loop-components contribute equal jitter in an optimized PLL design.

Given  $f_{c,opt}$  in (2.36), the minimum PLL output jitter variance  $\sigma^2_{t,PLL,min}$  is calculated as:

$$\sigma_{t,PLL,\min}^{2} = \frac{1}{\sqrt{P_{loop} \cdot P_{VCO}}} \cdot 10^{\frac{FOM_{loop} + FOM_{VCO}}{20}} \cdot \frac{2}{\pi}$$

$$\cdot \sqrt{\int_{0}^{\infty} |\frac{G_{0}(s)}{1 + G_{0}(s)}|^{2} df} \cdot \int_{0}^{\infty} |\frac{1}{s \cdot [1 + G_{0}(s)]}|^{2} df} \cdot \frac{\mathrm{ImW}}{\mathrm{IHz}}$$

(2.41)

where the VCO and loop phase noise in (2.35) has been represented with  $FOM_{VCO}$  and  $FOM_{loop}$  using (2.5) and (2.26).

For a fixed PLL power budget  $P_{PLL} = P_{loop} + P_{VCO}$ , it is easy to show that the minimum value of (2.41) occurs when  $P_{loop} = P_{VCO} = P_{PLL}/2$ , when the other conditions are kept the same. This means that *the VCO and the loop components consume equal power in an optimized PLL design*. Under this condition, the minimum PLL jitter variance in (2.41) can be re-written as

$$\sigma_{t,PLL,\min}^{2} = \frac{1}{P_{PLL}} \cdot \{ 10^{\frac{FOM_{loop} + FOM_{FCO}}{20}} \cdot \frac{4}{\pi} \cdot \frac{\text{ImW}}{\text{IHz}} \} \cdot \left\{ \sqrt{\int_{0}^{\infty} |\frac{G_{0}(s)}{1 + G_{0}(s)}|^{2} df} \cdot \int_{0}^{\infty} |\frac{1}{s \cdot [1 + G_{0}(s)]}|^{2} df} \right\} \cdot (2.42)$$

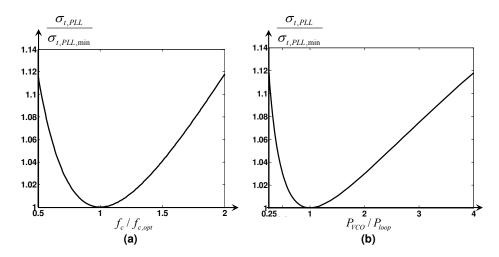

It should be noted that the optimal PLL bandwidth for minimum jitter may not meet the stability or locking time requirements, spending equal power on the loop and the VCO may also have practical difficulties. However, they are still the theoretical optimum under the conditions mentioned and provide designers directions for PLL jitter and power optimization. From a practical point of view, it is useful to know how sensitive the optimum is for

Figure 2.4. Variations of PLL output jitter when (a) PLL bandwidth is not optimal; (b)  $P_{loop} \neq P_{VCO}$  for a given PLL power budget.

parameter variations and how much the PLL jitter will be increased when the optimum condition is not met. Fig. 2.4(a) draws the relative change in the amount of PLL output jitter when  $f_c$  deviates from  $f_{c,opt}$  and Fig. 2.4(b) shows what happens when the VCO and loop do not consume equal power for a given PLL power budget. We see that setting the PLL bandwidth two times larger/smaller than the optimum one or spending 4 times more/less power on the VCO than the loop instead of making them equal increases the output jitter by less than 12%. Therefore, we can conclude that the optimum is relatively flat.

### 2.5.3 PLL Benchmarking

In (2.42), the first bracketed part is a constant determined by the quality of the VCO and loop design. The value of the second bracketed part, the integration, is related to the phase margin of the loop transfer function. In an over-damped second-order PLL (for small jitter peaking), the result of the integration is about 0.25 and we get:

$$\sigma_{t,PLL,\min}^{2} = \frac{1}{P_{PLL}} \cdot 10^{\frac{FOM_{loop} + FOM_{FCO}}{20}} \cdot \frac{1}{\pi} \cdot \frac{1 \text{mW}}{1 \text{Hz}} \cdot (2.43)$$

When the integration part in (2.42) is treated as a (PLL type and order dependent) constant, we can conclude that

$$\sigma_{t,PLL,\min}^2 \propto 1/P_{PLL}.$$

(2.44)

Figure 2.5. ISSCC low jitter PLL designs (Year\_PaperNumber).

We see that when a PLL design is optimized, i.e., when (2.42) holds (equal loop and VCO power, and optimal PLL bandwidth), the minimum PLL jitter is *independent* of  $f_{PD}$  and  $f_{out}$ , given a fixed PLL power budget. Note that for a higher  $f_{out}$ , the loop and VCO phase noise is higher according to (2.5) and (2.26). However, the output clock period is smaller with a higher  $f_{out}$ . When phase noise is converted to jitter using (2.27), these two factors cancel out. A similar observation was also made in [23]. Based on (2.44), we define a PLL benchmark FOM as

$$FOM_{PLL} = 10\log[(\frac{\sigma_{\iota,PLL}}{1s})^2 \cdot \frac{P_{PLL}}{1mW}]$$

(2.45)

The unit of  $FOM_{PLL}$  is dB. A smaller  $FOM_{PLL}$  corresponds to a better PLL design.

Comparing (2.42) and (2.45), we can see that

$$FOM_{PLL} \propto FOM_{loop} + FOM_{VCO}$$

(2.46)

Therefore, the design qualities of the loop and the VCO are equally important. This is intuitive since the loop and the VCO have equal contribution to both power and jitter in an optimized PLL design.

With the defined PLL FOM, different PLL designs can be compared using a single number. Fig. 2.5 shows the performance of some PLL designs in recent years' International Solid State Circuits Conference (ISSCC) along with the  $FOM_{PLL}$  lines. We see that the  $FOM_{PLL}$  improves over the years, as we would expect for a conference that claims to present the state-of-the-art work. The state-of-the-art  $FOM_{PLL}$  is close to -240 dB.

# **2.6 Conclusion**

The phase noise and power consumption of the VCO and loop components in a classical PLL is analyzed. A benchmark FOM for loop designs ( $FOM_{loop}$ ) is proposed, complementary to the existing VCO FOM. The absolute PLL output jitter is calculated and an expression for the minimum jitter is derived. It is shown that, to minimize the output jitter for a given power budget, designers should aim at: 1) spending equal power on the loop and the VCO; and 2) setting the loop bandwidth such that the loop and the VCO contribute equally to the total jitter. In such an optimized PLL, the output jitter is independent of the reference frequency and output frequency for a given power budget. Based on these insights, a benchmark FOM for PLL designs ( $FOM_{PLL}$ ) is proposed. This  $FOM_{PLL}$  can be used to compare various PLL designs in applications where jitter and power are important. Moreover, system designers can use it to predict and trade-off jitter and power during system level design.

# 2.7 References

- V. F. Kroupa, Frequency Synthesis: Theory, Design and Applications. London, U.K.: Griffin, 1973.

- [2] J. A. Crawford, *Frequency Synthesizer Design Handbook*. Boston, MA: Artech House, 1994.

- [3] W. F. Egan, Frequency Synthesis by Phase Lock, 2nd ed., New York: Wiley, 1999.

- [4] C. S. Vaucher, Architectures for RF Frequency Synthesizers. Boston, MA: Kluwer, 2002.

- [5] D. C. Lee, "Analysis of jitter in phase-locked loops," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 704–711, Nov.2002.

- [6] R. C. H. van de Beek, E. Klumperink, C. S. Vaucher and B. Nauta, "Low-jitter clock multiplication: a comparison between PLLs and DLLs," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 555-566, Aug. 2002.

- [7] M. Mansuri and C. K. K. Yang, "Jitter optimization based on phase-locked loop design parameters," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1375-1382, Nov. 2002.

- [8] H. Arora, N. Klemmer, J. Morizio and P. Wolf, "Enhanced phase noise modeling of fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. I*, vol. 52, no.2, pp. 379-395, Feb. 2005.

- [9] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE J. Sel. Areas Commun.*, vol. 17, no.4, pp. 539-550, Apr. 1999.

- [10] P. G. M. Baltus, A. G. Wagemans, R. Dekker, A. Hoogstraate, H. Maas, A. Tombeur and J. van Sinderen, "A 3.5-mW, 2.5-GHz diversity receiver and a 1.2-mW, 3.6-GHz VCO in silicon on anything," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2074-2080, Dec. 1998.

- [11] P. Kinget, "Integrated GHz voltage controlled oscillators," Analog Circuit Design: (X)DSL and Other Communication Systems; RF MOST Models; Integrated Filters and Oscillators, W. Sansen, J. Huijsing and R. van de Plassche, Ed. Boston, MA: Kluwer, pp. 353-381, 1999.

- [12] A. Demir, "Computing timing jitter from phase noise spectra for oscillators and phaselocked loops with white and 1/f Noise," *IEEE T. Circuits Systems I*, vol. 53, no. 9, pp. 1869-1884, Sep. 2006.

- [13] H. Rategh, H. Samavati and T. H. Lee, "A CMOS frequency synthesizer with an injection-locked frequency divider for a 5 GHz Wire LAN receiver," *IEEE J. Solid-State Circuits*, vol. 35, pp. 779-786, May 2000.

- [14] R. Nonis, N. Da Dalt, P. Palestri and L. Selmi, "Modeling, design and characterization of a new low-jitter analog dual tuning LC-VCO PLL architecture," *IEEE J. Solid-State Circuits*, vol. 40, pp. 1303-1309, Jun. 2005.

- [15] A. Hajimiri, S. Limotyrakis and T. H. Lee, "Jitter and phase noise in ring oscillators," *IEEE J. Solid-State Circuits*, vol. 34, pp. 790–804, Jun. 1999.

- [16] P. Andreani and A. Fard, "More on the 1/f<sup>2</sup> phase noise performance of CMOS differential-pair LC tank oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2703–2712, Dec. 2006.

- [17] E. Hegazi, H. Sjoland and A. A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, pp.1921–1930, Dec. 2001.

- [18] D. Banerjee, PLL performance, simulation, and design, 4<sup>th</sup> edition, National Semiconductor, 2006. [on-line] Accessed on Mar. 20<sup>th</sup>, 2010. http://www.national.com/analog/timing/pll designbook

- [19] S. Levantino, L. Romano, S. Pellerano, C. Samori and A. L. Lacaita, "Phase noise in digital frequency dividers," *IEEE J. Solid-State Circuits*, vol. 39, no.5, pp. 775–784, May 2004.

- [20] A. A. Abidi, "Phase noise and jitter in CMOS ring oscillators", *IEEE J. Solid-State Circuits*, vol. 41, no.8, pp. 1803-1816, Aug. 2006.

- [21] E. Klumperink and B. Nauta, "Systematic comparison of HF CMOS transconductors," *IEEE Trans. Circuits Syst. II*, vol. 50, no.10, pp. 728-741, Oct. 2003.

- [22] R. C. H. van de Beek, "High-speed low-jitter clock multiplication in CMOS," PhD thesis, University of Twente, ISBN 90-365-1989-6, 2004.

- [23] X. Gao, E. Klumperink and B. Nauta, "Advantages of shift registers over DLLs for flexible low jitter multiphase clock generation," *IEEE Trans. Circuits Syst. II*, vol. 55, no.3, pp. 244-248, Mar. 2008.

# Chapter 3

# Low Jitter Multi-phase Clock Generation

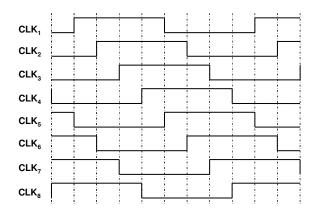

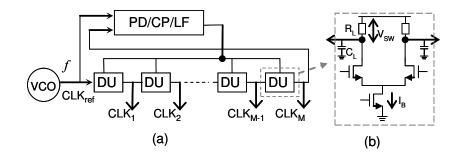

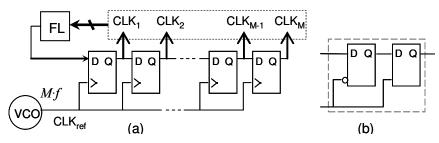

### 3.1 Introduction