### Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

4-21-2014

# Low-loss and low-crosstalk 8 x 8 silicon nanowire AWG routers fabricated with CMOS technology

Jing Wang Purdue University, Birck Nanotechnology Center, Chinese Academy of Sciences

Zhen Sheng Chinese Academy of Sciences

Le Li Grace Semicond Mfg Corp

Albert Pang Grace Semicond Mfg Corp

Aimin Wu Chinese Academy of Sciences

See next page for additional authors

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub Part of the <u>Nanoscience and Nanotechnology Commons</u>

Wang, Jing; Sheng, Zhen; Li, Le; Pang, Albert; Wu, Aimin; Li, Wei; Wang, Xi; Zou, Shichang; Qi, Minghao; and Gan, Fuwan, "Lowloss and low-crosstalk 8 x 8 silicon nanowire AWG routers fabricated with CMOS technology" (2014). *Birck and NCN Publications*. Paper 1612. http://dx.doi.org/10.1364/OE.22.009395

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

### Authors

Jing Wang, Zhen Sheng, Le Li, Albert Pang, Aimin Wu, Wei Li, Xi Wang, Shichang Zou, Minghao Qi, and Fuwan Gan

### Low-loss and low-crosstalk 8 × 8 silicon nanowire AWG routers fabricated with CMOS technology

Jing Wang,<sup>1,3</sup> Zhen Sheng,<sup>1,\*</sup> Le Li,<sup>2</sup> Albert Pang,<sup>2</sup> Aimin Wu,<sup>1</sup> Wei Li,<sup>1</sup> Xi Wang,<sup>1</sup> Shichang Zou,<sup>1,2</sup> Minghao Qi,<sup>3</sup> and Fuwan Gan<sup>1</sup>

<sup>1</sup>State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China <sup>2</sup>Grace Semiconductor Manufacturing Corporation, Shanghai 201203, China

<sup>3</sup>School of Electrical and Computer Engineering, and Birck Nano-technology Center, Purdue University, West

Lafayette, IN 47906, USA zsheng@mail.sim.ac.cn

Abstract: Low-loss and low-crosstalk  $8 \times 8$  arrayed waveguide grating (AWG) routers based on silicon nanowire waveguides are reported. A comparative study of the measurement results of the 3.2 nm-channelspacing AWGs with three different designs is performed to evaluate the effect of each optimal technique, showing that a comprehensive optimization technique is more effective to improve the device performance than a single optimization. Based on the comprehensive optimal design, we further design and experimentally demonstrate a new 8-channel 0.8 nmchannel-spacing silicon AWG router for dense wavelength division multiplexing (DWDM) application with 130 nm CMOS technology. The AWG router with a channel spacing of 3.2 nm (resp. 0.8 nm) exhibits low insertion loss of 2.32 dB (resp. 2.92 dB) and low crosstalk of -20.5~-24.5 dB (resp. -16.9~-17.8 dB). In addition, sophisticated measurements are presented including all-input transmission testing and high-speed WDM system demonstrations for these routers. The functionality of the Si nanowire AWG as a router is characterized and a good cyclic rotation property is demonstrated. Moreover, we test the optical eve diagrams and bit-error-rates (BER) of the de-multiplexed signal when the multiwavelength high-speed signals are launched into the AWG routers in a system experiment. Clear optical eye diagrams and low power penalty from the system point of view are achieved thanks to the low crosstalk of the AWG devices.

©2014 Optical Society of America

OCIS codes: (130.7408) Wavelength filtering devices; (130.3120) Integrated optics devices.

### **References and links**

- M. Smit and C. Van Dam, "PHASAR-based WDM-devices: Principles, design and applications," IEEE J. Sel. 1 Top. Quantum Electron. 2(2), 236-250 (1996).

- M. Zirngibl, C. Dragone, and C. Joyner, "Demonstration of a 15×15 arrayed waveguide multiplexer on InP," IEEE Photon. Technol. Lett. 4(11), 1250-1253 (1992).

- 3. R. Adar, C. Henry, C. Dragone, R. Kistler, and M. Milbrodt, "Broad-band array multiplexers made with silica waveguides on silicon," J. Lightwave Technol. 11(2), 212–219 (1993).

B. Yang, Y. P. Zhu, Y. Q. Jiao, L. Yang, Z. Sheng, S. L. He, and D. X. Dai, "Compact arrayed waveguide

- grating devices based on small SU-8 strip waveguides," J. Lightwave Technol. 29(13), 2009-2014 (2011).

- W. Bogaerts, S. K. Selvaraja, P. Dumon, J. Brouckaert, K. De Vos, D. Van Thourhout, and R. Baets, "Silicon-5. on-insulator spectral filters fabricated with CMOS technology," IEEE J. Sel. Top. Quantum Electron. 16(1), 33– 44 (2010).

- L. Wang, W. Bogaerts, P. Dumon, S. K. Selvaraja, J. Teng, S. Pathak, X. Han, J. Wang, X. Jian, M. Zhao, R. 6. Baets, and G. Morthier, "Athermal arrayed waveguide gratings in silicon-on-insulator by overlaying a polymer cladding on narrowed arrayed waveguides," Appl. Opt. 51(9), 1251-1256 (2012).

- K. Okamoto and K. Ishida, "Fabrication of silicon reflection-type arrayed-waveguide gratings with distributed 7. Bragg reflectors," Opt. Lett. 38(18), 3530-3533 (2013).

- S. Pathak, M. Vanslembrouck, P. Dumon, D. Van Thourhout, and W. Bogaerts, "Optimized silicon AWG with flattened spectral response using an MMI Aperture," J. Lightwave Technol. 31(1), 87–93 (2013).

- S. Pathak, M. Vanslembrouck, P. Dumon, D. Van Thourhout, and W. Bogaerts, "Compact 16×16 channels routers based on silicon-on-insulator AWGs," in *16th Annual symposium of the IEEE Photonics Benelux Chapter* (IEEE Photonics Society, 2011), 101–104.

- D. J. Kim, J. M. Lee, J. H. Song, J. Pyo, and G. Kim, "Crosstalk reduction in a shallow-etched silicon nanowire AWG," IEEE Photon. Technol. Lett. 20(19), 1615–1617 (2008).

- S. Pathak, M. Vanslembrouck, P. Dumon, D. Van Thourhout, and W. Bogaerts, "Compact SOI-based polarization diversity wavelength de-multiplexer circuit using two symmetric AWGs," Opt. Express 20(26), B493–B500 (2012).

- P. Dumon, W. Bogaerts, D. Van Thourhout, D. Taillaert, R. Baets, J. Wouters, S. Beckx, and P. Jaenen, "Compact wavelength router based on a Silicon-on-insulator arrayed waveguide grating pigtailed to a fiber array," Opt. Express 14(2), 664–669 (2006).

- G. Roelkens, D. Vermeulen, S. Selvaraja, R. Halir, W. Bogaerts, and D. Van Thourhout, "Grating-based optical fiber interfaces for silicon-on-insulator photonic integrated circuits," IEEE J. Sel. Top. Quantum Electron. 17(3), 571–580 (2011).

- Z. Sheng, D. Dai, and S. He, "Improve channel uniformity of an Si-nanowire AWG demultiplexer by using dualtapered auxiliary waveguides," J. Lightwave Technol. 25(10), 3001–3007 (2007).

- F. Gan, T. Barwicz, M. A. Popovic, M. S. Dahlem, C. W. Holzwarth, P. T. Rakich, H. I. Smith, E. P. Ippen, and F. X. Kartner, "Maximizing the thermo-optic tuning range of silicon photonic structures," in *Photonics in Switching* (2007), 67–68.

- J. Wang, C. Qiu, H. Li, W. Ling, L. Li, A. Pang, Z. Sheng, A. M. Wu, X. Wang, S. C. Zou, and F. W. Gan, "Optimization and demonstration of a large-bandwidth carrier-depletion silicon optical modulator," J. Lightwave Technol. 31(24), 4119–4125 (2013).

- 17. Y. Tachikawa, Y. Inoue, M. Ishii, and T. Nozawa, "Arrayed-waveguide grating multiplexer with loop-back optical paths and its applications," J. Lightwave Technol. **14**(6), 977–984 (1996).

- S. Suzuki, A. Himeno, and M. Ishii, "Integrated multichannel optical wavelength selective switches incorporating an arrayed-waveguide grating multiplexer and thermooptic switches," J. Lightwave Technol. 16(4), 650–655 (1998).

- P. Cheben, J. H. Schmid, A. Delâge, A. Densmore, S. Janz, B. Lamontagne, J. Lapointe, E. Post, P. Waldron, and D.-X. Xu, "A high-resolution silicon-on-insulator arrayed waveguide grating microspectrometer with submicrometer aperture waveguides," Opt. Express 15(5), 2299–2306 (2007).

- J. Zou, X. X. Jiang, X. Xia, T. T. Lang, and J. J. He, "Ultra-compact birefringence-compensated arrayed waveguide grating triplexer based on silicon-on-insulator," J. Lightwave Technol. 31(12), 1935–1940 (2013).

- T. Hiraki, H. Nishi, T. Tsuchizawa, K. Rai, H. Fukuda, K. Takeda, Y. Ishikawa, K. Wada, and K. Yamada, "Si-Ge-silica monolithic integration platform and its application to a 22-Gb/s×16-ch WDM receiver," IEEE Photonics J. 5(4), 4500407 (2013).

#### 1. Introduction

Arrayed waveguide grating (AWG) has become a key component in commercial wavelengthdivision multiplexing (WDM) systems for its multichannel wavelength selective function [1]. In low-index-contrast material systems, such as InP [2], silica [3] and polymer [4], highperformance AWGs have been demonstrated. However, these AWGs have large device sizes and cannot be easily integrated with other photonic devices. In recent years, AWG based on silicon nanowire waveguides [5–11] has attracted much attention for its compact size owing to the high-index-contrast property of the silicon-on-insulator (SOI) waveguide, which allows for sharp bends. Moreover, its fabrication is compatible with CMOS technology, offering a promising solution for large-scale integration with other silicon-based devices in a highdensity photonic chip. However, most of these Si nanowire AWGs have been demonstrated as wavelength (de)multiplexers previously. In 2011, S. Pathak *et. al* reported a compact  $16 \times 16$ Si nanowire AWG router with a channel spacing of 3.2 nm, which offers a more complicated wavelength selective function for its cyclic rotation property [9]. The AWG routers with smaller channel spacing (e.g., <1 nm) have not been reported yet. It is well known that the Si nanowire AWG has worse crosstalk performance than the low-index-contrast device due to its increased sensitivity to the phase error of the arrayed waveguides. By using rib waveguides instead of strip waveguides [10] and broadening the arrayed waveguide width [11], the crosstalk performance has been effectively improved. For the AWG with smaller channel spacing (e.g., 0.8 nm) which normally has several millimeter-long arrayed waveguides, the crosstalk performance becomes even worse because it is difficult to ensure good process uniformity in a relatively large area and consequently, a quite large phase error is induced.

Therefore, it is challenging to realize the Si nanowire AWG with a channel spacing less than 1 nm.

In this work, a comparative study of the Si nanowire AWGs with different optimization techniques is presented. The performance improvement is shown not only from the static spectral responses, but also from the system point of view, such as eye diagrams, bit-errorrates and power penalty. The characterization results of the AWGs show that a comprehensive optimal design by incorporating both the arrayed waveguides with larger waveguide width and bi-level tapers between the free propagation region (FPR) and the arrayed waveguides is superior to those with a single optimization technique. With the comprehensive optimal design, the fabricated 3.2 nm-channel-spacing Si nanowire AWG achieves a good crosstalk performance of less than -20 dB. Based on the optimal design and well-controlled 130 nm CMOS fabrication process, a new high-performance Si nanowire AWG router with 0.8 nm channel spacing for DWDM application is successfully demonstrated. The devices show a good performance in terms of low insertion loss and crosstalk. In addition, the functionality of the Si nanowire AWG as a router is characterized and a good cyclic rotation property is demonstrated The AWGs are further employed in a high-speed transmission system where multi-wavelength signals with data rate up to 10 Gb/s are launched into the devices. Clear optical eve diagrams and low power penalty are obtained due to the low device crosstalk.

### 2. Comparative study of 3.2 nm-channel-spacing Si nanowire AWGs with different design optimizations

All of the device design is performed based on the SOI strip nanowire waveguide with  $SiO_2$ upper-cladding. The waveguide has a height of 220 nm and a width of 450 nm, which ensures single-mode transmission and a low propagation loss. 35 arrayed waveguides with constant length difference are located between two FPRs. The performance of the AWG is usually characterized by the insertion loss and crosstalk in each channel. The optimization techniques considered here are used to reduce the mode transition loss between the FPR and the arrayed waveguides, and suppress the phase error in the arrayed waveguides. On one hand, a 20 µmlong bi-level taper which is etched 70 nm-deep and linearly tapered from 2.5 um to 0.45 um is adopted as a mode converter between the FPR and each arrayed waveguide, as implemented in [12]. On the other hand, the arrayed waveguides are designed to be 1  $\mu$ m-wide in order to reduce the sensitivity of the effective index to the waveguide dimension. This method is effective to alleviate the crosstalk due to the waveguide sidewall roughness [5]. Meanwhile, the width of the arrayed waveguides at bends remains 450 nm to enable small bending radius  $(5 \,\mu\text{m})$ . Considering the above two optimization techniques, three AWG devices with 3.2 nm channel spacing are designed for a comparison as follows: AWG (#1) without any optimization, AWG (#2) with optimization of the arrayed waveguides, and AWG (#3) with both optimizations. Since the arrayed waveguide width of AWG (#2) and (#3) is larger than that of AWG (#1), the path difference is modified accordingly to maintain a 3.2 nm channel spacing. The detailed design parameters are summarized in Table 1.

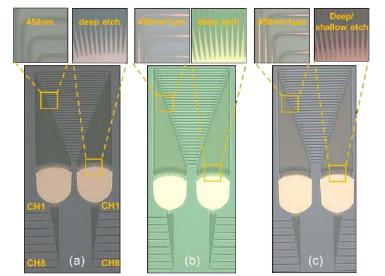

The devices were fabricated with a 130 nm CMOS process on the 200-mm SOI wafer with a top silicon layer of 220 nm-thickness and a buried oxide (BOX) layer of 2  $\mu$ m-thickness. Firstly a silicon nitride (SiN) film was deposited on the wafer surface as a hard mask layer for the subsequent Si etching. Then the waveguide pattern was defined by 248-nm deep-ultraviolet (DUV) lithography. Since the phase error is mainly caused by the sidewall roughness of the arrayed waveguides, the thickness of the bottom anti-reflection coating (BARC) layer and the exposure condition were both optimized to reduce the sidewall roughness. Inductively coupled plasma reactive ion etching (ICP-RIE) was used to form the silicon waveguides with smooth sidewall and a vertical profile. Finally, a thick SiO<sub>2</sub> layer was deposited on the wafer surface. The microscope pictures of the fabricated AWG routers are shown in Fig. 1.

|                                                                                  | # 1     | # 2     | # 3     |

|----------------------------------------------------------------------------------|---------|---------|---------|

| Channel spacing $(\Delta_{CH})$ (nm)                                             | 3.2     | 3.2     | 3.2     |

| Number of channels (N <sub>CH</sub> )                                            | 8       | 8       | 8       |

| Free spectral range (FSR) (µm)                                                   | 25.6    | 25.6    | 25.6    |

| Focal length of slab waveguide (L) (µm)                                          | 130.967 | 131.725 | 131.725 |

| Number of arrayed waveguides (N)                                                 | 35      | 35      | 35      |

| Path difference of arrayed waveguides ( $\Delta L$ ) ( $\mu m$ )                 | 23.088  | 25.4    | 25.4    |

| Diffraction order (m)                                                            | 45      | 45      | 45      |

| Separation between the input/output waveguides near the FPR (d) $(\mu m)$        | 3.2     | 3.2     | 3.2     |

| Separation between the arrayed waveguides<br>near the FPR (d <sub>a</sub> ) (µm) | 2.8     | 2.8     | 2.8     |

Table 1. AWG design parameters

Fig. 1. (a-c) The microscope pictures of the AWG routers (#1, #2, #3), respectively. Insets: Detail views of the bends in the arrayed waveguides and the tapers near the FPR.

The device performance including insertion loss and crosstalk can be characterized by measuring the transmission spectrum of each channel. The light from a tunable laser was adjusted to be TE mode by a polarization controller and then coupled into one of the input channels of the AWG through grating couplers [13]. Then the light passing through the AWG was received by a power-meter.

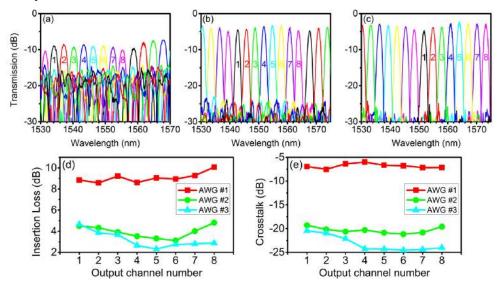

The measured transmission spectra of AWGs (#1, #2, #3), which have been normalized to a reference waveguide, are presented in Figs. 2(a)-2(c), respectively. For the ease of performance comparison, we extract the insertion loss and crosstalk of each channel in Figs. 2(d) and 2(e), respectively. AWG (#1) shows a poor performance with respect to both the insertion loss and crosstalk because of the large phase distortion of the arrayed waveguides. The waveguide sidewall roughness induces fluctuations of the effective index and thus degrades the imaging quality at the output waveguides. For this AWG, considerable optical power of certain wavelength enters into the unwanted output channels and thus the received power in the desirable channel is reduced, which leads to both poor crosstalk performance and large insertion loss. More details of the relationship between insertion loss and crosstalk

against phase error can be found in [10]. By broadening the arrayed waveguide width, it is obviously noted that the performance is greatly improved for both AWG (#2) and AWG (#3) since a wider waveguide is less susceptible to size variations. A low insertion loss of < 3 dB and a crosstalk level of < -17 dB are obtained. Further improvement is achieved by shallowly etching the arrayed waveguides near the FPR to reduce the mode transition loss, as for AWG (#3). The mode in the bi-level taper has a better match with that in the FPR, which reduces the insertion loss. According to the discussion above, a comprehensive optimal design by incorporating both the arrayed waveguides with larger waveguide width and bi-level tapers between the FPR and the arrayed waveguides is superior to those with a single optimization technique.

Fig. 2. (a-c) The measured spectra of the fabricated AWG (#1, #2, #3), respectively when light launched into the center input channel. (d) The insertion loss and (e) crosstalk of each output channel.

### 3. Demonstration of a high-performance Si nanowire AWG with 0.8 nm channel spacing

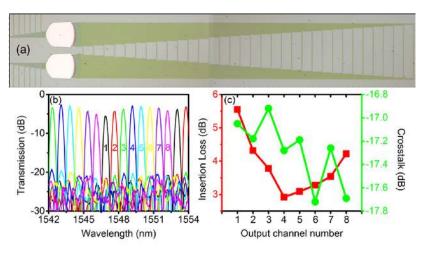

Based on the comprehensive optimal design and well-controlled 130 nm CMOS fabrication process mentioned above, a high-performance Si nanowire AWG (#4) router with 0.8 nm channel spacing is successfully demonstrated. Figure 3(a) shows the microscope picture of AWG (#4) with 0.8 nm channel spacing. Its size is about 4 times larger than those with 3.2 nm channel spacing. This is because the path difference of the arrayed waveguides scales inversely with the channel spacing. Therefore, AWG with smaller channel spacing requires a more radical optimization (*e.g.*, incorporating multiple optimizing techniques) to suppress the phase error as well as a more rigorous control of the process uniformity as mentioned above. Figure 3(b) shows the normalized transmission spectrum, where the insertion loss and crosstalk of each channel is extracted in Fig. 3(c).

Fig. 3. (a) The microscope picture, (b) transmission spectrum, and (c) extracted performance in each channel of the 0.8 nm-channel-spacing AWG router with a comprehensive optimal design. The design parameters of AWG (#4) are as follows:  $\Delta_{CH} = 0.8$  nm,  $N_{CH} = 8$ , FSR = 6.4 nm, L = 127.608 µm, N = 35,  $\Delta L = 101.599$  µm, m = 180, d = 3.1 µm, d<sub>a</sub> = 2.8 µm.

For comparison, Table 2 summarizes the insertion loss and crosstalk performance of previously reported silicon nanowire AWGs. It can be seen that our device with 3.2 nm channel spacing has a good performance in terms of both the insertion loss and crosstalk. Meanwhile, the AWG with 0.8 nm channel spacing shows a comparative performance with those of the 1.6 nm AWGs previously reported. The demonstration of the high-resolution AWG offers potential for DWDM with small channel spacing for silicon-based optical interconnects.

Table 2. Performance comparison of previously reported silicon nanowire AWGs with the devices in this work

| Reference            | [6] | [7] | [8]  | [9] | [10]    | [11]  | This work   | This work       |

|----------------------|-----|-----|------|-----|---------|-------|-------------|-----------------|

| Channel spacing (nm) | 3.2 | 3.2 | 3.2  | 3.2 | 1.6     | 1.6   | 3.2         | 0.8             |

| Insertion loss (dB)  | 2.6 | 3   | 3.29 | 3   | 3       | 2.6   | 2.32        | 2.92            |

| Crosstalk (dB)       | -15 | -20 | -17  | -20 | -16~-18 | -21.5 | -20.5~-24.5 | -16.9~-<br>17.8 |

## 4. Performance characterization for the cyclic rotation properties of the Si nanowire AWG routers

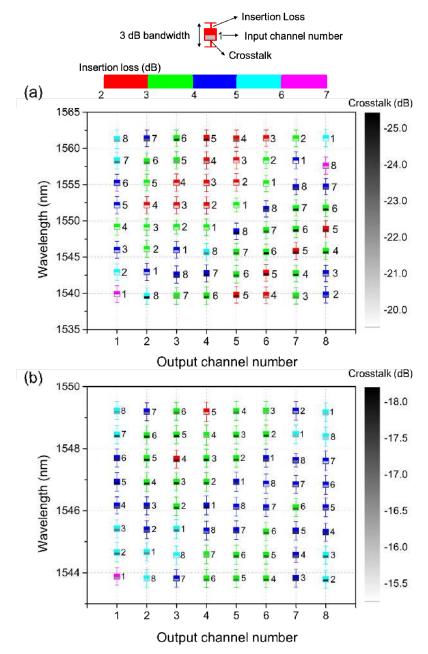

The cyclic properties of the Si nanowire AWG routers were measured for both AWG (#3) and AWG (#4), as shown in Fig. 4. Each point in these figures represents the peak wavelength of the channel, while the length of the bar equals to the 3 dB bandwidth. The insertion loss, crosstalk and input channel number are also labeled for each point. When the input light is transferred from one channel to its adjacent channel, the transmission spectra of the eight output channels shift by a channel spacing accordingly. All the points form a well-aligned 8 × 8 matrix, exhibiting clear cyclic rotation properties. For AWG (#3) and AWG (#4), the 3 dB bandwidth is ~1.1 nm and ~0.3 nm, respectively. For each input channel, the insertion loss ranges from 2 dB to 4 dB and the device exhibits a non-uniformity of 4.13 dB and 3.66 dB for AWG (#3) and AWG (#4), respectively. The insertion loss non-uniformity which results from the far field envelope with a quasi-Gaussian shape [1] can be further improved by increasing the length of FPR or introducing some special structures [14]. In addition, the crosstalk performance is slightly degraded when the light is input other than the central channel, but is still smaller than ~20 dB and ~15.5 dB for AWG (#3) and AWG (#4), respectively. Other important figures of merit include the central wavelength fluctuation and the channel spacing

deviation. Since the two optimization techniques implemented in this work are not effective to precisely control the absolute value of the effective index of the waveguides, which determines the central wavelength and channel spacing [1], AWGs (#3, #4) have little improvement in terms of the accuracy of central wavelength or channel spacing. The central wavelength fluctuation is several nanometers and the actual channel spacing has a ~5% deviation from the target value. Some post-fabrication tuning technology (e.g. thermal tuning [15]) can be further used for wavelength adjustment.

Fig. 4. The measured cyclic rotation properties of the  $8 \times 8$  Si nanowire AWG routers with (a) 3.2 nm (AWG #3) and (b) 0.8 nm (AWG #4) channel spacing, respectively.

#### 5. Multi-wavelength high-speed system demonstration

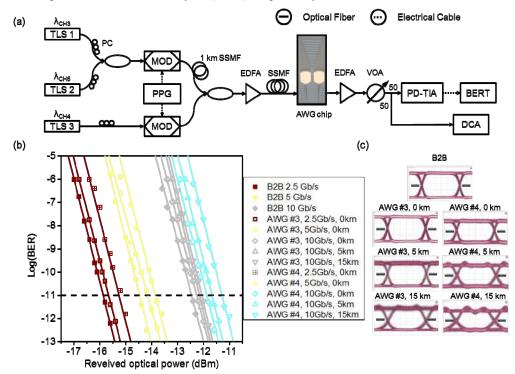

We further analyzed the transmission characteristics of AWG (#3) and AWG (#4) in a threechannel WDM communication system. Figure 5(a) shows the experimental setup. The tunable laser source (TLS) 3 was tuned to match the wavelength of the 4th channel (see Fig. 2(c) and Fig. 3(b)) in which the main signal is transmitted. The other two TLSs (TLS 2 and TLS 3) were tuned at the wavelengths that have a channel spacing of  $\pm$  3.2 nm ( $\pm$  0.8 nm) relative to channel 4. The pulse-pattern generator (PPG) was used to drive the lithium niobate modulators (MOD) to generate high-speed (2.5 Gb/s, 5 Gb/s and 10 Gb/s) optical signals with pseudo-random binary pattern (PRBS) length of  $2^{31}$ -1. Before amplified by an erbium-doped fiber amplifier (EDFA), the signals with the wavelengths of channel 3 and channel 5 were decorrelated by using standard single-mode fiber (SSMF) with a length of 1 km. Then the multiplexed signals passed through another SSMF with various lengths (0 km, 5 km and 15km) and entered into the central input channel of the AWG, which works as a demultiplexer in this experiment. The output signal from the 4th channel was amplified by another EDFA and passed through a variable optical attenuator (VOA) and a 3 dB coupler. Finally, the BER and optical eye diagrams were measured by a bit-error-rate tester (BERT) and a digital communication analyzer (DCA), respectively.

Fig. 5. (a) The experimental setup for evaluating the transmission characteristics of the Si AWGs (#3, #4). (b) BER measurement for the demultiplexed output signal when the input signals are modulated at various data rate (2.5 Gb/s, 5 Gb/s and 10 Gb/s) and passed through various lengths (0 km, 5 km and 15 km). (c) Optical eye diagrams of the output signal modulated at 10 Gb/s data rate for fibers with various lengths.

Figure 5(b) shows the results of the BER measurement performed for the demultiplexed signals from AWG (#3) and AWG (#4). Here the BER measurement results in a back-to-back (B2B) link without AWGs are also shown for reference. One can note that at the same driving data rate, a lower power penalty is obtained in a link with AWG (#3) due to the lower interchannel crosstalk. In addition, since the extinction ratio (ER) is considerably affected by the crosstalk, the power penalty in a 10 Gb/s link with AWG (#3) and a 15 km fiber is better than

that in a link with AWG (#4) and 0 km fiber. Nevertheless, a low power penalty of < 1.2 dB is achieved for the low-crosstalk 0.8 nm-channel-spacing AWG (#4) in a 10 Gb/s link with 15 km fiber length. Figure 5(c) shows clear optical eye diagrams of the output signals in a 10 Gb/s link thanks to the low inter-channel crosstalk of the AWGs.

### 6. Conclusion

The design, fabrication and measurement of  $8 \times 8$  Si nanowire AWG routers with low loss and low crosstalk have been presented. Based on the performance comparison of the 3.2 nmchannel-spacing AWGs with different designs, a comprehensive optimal design which incorporates both broadened arrayed waveguides and bi-level tapers between the FSR and the arrayed waveguides is proved to be more effective than those with a single optimization technique. With the comprehensive optimal design and well-controlled 130 nm CMOS fabrication process, a new high-performance Si nanowire AWG router with 0.8 nm channel spacing for DWDM application is successfully demonstrated. The cyclic rotation properties of the Si nanowire AWG routers are also shown. Moreover, system experiments have been carried out for WDM applications of the Si nanowire AWGs at various data rates and fiber lengths, showing clear 10 Gb/s eye diagrams and < 1.2 dB power penalty. These AWG devices can be integrated with other silicon-based devices [16] for various applications, such as add-drop multiplexers [17], wavelength-selective switches [18], spectrometers [19], triplexers [20], receivers [21], etc.

### Acknowledgments

This work was partially supported by the State High-Tech Development Plan (No. 2012AA012202), the Natural Science Foundation of Shanghai (No. 11ZR1443700) and the Natural Science Foundation of China (No. 61106051, 61107031, and 61275112). M. Qi was partially supported by National Science Foundation grant ECCS-0925759 and Defense Threat Reduction Agency grant HDTRA1-10-1-0106. J. Wang acknowledges the China Scholarship Council for a student study-abroad grant.