# Low-Loss, Low-Crosstalk, and Large-Scale Optical Switch Based on Silicon Photonics

Keijiro Suzuki<sup>®</sup>, *Member, OSA*, Ryotaro Konoike<sup>®</sup>, Satoshi Suda, Hiroyuki Matsuura<sup>®</sup>, Shu Namiki<sup>®</sup>, *Fellow, IEEE, Fellow, OSA*, Hitoshi Kawashima, *Member, OSA*, and Kazuhiro Ikeda<sup>®</sup>, *Senior Member, OSA*

(Top-Scored Paper)

Abstract—We review the research progress of strictly nonblocking optical switches based on silicon photonics. We have developed a switch chip fabrication process based on a complementary metal-oxide-semiconductor pilot line and optical and electrical packaging technologies. We demonstrated all-paths transmission and switching of up to 32 input ports  $\times$  32 output ports with an average fiber-to-fiber insertion loss of 10.8 dB. Furthermore, we demonstrated an operating bandwidth wider than 100 nm for -30 dB crosstalk with double-Mach-Zehnder element switches in an  $8 \times 8$  switch. For polarization-insensitive operation, we adopted a polarization diversity scheme and fabricated an  $8 \times 8$  switch with fiber-based polarization-beam-splitters and two switch chips. The  $8 \times 8$  switch exhibited a polarization-dependent loss of less than 0.5 dB. Moreover, an on-chip polarization diversity  $8 \times 8$  switch integrated with polarization splitter rotators and two switch matrices on a single chip demonstrated a differential group delay less than 1 ps. Based on current technologies, we discuss the prospects for further port count expansion and remaining challenges for commercial deployment.

Index Terms—Optical fiber coupling, optical switches, photonic integrated circuits, silicon photonics, strictly nonblocking switches.

#### I. INTRODUCTION

**D** ATACENTER-RELATED traffic is growing, especially within data centers, with traffic forecast to grow at a rate of 25% per year until 2021 [3]. The switching capacity requirements for the switch ASICs to handle the massive data flow is outpacing Moore's law. This switching capacity expansion is accompanied by increased power consumption that is approaching the thermal limit ( $\sim$ 300 W) of practical integrated electronic circuit cooling technology [5]. To overcome this energy bottleneck and build sustainable data centers with

Manuscript received May 31, 2019; revised July 25, 2019; accepted August 7, 2019. Date of publication August 12, 2019; date of current version January 23, 2020. This work was supported in part by the Project for Developing Innovation Systems of MEXT, Japan, and in part by the CREST, JST (JPMJCR15N6). The device fabrication was supported by TIA Super Clean-Room of the National Institute of Advanced Industrial Science and Technology (AIST). (*Corresponding author: Keijiro Suzuki.*)

The authors are with the National Institute of Advanced Industrial Science and Technology, Tsukuba 305-8569, Japan (e-mail: k.suzuki@aist.go.jp; r.konoike@aist.go.jp; s-suda@aist.go.jp; hiroyuki.matsuura@aist.go.jp; shu. namiki@aist.go.jp; kawashima-h@aist.go.jp; kaz.ikeda@aist.go.jp).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JLT.2019.2934768

TABLE I Optical Switch Technologies

| Switching<br>Time | Platform                     | Mechanism         | Port<br>Count | SNB | On-chip<br>Loss<br>[dB] | Ref. |

|-------------------|------------------------------|-------------------|---------------|-----|-------------------------|------|

| ~10 ms            | Space<br>Optics              | MEMS<br>Mirror    | 320           | Yes | $\leq 3 \text{ dB*}$    | [1]  |

| ~10 ms            | Space<br>Optics              | Piezo<br>Actuator | 384           | Yes | $\leq 3 \text{ dB*}$    | [2]  |

| ~ms               | Silica<br>PLC                | ТО                | 32            | Yes | 6.6*                    | [4]  |

| ~10 µs            | CMOS<br>compatible<br>Si Ph. | ТО                | 32            | Yes | 6.1                     | [6]  |

| ~µs               | MEMS<br>Si Ph                | MEMS              | 240           | Yes | 9.8                     | [7]  |

| ~10 ns            | CMOS<br>compatible<br>Si Ph. | Carrier<br>Plasma | 32            | No  | 12.9 –<br>16.5          | [9]  |

| ~ns               | InP                          | Carrier<br>Plasma | 8             | Yes | 24.0 –<br>28.5          | [13] |

| ~ns               | InP                          | SOA               | 8             | No  | 7.7 **                  | [15] |

SNB: strictly non-blocking, PLC: planar lightwave circuit, Si Ph.: silicon photonics, TO: thermo-optic, SOA: semiconductor optical amplifier, \*Fiber-to-fiber insertion loss, \*\*On-chip gain.

reasonable power consumption, optical switches are expected to be one of the key enablers.

Table I summarizes various optical switch technologies. Free-space optical switches can provide several hundred switching ports with a fiber-to-fiber insertion loss of only a few dB, and are commercially available. Silica planar lightwave circuit (PLC) based switches are also commercially available and can provide up to 32 ports switching with an insertion loss of 6.6 dB. However, the switching time of the three switches is of the order of milliseconds, and this limits their application to job-level system reconfiguration. On the contrary, optical switches based on integrated optical waveguides can provide fast switching ranging from ns to 10  $\mu$ s. For further reduction of the electric power consumption in a data center, a fast (<<1 ms) circuit switch or a flow switch is required [8]. Although optical characteristics and port-count scalability of integrated optical waveguides (such as loss, crosstalk, and polarization-dependent loss (PDL)) are not as good as those of the free-space optical switches, they can meet the fast switching requirement, and have thus been attracting attention.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Among the integrated waveguide-based optical switches, we focus on the complementary metal-oxide-semiconductor (CMOS)-compatible silicon photonics switch, because the CMOS-compatible silicon photonics platform provides high density and uniform integration, and potentially low cost owing to its mass producibility. As for the switching mechanism, we chose the thermo-optic (TO) switch because it can provide  $\sim 10$ - $\mu$ s or faster switching without any additional losses. Although the carrier plasma switch can provide ~ns order switching time, it accompanies absorption loss. As for micro electro mechanical system (MEMS) based silicon switches, they possess a switching speed of  $\sim \mu s$  and the maximum port count of 240. However, their electrical packaging is challenging, and transmissions of all paths have not been demonstrated yet. Moreover, tens of voltages are required to actuate the MEMS switch, which is difficult to handle with the CMOS technology. Hereafter, therefore, we focus on CMOS-based silicon photonics switches.

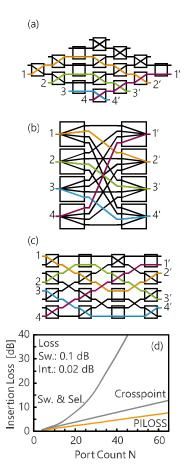

The strictly-non-blocking type of optical switch has the property that any optical path changes do not interfere any other established paths. This is an important characteristic for flexible network operation, and several groups reported such optical switches based on CMOS silicon photonics [10]-[12]. There are three typical topologies for the strictly-non-blocking switches, including the cross-point, the switch-and-select [14], and the path-independent insertion-loss (PILOSS) [16], which are illustrated in Fig. 1(a)-(c). Fig. 1(d) compares the insertion losses of the worst paths of the three topologies, in which the insertion losses of the element switch and the intersection are assumed to be 0.1 dB and 0.02 dB, respectively. We note that the insertion loss of the switch-and-select rapidly increases with the port count and moreover that the loss of the PILOSS remains the lowest. Therefore, we consider that the PILOSS topology has potential advantages for larger port count switches. In future, however, if multilayer platform technologies [17], [18] that can eliminate the insertion loss of the intersection get matured, the switch-and-select topology may be an option. The double-layer network [19] that is a different version of switch-and-select topology will be also another option in terms of loss, although the power consumption of the switch-and-select topology will be an issue for a large-port-count switch since the number of bar-state switches (ON switches) is much larger than that of the other topologies.

In this paper, we review the current performance of CMOSbased silicon photonics PILOSS switches and discuss the remaining challenges for their practical application [20]. In Section II, we describe a  $32 \times 32$  switch that is the largest port count silicon PILOSS switch. In Sections III and IV, we discuss wavelength and polarization insensitivities, respectively. In Section V, we discuss some obstacles and possible solutions toward further improvement of transmission characteristics and port count expansion. Finally, in Section VI, the conclusions of this paper are presented.

## II. $32 \times 32$ PILOSS Switch

The  $32 \times 32$  PILOSS switch chip was fabricated using our CMOS pilot line that can process 300-mm silicon-on-insulator wafers with an immersion ArF lithography. The switch chip

Fig. 1. Schematics of  $4 \times 4$  switch based on (a) cross-point, (b) switchand-select, and (c) path-independent insertion-loss (PILOSS) topologies. (d) Comparison of worst insertion loss. The losses of the element switch and the intersection were assumed to be 0.1 and 0.02 dB, respectively.

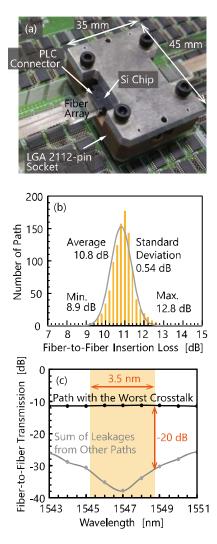

has 2,112 electrodes for the thermo-optic phase-shifter control, which were fanned out to a 0.5-mm-pitch land-grid-array (LGA) by a flip-chip bonded ceramic interposer. Optical connectors based on an extremely high- $\Delta$  silica PLC [21] were attached and secured with refractive-index-matched UV-cured glue. Finally, the assembled switch chip was inserted into an LGA socket on a printed circuit board (PCB) with control electronics [Fig. 2(a)]. We note that the switch chip with the optical connector is not placed under high temperature owing to the socket packaging. We controlled the thermo-optic phase shifters on the chip by adjusting the pulse width of the square pulse train generated by five field-programmable-gate-arrays (FPGAs) on the PCB [22]. The initial phase errors of the element switches, which are directional-coupler-based Mach-Zehnder (MZ) switches, were automatically calibrated [23]. The heating efficiency is 18.1 mW/ $\pi$ -shift [6]. The electric power consumption on the chip in the full-load condition was 1.9 W.

First, we evaluated fiber-to-fiber insertion loss of all (1,024) paths, and its distribution is shown in Fig. 2(b). The switch exhibited 10.8 dB average loss with 0.54 dB standard deviation. The maximum and minimum losses were 12.8 dB and 8.9 dB, respectively. We consider that the insertion loss variation was caused by the coupling loss variation, especially the input side, and the propagation loss difference among the routing waveguides that connect the edge couplers and the switch matrix.

Fig. 2. (a) Fabricated  $32 \times 32$  switch mounted on printed circuit board with control electronics. (b) Distribution of fiber-to-fiber insertion loss. The gray line is the fitted Gaussian whose standard deviation is 0.54 dB. (c) Wavelength spectrum of one of the worst crosstalk paths and sum of leakages from other paths.

Second, we characterized the crosstalk in one of the severest paths. Here, we defined the crosstalk as the ratio between the transmitted power from a path (path A) and the sum of the leaked powers from other paths to the path A. Fig. 2(c) presents the transmission spectra of one of the worst crosstalk paths and the sum of the leakages from other paths. We note that the crosstalk was less than -20 dB in a bandwidth of 3.5 nm due to the wavelength dependence of the directional coupler in the MZ switch. The wavelength dependence can be relaxed by exchanging the output port of the element MZ switch, resulting in the bandwidth expansion to 14.2 nm [6].

#### **III. WAVELENGTH INSENSITIVITY**

A straightforward method to expand the low crosstalk bandwidth is replacing the directional couplers with broadband couplers such as a multi-mode interference (MMI) coupler, or an adiabatic directional coupler. However, they are not suited for large port-count optical switches, because the MMI and

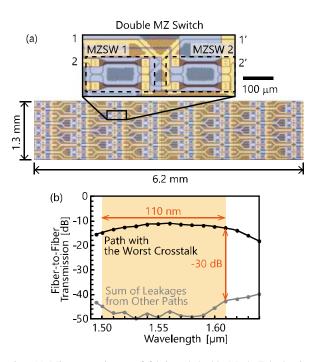

Fig. 3. (a) Microscope image of fabricated double Mach–Zehnder  $8 \times 8$  switch. (b) Fiber-to-fiber transmission spectra of one of the severest crosstalk paths and sum of leakages from other paths.

the adiabatic coupler possess high insertion loss. Therefore, we adopted a double-MZ switch that was originally proposed by Goh et al. for the silica PLC platform [24]. The double-MZ switch consists of two MZ switches and one intersection, as shown in Fig. 3(a). The rear MZ switch suppresses the leakage from the front MZ switch at the cross state or leads it to an idle port at the bar state, resulting in lower crosstalk and wider bandwidth of the switch matrix than those of a single MZ switch case. The numbers of the MZ switches and the intersections on a path in the double-MZ  $N \times N$  switch increase by one, and N-1, respectively, compared with those in the single-MZ  $N \times N$  switch. If we composed the double-MZ  $32 \times 32$  switch, the additional loss would be less than 1 dB ( $\approx 0.13$  dB (MZ switch) + 0.024 dB (intersection)  $\times (32 - 1)$ ), which is acceptable.

We fabricated an  $8 \times 8$  switch based on the double-MZ switch, as shown in Fig. 3(a). The switch chip was fabricated in the same manner described in Section II. Then, the switch chip was die-bonded and wire-bonded to a ceramic chip carrier with a 304-pin pin-grid-array (PGA). An optical fiber array was buttcoupled to the switch chip, then the chip carrier was inserted into a PGA socket on a PCB, which has one FPGA for thermo-optic phase-shifter control.

Fig. 3(b) presents the transmission spectra of one of the severest crosstalk paths and the sum of leakages from the other paths [25]. We note that the  $8 \times 8$  switch exhibited less than -30 dB crosstalk in a bandwidth of 110 nm.

#### IV. POLARIZATION INSENSITIVITY

The silicon waveguide exhibits significant polarization dependency due to strong optical confinement, and this prevents the deployment of silicon devices in practical applications. To

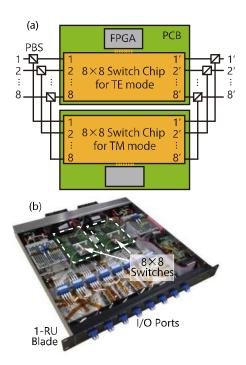

Fig. 4. (a) Configuration of polarization diversity  $8 \times 8$  switch by using polarization beam splitters with fiber pigtails. (b) Polarization-diversity double Mach–Zehnder  $8 \times 8$  switch assembled into 1-RU blade.

realize polarization-insensitive operation, there are two options; the polarization diversity scheme and the polarizationinsensitive structure. We consider that the polarization diversity scheme is a realistic option at this time because the polarizationinsensitive structure requires very high fabrication accuracy [26]. In the polarization diversity scheme, two switch matrices deal with the two orthogonal polarizations. This may become a disadvantage for high-radix switches because it requires handling double the footprint and optical and electrical input/output connections. However, a non-duplicate polarization diversity PILOSS topology will overcome the disadvantage [27].

Fig. 4(a) illustrates the configuration of a polarization diversity  $8 \times 8$  switch by using two double-MZ  $8 \times 8$  switches on the PCBs and 16 fiber-based polarization-beam-splitters (PBSs) [28]. We term this configuration as "off-chip" polarization-diversity. The input light was separated into two orthogonal polarizations with the PBS, then launched into each switch. The output lights from each switch were mixed with another PBS. The polarization diversity switch was assembled into a 1-RU chassis, as shown in Fig. 4(b).

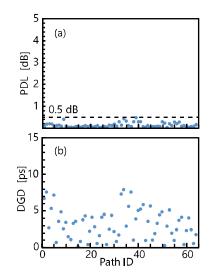

We measured the PDL and the differential group delay (DGD) of all paths with an optical component analyzer based on the Muller matrix, and the results are presented in Fig. 5(a) and (b). The PDL at a wavelength of 1535 nm was less than 0.5 dB. The residual PDL was attributed from the polarization variation of the experimental setup. The DGD was less than 8 ps, which reflects fiber length variations ( $\sim \pm 1$  mm) of the PBS and the optical fiber array. These polarization characteristics are low enough for optical signal transmission with digital signal recovery. In fact, the 8-stage cascaded operation of the 8 × 8 switch was demonstrated, in which 11-channel 44-Gbaud

Fig. 5. (a) Measured polarization dependent loss and (b) differential group delay of polarization diversity  $8 \times 8$  switch shown in Fig. 4 at a wavelength of 1535 nm. Path ID means input-output connections. 1: 1 (input) -1' (output), 2: 1-2, ..., 64: 8-8'.

Fig. 6. (a) Configuration of polarization diversity  $8 \times 8$  switch by using on-chip polarization splitter rotators. (b) Microscopic image of fabricated polarization-diversity  $8 \times 8$  switch chip.

DP-16QAM signals transmitted through all the paths of this  $8 \times 8$  switch [32]. Furthermore, we conducted a long-term (~2 years) reliability test in a test bed that simulates real-world deployment. Specifically, we have observed no degradations in fiber-to-fiber insertion loss and no drifts of calibration settings for the initial phase-error compensation since the installation of our switch [33].

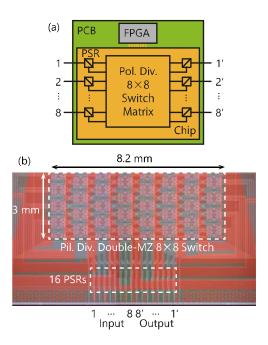

As a next step, we integrated the two double-MZ  $8 \times 8$  switch matrices and 16 on-chip polarization splitter rotators (PSRs) on a single die, as shown in Fig. 6(a). We term this configuration as "on-chip" polarization diversity. The PSR exploits adiabatic

Fig. 7. (a) Measured polarization dependent loss and (b) differential group delay of polarization diversity  $8 \times 8$  switch shown in Fig. 6 at a wavelength of 1550 nm. Path ID means input-output connections. 1: 1 (input) -1' (output), 2: 1–2, ..., 64: 8-8'.

modal conversion and directional coupling in a vertically asymmetric structure [34]. The PSRs at the input port and those at the output ports were placed so as to rotate original polarization by 90° (i.e., the originally TE (TM) mode is converted to TM (TE) mode). This configuration compensates the polarization dependence of input and output fiber coupling efficiency. Fig. 6(b) depicts the fabricated on-chip polarization-diversity double-MZ  $8 \times 8$  switch chip. The switch chip was packaged in the same manner as described in Section III.

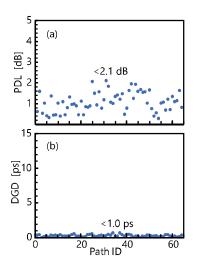

Fig. 7(a) and (b) present the PDL and the DGD of all paths, respectively. The measurement setup is the same as that of the "off-chip" polarization-diversity case. The measured PDL was less than 2.1 dB. We suspect that the residual PDL was caused by variations of the insertion loss and the conversion efficiency of the PSR. The design optimization of the PSR, especially robust design against structural fluctuation, improves the PDL. On the other hand, the DGD is less than 1.0 ps owing to fully integrated optical paths from the PSR and the switch matrix.

#### V. DISCUSSION

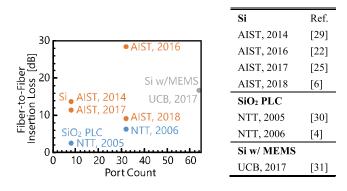

In this section, we discuss the remaining challenges for switch performance improvements and port count expansion. Regarding the fiber-to-fiber insertion loss of the  $32 \times 32$  switch, we believe that about 6 dB is possible. If we adopt the latest fabrication process, propagation loss of less than 0.5 dB/cm is achievable, resulting in 2 dB loss reduction. Moreover, there is potential for coupling loss reduction because the numerical simulation shows 0.6 dB/facet coupling [21]. Fig. 8 compares the fiber-to-fiber insertion losses of the multi-port switches fabricated on the integrated waveguide platforms. We note that 6 dB insertion loss is comparable with that of the silica PLC platform. For further loss reduction, integration with semiconductor optical amplifiers is an available option [35].

To realize larger port counts, one of the limiting factors is fan-out of the electrodes. For example, if we simply expanded the  $32 \times 32$  switch to a  $64 \times 64$  switch, we would have to handle

Fig. 8. Comparison of fiber-to-fiber insertion losses.

8320 electrodes, which is much larger than that of the latest CPU packaging (LGA 3647). Therefore, some technology that reduces the number of electrodes, such as dynamic control using diodes [36] or integration with an address decoder, is necessary.

### VI. CONCLUSION

We have reviewed the switching performance of strictly nonblocking silicon photonics switches. The largest port count 32  $\times$  32 PILOSS switch, fully packaged and controlled, exhibited an average fiber-to-fiber insertion loss of 10.8 dB with a standard deviation of 0.54 dB. In the double-MZ 8  $\times$  8 switch, -30 dB crosstalk bandwidth was wider than 100 nm. Regarding polarization insensitivity, we demonstrated 0.5 dB PDL in the polarization diversity 8  $\times$  8 switch with fiber-based PBSs, and less than 1.0 ps DGD in the fully integrated polarization diversity 8  $\times$  8 switch. We pointed out that further port count expansion requires the reduction of the number of electrode pads on the chip. As mentioned above, some technological challenges remain to be addressed for practical applications. However, we expect that silicon photonics switches offer new solutions for future energy efficient networks.

#### REFERENCES

- [1] Calient, [Online]. Available: https://www.calient.net/

- [2] Polatis, [Online]. Available: https://www.polatis.com/

- [3] Cisco, Global Cloud Index, 2016–2021. [Online]. Available: https://www. cisco.com/c/en/us/solutions/collateral/service-provider/global-cloudindex-gci/white-paper-c11-738085.html

- [4] S. Sohma, T. Watanabe, N. Ooba, M. Itoh, T. Shibata, and H. Takahashi, "Silica-based PLC type 32 × 32 optical matrix switch," in *Proc. Eur. Conf. Opt. Commun.*, Cannes, France, 2006, Paper Tu.4.4.3.

- [5] B. G. Lee, "Photonic switch fabrics in computer communications systems," in *Proc. Opt. Fiber Commun. Conf.*, San Diego, CA, USA, 2018, Paper Th3C.3.

- [6] K. Suzuki *et al.*, "Low-insertion-loss and power-efficient 32 × 32 silicon photonics switch with extremely high-Δ silica PLC connector," *J. Lightw. Technol.*, vol. 37, no. 1, pp. 116–122, Jan. 2019.

- [7] T. J. Seok, K. Kwon, J. Henriksson, J. Luo, and M. C. Wu, "Wafer-scale silicon photonic switches beyond die size limit," *Optica*, vol. 6, no. 4, pp. 490–494, 2019.

- [8] Q. Cheng, S. Rumley, M. Bahadori, and K. Bergman, "Photonic switching in high performance datacenters [Invited]," *Opt. Express*, vol. 26, no. 12, pp. 16022–16043, 2018.

- [9] L. Qiao, W. Tang, and T. Chu, "32 × 32 silicon electro-optic switch with built-in monitors and balanced-status units," *Sci. Rep.*, vol. 7, 2017, Art. no. 42306.

- [10] S. Nakamura, S. Takahashi, M. Sakauchi, T. Hino, M.-B. Yu, and G.-Q. Lo, "Wavelength selective switching with one-chip silicon photonic circuit including 8 × 8 matrix switch," in *Proc. Opt. Fiber Commun. Conf. Exhib.*, Los Angeles, CA, USA, 2011, Paper OTuM2.

- [11] L. Chen and Y.-K. Chen, "Compact, low-loss and low-power 8 × 8 broadband silicon optical switch," *Opt. Express*, vol. 20, no. 17, pp. 18977– 18985, 2012.

- [12] T. Tanemura, L. Langouche, and Y. Nakano, "Strictly non-blocking 8 × 8 silicon photonic switch based on optical phased array," in *Proc. Eur. Conf. Exhib. Opt. Commun.*, Valencia, Spain, 2015, Paper P.2.9.

- [13] M.-J. Kwack, T. Tanemura, A. Higo, and Y. Nakano, "Monolithic InP strictly non-blocking 8 × 8 switch for high-speed WDM optical interconnection," *Opt. Express*, vol. 20, no. 27, pp. 28734–28741, 2012.

- [14] R. Spanke, "Architectures for large nonblocking optical space switches," *IEEE J. Quantum Electron.*, vol. 22, no. 6, pp. 964–967, Jun. 1986.

- [15] Q. Cheng, A. Wonfor, J. L. Wei, R. V. Penty, and I. H. White, "Lowenergy, high-performance lossless 8 × 8 SOA switch," in *Proc. Opt. Fiber Commun. Conf.*, Los Angeles, CA, USA, 2015, Paper Th4E.6.

- [16] T. Shimoe, K. Hajikano, and K. Murakami, "Path-independent insertion loss optical space switch," in *Proc. Opt. Fiber Commun.*, Reno, NV, USA, 1987, Paper WB2.

- [17] R. Konoike *et al.*, "SiN/Si double-layer platform for ultralow-crosstalk multiport optical switches," *Opt. Express*, vol. 27, no. 15, pp. 21130– 21141, 2019.

- [18] Q. Cheng *et al.*, "Ultralow-crosstalk, strictly non-blocking microringbased optical switch," *Photon. Res.*, vol. 7, no. 2, pp. 155–161, 2019.

- [19] L. Chien-Chun and R. A. Thompson, "The double-layer network architecture for photonic switching," J. Lightw. Technol., vol. 12, no. 8, pp. 1482–1489, Aug. 1994.

- [20] K. Suzuki et al., "Low-loss, low-crosstalk, and large-scale silicon photonics switch," in Proc. Opt. Fiber Commun. Conf., San Diego, CA, USA, 2019, Paper M3B.2.

- [21] J. Hasegawa et al., "32-port 5.5%-Δ silica-based connecting device for low-loss coupling between SMFs and silicon waveguides," in Proc. Opt. Fiber Commun. Conf., San Diego, CA, USA, 2018, Paper Tu3A.4.

- [22] K. Tanizawa et al., "Silicon photonic 32 x 32 strictly-non-blocking blade switch and its full path characterization," in Proc. 21st Optoelectronics Commun. Conf., Int. Conf. Photon. Switching, Niigata, Japan, 2016, Paper PD2–3.

- [23] S. Suda *et al.*, "Fast and accurate automatic calibration of a 32 × 32 silicon photonic strictly-non-blocking switch," in *Proc. Adv. Photon. (IPR, NOMA, Sensors, Networks, SPPCom, PS)*, New Orleans, LA, USA, 2017, Paper PTu3C.5.

- [24] T. Goh, A. Himeno, M. Okuno, H. Takahashi, and K. Hattori, "Highextinction ratio and low-loss silica-based 8 × 8 strictly nonblocking thermooptic matrix switch," *J. Lightw. Technol.*, vol. 17, no. 7, pp. 1192–1199, Jul. 1999.

- [25] K. Suzuki et al., "2.5-dB loss, 100-nm operating bandwidth, and low power consumption strictly-non-blocking 8 × 8 Si switch," in Proc. Eur. Conf. Opt. Commun., Gothenburg, Sweden, 2017, Paper Tu.1.C.2.

- [26] S. Han, T. J. Seok, K. Yu, N. Quack, R. S. Muller, and M. C. Wu, "50 × 50 polarization-insensitive silicon photonic MEMS switches: design and experiment," in *Proc. Eur. Conf. Exhib. Opt. Commun.*, Düsseldorf, Germany, 2016, Paper Th.3.A.5.

- [27] K. Suzuki et al., "Polarization-diversity 32 x 32 Si photonics switch with non-duplicate diversity circuit in double-layer platform," in *Proc. Opt. Fiber Commun. Conf.*, San Diego, CA, USA, 2019, Paper Th1E.2.

- [28] K. Suzuki *et al.*, "Broadband silicon photonics 8 × 8 switch based on double-Mach–Zehnder element switches," *Opt. Express*, vol. 25, no. 7, pp. 7538–7546, 2017.

- [29] K. Suzuki et al., "Ultra-compact 8 × 8 strictly-non-blocking Siwire PILOSS switch," Opt. Express, vol. 22, no. 4, pp. 3887–3894, 2014.

- [30] T. Watanabe, S. Sohma, T. Goh, T. Shibata, and H. Takahashi, "Compact 8 × 8 silica-based PLC switch with compressed arrangement," in *Proc. Eur. Conf. Opt. Commun.*, 2005, pp. 991–992.

- [31] T. J. Seok, V. Kopp, D. Neugroschl, J. Henriksson, J. Luo, and M. C. Wu, "High density optical packaging of high radix silicon photonic switches," in *Proc. Opt. Fiber Commun. Conf. Postdeadline Papers*, Los Angeles, CA, USA, 2017, Paper Th5D.7.

- [32] T. Kurosu, T. Inoue, K. Suzuki, S. Suda, and S. Namiki, "High-capacity multi-stage operation of polarization-diversity silicon photonics 8 × 8 optical switch," *J. Lightw. Technol.*, vol. 37, no. 1, pp. 131–137, Jan. 2019.

- [33] National Institute of Advanced Industrial Science and Technology. Actual Operation of New Optical Network Using Silicon Photonics has Begun. Tsukuba, Japan: National Institute of Advanced Industrial Science and Technology (AIST), Sep. 2017. [Online]. Available: https://www.aist.go. jp/aist\_e/list/latest\_research/2019/20190409/en20190409.html

- [34] D. Dai and J. E. Bowers, "Novel concept for ultracompact polarization splitter-rotator based on silicon nanowires," *Opt. Express*, vol. 19, no. 11, pp. 10940–10949, 2011.

- [35] T. Matsumoto *et al.*, "Hybrid-integration of SOA on silicon photonics platform based on flip-chip bonding," *J. Lightw. Technol.*, vol. 37, no. 2, pp. 307–313, Jan. 2019.

- [36] A. Ribeiro and W. Bogaerts, "Thermo-optical phase shifter with integrated diodes for multiplexed control," in *Proc. Opt. Fiber Commun. Conf.*, San Diego, CA, USA, 2018, Paper Th2A.4.

**Keijiro Suzuki** received the B.E. and M.E. degrees from the Department of Electrical and Electronic Engineering, Shizuoka University, Hamamatsu, Japan, in 2004 and 2006, respectively. He received the Ph.D. degree from the Yokohama National University (YNU), Yokohama, Japan, in 2011.

After spending two years at Sumitomo Osaka Cement Co., Ltd., Tokyo, Japan, he joined the Department of Electrical and Computer Engineering, YNU, in 2008. After spending one year at YNU as a Postdoctoral Fellow, he joined the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan, in 2012. His research interests include photonic integrated circuits, nanophotonics, and nonlinear optics.

Dr. Suzuki was awarded the Research Fellowship for Young Scientists by Japan Society for the Promotion of Science (JSPS). He is a member of the OSA, the IEEE Photonics Society, the IEICE, and the JSAP.

**Ryotaro Konoike** received the M.S. and Ph.D. degrees from the Department of Electronic Science and Engineering, Kyoto University, Kyoto, Japan, in 2014 and 2017, respectively.

He is currently a Researcher with the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan. His research interests include optical switches and integrated silicon optical circuits.

Satoshi Suda was born in Kobe, Japan, in 1979. He received the B.S., M.S., and Ph.D. degrees in science and engineering from the Tokyo Institute of Technology, Yokohama, Japan, in 2003, 2004, and 2008, respectively.

He joined the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, in 2008, where he has been engaged in the research on silicon photonics circuits.

**Hiroyuki Matsuura** received the B.S. and M.S. degrees in electrical engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 1978 and 1980, respectively.

In 1980, he joined the Yokogawa Electric Corporation, Tokyo, Japan, where he was engaged in the research on medical imaging apparatuses, high-frequency circuits, and measuring instruments. From 1990 to 1992, he was a Visiting Scholar with the Stanford University, Stanford, CA, USA. From 1992 to 2011, he was with the Yokogawa Electric Corporation and was engaged in the technology development of high-speed, high-frequency circuits with compound semiconductors, and business development for optical communication modules. Since 2011, he has been a Senior Researcher with the National Institute of Advanced Industrial Science and Technology, Tsukuba, Japan, and involved in the development of control circuits and units for next-generation optical communication devices and systems. In 2017, he established HikariPath Communications Co., Ltd., which provides low-latency, high-resolution, and bi-directional video transmission services using optical technologies.

Mr. Matsuura is a member of the Institute of Electronics, Information and Communication Engineers (ICICE). He was a recipient of the 1988 Society of Instrument Control Engineers (SICE) Best Paper Award.

**Shu Namiki** received the M.S. and Dr.Sci. degrees in applied physics from the Waseda University, Tokyo, Japan, in 1988 and 1998, respectively.

From 1988 to 2005, he was with the Furukawa Electric Co., Ltd., Tokyo, Japan, where he developed award-winning high-power pump lasers and patented multiwavelength pumped-fiber Raman amplifiers. From 1994 to 1997, he was a Visiting Scientist with the Massachusetts Institute of Technology, Cambridge, MA, USA, where he studied mode-locked fiber lasers and ultra-short pulses in fibers. In 2005, he moved to the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan, where he has served as Chair of Executive Committee of a ten-year national project called "Vertically Integrated Center for Technologies of Optical Routing toward Ideal Energy Savings (VICTORIES)" in collaboration with ten telecom-related companies, and is currently Deputy Director of the Electronics and Photonics Research Institute, Tsukuba, Japan. He has authored or coauthored more than 500 conference presentations, papers, book chapters, articles, and patents. His current research interests include software-defined dynamic optical path networking and their enabling devices such as nonlinear fiber-optics and silicon photonics.

Dr. Namiki was an Associate Editor and Advisory Editor of the journal *Optics Express* and the Co-Editor-in-Chief of *IEICE Transactions on Communications*. He was on the technical committee for OFC, ECOC, CLEO, OECC, and OAA, and served as Program Co-Chair of OFC 2015 and General Co-Chair of OFC 2017. He is a Fellow of the Optical Society of America. He is a member of the Institute of Electronics, Information, and Communication Engineers, and the Japan Society of Applied Physics.

**Hitoshi Kawashima** received the Ph.D. degree in chemistry from the Kyoto University, Kyoto, Japan, in 1993.

He was a Postdoctoral Fellow at MIT from 1993 to 1995, where he worked on pulse-shaping technology for femtosecond optical pulses. In 1995, he joined the Electrotechnical Laboratory. In 2001, the Electrotechnical Laboratory and other fourteen national research laboratories were reorganized and renamed as the National Institute of Advanced Industrial Science and Technology (AIST). Since 2008, he has worked on silicon photonics and its applications to circuit switches. His research interests include integrated optics, nonlinear optics, and diagnostic techniques with ultrashort optical pulses.

Dr. Kawashima is a member of OSA, IEICE, and Japan Society of Applied Physics.

**Kazuhiro Ikeda** received the B.E. and M.E. degrees in precision science from the Osaka University, Suita, Japan, in 1998 and 2000, respectively, and the Ph.D. in electrical engineering (photonics) from the University of California, San Diego (UCSD), La Jolla, CA, USA, in 2008. His doctoral thesis was on nonlinear optical responses in silicon nitride and amorphous silicon and developed sidewall corrugated waveguide devices, all for silicon photonics applications.

From 2000 to 2004, he was with the Furukawa Electric Co., Ltd., Tokyo, Japan, and worked on polarization controllers and polarization mode dispersion compensators for optical fiber communications. In 2009, he joined the Graduate School of Materials Science, Nara Institute of Science and Technology (NAIST), Ikoma, Japan, as an Assistant Professor, where he studied opto-spintronics and plasmonic microresonators for semiconductor lasers. Since 2014, he is a Research Group Leader with the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan. His research interests include silicon photonic integrated circuits and hybrid nanophotonics on silicon.

Dr. Ikeda is a senior member of the OSA and a member of the IEICE, JSAP, and IEEE Photonics Society.