## **Grand Valley State University** ScholarWorks@GVSU

**Masters Theses**

Graduate Research and Creative Practice

4-2014

# Low Noise NMOS Imager Fabrication with a Study on the Effect of Photodiode Shape on Dark Current

Steven Taylor Grand Valley State University

Follow this and additional works at: http://scholarworks.gvsu.edu/theses

Part of the Engineering Commons

#### Recommended Citation

Taylor, Steven, "Low Noise NMOS Imager Fabrication with a Study on the Effect of Photodiode Shape on Dark Current" (2014). Masters Theses. 710.

http://scholarworks.gvsu.edu/theses/710

This Thesis is brought to you for free and open access by the Graduate Research and Creative Practice at ScholarWorks@GVSU. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@GVSU. For more information, please contact scholarworks@gvsu.edu.

## Low Noise NMOS Imager Fabrication with a Study on the Effect of Photodiode Shape on Dark Current

Steven Taylor

A Thesis Submitted to the Graduate Faculty of

GRAND VALLEY STATE UNIVERSITY

In

Partial Fulfillment of the Requirements

For the Degree of

Masters of Science

Electrical and Computer Engineering

April 2014

### Acknowledgements

I would like to thank my advisor, Dr. Jiao, for her support, guidance, and wealth of knowledge throughout this project. Dr. Dunne and Dr. Jack for their feedback and assistance. I would also like to thank Grand Valley for supplying the resources to make this project possible.

In addition, many thanks to Jeff Johnson for his guidance in the cleanroom and his answers to my endless questions. Also, thanks to Ron Grew for his support and help throughout the project.

#### Abstract

The purpose of this project was to fabricate a low noise N-type Metal-Oxide-Semiconductor (NMOS) imager in the Grand Valley State University (GVSU) Cleanroom with a focus on reducing pixel dark current. Previous research suggests Photodiode (PD) shape affects dark current and charge transfer characteristics of the pixel. Five PD shapes were designed to determine an optimized pixel shape with respect to dark performance. PN junction PDs with the Three Transistor (3T) pixel architecture were found to be the most suitable for imager fabrication in the GVSU cleanroom. The integrated circuit layout of several 8x8 pixel arrays was designed to test the influence of PD shape on dark current. The fabricated PDs exhibited dark current in the range of 9-18uA/cm<sup>2</sup>. The results indicate PDs with "rounder" geometry exhibit improved dark response; however, small saturation to cutoff current ratios prevented imager functionality. Improved charge transfer as a result of triangular PD shape was suggested but may have been masked by higher dark currents in these shapes.

A low noise Voltage and Sample and Acquisition Controller (VSAC) was developed to capture the output from the imager die and transfer the data to a computer. The VSAC was designed for flexible timing and voltage control while exhibiting low noise. Analysis with a logic analyzer verified timing flexibility which allowed the integration, reset, and other control pulses to be optimized for the application. Reset voltage control circuitry allowed a wide range of analog voltages to be supplied to the imager reset transistors. This prevented image lag due to incomplete reset. The noise performance of the VSAC was characterized by sampling a known voltage and observing the output deviation. With an output voltage accuracy of 99 percent to the input signal and less than 3.6 mV<sub>RMS</sub> output noise, the VSAC exhibited excellent low noise operation.

## **Table of Contents**

| 1 | Intro | oduction                                      | 13 |

|---|-------|-----------------------------------------------|----|

|   | 1.1   | Previous Research                             | 14 |

|   | 1.2   | Benchmark                                     | 16 |

|   | 1.3   | Purpose of Current Research                   | 16 |

| 2 | The   | ory                                           | 18 |

|   | 2.1   | MOS Imagers                                   | 18 |

|   | 2.1.  | 1 Photodiode Operation                        | 20 |

|   | 2.1.  | Performance Parameters                        | 23 |

|   | 2.1.  | Noise in NMOS Imagers                         | 26 |

|   | 2.2   | Photodiode Dark Current                       | 29 |

|   | 2.2.  | 1 Mechanisms                                  | 29 |

|   | 2.2.  | 2 Influence of Charge Traps on Dark Current   | 30 |

|   | 2.2.  | 3 Effect of PD Shape on Dark Current          | 30 |

| 3 | Exp   | erimental Method                              | 33 |

|   | 3.1   | Integrated Pixel Array Design                 | 33 |

|   | 3.1.  | 1 Functional Requirements                     | 33 |

|   | 3.1.  | 2 Integrated Circuit Layout                   | 34 |

|   | 3.1.  | 3 Calculations and Simulations                | 37 |

|   | 3.1.  | 4 IC Testing                                  | 41 |

|   | 3.2   | Control Circuit Design                        | 43 |

|   | 3.2.  | 1 Functional Requirements                     | 43 |

|   | 3.2.  | 2 Hardware and Simulations                    | 44 |

|   | 3.2.  | 3 Testing                                     | 48 |

|   | 3.3   | Fabrication Process                           | 49 |

|   | 3.3.  | 1 Limitations of the GVSU Fabrication Process | 50 |

|   | 3.3.  | 2 Testing                                     | 53 |

| 4 | Res   | ults                                          | 54 |

|   | 4.1   | Fabrication Results                           | 54 |

|   | 4.1.  | 1 Diffusion                                   | 54 |

|   | 4.1.  | 2 Gate Oxidation                              | 58 |

|   | 4.1.  | 3 Via One                                     | 60 |

|    | 4.1.4     | Metal One                                    | 61  |

|----|-----------|----------------------------------------------|-----|

|    | 4.1.5     | Spin on Glass                                | 62  |

|    | 4.1.6     | Via Two                                      | 62  |

|    | 4.1.7     | Metal Two                                    | 63  |

| 4  | .2 Pho    | todiode Characteristics                      | 63  |

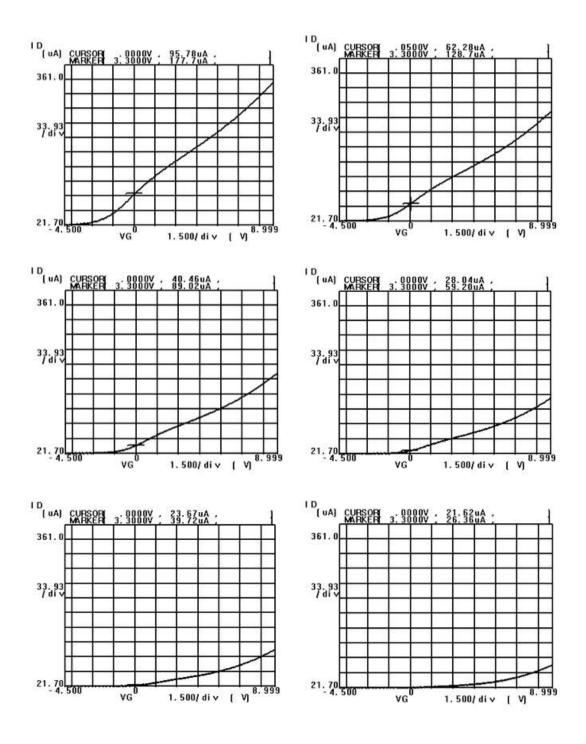

|    | 4.2.1     | Dark Currents                                | 64  |

|    | 4.2.2     | Illuminated Currents                         | 66  |

| 4  | .3 Trai   | nsistor Operation                            | 67  |

| 4  | .4 VS     | AC Verification                              | 71  |

|    | 4.4.1     | Image Readout                                | 74  |

|    | 4.4.2     | Readout Characterization                     | 76  |

| 5  | Conclus   | ions                                         | 82  |

| 6  | Reference | ces                                          | 83  |

| Ap | pendix A  | Semiconductor Physics Highlights             | 86  |

| A  | A.1 PN    | Junctions                                    | 86  |

|    | A.1.1     | Built in Potential                           | 86  |

|    | A.1.2     | Junction Width                               | 86  |

|    | A.1.3     | Junction Capacitance                         | 88  |

|    | A.1.4     | Diode Current                                | 89  |

| A  | A.2 Opt   | oelectronics                                 | 90  |

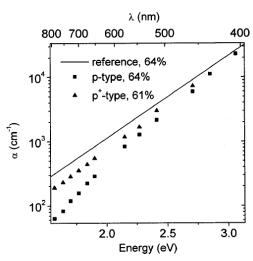

|    | A.2.1     | Absorption Coefficient and Penetration Depth | 91  |

|    | A.2.2     | Optical Generation Rate                      | 91  |

|    | A.2.3     | Photo-generated Current                      | 92  |

| A  | A.3 MO    | SFET Parameter Estimation                    | 92  |

|    | A.3.1     | Threshold Estimation                         | 92  |

|    | A.3.2     | Body biasing                                 | 94  |

| Ap | pendix B  | Schematics and Board Layouts                 | 95  |

| E  | 3.1 VS    | AC                                           | 95  |

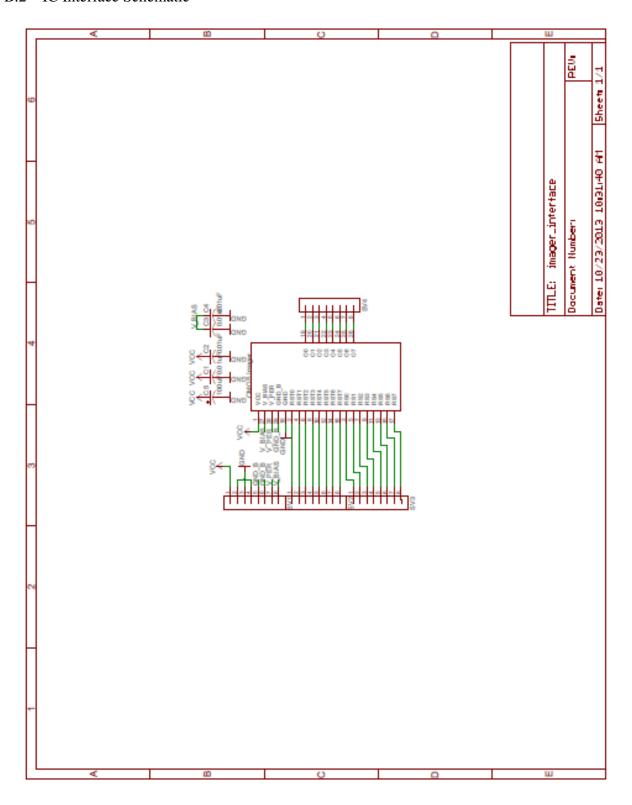

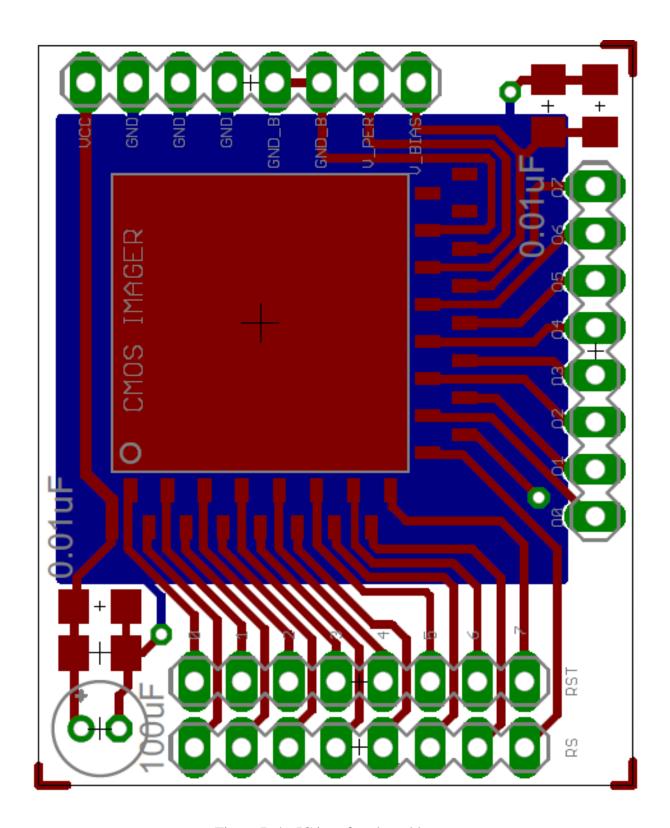

| E  | 3.2 IC I  | nterface Schematic                           | 97  |

| A  | Appendix  | C Code                                       | 99  |

| C  | C.1 mai   | n.c                                          | 99  |

| (  | 12 com    | amon variables h                             | 103 |

| C.3 | custom_functions.c | 104 |

|-----|--------------------|-----|

| C.4 | pin functions.c    | 106 |

## **Table of Figures**

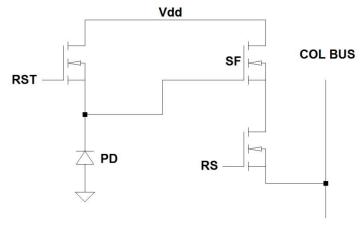

| Figure 2.1 - 3T APS Pixel Circuit                                                         | 18 |

|-------------------------------------------------------------------------------------------|----|

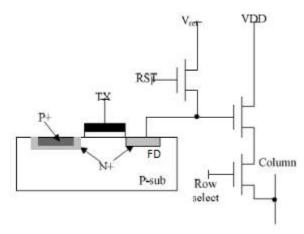

| Figure 2.2 - 4T pixel circuit.                                                            | 19 |

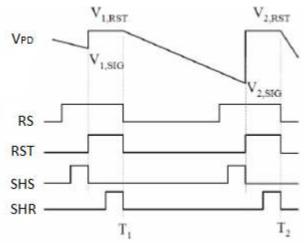

| Figure 2.3 - Timing diagram of MOS imager [30].                                           | 20 |

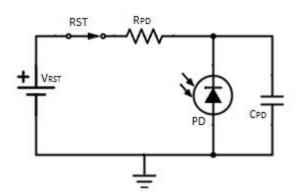

| Figure 2.4 - Simplified circuit for photon flux integrating mode operation.               | 21 |

| Figure 2.5 - Voltage dependence of illumination level on PD [18]                          | 22 |

| Figure 2.6 - Dark current response of PD in photon flux integrating mode [18].            | 22 |

| Figure 2.7 - Tapered PD design and E-field gradient [14].                                 | 31 |

| Figure 3.1 - Five PD designs to determine effect of PD shape on dark current.             | 35 |

| Figure 3.2 - Pixel layout with identified devices and traces.                             | 35 |

| Figure 3.3 - Imager die with type one PDs.                                                | 36 |

| Figure 3.4 - Pixel simulation circuit                                                     | 40 |

| Figure 3.5 - Simulation results of 3T pixel.                                              | 41 |

| Figure 3.6 - Test die for fabrication characterization.                                   | 42 |

| Figure 3.7 - Block diagram of the VSAC.                                                   | 43 |

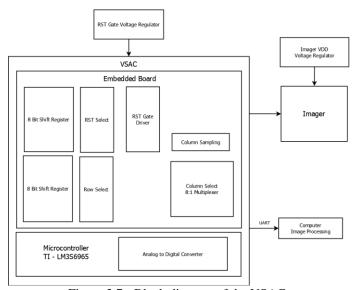

| Figure 3.8 - Schematic designed for testing noise performance of sample and hold circuits | 46 |

| Figure 3.9 - Noise response of sample and hold simulation.                                | 47 |

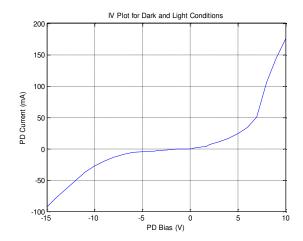

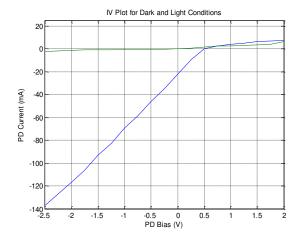

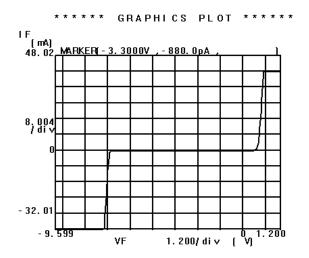

| Figure 3.10 - IV characteristics of dark pn junction.                                     | 52 |

| Figure 3.11 - IV characteristics of illuminated pn junction.                              | 52 |

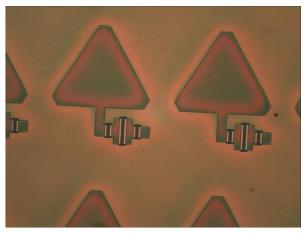

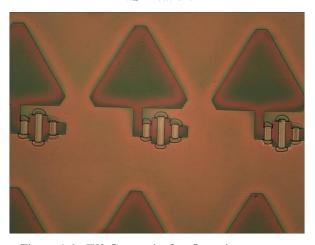

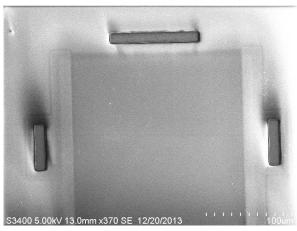

| Figure 4.1 - Diffusion pattern of W5 for 55s under 10x optical magnification              | 56 |

| Figure 4.2 - W2 diffusion pattern after 9min 45s etch time                                | 56 |

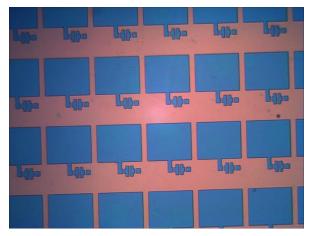

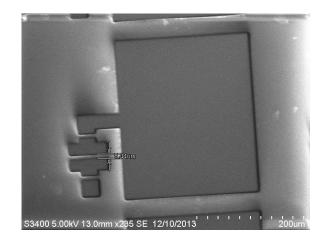

| Figure 4.3 - SEM image of rectangular pixel after diffusion etch.                         | 57 |

| Figure 4.4 - Transistor source and drain patterns after diffusion etch.                   | 57 |

| Figure 4.5 - W2 Gate development under 10x magnification.                                 | 58 |

| Figure 4.6 - W2 Gate etch after five minutes                                              | 58         |

|-------------------------------------------------------------------------------------------|------------|

| Figure 4.7 - W1 gate pattern after gate etch.                                             | 58         |

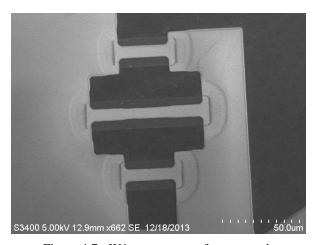

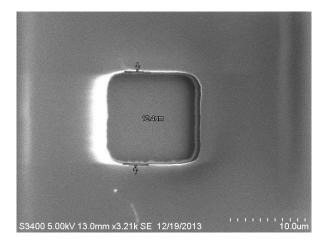

| Figure 4.8 - W6 via one development.                                                      | 60         |

| Figure 4.9 - W6 completed dry oxide etch and incomplete FOX etch after two min 30s e      | etch 60    |

| Figure 4.10 - W6 PD via etch showing completed vias                                       | 61         |

| Figure 4.11 - W6 via one measurement.                                                     | 61         |

| Figure 4.12 - W2 metal one development.                                                   | 61         |

| Figure 4.13 - W2 metal one etch.                                                          | 62         |

| Figure 4.14 - W5 via two pattern.                                                         | 62         |

| Figure 4.15 - W1 metal two formation. Traces exhibit no open circuits                     | 63         |

| Figure 4.16 - W1 unremoved aluminum.                                                      | 63         |

| Figure 4.17 - Diode dark current with respect to bias voltage of a square PD on W2        | 65         |

| Figure 4.18 - Diode illuminated current with respect to bias voltage of a square PD on v  | wafer      |

| two                                                                                       | 65         |

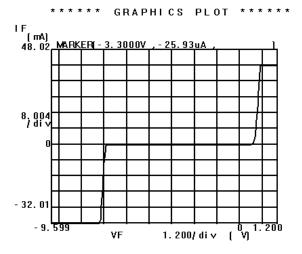

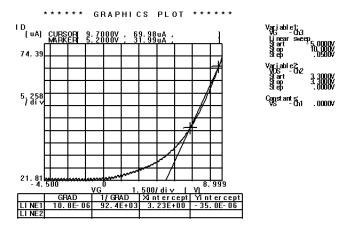

| Figure 4.19 - MOSFET characteristic curve obtained from wafer two.                        | 68         |

| Figure 4.20 - MOSFET transfer curve obtained from wafer two.                              | 68         |

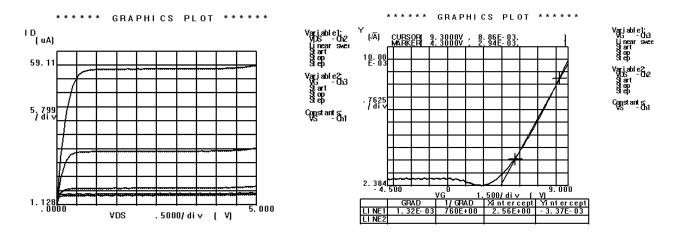

| Figure 4.21 - Effect of bulk biasing in 0.1V increments on a transistor from wafer one fa | abrication |

| one                                                                                       | 70         |

| Figure 4.22 - Scaled view of 0.5V bulk biased TX.                                         | 71         |

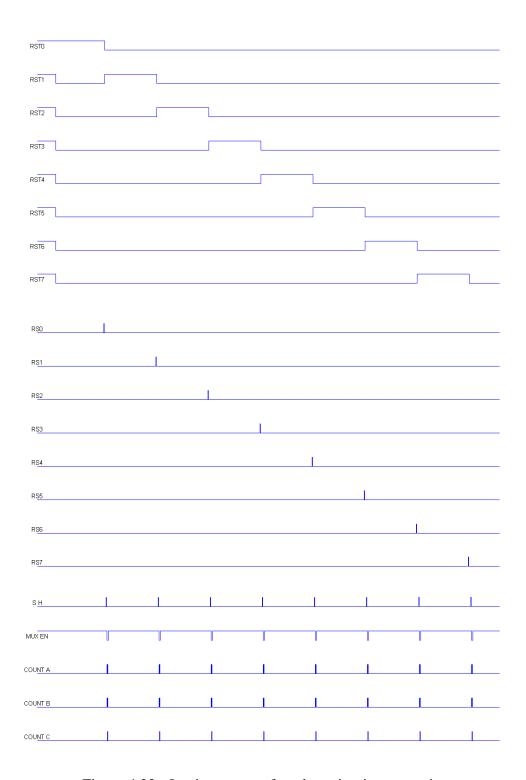

| Figure 4.23 - Logic capture of readout circuitry operation.                               | 72         |

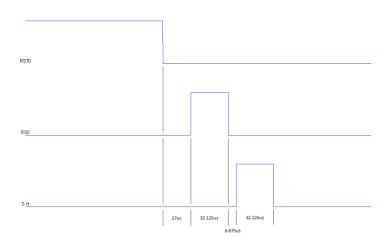

| Figure 4.24 - RST0, RS0, and SH pulse details                                             | 73         |

| Figure 4.25 - Counter operation during readout.                                           | 73         |

| Figure 4.26 - Test circuit for PD characterization.                                       | 74         |

| Figure 4.27 - Square PD voltage decay while illuminated.                                       | . 75  |

|------------------------------------------------------------------------------------------------|-------|

| Figure 4.28 - Square PD voltage decay in dark conditions                                       | . 75  |

| Figure 4.29 - Voltage response of PD shapes with respect to light intensity.                   | . 79  |

| Figure 4.30 - Standard Deviation of voltage response of PD shapes with respect to light intens | sity. |

|                                                                                                | . 81  |

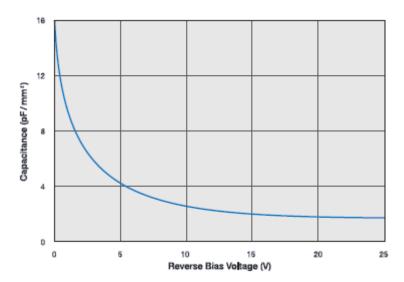

| Figure A.1 - PD Capacitance with respect to reverse bias voltage [34].                         | . 88  |

| Figure A.2 - Absorption coefficient of various wavelengths in Silicon [32]                     | . 91  |

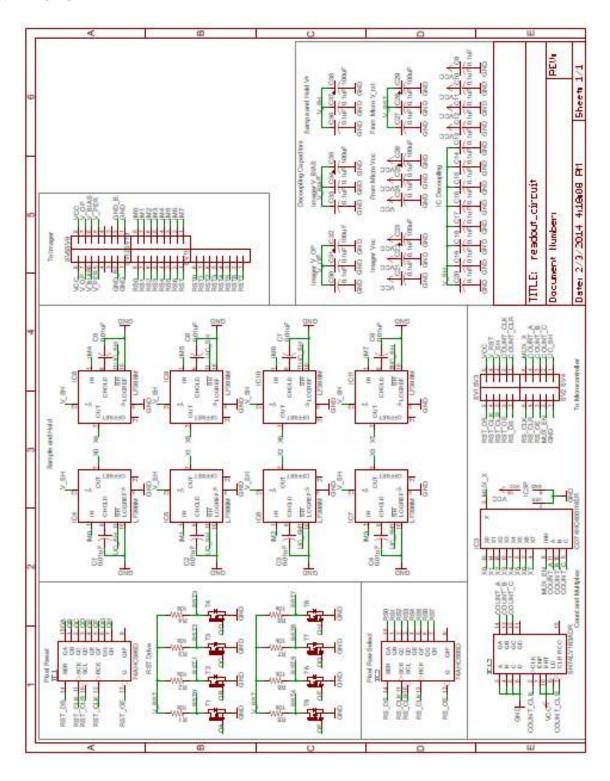

| Figure B.1 - VSAC schematic layout.                                                            | . 95  |

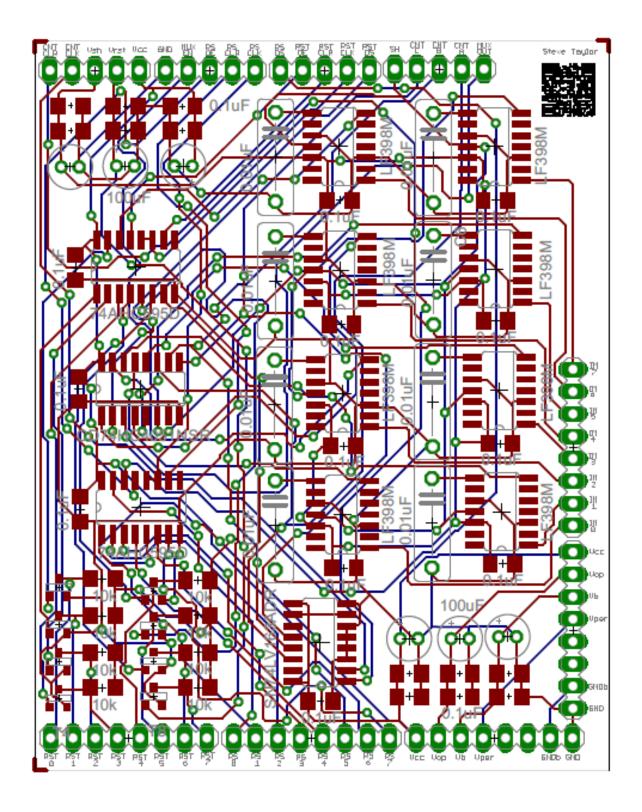

| Figure B.2 - VSAC embedded board layout.                                                       | . 96  |

| Figure B.3 - IC interface schematic layout.                                                    | . 97  |

| Figure B.4 - IC interface board layout.                                                        | . 98  |

## **Table of Tables**

| Table 1.1 - Comparison between CMOS imagers and CCD photodetectors                  | 13 |

|-------------------------------------------------------------------------------------|----|

| Table 3.1 - Functional requirements of the integrated PD arrays.                    | 33 |

| Table 3.2 - MOSFET threshold parameter estimates                                    | 38 |

| Table 3.3 - Parameters for estimating PD photocurrent.                              | 39 |

| Table 3.4 - Processing stages in imager fabrication in the GVSU cleanroom           | 49 |

| Table 4.1 - Wafer resistivity and circuit pattern.                                  | 54 |

| Table 4.2 - Fabrication two wet oxide thicknesses (Å) after initial oxidation       | 55 |

| Table 4.3 - Measured gate oxide thicknesses Å                                       | 59 |

| Table 4.4 - Normalized value of dark current density from wafer one fabrication two | 65 |

| Table 4.5 - Dark current and Dark Current Density Averages from W2                  | 66 |

| Table 4.6 - Measured PD capacitance at 3.3V reverse bias.                           | 76 |

| Table 4.7 - Input and Output voltage readings of readout circuitry                  | 77 |

| Table 4.8 - Voltage decay in dark conditions of PD shapes.                          | 80 |

| Table A.1 - Predicted threshold shift with respect to applied source to bulk bias   | 94 |

#### **Abbreviations**

3T – Three Transistor

4T – Four Transistor

ADC – Analog to Digital Converter

APS – Active Pixel Sensor

BOE - Buffered Oxide Etch

CCD - Charge Coupled Device

CDS – Correlated Double Sampling

CMOS - Complementary Metal-Oxide-Semiconductor

DDS – Delta Difference Sampling

EHP - Electron-Hole Pair

ENIG - Electroless Nickel Immersion Gold

FD – Floating Diffusion

FF - Fill Factor

FOX - Field Oxide

IC – Integrated Circuit

MUX – Multiplexor

NMOS – N-type Metal Oxide Semiconductor

PD – Photodiode

PPD – Pinned Photodiode

PPS – Passive Pixel Sensor

RS – Row Select

RST – Reset

SEM – Scanning Electron Microscope

SF – Source-Follower

SOG – Spin on Glass

VSAC - Voltage and Sample Acquisition Controller

#### 1 Introduction

Electronic cameras have traditionally been fabricated in one of two ways. The traditional Charge-Coupled Device (CCD) photodetector was first conceptualized in the 1970's at Bell Laboratories [1]. The second type of photodetector is the Complementary Metal-Oxide-Semiconductor (CMOS) imager. CMOS imagers are similar to CCDs in that they are based on MOS technology; however, the integration and charge transfer circuitry of the CMOS imager are implemented locally at each pixel allowing for individual pixel referencing. Although CMOS imagers were conceptualized around the same time period as CCDs, CMOS imagers did not see wide adoption until the late 1990s [2]. The pixel architecture of the CMOS imager requires smaller feature than CCD imagers for practical implementation. As trends in Integrated Circuit (IC) technology allowed for smaller features to be reliably fabricated, the realization of practical CMOS imagers became possible.

The different imagers exhibit different device characteristics. Table 1.1 shows the advantages of each type of imager as compared to the other [2]. The lower power consumption and lower cost of CMOS imagers has led to a significant effort in improving the quality of images obtained with CMOS technology and nearly ubiquitous adoption of the CMOS imager in consumer electronics.

Table 1.1 - Comparison between CMOS imagers and CCD photodetectors.

| CMOS Imagers                            | CCDs               |

|-----------------------------------------|--------------------|

| Power consumption                       | Sensitivity        |

| Fabrication cost                        | Quantum efficiency |

| On chip functionality                   | Noise              |

| Miniaturization                         | Dynamic Range      |

| Random access of image data             | Image Quality      |

| Selective readout mechanism             |                    |

| High speed imaging                      |                    |

| Avoidable blooming and smearing effects |                    |

Unlike CCDs, CMOS imagers can be fabricated in a standard CMOS process so the fabrication cost, integration density, and on chip functionality are improved over CCDs.

Currently, the best performing CMOS imagers are fabricated in a non-standard CMOS process to utilize the Pinned Photodiode (PPD) structure [3]. The PPD exhibits low dark current (current that flows through the diode under no illumination), but because it cannot be fabricated in a standard process, the realization of a high performance CMOS imager fabricated in a standard process has significant cost saving implications.

In CMOS imagers the output voltage is ideally directly proportional to the level of irradiation incident to the Photodiode (PD). However, in real devices, circuit noise introduces output variability that leads to degradation of image quality. Although the readout and amplification circuitry lead to noise in CMOS imagers, the light sensing element sets the fundamental limit on image quality in CMOS imagers [4]. Typically, a PD or some variation thereof is used as the light sensing element, and the optimization of such a device can greatly affect the overall imager performance. The dark current is the most significant source of noise during the integration period [5]. Because of this, the mitigation of the dark current in CMOS imagers can lead to substantial improvements in image quality.

#### 1.1 Previous Research

Several strategies have been applied to the fabrication of CMOS imagers with the intention of reducing dark current. In response to the findings that a narrower PD junction results in reduced dark current, Ji and Abshire implemented a pixel biasing technique intended to reduce the PD junction width [6]. Similarly, the pseudo active pixel developed by Shih and Wu attempted to minimize dark current through the use of a PD operating in photoconductive mode and a scheme to bias the PD near 0V [7]. Wuu *et al* report lower dark current and dark signal

non-uniformity (DSNU) associated with the non-silicide source/drain technique applied to PD structures [8]. Takenaka *et al* were able to reduce dark current to <1nA through gas phase GeO<sub>2</sub> passivation of Ge photodetectors in a waveguide geometry [9].

The majority of dark current in pn-junction PDs is generated in the bird's beak formed at the interface between the Field-Oxide (FOX) and the doped region. Wu *et al* proposed two alternative structures to minimize dark current generated at the PD periphery as well as minimize surface damage during implantation [10]. The proposed designs resulted in decreased dark current and improved spectral response as compared to standard PD designs.

Historically, the most successful reduction in dark current in CMOS imagers came from the adaptation of the CCD PPD to CMOS imagers. The PPD uses a thin p<sup>+</sup> layer applied over the n-type doped region to "pin" the PD. The p<sup>+</sup> implant isolates the charge collection region of the PD from the FOX interface and surface traps which results in significant reductions in dark current. Additionally, the PPD improves spectral response and quantum efficiency especially at short (blue) wavelengths [11]. Mheen *et al* report the design considerations of Four Transistor (4T) CMOS imager which require careful design to optimize charge transfer characteristics especially at lower operating voltages [12].

Shcherback, Belenky, and Yadid-Pecht investigated the effect of PD periphery shape on the dark-current [13]. It was found that PD shapes with less acute angles or "rounder" shapes resulted in less dark current than shapes with sharper corners. Sharp corners are more stressed and consequently contain a higher concentration of defects than rounder geometries.

Shin, Park, and Shin modified the shape of the typical square PD to determine how a tapered shape would affect the charge transfer of during imager readout [14]. It was found that a

triangular PD shape created an electric field gradient which assisted charge transfer during readout. The resultant triangular design exhibited 50 percent higher output voltage over the square PD and improved image lag due to faster readout.

#### 1.2 Benchmark

Furtado, Diniz, and de Lima Monteiro published the results of the fabrication of a simple N-type Metal-Oxide-Semiconductor (NMOS) imager with geometries similar to the current design [15]. Although the fabrication process used in the research of Furtado *et al* uses ion implantation (versus spin on dopant in the GVSU process), the presented numbers serve as good benchmark for designs on this scale.

The benchmark design has a minimum feature size of  $10\mu m$  with  $200\mu mx200\mu m$  square PDs and transistors with aspect ratios of 2:1 and 4:1. The PDs have dark current density of  $375 nA/cm^2$  at 5V reverse bias. The pixels are saturated in dark conditions after 48s and the PD has an estimated capacitance of approximately 10pF. The 2:1 transistors a drain current of  $705\mu A$  ( $V_{GS}=V_{DS}=V_{DD}$ ) and a cutoff current of 14pA. The transistors have a gate threshold voltage of 0.65 V.

#### 1.3 Purpose of Current Research

The purpose of this research was to fabricate a low noise NMOS imager implementing a large-area low-dark-current PD in the GVSU cleanroom. In current imagers, pixel dark current is often reduced using PPDs fabricated in a non-standard CMOS process. However, the GVSU process is designed for NMOS fabrication and alternative methods for implementing a pixel with low dark current were explored. The research of Shcherback *et al* demonstrates dark current improvement in relationship to the angle and number of internal and external corners of the PD. In order to maintain a high FF, only PDs with rounded external corners were designed for the

purposes of reducing pixel dark current in the current research. This technique was then applied to the triangular pixel reported by Shin *et al* to determine if rounded PD corners would maintain the voltage elevating effect of the triangular pixel while minimizing dark current.

To ensure the captured imager output was representative of PD array noise rather than readout noise, a low noise readout circuit (VSAC) was developed. The research suggests pixel performance is dependent upon operating voltage and circuit timing. To allow for flexible control of the operational parameters, an off-chip control circuit was devised. Because of the high noise associated with the readout bus of an embedded output, the circuit was designed to sample and hold the imager output as the data is digitized. Typically two sampling circuits and a differential amplifier are implemented at the imager output to facilitate Delta Difference Sampling (DDS) or Correlated Double Sampling (CDS). However, the small array size of the current design minimizes processing requirements which allows these functions to be implemented programmatically. This removes inherent noise in the processing circuits while allowing for greater device flexibility.

#### 2 Theory

#### 2.1 MOS Imagers

In its most basic form, the MOS imager is an array of pixels made up of a photosensitive element, typically a PD, and a charge transfer mechanism. Each pixel outputs a voltage corresponding to the intensity of light incident to the photosensitive element during integration which can be correlated to a black/white level after charge readout. Various filters and lenses can be applied to yield color imagers and improve the quality of the image.

The Passive Pixel Sensor (PPS) was the first conceptualized type of MOS imager. The PPS circuit contains a single transistor which allows this design to have a higher Fill Factor (FF) than Active Pixel Sensors (APS) created with similar design rules. PPS have been demonstrated with dynamic range (DR) of 10<sup>4</sup>-10<sup>5</sup> and noise of 250 electrons root-mean-square (RMS) [16]. The lack of pixel level amplification circuitry in the PPS leads to high readout noise due to noise associated with the capacitance of the column bus.

APS address the noise issues of PPS through the use of amplification, reset, and readout circuitry. The simplest APS designs utilize three transistors; however, more transistors can be added at the expense of FF [17]. Similar to the PPS pixel the Reset (RST) transistor (see Figure

Figure 2.1 - 3T APS Pixel Circuit

2.1) serves to reset the PD voltage to  $V_{DD}$  prior to integration. The Source-Follower (SF) transistor is implemented as a source-follower amplifier with a voltage gain of one which

at the source of the SF transistor is then transferred to the column bus through the operation of the Row Select (RS) transistor. The inclusion of the SF transistor in the three transistor (3T) pixel significantly improves the signal to noise ratio of the APS over the PPS. The SF amplifier allows for nondestructive readout and buffering at the integrating node.

The 4T pixel (Figure 2.2) further improves the noise characteristics of the 3T APS by implementing a PPD along with a charge transfer (TX) transistor. The PPD improves pixel dark current and spectral response by isolating the charge collection from surface and interface traps while

Figure 2.2 - 4T pixel circuit.

capturing charges generated by short wavelengths. In the standard pn-junction PD of the 3T pixel, photo-generated Electron-Hole Pairs (EHP) typically recombine prior to diffusing to the depletion region.

The TX transistor in the 4T pixel with a PPD facilitates charge transfer from the high capacitance of the PPD to a lower capacitance of the Floating Diffusion (FD) node. Thus, the conversion gain of the pixel is large as compared to the 3T pixel which improves imager noise performance. If designed properly, the two junctions in the PPD effectively push integrated charge from the integrating node to the FD when the TX transistor is turned on. If the PPD is designed incorrectly and is not fully depleted during TX operation, remaining electrons generate a thermal (kTC) noise component that degrades image quality [12].

Aside from the operation of the TX transistor in 4T pixels, operation of the 3T and 4T pixel are nearly the same. The timing diagram of a typical 3T pixel is shown in Figure 2.3. Initially, the RST transistor is pulsed to return the voltage across the PD capacitance to the reset voltage. As

Figure 2.3 - Timing diagram of MOS imager [30].

incident light generates EHPs, the voltage across the PD capacitance decreases. The charge stored on the PD capacitance is buffered by the SF amplifier which is then stored as a voltage at the RS node. After the integration period, the RS transistor is pulsed to transfer the charge along the column bus. External to the pixel array, there typically exists sampling circuitry to implement correlated double sampling (CDS) in 4T or delta difference sampling (DDS) in 3T pixels. The sample and hold signal (SHS) and sample and hold reset (SHR) allow for the caputure of two voltage samples which can be fed into a difference amplifier to perform noise cancelling. The final voltage is then digitized via Analog to Digital Converter (ADC) and stored as pixel data.

#### 2.1.1 Photodiode Operation

In CMOS imagers, the PD is operated in one of two modes: photon flux integrating mode or photoconductive mode. The former relies on the PD capacitance to store the integrated charge which is then read at the end of the integration period. In this configuration, the voltage across the PD decreases with respect to integration level. The latter maintains a constant bias across the PD and utilizes the photocurrent to charge an integrating capacitor. This discussion will focus on

photon flux integrating mode as it is most common for MOS imagers and will be utilized in the current research.

In photon flux integrating mode, the PD is first biased to a certain voltage, typically  $V_{DD}$ , and then a switch (RST) disconnects the PD cathode from the power supply. A simplified circuit diagram of this configuration is shown in Figure 2.4 where  $R_{PD}$  is the series resistance of the PD and  $C_{PD}$  is the junction capacitance of the PD.

Figure 2.4 - Simplified circuit for photon flux integrating mode operation.

Initially, the switch is closed and the capacitive PD node is charged to  $V_{RST}$ . Wekler *et al* explored the operation of such a circuit and the analysis is summarized in the following [18]. At time t=0, the switch opens and the current supplied by the capacitor is equal to the sum of the dark current and photo-generated current in the PD as shown in the expression

$$C_{PD}(v)\frac{d}{dt}V(t) = -I_{PD}$$

2.1

The junction capacitance changes with the magnitude of the applied reverse voltage due to the decreasing width of the space-charge region. The voltage dependent capacitance of a graded junction is given by

$$C_{PD}(v) = A \left(\frac{qa\epsilon^2}{12}\right)^{\frac{1}{3}} V^{-\frac{1}{3}}$$

2.2

In Equation 2.2 a is the junction gradient. The current through the PD is the sum of the dark and optically generated currents which are given by

$$I_d = \frac{Aqn_i}{2\tau_0} \left(\frac{12\varepsilon}{qa}\right)^{\frac{1}{3}} V^{1/3}$$

2.3

$$I_1 = I_0 A H 2.4$$

In Equations 2.3 and 2.4,  $\tau_0$  is the carrier lifetime in the depletion region,  $I_0$  is the photosensitivity of the junction in amps per unit area per foot-candela, and H is the illumination level in foot-candelas. Combining these four equations yields the following differential equation:

$$V^{-\frac{2}{3}}\frac{dV}{dt} + I_0 H I \left(\frac{12}{qa\varepsilon^2}\right)^{1/3} V^{-\frac{1}{3}} + \frac{n_i}{2\tau_0} \left(\frac{144Q}{\varepsilon a^2}\right)^{\frac{1}{3}} = 0$$

2.5

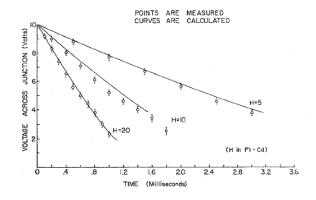

An analytical solution for Equation 2.5 does not exist. Through approximation and simulation, Weckler *et al* demonstrated that the integrating voltage is approximately linear regardless of illumination level as shown in Figure 2.5 and Figure 2.6. Figure 2.6 shows the voltage across the junction under no incident illumination. In this case, the curves exhibit slightly less linear behavior which is likely due to the dark current dependence on the width of the space charge region.

Figure 2.5 - Voltage dependence of illumination level on PD [18].

Figure 2.6 - Dark current response of PD in photon flux integrating mode [18].

In this implementation scheme, lower PD voltages represent higher levels of illumination or a "whiter" pixel color. It is important to note the saturation level for these devices. The upper level of the saturation region is determined by the amount of charge that can be stored on the integrating capacitance. A higher capacitance will allow for greater charge storage which can be accomplished through higher doping concentrations, higher reverse bias, and larger PD area. However, higher capacitance will result in poorer conversion gain, and the increase in the width of the space-charge region will result in an increase in the dark signal. The lower level of the saturation region is typically determined by the SF transistors ability to buffer the charge. Thus, at PD voltages below V<sub>TH-SF</sub>, the pixel will appear white.

#### 2.1.2 Performance Parameters

The characteristics and image quality of CMOS imagers are measured through the application of various parameters. These parameters quantify the imager's response to light, charge transfer characteristics, operational range etc. The following is a brief outline of the most common measurements used to evaluate imager performance.

#### 2.1.2.1 Fill Factor

The pixel FF is the ratio of the area occupied by the photo-sensing element to the area occupied by the pixel. FFs in the range of 30 percent are typical; however, the use of microlenses overtop the pixel can increase the effective FF to upwards of 80 percent [16]. High FF captures more incident light which results in a better digital representation of an analog image.

#### 2.1.2.2 Dynamic Range

Dynamic range is the maximum integrated voltage divided by the noise floor. The maximum integrated voltage is determined by the charge storage characteristics of the PD. The noise floor of the pixel is determined by the threshold characteristics of the source-follower

amplifier. Dynamic range can be increased through the reduction of dark current through the effect of lowering the noise floor. Dynamic range is typically measured in dB.

#### 2.1.2.3 Dark Current

Dark current, also known as leakage current, is a measure of generated charge carriers under no incident illumination. Dark current in CMOS imagers decreases the integration voltage in dark conditions which leads to a misrepresentation of pixel color. In highly illuminated scenarios, dark current has little effect on overall image quality. However, as illumination levels drop the dark current occupies a larger percentage of the pixel output which leads to poorer image quality. According to Pain *et al*, dark current sets the performance limit of CMOS imagers [19].

Dark current is presented as a voltage at the integrating node with respect to integration time, a current density with respect to the photo-sensitive element, or as the root-mean-square of non-photogenerated electrons. The measured voltage at the integrating node is dependent upon the conversion gain and size of the PD. For this reason, dark current measurements are often standardized and presented in terms of current/cm<sup>2</sup>.

#### 2.1.2.4 Conversion Gain

Conversion gain refers to the output voltage fluctuation per integrated electron and serves as a measurement of the responsivity of the pixel. High conversion gain is desirable to allow for more accurate ADC capture. Conversion gain is calculated as

$$CG = -\frac{q}{c}G_{SF}$$

2.6

In Equation 2.6,  $G_{SF}$  is the gain of the source follower (ideally 1), and c is the total parasitic capacitance at the integrating node. Conversion gain can be used to estimate the total parasitic capacitance by injecting a known charge into the integrating node and measuring the output. The parasitic capacitance in a 3T pixel is comprised of the junction capacitance of the PD,  $C_{gs}$  of the RST transistor,  $C_{g}$  of the SF transistor, the sidewall capacitance of the PD, and other parasitic components [20].

#### 2.1.2.5 Well Capacity

The well capacity is the maximum amount of charge that can be stored on the integrating node. The upper limit is determined by the capacitance at the integrating node and the reset voltage prior to integration. The empty well voltage is determined by the minimum amount of charge the SF transistor is able to buffer which is often significantly higher than the fully depleted level of the integrating node. Thus, conversion gain can be maximized by increasing the operating voltage at the expense of noise and power consumption or by optimizing the behavior of the SF transistor.

#### 2.1.2.6 Dark Signal Non-Uniformity

Dark signal non-uniformity (DSNU) is a measure of the uniformity of pixel dark currents in the imager. Pixel dark current is usually noisy which necessitates statistical characterization of the dark signal. DSNU is the reason dark current cannot simply be subtracted from the integrated voltage for image correction. DSNU is calculated according to the following:

$$DSNU = \frac{\sigma_{DM}}{S_{DM}}$$

2.7

In Equation 2.7,  $\sigma_{DM}$  is the square root of the variance of the mean of various dark signal values, and  $S_{DM}$  is the average dark signal value [21].

#### 2.1.3 Noise in NMOS Imagers

Noise in a circuit refers to any deviations in circuit signals that are caused by the non-ideal behavior of circuit components. In a MOS imager pixel, the sources of noise include reset noise, readout noise, fixed pattern noise, and PD noise which are outlined in the following sections.

#### 2.1.3.1 Reset Noise and Image Lag

Reset noise is defined by the mode of operation, either hard reset or soft reset. Hard reset refers to the case in which the PD capacitance is reset to  $V_{DD}$  by applying a sufficiently high voltage to the gate of the reset transistor such that the transistor operates in saturation regardless of the rising voltage at the capacitive node. According to Pain *et al*, the higher driving voltages associated with hard reset lead to hot-carrier stress and possible breakdown [22]. For this reason the saturation voltage is usually decreased below  $V_{DD}$  in order to reduce noise. This has the effect of decreasing the voltage range at the integrating node which can result in poor dynamic range.

To improve the dynamic range loss and high noise associated with hard reset, the RST transistor is often operated in soft reset mode. In this case, the voltage level the integration node reaches is dependent on the integration level of the previous frame. If the previous frame was exposed to sufficient illumination, the gate to source voltage across the RST transistor may be high enough for the transistor to operate in saturation. As the voltage at the integration node rises, the RST transistor will begin to operate in the subthreshold regime. The voltage at the integration node will have a logarithmic response, and the maximum voltage reached is dependent on the amount of time the circuit is in reset mode as well as the residual voltage from the previous frame.

According to Pain *et al*, when a small amount of charge is restored to the integration node during reset, the noise on the signal is dominated by shot noise [22]. In the case where a large amount of charge is restored to the pixel, thermal noise becomes the dominating noise factor. When the pixel is operated in hard reset, the noise is  $\sqrt{\frac{kT}{c}}$ . When thermal noise is the dominant source of noise during soft reset, the noise is  $\sqrt{\frac{kT}{2c}}$  [23]. The implication is that the noise will be lower when operated in soft reset; however, with soft reset, it is common for the integration node to remain below  $V_{DD}$  after the reset period resulting in image lag.

#### 2.1.3.2 Readout Noise

During the readout phase the pixel noise sources include RS, SF, and the SF biasing transistor external to the pixel. Because RS is operated in switch mode, its contribution to the noise is negligible in the readout phase. Thus, the SF and biasing transistor are the main components of signal noise during readout. The noise analysis performed by Brouk *et al* suggests that thermal noise and 1/f noise are the dominant sources of noise in these transistors [5]. The variance of the voltage from the thermal noise contribution of SF and the biasing transistor is given by

$$\sigma_{TH}^{2}(t_{read}) = \frac{2}{3} \frac{kT}{C_{L}} \frac{\left(g_{m,1}(1+\eta_{1}) + g_{m,2}\right)}{C_{L}\omega_{0}}$$

2.8

In Equation 2.8,  $C_L$  is the load capacitance external to the pixel used during readout,  $g_m$  is the transconductance of the respective MOSFET,  $\eta = g_{m,bs}/g_m$ , and  $\omega_0 = (r_{sF\_out}C_L)^{-1}$  where  $r_{sF\_out}$  is the output impedance of the source-follower [5].

As is shown in Equation 2.8, a large load capacitance at the readout node will reduce the effect of thermal noise. According to Van Zeghbroek, the transconductance of a MOSFET is proportional to  $C_{ox}W/L$  which implies the thermal noise during readout can be reduced by decreasing the MOSFET aspect ratio and gate capacitance [24].

The 1/f noise variance during readout can be found according to the following:

$$\sigma_{\frac{1}{f}}^{2}(t_{read}) = \frac{\rho_{0}}{2} \left( \frac{I_{DC,n}}{N_{eff,n}C_{L}\omega_{0}} \right)^{2}$$

2.9

In Equation 2.9,  $\rho_0$  is the density of traps per unit depth of the oxide,  $I_{DC,n}$  is the current through the channel of transistor  $M_n$ , and  $N_{eff,n}$  is the effective number of charges in the MOSFET channel [5]. The dependence on the channel current implies that 1/f noise will be lower for longer channel devices. Similar to thermal noise, a higher load capacitance will reduce the effect of noise.

#### 2.1.3.3 Fixed Pattern Noise

The individual devices within a pixel array will have varying characteristics which result in slightly different response from pixel to pixel. These differences are manifest as FPN which is typically constant from frame to frame but varies from pixel to pixel. The primary sources of fixed pattern noise are due to device mismatch; however, the majority of this noise can be reduced by the implementation of correlated double sampling in 4T cells and delta difference sampling in 3T cells [25]. The remaining source of fixed pattern noise in the pixel is PD dark current. The mismatched dark response from pixel to pixel results in FPN; however, minimizing the dark current in the PD will also improve FPN due to dark current.

#### 2.1.3.4 PD Noise

During integration the primary source of noise is shot noise due to the PD dark current and PD photo-generated current. The noise voltage on the PD sampled at the end of integration is given by the following [23]:

$$\sigma_{PD}^{2}(t_{int}) = \frac{q(i_{ph} + i_{dc})}{C_{ph}^{2}(v_{ph}(0))} t_{int} \left(1 - \frac{1}{2(v_{ph}(0) + v_{bi})} \frac{i_{ph} + i_{dc}}{C_{ph}^{2}(v_{ph}(0))} t_{int}\right)^{2}$$

2.10

Equation 2.10 takes into account the varying PD capacitance during integration. It is important to note the dependence of PD noise on the integration time. This suggests that as integration time is extended to accommodate for lower light conditions, there is less signal fidelity. Thus, to minimize PD noise during integration, the integration time should be as short as possible. Also, a higher PD capacitance and higher bias voltage will result in less PD noise.

#### 2.2 Photodiode Dark Current

In a MOS imager pixel circuit, the dark current continues to lower the voltage at the integrating node which results in a non-black pixel in dark conditions. As the illumination level decreases, the dark signal occupies a greater portion of the readout signal which results in poor imager quality in low light environments. The DSNU of the imager from pixel to pixel prevents the dark signal from simply being subtracted from each pixel. Thus, a reduction in pixel dark current has a strong implication on improving picture quality in low light scenarios.

#### 2.2.1 Mechanisms

Dark current generation is typically attributed to four different sources in CMOS devices: charge carrier generation and diffusion in the neutral bulk, charge generation due to surface states at the Si-SiO<sub>2</sub> boundary, charge generation in the depletion region, and charge generation

at interface traps at the diode perimeter [26]. The dark current components produced at the Si-SiO<sub>2</sub> interface and the diode perimeter are similar in that they are both the result of a high concentration of lattice defects at interfaces. The dark current components in the bulk and space-charge region are the effect of buried traps in the substrate. Research suggests that the net G/R rate can be controlled through the dopant concentration and trap concentration [27]. Because the dopant concentrations are set for device operation, the trap concentration must be reduced in order to reduce dark signal. Deep level traps are often the result of impurities introduced to the substrate during wafer fabrication. The number of interface traps is typically much larger than deep level traps, so contribution of deep level traps to dark current is often neglected.

#### 2.2.2 Influence of Charge Traps on Dark Current

Impurities and defects in a silicon lattice contribute to a band gap dividing phenomenon in which impurities and defects act as intermediate generation/recombination centers inside the forbidden gap. The Fermi distribution allows the concentration of holes and electrons to be determined for a trap energy level. Trap energy levels that result in equal probability of electron and hole concentrations contribute most to the charge carrier generation and recombination [27]. For this reason, impurities that create energy states near the midgap of the forbidden region contribute most to an increase in the dark signal.

#### 2.2.3 Effect of PD Shape on Dark Current

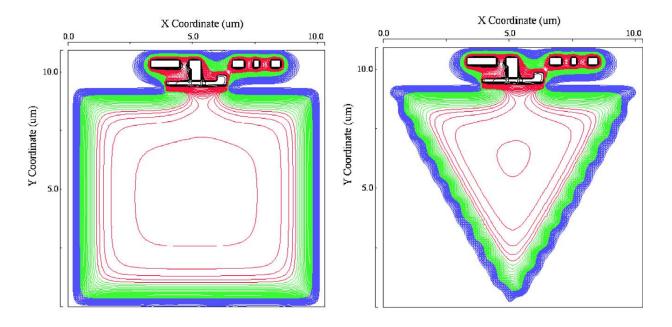

A higher concentration of defects is typically found in areas of the PD that are exposed to high stress. These areas are typically junctions and sharp edges. For this reason Shcherback, *et al* investigated the effect of PD shape on the dark signal of a 3T pixel [13]. In this research it was found that the PD with external angles ranging from 90 to 135 degrees contributed to a

reduction in dark current from 8.5nA/cm<sup>2</sup> to 7nA/cm<sup>2</sup>. The reduction in dark current indicates a reduction in trap concentration at the perimeter of the PD.

Shin *et al* explored a tapered PD design to facilitate charge transfer from the PD during the readout of a 4T pixel [14]. It was found that when the size of the PD was tripled, the voltage output only increased 20 percent. This is due to incomplete charge transfer in large PDs. The tapered design establishes a lateral electric field gradient due to the charge concentration gradient (Figure 2.7). An angle of 26.1 degrees results in a triangular shape and optimum charge transfer characteristics. This design leads to a reduction in reset noise and readout noise due to the field assisted charge transfer. The mitigation of dark current is not mentioned in the article; however, it can be assumed that the 26.1 degree angle used in the design would introduce a higher stressed region in the PD and lead to a comparatively higher dark current. However, the introduction of rounded corners may reduce dark current while maintaining the higher output voltage.

Figure 2.7 - Tapered PD design and E-field gradient [14].

The methods of dark current response and improved charge transfer presented in [13] and [14] are easily applied to the large area PDs that can be fabricated in the GVSU cleanroom. More sophisticated techniques of dark current reduction are beyond the scope of the GVSU cleanroom. For this reason, these two methods were used to form the basis of designing a reduced noise NMOS imager in the GVSU cleanroom.

#### 3 Experimental Method

The purpose of this research was to fabricate a low noise NMOS imager in the GVSU Cleanroom with a focus on the reduction of pixel dark current. Dark current reduction was attempted through the use of alternative PD designs. The readout circuitry attempted to maintain signal integrity through sample and hold circuitry and ADC sample averaging. Also, the Voltage and Sample and Acquisition Controller (VSAC) was designed for flexible control of the timing and voltage parameters of the control circuitry for imager optimization.

#### 3.1 Integrated Pixel Array Design

#### 3.1.1 Functional Requirements

The pixel arrays should implement the following characteristics:

Table 3.1 - Functional requirements of the integrated PD arrays.

| Functional Requirements                      |                                                                      |

|----------------------------------------------|----------------------------------------------------------------------|

| Requirement                                  | Description of requirement                                           |

| 8x8 pixel array.                             | The 8x8 pixel interface allows easy interface with common            |

|                                              | eight I/O circuit components.                                        |

| Sensitivity to illumination level            | The PD arrays should respond to incident illumination.               |

| Output voltage near V <sub>DD</sub> in dark  | Voltages nearer V <sub>DD</sub> represents darker pixel color. Under |

| conditions                                   | zero illumination the voltage increase is mainly due to dark         |

|                                              | current.                                                             |

| Output voltage near V <sub>TH,SF</sub> under | Under high intensity illumination, voltages nearer the lower         |

| high intensity illumination                  | bound of the readout circuit result in better dynamic range.         |

| Implement one PD shape per array.            | Limit PD test shapes to one per array to allow for simple            |

|                                              | comparison between shapes.                                           |

| Individually accessible pixels               | Each pixel should be accessible one by one through                   |

|                                              | operation of row and column elements.                                |

| Current source for SF transistor             | To achieve appropriate gain, a current bias (biasing                 |

|                                              | transistor) is necessary for the SF amplifier.                       |

| Compatibility with GVSU                      | Only devices capable of being fabricated in the GVSU                 |

| fabrication process                          | cleanroom are included in IC layout.                                 |

Additionally, the fabrication of a 4T pixel requires the ability to implant various doping concentrations of both P and N type which is beyond the scope of the GVSU fabrication process. For this reason, 3T pixels were used in the current research. Because the readout circuitry is not

integrated, the array size was kept small. This allows the readout circuitry to be hardwired to the interface board housing the fabricated IC. The pixel arrays were designed such that each array contained a single PD shape so that developed imagers implementing each type of PD can be compared. To maximize dynamic range, the output voltage should vary between  $V_{DD}$  and  $V_{TH,SF}$ . The SF amplifier requires a current source for proper operation. A biasing transistor is included on each column bus for this purpose. The NMOS imager was designed with standard pn-junction PDs and a minimum feature size of  $10\mu m$  for compatibility with the GVSU fabrication process. The fabrication process is outlined in more detail in section 3.3.

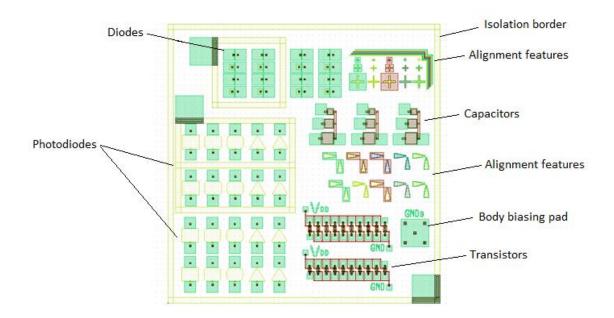

#### 3.1.2 Integrated Circuit Layout

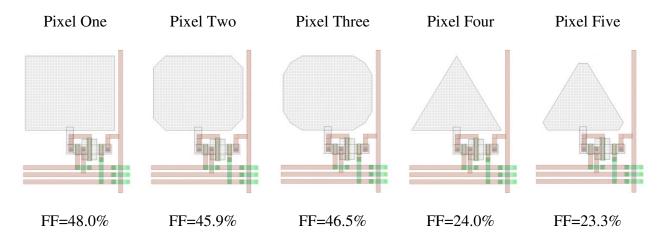

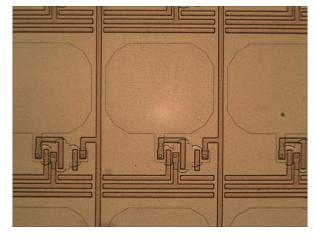

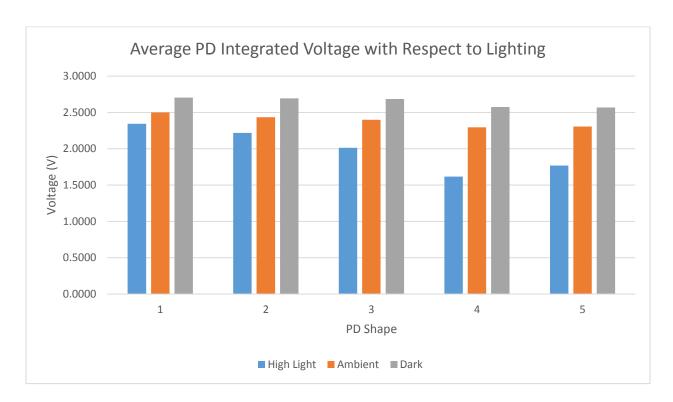

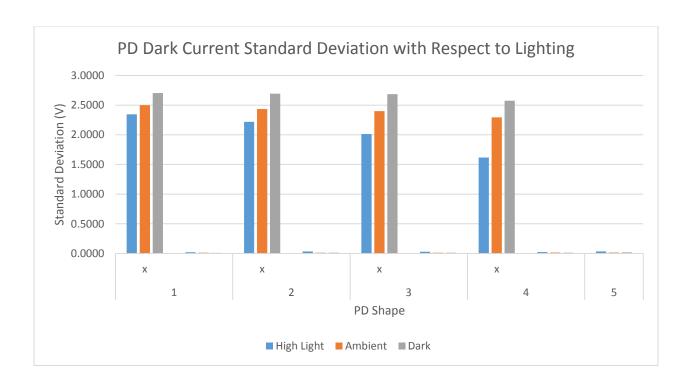

Five PD geometries were designed to test the influence of PD shape on the dark signal. These designs are adapted from the findings of Shcherback *et al* and Shin *et al* [13] [14]. The integrated circuit layout along with the FF of each pixel is shown in Figure 3.1. Pixel One is the test bench with which the altered designs will be compared. The PD of Pixel One occupies the greatest area and yields the best FF. Shcherback *et al* tested the influence of the number of corners and corner angle on the pixel dark response. Only the angles of the four corners in the rectangular shape were modified in this research in order to maintain a high FF. For this reason, pixels two and three are rectangular in shape with increasingly rounder corners.

Pixel Four serves as a benchmark to test the output voltage elevating effect demonstrated in the research of Shin *et al* [14]. The sharp corners of the triangular design are areas of high stress. The corners will have high concentrations of interface defects which will lead to elevated dark current. The sharp corners of Pixel Four were rounded as seen in Pixel Five with the hope of maintaining the voltage elevating effect while reducing dark current. The PD of Pixel One is

300 µm x 250µm and each subsequent design is based off this size. The corners of Pixel Two and three are 135 and 150 degrees respectively. The corners of Pixel Five are 120 degrees.

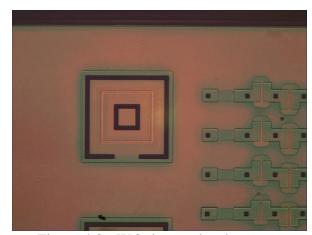

Figure 3.1 - Five PD designs to determine effect of PD shape on dark current.

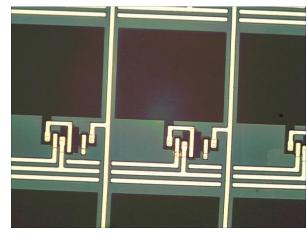

Pixel One is shown in Figure 3.2 with the devices and traces identified. The transistors are formed by creating two diffusion regions separated by the transistor channel with width equal to the minimum feature size; in this case 10µm. A gate oxide layer is grown on top of the transistor channel. A metal layer is then formed above the gate oxide to form the MOS capacitor which is the gate of the FET. Voltage

Figure 3.2 with the devices are formed by

Figure 3.2 - Pixel layout with identified devices and traces.

type FET which creates a conductive path from the source to drain of the transistor. Control signals are routed to the transistors through use of the RST,  $V_{DD}$ , and RS traces. The output of the pixel is transferred to the column bus using the RS transistor.

Each pixel contains three transistors. The RST and RS transistors have aspect ratios of 3:1 while the SF and biasing (not shown) transistors have aspect ratios of 7:1. The research suggests minimizing MOSFET aspect ratio will result in improved thermal noise performance during readout [5] [24]. The MOSFETs that source small currents (RST and RS) were designed with 3:1 aspect ratios for this reason. The amplifier transistors require a larger aspect ratio to improve the current sourcing abilities. Thus, the SF and biasing transistors were designed with an aspect ratio of 7:1.

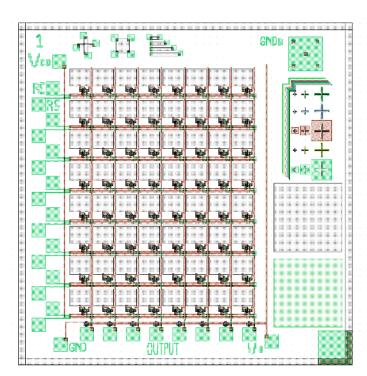

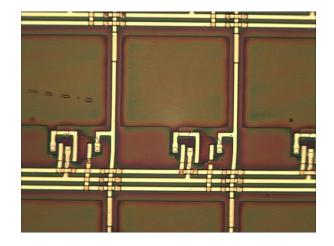

A sample die containing the rectangular PD array is shown in Figure 3.3. The 8x8 PD array consists of row and column readout busses as well as a biasing transistor for proper operation of the SF transistor in each pixel. The interface pads are 200x200µm and are used to supply control signals to the array as well as capture the array output. The array is designed for a single diffusion layer,

Figure 3.3 - Imager die with type one PDs.

gate oxide, two aluminum interconnect layers, and two via layers for a total of six layers. The array including readout pads occupies a 4.86mm by 5.00mm area.

An n-type isolation barrier was designed to surround each die with the intention of preventing bulk currents from interfering with the PD current. The isolation border encapsulates the PD array with a pn-junction. Biasing the border with a positive voltage creates a reversed

biased diode condition. This prevents currents from flowing into the die region from the areas of the bulk external to the PD array.

Designs with the source and bulk connected and disconnected have been designed to accommodate the likelihood that bulk biasing may need to be employed to obtain positive threshold operation with the transistors. The GND<sub>B</sub> pad in the upper right corner of the die is used to apply a voltage to the bulk of the die in designs where the transistor sources are not shorted to the bulk.

The five rows of cross structures and thin traces in Figure 3.3 are alignment features for use in the fabrication process. Each row compares the current layer to the previous layer.

During the alignment process these structures are used to ensure proper alignment from row to row. If the layers are not aligned the devices will not operate correctly.

The three Van der Pauw structures at the top of Figure 3.3 are used for measuring the resistivity of the diffusion layer. Resistivity measurements help characterize the uniformity of the diffusion layer.

The two large squares on the right of the die are used for sheet resistance and gate oxide (from top to bottom) measurements. The large area of the windows was designed to allow the four point probe and ellipsometer to capture measurements from individual die. The measurement of sheet resistance and gate oxide thickness from dummy wafers serves the same purpose as these regions.

### 3.1.3 Calculations and Simulations

The MOSFET threshold voltage calculations outlined in Appendix A.3.1 were used to estimate behavior of the 3:1 and 7:1 MOSFETs in the imager pixels. The values presented in

Table 3.2 were used in estimating the threshold voltage. The acceptor doping concentration is a function of the wafer resistivity and the hole mobility in the substrate. The interface charge is an estimate of the concentration of mobile ionic impurities at the Si-SiO<sub>2</sub> interface. The thickness of the gate oxide is estimated from previous fabrication results. The work function difference is a function of the substrate doping. Based on the estimated substrate doping, Streetman suggests a value of approximately -1V for the work function variation [28]. Based on these preliminary numbers, the MOSFET threshold voltage is likely to be in the range of 1-2V.

Table 3.2 - MOSFET threshold parameter estimates.

(Bold value is the result of the calculation.)

| Parameter       | Value                                       |

|-----------------|---------------------------------------------|

| N <sub>a</sub>  | 1.30x10 <sup>18</sup> [cm <sup>-1</sup> ]   |

| $Q_i$           | 3.50x10 <sup>12</sup> [qC/cm <sup>2</sup> } |

| d               | 70.0 [nm]                                   |

| $\phi_{ms}$     | -1.00 [V]                                   |

| V <sub>TH</sub> | 1.65 [V]                                    |

PD size is typically 15-20 times the minimum feature size [16]. To maximize FF in the current design the PD dimensions were increased to approximately 25 times the minimum feature size. Using the PD equations in Appendix A.1, PD characteristics were estimated for simulation purposes. The parameters used and values calculated are shown in Table 3.3. The junction width and area of the photodiode are used to estimate a PD capacitance of 3.4pF. The carrier lifetime ( $\tau_0$ ) in the depletion region is an empirical estimate suggested by [18]. The photo current is estimated to be 1.16 $\mu$ A. The magnitude of the PD current and the size of the PD

capacitance are the primary mechanisms controlling the speed at which the voltage across the PD junction decays.

Table 3.3 - Parameters for estimating PD photocurrent.

(Bold values are the results of the calculations.)

| Parameter | Value                                     | Parameter | Value                                                 |

|-----------|-------------------------------------------|-----------|-------------------------------------------------------|

| A         | $7.50 \times 10^{-4} [\text{cm}^2]$       | $L_n$     | 35.2 [µm]                                             |

| $N_A$     | 9.00x10 <sup>15</sup> [cm <sup>-1</sup> ] | $L_p$     | 59.1 [μm]                                             |

| $N_D$     | 1.43x10 <sup>15</sup> [cm <sup>-1</sup> ] | $C_{j}$   | 3.40 [pF]                                             |

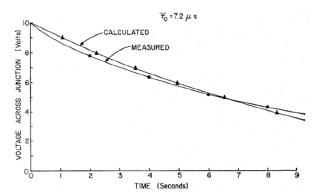

| $V_{bi}$  | 0.759 [V]                                 | $	au_0$   | 7.20 [µs]                                             |

| V         | -5 [V]                                    | $g_{op}$  | 10 <sup>18</sup> [(cm <sup>3</sup> s) <sup>-1</sup> ] |

| W         | 2.28 [µm]                                 | $I_{PD}$  | 1.16 [μΑ]                                             |

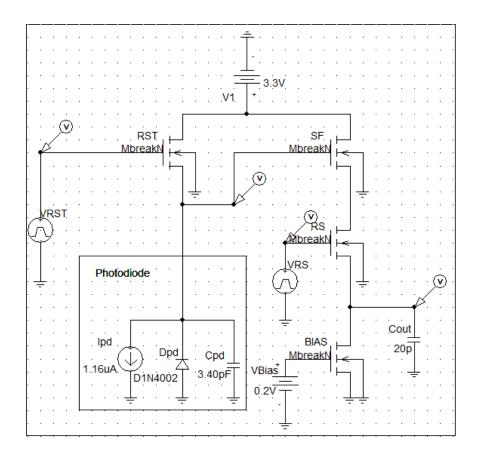

Figure 3.4 and Figure 3.5 show the schematic and simulation of the 3T APS respectively. The PD is modelled as a diode in parallel with a capacitance and current source. The effective capacitance during charge integration is the junction capacitance of the PD combined with parasitic RST and SF capacitances. The RST transistor contributes charge stored on the source-bulk and source-gate capacitors. The SF transistor contributes charge stored on the gate capacitance. The voltage across the PD capacitance after reset decreases due to the photocurrent modelled by the current source. Using the calculated parameter values, the 3T APS was simulated.

Figure 3.4 - Pixel simulation circuit

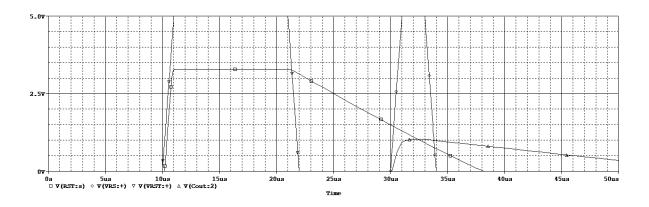

The following simulation results demonstrate the operation of the 3T APS. The gate of the RST transistor was overdriven at 5V during operation such that PD capacitance could be fully charged to  $V_{DD}$  before RST enters subthreshold operation. Because the fabricated transistors are likely to exhibit thresholds in the 1-2V range, a conservative ~1.5V<sub>DD</sub> pulse was applied to the RST gate to ensure adequate reset as suggested by Ji and Abshire [6]. After the reset pulse, the voltage across the PD rises to  $V_{DD}$  and slowly decreases proportional to the photocurrent. Because the SF transistor loses its buffering ability when the PD voltage decreases below the threshold voltage, operation of the RS transistor should occur prior to this point. When the gate to source voltage of the RS transistor is set to  $V_{DD}$ , the charge stored at the drain of the RS transistor is transferred to the output node modelled by a 20pF capacitance. The

simulation shows that the output voltage decreases with time due to leakage currents and the current through the bias transistor. However, in the circuit implementation, the output node will be captured by a sample and hold circuit to minimize losses during readout. Based on the values of the integrating capacitance and the photocurrent estimate, an integration time of roughly  $8\mu s$  is appropriate.

Figure 3.5 - Simulation results of 3T pixel.

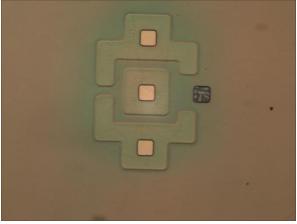

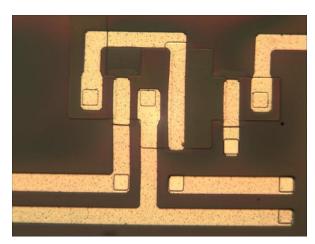

# 3.1.4 IC Testing

Each wafer layout contains several test die which will assist in the characterization of process fidelity. The test die is shown in Figure 3.6. Various alignment features are present on each test die. These features were visually inspected after each processing stage to ensure proper alignment from layer to layer. The test die has been designed with an n-type isolation border to test the influence of currents in the bulk on the operation of the device. The isolation border can be biased to prevent currents external to the structure from contributing to measured currents. The die also contains a bulk biasing pad which enables access to the substrate in order to test the effect of bulk potential on device operation. A Micromanipulator Company Inc. Model 6000 Probe Station is used to probe the IC test points.

The capacitance of the PDs was measured using the Agilent E4980A Precision LCR Meter. This is used to characterize the voltage decay during the integration period as compared to the simulation.

The test die contains two different transistor arrays with aspect ratios of 7:1 and 3:1. These arrays can be tested for correct transistor operation including threshold verification, the effect of body biasing, and drain current characterization. MOSFET and PD characteristics are captured using the HP4145A semiconductor parameter analyzer. An enclosure was built to house the ICs so dark conditions could be tested.

Figure 3.6 - Test die for fabrication characterization.

The test die will be utilized to obtain an average dark signal for each PD type as well as identify fabrication variations due to die position on the wafer. The GVSU fabrication process often exhibits performance variability with respect to die location. Thus, the test die can be used to identify regions likely to contain functional imagers.

## 3.2 Control Circuit Design

The readout circuitry captures the voltage output of the Imager IC and transfers that information to a PC for data analysis. The following sections outline the developed system used to capture image data.

# 3.2.1 Functional Requirements

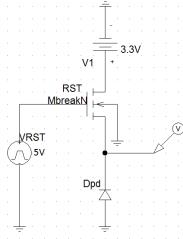

The diagram shown in Figure 3.7 shows the necessary components of the VSAC. The two shift registers, RST Select and Row Select blocks are used to index and control the RST and RS transistors of each row. The RST Gate Driver allows a logic level output from the RST shift register to supply a wide range of analog voltages to be used as the

Figure 3.7 - Block diagram of the VSAC.

RST transistor gate to source voltage. This allows the gates of the RST transistors to be overdriven to prevent image lag. The voltage regulators must be able to supply voltages in the range of 0.2 to 10V to various parts of the imager IC; so, BK Precision Model 1762 DC power supplies were used as the voltage regulators. The column sampling needs to sample the imager IC output with low noise and must maintain the signal level as the 8:1 multiplexor sequentially processes the parallel outputs. The ADC needs to be high resolution and low noise. The ADC is a peripheral of the TI LM326965 development board with 10-bit resolution. The development board is used to programmatically control the hardware and capture imager data. The UART peripheral of the microcontroller is used to send the data to a PC for processing and storage.

During transmission the 10 bit pixel values are byte extended to 16 bits and passed along the UART. The system is designed to capture and transmit the 64 pixel samples so for each image, the system should be capable of transmitting 128 bytes of image data.

### 3.2.2 Hardware and Simulations

The following sections outline the design decisions regarding the interface between the IC and PC. The schematic and board designs can be found in Appendix B.

## 3.2.2.1 TI Development Board

The TI LM3S6965 was used in this project to communicate between the developed embedded system and a PC, as well as convert the analog voltages at the imager output to digital. The LM3S6965 is a 32-bit microcontroller implementing an ARM Cortex M3 processor. The LM3S6965 was chosen for this project because it contains onboard ADC and UART peripherals which simplify the design of the developed PCB.

The LM3S6965 contains a 10-bit four channel ADC with hardware oversampling capability. This gives a voltage resolution of 2.93mV. Oversampling aids in noise reduction by sampling the analog voltage several times during a short period. The samples are then averaged together which effectively reduces the noise manifest in the reading. Hardware oversampling was used in this project to improve the noise performance during the readout stage.

## 3.2.2.2 VSAC

The VSAC is comprised of two shift registers, a voltage driver for the RST transistors, sample and hold circuitry, and multiplexor. Because the LM3S6965 does not have 16 extra outputs for the RS and RST transistors in each of the 8 rows, shift registers (74AHC595D) are used to expand the output size of the microcontroller. Using only four outputs from the

LM3S6965, each shift register can index eight outputs. Also, the clock functionality on the shift register allows a single pulse to swap control from one imager row to the next making programming the circuit simple.

The RST transistors need driving circuitry such that the gate can be overdriven to prevent image lag. An n-type transistor coupled with a pull up resistor at the transistor drain is used to supply a wide range of voltages to the RST gate. This configuration inverts the signal from the shift registers; so, the RST shift register is programmed opposite to that of the RS shift register.

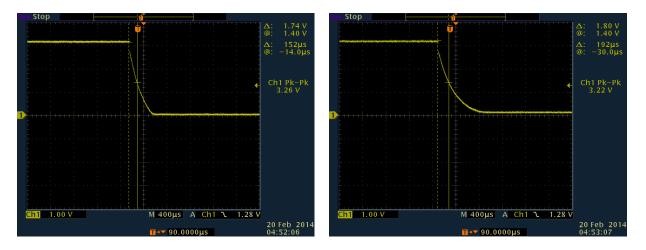

The sample and hold circuitry was designed to capture the analog voltage at the output pad of the imager IC and store the value as the data is serialized through the Multiplexor (MUX). The analog voltage at the output pads of the IC is subject to the bias current and other leakage which will result in significant voltage drops during serialization. The sample and hold ICs (LF398) are simultaneously triggered to sample the imager output with a single control signal from the LM3S6965. The use of a high quality polypropylene holding capacitor allows the sample and hold circuitry to maintain a steady voltage with a droop rate of less than 5mV per minute while the data is serialized through the MUX. Based on the capacitor choice for the sample and hold circuit, the LF398 datasheet suggests an acquisition time of roughly 20µs. Significant noise and quality degradation is not expected due to the sample and hold circuitry.

The LF398M sample and hold IC has a differential threshold voltage of 1.4V with a minimum to maximum of 0.8V to 2.4V. PD voltages below the logic threshold will appear as the logic threshold during readout. Characterization of the sample and hold circuits shows a differential threshold of 1.55V. This value should not limit the dynamic range of the imager as the SF transistors were designed for a threshold between 1-2V. The SF transistor sets the lower bound for the dynamic range.

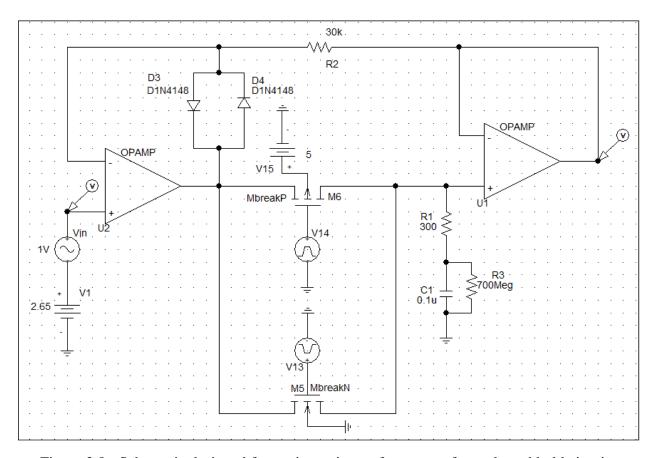

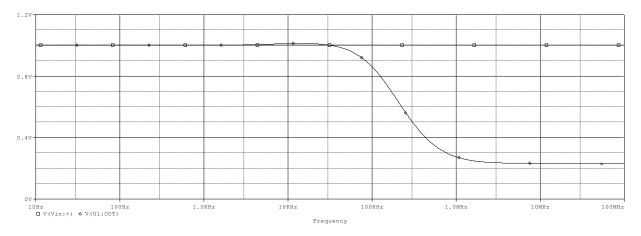

The schematic and simulation results in Figure 3.8 and Figure 3.9 show the noise simulation performed on the sample and hold circuitry. It is necessary that the sample and hold circuitry exhibit low noise characteristics so that captured samples are representative of the imager IC and not the readout circuitry. The capacitor at the positive terminal of op-amp U1 is the holding capacitor which is modelled with series and parallel parasitic resistances.

Figure 3.8 - Schematic designed for testing noise performance of sample and hold circuits.

The simulation results show that the input voltage suffers slight amplification between 10 and 100KHz; however, this amplification is less than 0.05dB and will not result in noticeable quality degradation. Due to the presence of the holding capacitor, high frequency noise is filtered from the output node.

Figure 3.9 - Noise response of sample and hold simulation.

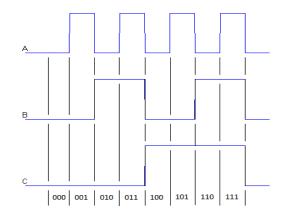

The MUX circuitry consists of a MUX and four bit counter (CD74HC4051NSR and SN54LV163A respectively). The MUX acts as a switch between one of the eight inputs to the single output where the analog voltage is digitized. The MUX is a high speed CMOS logic analog multiplexor which allows the IC output to be sampled quickly; thus, reducing the effective voltage droop at the holding node. The connected input is determined by the four bit counter. Only three of the counter's bits are used. The active bits between 000 and 111 are used to determine which of the eight MUX inputs is to be sampled at the output.

Several filtering and decoupling capacitors are also included on the circuit board near the power pins of each IC as well as the power lines of the board. This will help reduce noise due to changes in circuit current draw. Pin headers are also included on the circuit board which allows the LM3S6965, the VSAC, and the IC interface to be connected.

# 3.2.2.3 IC to PCB Interface

Due to limited space and probes, the probe station is only used to test individual devices. For this reason, an embedded board was developed for IC wafer bonding so that the developed imagers could be tested. Appendix B.2 contains the schematic and board layout of the developed

interface board. The pads on the interface board needed to have an Electroless Nickel Immersion Gold (ENIG) finish in order for wire bonding to work. Similar to the VSAC, the interface board was designed with filtering capacitors to improve the noise performance on the power supply lines.

### 3.2.3 Testing

The interface board, VSAC, and the LM3S6965 can be connected to test the imager performance. The timing and voltage parameters of imager operation are controlled by the LM3S6965 and power supplies respectively. The average dark signal can be calculated by measuring the voltage change with respect to time across the PD in dark conditions. This test can performed by connecting the LM3S6965 and the VSAC to discreet PDs using the probe station or testing imager output in dark conditions.

The minimum voltage the SF transistor can buffer must be determined for dynamic range calculation. To measure this, the RS transistor will be turned on during integration. When the output voltage levels off under these conditions the buffer threshold for the SF buffer is found. PD well capacity is then determined through the difference between  $V_{DD}$  and the minimum buffer voltage and effective capacitance of the integrating node. This will help determine appropriate timing for the integration period based on sensitivity at different levels of illumination.

After the performance parameters are optimized, image capture will take place and the voltage readout transferred to PC. Based on the well capacity of the imager circuit, the captured voltages will be mapped to black/white levels. Due to the small pixel array size and lack of optics, the imager output will likely not result in a discernable image. However, the voltage

output of the imager will demonstrate the ability of the imager to respond to the level of incident illumination.

The operation of the VSAC is confirmed through the use of the Salea eight bit 24MHz logic analyzer. The noise performance of the readout circuitry will be characterized by applying a known DC voltage to the readout pins of the VSAC. The variation in the VSAC readout will determine the noise injection of the readout circuitry.

The imager is tested by connecting the control signals of the VSAC to the interface board and LM3S6965. The integration period, reset period, and control voltages can be varied to accommodate the results of the IC testing. The imager output is digitized and sent to the PC for analysis to determine appropriate signal timing. The VSAC can be used to determine the average dark performance of each pixel shape through collection of imager output. This method will yield high volumes of comparable data for overall PD performance analysis.

# 3.3 Fabrication Process

The GVSU fabrication process is a nonstandard single diffusion, metal gate, two metal process with a minimum feature size of 10µm. The steps in Table 3.4 outline the fabrication process. It should be noted that the GVSU fabrication process uses a spin on dopant of type P509 from Filmtronics. Also, the insulating layer between the metal one and metal two layers is a Spin on Glass (SOG) of type B20 from Filmtronics. The SOG deposits a thin layer of SiO<sub>2</sub> to isolate trace routing on the two metal layers.

Table 3.4 - Processing stages in imager fabrication in the GVSU cleanroom.

| Step | Description           |

|------|-----------------------|

|      |                       |

| 1    | Standard RCA cleaning |

|      |                       |

| 2  | Wet oxidation (1100°C, 5000Å)                                                         |

|----|---------------------------------------------------------------------------------------|

| 3  | First photolithography process and wet oxide etch – definition of source and drain    |

| 4  | Phosphorous diffusion and drive in (~1µm junction depth)                              |

| 5  | Field oxide growth (1100 °C, 2000Å)                                                   |

| 6  | Second photolithography and wet oxide etch – gate definition                          |

| 7  | Dry oxidation for high quality gate oxide (1100 °C, 1000Å)                            |

| 8  | Third photolithography and wet oxide etch – definition of source and drain vias       |

| 9  | Aluminum evaporation deposition (~5000-6000Å)                                         |

| 10 | Fourth photolithography and aluminum etch – definition of aluminum routing            |

| 11 | Spin on glass deposition                                                              |