Linköping Studies in Science and Technology Dissertations, No. 1201

# Low Power and Low Complexity Shift-and-Add Based Computations

Kenny Johansson

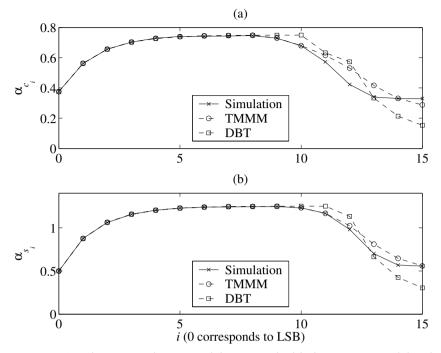

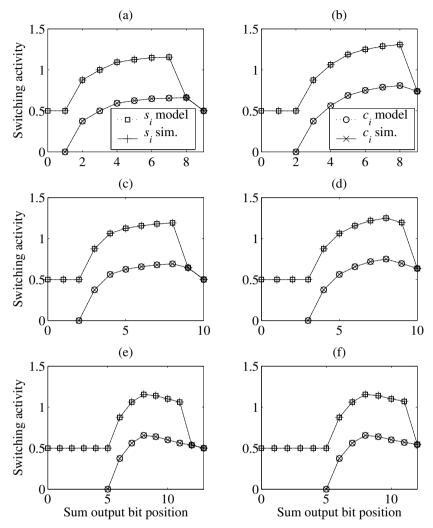

# Linköping University INSTITUTE OF TECHNOLOGY

Department of Electrical Engineering Linköping University, SE-581 83 Linköping, Sweden

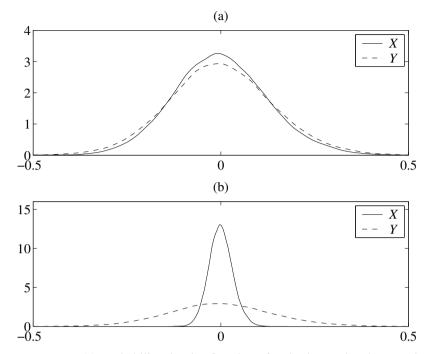

Linköping 2008

## Low Power and Low Complexity Shift-and-Add Based Computations

© 2008 Kenny Johansson

Division of Electronics Systems Department of Electrical Engineering Linköping University SE-581 83 Linköping Sweden

http://www.es.isy.liu.se/

ISBN 978-91-7393-836-5 ISSN 0345-7524

Printed by LiU-Tryck, Linköping 2008

# ABSTRACT

The main issue in this thesis is to minimize the energy consumption per operation for the arithmetic parts of DSP circuits, such as digital filters. More specific, the focus is on single- and multiple-constant multiplications, which are realized using shift-and-add based computations. The possibilities to reduce the complexity, i.e., the chip area, and the energy consumption are investigated. Both serial and parallel arithmetic are considered. The main difference, which is of interest here, is that shift operations in serial arithmetic require flip-flops, while shifts can be hardwired in parallel arithmetic.

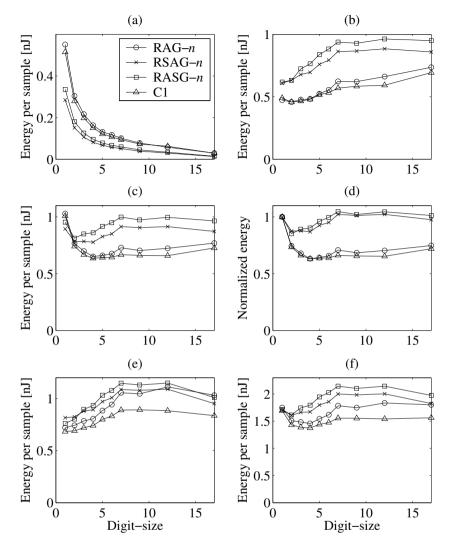

The possible ways to connect a given number of adders is limited. Thus, for single-constant multiplication, the number of shift-and-add structures is finite. We show that it is possible to save both adders and shifts compared to traditional multipliers. Two algorithms for multipleconstant multiplication using serial arithmetic are proposed. For both algorithms, the total complexity is decreased compared to one of the best-known algorithms designed for parallel arithmetic. Furthermore, the impact of the digit-size, i.e., the number of bits to be processed in parallel, is studied for FIR filters implemented using serial arithmetic. Case studies indicate that the minimum energy consumption per sample is often obtained for a digit-size of around four bits.

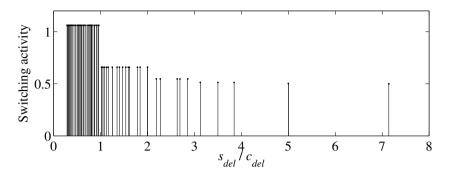

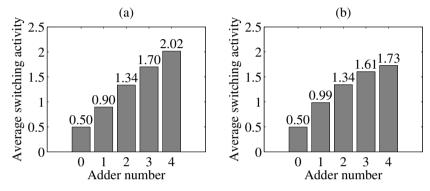

The energy consumption is proportional to the switching activity, i.e., the average number of transitions between the two logic levels per clock cycle. To achieve low power designs, it is necessary to develop accurate high-level models that can be used to estimate the switching activity. A method for computing the switching activity in bit-serial constant multipliers is proposed.

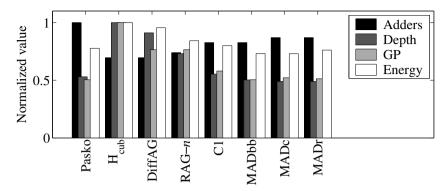

For parallel arithmetic, a detailed complexity model for constant multiplication is introduced. The model counts the required number of full and half adder cells. It is shown that the complexity can be significantly reduced by considering the interconnection between the adders. A main factor for energy consumption in constant multipliers is the adder depth, i.e., the number of cascaded adders. The reason for this is that the switching activity will increase when glitches are propagated to subsequent adders. We propose an algorithm, where all multiplier coefficients are guaranteed to be realized at the theoretically lowest depth possible. Implementation examples show that the energy consumption is significantly reduced using this algorithm compared to solutions with fewer word level adders.

For most applications, the input data are correlated since real world signals are processed. A data dependent switching activity model is derived for ripple-carry adders. Furthermore, a switching activity model for the single adder multiplier is proposed. This is a good starting point for accurate modeling of shift-and-add based computations using more adders.

Finally, a method to rewrite an arbitrary function as a sum of weighted bit-products is presented. It is shown that for many elementary functions, a majority of the bit-products can be neglected while still maintaining reasonable high accuracy, since the weights are significantly smaller than the allowed error. The function approximation algorithms can be implemented using a low complexity architecture, which can easily be pipelined to an arbitrary degree for increased throughput.

# ACKNOWLEDGEMENTS

I thank my supervisors, Dr. Oscar Gustafsson, who always takes an active interest in discussing new research ideas, and Professor Lars Wanhammar, for giving me the opportunity to do my Ph.D. studies at Electronics Systems. Furthermore, they both did a great job proofreading the thesis.

I also thank former and current colleagues at Electronics Systems. Dr. Henrik Ohlsson, for considerable support during my first working years, and for the many interesting, not only work related, discussions. Dr. Andrew Dempster for introducing me to the fundamentals in the field of multiple-constant multiplication.

I want to thank all the students that I have taught in various courses within the area of digital circuits. It has been enjoyable teaching you, and I hope that you have learned as much from me as I have learned from you.

All the friends during the years of undergraduate studies, in particular Magnus Karlsson, Joseph Jacobsson, and Ingvar Carlson, thanks to you this was the best time of my life.

Teachers through the years, especially Jan Alvarsson and Arne Karlsson in the upper secondary school. Also, the classmates Martin Källström and Peter Eriksson for all the conversations, about everything but school related subjects, both during and in between lessons.

Above all, I thank my parents, Mona and Nils-Gunnar Johansson, for all the support during my many years of studies. My sisters, Linda Johansson and Tanja Henze, who gave me an early start in mathematics. I remember getting extra homework when playing school because my 3:s looked angry. Considering this method of learning by discipline, it is not surprising that they became a teacher and a police officer.

Finally, I hope that selecting the colors of the club emblem for the front cover will help bringing home many gold medals to Färjestads BK!

This work was financially supported by the Swedish Research Council (Vetenskapsrådet).

The Coffee Room, August 24, 2008 Kenny Johansson Acknowledgements

# **TABLE OF CONTENTS**

| 1   | Introd                           | uction                                                                                                                                  | 1        |

|-----|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1 | Digital                          | Filters                                                                                                                                 | 2        |

|     | 1.1.1<br>1.1.2                   | IIR Filters<br>FIR Filters                                                                                                              |          |

| 1.2 | Numb                             | er Representations                                                                                                                      | 4        |

|     | 1.2.1<br>1.2.2                   | Negative Numbers<br>Signed-Digit Numbers                                                                                                |          |

| 1.3 | Logari                           | thmic Number Systems                                                                                                                    | 6        |

|     | 1.3.1<br>1.3.2                   | Conversions<br>Addition                                                                                                                 |          |

| 1.4 | Consta                           | ant Multiplication                                                                                                                      | 10       |

|     | 1.4.1<br>1.4.2<br>1.4.3<br>1.4.4 | Single-Constant Multiplication<br>Multiple-Constant Multiplication<br>Graph Representation<br>Terms used for Graph Based MCM Algorithms | 13<br>15 |

| 1.5 | Comp                             | uter Arithmetic                                                                                                                         | 18       |

|     | 1.5.1<br>1.5.2<br>1.5.3          | Parallel Arithmetic<br>Serial Arithmetic<br>Carry-Save Arithmetic                                                                       | 19       |

| 1.6 | Power                            | and Energy Consumption                                                                                                                  | 23       |

| 1.7 | Outline                          | e and Main Contributions                                                                                                                | 25       |

| 2   | Comp                             | lexity of Serial Constant Multipliers                                                                                                   | 31       |

| 2.1 | Graph                            | Multipliers                                                                                                                             | 32       |

|     | 2.1.1<br>2.1.2                   | Multiplier Types<br>Graph Elimination                                                                                                   |          |

| 2.2 | Comp                                                        | lexity Comparison – Single Multiplier                                                                                                                                                       | . 35                       |  |

|-----|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

|     | 2.2.1<br>2.2.2                                              | Comparison of Flip-Flop Cost<br>Comparison of Building Block Cost                                                                                                                           |                            |  |

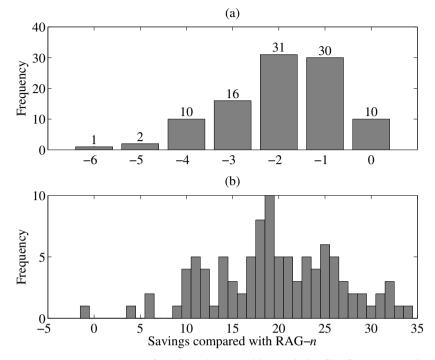

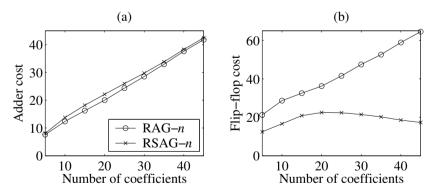

| 2.3 | Comp                                                        | lexity Comparison – RSAG- <i>n</i>                                                                                                                                                          | . 42                       |  |

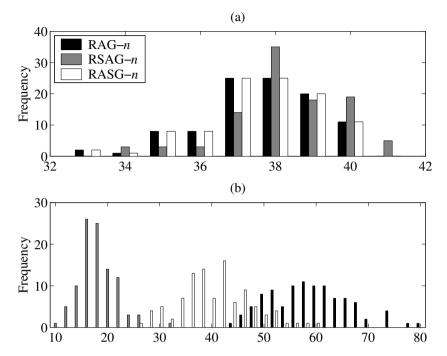

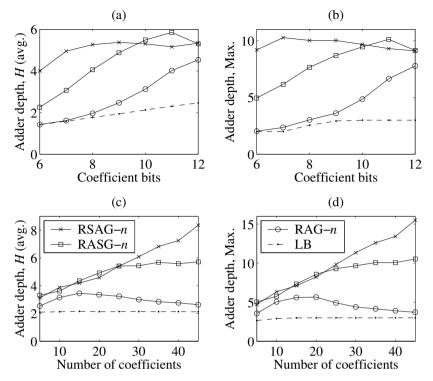

|     | 2.3.1<br>2.3.2<br>2.3.3                                     | The Reduced Shift and Adder Graph Algorithm<br>Comparison by Varying the Wordlength<br>Comparison by Varying the Setsize                                                                    | 46                         |  |

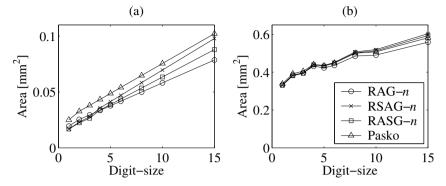

| 2.4 | Digit-S                                                     | Size Trade-Offs                                                                                                                                                                             | . 49                       |  |

|     | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5                   | Implementation Aspects<br>Specification of the Example Filter<br>Chip Area<br>Sample Rate<br>Energy Consumption                                                                             | 52<br>53<br>54             |  |

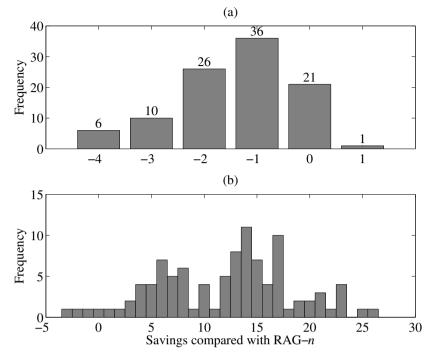

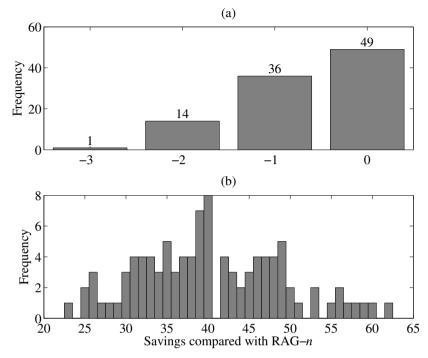

| 2.5 | Comp                                                        | lexity Comparison – RASG-n                                                                                                                                                                  | . 58                       |  |

|     | 2.5.1<br>2.5.2<br>2.5.3<br>2.5.4                            | The Reduced Adder and Shift Graph Algorithm<br>Comparison by Varying the Wordlength<br>Comparison by Varying the Setsize<br>Adder Depth                                                     | 59<br>61                   |  |

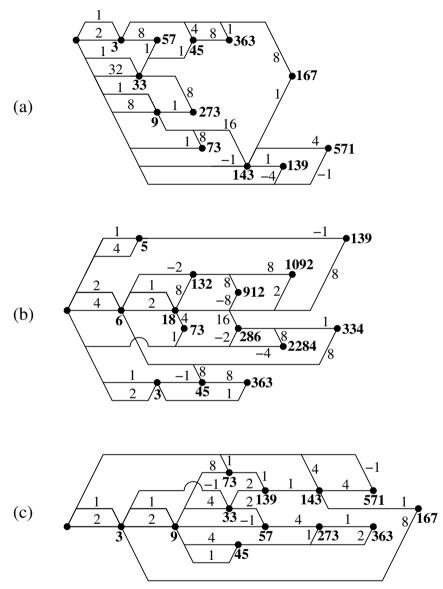

| 2.6 | Impler                                                      | nentation Examples                                                                                                                                                                          | . 65                       |  |

|     | 2.6.1<br>2.6.2                                              | Example 1<br>Example 2                                                                                                                                                                      |                            |  |

| 2.7 | Conclu                                                      | usions                                                                                                                                                                                      | . 77                       |  |

| 3   | Switc                                                       | hing Activity in Bit-Serial Multipliers                                                                                                                                                     | . 79                       |  |

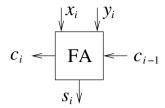

| 3.1 | Multip                                                      | lier Stage                                                                                                                                                                                  | . 80                       |  |

|     | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7 | Preliminaries<br>Sum Output Switching Activity<br>Switching Activity Using STGs<br>Carry Output Switching Activity<br>Input-Output Correlation Probability<br>Glitching Activity<br>Example | 81<br>83<br>87<br>88<br>91 |  |

| 3.2 | Graph Multipliers                                           |                                                                                                                                                                                             |                            |  |

|     | 3.2.1<br>3.2.2<br>3.2.3                                     | Correlation Probability Look-Up Tables<br>The Applicability of the Equations<br>Example                                                                                                     | 93                         |  |

| 3.3 | Serial                                                      | Serial/Parallel Multipliers9                                                                                                                                      |                                 |  |  |

|-----|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

|     | 3.3.1<br>3.3.2                                              | Simplification of the Switching Activity Equation<br>Example                                                                                                      |                                 |  |  |

| 3.4 | Concl                                                       | usions                                                                                                                                                            | 100                             |  |  |

| 4   | Comp                                                        | elexity of Parallel Constant Multipliers                                                                                                                          | 101                             |  |  |

| 4.1 | Bit-Le                                                      | vel Optimization                                                                                                                                                  | 102                             |  |  |

|     | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                            | Scaling<br>Complexity Model<br>Removing Half Adders<br>Single-Constant Multiplication Example                                                                     | 103<br>108                      |  |  |

| 4.2 | Low C                                                       | Complexity Algorithm                                                                                                                                              | 112                             |  |  |

|     | 4.2.1<br>4.2.2                                              | Multiple-Constant Multiplication Example                                                                                                                          |                                 |  |  |

| 4.3 | Interco                                                     | onnection Algorithms                                                                                                                                              | 115                             |  |  |

|     | 4.3.1<br>4.3.2                                              | Algorithm Formulations<br>Implementation Examples                                                                                                                 |                                 |  |  |

| 4.4 | Minimum Adder Depth Algorithm                               |                                                                                                                                                                   |                                 |  |  |

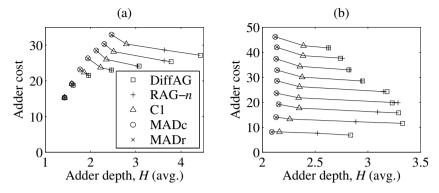

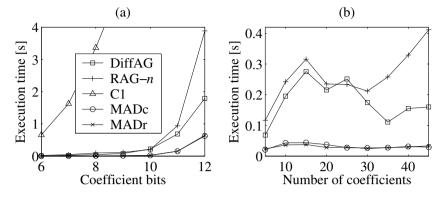

|     | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6<br>4.4.7 | Fundamental Pairs<br>MCM Defined as a Covering Problem<br>Optimal Approach<br>Heuristic Approaches<br>Optimal vs. Heuristic<br>Results<br>Implementation Examples | 130<br>130<br>134<br>143<br>148 |  |  |

| 4.5 | Concl                                                       | usions                                                                                                                                                            | 160                             |  |  |

| 5   | Energ                                                       | y Estimation for Ripple-Carry Adders                                                                                                                              | 163                             |  |  |

| 5.1 | Backg                                                       | pround                                                                                                                                                            | 164                             |  |  |

|     | 5.1.1                                                       | Exact Method for Transitions in RCA                                                                                                                               | 164                             |  |  |

| 5.2 | Energ                                                       | y Model                                                                                                                                                           | 165                             |  |  |

|     | 5.2.1                                                       | Timing Issues                                                                                                                                                     | 169                             |  |  |

| 5.3 | Switching Activity                                          |                                                                                                                                                                   |                                 |  |  |

|     | 5.3.1<br>5.3.2<br>5.3.3                                     | Switching due to Change of Input<br>Switching due to Carry Propagation<br>Total Switching Activity                                                                | 173                             |  |  |

|     | 5.3.4<br>5.3.5                   | Uncorrelated Input Data<br>Summary                                                                         |            |  |

|-----|----------------------------------|------------------------------------------------------------------------------------------------------------|------------|--|

| 5.4 | Exper                            | imental Results                                                                                            | . 180      |  |

|     | 5.4.1<br>5.4.2                   | Uncorrelated Data<br>Correlated Data                                                                       |            |  |

| 5.5 | Adopt                            | ing the Dual Bit Type Method                                                                               | . 183      |  |

|     | 5.5.1<br>5.5.2<br>5.5.3<br>5.5.4 | Statistical Definition of Signals<br>The DBT Method<br>DBT Model for Switching Activity in RCA<br>Example  | 187<br>189 |  |

| 5.6 | Switch                           | ning Activity in Constant Multipliers                                                                      | . 194      |  |

|     | 5.6.1<br>5.6.2<br>5.6.3<br>5.6.4 | Addition with High Correlation<br>Results<br>Discussion on Switching Activity in MCM<br>Time Instant Model | 199<br>202 |  |

| 5.7 | Concl                            | usions                                                                                                     | . 205      |  |

| 6   | Funct                            | ion Approximation by a Sum of Bit-Products                                                                 | . 207      |  |

| 6.1 | Backg                            | round                                                                                                      | . 208      |  |

|     | 6.1.1                            | PPA Methods                                                                                                | 209        |  |

| 6.2 | Functi                           | on Approximation Approach                                                                                  | . 211      |  |

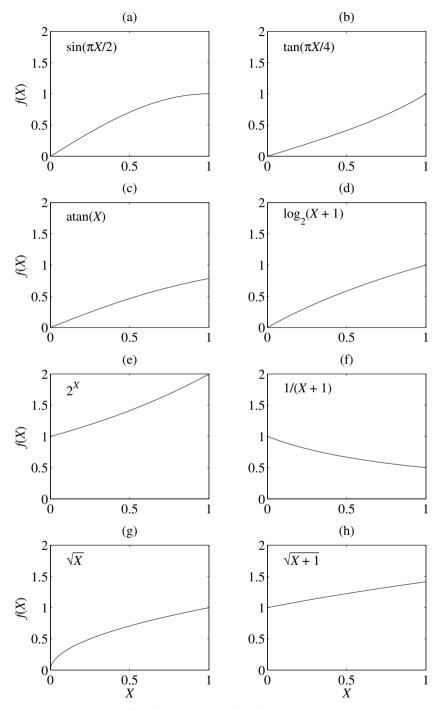

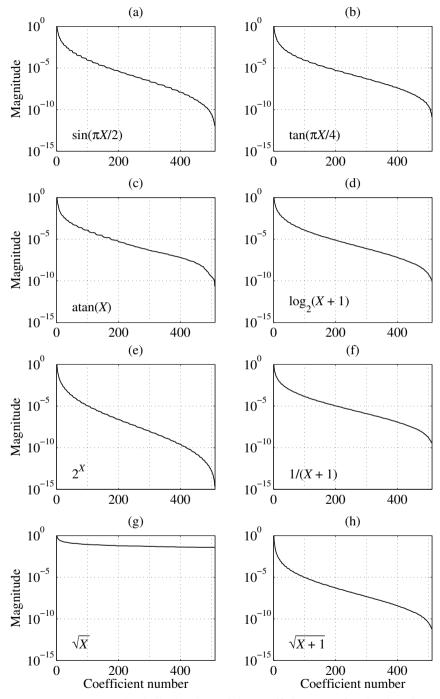

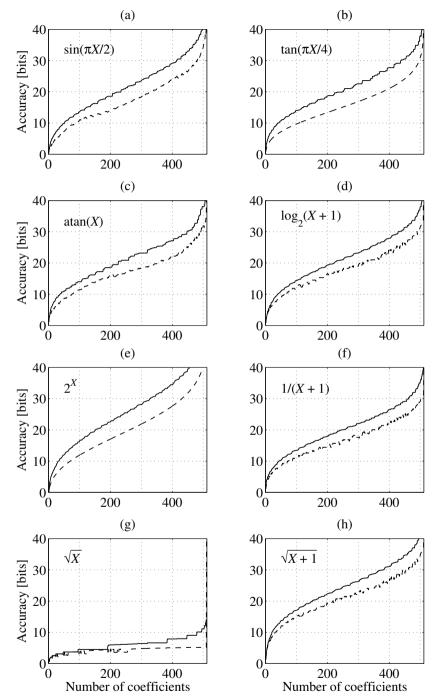

|     | 6.2.1<br>6.2.2<br>6.2.3          | General Formulation<br>Optimization<br>Results for Some Elementary Functions                               | 215        |  |

| 6.3 | Archite                          | ecture                                                                                                     | . 222      |  |

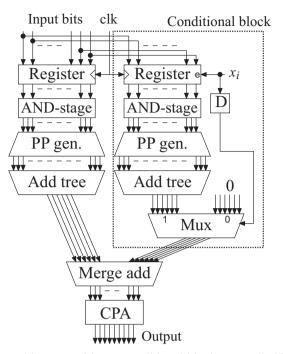

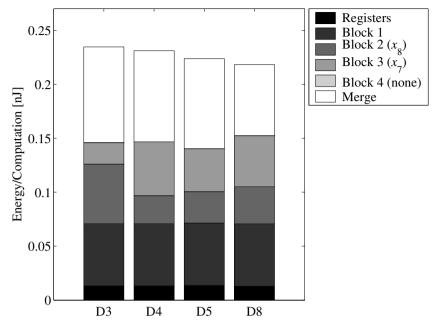

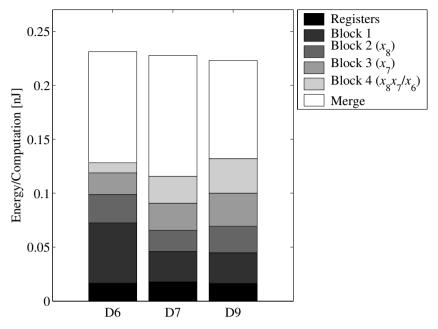

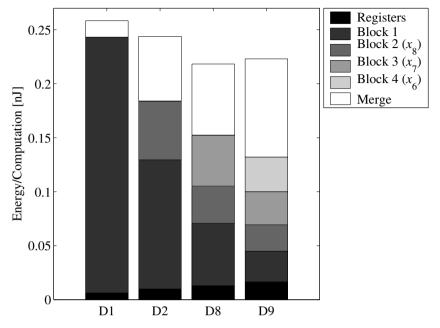

|     | 6.3.1<br>6.3.2<br>6.3.3          | Implementation for a Sum of Bit-Products<br>Conditional Blocks<br>Results Using Conditional Blocks         | 225        |  |

| 6.4 | Functions for LNS                |                                                                                                            |            |  |

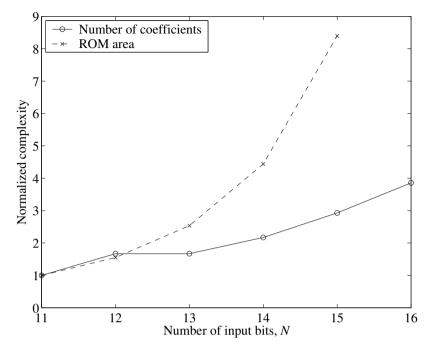

|     | 6.4.1<br>6.4.2<br>6.4.3          | Sign Transformation<br>Results for the LNS Functions<br>Comparison with ROM                                | 237        |  |

| 6.5 | Sine and Cosine Functions2       |                                                                                                            |            |  |

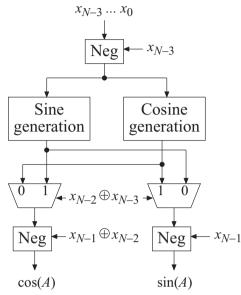

|     | 6.5.1<br>6.5.2<br>6.5.3          | Angle Rotation Based Approach<br>Octant Mapping<br>Comparison with CORDIC                                  | 246        |  |

| 7.2 | Future Work | 254 |

|-----|-------------|-----|

| 7.1 | Summary     | 251 |

| 7   | Conclusions | 251 |

| 6.6 | Conclusions | 249 |

**Table of Contents**

# 1

# INTRODUCTION

There are many hand-held products that include digital signal processing (DSP), for example, cellular phones and hearing aids. For this type of portable equipment, a long battery life time and a low battery weight is desirable. To achieve this, the circuits must have low power consumption.

The main issue in this thesis is to minimize the energy consumed per operation for the arithmetic parts of DSP circuits, such as digital filters. More specific, the focus will be on single- and multiple-constant multiplication, using either serial or parallel arithmetic. Different design algorithms will be compared, not just to determine which one that is the best in terms of complexity, but also to build up an understanding of the connection between algorithm properties and energy consumption. This knowledge is useful when models are derived to be able to estimate the energy consumption. Finally, to close the circle, the energy models can be used to design improved algorithms. However, although most parts are covered in some way, this circle is not completely closed within the content of this thesis.

In this chapter, an elementary background on the design of digital filters using constant multiplication will be presented. The information given here will be assumed familiar in the following chapters. In addition, terms that are used in the rest of the thesis will be introduced.

## 1.1 Digital Filters

Frequency selective digital filters are used in many DSP systems [149], [150]. The filters studied here are assumed to be causal, linear, and time-invariant systems.

The input-output relation for an *N*th-order digital filter is described by the difference equation

$$y(n) = \sum_{k=1}^{N} b_k y(n-k) + \sum_{k=0}^{N} a_k x(n-k)$$

(1.1)

where  $a_k$  and  $b_k$  are constant coefficients while x(n) and y(n) are the input and output sequences. If the input sequence, x(n), is an impulse, the impulse response, h(n), is obtained as output sequence.

#### 1.1.1 IIR Filters

If the impulse response has infinite duration, i.e., theoretically never reaches zero, it is an infinite-length impulse response (IIR) filter. This type of filters can only be realized by recursive algorithms, which means that at least one of the coefficients  $b_k$  in (1.1) must be nonzero.

The transfer function, H(z), is obtained by applying the *z*-transform to (1.1), which gives

$$H(z) = \frac{Y(z)}{X(z)} = \frac{\sum_{k=0}^{N} a_k z^{-k}}{1 - \sum_{k=1}^{N} b_k z^{-k}}$$

(1.2)

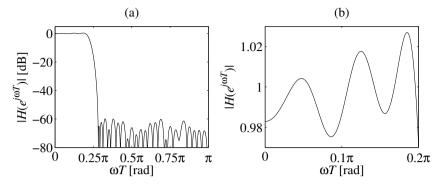

#### 1.1.2 FIR Filters

If the impulse response becomes zero after a finite number of samples, it is a finite-length impulse response (FIR) filter, which is a common component in many DSP systems. For a given specification, the filter order, N, is higher for an FIR filter than for an IIR filter. However, FIR filters can be guaranteed to be stable and to have a linear phase response, which corresponds to a constant group delay [150].

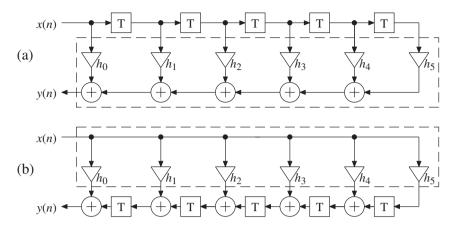

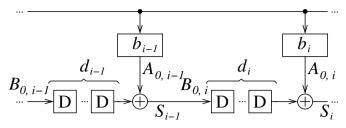

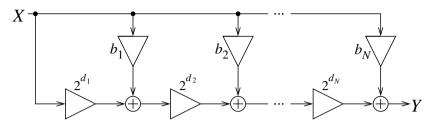

Figure 1.1 Different realizations of a fifth-order (six-tap) FIR filter. (a) Direct form and (b) transposed direct form.

It is not recommended to use recursive algorithms to realize FIR filters, because of stability problems. Hence, here all coefficients  $b_k$  in (1.1) are assumed to be zero. If an impulse is applied at the input, each output sample will be equal to the corresponding coefficient  $a_k$ , i.e., the impulse response, h(n), is an ordered sequence of the coefficients  $a_0, a_1, a_2, ..., a_N$ . The transfer function of an *N*th-order FIR filter can then be written as

$$H(z) = \sum_{k=0}^{N} a_k z^{-k}$$

(1.3)

A realization of (1.3) for N = 5 is shown in Fig. 1.1 (a), where  $h_k = a_k$ . This filter structure is referred to as a direct form FIR filter. If the signal flow graph is transposed the filter structure in Fig. 1.1 (b) is obtained, referred to as transposed direct form [150]. These are the two most common structures for realizing FIR filters. The dashed boxes in Figs. 1.1 (a) and (b) mark a sum-of-products (SOP) and a multiplier block (MB), respectively. In both cases, the part that is not included in the dashed box is referred to as the delay section, and the adders in Fig. 1.1 (b) are called structural adders.

In most practical cases of frequency selective FIR filters, linear-phase filters are used. This means that the phase response,  $\Phi(\omega T)$ , is proportional to  $\omega T$  as [150]

$$\Phi(\omega T) \propto -\frac{N\omega T}{2} \tag{1.4}$$

Furthermore, linear-phase FIR filters have a symmetric or antisymmetric impulse response, i.e.,

$$h(n) = \begin{cases} h(N-n) & \text{symmetric} \\ -h(N-n) & \text{antisymmetric} \end{cases} n = 0, 1, ..., N \quad (1.5)$$

This implies that for linear-phase FIR filters, the number of specific multiplier coefficients is at most N/2 + 1 and (N + 1)/2 for even and odd filter orders, respectively.

## 1.2 Number Representations

In digital circuits, numbers are represented as a string of bits, using the logic symbols 0 and 1. Normally, the processed data are assumed to take values in the range [-1, 1]. However, as the binary point can be placed arbitrarily by shifting, only integer numbers will be considered here.

The values are represented using *n* digits  $x_i$  with the corresponding weight  $2^i$ . Hence, for positive numbers an ordered sequence  $x_{n-1}x_{n-2} \dots x_1x_0$  where  $x_i \in \{0, 1\}$  correspond to the integer value, *X*, as defined by

$$X = \sum_{i=0}^{n-1} x_i 2^i$$

(1.6)

#### 1.2.1 Negative Numbers

There are different ways to represent negative values for fixed-point numbers. One possibility is the signed-magnitude representation, where the sign and the magnitude are represented separately. When this representation is used, simple operations, like addition, become complicated because a sequence of decisions has to be made [75].

Another possible representation is one's-complement, which is the diminished-radix complement in the binary case. Here, the complement is simply obtained by inverting all bits. However, a correction step where a one is added to the least significant bit position is required if a carry-out is obtained in an addition. For both signed-magnitude and one's-complement, there are two representations of zero, which makes a test for zero operation more complicated.

The most commonly used representation in DSP systems is the two's-complement representation, which is the radix complement in the binary case. Here, there is only one representation of zero and no correction is necessary when addition is performed. For two's-complement representation, an ordered sequence  $x_{n-1}x_{n-2} \dots x_1x_0$  where  $x_i \in \{0, 1\}$  correspond to the integer value

$$X = -x_{n-1}2^{n-1} + \sum_{i=0}^{n-2} x_i 2^i$$

(1.7)

The range of *X* is  $[-2^{n-1}, 2^{n-1} - 1]$ .

#### 1.2.2 Signed-Digit Numbers

In signed-digit (SD) number systems, the digits are allowed to take negative values, i.e.,  $x_i \in \{\overline{1}, 0, 1\}$  where a bar is used to represent a negative digit. The integer value, X, of an SD coded number can be computed according to (1.6) and the range of X is  $[-2^n + 1, 2^n - 1]$ . This is a redundant number system, for example,  $1\overline{1}$  and 01 both correspond to the integer value one.

An SD representation that has a minimum number of nonzero digits is referred to as a minimum signed-digit (MSD) representation. The most commonly used MSD representation is the canonic signed-digit (CSD) representation [149], where no two consecutive digits are nonzero. Here, each number has a unique representation, i.e., the CSD representation is nonredundant. Consider, for example, the integer value eleven, which has the binary representation 1011 and the unique CSD representation  $10\overline{1}0\overline{1}$ . Both these representations are also MSD representations, and so is  $110\overline{1}$ .

The SD numbers are used to avoid carry propagation in additions and to reduce the number of partial products in multiplication algorithms. An algorithm to obtain all SD representations of a given integer value was presented in [30].

## 1.3 Logarithmic Number Systems

Compared to conventional computer arithmetic, logarithmic number systems (LNS) have some advantages, which are desirable in applications such as adaptive filtering [121]. Logarithmic arithmetic has also been used in various processors [16],[17],[109]. Using LNS, multiplication and division are simplified to addition and subtraction, respectively. Furthermore, powers and roots are in general reduced to multiplication and division, while, in the special case, squaring and square roots are simply obtained by shift operations [75]. On the other hand, addition/subtraction and the conversions to and from LNS are complicated [32],[147]. These operations require that certain functions are computed, which, for example, can be done by using look-up tables.

In the first part of this section, conversions between the conventional fixed-point and the logarithmic number systems are considered. In the second part, addition (subtraction) within the logarithmic domain is discussed. Here, base two is assumed for the logarithms, but note that for a given application it may be advantageous to select another base [3].

#### 1.3.1 Conversions

Assume a fixed-point number, A, in the linear domain. After conversion to the logarithmic domain, A is represented by a logarithm  $E_A$  and a sign bit  $S_A$ , according to

$$E_A = \log_2 |A|$$

and  $S_A = \begin{cases} 0 & A > 0 \\ 1 & A < 0 \end{cases}$  (1.8)

Note that  $A \neq 0$  is assumed here. Zero can be approximated using the largest negative value of  $E_A$ . However, in many applications an extra bit is used as a zero flag.

The conversion back to the linear domain is performed by an antilogarithm operation computed as

$$A = (-1)^{S_A} 2^{E_A} \tag{1.9}$$

The logarithm and antilogarithm functions, which are used in the conversions, are often implemented using look-up tables. These functions are

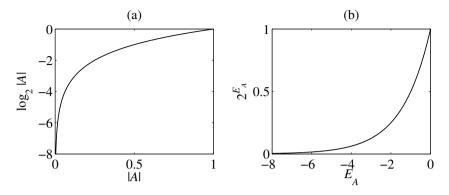

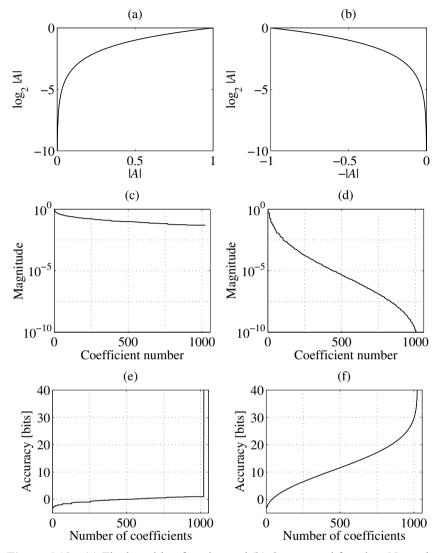

Figure 1.2 Conversions to and from logarithmic number systems. (a) The logarithm and (b) the antilogarithm function.

illustrated in Fig. 1.2 for the range  $|A| \le 1$  and  $-8 \le E_A < 0$ , respectively. Note that the same antilogarithm table can be used for both negative and positive values of  $E_A$  by shifting the result.

Since the numeric range of the two domains is different, certain rules can be formulated to preserve the range and resolution. Using two's-complement representation, a fixed-point number, A, is composed of k integer bits and l fractional bits. In the logarithmic domain,  $E_A$  includes a K bit integer part and an L bit fractional part, using two's-complement representation.

The maximum value of  $|E_A|$  can be limited by either a large value of |A|, which gives a large positive value of  $E_A$ , or by a small value of |A|, which gives a large negative value of  $E_A$ . Hence, the number of integer bits, K, is obtained as

$$K = \left\lceil \log_2(\max(k-1, l)) \right\rceil + 1 \tag{1.10}$$

Numbers are not equally spaced in the logarithmic domain, i.e., the accuracy depends on  $E_A$ . To obtain at least the same accuracy as in the linear domain, the following relation should hold for all values of  $E_A$

$$2^{E_A + 2^{-L}} - 2^{E_A} \le 2^{-l} \implies L = \left[ -\log_2(\log_2(2^{-l} + 2^{E_A}) - E_A) \right] \quad (1.11)$$

The required accuracy is higher for large values of |A| as the slope of  $|A| = 2^{E_A}$  then is larger, i.e.,  $E_A = \log_2 |2^{k-1} - 2^{-l}| \approx k - 1$  should be used in (1.11) to find the value of *L* that is required in the worst case.

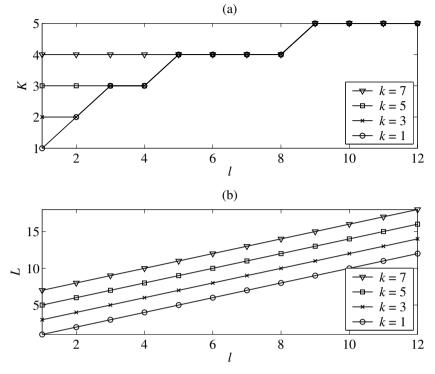

**Figure 1.3** Required number of (a) integer and (b) fractional bits using logarithmic number systems.

The relations between the number of required bits in the different domains according to (1.10) and (1.11) are illustrated in Figs. 1.3 (a) and (b), respectively. These rules are of course not suitable for all applications, since it depends on the required accuracy and number range.

#### 1.3.2 Addition

Consider the addition (subtraction)  $C = A \pm B$ . If |A| > |B| is assumed, the corresponding operation in the logarithmic domain is obtained as

$$E_{C} = \log_{2}|A \pm B| = \log_{2}\left|A\left(1 \pm \frac{B}{A}\right)\right| =$$

$$= E_{A} + \log_{2}\left|1 + (-1)^{S_{\Phi}}2^{E_{B} - E_{A}}\right| = E_{A} + \Phi(E_{B} - E_{A})$$

(1.12)

where  $\Phi$  is a function of the negative difference  $E_B - E_A$ . The variable  $S_{\Phi}$  is introduced to compensate for the signs of A and B after conversion to

the logarithmic domain, since the absolute values of *A* and *B* then are used. Furthermore,  $S_{\Phi}$  also include the performed operation. Because |A| > |B|, the sign of *C* will be the same as for *A*, i.e.,  $S_C = S_A$ .

If instead |B| > |A| the logarithm,  $E_C$ , is computed in a similar manner according to

$$E_{C} = E_{B} + \Phi(E_{A} - E_{B})$$

(1.13)

Since A - B = -(B - A), the sign,  $S_C$ , must be inverted if the performed operation is a subtraction, which can be implemented as a logic XOR operation, denoted by  $\oplus$ , i.e.,

$$S_C = S_B \oplus op$$

where  $op = \begin{cases} 0 & \text{addition} \\ 1 & \text{subtraction} \end{cases}$  (1.14)

The sign of the  $\Phi$  function,  $S_{\Phi}$ , must be switched if A and B have different signs, i.e., it should then be opposite to the performed operation. Hence,  $S_{\Phi}$  is obtained as

$$S_{\Phi} = S_A \oplus S_B \oplus op \tag{1.15}$$

and the  $\Phi$  function is then defined by

$$\Phi(x) = \begin{cases} \Phi^{+}(x) = \log_{2}|1+2^{x}| & S_{\Phi} = 0\\ \Phi^{-}(x) = \log_{2}|1-2^{x}| & S_{\Phi} = 1 \end{cases}$$

(1.16)

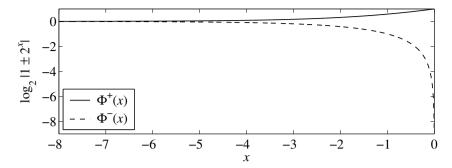

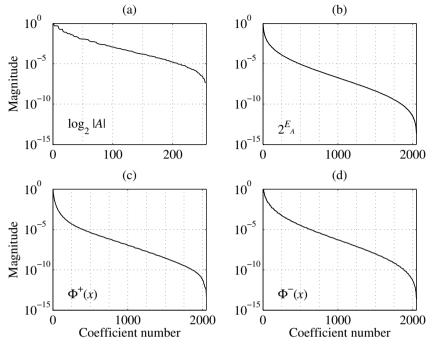

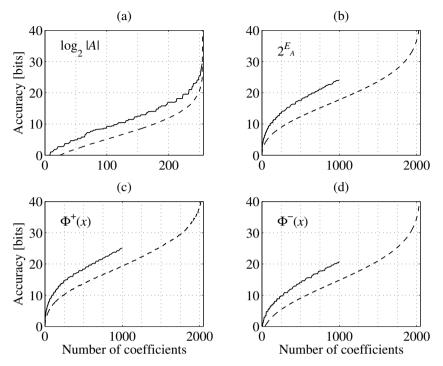

As stated before, x < 0. In Fig. 1.4, the characteristics of the two  $\Phi(x)$  functions are shown. Note that the maximum value of  $\Phi^+(x)$  is 1, i.e., no integer part is required for the corresponding look-up table.

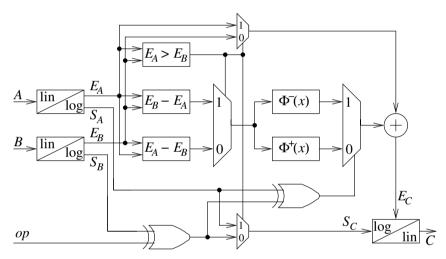

The complete schematic for an addition/subtraction, including the conversions to and from the logarithmic domain, is illustrated in Fig. 1.5. This design can be used as a testbench to verify the functionality of the look-up tables. Implementation of these tables will be considered in Section 6.4. Note that the architecture in Fig. 1.5 can be improved from a power consumption point of view by turning off parts that are not used in a specific computation.

**Figure 1.4** The  $\Phi(x)$  functions used to perform addition and subtraction in logarithmic number systems.

**Figure 1.5** Architecture for computing addition and subtraction using logarithmic number systems.

# **1.4 Constant Multiplication**

Multiplication with a constant is commonly used in DSP circuits, such as digital filters [142]. It is possible to use shift-and-add operations [90] to efficiently implement this type of multiplication. Since the general multipliers are replaced by shifts, adders, and subtractors this is sometimes referred to as multiplierless implementation. As the complexity is similar for adders and subtractors we will refer to both as adders, and adder cost will be used to denote the total number of adders/subtractors.

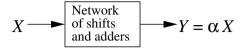

Figure 1.6 The principle of single-constant multiplication.

#### 1.4.1 Single-Constant Multiplication

The general design of a multiplier is shown in Fig. 1.6. The input data, X, is multiplied with a specific coefficient,  $\alpha$ , and the output, Y, is the result.

The method based on the CSD representation, which was discussed in Section 1.2.2, is commonly used to implement single-constant multipliers [50]. However, in many cases multipliers can be implemented more efficiently using other structures that require fewer operations [57]. Most work has focused on minimizing the adder cost [24],[37],[42], while the shifts are assumed to be free.

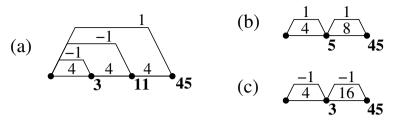

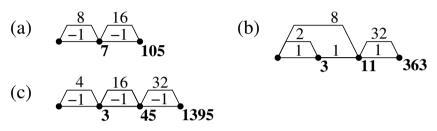

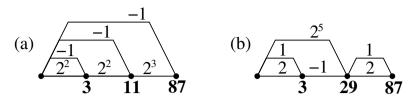

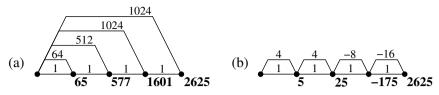

Consider, for example, the coefficient 45, which has the CSD representation  $10\overline{1}0\overline{1}01$ . The corresponding realization is shown in Fig. 1.7 (a), where 45 is computed as 64 - 16 - 4 + 1. Note that a left shift correspond to a multiplication by two. If the realization in Fig. 1.7 (b) is used instead, the adder cost is reduced from 3 to 2. Here, the constant 45 is obtained as  $5 \cdot 9 = (1 + 4)(1 + 8)$ . Furthermore, the number of shift operations is also reduced from 3 to 2, while the number of actual shifts is reduced from 6 to 5. For relatively short coefficient wordlengths, it is possible to find the most beneficial realization of each constant by an exhaustive search. Results on this will be given in Chapter 2.

#### Subexpression Sharing

Subexpression sharing was introduced in [48] as a method to utilize redundancy between FIR filter coefficients to reduce the number of required adders. However, subexpression sharing is also a commonly applied method in algorithms for design of single-constant multipliers.

In the CSD representation of 45,  $10\overline{10101}$ , the patterns  $10\overline{1}$  and  $\overline{101}$ , which correspond to  $\pm 3$ , are both included. Hence, the coefficient can be obtained as (4 - 1)(16 - 1) where the first part gives the value of the subexpression and the second part corresponds to the weight and sign difference. This structure is shown in Fig. 1.7 (c). Another set of subexpressions that can be found in the CSD representation of 45 is  $1000\overline{1}$  and  $\overline{10001}$ , which corresponds to (16 - 1)(4 - 1), i.e., the two stages in Fig. 1.7 (c) are performed in reversed order.

Figure 1.7 Different realizations of multiplication with the coefficient 45. The symbol  $\leq M$  is used to indicate *M* left shifts.

It is clear that the results are representation dependent, and in [114] it was shown that better results may be found if other MSD representations than CSD are used.

An algorithm introduced in [30], generates all SD representations of an integer using a specified number k of extra nonzero digits compared with the minimum, i.e., above that used by CSD. So, if k = 0, then all MSD representations are produced. For a heuristic approach, it has been shown that single-constant multipliers can be designed using fewer adders when k > 0 [29],[42]. In this approach, a subexpression sharing algorithm, for example the one in [48], is applied to all SD representations using at most k extra nonzero digits. The multiplier design with the lowest adder cost is then selected.

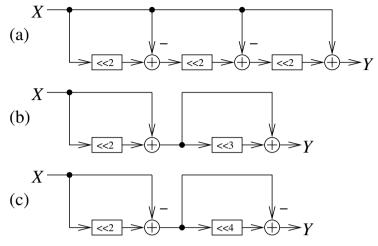

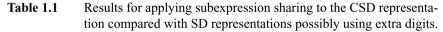

The CSD and the best SD representations for three different coefficients are given in Table 1.1, where the resulting number of required adders is also included. The smallest integer for which another MSD representation gives a better result than CSD is 105. The coefficient 363 is the smallest integer where a representation with one extra nonzero digit, i.e., k = 1, gives a better result than any MSD representation. The smallest integer where a representation with two extra nonzero digits, i.e., k = 2, gives a better result than any representation with up to one extra nonzero digit is 1395. These three coefficients can be realized as shown in Fig. 1.8. Note that the shifts sometimes can be placed in more than one way. For example, the first two adders in Fig. 1.18 (b) are used to com-

**Figure 1.8** Realization of single-constant multiplication using subexpression sharing for the coefficients (a) 105, (b) 363, and (c) 1395.

| Coefficient | CSD            |        |              | Best SD                                                    |        |

|-------------|----------------|--------|--------------|------------------------------------------------------------|--------|

|             | Representation | Adders | Extra digits | Representation                                             | Adders |

| 105         | 10101001       | 3      | 0            | 10011001                                                   | 2      |

| 363         | 1010010101     | 4      | 1            | 101101011                                                  | 3      |

| 1395        | 101010010101   | 4      | 2            | $10\overline{1}0\overline{1}\overline{1}11010\overline{1}$ | 3      |

pute 11, which here is done according to the expression (1 + 2) + 8. However, 11 can also be obtained as  $(1 + 4) \cdot 2 + 1$ .

### 1.4.2 Multiple-Constant Multiplication

In some applications, one signal is to be multiplied with several constant coefficients, as shown in Fig. 1.9. An example of this is the transposed direct form FIR filter where a multiplier block is used, as marked by the dashed box in Fig. 1.1 (b). A simple method to realize multiplier blocks is to implement each multiplier separately, for example, using the methods discussed in the previous section. However, multiplier blocks can be more

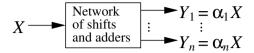

Figure 1.9 The principle of multiple-constant multiplication.

efficiently implemented by using structures that make use of redundant partial results between the coefficients in the shift-and-add network, and thereby reduce the required number of components.

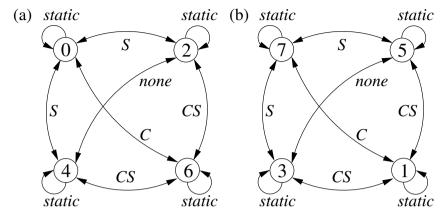

The implementation of FIR filters using shift-and-add based multipliers has received considerable attention during the last decade, and is referred to as the multiple-constant multiplication (MCM) problem. The MCM algorithms can be divided into three groups based on the operation of the algorithm; subexpression sharing [28],[48],[95],[115],[118], difference methods [38],[40],[43],[98],[108], and graph based methods [7], [25],[26],[144]. Heuristics based on subexpression sharing, usually represent each coefficient using the CSD representation, and subexpressions are sought among the coefficients. In difference algorithms, the fact that the successive coefficient values vary slowly in frequency selective FIR filters is exploited by realizing the differences between the coefficients. The graph algorithms are not representation dependent since the nodes simply have integer values. New values are obtained by adding/subtracting existing nodes. Graph based methods will be used in Chapters 2 and 4 to solve MCM problems.

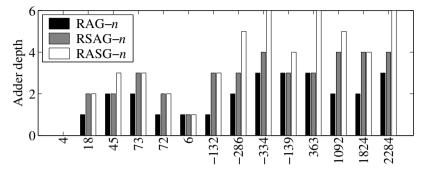

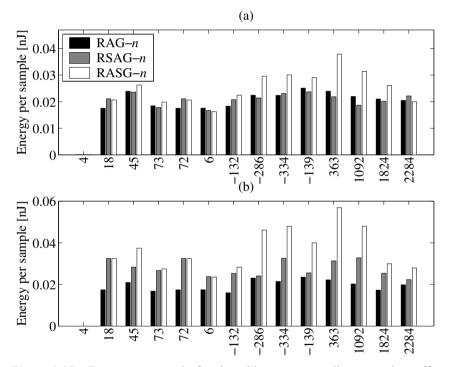

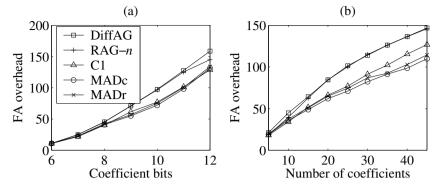

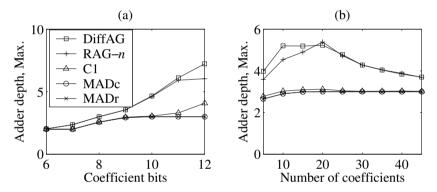

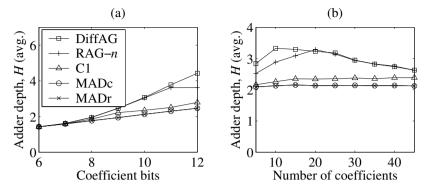

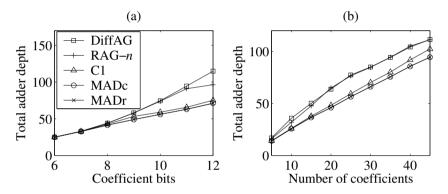

The only considered objective function for most of the MCM algorithms is to minimize the adder cost. However, besides complexity, the adder depth, i.e., the number of cascaded adders, has also been considered [26],[95]. This is partly motivated by the effect on the energy consumption, which in general is lower for a reduced adder depth [21],[22],[23].

Furthermore, the MCM problem has been extended by including the delay elements inherent in FIR filters in the redundancy utilization [48], and to matrix multiplications [27].

By transposing the shift-and-add network, corresponding to a multiplier block, a sum-of-products is obtained. This is illustrated by the dashed box in Fig. 1.1 (a), i.e., a multiplier block together with the structural adders correspond to a sum-of-products. Hence, MCM techniques can be applied to realize both direct form and transposed direct form FIR filters.

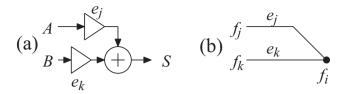

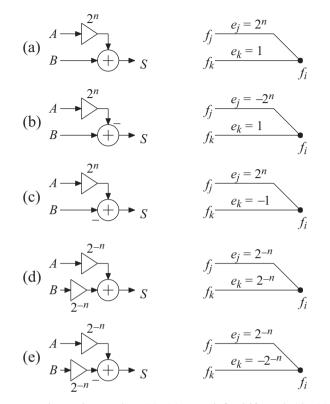

**Figure 1.10** Multiplier segment. (a) Arithmetic implementation of a shift-andadd operation and (b) the corresponding graph representation.

#### 1.4.3 Graph Representation

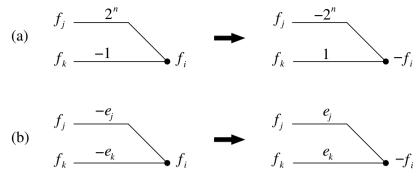

The graph representation of constant multipliers was introduced in [7], and used in, for example, [24], [25], [27], and [37]. As discussed in the two previous sections, single- and multiple-constant multiplications are composed of networks of shifts and adders. These networks can be represented using directed acyclic graphs with the following characteristics [24],[37].

- The input is the vertex that has in-degree zero, and vertices that have out-degree zero are outputs. However, for MCM, vertices with an out-degree larger than zero may also be outputs.

- Each vertex has out-degree larger than or equal to one, except for the output vertices, which may have out-degree zero.

- Each vertex that has an in-degree of two corresponds to an adder (subtractor). Hence, the adder cost is equal to the number of vertices with in-degree two.

- Each edge is assigned a value of  $\pm 2^n$ , which corresponds to |n| shifts, i.e., a multiplication by a power-of-two, and the sign for any subsequent addition or subtraction.

Although these graphs are directed, this is usually not marked, i.e., it is understood without saying that the leftmost node is the input and that operations are performed from left to right.

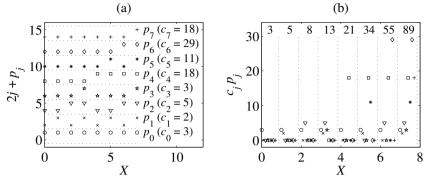

The nodes are assigned values, which are referred to as fundamentals. A fundamental,  $f_i$ , is computed from two other fundamentals  $f_i$  and  $f_k$  as

$$f_i = e_j f_j + e_k f_k \tag{1.17}$$

where  $e_j$  and  $e_k$  are edge values, as illustrated in Fig. 1.10. The obtained signal value in this node will then be  $f_i$  times the input signal.

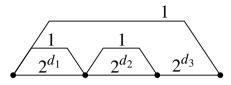

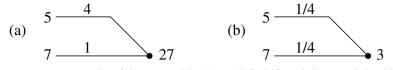

Figure 1.11 Graph representation of the realizations in Fig. 1.7.

Figure 1.12 Graph representation of the realizations in Fig. 1.8.

Some examples of the graph representation are shown in Figs. 1.11 and 1.12. Note that these illustrations are simpler than Figs. 1.7 and 1.8 although they contain the same information.

In [37], a vertex reduced representation of graph multipliers was introduced. However, since the placement of shift operations sometimes is of importance, the original, fully specified, graph representation will be used throughout this thesis.

#### 1.4.4 Terms used for Graph Based MCM Algorithms

Here, terms that will be used in descriptions of MCM algorithms are introduced.

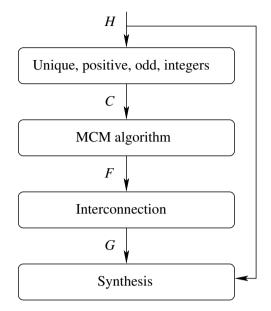

As discussed earlier, the MCM problem is to determine a shift-andadd network that can realize multiplications of a single input with a set of coefficients, H. It is usually sufficient to only consider odd integer coefficients, since even and fractional coefficients can be obtained by an appropriate shift operation at the output of the multiplier. In most cases, the sign of the coefficient can also be compensated for in other parts of the implementation. Hence, the coefficient set, C, which is the input to the MCM algorithm as illustrated in Fig. 1.13, is often assumed to only contain unique positive odd integers.

Figure 1.13 Design path for MCM blocks.

Figure 1.14 Graph representation for a shift-and-add MCM block.

If |H| = 1, i.e., there is only one coefficient in the set, the MCM problem is transformed into a single-constant problem. The design path in Fig. 1.13 may still be used, although there exist better strategies than to use general MCM algorithms for this special case, as discussed in Section 1.4.1. Also for the case when |H| = 2, there exist more specialized design techniques [31].

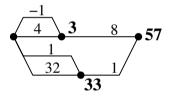

As an example, consider the coefficient set  $C = \{33, 57\}$ . The coefficient 33 can be obtained directly from the input as  $1 + 2^5$ . However, the coefficient 57 can not be realized and a new node must therefore be included. For example, the value 3 solves the problem by computing the constant 57 as  $33 + 3 \cdot 2^3$ , which is illustrated by the graph in Fig. 1.14. Hence, the set of extra fundamentals is  $E = \{3\}$ , and the total fundamental set  $F = C \cup E = \{3, 33, 57\}$  is the output of the MCM algorithm. The fundamental set include all vertex values. However, the input vertex value, 1, is usually excluded, since it does not require any adder.

The interconnection graph, G, can be given in a table format. For the graph in Fig. 1.14, the corresponding table is

$$G = \begin{vmatrix} 3 & 1 & 1 & -1 & 4 & 1 \\ 33 & 1 & 1 & 1 & 32 & 1 \\ 57 & 3 & 33 & 8 & 1 & 2 \end{vmatrix}$$

(1.18)

In [23] such an interconnection table was referred to as the Dempster format. Here, the first column is the fundamental value,  $f_i$ , columns 2 and 3 are the values of the input vertices,  $f_j$  and  $f_k$ , and columns 4 and 5 are the values of the input edges,  $e_j$  and  $e_k$ . Finally, the sixth column includes the adder depth,  $D_i$ , defined as one more than the largest depth of the input nodes according to

$$D_{i} = \max(D_{i}, D_{k}) + 1 \tag{1.19}$$

The theoretical minimum depth,  $D_{i, min}$ , for a fundamental,  $f_i$ , is well defined and computed as [45]

$$D_{i,min} = \left\lceil \log_2 S(f_i) \right\rceil \tag{1.20}$$

where  $S(f_i)$  denotes the number of nonzero digits in a minimum signeddigit representation of  $f_i$ .

## 1.5 Computer Arithmetic

The operations used in constant multiplication, i.e., additions and shifts, can be implemented using either parallel or serial arithmetic. Here, these two different approaches are discussed. Furthermore, the redundant carry-save arithmetic is also briefly introduced.

#### 1.5.1 Parallel Arithmetic

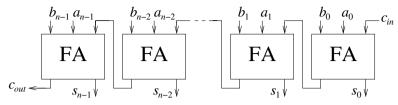

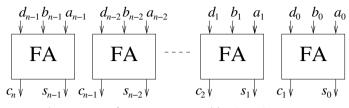

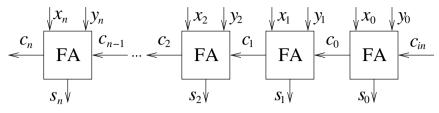

Using parallel arithmetic, all bits of the input data word are processed concurrently. This makes it possible to achieve a high throughput, at a relatively low clock frequency. In Fig. 1.15, the straightforward architecture for adding two signals, A and B, is given. A drawback with the ripple-carry adder (RCA) is that the carry propagation path is linearly proportional to the input wordlength. Several other carry propagation adders

Figure 1.15 The structure for a ripple-carry adder (RCA).

(CPA) have been proposed, where different types of carry acceleration are used [8],[75],[149]. However, these techniques always come with a cost of increased area.

The carry propagation can be avoided by using a redundant number system, as mentioned in Section 1.2.2. For example, the carry-save representation, which will be presented in Section 1.5.3.

#### 1.5.2 Serial Arithmetic

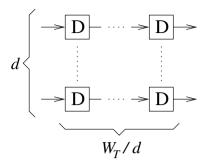

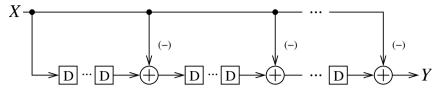

In digit-serial arithmetic, each data word is divided into digits that are processed one digit at a time [47],[130]. The number of bits in each digit is usually denoted the digit-size, d. This provides a trade-off between area, speed, and energy consumption [47],[134]. For the special case where d equals the data wordlength we have bit-parallel processing, and when d equals one we have bit-serial processing.

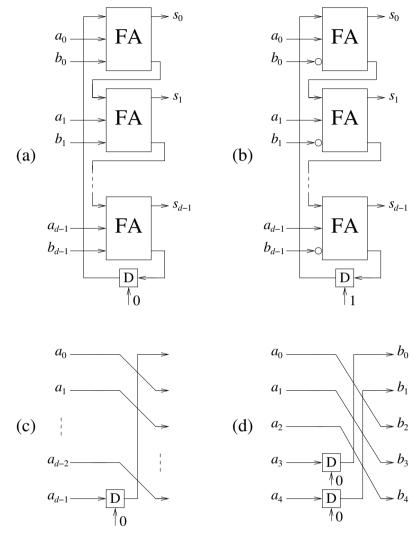

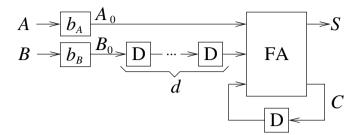

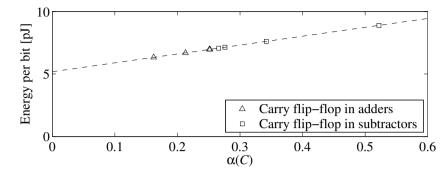

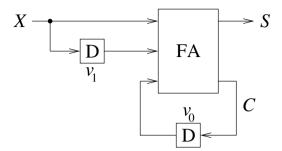

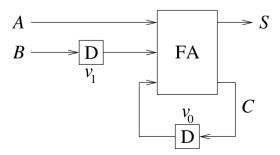

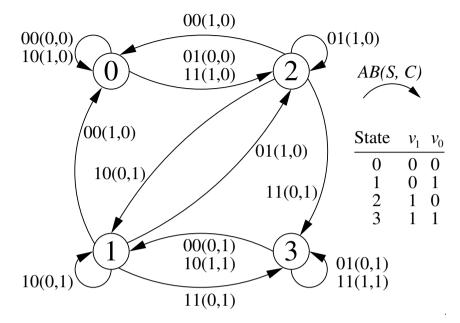

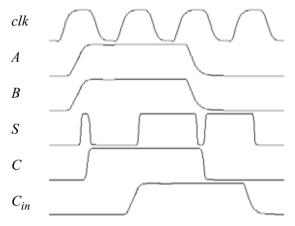

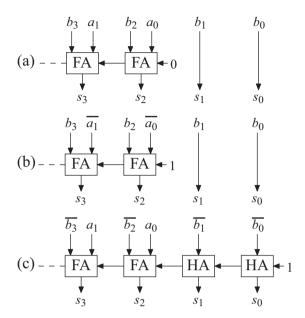

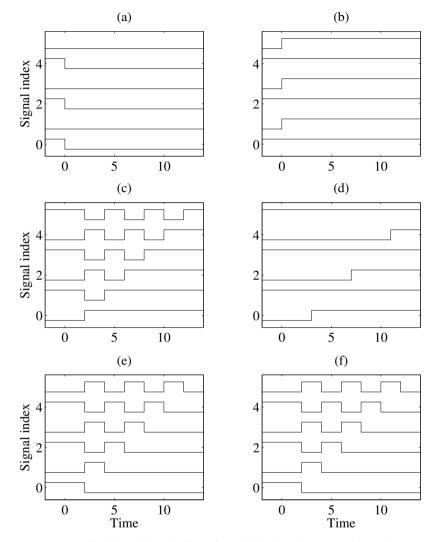

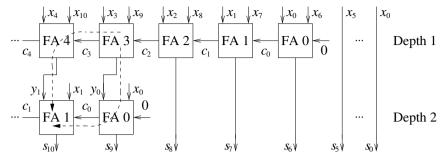

Digit-serial processing elements can be derived either by unfolding bit-serial processing elements [111] or by folding bit-parallel processing elements [112]. In Fig. 1.16, a digit-serial adder, subtractor, and shift are shown. These are the operations that are required to implement constant multiplication, as discussed in Section 1.4. Note that the carry feedback register should be set to one at the beginning of a subtract operation. Each left shift, corresponding to a multiplication by two, requires one flip-flop, as illustrated by Fig. 1.16 (d). Digit-serial arithmetic operations can be performed by either processing the most significant bit (MSB) first or the least significant bit (LSB) first. If the MSB is processed first, redundant arithmetic is required [149]. In this thesis, we will only consider the case with LSB first since this is less complicated.

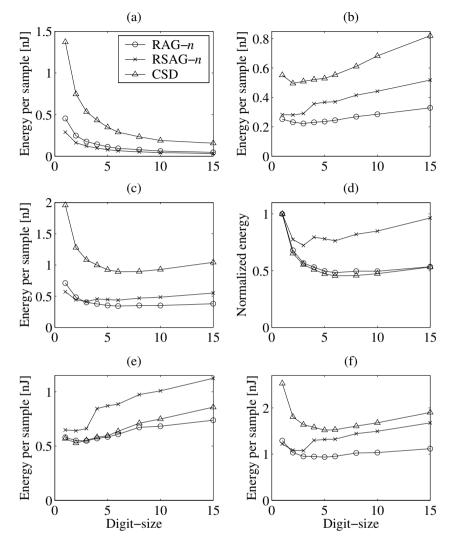

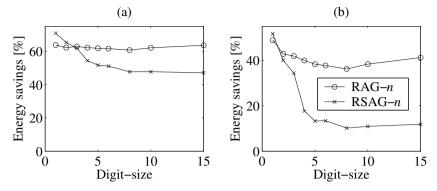

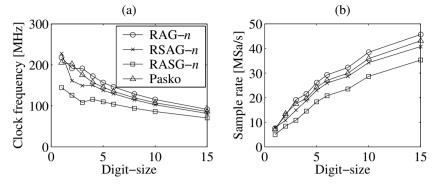

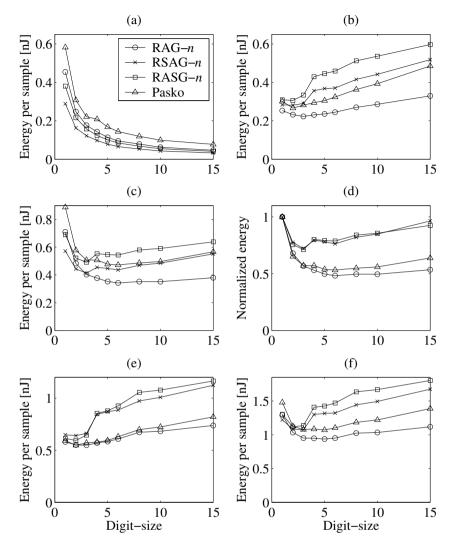

It is clear that serial architectures with a small digit-size have the advantage of area efficient processing elements. Furthermore, the routing complexity for communication between operators, including the required number of input and output pads, is also reduced. Another benefit is that the carry propagation path is short, since it increases linearly with the digit-size. On the other hand, only a few bits of the input data word are processed during each clock cycle for a small digit-size. Hence, a high clock frequency is required to obtain a reasonable throughput. How the energy consumption depend on the digit-size is difficult to predict, and this will be investigated in Sections 2.4.5 and 2.6.

One main difference compared to parallel arithmetic is that the shift operations can be hardwired, i.e., realized without using any flip-flops, in a bit-parallel architecture. However, the flip-flops included in serial shifts have the benefit of reducing the glitch propagation between subsequent adders/subtractors. To prevent glitches further, pipelining can be introduced, which also increases the throughput. Note that less hardware is needed for pipelining in serial arithmetic compared to the parallel case. For example, in bit-serial arithmetic a single flip-flop is required in the pipelining register between two operations. In addition, the available shifts can be rearranged to obtain an improved design, i.e., with a shorter critical path.

#### **Complexity of Serial Constant Multiplication**

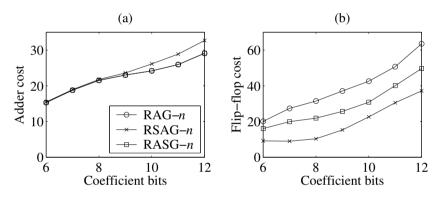

As mentioned before, shifts are normally assumed to be free as they can be hardwired in a bit-parallel implementation. However, since a serial shift requires a flip-flop, as seen in Fig. 1.16 (c), it must be taken into account when the overall complexity is considered. The total number of shifts,  $n_{SH}$ , will be referred to as the flip-flop cost.

From G and F, as defined in Section 1.4.4, the flip-flop cost can be computed as

$$n_{SH} = \sum_{i=1}^{M+1} \log_2(e(i))$$

(1.21)

where *M* is the length of *F*. The vector *e* contains the largest absolute edge value at the output of each vertex, including the input. Hence, e(i) is computed for each node value in the set  $F_1 = 1 \cup F$  as

$$e(i) = \max(1, |G_{4,5}(k)|) \qquad \begin{cases} \forall k | G_{2,3}(k) = F_1\{i\} \\ k \in \{1, 2, ..., 2M\} \\ i \in \{1, 2, ..., M+1\} \end{cases}$$

(1.22)

where  $G_{i, j}$  is a vector containing the elements in columns *i* and *j* of *G*.

Figure 1.16 Digit-serial (a) adder, (b) subtractor, and (c) left shift. (d) Two cascaded left shifts with digit-size five, i.e., B = 4A and d = 5.

Using (1.21) and (1.22), the flip-flop cost for the graph in Fig. 1.14 is obtained as

$$F_1 = \{1, 3, 33, 57\} \implies e = \begin{bmatrix} 32 & 8 & 1 & 1 \end{bmatrix} \implies n_{SH} = 5 + 3 = 8 (1.23)$$

A digit-serial implementation with d = 1 for this MCM example design is shown in Fig. 1.17. Note that the first two shifts are shared, which illus-

**Figure 1.17** Bit-serial implementation of the multiplier coefficients  $\alpha_1 = 33$  and  $\alpha_2 = 57$ , using one subtractor, two adders, and eight shifts.

trates why it is enough to only consider the maximum outgoing edge weight from each node, as defined by (1.22).

From this, it is obvious that an MCM algorithm that considers the number of shifts may yield digit-serial filter implementations with smaller overall complexity. As discussed in Section 1.4.4, it is normally sufficient to only realize odd coefficients. However, since the placement of shifts is important when serial arithmetic is used, it might be preferable to keep the even coefficients within the MCM algorithm. This will be further investigated in Chapter 2.

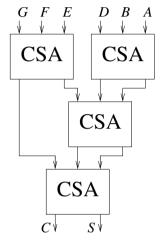

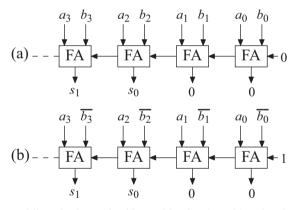

#### 1.5.3 Carry-Save Arithmetic

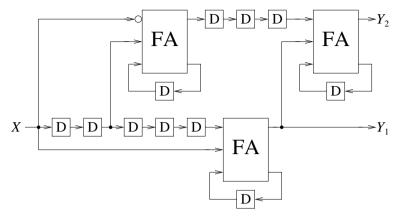

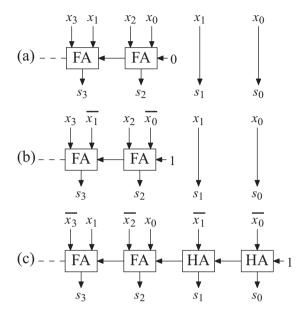

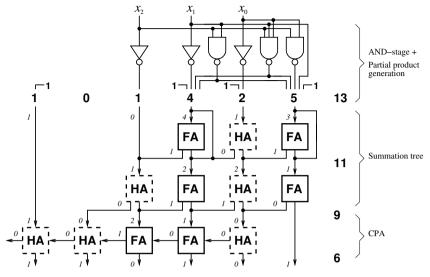

As mentioned earlier, the redundant carry-save representation can be used to avoid carry propagation. The architecture of a carry-save adder (CSA) is shown in Fig. 1.18. Note that the critical path is a single full adder. As can be seen, the adder has three inputs and two outputs. Hence, a number is here represented by two data, one sum and one carry vector. Conversion to the nonredundant two's-complement representation can be performed by simply adding the two vectors. The adder used for this is often referred to as a vector merging adder (VMA), and can be realized by any CPA.

An area where carry-save arithmetic is commonly used is for adding several operands in an adder tree architecture. An example of this, using a Wallace tree [145], is illustrated in Fig. 1.19. As can be seen, each CSA reduces the number of operands by one. For this tree, the critical path is only three full adders.

Figure 1.18 The structure for a carry-save adder (CSA).

Figure 1.19 The structure for an adder tree with six inputs using carry-save arithmetic, where S + C = A + B + D + E + F + G.

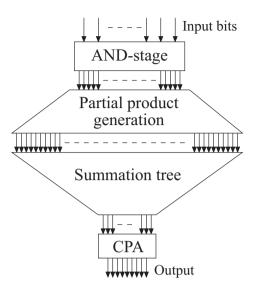

The carry-save arithmetic has been used for high-speed DSP algorithms [107] and constant multiplication [36],[39]. However, in this thesis, it will only be used for the adder trees in Chapter 6.

## 1.6 Power and Energy Consumption

Low power design is always desirable in integrated circuits. To obtain this, it is necessary to find accurate and efficient methods that can be used to estimate the power consumption. In digital CMOS circuits, the dominating part of the total power consumption is the dynamic part. Although the relation between static and dynamic power becomes more equal because of scaling. Note that serial arithmetic can be used to decrease the leakage power compared to parallel implementations due to the reduced number of devices [104],[105]. However, since the static part mainly depends on the process and transistor level circuitry rather than the design on the algorithm and arithmetic levels, the focus throughout this thesis will be on the dynamic part. Furthermore, the power figure of interest is the average power since this, opposed to peak power, determines the battery life time.

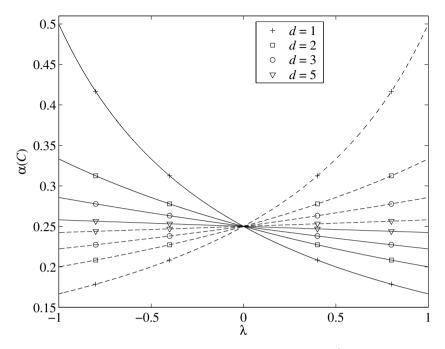

The average dynamic power can be approximated by

$$P_{dyn} = \frac{1}{2} \alpha f_c C_L V_{DD}^2 \tag{1.24}$$

where  $\alpha$  is the switching activity,  $f_c$  is the clock frequency,  $C_L$  is the load capacitance, and  $V_{DD}$  is the supply voltage. All these parameters, except  $\alpha$ , are normally defined by the layout and specification of the circuit. Hence, an important task is to develop accurate models for estimation of the switching activity, i.e., the average number of transitions between the two logic levels per clock cycle. For example, the switching activity is 2 for a clock signal and 0.5 for a random signal.

In this thesis, several examples are presented where we will see that implementations with the same functionality may differ significantly in power consumption. Hence, an algorithm, used to realize for example a digital filter, can often be modified to achieve lower power [13].

There exist many general methods for reducing the power consumption. An efficient method is to use power down techniques such as clock gating, which according to (1.24) result in zero dynamic power while in idle mode. Another method to reduce the switching activity is to limit the affect of glitches, i.e., the unwanted transitions. This can be done by equalizing the propagation delay between logical paths, either by introducing buffers [122] or by transistor sizing [152]. The power due to glitch spreading can also be reduced by pipelining [84],[125], i.e., by propagating delay elements into nonrecursive parts of the design, since shorter paths then are obtained. Furthermore, pipelining increase the throughput [12],[53], which can be traded for power by scaling the supply voltage [14]. However, the margin for power supply voltage scaling is naturally restricted in new technologies. In multiple-threshold voltage CMOS processes [100], high-speed low-threshold transistors can be used in time critical parts, while low-leakage high-threshold transistors are used in the rest of the circuit.

When different implementations are to be compared, a measure that does not depend on the clock frequency,  $f_c$ , used in the simulation, is often preferable. Hence, the energy consumption, E, can be used instead of the power, P, by computing

$$E = \frac{P}{f_c} \tag{1.25}$$

Since the number of clock cycles required to perform one computation varies with the digit-size in serial arithmetic, we will in this work use energy per computation, or energy per sample, as comparison measure for such implementations.

# 1.7 Outline and Main Contributions

Here, the outline of the rest of this thesis is given. In addition, related publications are specified. Papers that are not included in the thesis, although related, are marked with the symbol †. Parts of this work was earlier presented in

K. Johansson, Low Power and Low Complexity Constant Multiplication Using Serial Arithmetic, Linköping Studies in Science and Technology, Thesis No. 1249, ISBN 91-85523-76-3, Linköping, Sweden, Apr. 2006.

# Chapter 2

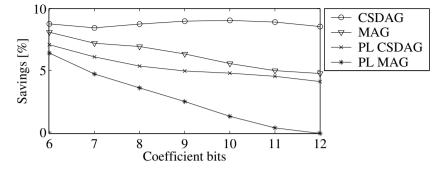

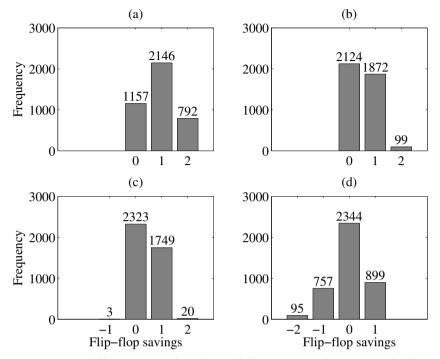

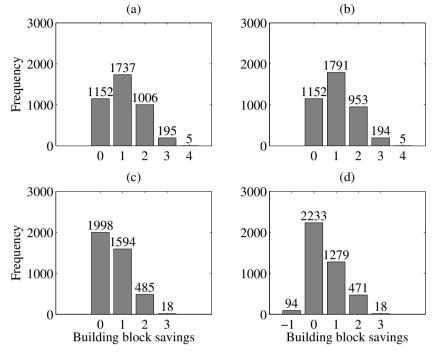

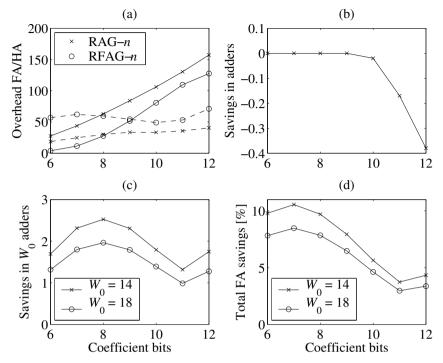

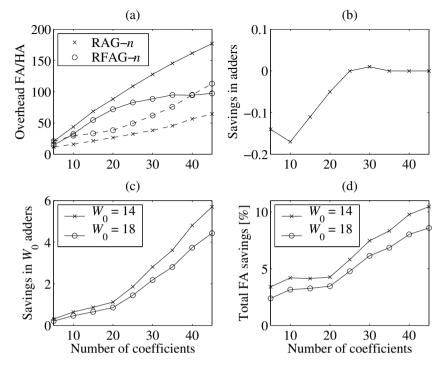

The complexity of constant multipliers using serial arithmetic is discussed in Chapter 2. In the first part, all possible graph topologies containing up to four adders are considered for single-constant multipliers. In the second part, two new algorithms for multiple-constant multiplication using serial arithmetic are presented and compared to an algorithm designed for parallel arithmetic. This chapter is based on the following publications

- K. Johansson, O. Gustafsson, A. G. Dempster, and L. Wanhammar, "Algorithm to reduce the number of shifts and additions in multiplier blocks using serial arithmetic," in *Proc. IEEE Mediterranean Electrotechnical Conf.*, Dubrovnik, Croatia, May 12–15, 2004, vol. 1, pp. 197–200.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Low-complexity bit-serial constant-coefficient multipliers," in *Proc. IEEE Int. Symp. Circuits Syst.*, Vancouver, Canada, May 23–26, 2004, vol. 3, pp. 649–652.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Implementation of low-complexity FIR filters using serial arithmetic," in *Proc. IEEE Int. Symp. Circuits Syst.*, Kobe, Japan, May 23–26, 2005, vol. 2, pp. 1449– 1452.

- K. Johansson, O. Gustafsson, A. G. Dempster, and L. Wanhammar, "Trade-offs in low power multiplier blocks using serial arithmetic," in *Proc. National Conf. Radio Science (RVK)*, Linköping, Sweden, June 14–16, 2005, pp. 271–274.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Trade-offs in multiplier block algorithms for low power digit-serial FIR filters," in *Proc. WSEAS Int. Conf. Circuits*, Vouliagmeni, Greece, July 10–12, 2006.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Multiple constant multiplication for digit-serial implementation of low power FIR filters," *WSEAS Trans. Circuits Syst.*, vol. 5, no. 7, pp. 1001–1008, July 2006.

# Chapter 3

Here, a novel method to compute the switching activities in bit-serial constant multipliers is presented. All possible graph topologies containing up to four adders are considered. The switching activities for most graph topologies can be obtained by the derived equations. However, look-up tables are required for some graphs. Related publications are

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Switching activity in bit-serial constant coefficient serial/parallel multipliers," in *Proc. IEEE NorChip Conf.*, Riga, Latvia, Nov. 10–11, 2003, pp. 260–263.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Power estimation for bit-serial constant coefficient multipliers," in *Proc. Swedish System-on-Chip Conf.*, Båstad, Sweden, Apr. 13–14, 2004.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Switching activity in bit-serial constant coefficient multipliers," in *Proc. IEEE Int. Symp. Circuits Syst.*, Vancouver, Canada, May 23–26, 2004, vol. 2, pp. 469– 472.

# Chapter 4

The complexity of constant multiplication using parallel arithmetic is investigated and optimized at the bit-level. A complexity model is developed, and an MCM algorithm based on this model is shown to reduce the number of full adders. Different strategies to obtain an improved interconnection graph, given the fundamental set, are formulated. Finally, an MCM algorithm where all coefficients are realized at a minimum adder depth is presented. These ideas have been discussed in

- K. Johansson, O. Gustafsson, and L. Wanhammar, "A detailed complexity model for multiple constant multiplication and an algorithm to minimize the complexity," in *Proc. European Conf. Circuit Theory Design*, Cork, Ireland, Aug. 28–Sept. 2, 2005, vol. 3, pp. 465–468.

- O. Gustafsson, A. G. Dempster, K. Johansson, M. D. Macleod, and L. Wanhammar, "Simplified design of constant coefficient multipliers," *Circuits Syst. Signal Processing*, vol. 25, no. 2, pp. 225–251, Apr. 2006. †

- O. Gustafsson, K. Johansson, H. Johansson, and L. Wanhammar, "Implementation of polyphase decomposed FIR filters for interpolation and decimation using multiple constant multiplication techniques," in *Proc. Asia-Pacific Conf. Circuits Syst.*, Singapore, Dec. 4–7, 2006, pp. 924–927. †

- H. Johansson, O. Gustafsson, K. Johansson, and L. Wanhammar, "Adjustable fractional-delay FIR filters using the Farrow structure and multirate techniques," in *Proc. Asia-Pacific Conf. Circuits Syst.*, Singapore, Dec. 4–7, 2006, pp. 1055–1058. †

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Bit-level optimization of shift-and-add based FIR filters," in *Proc. IEEE Int. Conf. Electronics Circuits Syst.*, Marrakech, Morocco, Dec. 11–14, 2007, pp. 713–716.

- M. Abbas, F. Qureshi, Z. Sheikh, O. Gustafsson, H. Johansson, and K. Johansson, "Comparison of multiplierless implementation of nonlinear-phase versus linear-phase FIR filters," in *Proc. Asilomar Conf. Signals Syst. Comp.*, Pacific Grove, CA, Oct. 26–29, 2008. †

- K. Johansson, O. Gustafsson, L. S. DeBrunner, and L. Wanhammar, "Low power multiplierless FIR filters implemented using a minimum depth algorithm," in preparation.

# Chapter 5

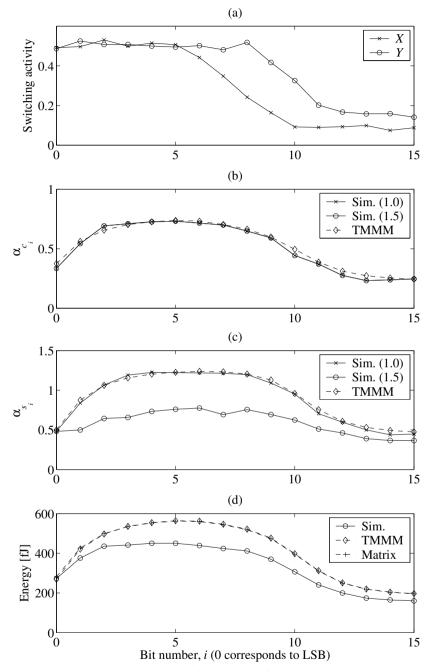

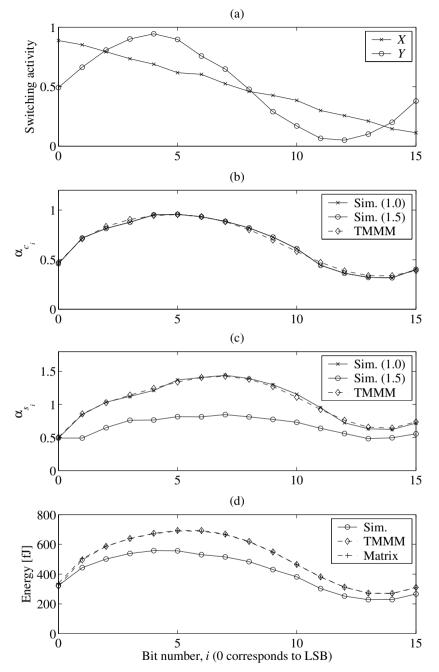

In this chapter, an approach to derive a detailed estimation of the energy consumption for ripple-carry adders is presented. The model includes both computation of the theoretic switching activity and the simulated energy consumption for each possible transition. Furthermore, the model can be used for any given correlation of the input data. The method is also simplified by adopting the dual bit type method [78]. Finally, the switching activity in constant multiplication is studied. An accurate model for single adder multipliers is presented. Parts of this work was previously published in

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Power estimation for ripple-carry adders with correlated input data," in *Proc. Int. Workshop Power Timing Modeling Optimization Simulation*, Santorini, Greece, Sept. 15–17, 2004, pp. 662–674.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Estimation of switching activity for ripple-carry adders adopting the dual bit type method," in *Proc. Swedish System-on-Chip Conf.*, Tammsvik, Sweden, Apr. 18–19, 2005.

- O. Gustafsson, S. T. Oskuii, K. Johansson, and P. G. Kjeldsberg, "Switching activity reduction of MAC-based FIR filters with correlated input data," in *Proc. Int. Workshop Power Timing Modeling Optimization Simulation*, Gothenburg, Sweden, Sept. 3–5, 2007, pp. 526–535. †

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Switching activity estimation for shift-and-add based constant multipliers," in *Proc. IEEE Int. Symp. Circuits Syst.*, Seattle, WA, May 18–21, 2008, pp. 676–679.

# **Chapter 6**

Function approximation is discussed in Chapter 6. A general method to rewrite any function as a sum of weighted bit-products is presented. It is shown that a majority of the bit-products can be neglected for many elementary functions, while still maintaining high accuracy. The proposed method can be implemented using a low complexity hardware architecture. In addition, it is possible to divide the architecture into sub-blocks, which may be turned off to reduce the energy consumption. To evaluate the presented approximation approach, functions that are required for conversions and addition in LNS are implemented. Furthermore, sine and cosine can be simultaneously computed. This work is covered in the listed publications

- L. Wanhammar, K. Johansson, and O. Gustafsson, "Efficient sine and cosine computation using a weighted sum of bit-products," in *Proc. European Conf. Circuit Theory Design*, Cork, Ireland, Aug. 28–Sept. 2, 2005, vol. 1, pp. 139–142.

- O. Gustafsson, K. Johansson, and L. Wanhammar, "Optimization and quantization effects for sine and cosine computation using a sum of bit-products," in *Proc. Asilomar Conf. Signals Syst. Comp.*, Pacific Grove, CA, Oct. 30–Nov. 2, 2005, pp. 1347–1351. †

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Low power architectures for sine and cosine computation using a sum of bit-products," in *Proc. IEEE NorChip Conf.*, Oulu, Finland, Nov. 21–22, 2005, pp. 161–164.

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Approximation of elementary functions using a weighted sum of bit-products," in *Proc. IEEE Int. Symp. Circuits Syst.*, Kos Island, Greece, May 21–24, 2006, pp. 795–798.

- O. Gustafsson and K. Johansson, "Multiplierless piecewise linear approximation of elementary functions," in *Proc. Asilomar Conf. Signals Syst. Comp.*, Pacific Grove, CA, Oct. 29–Nov. 1, 2006, pp. 1678– 1681. †

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Conversion and addition in logarithmic number systems using a sum of bit-products," in *Proc. IEEE NorChip Conf.*, Linköping, Sweden, Nov. 20–21, 2006, pp. 39–42.

- S. Tahmasbi Oskuii, K. Johansson, O. Gustafsson, and P. G. Kjeldsberg, "Power optimization of weighted bit-product summation tree for elementary function generator," in *Proc. IEEE Int. Symp. Circuits Syst.*, Seattle, WA, May 18–21, 2008, pp. 1240–1243. †

- K. Johansson, O. Gustafsson, and L. Wanhammar, "Implementation of elementary functions for logarithmic number systems," *IET Computers Digital Techniques (Selected Papers NorChip 2006)*, vol. 2, no. 4, pp. 295–304, July 2008.

- O. Gustafsson and K. Johansson, "An empirical study on standard cell synthesis of elementary function look-up tables," in *Proc. Asilomar Conf. Signals Syst. Comp.*, Pacific Grove, CA, Oct. 26–29, 2008. †

# Publications by the Author that are not Related to the Thesis

- T. Lindkvist, J. Löfvenberg, H. Ohlsson, K. Johansson, and L. Wanhammar, "A power-efficient, low-complexity, memoryless coding scheme for buses with dominating inter-wire capacitance," in *Proc. IEEE Int. Workshop System-on-Chip Real-Time Appl.*, Banff, Canada, July 19–21, 2004, pp. 257–262.

- H. Ohlsson, B Mesgarzadeh, K. Johansson, O. Gustafsson, P. Löwenborg, H. Johansson, and A. Alvandpour, "A 16 GSPS 0.18 μm CMOS decimator for single-bit ΣΔ-modulation," in *Proc. IEEE NorChip Conf.*, Oslo, Norway, Nov. 8–9, 2004, pp. 175–178.

- J. Löfvenberg, O. Gustafsson, K. Johansson, T. Lindkvist, H. Ohlsson, and L. Wanhammar, "New applications for coding theory in lowpower electronic circuits," in *Proc. Swedish System-on-Chip Conf.*, Tammsvik, Sweden, Apr. 18–19, 2005.

- J. Löfvenberg, O. Gustafsson, K. Johansson, T. Lindkvist, H. Ohlsson, and L. Wanhammar, "Coding schemes for deep sub-micron data buses," *National Conf. Radio Science (RVK)*, Linköping, Sweden, June 14–16, 2005, pp. 257–260.

- L. Wanhammar, B. Soltanian, K. Johansson, and O. Gustafsson, "Synthesis of circulator-tree wave digital filters," in *Proc. Int. Symp. Image Signal Processing Analysis*, Istanbul, Turkey, Sept. 27–29, 2007, pp. 206–211.

- L. Wanhammar, B. Soltanian, O. Gustafsson, and K. Johansson, "Synthesis of bandpass circulator-tree wave digital filters," in *Proc. IEEE Int. Conf. Electronics Circuits Syst.*, Malta, Aug. 31–Sept. 3, 2008.

# 2

# COMPLEXITY OF SERIAL CONSTANT MULTIPLIERS

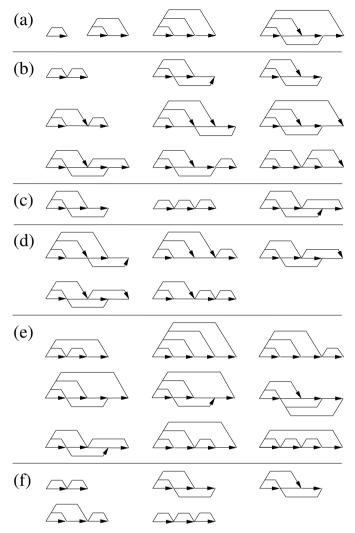

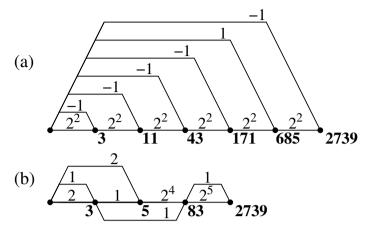

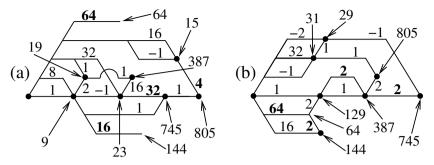

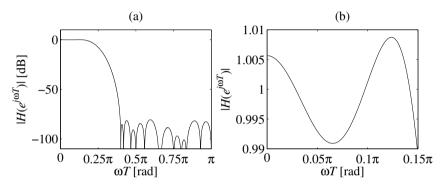

In this chapter, the possibilities to minimize the complexity of bit-serial single-constant multipliers are investigated [57]. This is done in terms of the required number of building blocks, which includes adders and shifts. The multipliers are described using a graph representation. It is shown that a minimum set of graphs, required to obtain optimal results given certain restrictions, can be found.

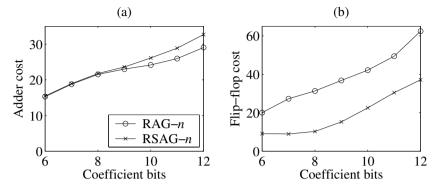

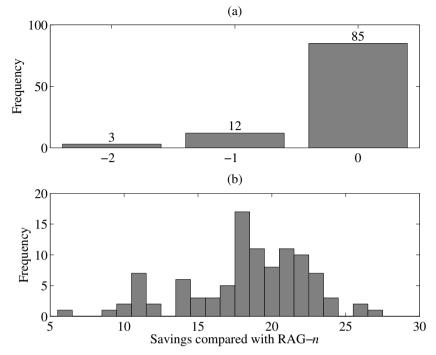

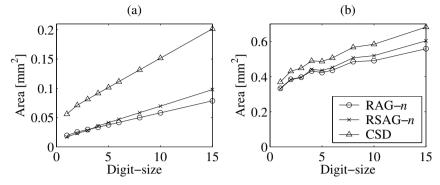

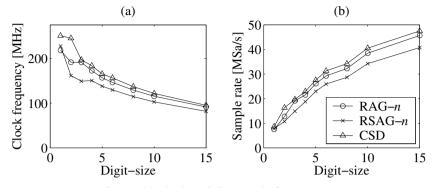

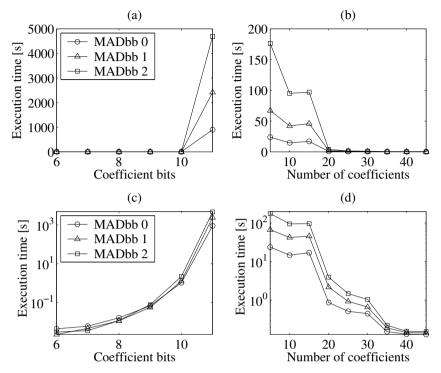

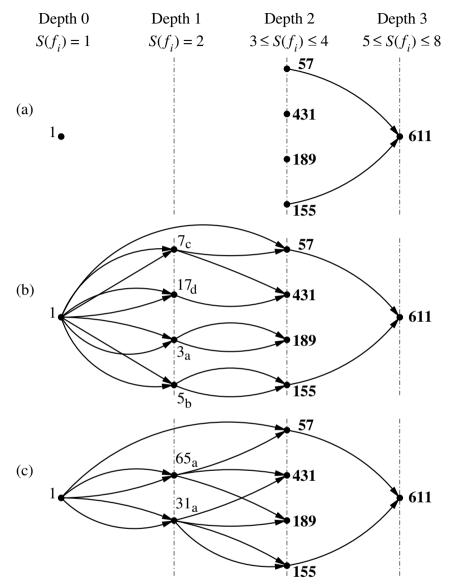

In the case of single-constant multipliers, the number of possible solutions can be limited because of the finite number of graph topologies. However, if a shift-and-add network realizing several coefficients is required, a multiple-constant multiplication (MCM) problem is obtained. Different heuristic algorithms can then be used to reduce the complexity, by utilizing the redundancy between the coefficients. Two algorithms suitable to achieve efficient realization of MCM using serial arithmetic are presented [56],[62],[66]. It is shown that the new algorithms reduce the total complexity significantly.

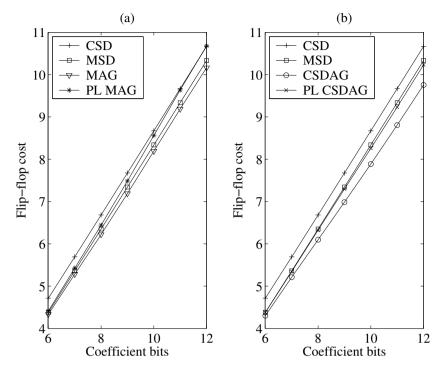

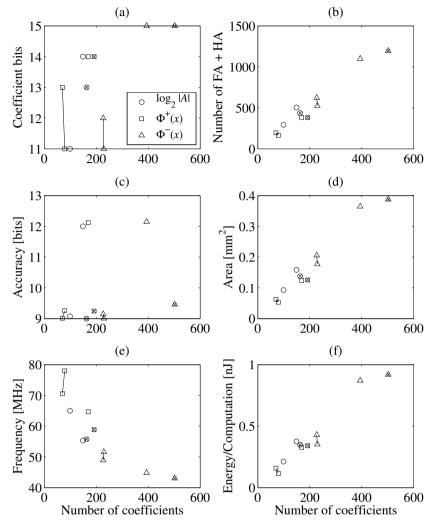

Furthermore, we study the trade-offs in implementations of FIR filters using MCM and digit-serial arithmetic. Comparisons considering area, speed, and energy consumption, with respect to the digit-size, are performed [61],[67].

# 2.1 Graph Multipliers

In this section, different types of single-constant graph multipliers will be defined, with respect to constraints on adder cost and throughput. Furthermore, the possibilities to exclude some graphs from the search space are examined.

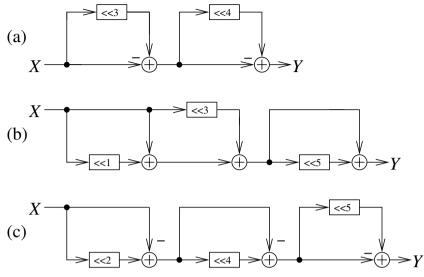

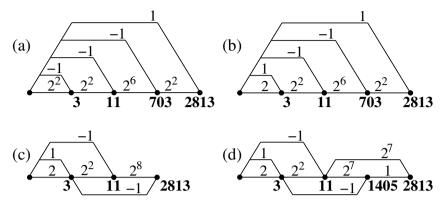

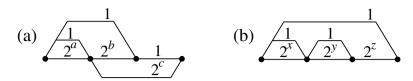

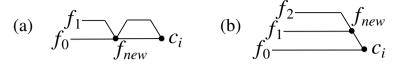

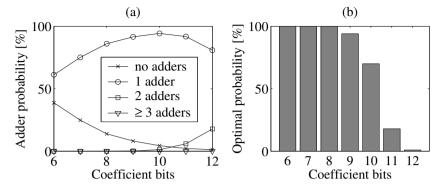

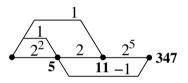

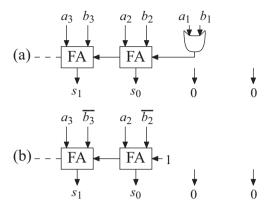

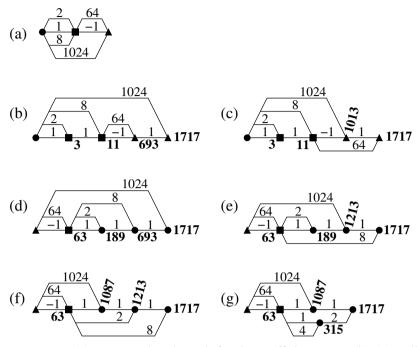

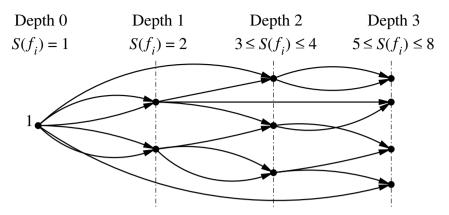

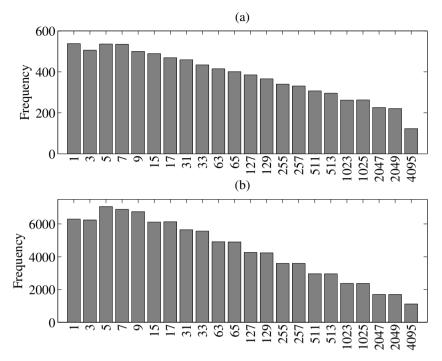

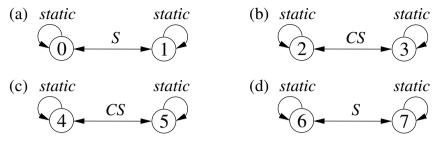

The investigation covers all coefficients up to 4095 and all types of graph multipliers containing up to four adders. All possible graphs, using the representation discussed in Section 1.4.3, for adder costs from 1 to 4 are presented in Fig. 2.1 [24].

Note that although bit-serial arithmetic will be assumed for the multipliers, results considering adder and flip-flop costs are generally also valid for any digit-serial implementation. However, the number of registers that are required to perform pipelining depend on the digit-size. Furthermore, the cost difference between adders and shifts becomes higher for larger digit-sizes, since the number of full adders increases linearly while the number of flip-flops is constant. Hence, such trade-offs are mainly of interest for small digit-sizes.

# 2.1.1 Multiplier Types

Different multiplier types can be defined based on the requirements considering adder cost, flip-flop cost, and pipelining. The types that will be discussed here are described in the following.

CSD – Canonic Signed-Digit multiplier Multiplier based on the CSD representation, as discussed in Section 1.4.1, with an adder cost equal to one less than the number of nonzero digits.

MSD – Minimum Signed-Digit multiplier Similar to the CSD multiplier and requires the same number of adders, but can in some cases decrease the flip-flop cost by using other MSD representations, which were discussed in Section 1.2.2.

• MAG – Minimum Adder Graph multiplier Graph multiplier that is based on any of the topologies in Fig. 2.1 and, for any given coefficient, has the lowest possible adder cost.

### • CSDAG – CSD Adder Graph multiplier Similar to the MAG multiplier, but may use the same number of

Figure 2.1 Possible graph topologies for an adder cost up to four.

adders as the corresponding CSD/MSD multiplier, and can by that reduce the flip-flop cost.

# • PL MAG/PL CSDAG – Pipelined graph multiplier

In a pipelined bit-serial graph multiplier, there is at least one intermediate flip-flop between the full adders. This property, which is always obtained for the CSD/MSD multipliers, result in higher throughput.

# Example

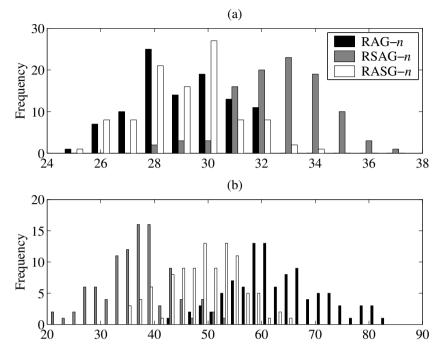

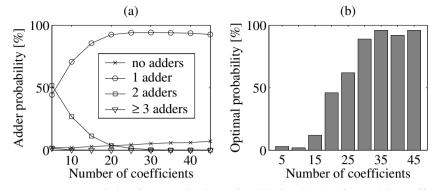

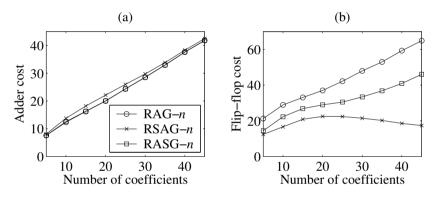

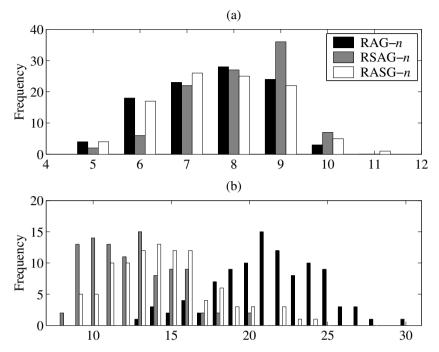

To describe the difference between the defined multiplier types, corresponding realizations of the coefficient 2813, which has the CSD representation  $10\overline{1}0\overline{1}00000\overline{1}01$ , are shown in Fig. 2.2. There are other possible solutions for all types except the CSD multiplier. However, note that the values corresponding to the nonzero digits in the CSD representation can