# Low power architectures for streaming applications

*Citation for published version (APA):* He, Y. (2013). *Low power architectures for streaming applications*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR759534

DOI: 10.6100/IR759534

#### Document status and date:

Published: 01/01/2013

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Low Power Architectures For Streaming Applications

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 14 oktober 2013 om 16.00 uur

door

Yifan He

geboren te Hangzhou, China

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. H. Corporaal en prof.dr.ir. P.P. Jonker

Copromotor: dr.ir. B. Mesman

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

He, Yifan

Low Power Architectures for Streaming Applications

/ by Yifan He. – Eindhoven : Technische Universiteit Eindhoven, 2013.

A catalogue record is available from the Eindhoven University of Technology Library ISBN 978-90-386-3461-6

NUR 959

Subject headings: low power / processor architecture / streaming applications / embedded systems

# Low Power Architectures For Streaming Applications

Committee:

prof.dr. H. Corporaal (promotor, TU Eindhoven) prof.dr.ir. P.P. Jonker (promotor, TU Eindhoven, TU Delft) dr.ir. B. Mesman (copromotor, TU Eindhoven) prof.dr. K. Bertels (TU Delft) prof.dr. B.H.H. Juurlink (TU Berlin) prof.dr. J. Pineda de Gyvez (TU Eindhoven, NXP Semiconductors) prof.dr.ir. A.C.P.M. Backx (chairman, TU Eindhoven)

This work has been carried out as part of the EVA project PID-07121. The project is supported by the Ministry of Economic Affairs of the Netherlands.

This work was carried out in the ASCI graduate school. ASCI dissertation series number 290.

© Yifan He, 2013.

All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

Printing: Printservice Technische Universiteit Eindhoven

To my parents, my wife, and my daughter

### ABSTRACT

#### LOW POWER ARCHITECTURES FOR STREAMING APPLICATIONS

Streaming applications are an important class in emerging embedded systems such as smart camera networks, unmanned vehicles, and industrial printing. On the one hand, these applications are usually very computationally intensive and have real-time constraints. On the other hand, embedded systems running these applications often have limited power sources like batteries or solar panels. Therefore, energy-awareness becomes increasingly important in architecture designs for these systems. To achieve high efficiency in such kind of systems, significant efforts at different hardware and software design levels are required. This thesis deals with part of the challenges in the design of energyefficient architectures for streaming applications, and discusses the following four main topics.

In embedded processors, a substantial part of the energy is consumed by the register file (RF). As a first contribution of this thesis, *MOVE-Pro*, a new *transport triggered architecture* (TTA) based processor architecture is proposed to reduce energy consumption of the register file. With fine-grained control over datapath and optimization in different software/hardware levels, we achieve significant RF accesses reduction in MOVE-Pro: on average about 70% of RF accesses are eliminated, resulting in a dramatic reduction of RF energy. More importantly, with the proposed MOVE-Pro architecture, the RF energy saving is fully transferred to the total core energy saving. Compared to its RISC counterpart, a total core energy saving of up to 11.6% is achieved.

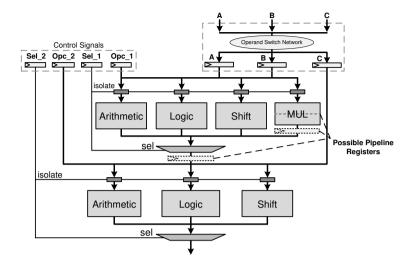

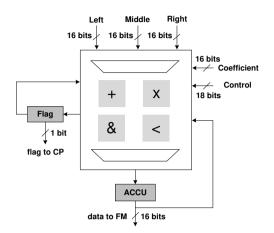

In application specific instruction set processor (ASIP) design, it is common to synthesize instruction sets that support patterns of operations in targeted applications to achieve better performance and energy efficiency. However, in an embedded generic processor with compact ISA, such instructions can lead to large overhead. As a second contribution of this thesis, an architecture that supports flexible operation pairs in processors with compact ISAs is proposed. It introduces a partially reconfigurable decoder and a software-controlled bypass network, allowing the processor to support operation pairs without increasing the instruction width or number of register file ports. Comprehensive and detailed experimental results demonstrate that the proposed architecture achieves an average of 26.0% reduction in dynamic cycle count and an average of 15.8% reduction in energy consumption compared to the reference processors.

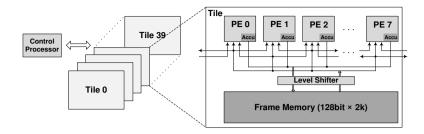

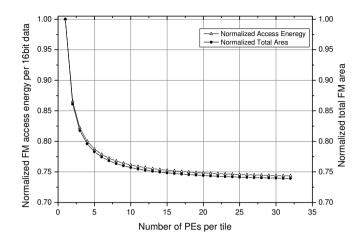

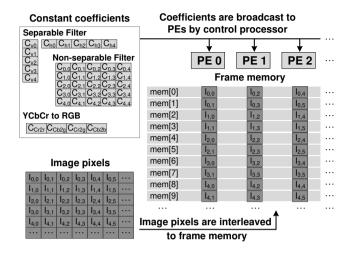

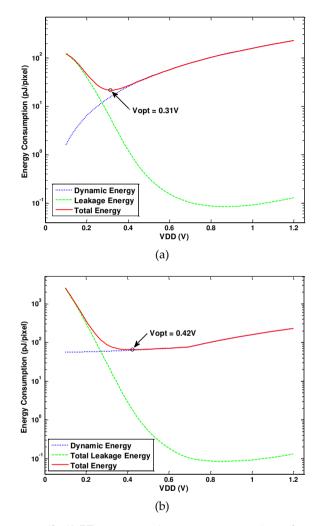

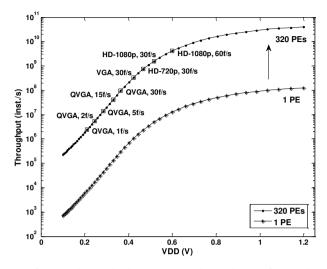

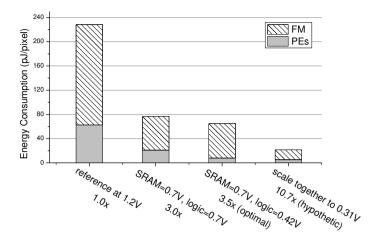

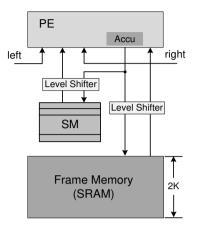

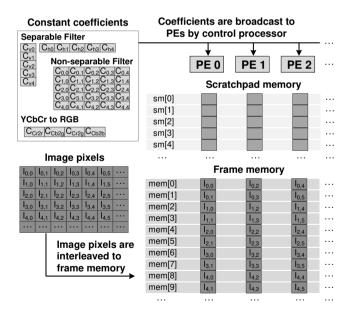

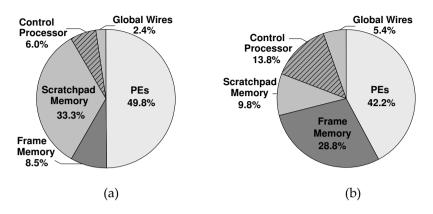

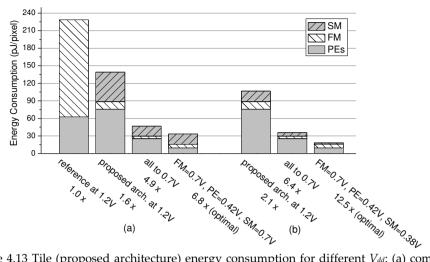

In many embedded streaming applications, substantial amounts of datalevel parallelism can be exploited. To deal with energy-efficiency in combination with high performance requirements, Xetal-Pro, a massively-parallel SIMD architecture, is proposed. The initial idea of combining massive parallelism and aggressive *V*<sub>dd</sub> scaling is presented and discussed in detail. A hybrid memory system, which reduces the non-local memory traffic and enables further *V*<sub>dd</sub> scaling, is also introduced. This work shows that it is possible to achieve 1 pJ/op core energy consumption for typical kernels of embedded streaming applications.

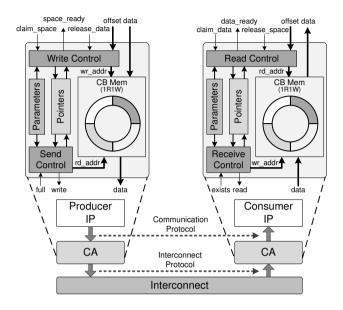

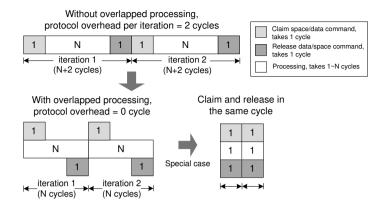

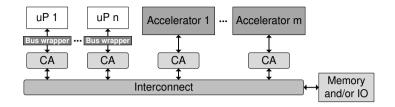

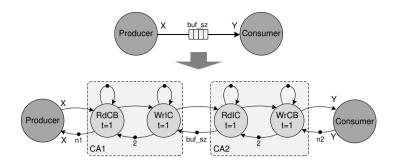

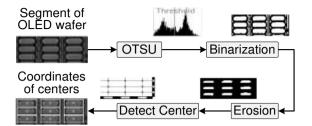

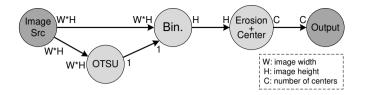

To meet the increasing demand for performance and efficiency in streaming applications, multi-processor system-on-chips (MPSoCs) are becoming a popular solution. As the fourth contribution of this thesis, an efficient and predictable *communication assist* (CA) for integrating generic IP cores into heterogeneous MPSoCs is proposed. The corresponding cycle-accurate *synchronous data flow* (SDF) model for the proposed communication assist is also presented. By integrating this SDF model into SDF analysis tools, worst-case system properties, such as throughput, latency, and buffer sizes can be conservatively analyzed at design time. As a case study, a vision processing pipeline of an industrial application, *Organic Light Emitting Diode* (OLED) screen printing, is mapped onto the proposed platform. This case study also demonstrates that the proposed design flow enables efficient integration of accelerator IPs into a heterogeneous MPSoC which targets streaming applications.

# **CONTENTS**

| 1 | 1 INTRODUCTION                                                                  |                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

|---|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

|   | 1.1                                                                             | Trends in Embedded Streaming Applications                                                                                                                                                                                                                                                                                          | 1                                                        |  |  |

|   | 1.2                                                                             | Challenges in Low-Power Architecture Designs                                                                                                                                                                                                                                                                                       | 3                                                        |  |  |

|   | 1.3                                                                             | Design Flow of Streaming Application Systems                                                                                                                                                                                                                                                                                       | 7                                                        |  |  |

|   | 1.4                                                                             | Problem Statement                                                                                                                                                                                                                                                                                                                  | 11                                                       |  |  |

|   | 1.5                                                                             | Contributions                                                                                                                                                                                                                                                                                                                      | 13                                                       |  |  |

|   | 1.6                                                                             | Thesis Overview                                                                                                                                                                                                                                                                                                                    | 14                                                       |  |  |

| 2 | 2 MOVE-PRO: A TTA-BASED PROCESSOR FRAMEWORK                                     |                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

|   | 2.1                                                                             | Register File Access Reduction                                                                                                                                                                                                                                                                                                     | 16                                                       |  |  |

|   | 2.2                                                                             | Exposed Datapath Architecture                                                                                                                                                                                                                                                                                                      | 18                                                       |  |  |

|   | 2.3                                                                             | Energy-Aware Compilation For MOVE-Pro                                                                                                                                                                                                                                                                                              | 24                                                       |  |  |

|   | 2.4                                                                             | Experimental Results                                                                                                                                                                                                                                                                                                               | 26                                                       |  |  |

|   | 2.5                                                                             | Related Work                                                                                                                                                                                                                                                                                                                       | 34                                                       |  |  |

|   | 2.6                                                                             | Summary                                                                                                                                                                                                                                                                                                                            | 35                                                       |  |  |

|   | 3 AN ENERGY EFFICIENT METHOD OF SUPPORTING FLEXIBLE SPECIAL<br>INSTRUCTIONS     |                                                                                                                                                                                                                                                                                                                                    |                                                          |  |  |

| 3 |                                                                                 |                                                                                                                                                                                                                                                                                                                                    | 37                                                       |  |  |

| 3 |                                                                                 | TRUCTIONS                                                                                                                                                                                                                                                                                                                          |                                                          |  |  |

| 3 | INS                                                                             | TRUCTIONS<br>Operation Patterns and Special Function Unit                                                                                                                                                                                                                                                                          | 39                                                       |  |  |

| 3 | <b>Ins</b><br>3.1                                                               | TRUCTIONS                                                                                                                                                                                                                                                                                                                          | 39<br>43                                                 |  |  |

| 3 | INS <sup>*</sup><br>3.1<br>3.2                                                  | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA                                                                                                                                                                                                                      | 39<br>43<br>50                                           |  |  |

| 3 | INS <sup>7</sup><br>3.1<br>3.2<br>3.3                                           | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions                                                                                                                                                                          | 39<br>43<br>50<br>52                                     |  |  |

| 3 | INS <sup>7</sup><br>3.1<br>3.2<br>3.3<br>3.4                                    | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis                                                                                                                                               | 39<br>43<br>50<br>52<br>58                               |  |  |

| 3 | INS <sup>7</sup><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis<br>Related Work                                                                                                                               | 39<br>50<br>52<br>58<br>61                               |  |  |

| _ | INS <sup>7</sup><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                      | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis<br>Related Work<br>Summary                                                                                                                    | 39<br>43<br>50<br>52<br>58<br>61<br>63                   |  |  |

| _ | INS <sup>3</sup><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>TOV               | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis<br>Related Work<br>Summary<br>WARDS AN ULTRA LOW-ENERGY SIMD PROCESSOR                                                                        | 39<br>50<br>52<br>58<br>61<br><b>63</b><br>64            |  |  |

| _ | INS <sup>3</sup><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Tov<br>4.1        | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis<br>Related Work<br>Summary<br>WARDS AN ULTRA LOW-ENERGY SIMD PROCESSOR<br>The Xetal-II Processor                                              | 39<br>50<br>52<br>58<br>61<br><b>63</b><br>64<br>69      |  |  |

| _ | INS <sup>5</sup><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>TOV<br>4.1<br>4.2 | TRUCTIONS<br>Operation Patterns and Special Function Unit<br>Integrating SFU into Processors with Compact ISA<br>Code Generation for Special Instructions<br>Evaluation and Analysis<br>Related Work<br>Summary<br>WARDS AN ULTRA LOW-ENERGY SIMD PROCESSOR<br>The Xetal-II Processor<br>Challenge of Ultra-Wide-Range Vdd Scaling | 39<br>50<br>52<br>58<br>61<br>63<br>64<br>64<br>69<br>74 |  |  |

|                                                               | 4.6                      | Summary                                        | .86 |  |

|---------------------------------------------------------------|--------------------------|------------------------------------------------|-----|--|

| 5 EFFICIENT COMMUNICATION SUPPORT FOR STREAMING APPLICATIONS. |                          |                                                |     |  |

|                                                               | 5.1                      | Inter-Core Communication Modeled with SDF      | .88 |  |

|                                                               | 5.2                      | Communication Assist                           | .90 |  |

|                                                               | 5.3                      | Proposed Architecture Template & Tool Flow     | .98 |  |

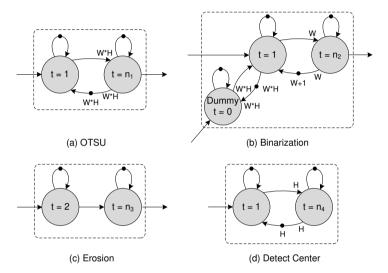

|                                                               | 5.4                      | Case Study: Vision Processing in OLED Printing | 101 |  |

|                                                               | 5.5                      | Related Work                                   | 105 |  |

|                                                               | 5.6                      | Summary                                        | 107 |  |

| 6                                                             | CON                      | NCLUSIONS AND FUTURE WORK                      | 109 |  |

|                                                               | 6.1                      | Conclusions                                    | 109 |  |

|                                                               | 6.2                      | Future Work                                    | 111 |  |

| BIBLIOGRAPHY 113                                              |                          |                                                |     |  |

| SAMENVATTING 12                                               |                          |                                                |     |  |

| ACKNOWLEDGEMENTS 127                                          |                          |                                                |     |  |

| C                                                             | CURRICULUM VITAE 12      |                                                |     |  |

| L                                                             | LIST OF PUBLICATIONS 131 |                                                |     |  |

# CHAPTER 1

### INTRODUCTION

There is an increasing demand for running applications with high performance requirements on embedded systems that have relatively limited resources. For example, a smart phone has to run high-definition video codecs, wireless signal processing, and 3D graphics processing. A smart camera may combine high resolution video sensing, low-level to high-level vision processing, and communication within a single embedded device. All these applications require an enormous amount of computation, and yet embedded system designers have to meet these requirements with a very small power budget. *Power efficiency* is thus becoming a dominant determinant in embedded system design, especially for those ones that run on restricted power sources like batteries or solar cells.

To achieve a highly power-efficient embedded system, many challenges at different design levels need to be overcome (Section 1.2). This thesis focuses on dealing with part of these challenges and contributes by providing solutions to the following four aspects, i.e., energy-efficient data movement in datapath (Chapter 2), flexible special instruction support (Chapter 3), ultra low-energy vector processing (Chapter 4), and efficient communication in heterogeneous MPSoCs (Chapter 5).

The remainder of this chapter is organized as follows. In Section 1.1, we take a closer look at the trends in embedded streaming applications. In Section 1.2, we look at the challenges in low-power architecture designs. Section 1.3 introduces design flows of streaming application systems. Section 1.4 clarifies the problems that this thesis mainly focuses on. Section 1.5 states the key contributions of the thesis. Finally, Section 1.6 gives a brief overview of the thesis.

#### 1.1 Trends in Embedded Streaming Applications

An *embedded system* is an information processing system designed to perform one or a few dedicated functions often with real-time constraints. Embedded

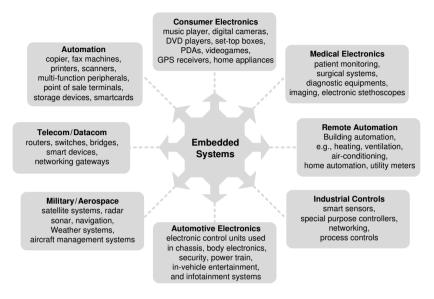

Figure 1.1 Application domains of embedded systems.

systems are widely used in our daily life, e.g., inside portable devices such as digital cameras and smart phones, or systems like televisions, printers, and electronic control unit (ECU) in automobiles. Figure 1.1 depicts the main application domains of embedded systems [5]. Compared to general computing devices, embedded systems perform a *limited* set of pre-defined functions and have *limited* field configuration capability. They are typically enclosed into a very compact packaging with *limited* power sources and cooling facilities. These features/constraints together mode embedded systems into the characteristics of domain specific, real time, low power, low cost, and small area. Among these characteristics, *low power* is usually a distinguishable feature and becoming one of the main challenges [6-8].

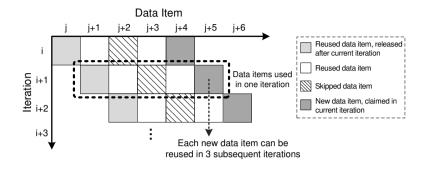

Many applications, such as image processing, computer vision, and multimedia applications, can be categorized as *streaming applications*, which periodically execute similar operations on a stream of data items (often called samples) [9]. Such applications are very common in embedded systems, e.g., 3G/4G [10, 11] wireless communication, H.263/H.264 [12, 13] video coding for mobile domain, MPEG-2/MPEG-4 [14, 15] for high resolution video streams, MP3/AAC [16] for digital audio compression and encoding, DAB/DAB+ [17] for digital radio coding, and various image processing applications such as image enhancement [18, 19], industrial inspection [20, 21], and 3D reconstruction [22, 23]. And their number grows very fast. For example, in the area of portable consumer systems, such as smart cameras and mobile phones, the number of applications doubles roughly every two years [24]. Many of these emerging applications fall into the category of streaming applications. The quick introduction of these new applications becomes an important driven for the development of new technologies [25].

A second trend in embedded streaming applications is the rapidly increasing computation intensity. This is caused by two factors: *i*) an increasing amount of computation must be applied on the data sets due to growing application complexity, e.g., more elaborate and complex coding schemes; *ii*) an increasing amount of data must be processed due to growing data sets, e.g., higher image resolution [26, 27]. As a result, the required processing power is expected to increase by an order of magnitude every five years [6]. Due to technology limitations and power/energy limitations, single processor systems can hardly keep up with the demand of emerging streaming applications [24]. A multi-processor system-on-chip (MPSoC) system seems to be the only solution to fulfill these requirements [6].

In most cases, embedded systems have very limited power sources, such as batteries, the capacity of which grows slowly. For example, in mobile devices, the energy density of Li-ion batteries only increased two to three times during the past fifteen years [28], which can hardly meet the power consumption requirement of modern embedded systems. And this gap is still enlarging. According to the recent research of Samsung's battery development team, the required power for mobile devices is predicted to increase about 20% per year, while the advancement in the energy density of batteries is expected to be only 10% per year [29]. This leads to the third trend: increasing emphasis on *low power*.

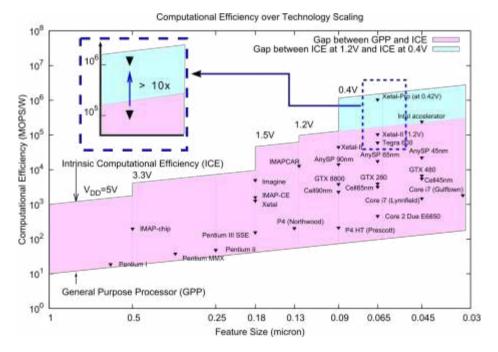

#### 1.2 Challenges in Low-Power Architecture Designs

Modern mobile devices, such as smart phones, perform nearly 100 giga operations per second (GOPS) within a power budget of only 1 W [6]. In other words, no more than 10 pJ can be spent on the execution of one operation, which includes memory accesses, instruction decoding, data movements, and computation. As workload grows at a much faster rate than the improvement of battery capacity, the requirement is becoming even more demanding. We will soon enter into the 1 pJ/op era. Under such a critical constraint, many challenges

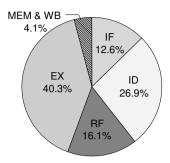

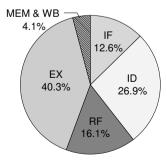

Figure 1.2 Energy breakdown of a classical 5-stage RISC processor (YUV2RGB).

need to be overcome to achieve an energy-efficient architecture for streaming applications.

#### **Computation Overhead**

In a typical reduced instruction set computing (RISC) processor, the energy consumed for executing an *add* instruction is 10× more than the energy spent in a 32-bit adder [30]. This basically means that most of the energy is not consumed by the computation we actually need, but "wasted" by the other overhead required to enable the computation. Among this overhead, the supplying of instructions and data to functional units dominates. This is the main reason why even low-power embedded processors consume significantly more energy than dedicated fixed-function hardware, which allows the communication of data between function units to be aggressively optimized [31]. The commonly used hierarchical memory subsystem can improve energy efficiency by exploiting locality. However, this is still not sufficient. Taking the register file (RF), which is usually at the top of a memory subsystem (i.e., most energy efficient), as an example, it alone can account for 16% of the energy consumed in an embedded processor [32, 33]. Our estimation also shows a similar result. Figure 1.2 presents the energy breakdown of a classical 5-stage RISC processor when executing a YUV to RGB color space conversion kernel<sup>1</sup>. This situation does

<sup>&</sup>lt;sup>1</sup> The energy consumption is calculated as  $P_{avg} \times T_{exe}$ , where  $P_{avg}$  is the average power consumption during kernel execution while  $T_{exe}$  is the kernel execution time. These values are derived by post-synthesis simulation. TSMC 90nm low-power (LP)  $SV_t$  library is used here. The synthesis condition is set to typical case, 1.2V, and 25°C. Clock gating is also enabled. To improve the accuracy of power estimation, physical library (6 metal layers) is included. The interconnect information is estimated based on the physical library.

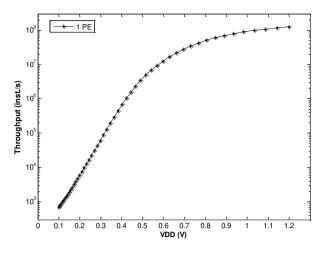

Figure 1.3 Impact of  $V_{dd}$  scaling on throughput of 1 processing element (PE) when executing a 5×5 non-separable filter kernel (refer to Chapter 4 for details).

not improve with advances in technology nodes as communication benefits less than computation from technology scaling. The interconnect-dominated register files and buses that deliver instructions and data to the function units will continuously increase the energy consumption portion [31].

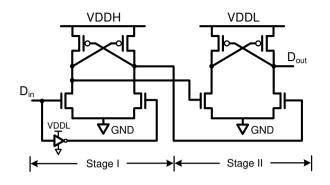

#### Wide-Range Voltage Scaling

Voltage scaling is one of the most effective means to bring quadratic dynamic energy savings to standard-cell based logic, i.e., *Elogic* ~ *Cload Vdd*<sup>2</sup>, where *Cload* is the loading capacitances including both gate and interconnection wire capacitances. However, the V<sub>dd</sub> scaling range of commercial processors is normally limited to about 2/3 of nominal supply due to two fundamental problems at a low Vad: i) severe throughput degradation (Figure 1.3); ii) high yield loss in the presence of process variations [34]. Compared to pure standard-cell based logic, widerange V<sub>dd</sub> scaling is even more difficult when applied to static random-access memories (SRAMs). First, the rapidly deteriorating read/hold static noise margin (SNM) of bit-cells causes severe reliability issues. A very small amount of injected noise can cause the bit-cell's state to flip [35]. Thus, commercial SRAMs with high density (6-T cells) strictly prohibit operating below 0.7~0.8 V. Second, SRAM's energy cannot scale quadratically with Vad. This is because the bit-cells' swing voltage, which must exceed a minimum magnitude required by senseamplifiers to perform correct decoding, cannot scale linearly with  $V_{dd}$ . Third, the speed of SRAMs degrades even faster with  $V_{dd}$  scaling, compared to that of

pure logic [36, 37]. This implies that SRAMs are more prone to be the system performance bottleneck when both SRAM and logic scale to the same low  $V_{dd}$ .

#### Variation

VLSI performance has increased by five orders of magnitude in the last three decades, made possibly by continued technology scaling [38]. This trend will continue, providing an integration capacity of billions of transistors. Advanced process technologies also lead to significant power reduction [24, 39]. However, a parallel trend is that process variation increases with each technology node, which becomes one of the main barriers to future scaling [40, 41]. Variation has many different causes, e.g., random dopant fluctuations [42], line-edge roughness [43], oxide thickness variations [44]. Transistor threshold voltage ( $V_{th}$ ) is one of the parameters that are severely affected by variation, which causes both inter- and intra-die heterogeneity in transistor delay and power consumption [39]. A 30% variation in operating frequency and a five to ten times variation in leakage power can be seen in current technology nodes. And the variation in total power could be as much as 50% [38]. To compensate the impact of variation and to guarantee certain yield, more margins need to be reserved in circuit designs. As a consequence, both design cost and energy consumption are raised.

#### "Energy-Aware" Compiler

Improving energy efficiency is a joint effort of hardware and software. However, while hardware optimization has been the focus of low power design for many years, software approaches to optimize power are still relatively new. Most of the compiler techniques consider only delay and code size as their main performance metrics. With the growing demand for energy-aware software, there is an acute need for investigating low-power compilation techniques and their interaction and integration with performance-oriented compiler optimizations [45]. There are already some useful compilation techniques used in low-power embedded systems, such as giving priority to the lowestenergy-consuming (instead of the fastest) instruction sequences [46], or moving frequently used program codes or data blocks into more energy-efficient levels of the memory hierarchy [47]. However, to meet the rigorous requirement for low energy, a more "energy-aware" compiler, i.e., a compiler armed with more advanced energy-oriented optimization techniques and a more accurate energy model of the target machine, is needed for overall system energy optimization.

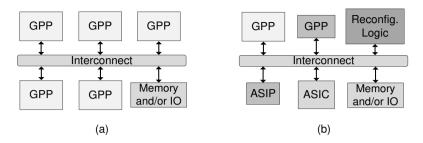

Figure 1.4 (a) a homogeneous MPSoC example; (b) a heterogeneous MPSoC example.

#### Heterogeneity

Since single core based systems alone can no longer keep up with the demand of emerging streaming applications, multi-processor system-on-chips (MPSoCs) are becoming a popular solution to fulfill the requirements. In general, an MPSoC can be categorized as one of the following two types. A homogeneous *MPSoC*, whose processing components are of the same type of programmable processor, can usually support a wide range of applications. Such a system provides high flexibility and is relatively easy to use. However, the overhead of supporting a wide range of applications in all cores may cause severe inefficiencies. Compared to a homogeneous MPSoC, a heterogeneous MPSoC, whose processing components can be general purpose processors (GPPs), applicationspecific instruction-set processors (ASIPs), dedicated application-specific integrated circuits (ASICs), or reconfigurable logic, can achieve much higher efficiency in both performance and power consumption by properly designing and configuring the system for the applications mapped onto it [48, 49]. Figure 1.4 shows examples of homogeneous and heterogeneous MPSoCs. Streaming applications are usually of high complexity and high diversity, so heterogeneous MPSoCs are commonly used when designing efficient systems for these applications [6]. However, heterogeneity also introduces extra complexity. Processing components of various types need to be designed and integrated. Modeling, mapping, scheduling, and debugging applications on a heterogeneous platform are also challenging tasks.

#### 1.3 Design Flow of Streaming Application Systems

With the increasing complexity of embedded systems for streaming applications, it is hardly possible to evaluate system level trade-offs using back-of-the envelope calculations. Designers can neither handle all design aspects at the same time nor handle them by the same person. Therefore, design flows, which

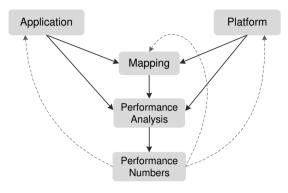

Figure 1.5 The Y-Chart.

can separate different design concerns, solve them efficiently with domainspecific knowledge, and then systematically integrate each component together with performance/cost evaluation, are required.

In this subsection, we first introduce the basic concepts of Y-chart and synchronous data-flow graph. Then we introduce MAMPS, an in-house design flow for mapping throughput constrained applications on an MPSoC.

#### Y-Chart

The Y-chart approach [50, 51] is a general paradigm used for designing embedded systems. Figure 1.5 illustrates the concept of the Y-chart, which involves the co-development of application(s), a platform, and the mapping of the application(s) onto the platform. To implement a system using this methodology, typically the designer studies the target applications with some initial calculations, and proposes an architecture. The performance of this architecture is then quantitatively evaluated and compared against alternative architectures. For such performance analysis, each application is mapped onto the architecture under investigation and the performance of each application-architecture combination is evaluated [52]. Subsequently, the resulting performance numbers may inspire the designer to improve the architecture, restructure the application(s) or modify the mapping of the application(s), which are shown as dotted lines in Figure 1.5. These feedback paths make the Y-chart an iterative design methodology that enables the co-evolution of hardware and software [53].

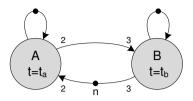

Figure 1.6 An SDF graph with two actors. Unmarked rates and buffer sizes are 1.

#### Synchronous Data-flow Graphs

In order to ensure that high performance or real-time requirement of an application can be met by the target platform, designers have to be able to model the application. In the absence of a good model, it is very difficult to know in advance whether the requirements can be met or not at all times, and extensive simulation and testing are needed [54].

The *Synchronous Data Flow* (SDF) graph is a very powerful model of computation (MoC) for analyzing streaming applications [55]. Both pipelined streaming and cyclic dependencies between tasks can be easily modeled with SDF graphs. There are many analysis algorithms for SDF that can be used to analyze at design time the throughput, latency, and buffer size requirements of applications modeled with an SDF graph [56-58].

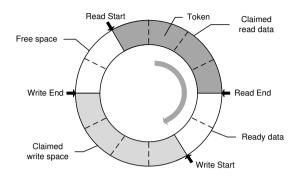

An application modeled with an SDF graph consists of nodes called actors and edges, called *channels*, between these actors. Actors transfer data items called tokens to each other via channels. An example SDF graph containing a producer actor A and a consumer actor B is depicted in Figure 1.6. Actor Atakes t<sub>a</sub> time units to finish one firing (i.e., perform a computation) and it produces 2 tokens at the end of this firing. Actor *B* consumes 3 tokens in each firing and its execution time is equal to  $t_b$  time units. The channel from actor A to actor B models the communication channel. The channel from *B* to *A* is used to model the buffer between these actors. The amount of initial tokens *n* on this channel represents the buffer size of the channel from actor A to actor B. The number of concurrent firings of an actor, defined as its *auto-concurrency*, is constrained by the number of initial tokens on the actor's *self-edge*. In Figure 1.6, both actors have an auto-concurrency of 1. Hence, subsequent firings of actor A (or B) need to be serialized. This could for example be necessary when an actor firing produces state that is needed for a subsequent firing. Note that when an actor has no self-edge, it is possible to have multiple firings of an actor running in paral-

Figure 1.7 MAMPS design flow overview [1].

lel. This makes it possible to model data-parallel executions in the SDF graph. We use SDF graphs to model and map applications to MPSoCs in Chapter 5.

#### MAMPS Design Flow

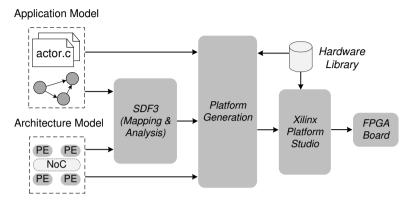

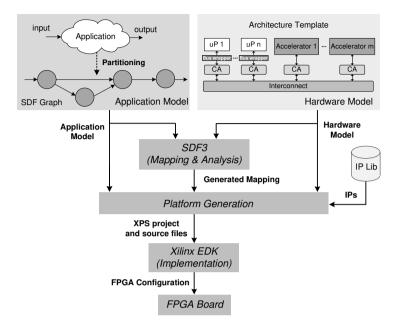

*MAMPS* (Multi-Application and Multi-Processor Synthesis) [59] is an in-house design flow for mapping throughput constrained applications on an MPSoC, which is based on the Y-chart. It integrates several state-of-the-art analysis, mapping, and synthesis tools into an automated tool flow. Figure 1.7 shows an overview of this design flow.

The inputs of this tool flow are an application modeled as an SDF graph, a C-based implementation for each actor in the graph, and a template based architecture description. The application SDF graph and its corresponding implementation of each actor are joined into the *application model*. The application model specifies a set of metrics of the actor implementations. These metrics include the worst-case execution time (WCET), required memory sizes, and the size of communicated tokens. The template based architecture description, i.e., *architecture model*, describes the various components available in the hardware platform and how these components are connected [60].

The output of the design flow is an MPSoC platform tailored for the target applications, with C implementation of each actor mapped to general purpose processors (e.g., MicroBlaze) [1]. The analysis framework that MAMPS uses is called *SDF3* [61]. It consists of several tools that allow automatic mapping of an application described as a SDF graph to a given platform. SDF3 also verifies if

such a mapping is deadlock free and analyzes worst-case system properties, such as throughput, latency, and buffer sizes conservatively at design time. Besides these SDF facilities, MAMPS also provides platform generation tools and tightly integrated Xilinx EDA tools, which automate the processes of system instantiation, synthesis, and download.

#### 1.4 Problem Statement

As discussed in the first section of this chapter, streaming applications are an important class in emerging embedded systems. On the one hand, these applications are usually computationally intensive and have real-time constraints. On the other hand, embedded systems running these applications often have limited power sources like batteries or solar panels. Therefore, energy-awareness becomes extremely important in architecture designs for these systems. Achieving such kind of highly energy-efficient systems is not an easy task. This thesis will deal with part of the challenges discussed in Section 1.2.

#### Energy-Efficient Data Movement

As a lot of energy is "wasted" in the supplying of data to functional units, the first problem handled in this thesis is to improve the energy-efficiency of data movement in embedded processors. Observing that a substantial part of the energy is consumed by the register file (RF) [33, 62], we particularly focus on reducing energy consumption of the RF, and converting this energy saving into the total core energy saving. In typical embedded streaming application kernels, most of the variables have very low use count (<3), i.e., the value of a variable is only used a very small number of times by the following instructions [63], which can be interpreted as a huge potential to eliminate RF accesses. In a pipelined processor, a lot of such variables can be accessed via the bypassing network instead of the RF. However, in conventional processor architectures, these RF accesses are usually performed regardless of the necessity, which result in a power hungry RF and a hotspot on the chip. A transport triggered architecture (TTA) can effectively reduce the RF pressure in both the number of accesses and the number of RF ports [64, 65]. However, conventional TTAs also have some disadvantages, such as relatively low code density and dynamicpower wasting. These disadvantages inhibit it being an energy-efficient architecture. In order to preserve the merit of conventional TTAs while solving these issues, new improvements in both architecture and compiler are required.

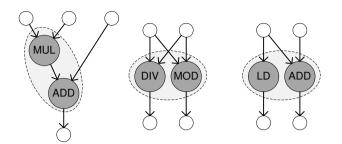

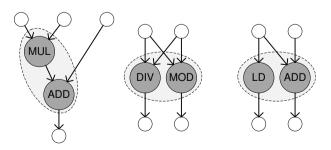

Figure 1.8 Operation patterns.

#### Flexible Special Instruction Support

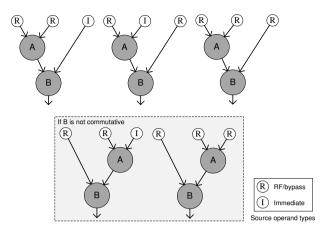

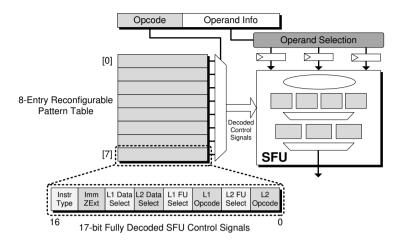

Many streaming applications contain frequently executed operation patterns in the data-flow graphs (DFGs), like the ones shown in Figure 1.8. In application specific instruction set processor (ASIP) design, it is common to synthesize instruction sets that support such patterns in targeted applications to achieve better performance and energy efficiency [66-68]. However, extending this idea to a generic embedded processor and efficiently supporting flexible special instructions is challenging. In most mainstream processor architectures, only a few of such patterns are supported, as supporting arbitrary operation patterns in a generic processor incurs large overhead. From energy efficiency perspective, the overhead includes extra opcode space, extra RF ports and RF index space, as well as increased complexity in both control path and datapath. Therefore, efficient software and hardware solutions are in demand if we want to use flexible special instructions to improve the energy efficiency of a generic embedded processor.

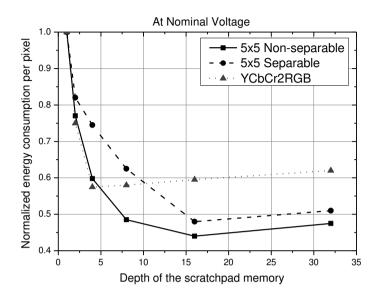

#### Ultra Low-Energy Vector Processing

Massive parallelism in streaming applications typically shows up as data-level parallelism (DLP). Therefore, achieving low-energy vector processing is of great importance when designing an energy-efficient system for streaming applications. DLPs can be inherently exploited by a *single instruction multiple data* (SIMD) processor, which is a low power architecture as it applies the same instructions to all *processing elements* (PEs) [69]. To further reduce energy consumption, *V*<sub>dd</sub> scaling can be applied to SIMDs. However, issues such as severe throughput degradation, high yield loss in the presence of process variations, and scaling-unfriendly SRAM limit the *V*<sub>dd</sub> scaling range, create a big obstacle to the energy efficiency improvement. So the third problem is how to mitigate these issues and achieve an ultra low-energy SIMD processor.

#### Efficient Communication Support

To meet the increasing demand for performance and efficiency in streaming applications, the use of energy-efficient programmable cores and accelerator cores in heterogeneous MPSoCs becomes inevitable [6, 48]. The problems discussed above aim at providing energy-efficient cores. These cores can be used as efficient computation components in a heterogeneous MPSoC. However, heterogeneity requires more than this. When mapping a streaming application onto a heterogeneous MPSoC that contains accelerators, several issues need to be solved: *i*) how to generate accelerator IPs for the application; *ii*) how to integrate these IPs into an MPSoC; and *iii*) how to predict performance/resource usage at design time. The first issue can be handled through the use of IP libraries or high level synthesis tools [70, 71]. Solving the other two issues requires an efficient and analyzable communication support.

#### 1.5 Contributions

The main contributions of this work include:

- MOVE-Pro, a new TTA based processor architecture is proposed to reduce energy consumption of the register file, and convert this energy saving into the total core energy saving. With fine-grained control over datapath and optimization in different software/hardware levels, about 70% of RF accesses are eliminated on average, resulting in a dramatic reduction of RF energy. More importantly, with the proposed MOVE-Pro architecture, the RF energy saving is fully transferred to the total core energy saving. Compared to its RISC counterpart, an energy saving of up to 11.6% is achieved (Chapter 2).

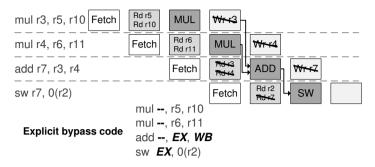

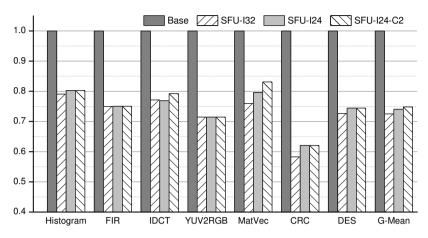

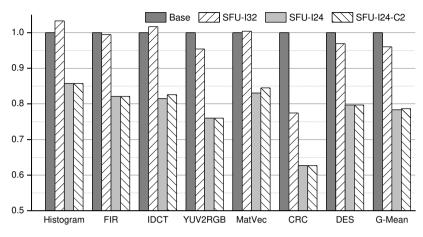

- An architecture that supports flexible operation pairs in a processor with a compact 24-bit RISC-like ISA is proposed. It introduces a partially reconfigurable decoder and a software-controlled bypass network, allowing the processor to support operation pairs without increasing the instruction width or number of register file ports. Comprehensive and detailed experimental results demonstrate that the proposed architecture achieves an average of 26.0% reduction in dynamic cycle count and an average of 15.8% reduction in energy consumption compared to the reference processors (Chapter 3).

- Xetal-Pro, a massively-parallel SIMD architecture is proposed in this work. The idea of combining massive parallelism and aggressive *V*<sub>dd</sub> scaling is presented and discussed in detail. A hybrid memory system, which reduces the non-local memory traffic and enables further *V*<sub>dd</sub> scaling, is also introduced. This work shows that it is possible to achieve less than 1 pJ/op core energy consumption for typical kernels of embedded streaming applications (Chapter 4).

- An efficient and predictable *communication assist* (CA) for integrating generic IP cores into heterogeneous MPSoCs is proposed. The corresponding cycle-accurate *synchronous data flow* (SDF) model for the proposed communication assist is also presented. By integrating this SDF model onto SDF analysis tools, worst-case system properties, such as throughput, latency, and buffer sizes can be conservatively analyzed at design time. The existing design flow, MAMPS, is updated with the proposed CA-based hardware template. As a case study, a vision processing pipeline of an industrial application, *Organic Light Emitting Diode* (OLED) screen printing, is mapped onto the proposed platform. This case study demonstrates that the proposed design flow enables efficient integration of accelerator IPs into a heterogeneous MPSoC which targets streaming applications (Chapter 5).

### 1.6 Thesis Overview

The thesis is organized as follows. Chapter 2 presents the first design proposal, MOVE-Pro, which is a low-power and high code density processor framework based on *transport triggered architecture* (TTA). In Chapter 3, a novel approach for supporting flexible operation pair patterns in a generic processor with a compact ISA is proposed. This work improves energy efficiency by reducing the computation overhead in generic processors. Chapter 4 discusses the progress in developing Xetal-Pro, an ultra low-energy vector processor. The results show that with massively-parallel SIMD and aggressive *V*<sub>dd</sub> scaling, it is possible to achieve computation efficiency of less than 1 pJ/op. Chapter 5 presents a *communication assist* (CA) to efficiently integrate generic IPs into an MPSoC with a predictable design flow. A case study is performed using an updated design flow called MAMPS+. Finally, Chapter 6 concludes this thesis and gives directions for future work.

# CHAPTER 2

## MOVE-PRO: A TTA-BASED PROCESSOR FRAMEWORK

Energy efficiency is becoming the dominant determinant of embedded system design: in most cases, embedded systems have limited power sources like batteries, which largely constrain the use of high performance processors. Moreover, high power dissipation also makes the chip's thermal design more difficult. A lot of work has been done to reduce the processor energy consumption in different ways [72-77]. We observed that a substantial part of the energy is consumed by the register file (RF), which mainly consists of data storage elements and (de)mux logic [62, 78]. Therefore in this chapter, we particularly focus on reducing energy consumption of the RF, and converting this energy saving into the total core energy saving.

In typical embedded application kernels, most of the variables have very low use count. Table 2.1 shows the local variable statistics of four representative kernels. In a pipelined processor, many of these variables can be accessed via the bypassing network instead of the RF. However, in conventional processor architectures, these RF accesses are usually performed regardless of the necessity, which results in a power hungry RF and a hotspot on the chip.

In this work, we propose MOVE-Pro, a new *transport triggered architecture* (TTA) based processor architecture, to solve this issue. With fine-grained control over datapath and optimization in different software/hardware levels, we achieve significant RF accesses reduction in MOVE-Pro: on average about 70% of RF accesses are eliminated, resulting in a dramatic reduction of RF energy. More importantly, with the proposed MOVE-Pro architecture, the RF energy saving is fully transferred to the total core energy saving. Compared to its RISC counterpart, a total core energy saving of up to 11.6% is achieved with no performance penalty. The experiment is carried out at 1.2V, 25°C, typical case, with TSMC 90nm low-power CMOS digital standard cell library.

|                                 | FIR    | Histogram | YUV2RGB | IDCT   |

|---------------------------------|--------|-----------|---------|--------|

| Average reads<br>per variable   | 1.71   | 1.59      | 1.77    | 1.55   |

| Local variable<br>with < 3 uses | 94.10% | 98.25%    | 90.31%  | 98.72% |

Table 2.1 Kernel local variable statistics.

The remainder of this chapter proceeds as follows: Section 2.1 introduces the basic idea behind register file access reduction. MOVE-Pro, the proposed TTA-based architecture is presented in Section 2.2. The energy-aware compilation flow for MOVE-Pro is briefly depicted in Section 2.3. In Section 2.4, the proposed design is verified with a detailed comparison between MOVE-Pro and its RISC/VLIW counterparts. Section 2.5 discusses the related work. Finally, Section 2.6 concludes our findings and discusses future work.

#### 2.1 Register File Access Reduction

In processors designed for multi-media and/or high performance signal processing, the RF is one of the most power hungry components in the datapath, which could account for over 40% of the datapath power consumption [33]. For multi-issue architecture, the demand for RF with many ports is especially costly [32].

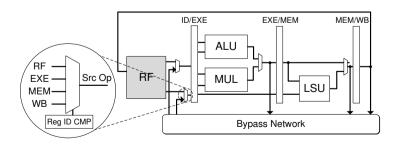

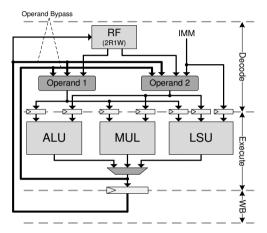

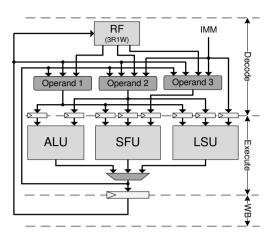

Figure 2.1 shows the datapath of a typical RISC processor with a 5-stage pipeline. To reduce pipeline stalls caused by data hazard, a bypass network (i.e., data wires which forward results to the previous pipeline stages) is usually employed to allow an instruction to use the results which are available in the pipeline but haven't yet been written back to the RF. With the bypass network, there are three situations where RF accesses are not necessary:

Figure 2.1 Operand bypassing in a typical processor datapath.

Figure 2.2 RF access elimination example.

- *Bypassing*: the result of an operation can be read from the pipeline register before it is written back to RF.

- *Dead result elimination*: if all uses of a variable are bypassed, writing it back to RF is not necessary.

- *Operand sharing*: when an operand is used successively on the same port of a function unit (FU), it only needs to be read from RF once.

Figure 2.2 shows an example in which all three types of RF access eliminations are possible:

- Register r3 in the second addition (*add*) and r12 in the store instruction (*sw*) can be bypassed, i.e., we can directly get the required data values from the bypass network instead of reading them from RF.

- After bypassing, write-back of r3 and r12 in the first two instructions can be discarded.

- Register r7 is shared by the two additions, therefore only the first addition needs to actually read r7 from RF.

In Table 2.2, four representative streaming kernels are depicted, which are studied in this work. Table 2.1 shows the percentage of local variables with 3 uses in these kernels. Clearly, most variables have very small use counts, which can be interpreted as a huge potential to eliminate RF accesses.

| Kernels   | Description                                        |

|-----------|----------------------------------------------------|

| FIR       | 5-tap 32-bit finite impulse response filter        |

| Histogram | 256-bin histogram for 8-bit gray-scale image       |

| YUV2RGB   | YUV to RGB color space conversion for 24-bit image |

| IDCT      | Inverse cosine transformation in the JPEG decoder  |

Table 2.2 Kernel description.

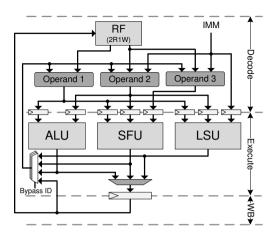

Figure 2.3 TTA architecture, with exposed inter FU and RF datapath.

#### 2.2 Exposed Datapath Architecture

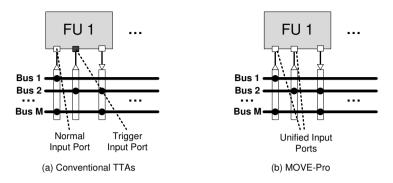

Architectures, such as RISC, Superscalar, and Very Long Instruction Word (VLIW), can be categorized as *operation-triggered architectures* (OTA). In such architectures, an instruction typically specifies what the operation is and what the source operands are. Usually, they cannot eliminate unnecessary RF accesses identified in Section 2.1. In a *transport triggered architecture* (TTA), however, an instruction directly controls the datapath by specifying the data transportation between different units, and operations are merely side-effect of the transportation [64]. As shown in Figure 2.3, by programming the communication network, data are explicitly transported from one unit to another.

In this work, we would like to explore TTA's low-power potential inherited from its *explicit datapath* nature, i.e., the capability of directly transferring an operand from the output of one unit to the input of another. With proper scheduling of the data transport, RF accesses can be dramatically reduced compared to its RISC/VLIW counterparts. As a result, the total processor energy consumption is expected to be reduced accordingly. However, it is challenging to achieve this goal due to some disadvantages of conventional TTAs.

#### 2.2.1 Disadvantageous of Conventional TTAs

A TTA is well-known for its cost-effective trade-off between performance and flexibility. It is able to generate optimized cores for various domains, e.g., multimedia, telecommunication [64, 79, 80]. However, the conventional TTAs also have some evident disadvantages:

• Code density is lower than RISC/VLIW. This is because to perform a 3address operation on a TTA in principle three *moves* are required. For

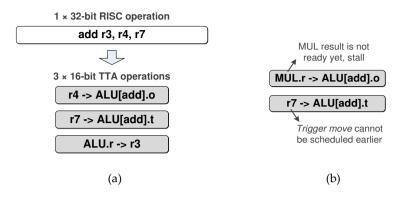

Figure 2.4 (a) Translation of a RISC operation onto TTA operations, where *o* is operand input port, *t* is trigger input port, and *r* is result output port. *r*4 -> *ALU[add].o*, for example, means that the value of register *r*4 is *moved* to the operand input port of the function unit *ALU* for addition; (b) Extra scheduling constraint introduced by trigger port.

example, a direct translation of one 32-bit RISC *add* operation onto TTA results in three 16-bit TTA *move* operations (Figure 2.4 (a)).

- The separate scheduling of source operands increases circuit switching activity, causing more energy consumption. This will be explained in more detail in Section 2.2.3.

- Operations can only be triggered by moving data to the trigger port (shaded ports in Figure 2.3), so a trigger move has to be scheduled no earlier than the operand moves of the same operation, which introduces extra scheduling constraint. For example, in Figure 2.4 (b), if the operand move (the first one) is pending due to the dependency on result of MUL, the trigger move (the second one) cannot be scheduled earlier even though it has no unresolved dependency.<sup>2</sup>

<sup>2</sup> In [64], a special latching discipline for the pipeline stages of function units, called *true virtual-time latching* (TVTL), is discussed. With TVTL, both operand moves and trigger moves can "trigger" operations. Since operand moves do not have opcodes, the opcode of the previous trigger move is used if an operand move triggers an operation. This latching discipline is not a very good choice in terms of power consumption, as many unnecessary operations may be triggered if an operand move is scheduled first. The TVTL also greatly reduces the scheduling freedom of result moves as the available time of useful results in FUs is reduced. Thus performance may also be degraded.

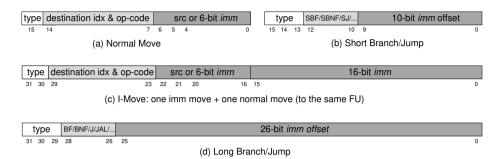

Figure 2.5 The MOVE-Pro instruction formats.

• Inefficient support for large immediates, which deteriorates code density and energy consumption. This is due to small immediate field in the conventional TTA instruction format and limited support for large immediate [64, 81].

Previous research on MOVE framework<sup>3</sup> [82] shows that comparing to a single-issue RISC processor (instr. width = 32 bit), the code density of a corresponding two-issue MOVE processor (instr. width = 32 bit) is 20% worse [83]. When using the TCE framework<sup>4</sup> [84], the overhead is about 30% based on our measurements. Poor code density becomes an obstacle for TTAs from being an energy efficient architecture.

In this work, in order to fully utilize TTA's low-power potential, more specifically, to successfully convert the potential energy saving in RF to energy saving of the complete processor core, we propose MOVE-Pro, a low-power and high code density TTA framework. In Section 2.2.2, we will introduce the instruction set architecture of the proposed MOVE-Pro processor. In Section 2.2.3, we will describe the details of the MOVE-Pro architecture.

#### 2.2.2 Proposed MOVE-Pro Instruction Set Architecture

Code density not only affects processing performance, but also has a strong influence on the total energy consumption. Fewer dynamic instructions counts mean that fewer instructions need to be fetched from instruction memory and fewer instructions need to be executed, resulting less energy consumption. In order to improve the code density of conventional TTAs and to provide flexible

<sup>3</sup> TTA implementation from Delft University of Technology

<sup>&</sup>lt;sup>4</sup> TTA implementation from Tampere University of Technology

Figure 2.6 Binding between trigger move and a specific destination port is removed in MOVE-Pro, resulting in more scheduling flexibility for the compiler.

immediate support, we combine some helpful features of RISC *instruction set architecture* (ISA) with conventional TTA ISA, and propose a new one for our MOVE-Pro architecture.

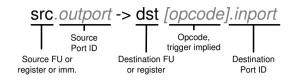

The MOVE-Pro instruction formats are shown in Figure 2.5. The 16-bit *Normal Move* (Figure 2.5 (a)) is similar to the conventional TTA instruction format. The main difference is that in MOVE-Pro we removed the constraint that operations can only be triggered by moving data to a specific destination register/buffer, i.e., the trigger port [64, 79]. Thus, the binding between trigger move and a specific destination port is removed, resulting in unified function unit (FU) input ports (Figure 2.6). This provides more scheduling flexibility for the compiler. To implement this idea with minimum overhead, we did not introduce an extra instruction bit to distinguish a trigger move operation and a non-trigger move operation. Instead, all non-trigger moves are considered as a same class of operation, i.e., *Not-a-Trigger-Operation*, which is encoded into the *op-code* field of the instruction similar as other normal operations like *add, mul*.

A 32-bit *I-Move* (Figure 2.5 (c)) is added to support 16-bit immediate, which is similar as the *I-Type* of RISC instructions. Two moves are encoded in this format: one is a normal move and the other is a 16-bit immediate move. Since there is no extra space to encode the destination address for the 16-bit immediate move, these two moves must share a same FU as their destination. This constraint is not an issue as an immediate is always ready for issue (no data dependency). Compiler can directly pack it with a *Normal Move* to the same FU, forming a 32-bit *I-Move* instruction. Compared to the conventional TTA, the introduction of *I-Move* in MOVE-Pro efficiently encodes the 16-bit immediate.

Figure 2.7 MOVE-Pro assembly format.

Two kinds of branch/jump instructions are supported, which differ in the range of branch offset. The purpose of introducing both short and long branch/jump formats is to achieve a better code density as well. A *Normal Move* with 6-bit immediate has an indexing range of only -32~31, which is often in-adequate to handle local branches. However, the 16-bit *Short Branch/Jump* (Figure 2.5 (b)) introduced in the proposed MOVE-Pro ISA has an indexing rang of -512~511, which is usually sufficient to deal with most of branches within a function. Compared to its RISC counterpart, the 16-bit *Short Branch/Jump* is only half of the size. When even larger indexing range is required, the 32-bit *Long Branch/Jump* (Figure 2.5 (d)) can be used, which has a 26-bit indexing range.

Since 32-bit instructions are introduced in the proposed MOVE-Pro ISA, the minimum number of issue slots in our MOVE-Pro processors is two. Figure 2.7 depicts the MOVE-Pro assembly format. Note that, unlike the conventional TTA, which has three types of ports (i.e., operand input port, trigger input port, and result output port), we have only input and output ports in MOVE-Pro.

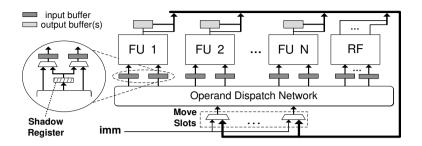

#### 2.2.3 Proposed MOVE-Pro Organization

Section 2.2.2 described the main features of MOVE-Pro ISA. In this section the proposed MOVE-Pro architecture will be presented in detail.

Unlike *operation-triggered architectures* (OTAs), TTAs can schedule the source operands of the same operation in different cycles. On the one hand, it introduces an extra level of scheduling freedom. On the other hand, it causes more energy consumption. Take a multiplication,  $a \times b = c$ , as an example. In OTA, the multiplicand *a* and multiplicator *b* are scheduled together. They are latched into the two input operand registers of a multiplier FU at the same clock cycle. The multiplier circuit only toggles once before producing the product *c*. However, for a TTA-based processor, *a* and *b* can be scheduled separately, e.g., first *a*, then *b*. Thus, before producing the useful product *c*, the multiplier circuit

Figure 2.8 MOVE-Pro architecture.

undergoes extra toggles to produce a useless result,  $a \times b'$ , where b' is the previous value of b. This extra circuit switching causes dynamic power wasting, i.e., two multiplications are executed instead of one.

In the proposed MOVE-Pro architecture, we solve this issue by introducing *shadow register(s)* before the input buffers of FUs with multiple input operands (Figure 2.8). Let's look at the multiplication example above again. Suppose FU<sub>1</sub> in Figure 2.8 is a multiplier, multiplicand *a* is scheduled in *cycle t*, and multiplicator *b* is scheduled in *cycle t+n*. In the proposed MOVE-Pro architecture, *a* will be first buffered in the shadow register for *n* cycles until *b* is also issued. Both of them will then be loaded into the two input operand buffers at the same cycle, triggering the multiplier circuit only once. With this improvement, we avoid the dynamic power wasting in the conventional TTA, while still keeping TTA's flexible scheduling feature. For FUs with only a single input, clearly no such shadow buffer is needed.

Introducing shadow buffer(s) has another important advantage. Let's still use the multiplication as an example. Since the early arrived operand a is first buffered in the shadow register, the input buffers of the multiplier can still latch the valid multiplicand and multiplicator of the previous multiplication. A direct consequence is that the value of the previous multiplication is valid in the output of the multiplier for longer time (i.e., more cycles), which would otherwise have already been flushed by a garbage data. This results in three beneficial outcomes:

• Increased availability of previous results in the bypass network, as they can stay in FU outputs for longer time. This results in reduced RF read accesses.

- Increased possibility for previous results to be dead results as their available time in the bypass network is longer. This results in reduced RF write accesses.

- FUs can more effectively act as virtual output buffers, as useful outputs will not be flushed by garbage data. This results in reduced physical output buffer and/or register file requirement.

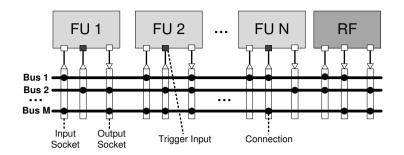

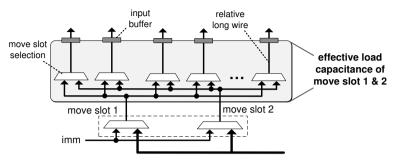

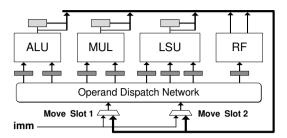

As discussed above, TTAs have finer scheduling granularity than their OTA counterparts. In OTAs such as a classical RISC datapath, the first and second operands usually correspond with FUs' different input buffers. For example, the first operand bus is only connected with the first input buffer of FU<sub>1</sub>~FU<sub>n</sub>, and the second operand bus is only connected with the second input buffer of FU<sub>1</sub>~FU<sub>n</sub>. So each operand bus has relatively limited load capacitance. However, in TTAs, the same operand move can be scheduled to different move slots (also called move buses), resulting in an *operand dispatch network* with higher load capacitance, i.e., higher power penalty to dispatch operand to the input buffers of FUs. In the most flexible case, each move slot can potentially send its operand to each destination location.

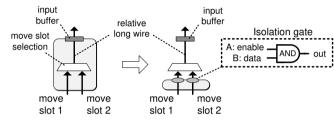

Reducing the *operand dispatch network* connectivity can mitigate this issue but at the cost of reduced scheduling flexibility [64]. So we would like to mitigate this issue from a different perspective. Viewing the fact that only part of the destination registers (input buffers of FUs) are enabled per cycle, we apply a circuit-level optimization to "isolate" the inactive destination registers. Figure 2.9 describes the basic idea. A 2-1 *AND* gate is inserted before the move slot selection *MUX*. Input *A* of the *AND* gate is the destination *write enable* signal, which is decoded in such a way that it arrives always earlier than the other input, *B*, which is the *move data*. When the destination register writing is not enabled, i.e., A = 0, the frequently changed move data, *B*, is isolated from propagating to the output, regardless of its value. With this method, the effective load capacitance of the *operand dispatch network* is reduced, resulting in lower data dispatch cost.

#### 2.3 Energy-Aware Compilation For MOVE-Pro

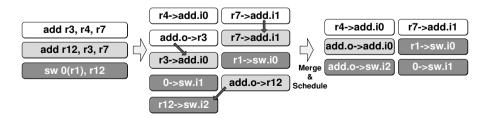

For a TTA, a typical binary operation needs three moves: two for the source operands and one for the result. It typically takes 16 bits to encode a move. Therefore, a direct translation from *operation code* to *move code* would probably result in a very bad code density. Figure 2.10 shows an example where move

(a) without isolation gates, move slots have high effective load capacitance

(b) after introducing isolation gates, the effective load capacitance is reduced when the input buffer is not a destination register.

Figure 2.9 Reduce the effective load capacitance by *AND*-gate isolation. *enable* is the destination write enable signal (early arrival signal) and *data* is the move data.

code is 60% larger in a direct translation. The problem can be solved by the compiler. In the example, after performing software bypassing and instruction scheduling, the final move code has the same size as the operation code, with half of the RF reads and all of the RF writes eliminated. Obviously the compiler plays an important role in a TTA.

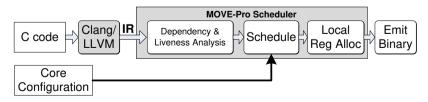

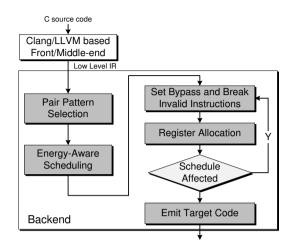

The compiler framework of MOVE-Pro is shown in Figure 2.11. The LLVM compiler framework is used as the front-end, which produces intermediate

Figure 2.10 TTA code scheduling example.

representation (IR) for the backend. The instruction set of the IR is similar to a RISC ISA, with support of extra meta-data. The core of the backend is the instruction scheduler. In this work, the scheduler performs basic block level scheduling. It minimizes the energy consumption by eliminating unnecessary RF accesses. The number of instructions is another optimization target. Otherwise the scheduler may choose to serialize operation execution in order to increase the bypassing opportunity. A post-pass register allocator is used. Due to the nature of TTA, spilling rarely happens in MOVE-Pro. When there is any spill code that fails to fit into the current schedule, the scheduler simply performs a partial reschedule. Since the compiler work is reported in a different thesis and papers, it will not be elaborated in this thesis. For more details, please refer to [63, 78].

# 2.4 Experimental Results

To verify the low-power feature of the proposed MOVE-Pro architecture, two head-to-head comparisons are carried out: *i*) MOVE-Pro vs. RISC; *ii*) MOVE-Pro vs. VLIW.

# 2.4.1 MOVE-Pro vs. RISC

In this experiment, we implemented in RTL both a classical 5-stage RISC processor which is compatible with OpenRISC ISA [85] and its TTA counterpart, a two-issue MOVE-Pro processor (Figure 2.12). The instruction width of both designs is 32 bits. The same FUs are used in these two implementations, as well as the same low-power techniques, e.g., FU clustering and clock gating. To reach a solid conclusion, we further optimized the reference RISC processor for lower power consumption at different implementation levels. For example, to reduce unnecessary switching activity in both RF and pipeline registers, we only propagate write data/index through pipeline stages when the instruction under execution indeed requires updating RF.

Figure 2.11 MOVE-Pro compiler framework.

Figure 2.12 The block diagram of the two-issue MOVE-Pro Processor.

TSMC 90nm low-power library is used in the experiment. The synthesis condition is set to typical case, 1.2V, and 25°C. To improve the accuracy of power estimation, physical library (6 metal layers) is included. The interconnect information is estimated based on the physical library. The maximum clock frequency is 200 MHz with the critical path inside the multiplier. All four kernels listed in Table 2.1 are tested. Power consumptions are estimated with the post-synthesis simulation and toggle rate generated by running each kernel with test data of 2000 samples.

Figure 2.13 shows the energy breakdown of the reference RISC processor when executing a YUV to RGB color space conversion kernel. The energy consumption is calculated as  $P_{avg} \times T_{exe}$ , where  $P_{avg}$  is the average power consumption during kernel execution while  $T_{exe}$  is the kernel execution time. Energy consumption of the memory part is not shown in this graph as it highly depends on the memory size. The register file consumes about 16% of the total core energy in this application.

Figure 2.13 Energy breakdown of the reference RISC processor (YUV2RGB).

|                 | FIR   | Histogram | YUV2RGB | IDCT  |

|-----------------|-------|-----------|---------|-------|

| Read reduction  | 65.5% | 63.6%     | 63.6%   | 68.6% |

| Write reduction | 82.3% | 71.4%     | 67.7%   | 66.7% |

Table 2.3 RF access reduction in MOVE-Pro.

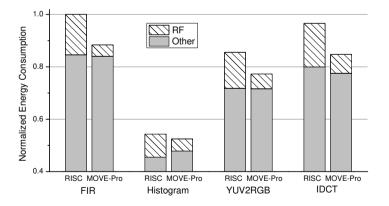

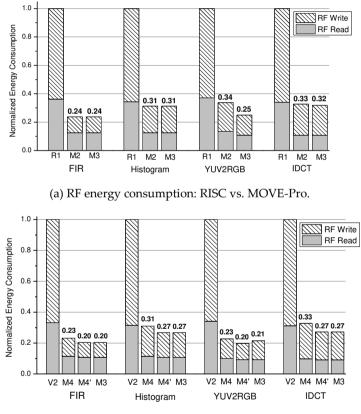

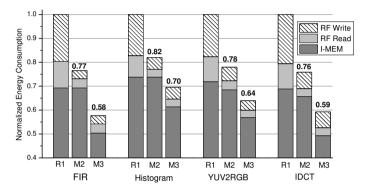

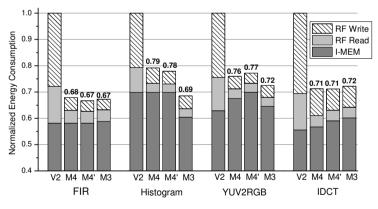

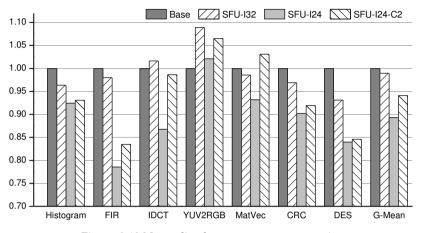

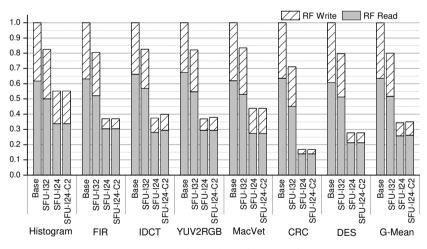

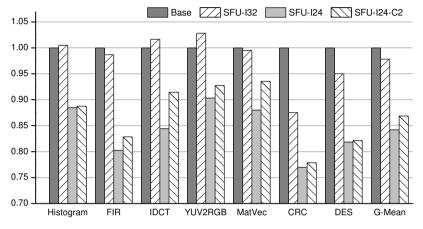

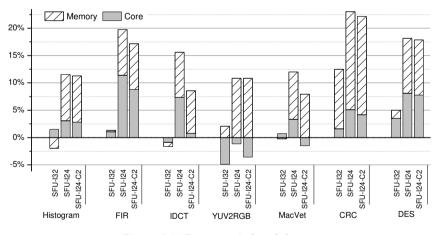

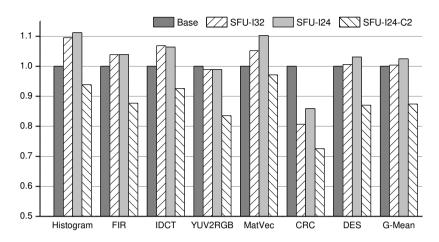

Table 2.3 shows the dynamic RF access reduction statistics obtained by cycle accurate simulation. In all tested kernels, both the RF read and write access reduction are substantial. Clearly, RF energy consumption is reduced dramatically. However, it would be more interesting to find out whether or not the total core indeed benefits from this saving. Figure 2.14 shows the normalized energy breakdown of both the reference RISC processor and the two-issue MOVE-Pro processor when executing the four benchmark kernels. Both dynamic energy and leakage energy are taken into consideration. However, since the processors are busy executing instructions in every cycle and the low power library we use has optimized for the leakage power, the leakage energy consumption is negligible compared to the dynamic energy consumption in this comparison. We can see that the reduction in RF energy is directly transferred to the total core energy saving, which demonstrates the low-power feature of the proposed MOVE-Pro architecture. In all kernels, the reduction of RF energy is more or less proportional to the reduction of RF accesses. The saving of total core energy is up to 11.6%. The detailed comparisons of power consumption and cycle counts are shown in Table 2.4.

Figure 2.14 Energy consumption comparison (normalized to the total energy consumption). For the comparison of energy per cycle, the diagram is similar as the cycle counts are exactly the same for FIR, Histogram, and YUV2RGB. And for IDCT, MOVE-Pro requires slightly less cycles according to Table 2.4.

|           |                      | Reference<br>RISC | Two-issue<br>MOVE-Pro |

|-----------|----------------------|-------------------|-----------------------|

|           | Relative Cycle Count | 1.00              | 1.00                  |

| FIR       | RF Power             | 0.84mW            | 0.24mW (-71.5%)       |

|           | Total Power          | 5.43mW            | 4.80mW (-11.6%)       |