has one dominant pole at the output of the opamp. A folded cascode opamp has been used to ensure stability. With proper design of the loop parameters, wide frequency range of operation can be achieved.

Experimental results: To illustrate the principle, a PWLL was designed as a duty cycle adjuster for the input clock of a 10 bit, 40 MS/s pipelined analogue-to-digital converter in a 0.18μ CMOS process at 1.8 V. The power consumption is <1 mW at 1.8 V. Fig. 4 shows the measured performance (SNRD and THD) of the ADC, both with the duty cycle adjuster turned ON and OFF at fs = 40 MHz and fin = 19 MHz. It can be seen that the SFDR and the THD remain flat as the input duty cycle is varied from 30 to 70% with the duty cycle adjuster ON. Conversely, when it is OFF, the performance drops drastically, even with 45% duty cycle. One enhancement to this design would be to use another FVC to control the coarse delay and hence a very wide operating frequency range can be achieved.

Fig. 4 Measured data with varying input clock duty cycle a SNRD

b THD

— DCA on

Conclusion: A novel approach based on a PWLL for the generation of a 50% duty cycle clock from an input clock with arbitrary duty cycle has been described. It can also be used to generate an output clock with duty cycles from 25 to 75%. The design has been shown to achieve this performance without affecting the jitter on one (sampling) edge of the input clock, which is very important for high-performance switched capacitor-based designs.

Acknowledgments: The author would like to thank E. Soenen for providing the opportunity to fabricate the design, K. Rao for the layout, and K. Nguyen for performing the measurements.

© IEE 2002

28 May 2002

Electronics Letters Online No: 20020657

DOI: 10.1049/el:20020657

S. Karthikeyan (Texas Instruments, Inc, Dallas, Texas 75243, USA)

# References

- WEIZMAN, A.: 'Delay line loop for 1X on-chip clock generation with zero skew and 50% duty cycle' US Patent No. 5,317,202

- NAKAMURA, K., et al.: 'A CMOS 50% duty cycle repeater using complementary phase blending'. Symp. on VLSI Circuits Dig. Tech. Papers, Honolulu, Hawaii, USA, 2000

- SIDROPOULOS, S., et al.: 'A 700 Mbps/pin CMOS signaling interface using current integrating receivers'. Symp. on VLSI Circuits, Honolulu, Hawaii, USA, June 1996, pp. 142-143

- DJEMOUAI, A., et al.: 'High performance integrated CMOS frequency to voltage converter'. ICM 1998, Berlin, Germany, 1998

- MINEATIS, J., and HOROWITZ, M.: 'Precise delay generation using coupled oscillations', IEEE J. Solid-State Circuits, 1993, 28, (12)

## Low power Schmitt trigger circuit

### S.F. Al-Sarawi

Three new Schmitt trigger circuits are described. The first circuit is a truly low power, while the second and third circuits are derived from the first circuit and provide smaller hysteresis width. Measurement results for the new Schmitt trigger circuits are presented.

Introduction: In most published Schmitt trigger circuits [1-7] the aspect of low power operation is not considered, this being sometimes due to the methodology used in designing such circuits or because this aspect is irrelevant to the targeted application. Such circuits are suitable for medium power applications, but the emergence of applications which can be sustained for many years on the energy available from a small battery or from a rectified RF signal, means that truly low power circuits must be developed.

All the designed circuits are simulated using HSPICE with level 28 model parameters for a 1.2  $\mu m$  standard CMOS technology.

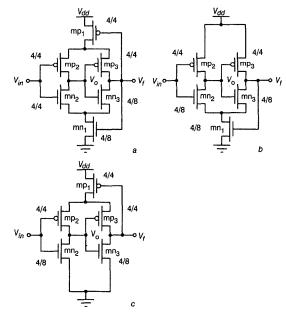

Low power prototype CMOS Schmitt trigger circuit: The prototype lower power Schmitt trigger circuit is shown in Fig. 1a. The prototype circuit consists of six transistors arranged in a complementary CMOS structure. Fig. 1b and c represent two variants of the first type with less hysteresis width.

Fig. 1 Three different Schmitt trigger circuits

Number next to each transistor represents width to length ratio in microns

- a Prototype low power circuits

- b Circuit derived from a

- c Second circuit derived from a

The operation of the prototype circuit can be understood as follows. When at first  $V_{in}$  is low,  $mn_2$  is OFF,  $mp_2$  is ON, forces  $mn_3$  to be ON,  $mp_3$  OFF, and  $mp_1$  ON.

As the input voltage rises, the input voltage  $V_{hl}$  at which the output switches from high to low then depends on the voltage at node  $V_n$  and switching point of the inverter structure which consists of mn2 and mp<sub>2</sub>. The result is

$$V_{hl} = V_n + \frac{V_{dd} + V_{th}(R-1) - V_n}{R+1}$$

(1)

where  $R = \sqrt{(\beta_{n2}/\beta_{p2})}$ ,  $\beta_{i_n}$  corresponds to the transconductance of transistor type i and number n in the schematic diagram. To simplify the analysis  $V_{th} = |V_{t_n}| = |V_{t_n}|$ , where  $V_{t_n}$  corresponds to the threshold voltage of a transistor n. The voltage at  $V_n$  can be found as a function of  $R_n$  and can be written as

$$V_n = \frac{V_{in}}{R_n + 1} + V_{th} \frac{(R_n - 1)}{(R_n + 1)},\tag{2}$$

where  $R_n = \sqrt{(\beta_{n1}/\beta_{n2})}$

Substituting (2) and  $V_{in} = V_{hl}$  in (1), we obtain

$$V_{hl} = V_{dd} \frac{(R_n + 1)}{R_n(R + 1) + 1} + V_{th} \frac{R_n(2R - 1) - 1}{R_n(R + 1) + 1}$$

(3)

(3) states the relation between the switching and supply voltage and the dependence of  $V_{hl}$  on the nMOS transistors geometry. From (3) it is possible to cancel the threshold voltage effect on the hysteresis by making  $\beta_n = \beta_p$ .

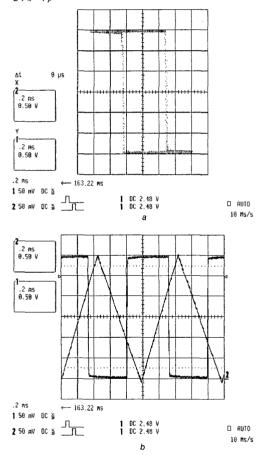

Fig. 2 Measured characteristics of fabricated low power Schmitt trigger circuit at 3 V supply voltage and input-output characteristics against time a Measured characteristics

b Input-output characteristics

A similar analysis can be performed to find the switching voltage  $V_{lh}$ from low to high. The answer can, however, be obtained directly by subtracting  $V_{hl}$  from  $V_{dd}$  which is given in (4) and introducing appropriate new definitions for the R and  $R_n$  factors.

$$V_{lh} = V_{dd} \frac{R_p(R+1)}{R_p(R+1) + 1} - V_{lh} \frac{R_p(2R-1) - 1}{R_p(R+1) + 1}$$

(4)

The hysteresis width of the fully symmetrical, low power Schmitt trigger circuit can be calculated by subtracting (4) from (3) and letting  $R_n = R_n$ , resulting in

$$V_{hw} = V_{hl} - V_{lh} = V_{dd} \frac{R_n(1-R)+1}{R_n(1+R)+1}$$

(5)

Experimental work: The circuit shown in Fig. 1a was fabricated in a 2 μm double poly, double metal standard p-well process through Orbit Semiconductor. The Schmitt trigger circuit was buffered with one inverter to drive the output node.

The measured results using 3 V supply voltage are shown in Fig. 2. The designed switching points for the Schmitt trigger can be calculated using (3), (4) and (5) with  $R_n = R_p = R = 1$ , resulting in  $V_{hl} = V_{dd}/3$ ,  $V_{lh} = 2V_{dd}/3$  and  $V_{hw} = V_{dd}/2$ . The measured switching point is slightly shifted from  $V_{dd}/2$  due to the difference in the ratio of the mobility of the fabricated n and p MOS transistors from the values used in the design. Although, direct measurement of the current was not possible, simulations show the short circuit current between the supply rails during switching is very small (of the order of 200 nA) using the transistor sizes shown in the schematic diagram, resulting in low fanout. The fan-out of the Schmitt trigger circuit can be improved by buffering the output node and increasing the width of mn2, mp2, mn<sub>3</sub> and mp<sub>3</sub>.

Conclusion: Three new Schmitt trigger circuits have been discussed, with one type having low power characteristics. Measured results verified the principle of operation and the characteristics of this low power Schmitt trigger circuit. The circuit has been used in the design of low power, very low frequency integrator oscillators.

© IEE 2002

22 November 2001

Electronics Letters Online No: 20020687

DOI: 10.1049/el:20020687

S.F. Al-Sarawi (The Centre for High Performance Integrated Technology & Systems (CHiPTec), Department of Electrical and Electronic Engineering, Adelaide University, North Terrace, Adelaide 5005. Australia)

E-mail: alsarawi@eleceng.adelaide.edu.au

#### References

- NAGARAJ, M., and SATYAM, K.: 'Novel CMOS Schmitt trigger', Electron. Lett., September 1981, 17, (19), pp. 693-694

- STEYAERT, M., and SANSEN, W.: 'Novel CMOS Schmitt trigger', Electron. Lett., February 1986, 22, (4), pp. 203-205

- DOKIC, B.L., ILISKOVIC, A.J., and BUNDALO, Z.V.: 'CMOS gates with regenerative action at one of the inputs', Microelectron. J., May-June 1988, **19**, (3), pp. 17–20

- ENNING, B.: 'A novel Schmitt-trigger circuit with GaAs MESFETs', Frequenz, May 1990, 44, (5), pp. 155-157

- PFISTER, A.: 'Novel CMOS Schmitt trigger with controllable hysteresis', Electron. Lett., March 1992, 28, (7), pp. 639–641 IBM. CMOS Schmitt trigger buffer. IBM Tech. Discl. Bull. August 1986,

- 29, (3), pp. 1353-1354.

- DOKIC, B.L.: 'CMOS NAND and NOR Schmitt circuits', Microelectron. J., November 1996, 27, (8), pp. 757–765

## Efficient implementation of lifting-based discrete wavelet transform

Hongyu Liao, M.K. Mandal and B.F. Cockburn

A recursive architecture for implementing the lifting-based discrete wavelet transform is proposed. Processing of the transform stages is interleaved, improving the hardware utilisation and efficiency.

Introduction: Factoring discrete wavelet transforms (DWT) into lifting steps can reduce the computational complexity by up to 50% [1]. Several lifting-based architectures have been proposed. Andra et al. [2] proposed an architecture (ACT) that uses simple functional blocks.