## Low resistance, nonalloyed Ohmic contacts to InGaAs

Adam M. Crook,<sup>a)</sup> Erik Lind, Zach Griffith, and Mark J. W. Rodwell

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106, USA

Jeremy D. Zimmerman and Arthur C. Gossard

Materials Department, University of California, Santa Barbara, California 93106, USA

Seth R. Bank

Microelectronics Research Center, University of Texas, Austin, Texas 78712, USA

(Received 19 July 2007; accepted 17 October 2007; published online 9 November 2007)

We report extremely low specific contact resistivity ( $\rho_c$ ) nonalloyed Ohmic contacts to *n*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As, lattice matched to InP. Contacts were formed by oxidizing the semiconductor surface through exposure to ultraviolet-generated ozone, subsequently immersing the wafer in ammonium hydroxide (NH<sub>4</sub>OH, 14.8 normality), and finally depositing either Ti/Pd/Au contact metal by electron-beam evaporation or TiW contact metal by vacuum sputtering. Ti/Pd/Au contacts exhibited  $\rho_c$  of (0.73±0.44)  $\Omega \ \mu m^2$ —i.e., (7.3±4.4)×10<sup>-9</sup>  $\Omega \ cm^2$ —while TiW contacts exhibited  $\rho_c$  of (0.84±0.48)  $\Omega \ \mu m^2$ . The TiW contacts are thermally stable, showing no observable degradation in resistivity after a 500 °C annealing of 1 min duration. © 2007 American Institute of *Physics*. [DOI: 10.1063/1.2806235]

High-speed electronic and optoelectronic devices require reliable, low resistance Ohmic contacts which do not contribute excess dc voltage drops or *RC* time constants as device dimensions are reduced and current densities are increased. For heterojunction bipolar transistors (HBTs), emitter and base contact resistivities must decrease in proportion to the inverse square of the transistor cutoff frequency.<sup>1,2</sup> Field-effect transistors<sup>3,4</sup> similarly require progressive reductions in contact resistivity as increased device bandwidths are sought. Because InP-based materials are employed in many of the widest-bandwidth electron devices,<sup>4–6</sup> further improvement of contacts to InP-based semiconductors is of central importance to the development of terahertz electronics.

In HBTs having the highest power-gain cutoff frequency  $(f_{\text{max}} = 755 \text{ GHz})$  reported to date,<sup>5,6</sup> the emitter contact resistance was  $\sim 5 \ \Omega \ \mu m^2 \ (5 \times 10^{-8} \ \Omega \ cm^2)$  and the base contact resistance was  $<5 \Omega \mu m^2$ . To obtain simultaneous current-gain  $(f_{\tau})$  and power-gain cutoff frequencies above 1.5 THz, the transistor lithographic and epitaxial dimensions must be reduced (scaled) and the emitter and base Ohmic contact resistance must be reduced to  $\sim 1 \Omega \mu m^{2.1,2}$  State-ofthe-art high electron mobility transistors have demonstrated  $f_{\tau}$  > 500 GHz with contact resistance of 0.007  $\Omega$  mm by utilizing high indium content  $n^+$  contact layer. The details of the surface preparation were not discussed.<sup>4</sup> While nonalloyed Ohmic contacts to high-indium-content  $In_xGa_{1-x}As$  generally exhibit low contact resistivity, the particular resistivity attained has a strong dependence on the procedures used to remove surface oxides prior to contact deposition.<sup>7</sup> Stareev et al. obtained 4.3  $\Omega \ \mu m^2$  resistivity Ohmic contacts to In<sub>0.53</sub>Ga<sub>0.47</sub>As and 1.7  $\Omega \mu m^2$  to InAs, both results using in situ Ar<sup>+</sup> sputter cleaning prior to contact deposition.<sup>4</sup> Here we report a surface preparation procedure for fabrication of extremely low resistivity (<1  $\Omega \mu m^2$  and <0.004  $\Omega mm$ ) Ohmic contacts to *n*-type  $In_{0.53}Ga_{0.47}As$ . In this procedure, the surface was first oxidized by exposure to UV-generated ozone, followed by an immersion in ammonium hydroxide (NH<sub>4</sub>OH, 14.8 normality). Then Ti/Pd/Au was deposited by electron-beam evaporation or TiW alloy contact metal was deposited via Ar<sup>+</sup> sputtering. The contact resistivities obtained are sufficiently low to allow transistor scaling to achieve  $f_{\tau}$  and  $f_{max}$  simultaneously above 1 THz.<sup>2</sup> The TiW alloy based contact preparation procedure can be readily incorporated into the process flow for fabrication of 125 nm emitter width InP mesa HBTs. The TiW contacts are thermally stable, showing no increase in contact resistivity after a 500 °C, 1 min annealing.

Samples were grown by solid-source molecular beam epitaxy. An unintentionally doped 1000 Å In<sub>0.52</sub>Al<sub>0.48</sub>As buffer was grown on (100) semi-insulating InP, followed by 1000 Å of *n*-type  $In_{0.53}Ga_{0.47}As$  with an active Si doping of  $\sim 3.5 \times 10^{19}$  cm<sup>-3</sup>. Hall measurements were used to determine the active dopant concentration and the electron mobility (1266 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) of the *n*-type InGaAs layer. Prior to metal deposition, the surface of each sample was prepared using a 10 min long UV-ozone<sup>8</sup> treatment followed by a 10 s ammonium hydroxide, NH<sub>4</sub>OH, dip, after which the sample were blown dry using N<sub>2</sub>. The effect of NH<sub>4</sub>OH concentration on specific contact resistance was investigated for each contact metal scheme. Samples were processed into transmission line method (TLM) structures in order to extract the specific contact resistance.<sup>9</sup> The Ti/Pd/Au contacts were patterned using I-line optical lithography and lifted off after a single pump down e-beam deposition of Ti/Pd/Au (200 Å/400 Å/2000 Å) The TiW/Ti/Ni(5000 Å/200 Å/ 1000 Å) contacts (TiW in a 10% Ti and 90% W alloy) process involved a blanket Ar sputtering deposition of TiW directly after the surface preparation. A Ti/Ni dry etch mask was then deposited with a single pump down e-beam evaporator and lifted off. The TiW was dry etched with SF<sub>6</sub>/Ar using inductively coupled plasma. After the contacts were

**91**, 192114-1

<sup>&</sup>lt;sup>a)</sup>Electronic mail: acrook@umail.ucsb.edu

<sup>© 2007</sup> American Institute of Physics

Downloaded 01 Jun 2010 to 129.116.135.80. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

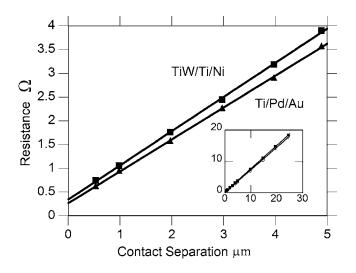

FIG. 1. TLM pattern resistance as a function of contact spacing for the TiW/Ti/Ni and Ti/Pd/Au contacts to  $In_{0.53}Ga_{0.47}As$ . The TLM pattern width was 25  $\mu$ m. Also shown are linear regressions to the data. The inset shows resistance vs contact separation for all measured lengths (0.5–25  $\mu$ m).

formed, a second lithographic step and wet etch were performed to isolate the TLM patterns.

Resistances were measured at room temperature using the four-point (Kelvin) probe technique on an Agilent 4155C semiconductor parameter analyzer. The TLM pattern and In-GaAs thickness were designed to obtain acceptable accuracy when measuring specific contact resistance of the order of 1  $\Omega \ \mu m^2$ . Kelvin probing measures only that fraction of the resistance within the circuit branch shared between the current biasing contacts and the voltage measurement contacts; for each TLM contact pad, separate probe contact pads were provided for current biasing and for voltage measurement, with  $<5 \ \mu m$  shared path length on the integrated circuit (IC) interconnects. This minimizes resistance contributions from IC metallization and renders the measurement independent of probe placement.<sup>10</sup> To ensure that the measured resistance was dominated by contact resistance at small TLM contact spacings, and by semiconductor sheet resistance at large contact spacings, the TLM pattern had spacings varying from 500 nm to 25  $\mu$ m. The TLM pattern width was 25  $\mu$ m. After fabrication, the TLM pattern lengths and widths were verified using a scanning electron microscope. Finally, the  $n^+$ layers were kept thin,  $\sim 100$  nm, to reduce the resistance contribution from two-dimensional current flow within the semiconductor. Under these circumstances, the TLM method has been previously found to be the most precise technique for measuring contact resistance.<sup>1</sup>

Typical data are shown in Fig. 1 for TiW/Ti/Ni and Ti/Pd/Au contacts deposited after a 14.8 normality NH<sub>4</sub>OH immersion. The specific contact resistance ( $\rho_c$ ) and the semiconductor sheet resistance ( $R_{\rm sh}$ ) were calculated (Fig. 1) from linear fits to the measured data by using the extrapolated transfer length ( $L_t$ ) and contact resistance ( $R_c$ ), using  $\rho_c = L_t^2 R_{\rm sh}$  and  $R_{\rm sh} = R_c W/L_t$ .

Ti/Pd/Au and TiW/Ti/Ni contacts yielded as-deposited  $\rho_c$  of 0.73 and 0.84  $\Omega \mu m^2$ , respectively, when treated with 14.8 normality NH<sub>4</sub>OH. At high NH<sub>4</sub>OH concentrations, contacts to In<sub>0.53</sub>Ga<sub>0.47</sub>As exhibited lower resistance than similar contacts to InAs (2.4  $\Omega \mu m^2$ ). The effect of concentration of NH<sub>4</sub>OH during surface preparation on specific Downloaded 01 Jun 2010 to 129.116.135.80. Redistribution subjects

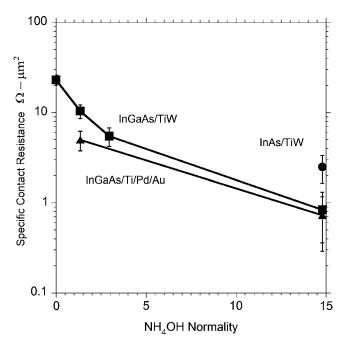

FIG. 2. Specific contact resistivity ( $\rho_c$ ) as a function of the concentration of the NH<sub>4</sub>OH predeposition soak.

contact resistance for  $In_{0.53}Ga_{0.47}As$  wafers for each metallization scheme is shown in Fig. 2. Both TiW/Ti/Ni and Ti/Pd/Au contacts showed a rapid reduction in specific contact resistance with increased NH<sub>4</sub>OH concentration during surface preparation. We can present only limited data with the Ti/Pd/Au metalization at high NH<sub>4</sub>OH concentrations because photoresist adhesion was greatly reduced and yield in metal lift-off was consequently impaired. By contrast, the TiW/Ti/Ni contacts were deposited by blanket metal deposition by sputtering, photoresist was not present during the concentrated NH<sub>4</sub>OH soak, and fabrication yield was not impaired.

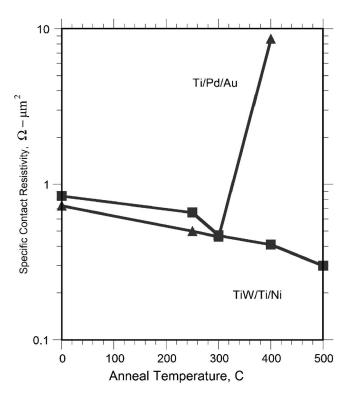

Contact thermal stability was investigated using rapid thermal annealing for temperatures up to 500 °C for an annealing time of 1 min in a N<sub>2</sub> atmosphere (Fig. 3). The Ti/Pd/Au contacts degraded for annealings >300 °C, whereas the TiW-based contacts showed very low  $\rho_c$  even after a 500 °C annealing. TiW based contacts exhibited a small decrease in contact resistivity from 0.84 to 0.5  $\Omega \mu m^2$ . The degradation of the Ti/Pd/Au contact above 300 °C is believed to originate from In outdiffusion from the semiconductor into the contact metal stack.<sup>12</sup> TiW, in contrast, appeared to be an effective diffusion barrier and substantially improved thermal stability.

Very low resistivity Ohmic contacts  $(0.5 \ \Omega \ \mu m^2)$  between Ti/Pt/Au and *n*-type InAs were reported in Ref. 12, but the surface preparation procedures were not described. We have been able (Fig. 2) to attain contact resistivities to In<sub>0.53</sub>Ga<sub>0.47</sub>As similar to Ref. 12 only through the use of predeposition surface preparation by immersion in concentrated (14.8 normality) NH<sub>4</sub>OH, while for contacts to InAs we can obtain contacts no better than 2.4  $\Omega \ \mu m^2$  even with concentrated NH<sub>4</sub>OH immersion. We are unable to ascribe the possible discrepancy between the results of Ref. 12 and ours to the resistance of the InAs/InGaAs abrupt heterojunction employed here (Ref. 12 incorporates a graded InGaAs/InAs heterojunction). The results reported in Ref. 10 indicate that this interface has an upper bound of 0.5  $\Omega \ \mu m^2$  resistivity at

Downloaded 01 Jun 2010 to 129.116.135.80. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Specific contact resistivity as a function of anneal temperature for  $In_{0.53}Ga_{0.47}As$  samples prepared with 14.8 normality ammonium hydroxide.

the doping levels we employ. It might be noted that the method used in Ref. 12 to extract  $\rho_c$  must distinguish two components of the total observed resistance, spreading resistance and contact resistance, by separating by the regression into two resistances each dependant on diameter (*D*) of a small circular contact: a spreading term of 1/D dependence and a contact term of  $1/D^2$  dependence. The amount of resistance attributed to the contacts in Ref. 12 for each measurement was less than 5% of the total measured resistance, making the extracted  $\rho_c$  sensitive to external sources of error.

Errors in measurement of the TLM resistance and dimensions will result in errors in the extracted  $\rho_c$ . Using the error analysis of Ref. 13 for the samples with the most concentrated NH<sub>4</sub>OH immersion, the specific contact resistivity  $\rho_c$  of the Ti/Pd/Au contacts is (0.73±0.44)  $\Omega \mu m^2$ , while TiW contacts exhibited  $\rho_c$ =(0.84±0.48)  $\Omega \mu m^2$ . Accurate determination of  $\rho_c$ <1.0  $\Omega \mu m^2$  will require minimum TLM gap spacings well below 0.5  $\mu m$ .

The one-dimensional current flow approximation used to extract the specific contact resistance in the transmission line method is reported to be valid for transfer lengths  $L_t$  longer than twice the conducting layer thickness t.<sup>14</sup> For our contacts, the extracted ~150 nm  $L_t$  corresponds to only 1.5t. From numerical finite-element analysis of the two-

dimensional current flow within a TLM structure having  $L_t=1.5t$ , we find that the experimentally determined  $\rho_c$  is 10% larger than the actual resistivity of the contacts. Therefore, the  $\rho_c$  we report using the 1D approximation is actually an overestimate.

In conclusion, we have been able to significantly reduce the contact resistance to *n*-type  $In_{0.53}Ga_{0.47}As$  through appropriate surface preparation prior to metal deposition. TiW contacts showed record low contact resistance even after annealing at 500 °C. The robust process and thermal stability of the TiW contacts make these an appealing choice for ~100 nm width emitter contacts in highly scaled HBTs, and in other electronic and optoelectronic devices of near-terahertz bandwidths.

The authors would like to thank the Office of Naval Research program (N000140610015), Defense Advanced Research Projects Agency under the SWIFT program, and a grant by the Swedish Research Council for partially supporting this work.

- <sup>1</sup>M. J. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. P. Smith, S. Jaganathan, S. Krishnan, S. I. Long, R. Pullela, B. Agarwal, U. Bhattacharya, L. Samoska, and M. Dahlstrom, IEEE Trans. Electron Devices **48**, 2606 (2001).

- <sup>2</sup>M. J. W. Rodwell, M. Le, and B. Brar, InP Bipolar ICs: Scaling Roadmaps, Frequency Limits, Manufacturable Technologies, Proceedings of the IEEE, (to be published).

- <sup>3</sup>T. Takahashi, M. Sato, K. Makiyama, T. Hirose, and N. Hara, Proceedings of the Conference on Indium Phosphide and Related Material, Matsue, Japan (IEEE, New York, 2007), pp. 55–58.

- <sup>4</sup>K. Shinohara, Y. Yamashita, A. Endoh, I. Watanabe, K. Hikosaka, T. Matsui, T. Mimura, and S. Hiyamizu, IEEE Electron Device Lett. 25, 241 (2004).

- <sup>5</sup>Z. Griffith, E. Lind, M. Rodwell, X. M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and A. W. K. Liu, Proceedings Conference on Indium Phosphide and Related Materials, Matsue, Japan (IEEE, New York, 2007) pp. 403–406.

- <sup>6</sup>E. Lind, Z. Griffith, and M. J. W. Rodwell, Proceedings of the Device Research Conference, University Park, Pennsylvania (IEEE, New York, 2006), late news, pp. 3–4.

- <sup>7</sup>G. Stareev, H. Künzel, and G. Dortmann, J. Appl. Phys. **74**, 7344 (1993).

- <sup>8</sup>R. Driad, Z. H. Lu, S. Laframboise, D. Scansen, W. R. McKinnon, and S. P. McAlister, Proceedings of the Conference on Indium Phosphide and Related Materials, Tsukuba, Japan (IEEE, New York, 1998), pp. 459–462.

<sup>9</sup>H. H. Berger, Solid-State Electron. 15, 145 (1972).

- <sup>10</sup>U. Singisetti, A. M. Crook, E. Lind, J. D. Zimmerman, M. A. Wistey, S. R. Bank, A. C. Gossard, and M. J. W. Rodwell, Proceedings of the Device Research Conference, Notre Dame, Indiana, (IEEE, New York, 2007), pp. 149–150.

- <sup>11</sup>W. M. Loh, S. E. Swirhun, T. A. Schreyer, R. M. Swanson, and K. C. Saraswat, IEEE Trans. Electron Devices ED-34, 512 (1987).

- <sup>12</sup>T. Nittono, H. Ito, O. Nakajima, and T. Ishibashi, Jpn. J. Appl. Phys., Part 1 27, 1718 (1988).

- <sup>13</sup>H. Ueng, D. Janes, and K. Webb, IEEE Trans. Electron Devices 48, 758 (2001).

- <sup>14</sup>E. G. Woelk, H. Krautle, and H. Beneking, IEEE Trans. Electron Devices 33, 19 (1986).