# Low-temperature atomic layer deposition-grown Al<sub>2</sub>O<sub>3</sub> gate dielectric for GaN/AlGaN/GaN MOS HEMTs: Impact of deposition conditions on interface state density

Milan Ťapajna, Lukáš Válik, Filip Gucmann, Dagmar Gregušová, Karol Fröhlich, Štefan Haščík, and Edmund DobročkaLajos Tóth and Béla PéczJán Kuzmík

Citation: J. Vac. Sci. Technol. B 35, 01A107 (2017); doi: 10.1116/1.4972870

View online: http://dx.doi.org/10.1116/1.4972870

View Table of Contents: http://avs.scitation.org/toc/jvb/35/1

Published by the American Vacuum Society

## Articles you may be interested in

On the origin of interface states at oxide/III-nitride heterojunction interfaces

J. Vac. Sci. Technol. B 120, 225305 (2016); 10.1063/1.4971409

Al2O3/SiO2 nanolaminate for a gate oxide in a GaN-based MOS device

J. Vac. Sci. Technol. B 35, 01B122 (2016); 10.1116/1.4971399

Plasma enhanced atomic layer deposition of Al2O3 gate dielectric thin films on AlGaN/GaN substrates: The role of surface predeposition treatments

J. Vac. Sci. Technol. B 35, 01B140 (2016); 10.1116/1.4972257

Incorporation of AI or Hf in atomic layer deposition TiO2 for ternary dielectric gate insulation of InAIN/GaN and AIGaN/GaN metal-insulator-semiconductor-heterojunction structure

J. Vac. Sci. Technol. B 35, 01B132 (2016); 10.1116/1.4972252

# Low-temperature atomic layer deposition-grown Al<sub>2</sub>O<sub>3</sub> gate dielectric for GaN/AIGaN/GaN MOS HEMTs: Impact of deposition conditions on interface state density

Milan Ťapajna, a) Lukáš Válik, Filip Gucmann, Dagmar Gregušová, Karol Fröhlich, Štefan Haščík, and Edmund Dobročka

Institute of Electrical Engineering, Slovak Academy of Sciences, Dúbravská cesta 9, SK-84104 Bratislava, Slovakia

#### Lajos Tóth and Béla Pécz

Institute of Technical Physics and Materials Sciences, EK MTA, Konkoly T. M. út 29-33, H-1121 Budapest, Hungary

# Ján Kuzmík

Institute of Electrical Engineering, Slovak Academy of Sciences, Dúbravská cesta 9, SK-84104 Bratislava, Slovakia

(Received 30 August 2016; accepted 5 December 2016; published 22 December 2016)

The oxide/semiconductor interface state density  $(D_{ii})$  in Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN metal-oxide-semiconductor high-electron mobility transistor (MOS-HEMT) structures with gate oxides grown by atomic layer deposition at low deposition temperature is analyzed in this work. MOS-HEMT structures with Al<sub>2</sub>O<sub>3</sub> gate oxide were deposited at 100 and 300 °C using trimethylaluminum precursor and H<sub>2</sub>O and O<sub>3</sub> oxidation agents. The structures were found to show negative net charge at oxide/barrier interface with density  $(N_{int})$  of  $10^{13}$  cm<sup>-2</sup>, which was attributed to the reduction of barrier surface donor density  $(N_{DS})$ .  $D_{it}$  was determined using capacitance transient techniques, and the results were assessed by the simulations of the capacitance-voltage characteristics affected by interface traps. The results indicate a lower interface quality of the sample with Al<sub>2</sub>O<sub>3</sub> grown using O<sub>3</sub> agent compared to those with H<sub>2</sub>O, even though the former provided lowest gate leakage among the analyzed structures. Moreover, to uncover the  $N_{DS}$  nature,  $D_{it}$  distributions determined here were compared to that reported previously on devices with  $N_{int}$  close to zero, i.e., with fully compensated surface barrier polarization charge by N<sub>DS</sub> [Tapajna et al., J. Appl. Phys. 116, 104501 (2014)]. No clear correlation between  $D_{it}$  and  $N_{DS}$  was concluded, indicating the nature of  $N_{DS}$  to be different from that of interface states in the energy range analyzed here. © 2016 American Vacuum Society. [http://dx.doi.org/10.1116/1.4972870]

### I. INTRODUCTION

Recently, GaN high-electron mobility transistors (HEMTs) have been considered to replace Si power switching transistors in high-efficiency AC/DC and DC/DC converters due to lower ON-state resistance and superior dynamic properties of the GaN devices. 1-3 For switching devices, enhancementmode transistors with threshold voltage  $(V_{th})$  as high as  $\sim 5 \text{ V}$ are often required from the system level.<sup>4</sup> Owing to inherent depletion-mode character of the GaN HEMTs, a great effort has been devoted toward the development of enhancementmode (or normally-off) devices for switching applications. 1-6 Although several concepts for normally-off GaN HEMTs have been proposed in the literature, 2,5,6 fabrication of such devices with sufficiently high  $V_{th}$  (~5 V) and uncompromised current driving capability (compared to normally-on counterparts) remains a challenge. Application of a metal-oxidesemiconductor (MOS) gate structure in GaN HEMTs (MOS-HEMTs) offers a promising approach to overcome the existing trade-off between  $V_{th}$  and output current of the device, providing sufficiently high negative polarization

charge  $(>1.8 \times 10^{13} \, \text{cm}^{-2})$  is left uncompensated at the oxide/barrier interface.<sup>7–9</sup> In this case, normally-off device operation can be achieved, and, moreover,  $V_{th}$  can be increased by oxide thickness  $(t_{ox})$  increasing to a desired value.<sup>8,10,11</sup> However, polarization charge at the barrier surface is fully compensated in most of the cases by the charge referred here to as surface donors, while its origin and nature has not been understood yet.

One of the possibilities to partially suppress the surface donors' formation in GaN MOS-HEMTs is to employ atomic layer deposition (ALD) for growth of the gate dielectric. Recently, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> grown by ALD at 100 °C provided normally-off operation of InAlN/GaN MOS-HEMT with positive  $V_{th}$  shift compared to the reference Schottkygated structure and  $V_{th}$  increase with the increase in  $t_{ox}$ . This has been attributed to the reduction of the surface donors' density from 4.5 to about  $1 \times 10^{13} \, \mathrm{cm}^{-2}$  as a result of low deposition temperature  $(T_D)$  during ALD. 11 It has been proposed by several authors that surface donors are located at or close to oxide/III-N barrier interface.<sup>7–9</sup> Therefore, a possible relationship between  $N_{DS}$  and distribution of the oxide/barrier interface traps  $(D_{it})$  represents a relevant question, yet not explored in more detail in the

a) Electronic mail: milan.tapajna@savba.sk

literature. In this work, we investigated  $D_{it}(E)$  distribution in  $Al_2O_3/GaN/AlGaN/GaN$  MOS-HEMT structures with gate oxide grown by ALD.  $D_{it}$  distribution was measured on samples with  $Al_2O_3$  deposited at 100 and 300 °C using trimethylaluminum (TMA) precursor and two oxidation agents:  $H_2O$  and  $O_3$ . First, the structural properties of the processed structures are presented, and the methodology for  $D_{it}$  determination using capacitance techniques is discussed. Experimentally determined  $D_{it}$  distributions were then compared to that of MOS-HEMTs with fully compensated surface polarization charges reported previously.

#### II. EXPERIMENTAL PROCEDURES

The Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MOS-HEMT structures were fabricated on commercial (Cree) GaN/Al<sub>0.29</sub>Ga<sub>0.71</sub> N/GaN heterostructures (from top 3 nm/17 nm/1.7  $\mu$ m) grown on 4H-SiC substrate by metal-organic chemical vapor deposition (MOCVD). After Ti/Al/Ni/Au Ohmic contacts evaporation and annealing (850 °C, 1 min), Al<sub>2</sub>O<sub>3</sub> gate dielectrics were grown by ALD at 100 and 300°C using TMA as Al precursor and H2O as oxidation agent (referred to as H2O-100 °C and H<sub>2</sub>O-300 °C in the following) and at 100 °C using  $O_3$  oxidation agent ( $O_3$ -100 °C). For all three sets of samples, Al<sub>2</sub>O<sub>3</sub> films with thickness of 10, 20, and 30 nm (nominal thickness) were deposited to allow analysis of the charge distributions in the gate stack. All structures then underwent postdeposition annealing step performed at 400°C for 15 min. Fabrication of MOS-HEMT structures was accomplished by Ni/Au (40 nm/50 nm) gate evaporation and patterning using optical lithography and lift-off process.

The structural and chemical properties of the prepared dielectric films were studied using high-resolution transmission electron microscopy (HR-TEM) and x-ray photoelectron spectroscopy (XPS) on bare samples with 10-nm thick Al<sub>2</sub>O<sub>3</sub> films grown on GaN/AlGaN/GaN heterostructures. The samples underwent similar postdeposition annealing step as to MOS-HEMT devices. For HR-TEM study, specimens embedded in a Ti disk were mechanically ground and polished down to 50  $\mu$ m, followed by 7 kV Ar<sup>+</sup> ion milling until perforation. JEOL 3010 was used operating at 300 kV with a point resolution of 0.17 nm. XPS measurements were performed using Perkin Elmer PHI 1600 system equipped with a spherical capacitor analyzer and a monochromated AlK $\alpha$  radiation source ( $h\nu = 1486.6 \,\mathrm{eV}$ ) with a 23.5 eV of pass energy. To determine the stoichiometry of the Al<sub>2</sub>O<sub>3</sub> films, the O/Al area ratio was calculated from the single peaks deconvoluted from the O1s and Al2p spectra (not shown in detail). The O/Al ratio ranges from 1.7 to 1.9 (as summarized in Table I), that is, slightly higher compared to stoichiometric Al<sub>2</sub>O<sub>3</sub> (1.5). Similar values have been reported in the literature for thin Al<sub>2</sub>O<sub>3</sub> films oxide that was attributed to excess of O atoms close to the surface. 12 X-ray reflectivity (XRR)<sup>13</sup> was used for oxide thickness ( $t_{ox}$ ) measurement using Al<sub>2</sub>O<sub>3</sub> layers deposited on commercial SiO<sub>2</sub>/ Si substrates in the same run as MOS-HEMT devices. For XRR measurements, Bruker AXS-D8 Discover equipment

Table I. Summary of  $Al_2O_3$  films thickness measured by HR-TEM (10-nm thick films only) and XRR, static dielectric constant extracted from the CV measurements, and O/Al ratio determined from the XPS analysis.

|                                             | Al <sub>2</sub> C   | 3 thickn |      |      |                        |            |

|---------------------------------------------|---------------------|----------|------|------|------------------------|------------|

|                                             | -                   | Nomin    |      |      |                        |            |

|                                             | 10                  |          | 20   | 30   |                        |            |

|                                             | HR-TEM <sup>a</sup> |          | XRR  |      | $\varepsilon_{ox}^{b}$ | O/Al ratio |

| O <sub>3</sub> -100 °C                      | 9.0                 | 9.4      | 23.1 | 34.3 | 9.6                    | 1.86       |

| $H_2O\text{-}100^{\circ}C$                  | 12.0                | 11.3     | 22.0 | 32.9 | 9.6                    | 1.94       |

| $\mathrm{H_2O}	ext{-}300^{\circ}\mathrm{C}$ | 11.5                | 11.4     | 22.9 | 33.7 | 8.3                    | 1.72       |

$^a\mathrm{Determined}$  on bare  $\mathrm{Al_2O_3}$  films deposited on GaN/AlGaN/GaN heterostructure using the same conditions as for the MOS-HEMT devices.

with Cu K $\alpha$  radiation generated by an x-ray tube with a rotating anode operating at 12 kW was used.

DC current–voltage (IV), capacitance–voltage (CV), and capacitance transients of MOS HEMT devices were performed on circular diode structures with diameter of  $80~\mu m$ . All the capacitance measurements were performed using AC signal with an amplitude of 30~mV and a frequency of 100~kHz. As will be discussed in Sec. III D, all three set of samples showed reduced  $N_{DS}$  by about 50% compared to full compensation of the surface polarization charge, resulting in the oxide/barrier net charge density ( $N_{int}$ ) ranging from -1.1 to  $-1.2 \times 10^{13}~cm^{-2}$  (see Table II). Note that for fully compensated surface polarization charge by  $N_{DS}$ , the net charge  $N_{int}$  tends to be close to zero.  $^{7-9,14}$

$D_{it}$  distribution was determined on MOS-HEMT structures with  $t_{ox} = 10 \,\mathrm{nm}$  only, as it is expected to be independent of  $t_{ox}$ . Two complementary techniques were used: (1)  $D_{it}$  in the energy range of  $E_C$ - $E = 0.5-1.0 \,\mathrm{eV}$  was determined using  $V_{th}$ -transients, deduced from the capacitance transients measured at  $V_g \approx V_{th} - 0.5 \text{ V}$  at temperatures of 25, 75, and 125 °C. Only relative change  $(\Delta V_{th})$  between  $V_{th}$  transients measured after "filling" pulse  $V_F = 0$  (no filling) and  $V_F = 1.5 \text{ V}$  (interface traps filling) was used for  $D_{it}$  determination, to cancel out possible bulk trapping process (i.e.,  $V_{th}$  drift) previously discussed in Ref. 15.  $D_{it}(E)$  was determined from the time derivative of  $\Delta V_{th}$ -t. (2) Filtered light-assisted  $V_{th}$  transient technique was used to determine  $D_{it}$  distribution of very deep interface states in the range of 1.75–3.25 eV below  $E_C$ . Here, the difference between  $V_{th}$  transient measured in the dark and after light exposure was taken into account. The light from the broad-band Xe-lamp (SP, ASB-XE-175) was filtered using band-pass metal interference filters with FWHM spectral transmittance ranging from 17.5 to 5 nm for light energy of 1.75 to 3.25 eV, respectively. In contrast to Ref. 15, the light was exposed 50s after beginning of the transient and kept exposed until the termination of the measurement. Finally, the C-V curves of the MOS-HEMT structures were calculated using a numerical solver of the one-dimensional Poisson equation with the Shockley-Read-Hall statistics

$<sup>^{\</sup>rm b}$ Extracted from the dependence of total capacitance of MOS-HEMT structure as a function of  ${\rm Al_2O_3}$  thickness.

Table II. Summary of  $V_{th}$ - $t_{ox}$  slopes extracted from the C-V measurements on set of MOS-HEMT structures with  $t_{ox}$  = 10, 20, and 30 nm, together with resulting  $Q_{eff}$ . Also listed are polarization charge in the quantum well,  $P_{QW}$ , net charge density at Al<sub>2</sub>O<sub>3</sub>/barrier interface,  $N_{int}$ , metal/Al<sub>2</sub>O<sub>3</sub> SBH, and position of Fermi level in the equilibrium ( $V_g$  = 0 V)  $E_{F,0}$  in respect to the bottom of the GaN-cap conduction band.

| Sample                                                                       | $V_{th}$ - $t_{ox}$ slope (V/cm) | $Q_{eff}/q~(\mathrm{cm}^{-2})$                                                                   | $P_{QW}/q \text{ (cm}^{-2})$ | $N_{int}$ (cm <sup>-2</sup> )                                        | SBH (eV)            | $E_C$ - $E_{F,0}$ (eV) |

|------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------|---------------------|------------------------|

| O <sub>3</sub> -100 °C<br>H <sub>2</sub> O-100 °C<br>H <sub>2</sub> O-300 °C | -0.035<br>-0.025<br>-0.011       | $\begin{aligned} 1.34 \times 10^{12} \\ 1.09 \times 10^{12} \\ 8.0 \times 10^{11} \end{aligned}$ | $1.27 \times 10^{13}$        | $-1.14 \times 10^{13}$ $-1.16 \times 10^{13}$ $-1.22 \times 10^{13}$ | 3.55<br>3.45<br>3.3 | 1.85<br>1.75<br>2.0    |

accounting for the interface traps response, taking the measurement time into account. <sup>16</sup>

#### III. RESULTS AND DISCUSSION

#### A. Structural analysis

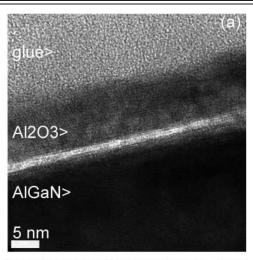

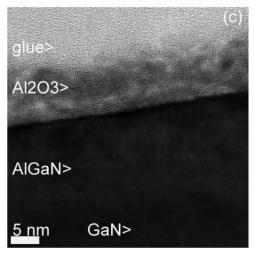

Cross-sectional HR-TEM images of samples with 10-nm thick Al<sub>2</sub>O<sub>3</sub> deposited by different ALD conditions on GaN/ AlGaN/GaN heterostructures are depicted in Figs. 1(a)–1(c). Atomically flat interface between Al<sub>2</sub>O<sub>3</sub> and III-N semiconductor can be inferred for all three samples. H<sub>2</sub>O-300 °C sample [Fig. 1(b)] shows notably smoother Al<sub>2</sub>O<sub>3</sub> surface compared to films grown at 100 °C [Figs. 1(a) and 1(c)]. The  $Al_2O_3$  thicknesses  $(t_{ox})$  measured by HR-TEM and XRR techniques are summarized in Table I. Similar  $t_{ox}$  (within the experimental error) was obtained from HR-TEM and XRR analyses for oxide films with nominal thickness of 10 nm grown on AlGaN/GaN and SiO<sub>2</sub>/Si substrates, respectively. Therefore,  $t_{ox}$  determined from the XRR measurement on all sets of samples was considered in the analysis described below. The barrier thickness (comprised of the GaN-cap and AlGaN layers) was found to be about 19 nm, in agreement with the nominal thickness.

Interestingly, despite low deposition temperature, all  $Al_2O_3$  films were found to have polycrystalline structure with the mean grain size of 15– $20\,\mathrm{nm}$ . Most of the crystal grains are well oriented to the GaN substrate with a face centered cubic structure (a =  $0.79\,\mathrm{nm}$ ). However, the crystallinity of the  $Al_2O_3$  films needs to be confirmed by the x-ray diffraction that is currently under investigation. It is worth mentioning that to avoid artifacts, special care was taken during the thinning procedure by using low temperature glue (> $100\,^{\circ}\mathrm{C}$ ) and the ion bombardment with a decreased ion energy of  $7\,\mathrm{kV}$  (instead of standard  $10\,\mathrm{kV}$ ). Crystallization of the ALD layers due to possible heating of electron beam during the TEM observation is unlikely in the experimental conditions used here.

#### B. I-V and C-V measurements

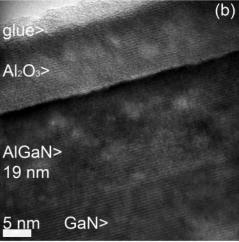

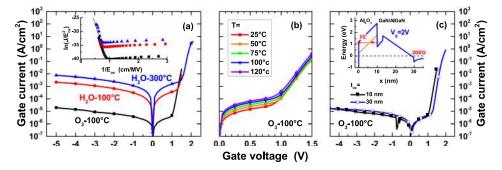

Figure 2(a) shows typical I-V characteristics of MOS-HEMT structures with  $t_{ox} = 10$  nm. Sample O<sub>3</sub>-100 °C shows lowest gate leakage ( $I_g$ ) of  $\sim 10^{-5}$  A/cm<sup>2</sup> at  $V_g = -5$  V, while it increases for devices with ALD-grown Al<sub>2</sub>O<sub>3</sub> using H<sub>2</sub>O to  $\sim 10^{-3}$  A/cm<sup>2</sup> at  $V_g = -5$  V. At positive  $V_g$ -s, a sharp increase in  $I_g$  can be observed. To understand this behavior, I-V measurements at different temperatures were performed as shown in Fig. 1(b). Weak temperature dependence of the exponential  $I_g$ - $V_g$  characteristics at  $V_g > 1$  V indicates tunneling

Fig. 1. (a) HR-TEM micrographs of  $H_2O\text{-}100\,^{\circ}\text{C}$  (a),  $H_2O\text{-}300\,^{\circ}\text{C}$  (b), and  $O_3\text{-}100\,^{\circ}\text{C}$  (c)  $Al_2O_3$  grown on GaN/AlGaN/GaN heterostructures taken on cross sectional thinned specimens.

Fig. 2. (Color online) (a) Typical I-V characteristics of Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MOS-HEMT structures with O<sub>3</sub>-100 °C, H<sub>2</sub>O-100 °C, and H<sub>2</sub>O-300 °C Al<sub>2</sub>O<sub>3</sub>. The inset shows the Fowler–Nordheim plot of I-V data at positive  $V_g$ -s resulting in tunneling barrier height of 0.92 eV using  $m^*$  = 0.28 $m_0$  (Ref. 17). (b) I-V characteristics of structure O<sub>3</sub>-100 °C measured at temperatures ranging from 25 to 120 °C. (c) Comparison between I-V characteristics of MOS-HEMT structures with 10 and 30-nm thick Al<sub>2</sub>O<sub>3</sub>. The inset of (c) depicts band diagram of the gate stack with sketch of field emission of electrons from bulk traps into Al<sub>2</sub>O<sub>3</sub> conduction band.

effects. Therefore, the I-V data at positive  $V_{g}$ -s were plotted in the so-called Fowler-Nordheim plot depicted in the inset of Fig. 2(a). From the high-field linear part of the plot, barrier height of 0.92 eV was extracted using effective electron tunneling mass of  $m^* = 0.28m_0$ , assuming electron tunneling from GaN into Al<sub>2</sub>O<sub>3</sub> conduction band through a triangular barrier. However, the resulting barrier height is more than two-times lower than the reported conduction band discontinuity between GaN and ALD grown Al<sub>2</sub>O<sub>3</sub>,  $\Delta E_C$  [~2.2 eV (Ref. 18)]. Moreover, I-V measurements on samples with different thickness depicted in Fig. 1(c) show similar gate voltage onsets of the  $I_g$  exponential increase, in contrast to its expected increase with  $t_{ox}$  (i.e., similar electric field in the oxide). Instead, this behavior can be explained by the field emission of electrons from trap centers in Al<sub>2</sub>O<sub>3</sub> located 0.92 eV below the conduction band minimum, as depicted in the inset of Fig. 2(c). We assume that for  $V_g > 1$  V, electrons are first injected from the channel into trap centers in Al<sub>2</sub>O<sub>3</sub> located near Al<sub>2</sub>O<sub>3</sub>/GaN-cap interface and then emitted into conduction band of the oxide. An important implication of the gate leakage onset at  $V_g > 1.5 \, \mathrm{V}$  is expected inability to form a free-electron accumulation in the AlGaN barrier upon higher positive  $V_g$ . <sup>19,20</sup> This effect excludes application of any AC admittance techniques for  $D_{it}(E)$  determination (such as that reported by Hori et al. in Ref. 21) in this voltage region, as leakage paths in Al<sub>2</sub>O<sub>3</sub>/AlGaN gate stack will effectively screen the capture-emission processes of interface traps.<sup>22</sup>

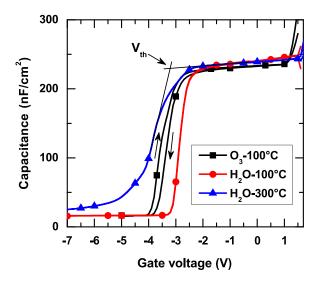

Figure 3 shows typical C-V characteristics of MOS-HEMT structures measured from depletion toward accumulation and backward with sweep rate of 0.2 V/s. From the C-V characteristics, the following features can be deduced:

- (1) As expected, similar  $V_{th}$  of -2.6, -3.0, and -3.3 V was extracted from the C-V curves (determined graphically in the depletion part similar to Refs. 15 and 23, cf. Fig. 3) for samples  $\text{H}_2\text{O}\text{-}100\,^{\circ}\text{C}$ ,  $\text{O}_3\text{-}100\,^{\circ}\text{C}$ , and  $\text{H}_2\text{O}\text{-}300\,^{\circ}\text{C}$ , respectively.

- (2) MOS-HEMT structure  $O_3$ -100 °C shows notable C-V (thus  $V_{th}$ ) hysteresis of  $\sim$ 0.2 V, while structures with oxide grown using  $H_2O$  show essentially no hysteresis.

- (3) While samples with O<sub>3</sub>-100 °C and H<sub>2</sub>O-100 °C Al<sub>2</sub>O<sub>3</sub> show similar and relatively steep *C-V* depletion, *C-V*

- curve for sample  $H_2O-300\,^{\circ}C$  is stretched-out in the depletion part.

- (4) All three C-V curves show sign of capacitance increase at  $V_g > 1.1\,\mathrm{V}$  (O<sub>3</sub>-100 °C) and  $V_g > 1.5\,\mathrm{V}$  (H<sub>2</sub>O-100 °C, H<sub>2</sub>O-300 °C) resembling C-V behavior for the so-called spill-over regime. In this case, population of free electrons in the AlGaN barrier leads to capacitance rise up to the gate oxide capacitance,  $C_{ox}$ . However, the capacitance increase may be also related to the gate leakage onset, as it appears at similar  $V_g$ -s [cf. Fig. 2(a)]. Moreover, 2DEG density extracted from the integration of the C-V curve in the range from  $V_g \sim V_{th}$  to spill-over regime would give sheet carrier density ranging from 6 to  $7 \times 10^{12}\,\mathrm{cm}^{-2}$  that is almost two-times lower than the expected value of  $1.3 \times 10^{13}\,\mathrm{cm}^{-2}$  given by AlGaN/GaN polarization charge. <sup>24</sup>

To analyze oxide/semiconductor interface quality in the processed MOS-HEMTs and its possible relation to the effects described above, first, we determined  $D_{it}$  distributions for all studied structures. Then, the MOS-HEMT C-V behavior as well as  $V_{th}$  hysteresis was simulated using 1D Poisson

Fig. 3. (Color online) Typical C-V characteristics of the Al $_2$ O $_3$ /GaN/AlGaN/GaN MOS-HEMT structures with  $t_{ox}=10$  nm.

calculation taking capture/emission processes of interface traps into account.

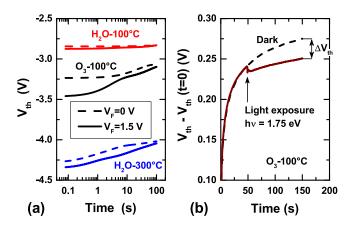

# C. $D_{it}(E)$ determination

$D_{it}$  distributions were measured using  $V_{th}$ -transient and photoassisted  $V_{th}$ -transient techniques on MOS-HEMT structures with  $t_{ox} = 10 \text{ nm}$ . Typical  $V_{th}$ -transients measured at T = 25 °C are compared in Fig. 4(a). Note that  $V_{th}$  increases with elapsed time for all three samples, suggesting electron capture rather than electron emission from interface traps expected to take place at negative bias. This can be understood as a result of electron injection from the gate electrode into bulk traps in the Al<sub>2</sub>O<sub>3</sub> similar to Ref. 15. To cancel this parasitic trapping out, only the difference between  $V_{th}$ -transients with  $V_F = 1.5 \,\mathrm{V}$  (interface traps filling) and  $V_F = 0 \,\mathrm{V}$ (no filling) was used to calculate  $D_{it}$  distribution for a given temperature. As expected, application of positive filling pulse induced more negative  $V_{th}$  shift at the beginning of the transients due to enhanced electron emission from filled traps. By repeating such measurements for T = 75 and 125 °C,  $D_{it}$  in the energy range of  $E_C$ -E = 0.6-1 eV was determined and is summarized in Fig. 5 for all studied structures. Although  $\Delta V_{th}$  transient includes emission from electron traps located also in the AlGaN and Al<sub>2</sub>O<sub>3</sub> aligned with the Fermi level, interface trap emission is expected to dominate, as evidenced in Refs. 23 and 25 by comparing  $V_{th}$  transients of Schottky- and MOS-gated HEMT structures.

The photoassisted  $V_{th}$  transient measurement is exemplified in Fig. 4(b) for sample O<sub>3</sub>-100 °C upon exposure of light with energy centered around 1.75 eV. Similar to  $V_{th}$  transients,  $V_{th}$  increases with elapsed time due to parasitic electron trapping. Therefore,  $V_{th}$  transient was first recorded in the dark and then repeated with light exposure. Light was exposed 50 s after beginning of transient measurement so that alignment between the two transients can be adjusted, as depicted in Fig. 4(b). Both measurements were stopped at t = 150 s, when the difference between the two transients (i.e.,  $\Delta V_{th}$ ) saturated. This procedure was then repeated for higher light energies.  $D_{it}$  was calculated from  $\Delta V_{th}$  and

Fig. 4. (Color online) (a) Comparison of  $V_{th}$  transients measured at room temperature using  $V_{meas} = V_{th} - 0.5 \text{ V}$ , without ( $V_F = 0 \text{ V}$ , dashed lines) and with filling pulse ( $V_F = 1.5 \text{ V}$ , solid lines) for separation of the parasitic bulk trapping effect. (b)  $V_{th}$  transients measured at the same voltage as in (a) upon dark condition and after exposure of filtered light at t = 50 s.

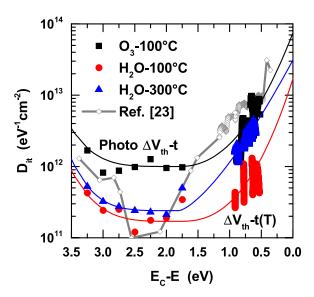

Fig. 5. (Color online) Summary of  $D_{it}$  distributions determined on Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MOS-HEMT structures analyzed here (symbols) and that reported in Ref. 23 (lines with symbols). Also shown are approximated  $D_{it}$  distributions (lines) used as input parameters for C-V simulations.

difference between two adjacent light energies as  $D_{it}(h\nu)$  =  $(\varepsilon_{ox}/t_{ox})[\Delta V_{th}/q(h\nu_i - h\nu_{i-1})]$ . Light energy  $h\nu$  was considered for  $E_{it}$ , as measured from the bottom of GaN conduction band. Capture of electrons (i.e., hole emission) from GaN valence band by interface traps for  $h\nu > E_g/2$  was not considered for simplicity.

The resulting  $D_{it}$  distributions of the analyzed MOS-HEMT structures are shown in Fig. 5. MOS-HEMT structures  $O_3$ -100 °C show highest  $D_{it}$  among the analyzed structures with a value of about  $10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  in the range of  $E_C$ -E = 3.25–1.75 eV that increases to a value of  $10^{13}$  eV<sup>-1</sup> cm<sup>-2</sup> in the range of  $E_C$ -E = 0.9- $0.5 \,\text{eV}$ . As compared to  $O_3$ -grown sample, both samples grown with H2O show an order of magnitude lower  $D_{it}$  of about  $2 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  in the range of  $E_C$ -E = 3.25–1.75 eV. Interestingly, despite lower deposition temperature, MOS-HEMT structure H<sub>2</sub>O-100 °C shows lower  $D_{it}$  of  $2 \times 10^{11} - 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  in the range of  $E_C - E = 0.9$  $-0.5 \,\mathrm{eV}$  compared to  $D_{it}$  ranging from 2 to  $5 \times 10^{12} \,\mathrm{eV}^{-1} \,\mathrm{cm}^{-2}$ for sample H<sub>2</sub>O-300 °C in the same energy range. Our data therefore indicates that application of O<sub>3</sub> oxidation agent during ALD growth of Al<sub>2</sub>O<sub>3</sub> at low deposition temperature provides lower interface quality compared to H<sub>2</sub>O, even though it gives the lowest gate leakage among the oxides analyzed here. Regarding the deposition temperature, our data suggest higher  $D_{it}$  in the range of  $E_C$ - $E = 0.9-0.5 \,\text{eV}$  for the structure with Al<sub>2</sub>O<sub>3</sub> grown with H<sub>2</sub>O at higher temperature, while the deposition temperature seems to have a minor impact on the gate leakage. Further, keeping in mind similar  $D_{it}$  distribution in the range of  $E_C$ - $E = 0.9 - 0.5 \,\text{eV}$  for  $O_3$ - $100 \,^{\circ}\text{C}$  and H<sub>2</sub>O-300 °C, one may expect similar C-V hysteresis for both MOS-HEMT structures. This is because interface traps in this energy range have been shown to re-emit electrons with time constant similar to duration of the  $V_g$  back-sweep (tenths of seconds). However, while structure O<sub>3</sub>-100 °C showed C-V hysteresis of about 0.2 V, sample H<sub>2</sub>O-300 °C showed negligible hysteresis (cf. Fig. 3).

#### D. C-V simulations

In order to support our hypothesis of the  $I_g$ -related capacitance increase at  $V_g = 1.5 \, \mathrm{V}$  and to understand discrepancies between C-V hysteresis and  $D_{it}$  distribution for sample  $\mathrm{H_2O}$ -300 °C, we performed the simulations of the C-V curves and corresponding hysteresis using the experimentally determined  $D_{it}$ . For the simulation, one needs to know exact charge distribution across the MOS-HEMT gate stack. While theoretical values can be used for the estimation of polarization charges at III-N interfaces, the net charge at oxide/III-N interface ( $Q_{int}$ ) has to be determined experimentally. To do so, we used dependence of  $V_{th}$  as a function of  $t_{ox}$ , similar to Refs. 8, 23, and 26. Following an analytical model for  $V_{th}$  in GaN MOS-HEMT structures, 9 the slope of  $V_{th}$ - $t_{ox}$  dependence can be expressed as

$$\frac{dV_{th}}{dt_{ox}} = -\frac{Q_{eff}}{\varepsilon_{ox}} = -\frac{1}{\varepsilon_{ox}} (P_S + P_{QW} + qN_{DS} + qN_{ox} + qN_{it}),$$

(1)

where  $P_S$  is the surface polarization charge (that includes GaN-cap surface and GaN-cap/AlGaN interface polarization charge),  $P_{QW}$  is the polarization charge in the AlGaN/GaN quantum well,  $N_{DS}$  is the ionized surface donors density (partially or fully compensating  $P_S$ ),  $N_{ox}$  is the sheet oxide fixed charge, and  $N_{it}$  is the interface trapped charge.  $^9$   $Q_{eff}$  represents an effective charge and it simply quantifies electrostatic impact of the charges residing in MOS-HEMT structure to  $V_{th}$  changes due to  $t_{ox}$  variation. Note that  $P_S$ ,  $N_{DS}$ ,  $N_{ox}$ , and  $N_{it}$  are assumed to be located at or close to oxide/III-N interface. From Eq. (1), it can be then defined that

$$Q_{eff} - P_{OW} = P_S + qN_{DS} + qN_{ox} + qN_{it} = Q_{int}.$$

(2)

This means that the net oxide/III-N charge  $(Q_{int} = qN_{int})$  can be calculated from  $Q_{eff}$  (extracted from the slope of  $V_{th}$ - $t_{ox}$  dependence) and polarization charge in the quantum well.

The dielectric constant of  $Al_2O_3$  films used in the simulations was also determined experimentally from the dependence of MOS-HEMT total capacitance ( $C_{tot}$ ) as a function of  $t_{ox}$ , similar to techniques used in Si MOS structures with high-k dielectrics. As  $C_{tot}$  is given by the serial combination of the barrier and oxide capacitance, the static dielectric constant of the latter ( $\varepsilon_{ox}$ ) can be determined from the slope of  $C_{tot}$ - $t_{ox}$  dependence using the calculated barrier capacitance from known barrier thickness (TEM) and its dielectric constant (8.8). The values of  $\varepsilon_{ox}$  for ALD-grown  $Al_2O_3$  films are summarized in Table I. It ranges from 8.3 to 9.6 in reasonable agreement with the value reported for amorphous  $Al_2O_3$  (9). All III-N material properties were taken from Ref. 16.

Using MOS-HEMT structures with 10, 20, and 30 nm, we determined  $Q_{eff}$  from the  $V_{th}$ - $t_{ox}$  dependences for all three set of samples, and the results are summarized in Table II. Then,  $P_{QW}$  and metal/Al<sub>2</sub>O<sub>3</sub> Schottky barrier height (SBH) were adjusted to account for the experimental  $V_{th}$  and its variation with  $t_{ox}$ . The same  $P_{QW}$  of  $1.27 \times 10^{13}$  cm<sup>-2</sup> for all

structures and SBH at Ni/Al<sub>2</sub>O<sub>3</sub> interface ranging from 3.3 to 3.55 eV were found to fit the experimental data. This procedure is reasonable, keeping in mind the same AlGaN/GaN wafer used for the sample processing. On the other hand, variation in the quality of the oxide surface can result in variation of the metal/oxide SBH (Ref. 29) and it compares well to the value reported in the literature for Ni/Al<sub>2</sub>O<sub>3</sub> interface [3.5 eV (Ref. 30)]. Somewhat smaller  $P_{QW}$  compared to a theoretical value [1.6 × 10<sup>13</sup> cm<sup>-2</sup> (Ref. 24)] can be attributed to slight differences between nominal and actual Al composition and/or presence of defects, such as dislocations, reducing crystal quality, and thus polarization charge density.

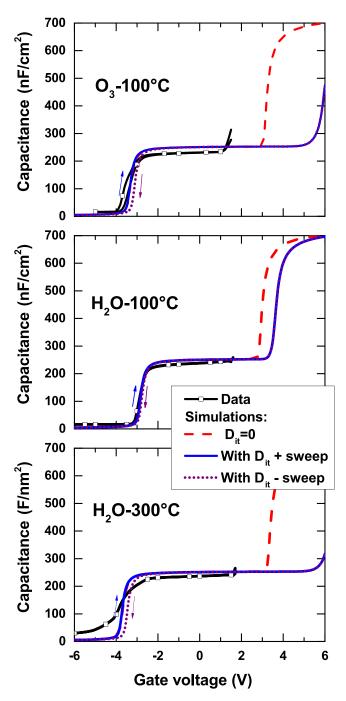

Simulated C-V curves for analyzed MOS-HEMT structures with oxide thickness of 10 nm are shown in Fig. 6. Beside the experimental curve, we plotted also C-V curve considering  $D_{it} = 0$  (dashed line) and  $D_{it}$  distribution similar to that determined experimentally (solid lines). For the calculation, actual  $D_{it}$  distribution was approximated by two exponential functions, as plotted in Fig. 5 by solid lines. To simulate the C-V hysteresis, also shown is the C-V curve calculated after setting the steady-state to  $V_g = 1.5 \,\mathrm{V}$  (dotted line). In this state, all traps are allowed to capture or emit charge carriers according to its position to Fermi level at this voltage. This is similar to the experimental condition at  $V_g = 1.5 \,\mathrm{V}$ , where mostly shallower traps are available and elevated leakage current further promotes charge capture/ emission processes. Note that in previous simulations, thermal equilibrium was set to  $V_g = 0$  V, as the first measurement steps from the equilibrium state.

Let us first discuss the gate voltage at which free electrons spill-over into the AlGaN barrier ( $V_{\text{spill}}$ ) that is characteristic by second increase of the capacitance. We note here that this voltage can be also referred to as flat-band voltage  $V_{FB}$ , as AlGaN bands become flat at this condition. Simulation data suggest that  $V_{\text{spill}}$  can be expected at  $V_g = 3 \text{ V}$  for an "ideal" structures without considering oxide/barrier interface traps. The presence of interface traps further shifts  $V_{\text{spill}}$  to higher positive voltages due to capture of electrons by (acceptorlike) interface traps which in turn stretches-out the C-V curve of the MOS-HEMT structure.  $V_{\rm spill}$  increases by 0.5 V for  $H_2O-100$  °C and by 3 V for  $O_3-100$  °C and  $H_2O-300$  °C, depending on  $D_{it}$  in the energy range of  $E_C$ - $E < E_{F,0}$  ( $E_{F,0}$  is the Fermi level position measured from GaN conduction band at oxide/barrier interface at  $V_g = 0 \text{ V}$ ), i.e., correlating with shallower  $D_{it}$  distribution measured by  $V_{th}$  transients. Therefore, it can be concluded that C-V simulations support our hypothesis of gate leakage related capacitance increase at positive  $V_{\varrho}$ -s, rather than being related to spill-over regime.

Regarding the C-V hysteresis, good agreement between experimental data and simulations can be inferred from Fig. 6 for samples  $O_3$ -100 °C (0.2 and 0.21 V, respectively) and  $H_2O$ -100 °C (<10 and 70 mV, respectively). As evidenced in Ref. 23, electron emission from interface traps centered around  $E_C$ -E = 0.6 eV dominantly determines the value of hysteresis upon sweep conditions used here (0.2 V/s), neglecting the effect of other traps, such as

Fig. 6. (Color online) Experimental and calculated C-V curves for  $Al_2O_3/GaN/AlGaN/GaN$  MOS-HEMT structures analyzed here. Lines with symbols represent experimental data and dashed lines shows calculated curves assuming  $D_{it}=0$ . Full and dotted lines depicts simulations with approximated  $D_{it}$  shown in Fig. 5 accounting for forward (from -6 to 6 V) and backward (from 6 to -6 V) measurements, respectively (see the text for details).

border traps. However, a large discrepancy between experimental ( $<10\,\text{mV}$ ) and simulated C-V (0.25 V) hysteresis can be inferred from Fig. 6(c) for structure  $H_2O\text{-}300\,^{\circ}\text{C}$ . We believe that the absence of any hysteresis can be attributed to coaction of parasitic electron trapping and interface trap emission during C-V sweeps at  $T=300\,^{\circ}\text{C}$ .

Having experimentally determined  $D_{it}(E)$  of samples with reduced  $N_{DS}$ , we can compare our results with  $D_{it}(E)$  measured

on AlGaN/GaN MOS-HEMT structures with fully compensated  $P_S$  in order to follow possible correlation between  $D_{it}$ and  $N_{DS}$ . Also plotted in Fig. 5 is  $D_{it}$  reported in our previous work<sup>23</sup> on Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MOS-HEMTs with Al<sub>2</sub>O<sub>3</sub> grown by MOCVD at 600 °C. As detailed in Ref. 23, this structure shows  $N_{int}$  of  $-3 \times 10^{12}$  cm<sup>-2</sup>, i.e., almost an order of magnitude lower  $N_{int}$  compared to structures analyzed here  $(\sim -1 \times 10^{13} \text{ cm}^{-2})$ . Keeping in mind an order of magnitude difference between  $D_{it}$  in the range of  $E_C$ -E = 3.25-1.75 eVfor O<sub>3</sub>-100 °C sample and those grown using H<sub>2</sub>O while featuring similar  $N_{int}$  (thus  $N_{DS}$ ), variation of  $D_{it}$  for structure with MOCVD grown Al<sub>2</sub>O<sub>3</sub> in this energy range can be disregarded in terms of correlation with  $N_{DS}$ . Comparing the shallower traps ( $E_C$ -E = 0.9-0.5 eV), sample from Ref. 23 shows similar  $D_{it}$  to that determined for O<sub>3</sub>-100 °C sample, except the energy range of  $E_C$ -E = 0.9-0.7 eV, in which MOCVD grown structure shows slightly higher  $D_{it}$  (from 7 to  $4 \times 10^{13} \,\mathrm{eV}^{-1} \,\mathrm{cm}^{-2}$ ) compared to  $O_3$ -100 °C structure (from 5 to 1  $\times 10^{13} \text{ eV}^{-1} \text{ cm}^{-2}$ ). However,  $D_{it}$  differs by an order of magnitude for structures H<sub>2</sub>O-100 °C and O<sub>3</sub>-100 °C in the same energy range, while both samples showed similar  $N_{DS}$ . For more quantitative comparison, the difference of  $N_{it}$  obtained from  $D_{it}$  distributions as  $N_{it} = \int_{E_C - 0.9 \text{ eV}}^{E_C - 0.9 \text{ eV}} D_{it}(E) dE$  gives the  $\Delta N_{it}$  of  $1.4 \times 10^{12} \text{ cm}^{-2}$ , which is much lower value compared to  $\Delta N_{int} = 8 \times 10^{12} \, \text{cm}^{-2}$ . Therefore, it can be concluded that, in the energy range considered, there is no clear correlation between  $D_{it}$  and  $N_{DS}$  for samples analyzed here and that reported previously.<sup>23</sup> Nevertheless, this conclusion does not mean that possible correlation between  $D_{it}$  and  $N_{DS}$  can exist for shallow traps located close to the conduction band edge.

Finally, let us point out the stretch-out of the C-V curve for structure  $H_2O\text{-}300\,^{\circ}\text{C}$  in the region corresponding to 2DEG depletion. As pointed out by several authors,  $^{16,23}$  it is unlikely to attribute the stretch-out in this region to interface traps, as the Fermi level at oxide/barrier interface coincide with very deep traps ( $E\text{-}E_C>1\,\text{eV}$ ) featuring much longer time constant in respect to the measurement time. Instead, traps in the GaN channel or spatial inhomogeneity of the gate oxide can account for this effect. Again, keeping in mind the same wafer used for the device processing and the absence of such effect for  $O_3\text{-}100\,^{\circ}\text{C}$  and  $H_2O\text{-}100\,^{\circ}\text{C}$ , the latter effect is more likely. Local inhomogeneity in  $Al_2O_3$  thickness can induce variation in gate oxide electric field which in turn smears-out the pinch-off voltage of the structure.

#### IV. CONCLUSIONS

$D_{it}(E)$  distribution in Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS-HEMT structures with low- $T_D$  ALD grown oxides and reduced  $N_{DS}$  was analyzed. Although our results indicates lower interface quality for Al<sub>2</sub>O<sub>3</sub> deposited on III-N heterostructure using O<sub>3</sub> oxidation agent compared that with H<sub>2</sub>O, the former gives the lowest gate leakage among the structures analyzed here. From the comparison between  $D_{it}$  determined here and those reported in the literature, there seems to be no correlation between  $D_{it}$  and  $N_{DS}$ . Also, the methodology for  $D_{it}$  determination using capacitance techniques was discussed,

focusing on enhanced forward gate leakage constraints on the application of the AC admittance techniques for  $D_{it}$  determination. Finally, we described a simple experimental methodology for the extraction of the MOS-HEMT gate charge distribution using experimental  $V_{th}$ - $t_{ox}$  dependence and theoretical polarization charge in the quantum well that can be used for C-V simulations.

#### **ACKNOWLEDGMENTS**

This work was supported by V4-Japan joint call on advanced materials (project SAFEMOST), Slovak projects VEGA 2/0138/2014 and project "CENTE I" (1/2, ITMS code 26240120011) funded by Structural Funds of the EU by means of the Agency of the Ministry of Education, Science, Research and Sport of the Slovak republic. L. Tóth and B. Pécz thank the financial support from OTKA Project Nos. 118201 and 108869. The authors would like to thank Roman Stoklas and Tamotsu Hashizume (RCIQE, Hokkaido University, Japan) for providing XPS measurements and analysis.

- <sup>1</sup>O. Hilt, E. Bahat-Treidel, A. Knauer, F. Brunner, R. Zhytnytska, and J. Würfl, MRS Bull. **40**, 418 (2015).

- <sup>2</sup>T. Kachi, IEICE Electron. Express 10, 20132005 (2013).

- <sup>3</sup>M. Kuzuhara and M. Tokuda, IEEE Trans. Electron Devices **62**, 405 (2015).

- <sup>4</sup>M. A. Briere, Power Electronics Europe 30 (2013), available at http://www.power-mag.com/pdf/issuearchive/62.pdf.

- <sup>5</sup>Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueada, IEEE Trans. Electron Devices **54**, 3393

- <sup>6</sup>O. Hilt, F. Brunner, E.-M. Cho, A. Knauer, E. Bahat-Treidel, and J. Wurfl, Proceedings 23rd IEEE International Symposium on Power Semiconductor Device Integrated Circuit (ISPSD), May (2011), pp. 239, 242.

- <sup>7</sup>M. Esposto, S. Krishnamoorthy, D. N. Nathan, S. Bajaj, T.-H. Hung, and S. Rajan, Appl. Phys. Lett. **99**, 133503 (2011).

- <sup>8</sup>S. Ganguly, J. Verma, G. Li, T. Zimmermann, H. Xing, and D. Jena, Appl. Phys. Lett. **99**, 193504 (2011).

- <sup>9</sup>M. Ťapajna and J. Kuzmík, Appl. Phys. Lett. **100**, 113509 (2012).

- <sup>10</sup>M. Ťapajna and J. Kuzmík, Jpn. J. Appl. Phys., Part 1 **52**, 08JN08 (2013).

- <sup>11</sup>M. Blaho *et al.*, Phys. Status Solidi A **212**, 1086 (2015).

- <sup>12</sup>R. E. Sah, C. Tegenkamp, M. Baeumler, F. Bernhardt, R. Driad, M. Mikulla, and O. Ambacher, J. Vac. Sci. Technol., B 31, 04D111 (2013).

- <sup>13</sup>M. Ťapajna, A. Paskaleva, E. Atanassova, E. Dobročka, K. Hušeková, and K. Fröhlich, Semicond. Sci. Technol. 25, 075007 (2010).

- <sup>14</sup>X. Liu et al., J. Appl. Phys. **114**, 164507 (2013).

- <sup>15</sup>M. Ťapajna, M. Jurkovič, L. Válik, Š. Haščík, D. Gregušová, F. Brunner, E.-M. Cho, and J. Kuzmík, Appl. Phys. Lett. **102**, 243509 (2013).

- <sup>16</sup>M. Miczek, C. Mizue, T. Hashizume, and B. Adamowicz, J. Appl. Phys. 103, 104510 (2008).

- <sup>17</sup>M. L. Huang, Y. C. Chang, C. H. Chang, T. D. Lin, J. Kwo, T. B. Wu, and M. Hong, Appl. Phys. Lett. **89**, 012903 (2006).

- <sup>18</sup>Y. Hori, C. Mizue, and T. Hashizume, Jpn. J. Appl. Phys., Part 1 49, 080201 (2010).

- <sup>19</sup>C. Mizue, J. Hori, M. Miczek, and T. Hashizume, Jpn. J. Appl. Phys., Part 1 50, 021001 (2011).

- <sup>20</sup>H.-A. Shih, M. Kudo, and T. Suzuki, J. Appl. Phys. **116**, 184507 (2014).

- <sup>21</sup>Y. Hori, Z. Yatabe, and T. Hashizume, J. Appl. Phys. **114**, 244503 (2013).

- <sup>22</sup>M. Capriotti, P. Lagger, C. Fleury, M. Oposich, O. Bethge, C. Ostermaier, G. Strasser, and D. Pogany, J. Appl. Phys. 117, 024506 (2015).

- <sup>23</sup>M. Ťapajna, M. Jurkovič, L. Válik, Š. Haščík, D. Gregušová, F. Brunner, E.-M. Cho, T. Hashizume, and J. Kuzmík, J. Appl. Phys. 116, 104501 (2014).

- <sup>24</sup>O. Ambacher *et al.*, J. Appl. Phys. **85**, 3222 (1999).

- <sup>25</sup>M. Ťapajna, K. Čičo, J. Kuzmík, D. Pogany, G. Pozzovivo, G. Strasser, J.-F. Carlin, N. Grandjean, and K. Fröhlich, Semicond. Sci. Technol. 24, 035008 (2009).

- <sup>26</sup>H. Hahn, B. Pécz, A. Kovács, M. Heuken, H. Kalisch, and A. Vescan, J. Appl. Phys. 117, 214503 (2015).

- <sup>27</sup>M. Ťapajna, P. Písečný, R. Lupták, K. Hušeková, K. Fröhlich, L. Harmatha, J. C. Hooker, F. Roozeboom, and J. Jergel, Mater. Sci. Semicond. Proc. 7, 271 (2004).

- <sup>28</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. 89, 5243 (2001).

- <sup>29</sup>G. Pourtois, A. Lauwers, J. Kittl, L. Pantisano, B. Sorée, S. De Gendt, W. Magnus, M. Heyns, and K. Maex, Microelectron. Eng. 80, 272 (2005).

- <sup>30</sup>J. Robertson and B. Falabretti, J. Appl. Phys. **100**, 014111 (2006).