## Louisiana State University LSU Scholarly Repository

LSU Historical Dissertations and Theses

**Graduate School**

1996

# Low Temperature Silicon Oxide and Fluorinated Silicon Oxide Films Prepared by Plasma-Enhanced Chemical Vapor Deposition Using Disilane as Silicon Precursor.

Juho Song Louisiana State University and Agricultural & Mechanical College

Follow this and additional works at: https://repository.lsu.edu/gradschool\_disstheses

#### **Recommended Citation**

Song, Juho, "Low Temperature Silicon Oxide and Fluorinated Silicon Oxide Films Prepared by Plasma-Enhanced Chemical Vapor Deposition Using Disilane as Silicon Precursor." (1996). *LSU Historical Dissertations and Theses.* 6281.

https://repository.lsu.edu/gradschool\_disstheses/6281

This Dissertation is brought to you for free and open access by the Graduate School at LSU Scholarly Repository. It has been accepted for inclusion in LSU Historical Dissertations and Theses by an authorized administrator of LSU Scholarly Repository. For more information, please contact gradetd@lsu.edu.

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

### LOW TEMPERATURE SILICON OXIDE AND FLUORINATED SILICON OXIDE FILMS PREPARED BY PLASMA ENHANCED CHEMICAL VAPOR DEPOSITION USING DISILANE AS SILICON PRECURSOR

A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Department of Electrical and Computer Engineering

by Juho Song B.S., Kyungpook National University. Korea, 1985 M.S., Louisiana State University, 1994 August 1996

#### UMI Number: 9706364

UMI Microform 9706364 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

### UMI 300 North Zeeb Road Ann Arbor, MI 48103

. .

\_

To my late aunt, Taechul Song, who taught me my first letters in life.

### ACKNOWLEDGMENTS

I would like to express my sincere appreciation and thanks to all persons who directly or indirectly contributed to completion of my study here at Louisiana State University, home of fighting tigers.

I would like to express my sincere gratitude and respect to my major professor, Dr. Gil S. Lee, who gave me constant encouragement and support for the completion of this study. His help and guidance, personally and academically, will not be forgotten.

I would also like to thank Dr. Pratul K. Ajmera for his incredible support and technical guidance. It would be impossible for me to be at this point without him. His help during the entire program of this study is gratefully acknowledged.

My special thanks are due to Dr. Martin Feldman, Dr. Alexander Skavantzos, and Dr. Roger L. Stockbauer for serving as members of my academic advisory committee. I also would like to thank my minor professor, Dr. E. I. Meletis, for his criticism and advice.

More thanks also go to Dr. Alan Marshak who gave me a chance to hold teaching assistantship and allowed me to use all facilities at the Department of Electrical and Computer Engineering.

Special thanks to Golden Hwaung for his technical assistance and endless encouragement during the entire time of my work at Solid State Laboratory. Thanks to all faculty, staff and fellow students at the Department of Electrical and Computer Engineering who helped me one way or other.

The equipment grant from the Louisiana Educational Quality Support Fund and the grant from the Office of Research and Economic Development, Louisiana State University are sincerely acknowledged.

iii

In addition, I would like to express my gratitude to Dr. L. Dayle Yeager at East Texas State University at Commerce, Texas. His warm advice and constant belief in my abilities over the last four years made me strive to do my best in everything I undertook.

! appreciate the emotional support from students in Korean Student Association at Louisiana State University and from Hyungsool and Inshil Kim. Also thanks to Ang-Goo Lee and Dr. Jung-Kyu Lee for their advice and suggestion from Korea.

I would especially like to thank my parents, Jaekyung Song and Pilsaeng Kim, my parents-in-law, Wontaek Lim and Dalseon Kang, and all of my brothers and sisters living in Korea, 7500 miles away from Baton Rouge, for their unconditional support. No words can properly state their help given to me and my family here. They deserve the degree more than I do. I am proud of them as they are proud of me. I really appreciate what they did, what they do, and what they mean to me and my family.

I also would like to thank my late aunt, Taechul Song, for her endless love. I know she is far and far away from me. This professional degree is hers, not mine.

Finally, I would like to express my deepest appreciation to my wife, Myungae Lim for helping me and standing by me all the time, and also to my kids, Youngmin and Michelle (Naeun). Their infinite patience, endurance, and encouragement helped my tiny dream come true. I am truly grateful for their love.

iv

## **TABLE OF CONTENTS**

|         |            |                                                | page   |

|---------|------------|------------------------------------------------|--------|

| ACKNO   | WLEDGI     | MENTS                                          | iii    |

| LIST OF | TABLES     | S                                              | vii    |

| LIST OF | FIGURE     | S                                              | viii   |

| ABSTR   | ACT        |                                                | xiii   |

| СНАРТЕ  | ER         |                                                |        |

| 1       | INTRO      |                                                | 1      |

| •       | 1.1        | Overview                                       | 1      |

|         | 1.2        | General Principles of PECVD                    |        |

|         | 1.2        | 1.2.1 Nature of Plasma                         | 3      |

|         |            | 1.2.2 Deposition Mechanism                     | 3<br>5 |

|         |            | 1.2.2.1 Radical Mechanism                      | 5      |

|         |            | 1.2.2.2 Ionic Mechanism                        | 7      |

|         | 1.3        | Research Objectives                            | 8      |

| 2       | SILICO     | N OXIDE FILM DEPOSITION                        | 12     |

| _       | 2.1        | Introduction                                   | 12     |

|         | 2.2        | Experiment                                     | 12     |

|         | 2.3        | Results and Discussion                         | 14     |

|         | 2.4        | Conclusion                                     | 24     |

| 3       | -          | T OF DEPOSITION TEMPERATURE                    |        |

|         |            | M QUALITY                                      | 27     |

|         | 3.1        | Introduction                                   | 27     |

|         | 3.2        | Experiment                                     | 27     |

|         | 3.3        | Results and Discussion                         | 29     |

|         | 3.4        | Conclusion                                     | 44     |

| 4       |            | TURAL PROPERTIES OF SILICON OXIDE FILMS        | 47     |

|         | 4.1        | Introduction                                   | 47     |

|         | 4.2        | Experiment                                     | 47     |

|         | 4.3        | Results and Discussion                         | 48     |

|         | 4.4        | Conclusion                                     | 56     |

| 5       |            | T OF NATIVE OXIDE REMOVAL ON FILM QUALITY      | 58     |

|         | 5.1        | Introduction                                   | 58     |

|         | 5.2        | Experiment                                     | 58     |

|         | 5.3        | Results and Discussion                         | 59     |

|         |            | 5.3.1 Effect of Native Oxide on C-V Curves     | 59     |

|         | <b>F</b> 4 | 5.3.2 Improvement of Film Quality by Annealing | 64     |

|         | 5.4        | Conclusion                                     | 74     |

-----

----

\_ - - -

-----

| 6      | FLUORINATED SILICON OXIDE FILM DEPOSITION.6.1Introduction                                                     | 78<br>78<br>79<br>80<br>88 |

|--------|---------------------------------------------------------------------------------------------------------------|----------------------------|

| 7      | HIGH QUALITY FLUORINATED SILICON OXIDE FILM7.1Introduction7.2Experiment7.3Results and Discussion7.4Conclusion | 89<br>89<br>89<br>90<br>95 |

| 8      | SUMMARY                                                                                                       | 98                         |

| REFERE | INCES                                                                                                         | 100                        |

| APPEN  | DICES                                                                                                         |                            |

| Α      | SERIES RESISTANCE CORRECTION                                                                                  | 106                        |

| В      | C-V MEASUREMENT PROGRAM                                                                                       | 107                        |

| С      | LETTERS OF PERMISSION                                                                                         | 113                        |

| VITA   |                                                                                                               | 118                        |

---- -----

-

\_\_\_\_

. . . .

## LIST OF TABLES

| 1.1. | Metastable energy levels and ionization energies of major inert gases used for thin film deposition in CVD.                           | 6  |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1. | Typical etch rate in the P-etch solution for the silicon oxide films prepared by various methods.                                     | 15 |

| 3.1. | Average non-destructive dielectric breakdown field strength for the silicon oxide films deposited at different temperatures.          | 45 |

| 4.1. | Summary of structural properties of the silicon oxide films                                                                           | 55 |

| 5.1. | Summary of high frequency C-V measurements for the silicon oxide films cleaned with two different pre-deposition cleaning procedures. | 75 |

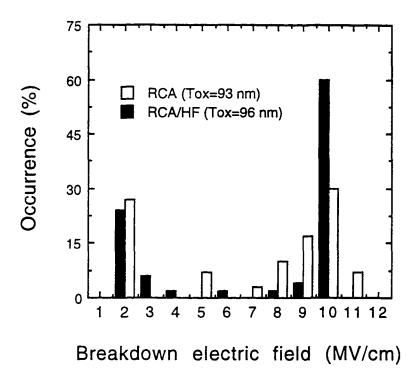

| 5.2. | Intrinsic dielectric breakdown distribution for devices cleaned with two different pre-deposition cleaning procedures.                | 76 |

| 7.1. | Comparison of intrinsic dielectric breakdown distributions for the silicon oxide and the fluorinated silicon oxide films.             | 97 |

\_.

-----

## LIST OF FIGURES

-

....

\_\_\_\_\_

### page

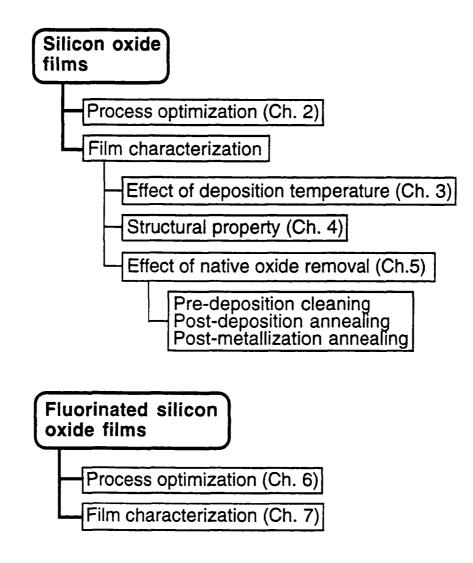

| 1.1. | Overall research outline. The research is divided into two major parts, silicon oxide and fluorinated silicon oxide film deposition                                                                                                                           | 9  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

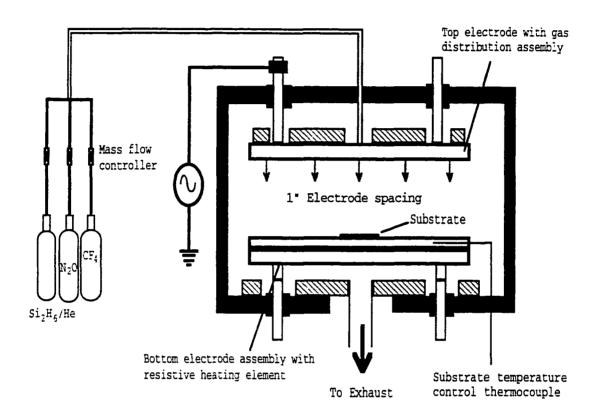

| 1.2. | Schematic diagram of a Plasma Therm VII-70 parallel plate plasma reactor equipped with 13.56 MHz rf source and 1 inch electrode spacing.                                                                                                                      | 10 |

| 2.1. | The detailed deposition recipe consisting of six different steps. The process chamber is pumped to a base pressure before starting step 1. The films are deposited during step 4.                                                                             | 13 |

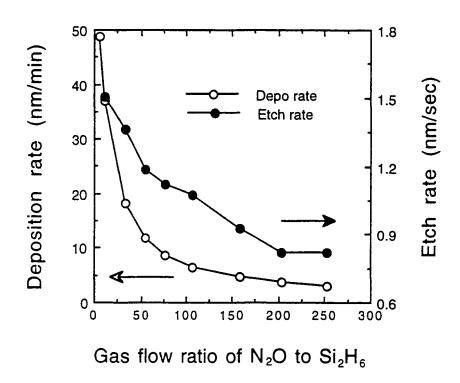

| 2.2. | Deposition rate and etch rate in the P-etch solution as a function of $N_2 O/Si_2 H_6$ gas flow ratio.                                                                                                                                                        | 16 |

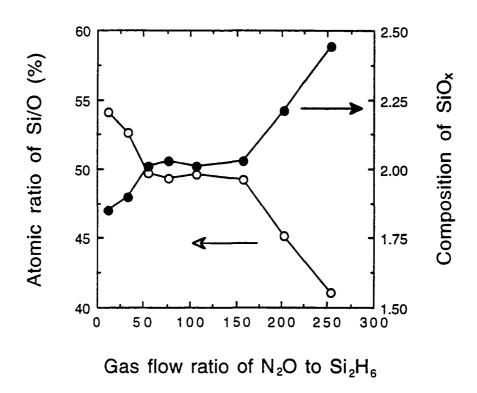

| 2.3. | Atomic ratio of silicon to oxygen and composition of $SiO_x$ obtained from Auger electron spectroscopy measurements as a function of $N_2O/Si_2H_6$ gas flow ratio.                                                                                           | 17 |

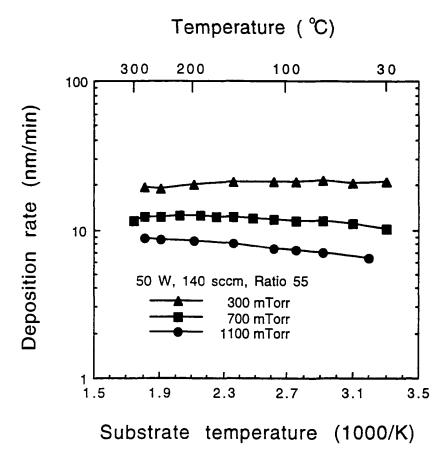

| 2.4. | Deposition rate as a function of temperature for the silicon oxide films deposited at 300, 700, 1100 mTorr.                                                                                                                                                   | 19 |

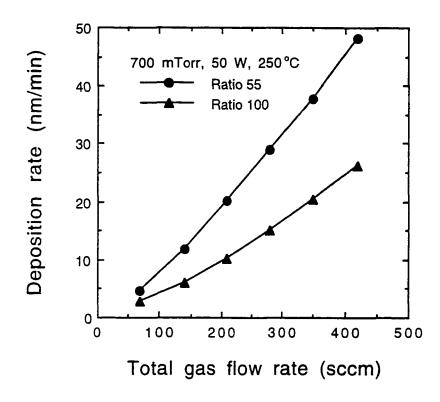

| 2.5. | Deposition rate as a function of total gas flow rate for the silicon oxide films deposited with $N_2O/Si_2H_6$ gas flow ratio of 55 and 110                                                                                                                   | 21 |

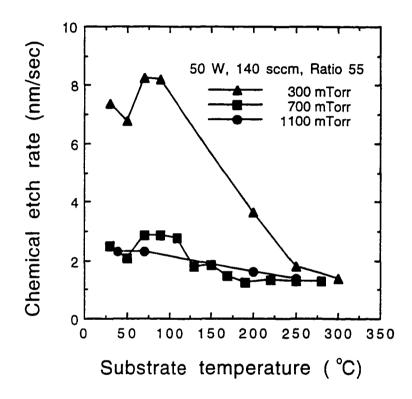

| 2.6. | Chemical etch rate in the P-etch solution vs. substrate deposition temperature.                                                                                                                                                                               | 22 |

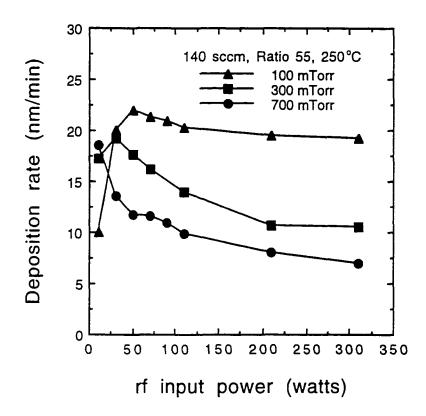

| 2.7. | Deposition rate as a function of rf input power for the silicon oxide films deposited at 100, 300, and 700 mTorr.                                                                                                                                             | 23 |

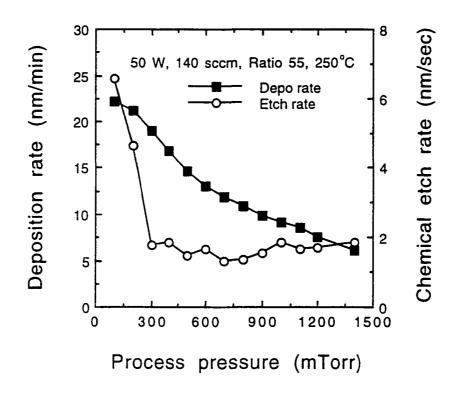

| 2.8. | Deposition rate and chemical etch rate vs. deposition pressure                                                                                                                                                                                                | 26 |

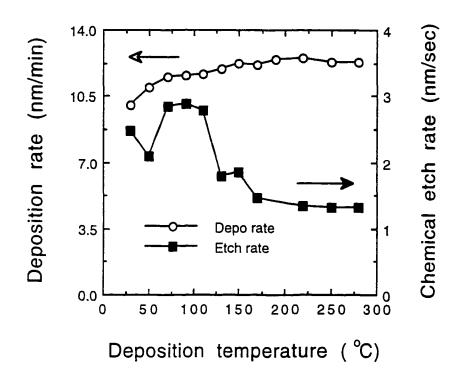

| 3.1. | Deposition rate and etch rate of the silicon oxide films as a function of deposition temperature. The P-etch solution consists of 15 parts by volume of 48 $\%$ HF, 10 parts by volume 70 $\%$ HNO <sub>3</sub> , and 300 parts by volume of deionized water. | 30 |

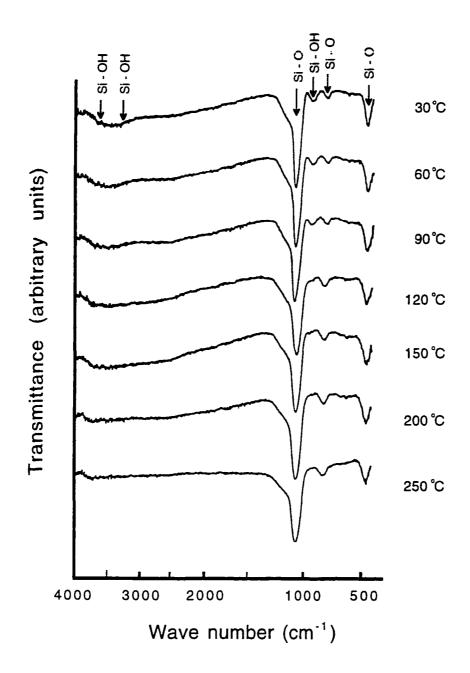

| 3.2. | Infrared transmission spectra of the as-deposited silicon oxide films<br>as a function of deposition temperature in the range of 30-250°C.<br>The arrows indicate the location of absorption peaks in the<br>vibrational spectra.                             | 32 |

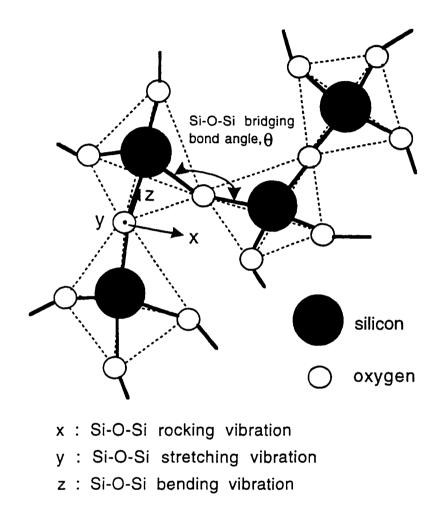

| 3.3. | Three-dimensional representation of two neighboring $SiO_4$ cell, bridged by an oxygen atom. Directions for three characteristic vibration motions are also marked.                                                                                           | 33 |

viii

----

| 3.4.  | Si-O-Si stretching absorption peak and FWHM of the as-deposited silicon oxide films shown in Fig. 3.2 as a function of film deposition temperature.                                                                                                                                                                                   | 34 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5.  | Infrared transmission spectra of the annealed silicon oxide films as a function of film deposition temperature. The annealing is carried out at $400^{\circ}$ C in N <sub>2</sub> ambient for 30 min.                                                                                                                                 | 36 |

| 3.6.  | Dielectric constant of the as-deposited and the annealed silicon oxide films as a function of film deposition temperature. Anneal is carried out at 400°C in N <sub>2</sub> ambient for 30 min. The thickness of the silicon oxide film is about 100 nm and the gate area is $2.7 \times 10^{-3}$ cm <sup>2</sup> .                   | 37 |

| 3.7.  | J-E characteristics of the silicon oxide films for various deposition temperatures in the range of $30-150^{\circ}$ C. The voltage ramp rate is fixed at 1 V/sec. The bias polarity corresponds to electron injection from the gate. The oxide thickness is 100 nm and the gate area is $8.3 \times 10^{-3}$ cm <sup>2</sup> .        | 39 |

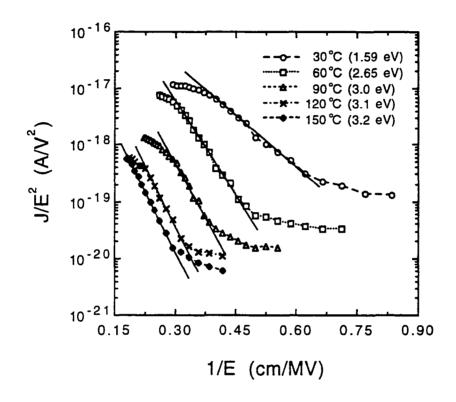

| 3.8.  | Fowler-Nordheim current plots of the silicon oxide films shown in Fig. 3.7. The linear dependence of $J/E^2$ against 1/E gives the barrier height indicated in the parentheses .                                                                                                                                                      | 41 |

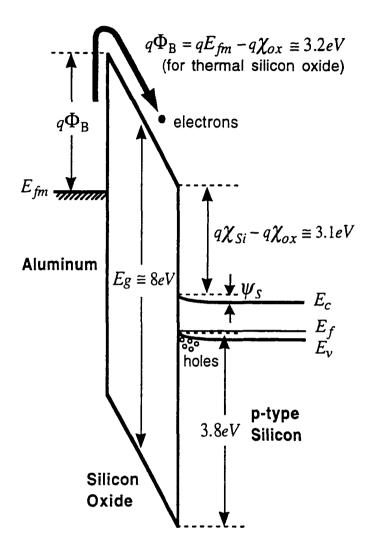

| 3.9.  | Energy-band diagram of a MOS system with p-type silicon biased into accumulation. The barrier height is marked.                                                                                                                                                                                                                       | 42 |

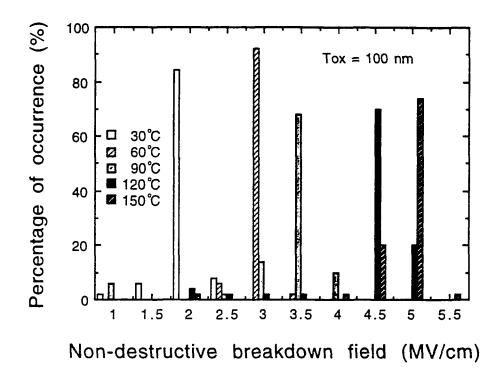

| 3.10. | Distribution of the non-destructive dielectric breakdown occurrence<br>as a function of electric field for the silicon oxide films deposited at<br>different temperatures. Fifty devices are measured for each case.<br>The voltage ramp rate is fixed at 1 V/sec and the gate polarity is<br>negative with respect to the substrate. | 43 |

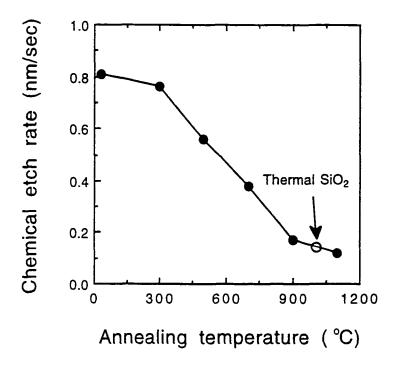

| 4.1.  | Chemical etch rate in the P-etch solution of the silicon oxide films<br>as a function of post-deposition annealing temperature.<br>Experimental data at 25°C are for the as-deposited film. The circle<br>corresponds to etch rate of the thermal silicon oxide films grown at<br>1000°C, 0.15 nm/sec.                                | 49 |

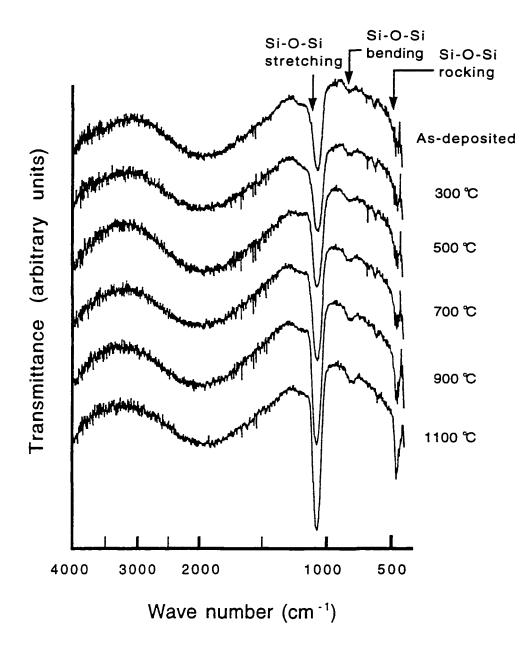

| 4.2.  | Infrared transmission spectra of the silicon oxide films annealed at different temperatures. Three characteristic peaks of Si-O-Si vibrational motion are marked.                                                                                                                                                                     | 51 |

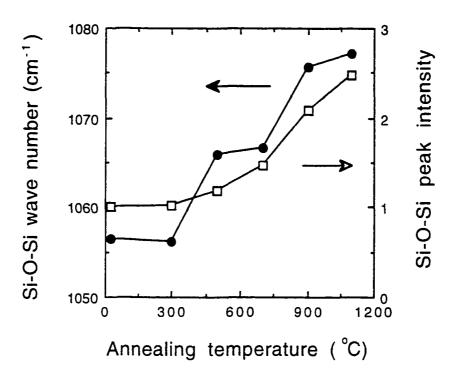

| 4.3.  | Si-O-Si asymmetric stretching peak wave number and its relative<br>peak intensity with respect to the as-deposited silicon oxide films as<br>a function of post-deposition annealing temperature.                                                                                                                                     | 52 |

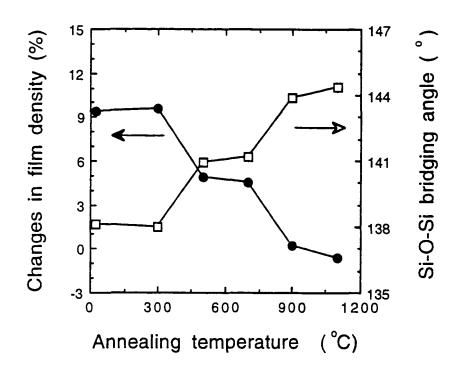

| 4.4.  | Changes in the silicon oxide film density, $\Delta \rho / \rho$ , and Si-O-Si bridging bond angle, $\theta$ as a function of post-deposition annealing                                                                                                                                                                                |    |

|      | temperature. It is assumed that $\rho$ and $\theta$ of the undensified amorphous silicon oxide films are 2.2 g/cm <sup>3</sup> and 144°, respectively.                                                                                                                                                                                                                                                                                                                     | 54 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

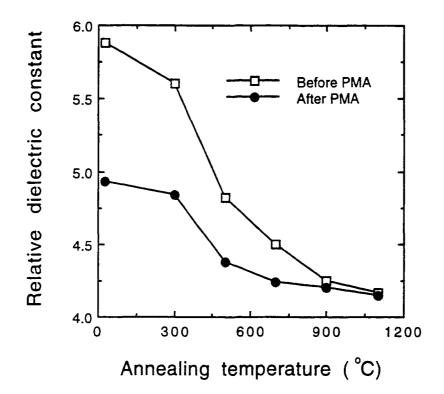

| 4.5. | Dependence of dielectric constant of the silicon oxide films annealed at different temperatures on post-metallization annealing. The post-metallization annealing was carried out in 5 % $H_2$ in $N_2$ ambient at 400°C for 30 min.                                                                                                                                                                                                                                       | 57 |

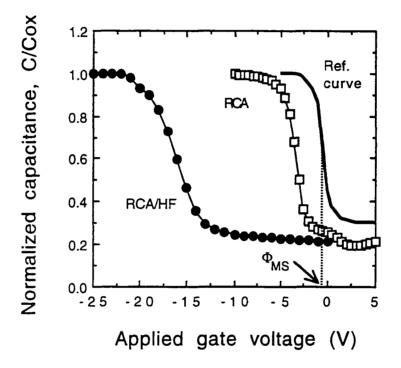

| 5.1. | High frequency normalized capacitance as a function of applied gate voltage for two different pre-deposition cleaning procedures which are RCA and RCA followed by a dip in a dilute HF. The reference curve marked is drawn for $\Phi_{MS}$ = -0.83 V and with no oxide or interface charges. Neither post-deposition nor post-metallization annealing was performed on these samples.                                                                                    | 60 |

| 5.2. | Normalized high frequency capacitance for devices on the silicon oxide films cleaned with RCA followed by a dip in dilute HF as a function of applied gate voltage for post-deposition annealing at different temperatures in $N_2$ ambient for 30 min. For comparison purposes, values for a thermal silicon oxide film grown at 1000°C are also shown.                                                                                                                   | 65 |

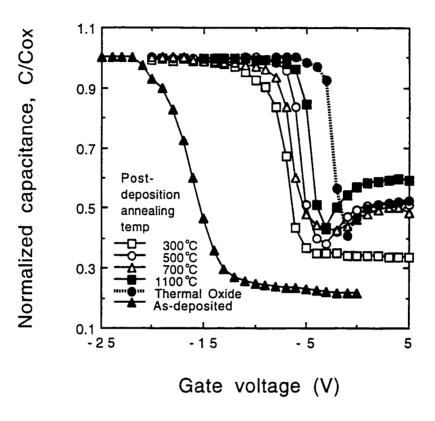

| 5.3. | Normalized high frequency capacitance for devices on the silicon oxide films shown in Fig. 5.2 as a function of applied gate voltage after subjecting the samples to post-metallization annealing in 5 % $H_2$ in $N_2$ ambient at 400°C for 30 min. The values for the asdeposited films cleaned with two different pre-deposition procedures, RCA and RCA/HF, are also shown.                                                                                            | 66 |

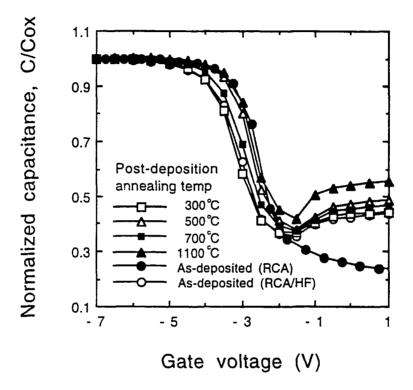

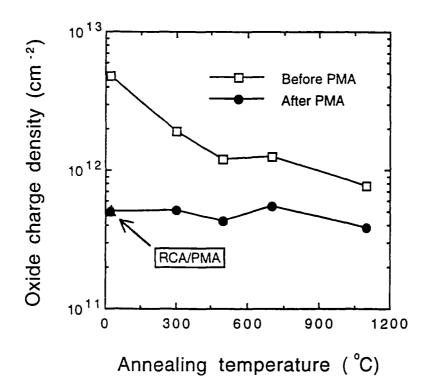

| 5.4. | Effective oxide charge density in the silicon oxide films cleaned with RCA followed by a dip in a dilute HF before and after poet-<br>metallization annealing as a function of post-deposition annealing<br>temperatures. Experimental data indicated at 25°C are for the as-<br>deposited films. The observed value after the post-metallization<br>annealing for the as-deposited films on RCA cleaned substrates is<br>also shown ( $\Delta$ ) for comparison purposes. | 68 |

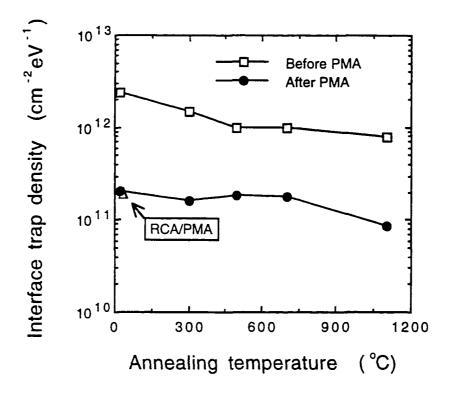

| 5.5. | Interface trap density under the flat band condition before and after poet-metallization annealing as a function of post-deposition annealing temperatures. The substrates were cleaned with the RCA/HF procedure. Experimental data at 25°C are for the as-deposited films. The observed value after the post-metallization annealing for the as-deposited films on RCA cleaned substrates is also shown ( $\Delta$ ) for comparison purposes.                            | 70 |

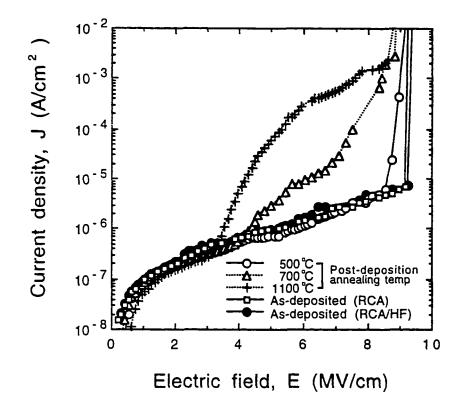

| 5.6. | J-E characteristics of the silicon oxide films for various post-<br>deposition annealing temperatures followed by post-metallization                                                                                                                                                                                                                                                                                                                                       |    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

and the second second

\_

|      | annealing. The voltage ramp rate is fixed at 0.5 V/sec. The bias polarity corresponds to electron injection from the gate.                                                                                                                                                                                                                                                       | 71 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.7. | Distribution of occurrence of catastrophic dielectric breakdown as a function of electric field for the as-deposited silicon oxide films cleaned with two different pre-deposition cleaning procedures. The measurements were performed after poet-metallization annealing at $400^{\circ}$ C for 30 min in a forming gas ambient. T <sub>ox</sub> is a silicon oxide thickness. | 73 |

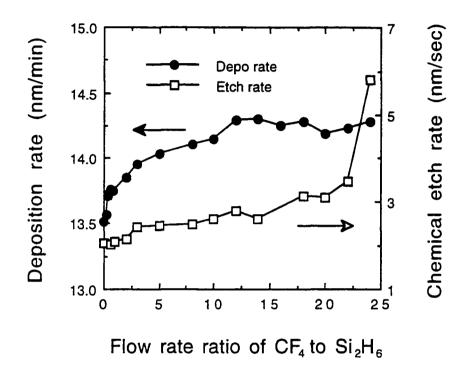

| 6.1. | Deposition rate and etch rate in the P-etch solution of the films as a function of flow rate ratio of $CF_4$ to $Si_2H_6$ during film deposition. Films were deposited at 120°C by flowing 40 sccm of 4.8 % $Si_2H_6$ in He (2 sccm of $Si_2H_6$ ), 100 sccm of $N_2O$ , and 0-48 sccm of $CF_4$ . The process pressure and rf power were 700 mTorr and 50 W, respectively.      | 81 |

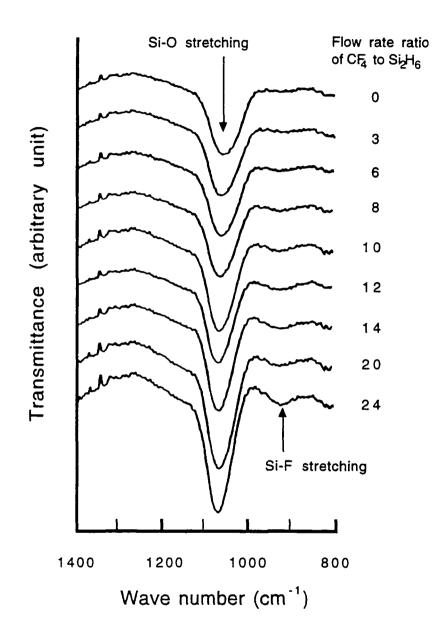

| 6.2. | Infrared transmission spectra of the films deposited with different flow rate ratios of $CF_4$ to $Si_2H_6$ . The process conditions were the same as in Fig. 6.1. The characteristic peaks of Si-O and Si-F stretching motion are marked.                                                                                                                                       | 82 |

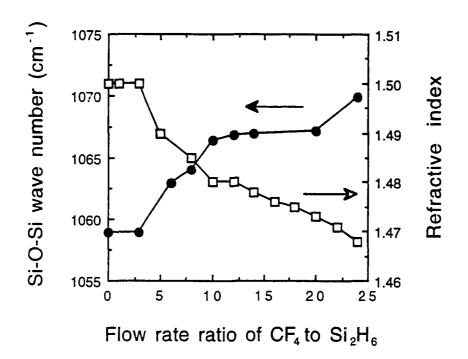

| 6.3. | Si-O-Si asymmetric stretching peak wave number and refractive index of the film as a function of flow rate ratio of $CF_4$ to $Si_2H_6$ during film deposition.                                                                                                                                                                                                                  | 83 |

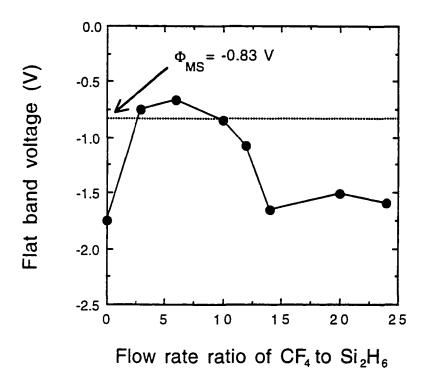

| 6.4. | Dependence of flat band voltage of the films as a function of flow rate ratio of $CF_4$ to $Si_2H_6$ during film deposition. The broken line is drawn for $\Phi_{MS}$ = -0.83 V. The post-metallization annealing was carried out in 5 % H <sub>2</sub> in N <sub>2</sub> ambient at 400°C for 30 min prior to measurements.                                                     | 86 |

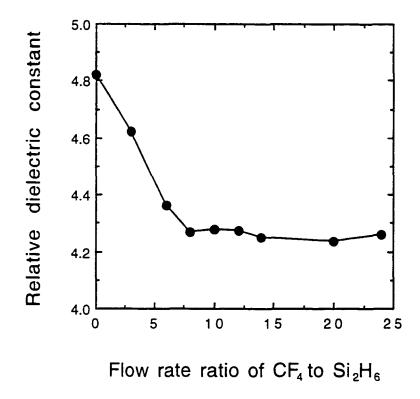

| 6.5. | Dependence of dielectric constant of the films as a function of flow rate ratio of $CF_4$ to $Si_2H_6$ during film deposition. The post-metallization annealing was carried out in 5 % H <sub>2</sub> in N <sub>2</sub> ambient at 400°C for 30 min prior to measurements.                                                                                                       | 87 |

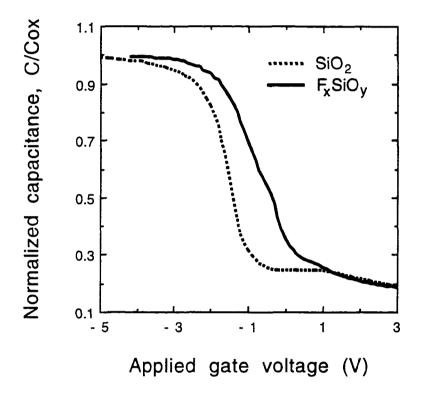

| 7.1. | High-frequency normalized capacitance as a function of applied gate voltage for devices on the silicon oxide and the fluorinated silicon oxide films. The post-metallization annealing was carried out in 5 % $H_2$ in $N_2$ ambient at 400°C for 30 min prior to measurements.                                                                                                  | 91 |

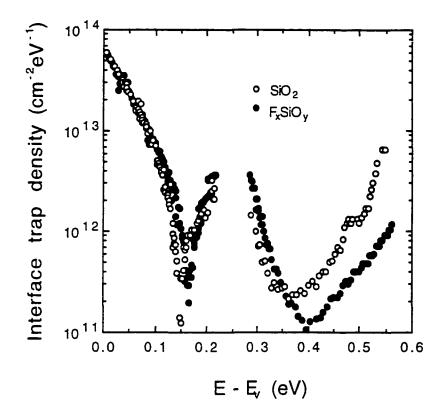

| 7.2. | Interface trap density vs. the energy level location from the majority carrier band edge ( $E_v$ ) for the silicon oxide and the fluorinated silicon oxide films.                                                                                                                                                                                                                | 93 |

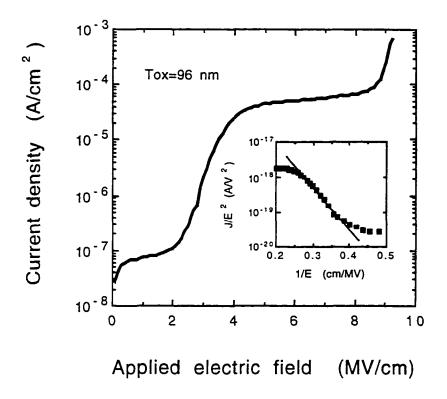

| 7.3. | Typical J-E characteristic of the fluorinated silicon oxide films with a thickness of 96 nm. The voltage ramp rate is fixed at 0.5 V/sec. The                                                                                                                                                                                                                                    |    |

|      | bias polarity corresponds to electron injection from the gate. The inserted figure is a plot of $ln(J/E^2)$ vs. 1/E described by the simple Fowler-Nordheim expression.                                                                                 | 94 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

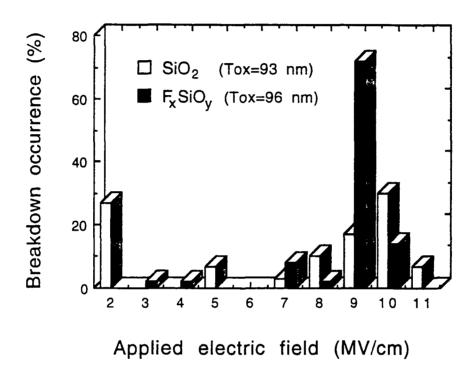

| 7.4. | Distribution of breakdown occurrences as a function of electric field strength for the silicon oxide and the fluorinated silicon oxide films. Fifty devices were used in the measurement done at room temperature. $T_{ox}$ stands for oxide thickness. | 96 |

\_ . . . . . .

- ----

- -- -

\_\_\_\_\_

### ABSTRACT

The deposition and characterization of the silicon oxide and fluorinated silicon oxide films, as interlevel dielectrics in microelectronics devices, prepared by plasma enhanced chemical vapor deposition at low substrate temperature using  $Si_2H_6$  as silicon precursor are studied.

The film deposition is limited by the mass transport regime, resulting in nearly temperature independent deposition rate. The characteristics for the silicon oxide films deposited at 120°C show that the film etch rate is comparable to that obtained by TEOS-based PECVD at 400°C and the leakage current is comparable to that of the films deposited at 350°C with conventional SiH<sub>4</sub> precursor. It also shows that the as-deposited silicon oxide films, resulting in the Si-O-Si bridging bond angle of 138°. The post-metallization annealing in forming gas ambient at 400°C rather than post-deposition annealing at high temperatures in N<sub>2</sub> is the most effective way to reduce both the oxide charge and interface trap densities, especially for devices fabricated on the native oxide-free surface.

For the fluorinated silicon oxide film deposition, the optimum gas flow ratio of  $CF_4$ , as fluorine precursor, to  $Si_2H_6$  is observed to be in the range of 8-10. The films deposited at a flow ratio of 10 give the film a dielectric constant of 4.25 which is 12 % lower than 4.88 obtained for the fluorine-free silicon oxide films. The addition of fluorine into Si-O network helps not only in reducing the effective oxide charges to as low as 1/6 of the value for the fluorine-free silicon oxide films, but also improves the breakdown property by significantly reducing early failures, resulting in the average dielectric breakdown field strength of 8.91 MV/cm.

These films have a strong potential for the use as interlayer dielectric material making available a low temperature and high quality film deposition process for submicron device fabrication in the microelectronics industry.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

xiv

# CHAPTER 1 INTRODUCTION

#### 1.1 Overview

The present trend in the deposition of dielectric thin films for microelectronic integrated circuit applications is towards lower deposition temperatures. Low temperature deposition of dielectrics is advantageous for the reduction of diffusion related or temperature sensitive phenomenon such as hillock formation in metals, dopant redistribution, and lattice damage and stoichiometry degradation in compound semiconductors [1].

Numerous studies [2]-[6] have reported deposition of silicon oxide films as primary dielectric films for applications such as passivation layers, intermetal insulators, and lithographic masks. Recently, attention has also been given to the silicon oxide films as primary insulators in thin film transistors based on amorphous or polycrystalline silicon [7], enabling one to fabricate large arrays of thin film transistors for flat panel displays in conjunction with liquid crystal display technology to replace conventional cathode-ray tubes.

One of the widely preferred low temperature techniques for the deposition of the silicon oxide films is plasma enhanced chemical vapor deposition (PECVD). In the low pressure glow discharge plasma, high electron energy takes the place of thermal energy in activating the desired chemical reactions by dissociating the chemical vapor molecules to produce highly reactive free radicals. Properties of the PECVD silicon oxide films have been extensively studied in recent years, with regard to their applications in integrated circuits.

The PECVD silicon oxide films are typically obtained in the temperature range of 200-350°C by the chemical reaction of a silicon containing compound

such as silane (SiH<sub>4</sub>) or tetra-ethyl-ortho-silicate (TEOS, Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>) with a gaseous oxidant such as O<sub>2</sub>, N<sub>2</sub>O, and CO<sub>2</sub> [7]-[14]. In general, O<sub>2</sub> is not recommended in conventional PECVD due to its high reactivity with SiH<sub>4</sub>, which may result in a general reduction in film quality, including nonreproducible deposition, increased particulates and pinhole densities, and nonuniform deposition [15]. Typically N<sub>2</sub>O has been the oxidant of choice due to the low bonding energy (2.08 eV) of N-O in the molecule [16].

Numerous works have been reported on the physical, mechanical, and chemical properties of the silicon oxide films deposited by the use of SiH<sub>4</sub> as silicon precursor. The SiH<sub>4</sub>-based PECVD silicon oxide process, however, possesses deposition temperature limitation, especially below 200°C. PECVD silicon oxide films deposited at temperature lower than 200°C show poor film integrity caused by undesirable chemical bonding groups. Though the use of helium as a dilution gas during the film deposition minimizes the formation of these bonding groups, the dilution process itself causes a significant decrease in the film deposition rate [10]. To compensate for the decrease in the deposition rate for the latter process, one requires either the use of much higher deposition temperatures which would be against the desirable trend or an increase in the deposition time which causes concern about the unwanted plasma radiation induced device degradation.

Disilane (Si<sub>2</sub>H<sub>6</sub>) is known to give better thermal processing budget to prepare silicon containing films due to its high reactivity resulting from the fact that Si<sub>2</sub>H<sub>6</sub> has quite a long surface residence time and a high sticking coefficient compared to those for SiH<sub>4</sub> [17], [18]. The pyrolysis of Si<sub>2</sub>H<sub>6</sub> was studied first by Emeleus and Reid [19] in 1939 and then modeled experimentally by Bowrey and Purnell [20] in 1971. Roenigh *et al.* [21] reported Arrhenius parameters for SiH<sub>4</sub> and Si<sub>2</sub>H<sub>6</sub> decomposition kinetics. According to their study, activation

2

energies for SiH<sub>4</sub> and Si<sub>2</sub>H<sub>6</sub> were 57.4-61.1 kcal/mol and 51.1-52.5 kcal/mol, respectively. The important contribution towards understanding of Si<sub>2</sub>H<sub>6</sub> chemistry was due to Gates [15] who analyzed the rates and mechanisms of chemisorption on the silicon surface for SiH<sub>4</sub> and Si<sub>2</sub>H<sub>6</sub> and confirmed that the reactive sticking coefficient at room temperature, S<sup>R</sup>, for SiH<sub>4</sub> was less than 0.001 (~ near zero coverage) on silicon (111) surface, while S<sup>R</sup> for Si<sub>2</sub>H<sub>6</sub> was 0.47. This suggests that the reactivity of Si<sub>2</sub>H<sub>6</sub> over SiH<sub>4</sub> is at least 1000 times greater on a clean surface.

The first successful usage of  $Si_2H_6$  was towards deposition of silicon films by molecular beam epitaxy [22] and showed advantages of the  $Si_2H_6$ based process in preparation of epitaxial films at much lower deposition temperatures compared to the conventional SiH<sub>4</sub>-based process. Gas-phase reaction mechanisms for the silicon oxide deposition from  $Si_2H_6$  and  $N_2O$  for pyrolytic atmosphere CVD were modeled by Giunta *et al.* [23]. They suggested that rapid reaction of the decomposition products SiH<sub>2</sub> with N<sub>2</sub>O, suppresses the formation of larger silicon hydrides, generates the film precursor, silanone(SiH<sub>2</sub>O), and hence causes a strong dependence of the growth rate on Si<sub>2</sub>H<sub>6</sub> concentration in presence of excess N<sub>2</sub>O concentration. Several studies of Si<sub>2</sub>H<sub>6</sub> application for the deposition of the silicon oxide films have been reported, mainly with the use of either excimer, ultraviolet, or synchrotroninduced photo CVD [18], [24]-[26].

### 1.2 General Principles of PECVD [27]

1.2.1 Nature of Plasma

The primary role of plasma is to produce chemically active species that subsequently react via conventional pathways. A key factor is that substitution of electron kinetic energy for thermal energy avoids excessive heating and consequent degradation of substrates. The plasmas used for semiconductor application are produced by the application of a high frequency electric field across a body of gas and are weakly ionized gases comprising of electrons, ions, and neutral species. The electron concentration ranges from  $10^9$  to  $10^{12}$  cm<sup>-3</sup>, the ratio of concentration of the charged species to neutral species ranges from  $10^{-6}$  to  $10^{-4}$ , and the electron energy varies from 1-20 eV. One important characteristic of the glow discharge plasma is the electron temperature ( $10^4$ - $10^5$  K), which is typically 30 to 1000 times greater than the average temperature for the ions and neutral species (25-300 K). This high electron energy relative to the low temperature neutral species makes the glow discharge useful in driving CVD reactions.

When the plasma process first starts, energy from the electric field is coupled into the gas almost entirely via the kinetic energy of a few free electrons. The electrons acquire energy rapidly from the applied electric field and lose it to collisions. Collisions between electrons and gas molecules in plasma can be characterized as either elastic or inelastic, according to whether or not the internal energies of the colliding bodies are maintained. In the elastic case, only a small amount of energy is transferred, while the inelastic case involves a much larger energy loss and the excitation of internal modes (electronic, vibrational or translations) of target molecules. Inelastic collisions between the high energy electrons and neutral molecules result in, among other processes, electron impact ionization and molecular dissociation. Electron impact ionization helps to sustain the glow discharge by producing secondary electrons. Meanwhile, molecular dissociation creates free radicals that contribute to the film deposition.

In many plasma deposition processes, inert carrier gases are normally used as carrier or dilute gases. At low pressure, inert gas can absorb electron energy from the glow discharge and be excited to metastable states which are

4

summarized in Table 1.1. The metastable inert gas atoms can then transfer their energy to other reactant gases via inelastic collision. Thus, more ions and radical reactant gases are uniformly generated throughout the glow discharge. As a result, the deposition will be more uniform throughout the radius of reactor chamber.

### 1.2.2 Deposition Mechanism

The properties of plasma deposited films are strongly dependent on process parameters. Generally, the deposition mechanism of PECVD processes can be explained by four major steps. First, the primary reactions occur between electrons and reactant gases in the plasma to form a mixture of ions and free radical reactive species. Second, reactive species transport from the plasma to the substrate surface in parallel with various secondary inelastic and elastic reactions. Third, the reaction or adsorption of reactive species with or onto the substrate surface occurs. Finally, the rearrangement processes follow where active species or their reaction products incorporate into the film or re-emit from the surface back into the gas phase. However, many questions regarding plasma thin film deposition mechanism still remain unanswered.

In general, plasma deposition can be classified into two mechanisms, radical and ionic, depending on the type of species that interact with the solid surface during the plasma process. Both the radical and ionic mechanisms happen concurrently during the deposition process. Depending on the plasma process parameters, one mechanism may dominate the other.

### 1.2.2.1 Radical Mechanism

During the plasma deposition process, the generation rate and lifetime for neutral radicals are usually greater than they are for ions. These two effects make the radical concentration higher than that for ions. Hence, it is believed that neutral radicals are the major deposition agents under most deposition

| Inert gas | Metastable energy (eV) | Ionization energy (eV) |  |  |

|-----------|------------------------|------------------------|--|--|

| Не        | 19.8                   | 24.53                  |  |  |

| Ne        | 16.6                   | 21.56                  |  |  |

| Ar 11.5   |                        | 15.76                  |  |  |

| Kr        | 9.9                    | 14.0                   |  |  |

| Xe        | 8.32                   | 12.13                  |  |  |

Table 1.1. Metastable energy levels and ionization energies of major inert gases used for thin film deposition in CVD.

\_\_\_\_\_

...

-----

conditions. After being generated in the glow discharge and adsorbed on the substrate surface, the adsorbed radicals have to diffuse into a stable site to become a part of films. Surface diffusion of such adsorbed atoms is much slower, compared with diffusion in the CVD process, at normal plasma process temperature which is lower than 300°C.

At these low temperatures, surface diffusion and rearrangement of reactive species on the substrate become dominant and strongly affect the composition of weakly bonded and high diffusive species such as hydrogen. Thus, the films deposited at low temperatures normally contain more trapped radicals and defects. As a result, the films will be more porous and contain more hydrogen, resulting in poor thermal and electrical stability. The instabilities are due to a large amount of weakly bonded hydrogen that breaks easily under thermal or electrical stress and thus creates more dangling bonds in the film structure.

### 1.2.2.2 Ionic Mechanism

Coincidental with the large number of radicals generated during the plasma process, a small number of electron and ionic species are constantly bombarding the surface. Some ionic species react with the surface to become a part of the films, and others bounce off after neutralizing. Depending on the energy of the bombarding species and the surface state of the substrate, either deposition, densification, or sputtering may occur. Various ionic species exist during the plasma process with varying energies, so that all three reactions may happen at the same time. Because ionic species carry a charge, their attachment to the surface will be preferential. The constant bombardment of the surface by electrons and ions also speed up the rearrangement of adsorbed atoms on the substrate surface, resulting in higher compressive stress and a greater scratch resistance.

7

### 1.3 Research Objectives

The research is directed towards developing a silicon oxide deposition process resulting in high quality and reliable films to be used as passivation layers and interlevel insulators in the integrated circuit fabrication. The work culminates in developing a fluorinated silicon oxide film deposition process.

In this work, the use of  $Si_2H_6$ , instead of  $SiH_4$ , as silicon precursor to deposit the films in PECVD is extensively studied for the first time in the history of silicon oxide film deposition process. The research is divided into two major parts which are the silicon oxide film deposition for the first phase and the fluorinated silicon oxide film deposition for the second phase, as shown in Fig. 1.1. The equipment used for the film deposition is a Plasma Therm model VII-70 parallel plate plasma reactor system which uses a 13.56 MHz rf plasma source and has 500 W maximum output power as shown in Fig. 1.2. The electrode spacing was held constant at 1 inch. The top electrode was always maintained at  $60^{\circ}C$  for the film deposition.

In chapter 2, the plasma process characteristics of the silicon oxide films as a function of various process parameters such as gas flow ratio of  $N_2O$  to  $Si_2H_6$ , rf input power, deposition temperature, total gas flow rate, and process pressure are addressed. This experiment enables not only to understand chemical reaction mechanisms but to optimize each and every process parameter that affects the film deposition and eventually the film properties.

In chapter 3, effect of deposition temperature on the chemical and electrical film properties is addressed with the help of chemical etch rate, infrared transmission spectroscopy, high-frequency capacitance-voltage (C-V) technique, and current-voltage (I-V) measurements. As the most important goal for this research is to decrease the deposition temperature as much as

Fig. 1.1. Overall research outline. The research is divided into two major parts, silicon oxide and fluorinated silicon oxide film deposition.

Fig. 1.2. Schematic diagram of a Plasma Therm VII-70 parallel plate plasma reactor equipped with 13.56 MHz rf source and 1 inch electrode spacing.

possible, careful investigation is made to find the lowest viable deposition temperature.

In chapter 4, structural properties of the silicon oxide films annealed at various temperatures in the range of 300-1100°C are presented. The dependence of the physical and chemical properties of the silicon oxide films on the post-deposition annealing process is characterized.

In chapter 5, effect of the native oxide removal on the substrate surface prior to the silicon oxide film deposition is detailed. The electrical properties of the silicon oxide films derived from C-V and I-V measurements are studied. In addition, the effect of annealing the as-deposited films either in  $N_2$  just after the film deposition or in forming gas ambient after the formation of metal electrode is discussed.

In chapter 6, deposition characteristics for the fluorinated silicon oxide films incorporating  $CF_4$  as fluorine precursor into the silicon oxide deposition process, are addressed. The chemical and electrical film properties are examined as a function of flow rate ratio of  $CF_4$  to  $Si_2H_6$  in the film deposition process.

In chapter 7, electrical characterization details for the fluorinated silicon oxide films, deposited by the optimum deposition condition as derived from Chapter 6, are addressed. The results of C-V and I-V measurements are discussed. The improvements in film quality due to fluorine incorporation are summarized and comparisons made with the fluorine-free silicon oxide films.

## CHAPTER 2 SILICON OXIDE FILM DEPOSITION

### 2.1 Introduction

The many results presented in this chapter have been published in Journal of Electronic Materials, volume 24, pages 1507-1510, 1995. Their permission was gratefully acknowledged.

The deposition variables such as gas flow ratio of  $N_2O$  to  $Si_2H_6$ , deposition temperature, process pressure, total gas flow rate, and rf input power affect the film deposition in PECVD. It is necessary to understand these parameters that result in one mechanism becoming dominant between the radical and the ionic mechanisms, and how it effects the film properties. Therefore, each variable should be properly manipulated to optimize the film deposition process and to obtain high quality film properties. In this chapter, the first results on the silicon oxide films deposited by PECVD using  $Si_2H_6$  and  $N_2O$ as silicon and oxygen precursors as a function of those variables in a conventional parallel plate plasma reactor are presented.

### 2.2 Experiment

Boron doped, chemically polished 10-20  $\Omega$ -cm silicon wafers with (100) orientation were used as the substrates. The film deposition was carried out without any in-situ cleaning. After loading the wafers into the process chamber, the chamber was pumped to a base pressure of  $1 \times 10^{-3}$  Torr. High purity N<sub>2</sub>O (99.99 %) was then first introduced into the chamber, followed by a mixture of 4.8 % Si<sub>2</sub>H<sub>6</sub> in helium. The deposition recipe in detail is shown in Fig. 2.1. The use of the inert gas, He, is known to increase the stoichiometry of the film by reducing the incorporation of hydrogen in SiH bonding groups, and of nitrogen in SiN and NH bonding groups [10].

| Step<br>Parameter              | 1 | 2   | 3 | 4    | 5 | 6   | Remark                               |

|--------------------------------|---|-----|---|------|---|-----|--------------------------------------|

| N <sub>2</sub>                 | - |     |   |      |   |     |                                      |

| Si <sub>2</sub> H <sub>6</sub> |   |     |   |      |   |     |                                      |

| NĮO                            |   |     |   |      |   |     |                                      |

| CF₄                            |   |     |   |      |   |     | Fluorinated<br>silicon oxide<br>film |

| Chamber<br>pressure            |   |     |   |      |   |     |                                      |

| Temperature                    |   |     |   |      |   |     |                                      |

| rf power                       |   |     |   |      |   |     |                                      |

| Time (min)                     | 2 | 1.5 | 1 | 5-15 | 2 | 1.5 |                                      |

Fig. 2.1. The detailed deposition recipe consisting of six different steps. The process chamber is pumped to a base pressure before starting step 1. The films are deposited during step 4.

13

The thickness of the deposited silicon oxide films was measured by a Nanometrics 210XP thickness meter. Auger electron spectroscopy (AES) measurement on the films was carried out on a Physical Electronics model PHI-48 to determine the film composition. For the AES measurement, 100 nm thick silicon oxide film grown at 950°C by dry oxidation was used as a reference wafer to normalize the silicon and oxygen peaks. The etch rate was obtained by dipping the film for 1 min into P-etch solution consisting of 15 parts by volume 48 % HF, 10 parts by volume 70 % HNO<sub>3</sub>, and 300 parts by volume of deionized water. Typical etch rate in the P-etch solution for the silicon oxide films prepared by various methods [7], [28] are summarized in Table 2.1.

### 2.3 Results and Discussion

Figure 2.2 shows the film deposition rate and the chemical etch rate in the P-etch solution as a function of the gas flow ratio of  $N_2O$  to  $Si_2H_6$ . The deposited silicon oxide film thicknesses are in the range of 100-150 nm for the 250°C deposition temperature. The rf input power and the process pressure was 50 W and 700 mTorr, respectively. The increase in the gas flow ratio results in decrease in both the deposition rate and the chemical etch rate. The increase in Si<sub>2</sub>H<sub>6</sub> concentration causes higher film deposition rate presumably due to an increase in the number of active species in the glow discharge and drives the silicon oxide film more porous resulting in faster etch rate.

The gas flow ratio is the most important process parameter in determining the stoichiometry of the film [29]. The ratio for obtaining stoichiometric silicon oxide depends on the process condition used, as shown in Fig. 2.3. It can be seen that  $N_2O/Si_2H_6$  ratios, which are smaller than 50, result in silicon-rich oxide films while the ratio in the range of 50-150 gives the stoichiometric silicon oxide films with the atomic ratio of silicon to oxygen equal to 50 %. At ratios higher than 150, the film becomes oxygen-rich.

| Films                                  | Etch rate (nm/sec) |

|----------------------------------------|--------------------|

| Sputtered silicon oxide                | 2-7                |

| Atmospheric pressure CVD silicon oxide | 1-2                |

| Thermal silicon oxide                  | 0.2                |

| SiH₄-based PECVD silicon oxide         | ~ 1.6              |

Table 2.1. Typical etch rate in the P-etch solution for the silicon oxide films prepared by various methods.

Fig. 2.2. Deposition rate and etch rate in the P-etch solution as a function of  $N_2O/Si_2H_6$  gas flow ratio.

Fig. 2.3. Atomic ratio of silicon to oxygen and composition of  $SiO_x$  obtained from Auger electron spectroscopy measurements as a function of  $N_2O/Si_2H_6$  gas flow ratio.

The dependence of film deposition rate as a function of deposition temperature is illustrated in Fig. 2.4. The rf input power was 50 W, total flow rate was 140 scom, and N<sub>2</sub>O/Si<sub>2</sub>H<sub>5</sub> flow ratio was 55. Under these experimental conditions, it is evident from Fig. 2.4 that the deposition is limited by the mass transport process. For pyrolytic atmosphere pressure CVD of the silicon oxide films using  $Si_2H_6$  and  $N_2O$  as source materials, formation of a gas phase intermediary SiH<sub>2</sub>O precursor has been suggested [23]. Disiloxane, (SiH<sub>3</sub>)<sub>2</sub>O, gas phase intermediary precursor has been suggested for the silicon oxide films in PECVD by using SiH<sub>4</sub> and N<sub>2</sub>O [10]. These precursor molecules reach the surface and undergo surface reaction by which hydrogen is replaced by oxygen. It is quite likely that intermediary gas phase precursors are also formed in PECVD utilizing Si<sub>2</sub>H<sub>6</sub> and N<sub>2</sub>O. From Fig. 2.4, the deposition rate is seen to decrease with an increase in deposition pressure. This is consistent with lower flux of the active intermediary species transported to the surface through the boundary layer. Thermal dissociation study of  $Si_2H_6$  has shown that  $Si_2H_6$ partially dissociates on a clean silicon (100) surface even below room temperature [30]. Hence, Si<sub>2</sub>H<sub>6</sub> can also contribute to film deposition observed in this study at low temperature.

The peak deposition rates are dependent on the process pressure and are observed to be 22 nm/min and 14 nm/min for the deposition pressure of 300 mTorr and 700 mTorr, respectively. The slight decrease in the deposition rate for higher deposition temperatures is believed to be due to the re-emission characteristics of the adsorbed active radical species on the surface. Films deposited at low deposition rate (7-15 nm/min) reveal reproducible deposition properties and good thickness uniformity of within  $\pm$  3 % across four inch diameter wafers.

Fig. 2.4. Deposition rate as a function of temperature for the silicon oxide films deposited at 300, 700, 1100 mTorr.

Deposition rate is plotted as a function of the total gas flow rate into the process chamber with the gas flow ratio of  $N_2O$  to  $Si_2H_6$  held at a constant value in Fig. 2.5. The rf input power was 50 W, process pressure was 700 mTorr, and the deposition temperature was 250°C. As evident from this figure, the deposition rate increases with increase in the total flow rate with deposition pressure held constant. This observation is consistent with a mass transport limited process.

Figure 2.6 shows the chemical etch rate of the films as a function of deposition temperature at 50 W rf power, constant N<sub>2</sub>O/Si<sub>2</sub>H<sub>6</sub> ratio of 55, and constant gas flow rate of 140 sccm. The silicon oxide film deposited at room temperature at 300 mTorr has an etch rate of 7-8 nm/sec, which is four times faster than the etch rate of 1.7 nm/sec for the film deposited at 250°C at the same pressure. In addition, the silicon oxide films deposited at room temperature with higher pressure of 700 mTorr show almost twice the etch rate of 2.5 nm/sec, compared to 1.3 nm/sec etch rate of the silicon oxide deposited at 250°C. The faster etch rate for lower deposition temperature indicates less film integrity, which may be due to lower surface diffusion and rearrangement of active species on the substrate surface. For purposes of comparison, the Petch solution used here etches silicon oxide films deposited at 350°C in PECVD utilizing SiH<sub>4</sub> at a rate of 1.6 nm/sec, as summarized in Table 2.1. This suggests that the etch rate of the Si<sub>2</sub>H<sub>6</sub>-based PECVD silicon oxide films deposited at 200°C is comparable to that of the SiH₄-based PECVD films deposited at 350°C.

The effect of the deposition rate on the rf discharge power is illustrated in Fig. 2.7 for three different pressure conditions. The deposition temperature is maintained at  $250^{\circ}$ C, total flow at 140 sccm, and the N<sub>2</sub>O/Si<sub>2</sub>H<sub>6</sub> ratio at 55. At low power (< 30 W), the reaction is limited by the number of active radical

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Fig. 2.5. Deposition rate as a function of total gas flow rate for the silicon oxide films deposited with  $N_2O/Si_2H_6$  gas flow ratio of 55 and 110.

Fig. 2.6. Chemical etch rate in the P-etch solution vs. substrate deposition temperature.

Fig. 2.7. Deposition rate as a function of rf input power for the silicon oxide films deposited at 100, 300, and 700 mTorr.

species created in the glow discharge. The low chamber pressure causes an increase in the mean free path resulting in low deposition rate. As the rf power increases, the deposition rate saturates and then decreases. This decrease in the deposition rate with high power is mainly due to the sputtering effects caused by higher energy of the bombarding species [27].

The deposition rate and the etch rate as a function of the process pressures are shown in Fig. 2.8. The deposition rate in the mass transport controlled regime is strongly affected by a change in the total pressure and is proportional to the diffusivity of the active radical species in the boundary layer. The diffusivity in the boundary layer is inversely proportional to the total pressure. Increasing pressure decreases the number of species arriving on the substrate surfaces, thus causing a fall in the deposition rate from 22 nm/min at 100 mTorr to 6 nm/min at 1400 mTorr. The almost flat curve for pressures above 300 mTorr indicates lower dependence of etch rate on pressure. However, the etch rate has a minimum value of 1.3 nm/sec for the silicon oxide films deposited at 700 mTorr.

## 2.4 Conclusion

Stoichiometric, reproducible, and uniform PECVD silicon oxide films have been deposited between room temperature and  $300^{\circ}$ C using Si<sub>2</sub>H<sub>6</sub> and N<sub>2</sub>O as silicon and oxygen precursors, respectively. The dependence of film properties for processing parameters was investigated. The stoichiometric silicon oxide films were obtained when the gas ratio of N<sub>2</sub>O to Si<sub>2</sub>H<sub>6</sub> was in the range of 50-150. The deposition was also found to be nearly temperature independent indicating the mass transport limited regime. Films deposited at low deposition rate (7-15 nm/min) showed reproducible deposition properties and good thickness uniformity of within ± 3% across 4 inch diameter silicon wafers. The best process parameters were 700 mTorr for the pressure, 50 W for the plasma power, 50 for the gas flow ratio of N<sub>2</sub>O to Si<sub>2</sub>H<sub>6</sub>, and 140 sccm for the total gas flow rate. The film deposition rate with this condition at the deposition temperature of  $120^{\circ}$ C was about 12-13 nm/min. This process shows significant promise as a low temperature substitute for the conventional SiH<sub>4</sub>-based PECVD silicon oxide deposition process in the integrated circuit technology.

Fig. 2.8. Deposition rate and chemical etch rate vs. deposition pressure.

# **CHAPTER 3**

# **EFFECT OF DEPOSITION TEMPERATURE ON FILM QUALITY**

## 3.1 Introduction

The many results presented in this chapter have been published in Thin Solid Films, volume 270, pages 512-516, 1995. Their permission was gratefully acknowledged.

Semiconductor devices are being scaled down to submicron dimensions to meet device requirements for high operaing speed, low power consumption, and high packing density. This requires the semiconductor industry to look for lower temperature processes. Silicon oxide is a common dielectric material in the integrated circuit technology for purposes such as interlevel isolation and dielectric passivation. It is desirable to deposit the silicon oxide films at as low a temperature as possible to avoid the various adverse effects accompanied with processing at elevated temperatures.

In this chapter, results of deposition of PECVD silicon oxide films at significantly lower temperatures using  $Si_2H_6$ , instead of  $SiH_4$ , as the silicon source, are presented. For the first time, the chemical and electrical characteristics of the silicon oxide films deposited in the temperature range of  $30-250^{\circ}C$  with the above  $Si_2H_6$  process are studied. In particular, the effect of the film deposition temperature on the film properties measured by chemical etch rate, infrared transmission spectroscopy, high-frequency C-V technique, and I-V measurements are discussed.

## 3.2 Experiment

Boron doped, chemically polished 100 mm diameter p-type silicon wafers with (100) orientation and resistivity in the range of 5-15  $\Omega$ ·cm were used as the substrate material. The chamber pressure during film deposition was kept at 700 mTorr. The deposition rf power was 50 W. The total gas flow rate was 140 sccm while the  $N_2O$  to  $Si_2H_6$  gas ratio set at 50. The deposition temperature was the only process parameter varied in this experiment. The wafers for the electrical characterization were cleaned as per the standard RCA cleaning process [31], followed by a dip in dilute HF (100:1 by volume ratio of deionized water to 48 % HF).

The RCA cleaning procedure consists of two different steps. In the first step (called standard clean-1 or SC1), wafers are exposed to 5:1:1 solution of deionized water : 30 %  $H_2O_2$ : 30 %  $NH_4OH$  at 70°C for 5 min. This procedure is designed to remove organic surface films and to expose the surface to decontamination reactions. In the second step (called SC2), the rinsed wafer is exposed to 6:1:1 solution of deionized water : 30 %  $H_2O_2$ : 37 % HCl at 70°C for 5 min. This procedure is designed to remove metallic contaminants that were not entirely removed by the first treatment.

The wafers were then rinsed in deionized water and blown dry using N<sub>2</sub>. Silicon oxide films of 100 nm thickness were deposited at different deposition temperatures within the 30-250°C temperature range. A 300 nm thick aluminum film was then thermally evaporated on the silicon oxide films. Metal-oxide-semiconductor (MOS) capacitors with predefined electrode area were fabricated by wet etching aluminum using standard photolithography techniques. The chemical solution, consisting of 1:1:17:1 by volume of 70 % HNO<sub>3</sub> : CH<sub>3</sub>COOH : 85 % H<sub>3</sub>PO<sub>4</sub> : deionized water, was used as an aluminum etchant. The typical etch rate for a sputtered aluminum with this solution is about 50 nm/min at room temperature.

The gate electrode areas for the C-V and the I-V measurements were  $2.73 \times 10^{-3}$  cm<sup>2</sup> and  $8.3 \times 10^{-3}$  cm<sup>2</sup>, respectively. Post-metallization annealing was done at 400°C in N<sub>2</sub> ambient for 30 minutes. The thickness of the silicon

oxide films was measured by ellipsometry on an Applied Materials Ellipsometer II and by a Nanometrics 210XP thickness meter. The dielectric constant of the silicon oxide films was calculated from the accumulation capacitance and conductance at high-frequency (1 MHz) C-V measurements with a HP 4275A LCR meter. The ramp I-V characteristics were obtained with a HP 4140 voltage source and a Keithley 485 picoammeter.

Infrared transmission spectroscopic measurements were made on 200-220 nm thick silicon oxide films deposited on substrates that had not undergone any pre-deposition cleaning. The vibrational properties in the 400-4000 cm<sup>-1</sup> wave number range were observed using a Perkin Elmer Fourier transform infrared spectrophotometer 1600 with a resolution of 4 cm<sup>-1</sup>. A bare silicon wafer was used as the background reference.

#### 3.3 Results and Discussion

The deposition rate and etch rate of the silicon oxide films as a function of the deposition temperature is shown in Fig. 3.1. The etch rate was obtained by dipping the films in the P-etch solution. The silicon oxide deposition by PECVD using Si<sub>2</sub>H<sub>6</sub> and N<sub>2</sub>O chemistry is a mass transport limited process [32] especially in the temperature range above  $150^{\circ}$ C as evident from the nearly temperature independent deposition rate observed in Fig. 3.1. The fastest deposition rate observed in this study is 12.5 nm/min at 220°C. The faster etch rate for the films deposited at lower temperature reflects a increase in the film porosity, probably due to reduced surface diffusion and rearrangement of active species on the substrate surface [33]. This may result in a higher density of hydroxyl (OH)-containing bonds as explained later. The etch rate approaches a constant value of 1.3 nm/sec for films deposited at 150°C and above. This observed etch rate value of 1.3 nm/sec is comparable to the etch rate observed on silicon oxide films deposited by TEOS/ozone CVD at 400°C [34].

Fig. 3.1. Deposition rate and etch rate of the silicon oxide films as a function of deposition temperature. The P-etch solution consists of 15 parts by volume of 48 % HF, 10 parts by volume 70 %  $HNO_3$ , and 300 parts by volume of deionized water.

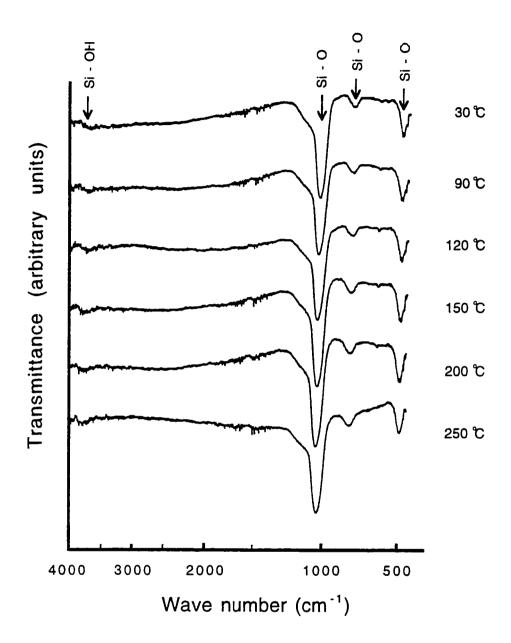

Figure 3.2 shows the infrared transmission spectra of the silicon oxide films deposited at various deposition temperatures from  $30^{\circ}$ C to  $250^{\circ}$ C. A decrease in the transmission intensity of the hydroxyl-containing bonds located at 3380-3620 cm<sup>-1</sup> and at 940 cm<sup>-1</sup> is observed with an increase in the deposition temperature [5]. This gradual disappearance of the hydroxyl-containing peaks with increasing deposition temperature is consistent with the improvement in the film integrity reflected by a decrease in the etch rate in Fig. 3.1.

In the silicon oxide, the basic structural unit is the SiO₄ tetrahedron with a silicon atom at the center, bonded to four oxygen atoms placed at the corners as shown in Fig. 3.3. Each oxygen atom belongs to two tetrahedra and is thus bonded to two silicon atoms. The vibrational mode associated with the Si-O-Si stretching is frequently used to study the structural property of the silicon oxide films. The infrared transmission spectra for stoichiometric silicon oxide film exhibits three characteristic peaks [35] which occur approximately at 450, 800, and 1075 cm<sup>-1</sup>. The lowest frequency vibration near 450 cm<sup>-1</sup> is a Si-O-Si bond. The intermediate frequency and the weakest transmission at about 800 cm<sup>-1</sup> is a Si-O-Si bending vibration mode in which the oxygen atom motion is out of the plane of the Si-O-Si bidging bond angle. The strongest transmission near 1075 cm<sup>-1</sup> is a stretching vibration in which the oxygen atom motion is in the plane of the Si-O-Si bond and along the direction of the Si-O-Si bidging bond angle. The strongest transmission near 1075 cm<sup>-1</sup> is a stretching vibration in which the oxygen atom motion is in the plane of the Si-O-Si bond and along the direction of the Si-O-Si bond and along the direction of the bisector of Si-O-Si bidging bond angle. The strongest transmission near 1075 cm<sup>-1</sup> is a stretching vibration in which the oxygen atom motion is in the plane of the Si-O-Si bond and along the direction of the Si-O-Si bond and in a direction parallel to a line joining the two silicon atoms.

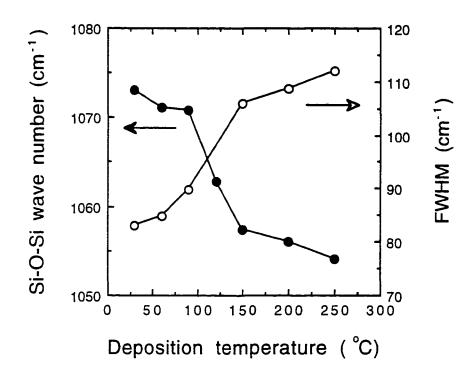

The Si-O-Si stretching peak and its full width at half maximum (FWHM) as a function of the deposition temperature is shown in Fig. 3.4. As the deposition temperatures increase, the wave number corresponding to the Si-O-Si stretching decreases from 1073 cm<sup>-1</sup> to 1054 cm<sup>-1</sup> while the FWHM increases

Fig. 3.2. Infrared transmission spectra of the as-deposited silicon oxide films as a function of deposition temperature in the range of 30-250°C. The arrows indicate the location of absorption peaks in the vibrational spectra.

Fig. 3.3. Three-dimensional representation of two neighboring  $SiO_4$  cell, bridged by an oxygen atom. Directions for three characteristic vibration motions are also marked.

Fig. 3.4. Si-O-Si stretching absorption peak and FWHM of the as-deposited silicon oxide films shown in Fig. 3.2 as a function of film deposition temperature.

from 83 cm<sup>-1</sup> to 112 cm<sup>-1</sup>. It is now well accepted [1], [11], [36], [37] that shifts in the stretching wave number toward lower values and increases in the FWHM are related to smaller values of the average Si-O-Si bridging bond angle which is believed to be about 144° for thermally grown silicon oxide and somewhat smaller than 144° for PECVD films [38]. As the Si-Si distance is directly related to the Si-O-Si bond angle, changes in wave number with compaction can be explained in terms of changes in the bond angle. By assuming that the density of silicon oxide scales inversely as the cube of the Si-Si distance, a decrease in the Si-O-Si bond angle results in an increase in the film density. From Fig. 3.2, the hydroxyl content decreases with increasing deposition temperature. An increase in the Si-OH content is known to result in more porous silicon oxide CVD films [3], causing faster etch rate for the silicon oxide films deposited at lower deposition temperatures.

The infrared transmission spectra as a function of the deposition temperature after conventional furnace anneal at  $400^{\circ}$ C in N<sub>2</sub> ambient for 30 min is shown in Fig. 3.5. For the annealed case, the hydroxyl-containing peak located at 940 cm<sup>-1</sup> has nearly disappeared even for the silicon oxide deposited at  $30^{\circ}$ C.

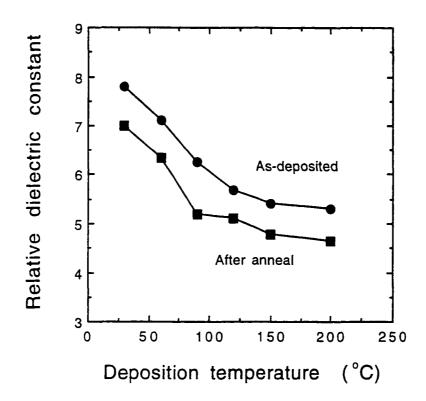

Figure 3.6 indicates the relative dielectric constant of the as-deposited and annealed silicon oxide films as a function of the deposition temperature. The dielectric constant is calculated from the observed values of the capacitance in accumulation of MOS devices fabricated with the deposited films. The observed capacitance was corrected for series resistance [39], as described in Appendix A. The dielectric constant has been reported to be proportional to the hydroxyl-containing species in the films. The increase in the dielectric constant due to H<sub>2</sub>O and OH content can be explained by the fact [3] that these are dipolar species with relatively large dipole moments  $\mu_{H_2O}=1.84$

Fig. 3.5. Infrared transmission spectra of the annealed silicon oxide films as a function of film deposition temperature. The annealing is carried out at  $400^{\circ}$ C in N<sub>2</sub> ambient for 30 min.

Fig. 3.6. Dielectric constant of the as-deposited and the annealed silicon oxide films as a function of film deposition temperature. Anneal is carried out at 400°C in N<sub>2</sub> ambient for 30 min. The thickness of the silicon oxide film is about 100 nm and the gate area is  $2.7 \times 10^{-3}$  cm<sup>2</sup>.

debye and  $\mu_{OH}$ =1.5 debye (1 debye=3.338 × 10<sup>-30</sup> C·m), respectively, with the relative dielectric constant of 78.2 for liquid water being large. Hence, the silicon oxide films deposited at lower temperatures with higher Si-OH content result in higher values for the relative dielectric constant. The dielectric constant of the as-deposited silicon oxide films decreases from 7.8 to 5.2 as the deposition temperature increases from 30°C to 200°C. Similarly, the dielectric constant of the annealed silicon oxide films decreases from 7 to 4.6. Assuming that the anneal temperature at 400°C is low enough not to change the thickness of the silicon oxide films, the decreased values of the dielectric constant indicate that even though the annealing is carried out after the gate electrode fabrication, it is able to partially reduce the hydroxyl-related bonds. The smallest value that of 4.6 for the relative dielectric constant obtained in this study, is still higher than the corresponding value of 3.9 for the thermally grown silicon oxide. The N<sub>2</sub> ambient gas during annealing is chemically stable at the 400°C annealing temperature used and can not result in significant nitridation [40].

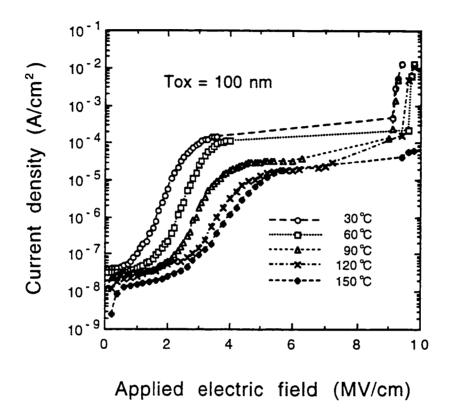

Time zero dielectric breakdown characteristics of the silicon oxide films deposited at different deposition temperatures are shown in Fig. 3.7. The details of the ramp I-V characteristic are basically described as follows [7]. As a current flows through the silicon oxide, some electrons are captured into deep bulk traps, creating a space charge. At a suitably high current, the charge build-up is enough to significantly affect the electric field at the injecting interface which opposes the ramp voltage and on a logarithmic plot a trapping ledge is observed. If all of the traps are filled, or if a dynamic equilibrium is achieved between trapping and high field detrapping, then the curve may go through the ledge onto a new Fowler-Nordheim characteristic before breakdown. The ramp I-V measurements, here, are taken at 25°C with the voltage ramp rate set at 1 V/sec. The polarity of the field causes carrier accumulation at the substrate

Fig. 3.7. J-E characteristics of the silicon oxide films for various deposition temperatures in the range of  $30-150^{\circ}$ C. The voltage ramp rate is fixed at 1 V/sec. The bias polarity corresponds to electron injection from the gate. The oxide thickness is 100 nm and the gate area is  $8.3 \times 10^{-3}$  cm<sup>2</sup>.

surface. This for p-type substrate used in this study corresponds to electron injection from the aluminum gate. Current density, J, in the silicon oxide film as a function of the applied electric field, E, indicates higher leakage currents for the films deposited at lower temperatures. However, the leakage current density of  $5 \times 10^{-8}$  A/cm<sup>2</sup> at 0.5 MV/cm field strength for the silicon oxide film deposited at the lowest temperature of 30°C is of the same order as through the silicon oxide film deposited by PECVD using SiH<sub>4</sub> as the silicon source at 350°C [7]. The J-E characteristics in Fig. 3.7 have similar features for all the deposition temperatures considered. The current through the silicon oxide film saturates at high electric field, known as the trapping ledge [41], [42]. The trapping ledge seems to be caused by the hydroxyl-containing bonds which either act as deep traps or recombination centers in the silicon oxide films [2]. Further experiments are required for a better understanding of the parameters related to the trapping ledge. At about 10 MV/cm, the intrinsic dielectric breakdown of the silicon oxide films is observed. For the film deposition at 150°C, the dielectric breakdown field is greater than 10 MV/cm.

In Fig. 3.8, J/E<sup>2</sup> is plotted against 1/E. The slope corresponds to the barrier height [43] as shown in Fig. 3.9. The slope of the linear part of this curve is observed to increase with increasing deposition temperature. From this, the barrier height values of 3.1 eV and greater obtained for the oxide films deposited at 120°C and above are close to the reported value of 3.2 eV. For the silicon oxide films deposited at 30°C, the observed barrier height of 1.59 eV is half that of the reported value, indicating existence of a large number of traps or energy states in the film.

A distribution of the non-destructive dielectric breakdown field of the silicon oxide films deposited at various deposition temperatures is shown in Fig. 3.10. In the measurements, a non-destructive breakdown field is defined as the

Fig. 3.8. Fowler-Nordheim current plots of the silicon oxide films shown in Fig. 3.7. The linear dependence of  $J/E^2$  against 1/E gives the barrier height indicated in the parentheses .

Fig. 3.9. Energy-band diagram of a MOS system with p-type silicon biased into accumulation. The barrier height is marked.