Linköping Studies in Science and Technology Dissertations, No. 1728

### Low-Voltage Analog-to-Digital Converters and Mixed-Signal Interfaces

Prakash Harikumar

Division of Integrated Circuits and Systems Department of Electrical Engineering (ISY) Linköping University SE-581 83 Linköping, Sweden

Linköping 2015

Low-Voltage Analog-to-Digital Converters and Mixed-Signal Interfaces Copyright © 2015 Prakash Harikumar ISBN 978-91-7685-890-5 ISSN 0345-7524 Printed by LiU-Tryck, Linköping, Sweden, 2015

### Abstract

Analog-to-digital converters (ADCs) are crucial blocks which form the interface between the physical world and the digital domain. ADCs are indispensable in numerous applications such as wireless sensor networks (WSNs), wireless/wireline communication receivers and data acquisition systems. To achieve long-term, autonomous operation for WSNs, the nodes are powered by harvesting energy from ambient sources such as solar energy, vibrational energy etc. Since the signal frequencies in these distributed WSNs are often low, ultra-low-power ADCs with low sampling rates are required. The advent of new wireless standards with ever-increasing data rates and bandwidth necessitates ADCs capable of meeting the demands. Wireless standards such as GSM, GPRS, LTE and WLAN require ADCs with several tens of MS/s speed and moderate resolution (8-10 bits). Since these ADCs are incorporated into battery-powered portable devices such as cellphones and tablets, low power consumption for the ADCs is essential.

The first contribution is an ultra-low-power 8-bit, 1 kS/s successive approximation register (SAR) ADC that has been designed and fabricated in a 65-nm CMOS process. The target application for the ADC is an autonomously-powered soil-moisture sensor node. At  $V_{DD} = 0.4$  V, the ADC consumes 717 pW and achieves an FoM = 3.19 fJ/conv-step while meeting the targeted dynamic and static performance. The 8-bit ADC features a leakage-suppressed S/H circuit with boosted control voltage which achieves > 9-bit linearity. A binary-weighted capacitive array digital-to-analog converter (DAC) is employed with a very low, custom-designed unit capacitor of 1.9 fF. Consequently the area of the ADC and power consumption are reduced. The ADC achieves an ENOB of 7.81 bits at near-Nyquist input frequency. The core area occupied by the ADC is only 0.0126 mm<sup>2</sup>.

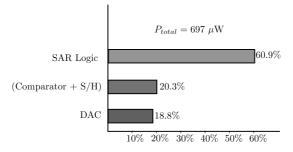

The second contribution is a 1.2 V, 10 bit, 50 MS/s SAR ADC designed and implemented in 65 nm CMOS aimed at communication applications. For medium-tohigh sampling rates, the DAC reference settling poses a speed bottleneck in chargeredistribution SAR ADCs due to the ringing associated with the parasitic inductances. Although SAR ADCs have been the subject of intense research in recent years, scant attention has been laid on the design of high-performance on-chip reference voltage buffers. The estimation of important design parameters of the buffer as well critical specifications such as power-supply sensitivity, output noise, offset, settling time and stability have been elaborated upon in this dissertation. The implemented buffer consists of a two-stage operational transconductance amplifier (OTA) combined with replica source-follower (SF) stages. The 10-bit SAR ADC utilizes split-array capacitive DACs to reduce area and power consumption. In post-layout simulation which includes the entire pad frame and associated parasitics, the ADC achieves an ENOB of 9.25 bits at a supply voltage of 1.2 V, typical process corner and sampling frequency of 50 MS/s for near-Nyquist input. Excluding the reference voltage buffer, the ADC consumes 697  $\mu$ W and achieves an energy efficiency of 25 fJ/conversion-step while occupying a core area of 0.055 mm<sup>2</sup>.

The third contribution comprises five disparate works involving the design of key peripheral blocks of the ADC such as reference voltage buffer and programmable gain amplifier (PGA) as well as low-voltage, multi-stage OTAs. These works are a) Design of a 1 V, fully differential OTA which satisfies the demanding specifications of a PGA for a 9-bit SAR ADC in 28 nm UTBB FDSOI CMOS. While consuming 2.9  $\mu$ W, the PGA meets the various performance specifications over all process corners and a temperature range of [-20°C +85°C]. b) Since FBB in the 28 nm FDSOI process allows wide tuning of the threshold voltage and substantial boosting of the transconductance, an ultra-low-voltage fully differential OTA with  $V_{DD} = 0.4$  V has been designed to satisfy the comprehensive specifications of a general-purpose OTA while limiting the power consumption to 785 nW. c) Design and implementation of a power-efficient reference voltage buffer in 1.8 V, 180 nm CMOS for a 10-bit, 1 MS/s SAR ADC in an industrial fingerprint sensor SoC. d) Comparison of two previously-published frequency compensation schemes on the basis of unity-gain frequency and phase margin on a three-stage OTA designed in a 1.1 V, 40-nm CMOS process. Simulation results highlight the benefits of split-length indirect compensation over the nested Miller compensation scheme. e) Design of an analog front-end (AFE) satisfying the requirements for a capacitive body-coupled communication receiver in a 1.1 V, 40-nm CMOS process. The AFE consists of a cascade of three amplifiers followed by a Schmitt trigger and digital buffers. Each amplifier utilizes a two-stage OTA with split-length compensation.

## Populärvetenskaplig sammanfattning

Analog-till-digital omvandlare (ADC) är viktiga byggstenar för att konvertera signaler i den fysiska världen till den digitala domänen. AD-omvandlare är nödvändiga i flera applikationer som trådlösa sensornätverk (WSN), trådlös/trådbundna kommunikationsmottagare och datainsamlingssystem. För att ge trådlösa sensornoder lång autonom livslängd kan de utvinna energi från sin omgivning exempelvis från solenergi, rörelseenergi etc. Eftersom frekvensen på insignalerna i dessa distribuerade sensornoder ofta är låg behövs AD-omvandlare med ultralåg effektförbrukning och låg samplingshastighet. Även skapandet av nya trådlösa standarder med ständigt ökande datatakter och bandbredd kräver AD-omvandlare som kan tillgodose dessa krav. Trådlösa standarder som GSM, GPRS, LTE och WLAN behöver AD-omvandlare med samplingshastigheter på flera tiotals miljoner samplingar per sekund och moderat upplösning (8-10 bitar). Eftersom AD-omvandlare används i batteridrivna portabla enheter som mobiltelefoner och surfplatta är även låg effektförbrukning viktigt.

Det första bidraget är en 8-bit, 1 kS/s succesivapproximationsregister (SAR) ADomvandlare med ultralåg effektförbrukning designad och tillverkad i en 65-nm CMOS process. Applikationen är en jordfuktighetssensornod som skördar energi från sin omgivning. Vid en matningsspänning på 0.4 V förbrukar AD-omvandlaren 717 pW och har en FoM på 3,19 fJ/konvertering samtidigt som den möter kraven på dynamisk och statisk prestanda. AD-omvandlaren har en läckdämpande S/H krets med boost kontroll som når > 9 bitars linjäritet. En digital-till-analog omvandlare (DAC) med binärviktad kapacitiv array används, arrayen använder en väldigt liten specialgjord enhetskapacitans på 1,9 fF för att reducera både arean och effektförbrukningen av AD-omvandlaren. Den når en ENOB på 7,81 bitar för infrekvenser nära Nyquistfrekvensen. AD-omvandlarens area är bara 0,0126 mm<sup>2</sup>.

Det andra bidraget är en 1,2 V, 10-bit, 50 MS/s SAR AD-omvandlare designad och implementerad i 65-nm CMOS för kommunikationsapplikationer. För medelhöga till höga samplingshastigheter begränsar insvängningstiden för DA-omvandlarens referensspänning hastigheten i laddningsredistributions SAR AD-omvandlare på grund av ringningar orsakad av parasitiska induktanser. Trots att SAR AD-omvandlare har varit fokus för intensiv forskning de senaste åren har inte mycket forskning gjorts på högpresterande integrerade spänningsreferensbuffrar. Estimering av viktiga design parametrar för buffern och kritiska specifikationer som känslighet mot ändringar i matningsspänningen, utsignals brus, offset, insvängningstid och stabilitet har undersökts i denna avhandling. Den implementerade buffern består av en två-stegs operationstranskonduktansförstärkare (OTA) kombinerad med ett replikerande sourceföljarsteg (SF). AD-omvandlaren använder en kapacitiv DA-omvandlare med delad array för att reducera arean och effektförbrukningen. I post-layout simuleringar, inklusive alla pinnar och deras associerade parasiter, når AD-omvandlaren 9,25 effektiva bitar (ENOB) med en matningsspänning på 1,2 V, typiska processparametrar och en samplingshastighet på 50 MS/s för insignaler nära Nyquist frekvensen. Utan spänningsreferensbuffern förbrukar AD-omvandlaren 697  $\mu$ W och har en energieffektivitet på 25 fJ/konvertering med en area på 0,055 mm<sup>2</sup>.

Det tredje bidraget består av fem olika arbeten bestående av viktiga assisterande block för en AD-omvandlare som spänningsreferensbuffer och programmerbara förstärkare (PGA) samt lågspännings, flerstegs OTAs. Dessa arbeten är a) Design av en 1 V, differentiell OTA som möter kraven som ställs för en PGA till en 9-bitars SAR AD-omvandlare i 28-nm UTBB FDSOI CMOS. Med en effektförbrukning på 2,9 µW når PGA:n alla specifikationerna över alla processhörn och för temperaturer mellan -20°C till +85°C. b) Eftersom FBB i 28-nm FDSOI tillåter stora justeringar av tröskelspänningen och boostning av transkonduktansen, har en differentiell OTA med en matningsspänning på 0,4 V designats för att möta alla krav som ställs på en universell OTA med en effektförbrukning på 785 nW. c) Design och implementation av en effekteffektiv spänningsreferensbuffer med en matningsspänning på 1,8 V i 180-nm CMOS för en 10-bitars, 1 MS/s SAR AD-omvandlare för en industriell fingeravtrycksläsare. d) Jämförelse av tidigare publicerade frekvenskompenseringstekniker för att möta kraven för förstärkar-bandbredds-produkten och fasmarginalen i en tre-stegs OTA designad i en 1,1 V, 40-nm CMOS process. Simuleringsresultaten visade på fördelarna med en indirekt kompensering jämfört med Miller kompensering. e) Design av ett analogt front-end (AFE) som tillgodoser kraven för en kapacitiv kroppskopplad kommunikationsmottagare i en 1,1 V, 40-nm CMOS process. AFE:n består av tre seriekopplade förstärkare följt av en Schmittrigger och en digital buffer. Varje förstärkare använder en två-stegs OTA med indirekt kompensering.

## Preface

This dissertation presents the research work performed during the period August 2011 – September 2015 at the Department of Electrical Engineering, Linköping University, Sweden. The main contributions of this dissertation are as follows:

- Design and implementation of a 0.4 V, 717 pW, 8-bit 1 kS/s SAR ADC in 65 nm CMOS. The ADC features a leakage-reduced sampling switch with a multi-stage charge pump to guarantee sufficient linearity. A custom-designed unit capacitor achieves reduced area and power consumption for the capacitive DAC.

- Design and implementation of a 10-bit, 50 MS/s SAR ADC with an on-chip reference voltage buffer in 65 nm CMOS. The speed limitation for medium/high-speed SAR ADCs due to inaccurate DAC settling in the presence of bondwire parasitics is discussed. The performance specification and design details of a high-speed reference voltage buffer are elaborated upon in this work.

- Design of a low-power PGA for a 9-bit SAR ADC in 28 nm UTBB FDSOI CMOS process. The RBB feature of this CMOS process node was utilized to enhance the DC gain while avoiding large resistors in the CMFB circuit for the first stage.

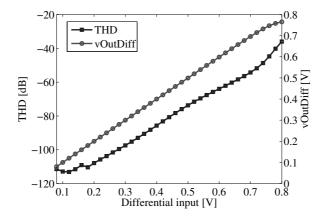

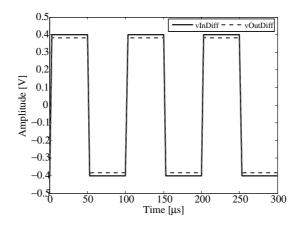

- Design of an ultra-low-voltage fully differential OTA in 28 nm UTBB FD-SOI CMOS. With a differential output swing of 0.8FS, the OTA achieves an SNR of 8.7 bits and a THD of -60.3 dB while consuming 785 nW from a 0.4 V supply. The small-signal and large signal performance as well as the matching-constrained specifications such as PSRR, CMRR and offset have been determined using exhaustive simulations.

- Design and implementation of a power-efficient reference voltage buffer in 180 nm CMOS for a 10-bit, 1 MS/s SAR ADC in a fingerprint sensor. The buffer meets the requirements on settling time, PSRR, output noise, stability and also supports a low-power standby mode.

- Comparison of two previously-published frequency compensation schemes using a three-stage OTA designed in 40 nm CMOS. Utilizing metrics such as phase margin, unity-gain frequency and total compensation capacitance, the advantages of the reversed nested indirect compensation technique are illustrated for high-speed multi-stage OTAs.

- Design of a receiver AFE for capacitive body-coupled communication in 1.1 V, 40 nm CMOS. Three different AFE topologies were designed and compared in terms of noise, gain and power consumption.

The contents of this dissertation are based on the following publications:

- **Paper I P. Harikumar**, J. J. Wikner and A. Alvandpour, "A 0.4 V, sub-nW, 8-bit 1 kS/s SAR ADC in 65 nm CMOS for Wireless Sensor Applications", *IEEE Trans. Circuits Syst. II* (submitted).

- **Paper II P. Harikumar** and J. J. Wikner, "A 10-bit 50 MS/s SAR ADC in 65 nm CMOS with on-chip reference voltage buffer", *Elsevier Integration, the VLSI Journal*, vol. 50, pp. 28-38, June 2015.

- **Paper III P. Harikumar** and J. J. Wikner, "Design of a Sampling Switch for a 0.4 V SAR ADC Using a Multi-Stage Charge Pump", in *Proc. IEEE Norchip Conf.*, Tampere, Finland, pp. 1-4, Oct. 2014.

- **Paper IV P. Harikumar** and J. J. Wikner, "Design of a Reference Voltage Buffer for a 10 bit, 50 MS/s SAR ADC in 65 nm CMOS", in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Lisbon, Portugal, pp. 249-252, May 2015.

- **Paper V P. Harikumar**, J. J. Wikner, and A. Alvandpour, "A Fully-Differential OTA in 28 nm UTBB FDSOI CMOS for PGA Applications", in *Proc. European Conf. Circuit Theory and Design (ECCTD)*, Trondheim, Norway, pp. 1-4, Aug. 2015.

- Paper VI P. Harikumar, J. J. Wikner, and A. Alvandpour, "An Ultra-Low-Voltage OTA in 28 nm UTBB FDSOI CMOS Using Forward Body Bias", in *Proc. IEEE Nordic Circuits and Systems Conf. (NORCAS)*, Oslo, Norway, pp. 1-4, Oct. 2015.

- Paper VII P. Harikumar, P. Angelov, and R. Hägglund, "Design of a Reference Voltage Buffer for a 10-bit 1-MS/s SAR ADC", in *Proc. Int. Mixed Design of Integrated Circuits and Systems (MIXDES) Conf.*, Lublin, Poland, pp. 185-188, June 2014.

- **Paper VIII** S. A. Aamir, **P. Harikumar** and J. J. Wikner, "Frequency Compensation of High-Speed, Low-Voltage CMOS Multistage Amplifiers", in

*Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Beijing, China, pp. 381-384, May 2013.

Contribution: I designed a three-stage OTA in 40 nm CMOS and employed two frequency compensation schemes on it. I carried out the relevant simulations and played a major role in manuscript preparation. Aamir designed and simulated the four-stage OTA in 65 nm CMOS and was involved in manuscript preparation.

• **Paper IX** – **P. Harikumar**, M. I. Kazim, and J. J. Wikner, "An analog receiver front-end for capacitive body-coupled communication", in *Proc. IEEE Norchip Conf.*, Copenhagen, Denmark, pp. 1-4, Nov. 2012.

Contribution: I designed a two-stage OTA in 40 nm CMOS as well as the three AFE topologies. I carried out the necessary simulations and played a major role in manuscript preparation. The calculation of the noise level allowed for the AFE was provided by Jacob. Irfan was responsible for including the details of the human body electrical model and discrete transceiver realization.

The following papers were also published during this period which are outside the scope of this dissertation:

- K. Chen, P. Harikumar and A. Alvandpour, "Design of a 12.8 ENOB, 1 kS/s Pipelined SAR ADC in 0.35-μm CMOS", *Analog Integr. Circ. Sig. Process.*, 2015 (Accepted).

- M. Nielsen-Lönn, P. Harikumar, J. J. Wikner, and A. Alvandpour, "Design of Efficient CMOS Rectifiers for Integrated Piezo-MEMS Energy-Harvesting Power Management Systems", in *Proc. European Conf. Circuit Theory and Design (ECCTD)*, Trondheim, Norway, pp. 1-4, Aug. 2015.

## Acknowledgments

It has been an arduous, oft-enervating trek. I am beholden to those who helped me prevail.

- My grandmother H. Balambal for her selfless, doting love. She cossets me from within and awaits me at the egress from this earthly sojourn.

- My parents Dr. V. Thankamani and M. Harikumar for imbuing me with tenacity and rectitude that have stood me in good stead throughout my Ph.D. studies. Their boundless affection, foursquare support and sagacious precepts efface despondency and whet my resolve.

- My supervisor Dr. J Jacob Wikner who extended me a carte blanche on research albeit with a caveat on robustness and testability of the circuits. He never shoehorned me into confined perspectives, yet spurred me on with the celerity of his pithy emails. Completing his exacting Ph.D. courses is a badge of honour, akin to earning the beret from Fort Bragg, NC, USA.

- My co-supervisor Prof. Atila Alvandpour who reposed faith in my abilities and proffered several opportunities to parlay my skills. His candid and germane feedback ameliorated the quality of my work and manuscripts.

- The profound philosophical depth of the Hindu religion which exhorts "Thy right is only to act and not to its fruits. Let not the fruit of action be thy motive; nor let thy attachment be to inaction. (The Bhagavad Gita)"

- My uncle V. Murali who edified me through his life. He was and still remains virtues incarnate. Yet he was flagrantly shortchanged by God and mortals alike.

- Dr. Oscar Gustafsson and Prof. Håkan Johansson for providing me an opportunity to pursue Ph.D. studies.

- Dr. Darius Jakonis (Acreo AB, Sweden) for the numerous discussions regarding the 28 nm UTBB FDSOI CMOS process. Despite having no stake in my research, he responded with alacrity and zeal to my emails, and galvanized me to investigate the potential of this advanced process node.

- *Tongzhi* Dr. Dai Zhang for the countless technical discussions and resilient friendship. Her stellar accomplishments are snugly ensconced amidst her endearing humility and modesty. In the domain of ultra-low-power ADC design, I regard her as an exemplar worthy of emulation.

- Pavel Angelov (Fingerprint Cards AB, Sweden) who fortuitously shares his first name with the legendary Pavel. O. Sukhoi, for his munificence in sparing time for technical discussions. Such rendezvous disabused me of several misconceptions regarding ADC design and widened my horizons.

- Dr. Anu Kalidas with whom I cherish a fraternal bond, a bond forged between compatriots confronting bitter winters and daunting exams/labs in an alien land. Conferring with A. K. Das (one among his myriad noms de guerre) has been the perfect salve for my ruffled mind during these years.

- Dr. Ameya Bhide for his valuable advice on a slew of issues and for sharing the LaTeX template for his thesis.

- Martin Nielsen-Lönn (Ph.D. student, ICS), whose metiér spans the gamut of electronics from precision soldering and CAD to oscillosope-based Flappy-Pong, for the fruitful collaboration on the SMS and smartMemphis projects. To me, his indefatigable verve for troubleshooting remains an enigma.

- Kairang Chen (Ph.D. student, ICS) from Henan, the land of the warrior monks, for the unencumbered co-operation on the pipelined ADC work.

- Arta Alvandpour, Principal Research Engineer, ICS whose assistance ensured that we were in lockstep with Cadence<sup>®</sup> on the CAD tool versions.

- Dr. Manil Dev for the camaraderie that has endured the inexorable passage of time.

- My wife Sruthi Kodoth for her unswerving support and encouragement. Her sangfroid was an indispensable equipoise to my angst during the chip measurements. Sruthi's parents Sailaja Kodoth and M. Madhusoodhanan buttressed my efforts with genuine concern and fervent prayers.

Prakash Harikumar Linköping, Sep. 2015

## Contents

| 1 | Intr | oduction                                                | 1  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | Background                                              | 1  |

|   | 1.2  | Objectives                                              | 3  |

|   | 1.3  | Methodology                                             | 3  |

|   | 1.4  | Organization and Scope of Dissertation                  | 3  |

| 2 | Desi | gn Considerations for SAR ADCs and OTAs                 | 7  |

|   | 2.1  | SAR ADC Design Considerations                           | 7  |

|   |      | 2.1.1 Sample-and-Hold Circuit                           | 7  |

|   |      | 2.1.2 Capacitive DAC                                    | 13 |

|   |      | 2.1.3 Comparator                                        | 15 |

|   | 2.2  | OTA Design Challenges                                   | 17 |

|   |      | 2.2.1 Stabilization of OTAs                             | 19 |

|   | 2.3  | Features of the 28 nm UTBB FDSOI CMOS Process           | 25 |

|   |      | 2.3.1 Control of Threshold Voltage Using Body Bias      | 25 |

|   |      | 2.3.2 Intrinsic Gain of Transistors                     | 26 |

|   |      | 2.3.3 Boosting Transconductance Using Forward Body Bias | 27 |

|   | 2.4  | Summary                                                 | 28 |

| 3 | Desi | ign of a 0.4 V, sub-nW, 8-bit 1 kS/s SAR ADC            | 29 |

|   | 3.1  | Introduction                                            | 29 |

|   | 3.2  | ADC Architecture                                        | 30 |

|   | 3.3  | Circuit Implementation                                  | 31 |

|   |      | 3.3.1 Input Sampling Switch                             | 31 |

|   |      | 3.3.2 Capacitive Array DAC                              | 34 |

|   |      | 3.3.3 Dynamic Latch Comparator                          | 37 |

|   |      | 3.3.4 SAR Logic                                         | 38 |

|   | 3.4  | Measurement Results                                     | 40 |

|   | 3.5  | Ultra-low-power RC Oscillator                           | 45 |

|   | 3.6  | Summary                                                 | 49 |

| 4  |        | ign of a 10-bit 50 MS/s SAR ADC                             | 51  |

|----|--------|-------------------------------------------------------------|-----|

|    | 4.1    | Introduction                                                | 51  |

|    | 4.2    | Limitations for DAC Settling                                | 52  |

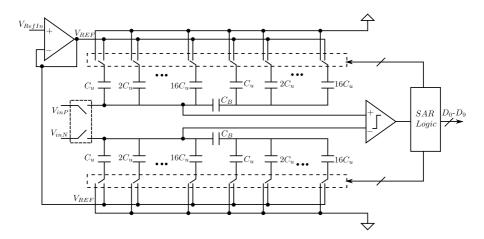

|    | 4.3    | ADC Architecture                                            | 53  |

|    | 4.4    | Implementation of ADC Building Blocks                       | 55  |

|    |        | 4.4.1 Reference Voltage Buffer                              | 55  |

|    |        | 4.4.2 Input Sampling Switches                               | 59  |

|    |        | 4.4.3 Dynamic Comparator                                    | 63  |

|    |        | 4.4.4 Split Binary-Weighted Array DAC                       | 65  |

|    |        | 4.4.5 SAR Controller                                        | 67  |

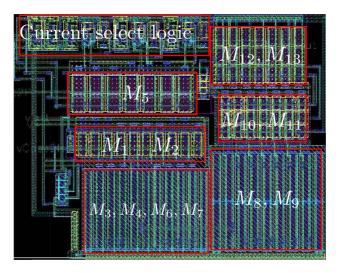

|    |        | 4.4.6 Layout of the ADC                                     | 69  |

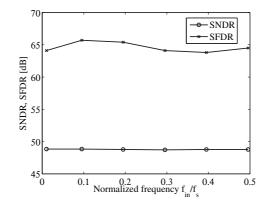

|    | 4.5    | Simulation Results                                          | 70  |

|    | 4.6    | Summary                                                     | 74  |

| 5  | Mix    | ed-Signal Interfaces                                        | 75  |

|    | 5.1    | Introduction                                                | 75  |

|    | 5.2    | A PGA for a 9 bit, 1 kS/s SAR ADC                           | 76  |

|    |        | 5.2.1 Performance Requirements                              | 76  |

|    |        | 5.2.2 Architecture                                          | 76  |

|    |        | 5.2.3 Common-mode Feedback                                  | 77  |

|    |        | 5.2.4 Simulation Results for the OTA                        | 78  |

|    | 5.3    | An Ultra-Low-Voltage OTA in 28 nm UTBB FDSOI CMOS           | 82  |

|    |        | 5.3.1 Ultra-low-voltage OTA Design                          | 83  |

|    |        | 5.3.2 OTA Architecture                                      | 83  |

|    |        | 5.3.3 Simulation Results                                    | 85  |

|    | 5.4    | Reference Voltage Buffer for a 10-bit 1-MS/s SAR ADC        | 91  |

|    |        | 5.4.1 Requirements on the RVBuffer                          | 91  |

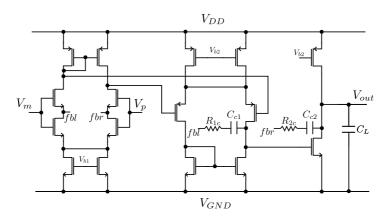

|    |        | 5.4.2 OTA Topology and Simulation Results                   | 92  |

|    |        | 5.4.3 Re-design of the RVBuffer                             | 96  |

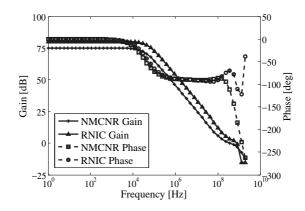

|    | 5.5    | Frequency Compensation of a Three-Stage OTA in 40 nm CMOS . | 97  |

|    |        | 5.5.1 RNIC Stabilization                                    | 97  |

|    |        | 5.5.2 NMCNR Stabilization                                   | 98  |

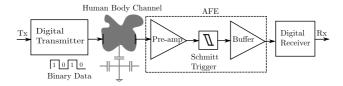

|    | 5.6    | A Receiver AFE for Capacitive Body-Coupled Communication    | 100 |

|    |        | 5.6.1 Requirements on the AFE                               | 100 |

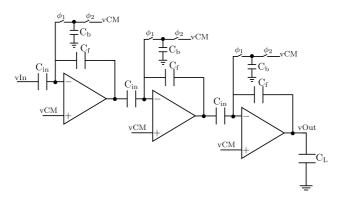

|    |        | 5.6.2 AFE Architecture                                      | 101 |

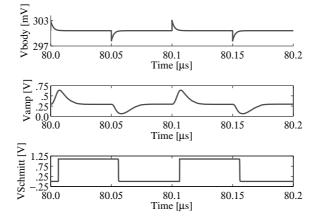

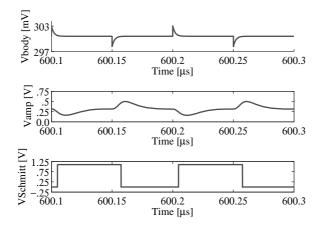

|    |        | 5.6.3 AFE Topologies and Simulation Results                 | 102 |

|    | 5.7    | Summary                                                     | 106 |

| 6  | Con    | clusions and Future Work                                    | 107 |

|    | 6.1    | Future Work                                                 | 108 |

| Re | eferen | ices                                                        | 109 |

#### A Paper Collection

121

# **List of Figures**

| 1-1  | Block diagram of a typical AFE and ADC                               | 2  |

|------|----------------------------------------------------------------------|----|

| 1-2  | Basic SAR ADC architecture.                                          | 2  |

| 2-1  | Basic S/H circuit.                                                   | 8  |

| 2-2  | Noise of the S/H circuit over PVT corners                            | 9  |

| 2-3  | Charge injection and clock feedthrough errors.                       | 9  |

| 2-4  | Impact of lower supply voltage on the $R_{ON}$ of a TG switch        | 11 |

| 2-5  | Variation of leakage current and threshold voltage with temperature. | 12 |

| 2-6  | Binary-weighted capacitive DAC.                                      | 13 |

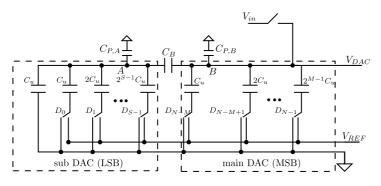

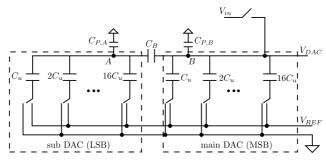

| 2-7  | Split-array capacitive DAC.                                          | 14 |

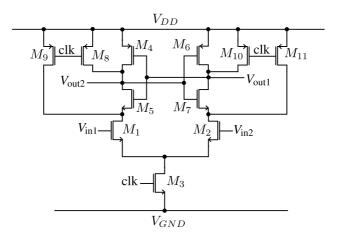

| 2-8  | Schematic of a dynamic comparator.                                   | 15 |

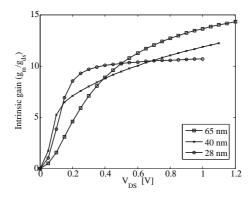

| 2-9  | Intrinsic gain vs. $V_{DS}$ in advanced CMOS process nodes           | 18 |

| 2-10 | Voltage headroom in a single-stage differential amplifier            | 18 |

|      | A single-stage OTA.                                                  | 20 |

| 2-12 | Simple Miller compensated (SMC) two-stage OTA.                       | 21 |

| 2-13 | Small-signal model of the SMC OTA.                                   | 22 |

| 2-14 | Simple Miller compensation with nulling resistor (SMCNR)             | 23 |

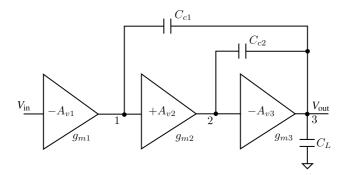

| 2-15 | A three-stage OTA with NMC                                           | 24 |

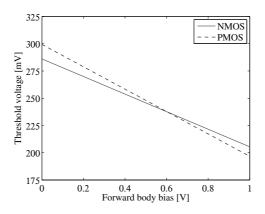

|      | Threshold voltage vs. forward body bias in low- $V_{TH}$ transistors | 26 |

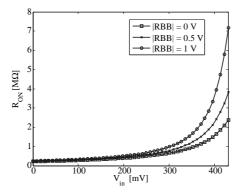

| 2-17 | Boosting $R_{ON}$ using reverse body bias                            | 26 |

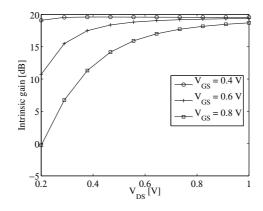

| 2-18 | Nominal intrinsic gain of minimum-sized LVT NMOS transistor          | 27 |

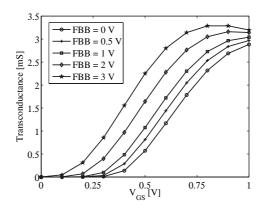

| 2-19 | Impact of forward body bias (FBB) on transconductance                | 27 |

| 3-1  | Block diagram of the proposed ADC.                                   | 30 |

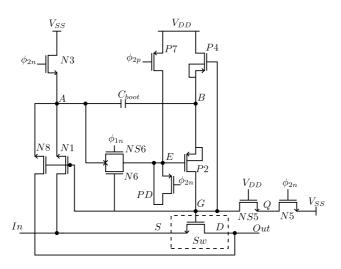

| 3-2  | Schematic of the multi-stage charge pump for the input S/H           | 32 |

| 3-3  | Schematic of the leakage-reduced S/H with multi-stage charge pump.   | 32 |

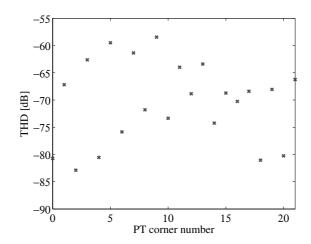

| 3-4  | THD performance of the S/H over process and temperature corners.     | 33 |

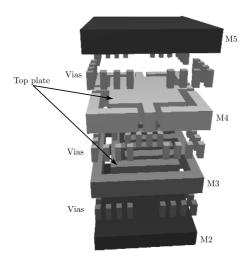

| 3-5  | Structure of the custom-designed unit capacitor.                     | 37 |

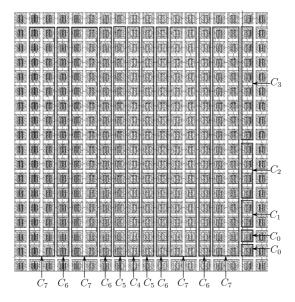

| 3-6  | Layout of the binary-weighted DAC.                                   | 38 |

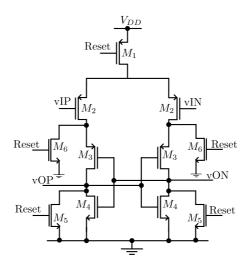

| 3-7  | Schematic of the dynamic latch comparator.                           | 39 |

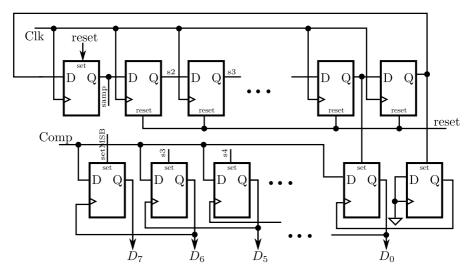

| 3-8  | Schematic of the synchronous SAR logic.                              | 39 |

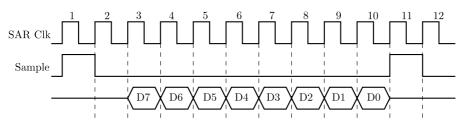

| 3-9        | Timing sequence for the synchronous SAR logic.                                | 40       |

|------------|-------------------------------------------------------------------------------|----------|

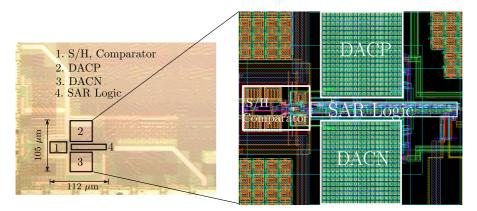

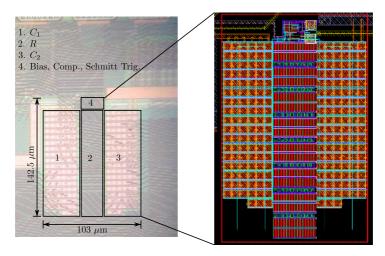

| 3-10       | Chip microphotograph and layout of the 8-bit SAR ADC                          | 40       |

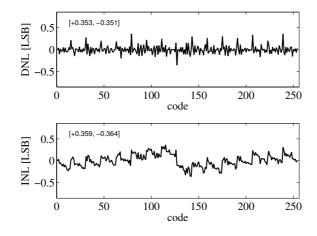

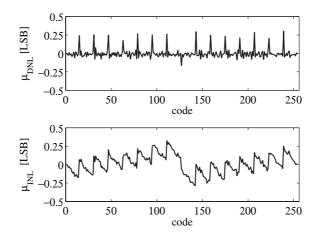

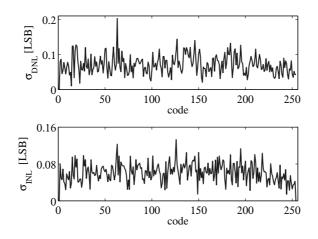

| 3-11       | Measured DNL and INL errors of the ADC                                        | 41       |

| 3-12       | Measured $\mu_{DNL}$ and $\mu_{INL}$ for seven ADC chips.                     | 41       |

| 3-13       | Measured $\sigma_{\text{DNL}}$ and $\sigma_{\text{INL}}$ for seven ADC chips. | 42       |

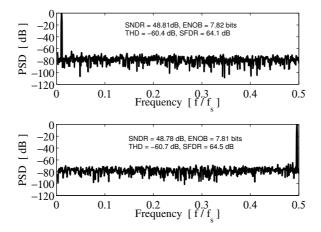

| 3-14       | Measured FFT spectrum (2048-point) for the ADC at 1 kS/s with                 |          |

|            | near-DC and near-Nyquist inputs.                                              | 42       |

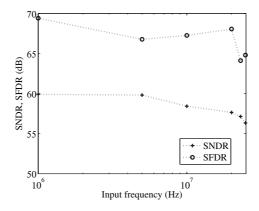

| 3-15       | Measured SNDR and SFDR of the ADC vs. input frequency                         | 43       |

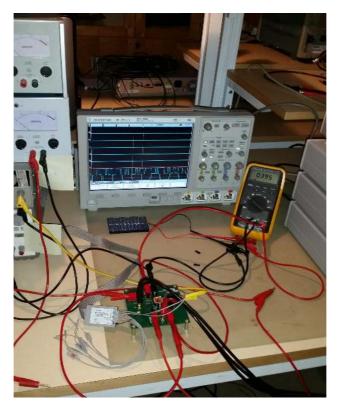

|            | ADC measurement set-up with solar panel.                                      | 44       |

| 3-17       | Schematic of the RC oscillator.                                               | 46       |

| 3-18       | Bias circuit for the RC oscillator.                                           | 46       |

| 3-19       | Variation of current vs. temperature for the bias circuit                     | 47       |

| 3-20       | Chip microphotograph and layout of the RC oscillator                          | 48       |

|            |                                                                               |          |

| 4-1        | The proposed SAR ADC architecture.                                            | 54       |

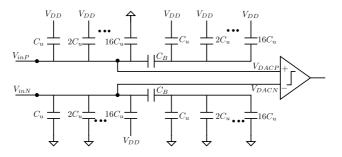

| 4-2        | Capacitive DAC during sampling phase of the SAR ADC                           | 54       |

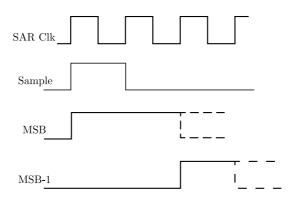

| 4-3        | Timing diagram for the sampling phase of the SAR ADC                          | 55       |

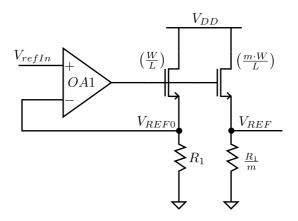

| 4-4        | Topology of the reference voltage buffer                                      | 59       |

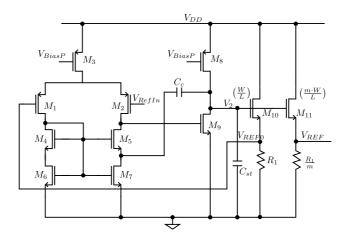

| 4-5        | Schematic of the reference voltage buffer                                     | 60       |

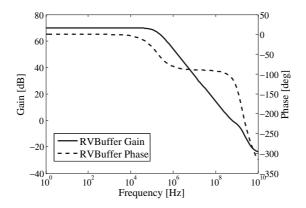

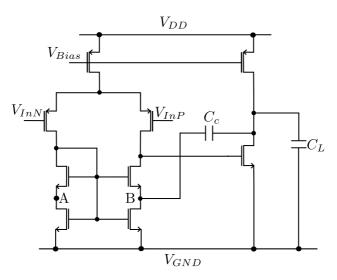

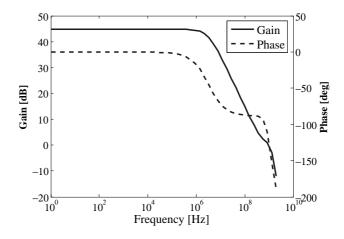

| 4-6        | Open-loop gain and phase plot for the RVBuffer.                               | 60       |

| 4-7        | Schematic of the constant- $g_m$ bias circuit                                 | 61       |

| 4-8        | Schematic of the bootstrapped switch.                                         | 62       |

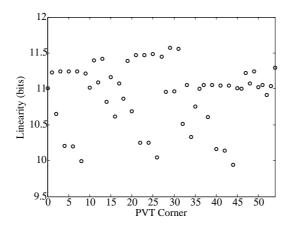

| 4-9        | Linearity performance of the bootstrapped switch                              | 63       |

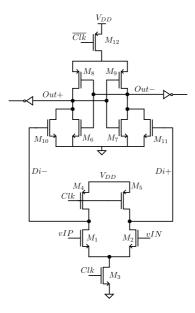

|            | Schematic of the double-tail dynamic comparator                               | 64       |

|            | Split-array DAC.                                                              | 65       |

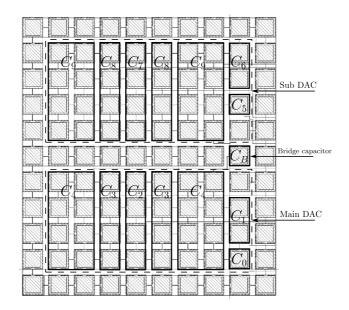

|            | Layout of the split-array DAC (single-side).                                  | 68       |

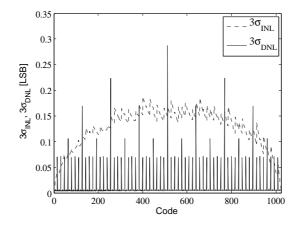

| 4-13       | INL/DNL of the 10-bit fully differential split-array DAC                      | 68       |

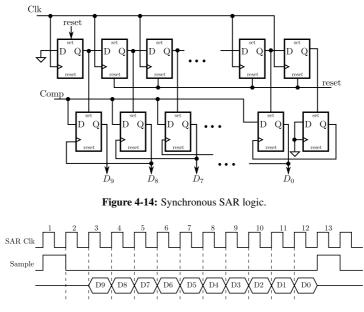

| 4-14       | Synchronous SAR logic.                                                        | 69       |

|            | Timing sequence of the SAR logic                                              | 69       |

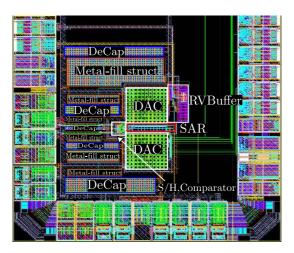

|            | Layout of the SAR ADC                                                         | 70       |

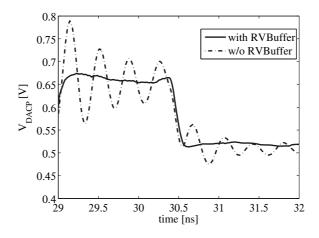

|            | Ringing on the DAC output due to inductance                                   | 71       |

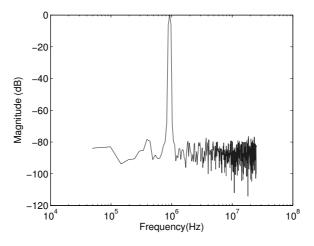

|            | Output spectrum of the SAR ADC for low-frequency input                        | 72       |

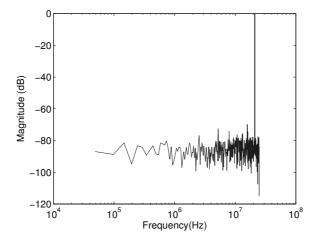

|            | Output spectrum of the SAR ADC for near-Nyquist input frequency               | 72       |

|            | Dynamic performance versus input frequency                                    | 73       |

| 4-21       | Power breakdown for the SAR ADC (typical PVT corner)                          | 73       |

| 5-1        | Schematic of the two-stage OTA                                                | 77       |

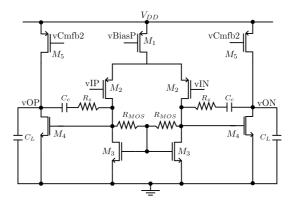

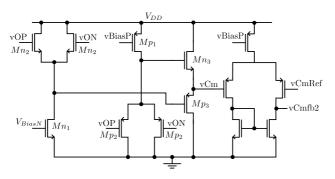

| 5-1<br>5-2 | CT CMFB for the second stage of the OTA.                                      | 78       |

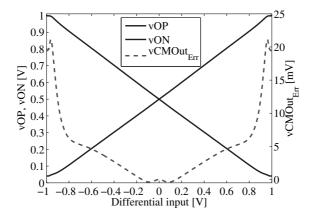

| 5-2<br>5-3 | Output signals and common-mode error for the OTA (closed-loop).               | 78<br>78 |

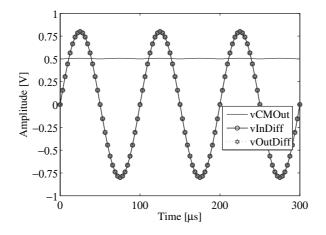

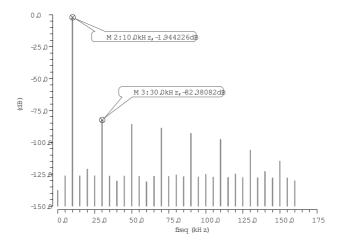

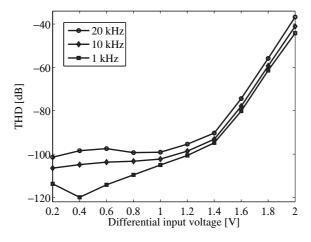

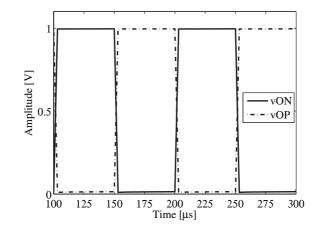

| 5-5<br>5-4 | Differential input, output and output CM level of the OTA.                    | 78<br>80 |

| 5-4<br>5-5 | DFT of the differential output of the OTA.                                    | 80<br>80 |

|            |                                                                               |          |

| 5-6        | THD vs. differential input voltage.                                           | 81       |

| 5-7        | Full-scale pulse outputs of the OTA.                                          | 81       |

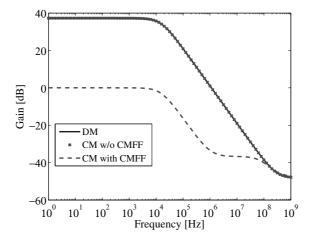

| 5-8  | Impact of CMFF on the CM gain of a pseudo-differential OTA    | 84  |

|------|---------------------------------------------------------------|-----|

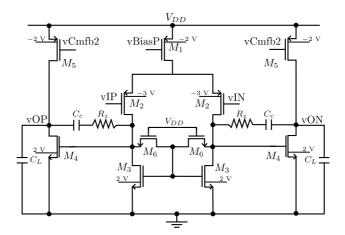

| 5-9  | Schematic of the two-stage OTA with FBB                       | 84  |

| 5-10 | Schematic of the second stage CT CMFB with FBB                | 85  |

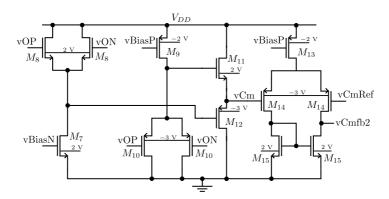

| 5-11 | Output voltages and output CM error voltage of the OTA        | 86  |

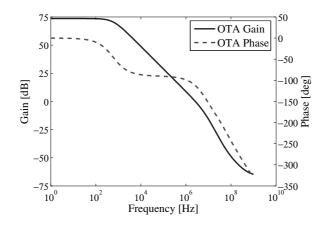

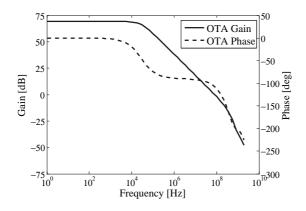

| 5-12 | Gain and phase plots of the OTA in open-loop                  | 87  |

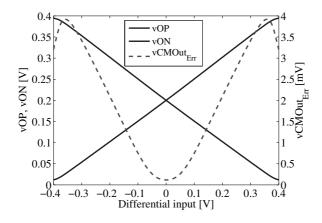

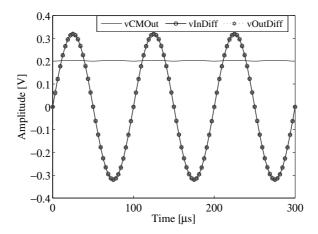

| 5-13 | Differential input, output and output CM voltages             | 87  |

| 5-14 | THD and differential output voltage vs. input voltage         | 88  |

| 5-15 | Full-scale differential input and output pulse voltages       | 89  |

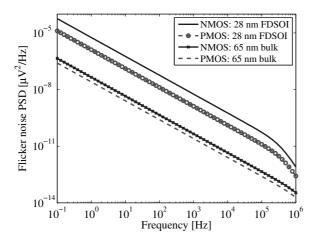

| 5-16 | Flicker noise comparison for 28 nm FDSOI and 65 nm bulk CMOS. | 90  |

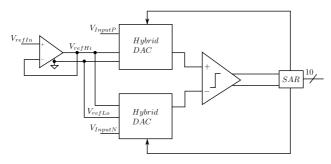

| 5-17 | Block diagram of the SAR ADC                                  | 91  |

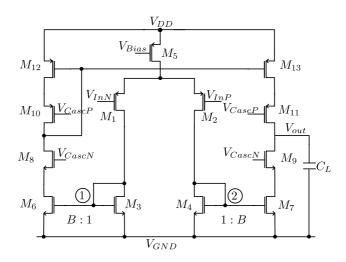

|      | Schematic of the PMOS-input RVBuffer                          | 93  |

|      | Gain-phase plot of the PMOS-input RVBuffer                    | 94  |

| 5-20 | Layout of the PMOS-input RVBuffer.                            | 96  |

| 5-21 | Schematic of the three-stage OTA with RNIC                    | 98  |

| 5-22 | Gain-phase plots of the three-stage OTA                       | 99  |

| 5-23 | Block diagram of the transceiver.                             | 100 |

|      | Schematic of the two-stage OTA                                | 102 |

| 5-25 | Gain-phase plot of the two-stage OTA                          | 103 |

| 5-26 | Schematic of the resistive-feedback AFE.                      | 104 |

| 5-27 | Schematic of the capacitive-feedback AFE.                     | 104 |

| 5-28 | Schematic of the capacitive-feedback AFE with SC bias         | 104 |

| 5-29 | Transient outputs for the capacitive feedback AFE.            | 105 |

| 5-30 | Transient outputs for the SC bias AFE                         | 106 |

|      |                                                               |     |

## **List of Tables**

| 3-1  | Multi-stage charge-pump performance over all PT corners | 33  |

|------|---------------------------------------------------------|-----|

| 3-2  | ADC performance summary and comparison.                 | 44  |

| 3-3  | Simulated performance of the RC oscillator.             | 48  |

| 3-4  | Measured performance of the RC oscillator.              | 48  |

| 4-1  | Performance summary of the reference voltage buffer     | 61  |

| 4-2  | Performance summary of the dynamic comparator           | 64  |

| 4-3  | Comparison to state-of-the-art works.                   | 74  |

| 5-1  | Performance of the OTA over PT corners.                 | 79  |

| 5-2  | Comparison to low-power OTAs.                           | 82  |

| 5-3  | Simulated performance of the OTA over PVT corners       | 88  |

| 5-4  | Comparison to ultra-low-voltage OTAs.                   | 90  |

| 5-5  | Simulated RVBuffer performance with NMOS capacitor load | 94  |

| 5-6  | Simulated performance of the RVBuffer                   | 95  |

| 5-7  | Pole-zero locations of the three-stage OTA with RNIC    | 98  |

| 5-8  | Pole-zero locations of the three-stage OTA with NMCNR   | 99  |

| 5-9  | Comparison of NMCNR and RNIC schemes.                   | 99  |

| 5-10 | Two-stage OTA performance summary.                      | 103 |

|      | Simulation results for the AFE configurations.          | 105 |

# **List of Abbreviations**

| ADC   | Analog-to-Digital Converter             |

|-------|-----------------------------------------|

| AFE   | Analog Front-End                        |

| BW    | Bandwidth                               |

| CMFB  | Common Mode FeedBack                    |

| CMFF  | Common Mode FeedForward                 |

| CMOS  | Complementary Metal Oxide Semiconductor |

| CS    | Common Source                           |

| СТ    | Continuous Time                         |

| DAC   | Digital-to-Analog Converter             |

| DFF   | D-Flip Flop                             |

| DFT   | Discrete Fourier Transform              |

| DNL   | Differential NonLinearity               |

| ENOB  | Effective Number of Bits                |

| ERBW  | Effective Resolution Bandwidth          |

| FBB   | Forward Body Bias                       |

| FDSOI | Fully Depleted Silicon-On-Insulator     |

| FFT   | Fast Fourier Transform                  |

| FF    | Flip Flop                               |

| FoM   | Figure of Merit                         |

| FS                                                               | Full Scale                                                                                                                                                                                                                                        |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GBW                                                              | Gain-BandWidth product                                                                                                                                                                                                                            |

| HD <sub>n</sub>                                                  | Harmonic Distortion of n <sup>th</sup> -order                                                                                                                                                                                                     |

| IA                                                               | Instrumentation Amplifier                                                                                                                                                                                                                         |

| INL                                                              | Integral NonLinearity                                                                                                                                                                                                                             |

| JLCC                                                             | J-Leaded Chip Carrier                                                                                                                                                                                                                             |

| LHP                                                              | Left Half Plane                                                                                                                                                                                                                                   |

| LSB                                                              | Least Significant Bit                                                                                                                                                                                                                             |

| MIM                                                              | Metal-Insulator-Metal                                                                                                                                                                                                                             |

| МОМ                                                              | Metal-Oxide-Metal                                                                                                                                                                                                                                 |

| MSB                                                              | Most Significant Bit                                                                                                                                                                                                                              |

| NMCNR                                                            | Nested Miller Compensation with Nulling Resistor                                                                                                                                                                                                  |

| NMC                                                              | Nested Miller Compensation                                                                                                                                                                                                                        |

| ОТА                                                              | Operational Transconductance Amplifier                                                                                                                                                                                                            |

| OIA                                                              | Operational Transconductance Amplifier                                                                                                                                                                                                            |

| PDK                                                              | Process Design Kit                                                                                                                                                                                                                                |

| -                                                                |                                                                                                                                                                                                                                                   |

| PDK                                                              | Process Design Kit                                                                                                                                                                                                                                |

| PDK<br>PGA                                                       | Process Design Kit<br>Programmable Gain Amplifier                                                                                                                                                                                                 |

| PDK<br>PGA<br>PT                                                 | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature                                                                                                                                                                      |

| PDK<br>PGA<br>PT<br>PVT                                          | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature                                                                                                                                  |

| PDK<br>PGA<br>PT<br>PVT<br>RBB                                   | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature<br>Reverse Body Bias                                                                                                             |

| PDK<br>PGA<br>PT<br>PVT<br>RBB<br>RHP                            | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature<br>Reverse Body Bias<br>Right Half Plane                                                                                         |

| PDK<br>PGA<br>PT<br>PVT<br>RBB<br>RHP<br>RNIC                    | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature<br>Reverse Body Bias<br>Right Half Plane<br>Reversed Nested Indirect Compensation                                                |

| PDK<br>PGA<br>PT<br>PVT<br>RBB<br>RHP<br>RNIC<br>RVBuffer        | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature<br>Reverse Body Bias<br>Right Half Plane<br>Reversed Nested Indirect Compensation<br>Reference Voltage Buffer                    |

| PDK<br>PGA<br>PT<br>PVT<br>RBB<br>RHP<br>RNIC<br>RVBuffer<br>S/H | Process Design Kit<br>Programmable Gain Amplifier<br>Process and Temperature<br>Process, Voltage and Temperature<br>Reverse Body Bias<br>Right Half Plane<br>Reversed Nested Indirect Compensation<br>Reference Voltage Buffer<br>Sample-and-Hold |

| SF    | Source Follower                                  |

|-------|--------------------------------------------------|

| SLCL  | Split Length Current mirror Load                 |

| SMCNR | Simple Miller Compensation with Nulling Resistor |

| SMC   | Simple Miller Compensation                       |

| SNDR  | Signal-to-Noise-and-Distortion Ratio             |

| SNR   | Signal-to-Noise Ratio                            |

| SoC   | System-on-Chip                                   |

| TG    | Transmission Gate                                |

| THD   | Total Harmonic Distortion                        |

| UTBB  | Ultra-Thin Box and Body                          |

| WSN   | Wireless Sensor Network                          |

### Chapter 1

## Introduction

#### 1.1 Background

Analog-to-digital converters (ADCs) are crucial blocks which form the interface between the physical world and the digital domain. ADCs are indispensable in numerous applications such as sensor networks, wireless/wireline communication receivers and data acquisition systems. Wireless sensor networks (WSNs) are increasingly employed for environmental and structural health monitoring, military surveillance and personal health monitoring [1]. Each sensor node in the WSN consists of a sensor, ADC, digital control logic and storage as well as a radio to relay the data to a central base station. To achieve long-term, autonomous operation, the nodes are powered by harvesting energy from ambient sources such as solar energy, vibrational energy etc. Such energy-constrained operation makes it imperative for the WSN electronics including the ADC to have minimum power consumption. Since the signal frequencies in these distributed WSNs are often low, ultra-low-power ADCs with low sampling rates are required. In wireless communication receivers, ADCs convert the received analog signal for subsequent digital processing. The advent of new wireless standards with ever-increasing data rates and bandwidth necessitates ADCs capable of meeting the demands. Wireless standards such as GSM, GPRS, LTE and WLAN require ADCs with several tens of MS/s speed and moderate resolution (8-10 bits) [2]. Since these ADCs are incorporated into battery-powered portable devices such as cellphones and tablets, low power consumption for the ADCs is essential.

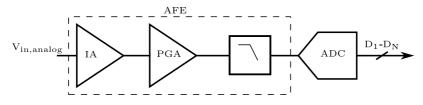

Figure 1-1 shows the block diagram of a typical analog front-end (AFE) along with the succeeding ADC. The instrumentation amplifier (IA) achieves rejection of common-mode disturbances with low input-referred noise [3]. The programmable gain amplifier (PGA) provides sufficient amplification to the input signal in order to maximize the dynamic range of the succeeding ADC. The PGA must possess fast settling time to drive the input sampling capacitance of the ADC. The low-pass filter

Figure 1-1: Block diagram of a typical AFE and ADC .

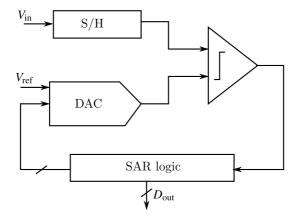

Figure 1-2: Basic SAR ADC architecture.

(LPF) performs the anti-aliasing function. For proper functionality, the ADC requires other peripheral blocks such as stable reference voltages and associated drivers, clock signal generator etc.

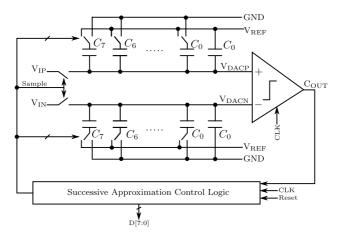

Figure 1-2 shows the block diagram of the basic SAR ADC architecture. It consists of a sample-and-hold block (S/H), a comparator, DAC and a successive approximation register (SAR). Each conversion consists of a sampling phase followed by the bit cycling phases. During the sampling phase, the input voltage is sampled. The successive-approximation register is set such that the output of the DAC is half of the reference voltage  $V_{ref}$ . In the initial bit cycle, the comparator compares the input voltage to  $V_{ref}/2$  in order to determine the most significant bit (MSB). The comparator output is stored in the SAR logic. Simultaneously, the SAR controller generates the next bit approximation. The DAC forms the corresponding scaled value of  $V_{ref}$  and the comparator compares the input voltage to the new value of the DAC output. The MSB-1 bit is thus determined. The bit cycles are repeated until all the bits upto the least significant bit (LSB) are determined.

In Fig. 1-2, if the comparator is implemented by a regenerative latch [4], then no static bias currents are required in the ADC which leads to excellent power-efficiency. Due to the fully dynamic nature of the SAR ADC, the power consumption scales

with the sampling frequency. High-performance pipelined ADCs require linear, high gain opamps that are increasingly challenging to design in advanced CMOS process nodes with low supply voltages. Since the SAR ADC does not require opamps, it has proven to be a very scaling-friendly architecture [5]. In recent years, SAR ADCs have been the subject of intense research and have become renowned for their power efficiency [6,7]. Hence this architecture was chosen for the ADC implementations described in this dissertation.

### 1.2 Objectives

The dissertation involves the following objectives.

- Design and implement an ultra-low-voltage ADC with power consumption less than 1 nW for WSNs.

- Design and implement a 10-bit, 50 MS/s SAR ADC with on-chip reference voltage buffer (RVBuffer). Identify the design challenges and suitable circuit topology for the buffer. Ensure that the various performance specifications of the RVBuffer are satisfied.

- Design power-efficient operational transconductance amplifiers (OTAs) for applications such as RVBuffer, PGA and AFEs. Determine the impact of advanced CMOS process nodes and frequency compensation schemes on OTA performance.

### 1.3 Methodology

The adopted methodology consists of an initial literature survey to identify appropriate circuit topologies and state-of-the-art performance. Based on the targeted system specification, the performance parameters for the constituent circuit blocks were derived. Subsequently, the design of these circuit blocks were commenced. Combining circuit techniques from different publications as well as modification of conventional circuit topologies were utilized to optimize the design. Simulation scenarios encompassed process corners, supply voltage variation and the relevant temperature range.

### 1.4 Organization and Scope of Dissertation

As delineated in Section 1.1, power-efficient ADCs are required in WSNs and in portable communication devices. Such ADCs will be part of System-on-Chips (SoC) implemented in advanced CMOS process nodes to take advantages of the benefits of scaling for the digital blocks. As the supply voltage reduces concomitantly with

4\_\_\_\_\_

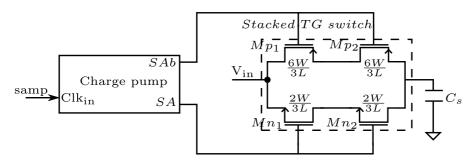

the reduction in feature size, the ADCs should meet the targeted performance at low supply voltages ( $V_{DD} \leq 1.2$  V). In this dissertation, an ultra-low-power 8-bit, 1 kS/s SAR ADC has been designed and fabricated in a 65 nm CMOS process. At  $V_{DD} = 0.4$  V, the ADC consumes 717 pW and achieves an FoM = 3.19 fJ/conv-step while meeting the targeted dynamic and static performance. It is very challenging to achieve an FoM < 5 fJ/conv-step for SAR ADCs with sampling rates in the range of 1 kS/s to 10 kS/s due to the substantial leakage power consumption [8]. The 8-bit ADC features a leakage-suppressed S/H circuit with boosted control voltage. The proposed S/H circuit is superior to conventional bootstrap/boosted switches and achieves > 9-bit linearity over process and temperature corners. The capacitive DAC is a crucial block that determines linearity performance, power and area of a SAR ADC. Instead of employing DAC switching schemes which suffer signal-dependent offset [9], additional voltages and switches [10], or increased number of capacitors and complex SAR logic [11], a conventional binary-weighted array DAC is employed with very low, custom-designed unit capacitors. Consequently the area of the ADC and power consumption are reduced while meeting INL/DNL specifications.

In this dissertation, the SAR architecture has been utilized to design and implement a 1.2 V, 10 bit, 50 MS/s SAR ADC in 65 nm CMOS aimed at communication applications. Accurate settling of the DAC voltage is essential to meet the performance in a charge-redistribution SAR ADC. For medium-to-high sampling rates, the DAC reference settling poses a speed bottleneck due to ringing associated with the parasitic inductances. In SAR ADCs embedded in SoCs, a high-speed buffer has to be incorporated to supply a stable reference voltage for the DAC. Although SAR ADCs have been the subject of intense research in recent years, scant attention has been laid on the design of high-performance on-chip RVBuffers. The few existing works [12] emphasize only the dominant power consumption of the buffer. The estimation of important design parameters of the buffer as well critical specifications such as PSRR, output noise, offset, settling time and stability have been elaborated upon in this dissertation. The implemented RVbuffer consists of a two-stage OTA combined with replica source-follower (SF) stages. The 10-bit SAR ADC utilizes split-array capacitive DACs to reduce area and power consumption. A constant- $q_m$  bias circuit with external resistor generates the biasing voltage for the buffer. A bootstrapped sampling switch maintains > 10-bit linearity over all PVT corners. In post-layout simulation which includes the entire pad frame and associated parasitics, the ADC achieves an ENOB of 9.25 bits at a supply voltage of 1.2 V, typical process corner and sampling frequency of 50 MS/s for near-Nyquist input. Excluding the reference voltage buffer, the ADC consumes 697  $\mu$ W and achieves an energy efficiency of 25 fJ/conversion-step while occupying a core area of 0.055 mm<sup>2</sup>.

The OTA is a key building block of mixed-signal processing systems. Due to the lower output resistance of transistors and low supply voltages in scaled CMOS technologies, the design of OTAs with adequate open loop DC gain, unity-gain frequency, output swing and linearity presents a formidable challenge. Techniques

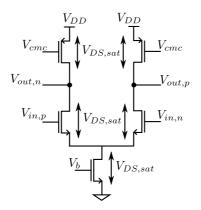

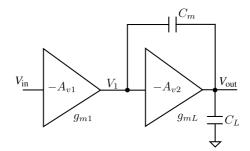

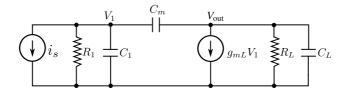

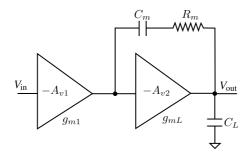

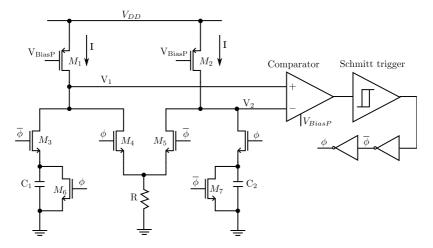

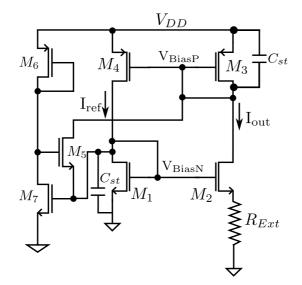

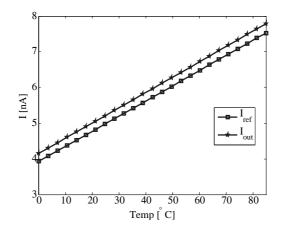

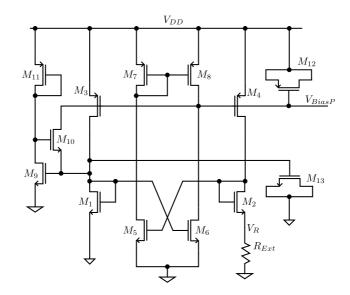

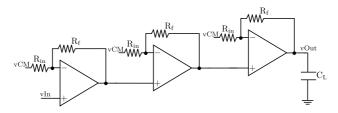

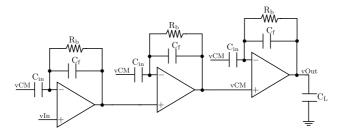

such as cascoding become less feasible and hence cascading multiple stages to achieve the targeted DC gain has emerged as an attractive design choice. However, the frequency compensation technique in multi-stage OTAs has to be appropriately chosen to achieve power efficiency and higher speed. The useful features of advanced CMOS process nodes such as 28 nm UTBB FDSOI CMOS can be enlisted to overcome the constraints imposed by low supply voltage and reduced intrinsic gain. A 1 V, fully differential OTA which satisfies the demanding specifications of a PGA for a 9-bit SAR ADC has been designed which supports rail-to-rail output swing and provides DC gain = 70 dB, unity-gain frequency = 4.3 MHz and phase margin =  $68^{\circ}$ while consuming 2.9  $\mu$ W. Crucial specifications for the PGA such as settling time and linearity are also satisfied over all process corners and a temperature range of [-20°C +85°C]. Since FBB in the 28 nm FDSOI process allows wide tuning of the threshold voltage and substantial boosting of the transconductance, an ultra-lowvoltage fully differential OTA with  $V_{DD} = 0.4$  V has been designed to satisfy the comprehensive specifications of a general-purpose OTA while limiting the power consumption to 785 nW. A power-efficient RV buffer has been implemented in 1.8 V, 180 nm CMOS for a 10-bit, 1 MS/s SAR ADC in an industrial fingerprint sensor SoC. The RVbuffer utilizes a single-stage, cascoded current-mirror OTA which minimizes current consumption, enhances PSRR and obviates frequency compensation while meeting the requirements on DC gain and settling speed. Even though numerous frequency compensation schemes for OTAs driving large capacitive loads have been proposed, their impact on high-speed, low capacitive-load OTAs in advanced CMOS nodes has not been studied in detail. Hence two previously-published frequency compensation schemes are compared on the basis of unity-gain frequency and phase margin on a three-stage OTA designed in 1.1 V, 40 nm CMOS process. Simulation results highlight the benefits of split-length indirect compensation over the nested Miller compensation scheme. An AFE satisfying the requirements for a capacitive body-coupled communication receiver has been designed in 1.1 V, 40 nm CMOS. The AFE consists of a cascade of three amplifiers followed by a Schmitt trigger and digital buffers. The amplifiers utilize a two-stage OTA with split-length compensation. Three AFE topologies were simulated and compared in terms of noise, gain and power consumption. The rest of the dissertation is organized as follows.

- Chapter 2 discusses the design considerations for low-voltage SAR ADCs and OTAs.

- **Chapter 3** presents the design and implementation of a 0.4 V, 717 pW, 8-bit 1 kS/s SAR ADC in 65 nm CMOS for wireless sensor network applications. This chapter is based on **Paper I** and **Paper III**.

- **Chapter 4** presents the design and implementation of a 10-bit, 50 MS/s SAR ADC with an on-chip reference voltage buffer in 65 nm CMOS. This chapter is based on **Paper II** and **Paper IV**.

- Chapter 5 presents the work on the design of mixed-signal interfaces with a focus on OTAs. This chapter is based on Paper V–Paper IX. Utilizing the beneficial features of the 28 nm UTBB FDSOI CMOS process, a PGA for a 9-bit SAR ADC (Paper V) and an ultra-low-voltage OTA (Paper VI) have been designed. A power-efficient reference voltage buffer has been designed for a 10-bit embedded SAR ADC in a fingerprint sensor (Paper VII). Frequency compensation techniques for a three-stage OTA and a receiver AFE for body coupled communication in 40 nm CMOS are described in Paper VIII and Paper IX respectively.

- Chapter 6 presents a conclusion and outlines the directions for future work.

Finally, Appendix A provides a copy of the published papers for a quick reference.

### **Chapter 2**

# **Design Considerations for SAR ADCs and OTAs**

This chapter describes the important design considerations for SAR ADCs and multistage amplifiers. The performance requirements of the crucial blocks in a SAR ADC and their associated design challenges are elaborated upon. Owing to the low intrinsic gain of transistors in advanced CMOS process nodes, multi-stage amplifiers with two or more stages are gaining popularity in mixed-signal systems. A discussion on frequency compensation of multi-stage amplifiers is included. The features of advanced process nodes such as the 28 nm ultra-thin box and body (UTBB) fully depleted silicon-on-insulator (FDSOI) CMOS process can be utilized to overcome performance bottlenecks and achieve significant trade-offs in power consumption vs. performance. Useful features of the 28 nm UTBB FDSOI CMOS process are also delineated.

#### 2.1 SAR ADC Design Considerations

This section describes the non-idealities and design trade-offs in the sub-blocks of the SAR ADC such as the sample-and-hold (S/H) circuit, capacitive DAC and comparator.

#### 2.1.1 Sample-and-Hold Circuit

The S/H circuit plays a critical role in determining the performance of the SAR ADC. The thermal noise associated with the sampling process degrades the SNR of the ADC. Nonlinear variation of the ON-resistance, signal dependent charge injection, and leakage are other non-idealities of the sampling switch that degrade the performance of the ADC.

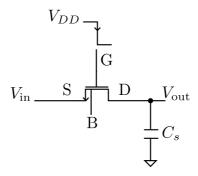

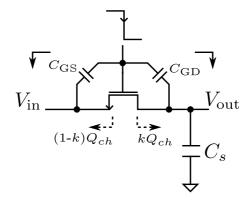

Figure 2-1: Basic S/H circuit.

#### 2.1.1.1 Thermal Noise

The basic S/H circuit consists of a MOS transistor switch and a capacitor as shown in Fig. 2-1. During the tracking phase, when the switch is ON, the NMOS device approximates a linear resistor. The thermal noise of the MOS transistor is sampled on the capacitor  $C_s$ . For an N-bit ADC with a full-scale input voltage of  $V_{\rm FS}$ , the quantization noise power is given by

$$P_{\rm Q} = \frac{V_{\rm FS}^2}{12\ 2^{2N}}.\tag{2.1}$$

If the thermal noise of the sampler is designed to be equal to the quantization noise power, a 3 dB degradation in SNR will be incurred. In such a scenario, the value of the total sampling capacitance is given by

$$C_{\rm s} = 12kT \frac{2^{2N}}{V_{\rm FS}^2}.$$

(2.2)

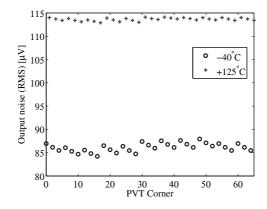

Assuming  $V_{\rm FS} = 1$  V, and N = 10 bits, a minimum sampling capacitance of 52 fF will be needed to satisfy (2.2) at room temperature. However, in reality, the sampling capacitance is chosen such that the thermal noise contribution is much lower than the quantization noise so as to minimize the SNR degradation. It is worth noting that the S/H noise given by  $kT/C_s$  is significantly impacted by the change in temperature. For the bootstrapped S/H circuit with a  $C_s = 480$  fF reported in [13], the simulated output noise over the entire set of process, supply voltage and temperature (PVT) corners is shown in Fig. 2-2. A supply voltage variation of  $\pm 10\%$  and temperature range of  $[-40^{\circ}\text{C} + 125^{\circ}\text{C}]$  were utilized for the simulation. The computed value of the output noise  $V_{noise,RMS} = \sqrt{\frac{kT}{C_s}}$  is 82  $\mu$ V and 107  $\mu$ V at  $-40^{\circ}\text{C}$  and  $+125^{\circ}\text{C}$  respectively. From Fig. 2-2, it is seen that the simulation results closely match the theoretical values. Also the process and supply voltage variations have negligible

Figure 2-2: Noise of the S/H circuit over PVT corners.

Figure 2-3: Charge injection and clock feedthrough errors.

influence on the output noise of the S/H circuit.

#### 2.1.1.2 Charge Injection and Clock Feedthrough

Charge injection and clock feedthrough are error sources associated with the sampling switch. When the switch turns off at the start of the hold phase, the charge in the conduction channel of the MOS transistor is injected into the drain and source nodes which perturbs the sampled value on the capacitor. Clock feedthrough refers to the coupling of the gate control signal of the switch through the parasitic capacitance to the output node. Both these error sources are shown in Fig. 2-3. The combined error voltage due to the two phenomena in an NMOS and PMOS switch are given by [14]

$$\Delta V_{\text{err,NMOS}} = \frac{-kW_N L_N C_{\text{ox}} (V_{DD} - V_{\text{THN}} - V_{\text{IN}})}{C_{\text{s}}} - \frac{C_{\text{GD,NMOS}}}{C_{\text{s}} + C_{\text{GD,NMOS}}} V_{DD}, \quad (2.3)$$

$$\Delta V_{\text{err,PMOS}} = \frac{kW_P L_P C_{\text{ox}}(V_{\text{IN}} - |V_{\text{THP}}|)}{C_{\text{s}}} + \frac{C_{\text{GD,PMOS}}}{C_{\text{s}} + C_{\text{GD,PMOS}}} V_{DD}, \qquad (2.4)$$

where k is the fraction of the charge injected on the output node,  $C_{ox}$  is the gate-oxide capacitance,  $V_{THN}$  and  $V_{THP}$  are the threshold voltages, and  $C_{GD,NMOS}$ ,  $C_{GD,PMOS}$  are the gate-drain overlap capacitance of the NMOS and PMOS respectively. In (2.3) and (2.4), the first part represents the charge-injection error. It is seen that the charge injection error has a linear dependency on the input signal which causes nonlinearity. An obvious way to reduce charge injection error is to use a larger sampling capacitor  $C_s$ . However, this impacts the speed and power consumption adversely. Charge injection error can also be mitigated by circuit techniques such as dummy switch and bottom-plate sampling. Clock feedthrough error represented by the second part in (2.3) and (2.4) contributes an offset. It can be alleviated by adopting a fully-differential topology for the converter.

#### 2.1.1.3 Tracking Bandwidth

During the tracking phase of the S/H circuit, the MOS transistor is turned ON in the linear region with an ON-resistance  $R_{ON}$  and the S/H circuit constitutes a simple RC filter. The primary source of non-linearity in the S/H circuit is the input-dependent variation of  $R_{ON}$ . An N-bit SAR ADC with a sampling rate of  $f_s$  uses an internal clock frequency  $f_{sys} = (N + 1)f_s$ . Assuming a half clock cycle period of  $f_{sys}$  for settling of the S/H circuit output gives the settling time as

$$t_s = \frac{1}{2f_{sys}}.$$

(2.5)

For an *N*-bit ADC to achieve sufficient performance, the settling error at the output of the S/H circuit must be  $\langle LSB/2$  [15] where LSB is the voltage corresponding to the least significant bit of the ADC. Utilizing the voltage settling expression for a single-pole RC filter with a time constant  $\tau$ , we require

$$e^{\frac{-t_s}{\tau}} < 2^{-(N+1)}.$$

(2.6)

The time-constant  $\tau$  can be expressed as

$$\tau = \frac{1}{2\pi f_{3dB}},\tag{2.7}$$

where  $f_{3dB}$  is the -3 dB bandwidth of the RC filter formed by the S/H circuit. Let  $C_s$  be the sampling capacitance of the ADC that constitutes the load for the sampling

Figure 2-4: Impact of lower supply voltage on the  $R_{ON}$  of a TG switch.

switch. Then the  $f_{3dB}$  of the S/H circuit can be expressed as

$$f_{3dB} = \frac{1}{2\pi R_{ON}C_s}.$$

(2.8)

Re-arranging (2.6) and substituting for  $t_s$  and  $\tau$  using (2.5) and (2.7) respectively results in

$$f_{3dB} \ge \frac{(N+1)\ln 2}{\pi} f_{sys}.$$

(2.9)

From (2.8) and (2.9), it is evident that, for a given value of  $C_s$ , an upper-bound is set on the  $R_{ON}$  of the S/H circuit to satisfy the targeted ADC performance.

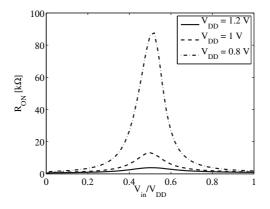

A lower supply voltage reduces the available gate-overdrive for the MOS switches in the S/H circuit leading to increased values for  $R_{ON}$  and consequent degradation in linearity. The impact of lowering the supply voltage on the  $R_{ON}$  of a transmission-gate (TG) S/H circuit in a 65 nm CMOS process is illustrated in Fig. 2-4. The TG switch uses standard- $V_{TH}$  devices with  $(W/L)_N = (1.2 \ \mu m/.12 \ \mu m)$ and  $(W/L)_P = (2.4 \ \mu m/.12 \ \mu m)$  For ultra-low-voltage applications, conventional bootstrapping [16] proves inadequate to overcome this limitation, and hence doublebootstrapping [17] or cascade of charge pumps [18–20] are often employed. It is worth noting that there exists a trade-off between the number of charge pump stages in the cascade and the deterioration in voltage boosting due to parasitic capacitances [19].

#### 2.1.1.4 Impact of Leakage

Even though the S/H circuit will remain OFF during the bit conversion cycles in the SAR ADC, subthreshold leakage in the transistors will cause the sampled voltage to

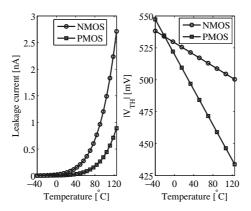

Figure 2-5: Variation of leakage current and threshold voltage with temperature.

droop. The subthreshold current is given by [21]

$$I_{\rm DS} = \mu_0 C_{\rm ox} \frac{W}{L} (m-1) V_{\rm T}^2 e^{\frac{V_{\rm CS} - V_{\rm TH}}{mV_{\rm T}}} (1 - e^{\frac{-V_{\rm DS}}{V_{\rm T}}}), \qquad (2.10)$$

where  $V_{\rm TH}$  is the threshold voltage,  $V_{\rm T} = kT/q$  is the thermal voltage,  $C_{\rm ox}$  is the gate oxide capacitance,  $\mu_0$  is the zero-bias mobility and m is the subthreshold swing coefficient. Another contributor is the gate leakage current which occurs due to the high electric field across the gate oxide and the low oxide thickness. Major constituents of gate leakage are gate oxide tunneling and injection of hot carriers from substrate to the gate oxide [21]. In analog and mixed-signal circuits working at very low frequencies, the leakage power forms a significant portion of the total power consumption. The sub-threshold leakage current depends on the voltage across the switch as seen in (2.10) and hence causes harmonic distortion at the ADC output [20, 22]. This problem is particularly acute in SAR ADCs with low sampling rates. With bottom-plate input sampling, the leakage of the S/H switches is not a major concern since the bottom-plate nodes of the DAC capacitors will be connecting to the reference voltages. However, bottom-plate input sampling technique is not suitable for ultra-low voltage SAR ADCs since a large number of charge-pump based switches will be required. Leakage-suppression is achieved in top-plate S/H circuits using device-stacking [22], employment of high- $V_{TH}$  devices [20], negative body bias [19], negative gate bias [23] or a combination of these techniques. For the MOS transistors, the subthreshold leakage current increases with temperature while the threshold voltage reduces with temperature. For minimum-sized, standard- $V_{TH}$ devices in 65 nm CMOS, the variation of leakage current and  $V_{TH}$  with temperature are shown in Fig. 2-5. Hence the worst leakage PVT condition must be considered to satisfy robust S/H performance. Paper I implements a leakage-reduced switch with

Figure 2-6: Binary-weighted capacitive DAC.

a multi-stage charge pump for a 0.4 V, 8-bit SAR ADC while **Paper II** describes a bootstrapped switch for a 1.2 V, 10-bit SAR ADC.

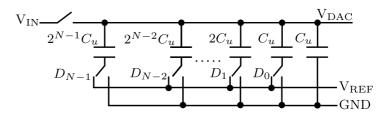

#### 2.1.2 Capacitive DAC

The capacitive DAC in the SAR ADC provides feedback of the scaled reference voltage based on the control bits from the SAR logic. The capacitive array DAC is preferred to the resistor string DAC because of the improved matching properties of capacitors and the absence of static power dissipation. Figure 2-6 shows an Nbit conventional binary-weighted capacitive array DAC. Mismatches between the capacitors in the DAC as well as parasitic capacitances in the DAC layout cause nonlinearity at the ADC output and thus limit the INL, DNL performance of the SAR ADC. To reduce mismatch effects, the entire DAC capacitor array is constructed using multiples of a unit capacitor  $C_u$ . The capacitive DAC is usually laid out in commoncentroid configuration to cancel global errors such as non-uniform oxide growth. To minimize the impact of parasitic capacitance due to the interconnections, adequate shielding is provided. In most SAR ADCs, the capacitive DAC also performs the sampling of the input signal. The choice of the unit capacitor is primarily determined by thermal noise and matching requirements. Limitations imposed by the process technology on the minimum capacitor value also have to be considered in the choice of  $C_u$ . The mismatch-limited  $C_u$  value for the fully differential binary-weighted array DAC is given by

$$C_u \ge 9(2^N - 1)K_\sigma^2 K_c, \tag{2.11}$$

where  $K_{\sigma}$  is the matching coefficient and  $K_c$  is the capacitance density parameter. The detailed derivation of (2.11) is provided in Chapter 3.

The disadvantage of a conventional binary-weighted array DAC is that the capacitance increases exponentially with the resolution of the ADC. For medium/high speed SAR ADCs, the RC settling time for the DAC capacitor and associated switch poses a speed bottleneck. Furthermore the binary-weighted array entails increased chip area and power consumption. The split-array capacitive DAC aims to mitigate these drawbacks. Figure 2-7 shows an N-bit split array consisting of a M-bit main DAC and S-bit sub DAC where M + S = N. The bridge capacitor  $C_B$  is given by

Figure 2-7: Split-array capacitive DAC.

$$C_B = \frac{2^S}{2^M - 1} C_u. \tag{2.12}$$

For a 10-bit split-array DAC with M = S = 5,  $C_B = \frac{32}{31}C_u$ . This fractional value of  $C_B$  poses difficulty for layout and worsens mismatch. A technique to overcome this limitation is to remove the dummy  $C_u$  in the sub DAC such that  $C_B = C_u$  [24]. However this causes a gain error of  $1/1 - 2^{-N}$  [25] which can be calibrated in the digital domain if needed. It is shown in [26] that the parasitic capacitance  $C_{P,A}$  causes code-dependent errors and thus degrades linearity of the ADC. In order to reduce  $C_{P,A}$ , the bottom plate node of  $C_B$  which contributes larger parasitic capacitance should be connected to the main DAC. Reducing the number of bits in the sub DAC helps to decrease  $C_{P,A}$ . However, this results in a larger main DAC for a given N and consequently larger spread in capacitor values. Hence the distribution of bits between the main DAC and sub DAC should consider the trade-off between nonlinearity and capacitance spread [26]. The mismatch-limited  $C_u$  value for the fully differential N-bit split-array DAC is given by

$$C_u \ge 9 \cdot (2^M - 1) \cdot 2^{2(N - M)} \cdot K_{\sigma}^2 \cdot K_c.$$

(2.13)

The detailed derivation of (2.13) is provided in Chapter 4. The ratio of the mismatchlimited  $C_u$  values for the split-array and binary-weighted DACs with N = 10, M = S = 5, assuming same  $K_{\sigma}$  and  $K_c$  is given by

$$\frac{C_{u,split}}{C_{u,bw}} = \frac{(2^M - 1) \cdot 2^{2(N-M)}}{2^N - 1} \approx 31,$$

(2.14)

indicating that the split-array DAC imposes significantly larger  $C_u$  to meet the desired linearity. If a particular ADC design uses only capacitors provided in the design kit and  $C_{u,split} \ll C_{u,proc}$  where  $C_{u,proc}$  is the minimum value of the capacitor available in the design kit, then selecting a split-array DAC offers benefits over the binary-

Figure 2-8: Schematic of a dynamic comparator.

weighted topology. However, if very low custom-designed unit capacitors much lower than  $C_{u,proc}$  are used, then the binary-weighted DAC will be advantageous [27]. The 8-bit ADC in **Paper I** utilizes a binary-weighted capacitive array DAC with custom-designed unit capacitors while **Paper II** implements a 10-bit ADC using a split-array DAC.

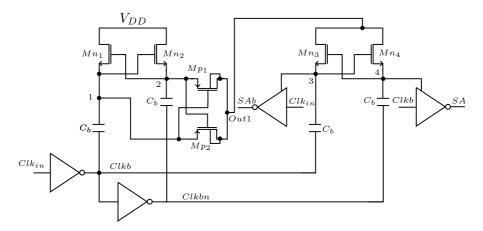

#### 2.1.3 Comparator

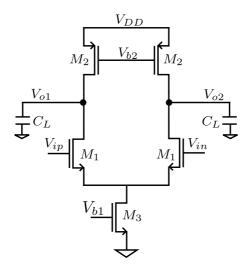

The dynamic comparator commonly used in SAR ADCs consists of a differential pair loaded by a regenerative latch [28]. In some applications, a preamplifier is used before the dynamic comparator to attenuate the thermal noise and improve the speed. However, many recent works on SAR ADCs employ only the dynamic comparator to achieve moderate resolution with high power efficiency. Consider the dynamic comparator shown in Fig. 2-8. The operation of the dynamic comparator consists of two phases. During the reset phase (clk is LOW), the switches  $M_8$ - $M_{11}$  are ON and the outputs as well as the drain nodes of  $M_1, M_2$  are charged to  $V_{DD}$ . In this phase, the comparator is cleared of the previous state. Since the tail-current device  $M_3$  is OFF, no current is drawn. During the evaluation phase (clk is HIGH), the input voltage difference at the differential pair causes their drain nodes to be discharged from  $V_{DD}$ . The cross-coupled inverters are initially OFF. The input transistors have different drain currents and this causes their drain nodes and the outputs to be discharged at different speeds. Finally, one of the cross-coupled inverters is activated. Strong positive feedback of the regenerative latch amplifies the output voltage difference until one output reaches  $V_{DD}$  and the other reaches ground. The important performance specifications of the comparator such as offset, noise, speed and metastability are discussed in the following subsections.

#### 2.1.3.1 Offset

Offset in the dynamic comparator is caused by mismatches in the threshold voltages, device dimensions, and current factor  $\mu C_{ox}$  [29]. Capacitive load imbalance on the output nodes also contributes to offset [30]. The offset voltage contribution is usually dominated by mismatches in the input differential pair of the dynamic comparator [29]. An obvious technique to reduce the offset voltage is to increase the size of the input pair. But this method entails high power consumption due to the parasitic capacitances in the input pair. Conventionally, a preamplifier is added before the dynamic comparator to reduce the input-referred offset. In such a case, the preamplifier provides sufficient gain to the comparator inputs so that the offset voltage is overcome. However, a high bandwidth preamplifier will consume large power. Also, attaining sufficient gain in the preamplifier becomes more challenging in scaled CMOS technologies. Intentional capacitor mismatch is often introduced at the comparator output nodes to cancel the input-referred offset [1].

#### 2.1.3.2 Noise