Access

`Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Low-Voltage Capacitive-Based Step-Up DC-DC Converters for RF Energy Harvesting System: A Review

## Kishore Kumar Pakkirisami Churchill<sup>1</sup>, Gabriel Chong<sup>2</sup>,(Student Member, IEEE), Harikrishnan Ramiah<sup>3</sup>, (Senior Member, IEEE), Mohd Yazed Ahmad<sup>4</sup>, (Member, IEEE), and Jagadheswaran Rajendran<sup>5</sup>, (Senior Member, IEEE)

<sup>1,2,3</sup>Department of Electrical Engineering, <sup>4</sup>Department of Biomedical Engineering, Faculty of Engineering University of Malaya, 50603, Kuala Lumpur, Malaysia

<sup>5</sup>Collaborative Microelectronics Design Excellence Center(CEDEC), School of Electrical and Electronic Engineering, Universiti Sains Malaysia, 11900, Penang, Malaysia

Email: hrkhari@um.edu.my

This work was supported in part by the Partnership Grant (RK004-2019) and the Ministry of Higher Education Malaysia through Fundamental Research Grant Scheme (FRGS, FP049-2017A)

#### ABSTRACT

Bulky off-chip inductors are predominantly adopted for inductive-based step-up DC-DC converter in RF energy harvesting (RFEH) systems, which impose a restriction in physical form factor for miniaturized device. This paper review and explores the capacitive-based step-up DC-DC converters (charge-pump) as voltage boosting element for low-voltage RFEH systems. An overview of RFEH is established and a comprehensive review of CMOS charge-pump is followed along with the complementary frequency generation circuit used as a clocking element. Key design considerations of charge-pump circuits are included here along with recommendations to circumvent its bottlenecks for future development in RFEH systems.

**INDEX TERMS** - RF energy harvesting (RFEH), charge-pump, capacitive-based converters, DC-DC converter, CMOS.

### I. INTRODUCTION

In the recent decade, the demand for miniaturized ultralow-power (ULP) wireless sensor nodes (WSNs) [1, 2], medical implants[3], and wearable devices [4] for the Internet of Things (IoT) [5] are gaining momentum in academic and industrial research. Power consumption of ULP analog-frontend (AFE) and transceivers are ever decreasing, prompting the use of energy harvesting (EH) as an alternative solution to batteries where their replacement is a constraint and impractical for implantable devices. Research works are keen on harvesting ambient energy from solar [6, 7], thermal [8], vibration [9], or electromagnetic/RF [10] to power up ULP devices.

Solar or piezoelectric (PZ) energy has significant power density compared to thermal and RF energy [9], however, limitations due to weather dependency and irregularity of the energy source is unattractive for applications that require a constant power source; i.e: biomedical sensor nodes (BSNs)[1, 3, 4]. Alternatively, is it a challenge to design an effective and efficient start-up circuit for thermoelectric generators (TEG) harvesting in complementary-metal-oxide-semiconductor (CMOS) due to the low-voltage generated [3, 8]. On the other hand, RF energy harvesting (RFEH) is an attractive solution for powering ULP circuits despite its low power density. High reliability of the energy source (in far-field RFEH) and small physical form factor of the transducer (antenna) are key advantages of adopting RFEH.

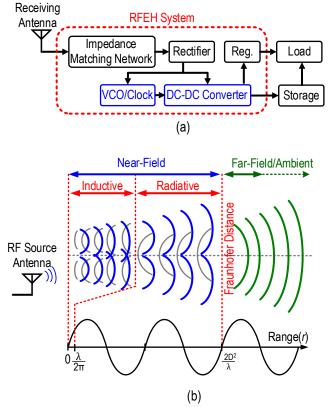

The block diagram of an RFEH system is shown in Fig.1(a). Till date, prior-art CMOS RFEH systems have predominantly been adopted inductive-based step-up DC-DC converters[10]. This is due to the effectiveness in design for low start-up and promotes high power conversion efficiency (PCE) compared to the capacitive-based counterpart (chargepump). Recently, it has been demonstrated that capacitivebased step-up DC-DC converters are becoming competitive in effective start-up and improved PCE performance for EH applications[5, 6]. However, there are only limited development of capacitive-based CMOS step-up DC-DC converters implemented in RFEH systems[11-15]. This prompts the need to investigate and explore design considerations, limitations, and future development goals of capacitive-based CMOS step-up DC-DC converters for RFEH systems to achieve reduction in the physical form factor of the overall miniaturized IoT device.

Therefore, this paper investigates the constraints of implementing a capacitive-based step-up DC-DC converter for RFEH systems. First, an overview of RFEH system is presented in section II. Section III covers a comprehensive

Access

review of charge-pump circuits and the corresponding frequency generation circuit as a clock element. A discussion on the findings are made in section IV to review design considerations, limitations, and future development goals of implementing capacitive-based CMOS step-up DC-DC converters for RFEH systems. Section V concludes the paper.

#### **II. RF ENERGY HARVESTING (RFEH)**

RFEH systems can be classified into two types: Near-field and Far-field RFEH. The depiction in operation of each RFEH type is shown in Fig. 1(b). Its classification is typically determined based on power density, frequency, and range of transmission of the RF energy being harvested. Near-field RFEH operates through magnetic coupling where the transmitter and receiver are placed in proximity within the Fraunhofer distance  $(2D^2/\lambda)$  where D is the diameter of the antenna and  $\lambda$  is the wavelength of the RF signal. Also, the power density of near-field RFEH is significantly larger compared to far-field RFEH. Furthermore, near-field RFEH can be subclassified into the reactive/inductive region and radiative/Fresnel region according to the transmission range or the RF wavelength. Electromagnetic (EM) radiation consists of electrical (E) and magnetic (H) fields which characterize the freely propagated wave. The relation between E and H in nearfield RFEH is highly complex in predicting the power density where either E or H may dominate at a given time.

When the transmission range of the propagated RF energy is beyond the Fraunhofer's distance, the system is classified as dedicated far-field or ambient RFEH. The E and H fields in far-field RFEH have equal magnitude at different points in space. Hence, the received power of the antenna is predictable through Friis transmission equation[16] expressed as,

$$P_{\rm RX} = \frac{P_{\rm TX} \, G_{\rm RX} \, \lambda^2}{(4\pi R)^2} \tag{1}$$

$P_{\text{TX}}$  is the transmitted power,  $G_{\text{TX}}$  is the gain of the transmitting antenna,  $P_{\text{RX}}$  is the received power,  $G_{\text{RX}}$  is the gain of the receiving antenna and R is the distance between transmitting and receiving antenna. Alternatively, the peak input voltage amplitude,  $V_{\text{Ant}}$  received at the antenna can be calculated by[17],

$$V_{\rm Ant} = \sqrt{8 \times R_{\rm Ant} \times P_{\rm RX}}$$

(2)

where  $R_{Ant}$  is the radiation resistance of the antenna. The efficiency of the RFEH system can be calculated based on the efficiency of each block in the system by,

$$\eta_{\text{System}} = \eta_{\text{IMN}} \, . \, \eta_{\text{Rectifier}} \, . \, \eta_{\text{PMU}} \tag{3}$$

in which  $\eta_{\text{IMN}}$ ,  $\eta_{\text{Rectifier}}$  and  $\eta_{\text{PMU}}$  corresponds to the efficiency of the impedance matching network (IMN), rectifier, and power management unit (PMU), respectively.

## A. RECTIFIER

The rectifier block is considered as the core circuit in an RFEH system. It converts the input RF power in alternating current (AC) to usable direct current(DC) for powering up ULP circuits [18-20]. Previously, rectifiers in RF identification (RFID) are constructed using Schottky diodes due to its low turn-on voltage characteristic [21]. The exponential growth of integrated circuit (IC) has delivered the MOSFET, particularly

FIGURE 1. RF energy harvesting. (a) Block diagram (b) Propagation of energy through space.

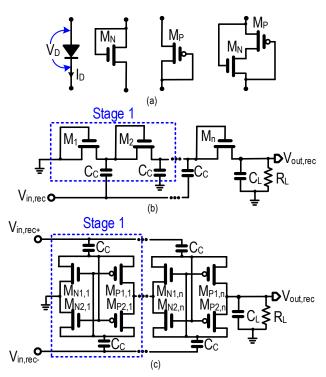

CMOS technology in which diode-connected transistors have replaced the Schottky diode. The equivalent diode configuration of MOSFET is shown in Fig. 2(a). However, the threshold voltage ( $V_{th}$ ) of diode-connected transistors are higher than the Schottky diodes. To overcome this issue, static- $V_{th}$  compensation schemes have been introduced to reduce the forward loss as well as to reduce its *on*-resistance to attain better forward-biasing. The penalty of the trade-off is in the increase of the reverse leakage current due to higher gate bias voltage in reverse bias mode. To overcome this effect, the active compensation technique is introduced[22]. This technique reduces the  $V_{th}$  during forward-bias mode and increases the  $V_{th}$  during reverse bias mode.

Conventional rectifier topologies in CMOS are the Dickson and Cross-Coupled Differential Drive (CCDR) shown in Fig. 2(b) and Fig. 2(c), respectively. The CMOS rectifiers were initially adopted in ultra-high frequency (UHF) RFID application with the circuit structure and performance features being the same for RFEH application. The operation of CCDR is described in two operation cycles, which are the positive and negative RF input cycles. During the positive cycle,  $M_{P1,1}$  and  $M_{N2,1}$  of Fig. 2(c) are operated in a linear mode as switches and  $M_{P2,1}$  and  $M_{N1,1}$  are in cut-off mode. The current flows to the next stage through  $M_{P1}$  and flows back to the negative terminal of the input source through  $M_{N2}$ . A similar operation occurs during the negative cycle where  $M_{P2}$  and  $M_{N1}$  operates in linear mode and  $M_{P1}$  and  $M_{N2}$ , in cut-off mode. This operation is the same for all succeeding stages in a multi-stage rectifier.

The peak amplitude of the rectifier's input voltage,  $V_{in,rec}$  can be quantified with the expression given by[23],

Access

Multidisciplinary Repid Review Open Access Journal

FIGURE 2. (a) Equivalent diode configuration of MOSFET RF rectifier topology (b) Dickson (c) Cross-Coupled Differential-Drive (CCDR).

$$V_{\rm in,rec} = \frac{V_{\rm Ant}}{2} \sqrt{1 + Q^2} \tag{4}$$

where Q is the quality factor of the inductor in the IMN. The expression to compute the rectifier's input power,  $P_{in,rec}$  excluding the IMN interface is given by,

$$P_{\rm in,rec} = P_S \left( 1 - |S_{11rec}|^2 \right) \tag{5}$$

where  $S_{11rec}$  denotes the input reflection coefficient of the rectifier and  $P_{\rm S}$  represents the input power source. An accurate formulation for the CCDR to determine the input power is given as:

$$P_{\rm in,rec} = P_S \left( 1 - \left| S_{\rm dd11,rec} \right|^2 - \left| S_{\rm cd11,rec} \right|^2 \right)$$

(6)

where  $S_{dd11,rec}$ , and  $S_{cd11,rec}$  is the rectifier reflection coefficient of differential-to-differential mode and differential-tocommon mode respectively.

The power conversion efficiency (PCE) primarily depends on the input RF frequency,  $V_{Ant}$ ,  $V_{in,rec}$ , and the output load resistor ( $R_L$ ), with the general formula,

$$PCE = \frac{P_{out,rec}}{P_{in,rec}} = \frac{V_{out,rec}^2/R_L}{P_{in,rec}}$$

(7)

$P_{\text{out,rec}}$  is the output power delivered to the load, calculated by the rectified output voltage,  $V_{\text{out,rec}}$  divided by  $R_{\text{L}}$ .

In summary, Schottky diodes were primarily integrated as rectifier on an IC for RFID to overcome the limitation of forward voltage drop and reverse leakage current. However, a complete CMOS implementation is still preferred due to cost, form factor, and technology integration compatibility. CMOS implementation of the rectifier has focused solely towards reducing the forward voltage drop and reducing the reverseleakage current. These are the primarily consideration needs to taken into account when designing the rectifier for ambient RFEH.

### B. IMPEDANCE MATCHING NETWORK (IMN)

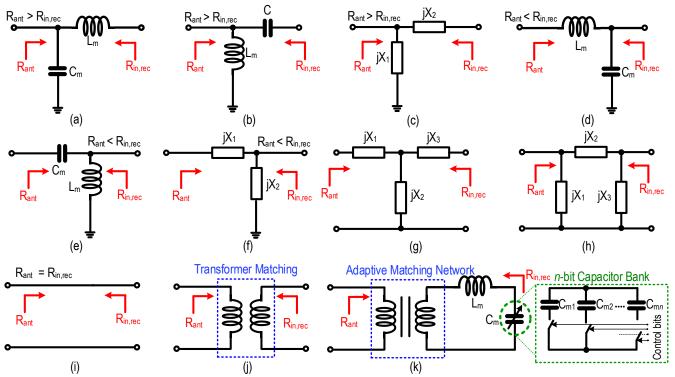

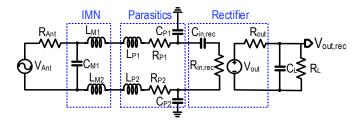

The IMN is an interface between the antenna and the rectifier as shown in the equivalent circuit model in Fig.4.  $R_{\rm L}$ and  $C_L$  are the load resistor and capacitor, respectively. Alternatively, Rin,rec, and Cin,rec are the rectifier's equivalent resistor and capacitor, respectively. L<sub>M1</sub>, L<sub>M2</sub>, and C<sub>M1</sub> forms the IMN where  $L_{P1}$ ,  $L_{P2}$ ,  $R_{P1}$ ,  $R_{P2}$ ,  $C_{P1}$ , and  $C_{P2}$  represent the parasitic components[24-26]. Parasitics exist from various sources such as substrate capacitance, bond wires, and printed circuit board (PCB). The IMN entails a combination of capacitive and inductive elements which acts as a bridge between the receiver antenna to the rectifier for maximum power transfer by reducing impedance mismatch at the desired frequency. Besides achieving maximum power transfer, various work on ambient RFEH has looked upon IMN as a voltage boosting element to increase the sensitivity of the RFEH system [27]. Fig.3 summaries various IMN configurations that are suitable for RFEH systems [26, 28-35].

The performance of the IMN is quantified through the input reflection coefficient,  $S_{11}$  given by,

$$S_{11} (dB) = \Gamma = \frac{Z_{in,rec} - Z_{Ant}^*}{Z_{in,rec} + Z_{Ant}^*}$$

(8)

$Z_{\text{in,rec}} = R_{\text{in,rec}} + X_{\text{in,rec}}$  is the impedance of the rectifier and  $Z^*_{\text{Ant}}$  is the complex conjugate of  $Z_{\text{Ant}}$  and  $Z_{\text{Ant}} = R_{\text{Ant}} + X_{\text{Ant}}$  is the impedance of the antenna (typically 50- $\Omega$ ). Equation (9) refers to the amount of power reflected which is the square of the reflection coefficient in (8).

$$|\Gamma|^{2} = \left| \frac{Z_{\text{in,rec}} - Z_{\text{Ant}}^{*}}{Z_{\text{in,rec}} + Z_{\text{Ant}}^{*}} \right|^{2}$$

(9)

To attain a maximum power transfer and minimize losses, the real term of the antenna and rectifier has to be equal. Also, the imaginary term has to be cancelled out through the conjugate term respective to each other.

As demonstrated in [27], the IMN can also act as a passive voltage booster where the  $V_{Ant}$  from the antenna is boosted. This technique could improve the operation of the rectifier by boosting the input voltage signal beyond the  $V_{th}$  of the transistors. The voltage gain,  $A_v$  is directly proportional to the quality factor of inductor [21, 36] evaluated by,

$$A_{\rm V} = \frac{1}{2} \sqrt{1 + Q_{\rm L}^2} \tag{10}$$

As can be described in (10), the level of voltage boosting is highly dependent on the inductor's quality(Q)-factor. Generally, off-chip inductors have larger Q-factor compared to on-chip inductors. As an example, with an off-chip inductor with a Q-factor that is four times higher compared to an on-chip inductor, the voltage gain is increased by a factor of two in comparison to its on-chip counterpart[37]. Hence, the Q-factor of the IMN inductor plays a significant role in enhancing the sensitivity performance of the RFEH system by boosting  $V_{Ant}$ to drive the transistors of the rectifier in improving the operation.

VOLUME XX, 2020

ŀ

Access

FIGURE 3. Various types of impedance matching networks. (a)-(f) LC networks [27]. (g) T-network. (h) π-network (i) Co-design [28-31] (j) Transformer Matching [32-34] (k) Reconfigurable Matching [25].

FIGURE 4. Equivalent circuit of RFEH front-end.

The Q-factor[21] of an inductor is given by,

$$Q_{\rm L} = \frac{X_{\rm L}}{R_{\rm Ls}} = \frac{\omega_{\rm o}L}{R_{\rm Ls}} \tag{11}$$

where  $\omega_0$  is the resonance frequency in radians per second, L is the inductance,  $X_L$  is the inductive reactance, and  $R_{Ls}$  is the series resistance of the inductor. Alternatively, the *Q*-factor of the capacitor is given by,

$$Q_{\rm C} = -\frac{X_{\rm C}}{R_{\rm C}} = \frac{1}{\omega_{\rm o} C R_{\rm C}} \tag{12}$$

$X_{\rm C}$  is the capacitive reactance,  $R_{\rm C}$  is the series resistance of capacitor and C is the lumped capacitance. Together, the *Q*-factor of the *RLC* circuit is given by,

$$Q = 2\pi \times \frac{\text{Maximum Energy Stored}}{\text{Energy dissipated per cycle}}$$

(13)

where  $R_L$  and  $X_L$  of the IMN represent the input of the rectifier. It is worth noting that the rectifier is a non-linear circuit, where the input impedance changes respective to the level of  $V_{in,rec}$ . A

TABLE 1. Q-factor of Inductor Type/Model

| Ref. | Q-factor | Inductor Model/Type       |

|------|----------|---------------------------|

| [10] | 120      | Co-design antenna         |

| [27] | 80       | Off-chip (MURATA-LQW18AN) |

| [28] | 10       | On-chip                   |

| [28] | 50       | Off-chip                  |

| [38] | 12       | On-chip                   |

| [41] | 130      | Co-design antenna         |

diligent design methodology is essential when designing the IMN to ensure maximum power transfer and effective voltage boosting across a wide range of RF input power. The Q factor of an on-chip inductor is dependant on parasitics which is proportional to the technology node[38]. Nevertheless, there are various techniques reported in improving the Q-factor through the physical design innovation of on-chip inductors[37, 39, 40] and high-Q co-design antenna [10, 41] to attain superior performance in sensitivity. Table I summarizes the Q-factor of various inductors.

#### III. CAPACITIVE-BASED STEP-UP DC-DC CONVERTER A. CHARGE-PUMP

A charge-pump circuit boosts a low DC voltage to a higher DC voltage to a load. The charge-pump is an alternative to the inductive-based step-up DC-DC converter [42] which typically requires a bulky off-chip inductor [27, 43]. In the current era of IC design, switch-capacitor (SC) or charge-pump circuits has gained interest in miniaturized devices to achieve a reduction in physical form factor and to promote system-on-chip(SoC) solution[44].

Access

Multidisciplinary : Rapid Review : Open Access Journal

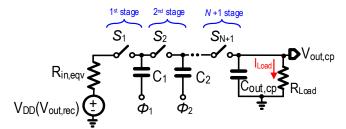

FIGURE 5. A simple scheme of a charge pump.

Fig.5. shows a simplified schematic of a charge-pump circuit. It is comprised of switches,  $S_i$  (where i = 1, 2...N, N + 1), pumping capacitors  $C_{pump}$  (pump = 1, 2, N), a load capacitor ( $C_{out,cp}$ ), and a load resistor ( $R_{Load}$ ).  $R_{Load}$  represents the circuit element to be powered by the charge-pump. In a capacitivebased step-up DC-DC converter, charge is transferred from a supply voltage ( $V_{DD}$ ) or the output DC voltage of a rectifier ( $V_{out,rec}$ ) to  $R_{Load}$  through  $C_{pump}$  which are activated by  $S_i$  using two alternating clock signals,  $\Phi_1$ , and  $\Phi_2$ . The clock signals alternate sequentially to activate the switches to avoid short circuit losses or latch-up [45].

The operations of an *N*-stage charge-pump are described as follow. During the first half cycle,  $\Phi_1$  is low and  $\Phi_2$  is high. Odd-numbered  $S_i$  are activated to allow charges from the prior stage to be transferred to the next immediate  $C_{\text{pump}}$  stage. Alternatively, during the next half-cycle where  $\Phi_1$  is high and  $\Phi_2$  is low, the odd-numbered switches are open and evennumbered switches are activated. The charge stored in the oddnumbered pumping capacitors are transferred to the next immediate  $C_{\text{pump}}$ . The output voltage of the charge pump,  $V_{\text{out,cp}}$ rises steadily as the cycles repeats and reaches a steady-state value. The steady-state value of  $V_{\text{out,cp}}$  can be mathematically expressed as,

$$V_{\rm out,cp} = V_{\rm clk} \cdot N_{\rm cp} + V_{\rm DD} - N_{\rm cp} \frac{I_{\rm Load}T}{C_{\rm pump}}$$

(14)

$N_{\rm cp}$  is the number of charge-pump stages, *T* is the period of the clock, and  $I_{\rm Load}$  is the output current. Alternative, the output voltage at no-load condition can be written as,

$$V_{\text{out,cp(n.l.)}} = V_{\text{clk}} N_{\text{cp}} + V_{\text{DD}}$$

(15)

The total current consumption of the charge-pump is the sum of the ideal current and parasitic current which is expressed in (16).

$$I_{\rm in} = \left[ (N+1) + \alpha \frac{N^2}{\left(N_{\rm cp}, V_{\rm clk} + V_{\rm DD} - V_{\rm out,cp}\right)} \cdot V_{\rm DD} \right] \cdot I_{\rm Load} \quad (16)$$

$I_{\rm in}$  is the input current into the charge-pump and  $\alpha$  is a factor of the pumping capacitor at the bottom plate parasitic capacitance.

The power loss in a charge-pump and its peripheral circuit has to be kept minimal to attain high PCE and voltage conversion efficiency (VCE) performances which are expressed by (17) and (18), respectively.

Power Conversion Efficiency

$$= \frac{P_{out,cp}}{P_{in,cp} + P_{peri}}$$

(17)

Voltage Conversion Efficiency

$$= \frac{V_{out,cp(actual)}}{V_{out,cp(ideal)}}$$

(18)

$P_{\text{out,cp}}$  is the output power,  $P_{\text{in,cp}}$  is the input power, and  $P_{\text{peri}}$  is the power consumed by the peripheral circuit(s) like voltagecontrolled oscillator(VCO), buffer, Non-overlap clock generator(NOC), and level shifter circuit(s) of the chargepump. Alternatively,  $V_{\text{out,cp(ideal)}}$  is the ideal output voltage whereas  $V_{\text{out,cp(actual)}}$  is the actual output voltage of the chargepump. The power losses in a charge-pump are contributed by the following factors:

## 1) REDISTRIBUTION LOSS

A non-negligible loss in between  $C_{\text{out,cp}}$ , and the  $N_{\text{th}}$  stage of the charge-pump which causes the last node voltage swing to be higher than  $V_{\text{out,cp}}$  [46]. Therefore, the output voltage for no-load condition is usually lesser than (15).

#### 2) CONDUCTION LOSS

Conduction loss occurs in the channels when the transistor is turned-on with an *on*-resistance ( $R_{on}$ ) expressed through [47-49],

$$R_{\rm on} = \frac{1}{\mu C_{\rm ox} \frac{W}{L} (V_{\rm gs} - V_{\rm th})} \tag{19}$$

where  $\mu$  is the mobility of the electron/holes and  $C_{\rm ox}$  is the oxide capacitance which is a technology dependent parameters. Conduction loss can be reduced by increasing the gate-to-source voltage ( $V_{\rm gs}$ ) and width (W) of the transistor. However, increasing the width of the transistor leads to an increase in absolute  $V_{\rm th}$ . Thus, adopting mature CMOS technology (>100 nm) might not be well suited for low-voltage operation due to higher  $V_{\rm th}$  [50].

#### 3) REVERSE CHARGE SHARING AND LEAKAGE

As an antithetical to the aforementioned losses, reverse charge leakage are significant in advanced CMOS technology which is attributed to shorter device length. The reverse sharing phenomenon causes current to flow from the  $N_{\text{th,cp}}$  node to  $(N-1)_{\text{th,cp}}$  by indecorous switching effects through  $V_{\text{th}}$  variation, lack of gate-to-source voltage( $V_{\text{gs}}$ ) drive, and short circuit dissipation [51-53].

#### 4) SHORT CIRCUIT LOSS

When  $V_{\text{DD}} > V_{\text{tn}} + |V_{\text{tp}}|$ , the NMOS and PMOS are shorted for a brief period. This leads to short circuit loss, shoot-through current loss, or shoot through loss[53]. These phenomena can be avoided with non-overlap clock signal and various body-biasing techniques for the charge-pump.

#### 5) SWITCHING LOSSES OR DYNAMIC LOSSES

Switching loss of a transistor is proportional to the switching frequency, parasitic capacitance, and transistor size [47]. Also, switching loss is inversely proportionally to the conduction loss.

Conduction loss

$$\alpha \frac{1}{\text{Switching loss}}$$

(20)

Proper transistor sizing and aspect ratio of the PMOS: NMOS transistors (2:1 or 2.5:1) is maintained for a compromised trade-off in the switching loss and conduction loss.

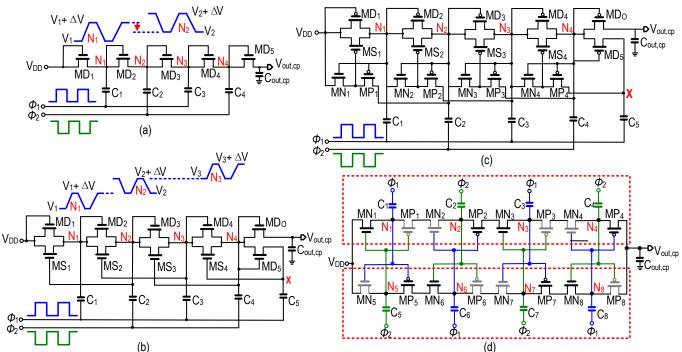

FIGURE 6. Charge-pump topologies. (a) Conventional [54]. (b) Charge transfer switch: Type-I [56]. (c) Charge transfer switch: Type-II [56]. (d) Two-branch latch charge-pump [57].

#### **B. REVIEW OF CHARGE-PUMP**

The first monolithic integrated charge-pump using MOS diodes with the pumping capacitor was introduced in [54] with the schematic shown in Fig.6(a). The Dickson charge-pump was invented for high voltage applications whereas today's state-of-the-art charge-pumps cater for low-voltage EH applications. The Dickson charge-pump operates in two modes; saturation and cut-off. Efficient voltage multiplication relies on the size of the pumping capacitors with its value greater than the stray capacitor of the charge-pump expressed in (21-23).

$$\Delta V = V_{\phi} \cdot \frac{C_{\text{pump}}}{C_{\text{pump}} + C_s} - \frac{I_{\text{Load}}}{f(C_{\text{pump}} + C_s)}$$

(21)

$$2\Delta V > V_{\rm tn}(V_2) \tag{22}$$

$$2\Delta V < V_{\rm tn}(V_1) \tag{23}$$

$C_{\rm s}$  is the node parasitic capacitance or stray capacitance of the node, f is the frequency of clock signals,  $V_{\Phi}$  represents the supply voltage ( $V_{\rm DD}$  or  $V_{\rm out,rec}$ ), and  $\Delta V$  is the change in voltage at each node. The peak output voltage is limited by  $N_{\rm cp}$  as the output impedance increases to limit the allowable  $V_{\rm out,cp}$ . Body effect in charge-pumps can be eliminated through floating well technique to increase the maximum allowable  $V_{\rm out,cp}$  [55], but this creates an increase in substrate current and reduces the pumping efficiency due to  $V_{\rm th}$ .

As an example, to ensure the MOSFET switch  $MS_2$  in Fig.6(a) is fully turned off, the  $V_{gs}(2\Delta V)$  has to be less than the change in  $V_{th}$  denoted in (23). However, this condition is not attained in a *Type-I* charge transfer switch (CTS1) shown in Fig.6(b), indicating  $MS_2$  will not be completely switched off [56]. Due to this, reverse charge flowing from node 3 ( $V_3$ ) to node 1 ( $V_1$ ) is inevitable. Therefore, the pumping efficiency of

the charge-pump is retained by attaining  $\Delta V$  according to (21) until it satisfies (22).

The *Type-2* charge transfer switch (CTS2) in Fig. 6(c) is introduced to eliminate the reverse charge phenomenon by adding two pass transistors and creating a dynamically controlled charge-pump circuit [56]. This allows for  $MS_2$  to be completely turned off/on by the pass transistor through a backward control technique. However, both CTS types can suffer from high voltage stress on its gate oxide due to maximum change in voltage of each stage; usually ~2 $V_{DD}$ which can cause reliability issues. Besides, a dynamic controlling switch is limited at the last stage of the chargepump. Hence, diode-connected configuration is typically adopted for the last stage in a CTS-*type* charge-pump. Transistor  $MD_0$  shown in Fig.6(b) is added to push charges to the output.  $MD_5$  is connected to  $C_5$  as well to provide a control signal to  $MS_4$ .

Voltage fluctuation at node X ( $\Delta V_x$ ) can be large due to the absence of output load (open-circuit). This limits the minimum input voltage as well as the maximum output voltage. Body effect also occurs in the diode-connected MOSFET at the last stage of a CTS charge-pump. To overcome this effect, cross-coupled bootstrap technique is applied to boost the input clock amplitude of the last stage [56]. However, a ~3× increase in parasitics capacitance at nodes 1 to 4 of the charge-pump is evident. Hence,  $C_s$  is non-negligible and can reduce the pumping efficiency of the charge-pump according to (21). Therefore, larger pumping capacitor is needed to suppress the effect of  $C_s$  to attain higher efficiency performance.

Two branch latch charge-pump shown in Fig.6(d) gives a complete solution for reliability issue occurs due to gate oxide stress by ensuring the non-overlap clock, drain-to-source voltage ( $V_{\rm ds}$ ) and  $V_{\rm gs}$ , does not exceed  $V_{\rm DD}$  [57]. This was demonstrated through two power-efficient charge-pumps in 3

Access

stage and 5 stage configuration in a triple-well CMOS technology [50, 58, 59]. Optimal frequency is maintained to attain peak current and pumping efficiency. By integrating larger capacitors, higher efficiency can be attained with a trade-off in chip area through large on-chip capacitors which can incur additional cost. Hence, adopting large capacitors is not an optimal solution. Increasing the oscillating frequency can be adopted to reduce the size of capacitors while retaining PCE performance [60].

Clock boosting techniques can be explored to overcome the limitations of prior-art charge-pump circuits. There are 4 clock schemes for a clock boosting technique for charge-pump which delivers better PCE at low output current (65% at 40  $\mu$ A). However, PCE is impinged at high output current (~20% at 200  $\mu$ A)[60]. Boosted charge transistors have to withstand the voltage drop twice the value of  $V_{DD}$ . Therefore, high voltage transistors are used to prevent breakdown. Higher  $V_{th}$ and increase parasitics are evident in high voltage transistors which leads to deteriorating switching efficiency. Also, the voltage doubler cannot be cascaded due to their breakdown limit. To overcome this limitation, a triple-well process is used where the bulk of the NMOS can be shorted to any terminal point in the circuit so that the voltage drop across the transistors never exceeds V<sub>DD</sub>.

In [61], an NMOS based CTS is replaced by PMOS with lower charge mobility, improving the efficiency of prior-art CTS by reducing reverse charge sharing phenomena. The size of a PMOS has less impact on the absolute  $V_{th}$  than the NMOS counterpart [62] where wider devices are able to reduce conduction loss. Therefore, there is no need of a diodeconnected MOS as the last transistor in a charge-pump circuit [61] where the gate control of the last PMOS stage is connected with the gate of the prior stage for effective switching.

However, in a linear charge-pump (LCP), effective switching efficiency is limited when the input voltage is lesser than the  $V_{\text{th}}$ . The Meindl limits [63] sets the permissible supply voltage according to,

$$V_{DD,min} = 2ln2\left(\frac{kT}{q}\right)$$

(24)

where k is Boltzmann's constant, T is the absolute temperature and q is the electron charge. This is less than the  $V_{\text{th}}$  of the transistor. Hence  $V_{\text{DD,min}}$  is depended on the subthreshold swing (S<sub>s</sub>) of CMOS technology described by [63],

$$V_{DD,min} = 52 \text{ mV. In} \left(1 + \frac{s_s}{60 \text{ mV}}\right)$$

(25)

at a temperature of 300K. In standard CMOS technology, the range of subthreshold slope is between 70 to 100 mV/decade. State-of-art charge-pumps are able to operate as low as 120 mV to 150 mV [64-66]. However, these charge-pumps are not operating in vicinity to Meindl limits due to parasitics effect which causes conduction losses and dead time during switching [67]. Therefore, advanced CMOS technology can be beneficial for achieving an operation approximating to Meindl limit.

Charge-pump improvement techniques for EH application can be classified into their operational techniques: gatebiasing, bulk-biasing, reconfigurable, clock boosting, precharging node, and adiabatic. The performances of recent published charge-pumps for EH are compiled in Table II. Gatebiasing can be subclassified into internal gate-biasing and external gate-biasing. The effective switching of the transistors relies on  $V_{\rm gs}$ . The transistor has to be driven in the triode region for effective charge transfer. Current state-of-the-art chargepumps has achieved a minimum input/start-up voltage of ~150 mV. This input voltage is lower than  $V_{\rm th}$  which is typically between 300 to 500 mV. This implies that the transistors are operating in weak inversion which dwindles the conduction of the MOSFETs. The various operational techniques in chargepump for EH application aims to circumvent this drawback.

In gate-control (biasing) [67-71], the gate voltage of the  $N_{\rm th,cp}$  stage is provided through a voltage potential generated internally from a higher node in the charge-pump. As the pumping efficiency of the charge-pump degrades due to the off-state of the device, a CMOS inverter is adopted to dynamically control the gate by providing a higher voltage potential from the subsequent stage in the charge-pump as a voltage supply  $(V_{DD})$  to the inverter. This also lowers potential from the previous stage of the charge-pump to negative supply (Vss) of the inverter. By adopting internal gate biasing techniques, effective on-state and off-state of the switches can be attained [72] by improving the overdrive voltage and an increase in the subthreshold conduction of the transistor. This reduces the negative reverse charge sharing and conduction losses phenomenon. Adopting PMOS transistor can reduce reverse leakage as discussed earlier to improve the pumping efficiency of the charge-pump.

External gate biasing technique adopts a similar concept but through the aid of external peripherals[73]. Clock boosting techniques [74] as external gate control elements can be generated by level shifters[75], *LC*-oscillators [76-78], ringoscillators [64], multiphase-multi voltage level clock generator, or bootstrapping techniques. These techniques provide an improvement in the clock voltage swing of more than 3x of the input supply voltage, reducing conduction losses. Besides, the external clock boosting significantly reduces the number of charge-pump stages required. This reduces the rise time, improves the PCE, and reduces the active chip area [79]. However, external gate biasing requires peripheral circuits that consume additional power which are accounted in the efficiency computation of the charge-pump.

Bulk-biasing or body-biasing is another key technique in charge-pump for EH application[65, 67, 70, 80, 81]. This technique reduces  $V_{\rm th}$  through biasing of the transistor's bulk. Deep N-well transistors are required to isolate the bulk and the IC substrate. There are 3 types of body-biasing techniques: forward bulk-biasing, reverse bulk-biasing, and dynamic bulkbiasing. State-of-art charge-pump and peripheral circuits have adopted bulk-biasing to achieve low-startup. However, utilizing forward or reverse bulk-biasing could limit the attainable PCE as reverse sharing and switching losses increases. Alternatively, dynamic bulk-biasing provides  $V_{\rm th}$ reduction at forward bias and increases  $V_{\rm th}$  during reverse bias to ensure on- or off-state of the transistors according to the operational cycle. Auxiliary transistors which are used for bulk bias are kept at a minimum size to avoid increases in capacitance. Switching losses, body effect, and extreme  $V_{\rm th}$ drop are reduced and a significant reduction in conduction losses is achieved.

Access

Reconfigurable techniques in charge-pump are developed to improve the switching performance with the aid of pass transistor switches which configure the circuit's architecture according to predetermine conditions [82, 83]. Optimal charge-pump stage selection [84], series-parallel configuration [83], dual-mode operation [66] and sleep-wake mode [10] are some example of the reconfigurable techniques. Attentive design of the pass transistor as a switching element is required to avoid inadequacy in switching which can increase the prospect for various losses.

In [85], precharge node technique is introduced and adopted at the intermediate nodes of the charge pump. This is to mitigate the rise time and input requirement during wake-up phase of EH systems. This concept improves efficiency by maintaining the node voltage between charge-pump stage equals to the input power by applying precharge current ( $I_{pc}$ ) into intermediate isolated p-well. Therefore,  $I_{pc}$  is greater than the leakage current in which more charges will be fed to the next immediate top-plate capacitor stage. Hence, this technique minimizes the leakage as well as parasitics capacitance at the top-plate of the capacitor. However, auxiliary transistor, as well as triple well CMOS process, are required in this technique.

Last but not least, the adiabatic charge-pump is employed to reduce current peaking and improve the PCE [86, 87]. Assuming that a clock boosting element provides a signal amplitude greater than  $V_{DD}$  (i.e.:  $2V_{DD}$  or  $3V_{DD}$ ), higher charge transferability can be achieved while simultaneously attaining better PCE performance with lower charge-pump stages. Peak current is evident and can cause reliability issues. Therefore, the clock signals are divided into two steps to attain peak amplitude and vice versa. The charging of capacitors to 3x of  $V_{DD}$  in a single step can be mathematically expressed as [60],

$$E_{\text{Single-Step}} = Q * 3V_{\text{DD}} \tag{26}$$

The energy delivered by the supply voltage for charging the capacitor to  $V_{\text{DD}}$  in two steps is,

$$E_{\text{Two-Step}} = Q.\frac{1}{4} \, 3V_{\text{DD}} + \frac{1}{2}Q.\, 3V_{\text{DD}} = 2.25.\, QV_{\text{DD}}$$

(27)

The first term of (27) is obtained through charge sharing. A two-step charging with sharing charge observes a 50% reduction in energy compared to single-step charging. The energy needed to charge/discharge the capacitor at a specific node is given as,

$$E_{\text{source}} = \frac{1}{2} Q.3V_{\text{DD}} = \frac{9}{2} C.V_{\text{DD}}^2$$

(28)

To summarize the adiabatic technique, energy dissipation is reduced by minimizing the voltage swing[88]. Two-step of gate control are available for the PMOS device to reduce the peak current which reduces half of the power dissipation, improving the PCE of the charge-pump.

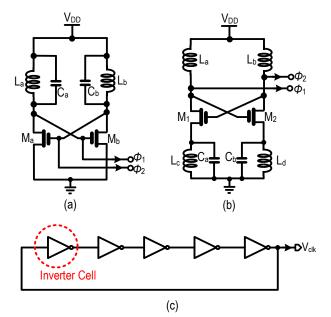

### C. VOLTAGE CONTROLLED OSCILLATOR (VCO)

The oscillator is considered the main peripheral circuit of the charge-pump. Power consumption, frequency, number of clock phases, and clock boosting voltages are inherent to the performance of an oscillator. Monolithic voltage-controlledoscillators (VCOs) are classified majorly into two types; *LC*-

FIGURE 7. (a,b) LC-VCO. (c) conventional R-VCO.

VCOs and Ring-VCOs (*R*-VCO). The schematic of conventional *LC*- and *R*-VCOs are shown in Fig.7. *R*-VCO can be classified into single-ended *R*-VCO and differential *R*-VCO. *R*-VCOs are best suited for EH applications due to their wide range of operation frequency, low power-loss, and simplicity in design compared to the *LC*-VCO. *LC*-VCOs are rarely used in charge-pump for EH application and will be omitted for discussion in this article.

*R*-VCO is commonly designed with a feedback loop of odd inverters [Fig.7(c)]. Its operational frequency ( $f_{vco}$ ) is inversely proportional to the propagation delay ( $t_{delay}$ ) and the number of inverters stages ( $N_{inv}$ ) expressed as,

$$f_{\rm vco} = \frac{1}{2N_{\rm inv} * t_{\rm delay}}$$

(29)

The frequency can be controlled by altering the number of stages or through the supply voltage. The minimum supply voltage in which R-VCO starts to oscillates is known as the start-up voltage and is dependent on the MOSFET's threshold voltage, where the  $V_{\rm th}$  is expressed as,

$$V_{\rm th} = V_{\rm th0} + \gamma \left( \sqrt{|V_{\rm sb} + 2\Phi_{\rm f}|} - \sqrt{2\Phi_{\rm f}} \right)$$

(30)

$V_{\rm th}$  and  $V_{\rm th0}$  are the threshold voltage and threshold voltage at zero source-to-bulk voltage ( $V_{\rm sb}$ ), respectively.  $\Phi_{\rm f}$  is the Fermi potential and  $\gamma$  is the body effect parameter. As suggested in (30), a transistor's  $V_{\rm th}$  can be reduced through bulk-biasing( $V_{\rm sb}$ ), either forward body-biasing or dynamic body-biasing.  $V_{\rm sb}$  can be a positive or negative voltage potential to influence  $V_{\rm th}$  of the NMOS or PMOS, respectively.

Shift register-based *R*-VCO and *N*-stage frequency divider can be adopted to control the frequency of the VCO for a wideinput operation range [89]. A six-phase differential bootstrapped *R*-VCO is proposed in [64] to deliver a high PCE charge-pump EH circuit. Alternatively, bootstrap single-ended *R*-VCO [90] achieves low start-up but suffers from leakage current and switching loss with a detailed analysis is reported in [91]. Clock booster circuits can provide faster rise time for

Access

| TABLE 2. Cor | nparison o | f state-of-the-art | energy harv | esting CM0 | OS charge-pum | ıp |

|--------------|------------|--------------------|-------------|------------|---------------|----|

| Innut        |            | Dumping            | Lood        |            |               |    |

|       | TABLE 2. Comparison of state-or-the-art energy narvesting CMOS charge-pump |                                                                                               |                                    |                          |                                  |                               |                |                                                       |               |                                        |                     |

|-------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|--------------------------|----------------------------------|-------------------------------|----------------|-------------------------------------------------------|---------------|----------------------------------------|---------------------|

| Ref.  | Tech.<br>(nm)                                                              | Topology                                                                                      | Input<br>Voltage<br>(V)            | No. of<br>Stage          | Pumping<br>Cap.<br>(pF)          | Load<br>Cap.<br>(pF)          | Load<br>(µA)   | VCE (%)                                               | PCE<br>(%)    | Clock<br>Freq.<br>(MHz)                | Area<br>(mm²)       |

| [6]   | 130                                                                        | Switched four-<br>branches<br>Bootstrap<br>based CP                                           | 0.5                                | 5                        | 10x4x14.56<br>+<br>20x4x0.097    | 800                           | 30             | 93<br>@ 500<br>mV                                     | 78.6          | 0.8-2.5                                | 0.98                |

| [7]   | 180                                                                        | CC-CP:<br>MVG and<br>HVG                                                                      | 0.35                               | 2<br>(MVG)<br>2<br>(HVG) | 4x480<br>(MVG)<br>4x360<br>(HVG) | 1300<br>(MVG)<br>200<br>(HVG) | 114/<br>396    | 79.7<br>@ 0.59 V<br>(MVG)<br>60.5<br>@ 2.5 V<br>(HVG) | 49.1/<br>75.8 | -                                      | 1.75                |

| [42]  | 130                                                                        | Bootstrap                                                                                     | 0.27 -<br>no reg.<br>0.4 -<br>reg. | 3                        | 50 x 3                           | 500                           | 5              | 65<br>@ 450<br>mV                                     | 58            | 0.8<br>[nominal]<br>0.6-1<br>[tunable] | 0.42                |

| [45]  | 65                                                                         | CC-CP: low-<br>leakage<br>drivers                                                             | 0.1-0.6                            | 3                        | 50 x 6                           | 100                           | 0.032/<br>1000 | 90.5@100<br>mV / 99<br>@ 600<br>mV                    | 12.7/<br>70.3 | -                                      | -                   |

| [64]  | 65                                                                         | CC-CP: clock<br>boosting to 3<br>x V <sub>DD</sub> and 6-<br>phase<br>frequency<br>generation | 0.15                               | 3                        | 2.5 x 9                          | 30                            | 1.74           | 80 @ 150<br>mV                                        | 38.8          | 15.2                                   | 0.032               |

| [65]  | 65                                                                         | CC-CP: FBB<br>start-up<br>technique                                                           | 0.18                               | 3                        | 12.3 x 6 +<br>0.4 x 2            | 12.30                         | 8.75           | 69<br>@ 180<br>mV                                     | -             | 10                                     | 0.296               |

| [66]  | 65                                                                         | Dickson: dual<br>mode [startup/<br>operation]                                                 | 0.12                               | 10                       | 28.6 x 10                        | -                             | 3.9            | 58<br>@ 120<br>mV                                     | 38.8          | 1 [startup]<br>20 [op.]                | 0.78                |

| [ 70] | 180                                                                        | CC-CP:<br>D(G/B)B                                                                             | 0.32                               | 6                        | 24 x 12                          | 50.7                          | -              | 89<br>@ 320<br>mV                                     | -             | 0.45                                   | 0.14                |

| [71]  | 65                                                                         | Dickson: DGB                                                                                  | 0.55                               | 4                        | 40 x 4                           | 400                           | 10             | 98<br>@ 700<br>mV                                     | 66            | 0.5-1.8                                | 0.17                |

| [72]  | 65                                                                         | Charge<br>Transfer<br>Switch                                                                  | 0.4/0.2                            | 4                        | 4 x 20                           | 160                           | 20/50          | 94.3/<br>99.4                                         | 72.7/<br>78.2 | 25                                     | 0.019               |

| [73]  | 65                                                                         | Bootstrap CP:<br>DGB                                                                          | 0.1                                | 10                       | 100 x 10 +<br>0.1 x 10           | 100                           | 6.6            | 76<br>@ 100<br>mV                                     | 33            | 1                                      | 1.32                |

| [ 81] | 130                                                                        | Cross-<br>doubler: DBB                                                                        | 0.15                               | 3                        | 10000 x 6<br>(off-chip)          | 10000<br>(off<br>chip)        | 21             | 86<br>@ 180<br>mV                                     | 34            | 0.25                                   | 0.066<br>w/o<br>cap |

| [83]  | 180                                                                        | Reconfigurabl<br>e CP                                                                         | 0.45                               | 4                        | 62.7 x 4                         | 2050                          | -              | 89 @<br>0.45V                                         | -             | 0.286-1                                | 4.00                |

| [ 85] | 65                                                                         | CC-CP                                                                                         | 0.4                                | 4                        | 8 x 10                           | 160                           | 0.1            | 99.2                                                  | 87.8          | 4                                      | 0.021               |

| [86]  | 130                                                                        | 2-Branches<br>Diode-PMOS<br>with DGB to<br>implement<br>two-step clock<br>signal.             | 0.125                              | 3/7                      | 16 x 6,<br>16x14                 | 100                           | 0.1            | 80<br>@ 125<br>mV,<br>70<br>@ 125<br>mV               | 65/<br>59     | 0.36                                   | 0.10,<br>0.15       |

Acces

the charge-pump. An 8 phase bootstrap R-VCO with an internal pseudo-differential clocking scheme as reported in[92] has demonstrated the advantages of clock booster circuits. However, a trade-off in design complexity and power dissipation exists and has to be taken into consideration[79].

Low voltage selective-Schmitt trigger inverters are used in the *R*-VCO to achieve 90% swing at 60 mV of input voltage [93]. Another process tolerant *R*-VCO is proposed with a single-cell inverter to provide start-up at 60 mV[94]. In [70], a 5 stage *R*-VCO is reported with two parallel phase shifters operating in subthreshold with a resistive voltage divider to provide bulk biasing for  $V_{\rm th}$  reduction. The *W/L* of the *R*-VCO is kept to a minimal for achieving low  $V_{\rm th}$  with the *W/L* of the buffer maximized [95] to achieve high current drivability as well as maximum clock swing.

#### **IV. DISCUSSION**

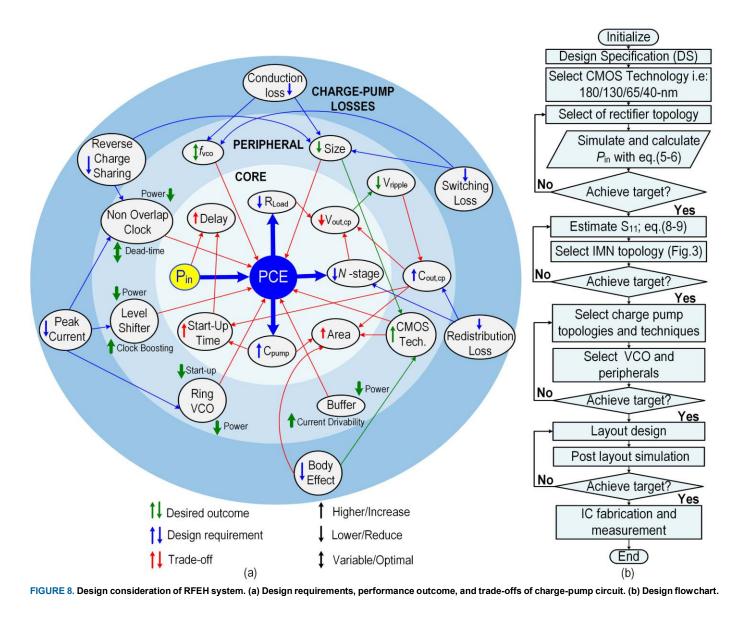

All the charge-pump techniques reviewed in this article are identified to be suitable for RFEH system in which two or more of these techniques can be fused to attain overall system improvement in PCE and start-up performance. As for the peripheral circuits, *R*-VCO will the most preferred peripheral circuits for RFEH systems as it occupies smaller chip area, achieve low-power consumption and wide-dynamic operational frequency to accommodate variation of the input harvesting voltage compared to the *LC*-VCO. However, it is worth noting that implementing too many peripheral circuits is detrimental to the overall PCE of the harvesting system. Designers should pay attention to the various trade-offs [Fig.8.(a)] that may incur cost, increase parasitic, or leakages that degrade the PCE.

Considering all these design factors of a capacitive-based step-up DC-DC converter (charge-pump), Fig. 8(a) provides a visual illustration of the performance trade-offs. Fig.8(a) outlays all the trade-offs associated in the attempt to attain high PCE and low-input-voltage in designing the charge-pump for RFEH system. The design considerations of a charge-pump are categorized into three layers, namely the core (overall DC-DC converter), intermediate ring (peripherals), and outer ring (second-order effects/losses) for maximizing the PCE and start-up voltage.

Access

Multidisciplinary Rapid Review Open Access Journal

FIGURE 9. Optimal transistor sizing.

The main design aim of the charge-pump is to maximize its PCE. Based on Fig.8(a), the core elements that affects the PCE is the  $R_{\text{load}}$ [96], *N*-stage [54, 64, 66, 79, 97, 98] and  $C_{\text{pump}}$ [99]. However, as described in Fig.8(a), there are contradicting trade-offs in achieving the desired specification such as start-up time [79, 85, 100, 101],  $V_{\text{out,cp}}$ , and area. However, peripheral circuits also contribute in altering the specification which affects the PCE of the overall charge-pump circuit.

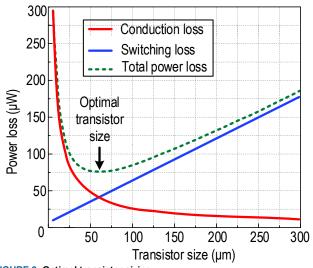

Respective to the design of the peripherals, it is desirable to ensure that the charge-pump achieve its function such as clock generation [64, 70], level shifting [56, 59, 81], and low output voltage ripple [64] with minimal degradation to achieve high-PCE in the overall charge-pump circuit. However, designers should be aware of the trade-offs associated with the design in the peripherals as shown in Fig.8(a). As an example, if we alter the transistor size of the charge-pump by increasing its width, this will increase the gate capacitance, thus, affecting the switching loss. Similarly, conduction loss increases when the width of the transistor is minimized, alleviating switching losses where the losses are reflected in the overall PCE of the RFEH system. Therefore, there is an optimal sizing of the transistor for minimal losses [102] and to attain the maximum PCE of the charge-pump, achieving higher power conversion ratio as illustrated in Fig.9. Table II summarized the performance of the state-of-art EH charge-pumps which are a promising option for further enhancement as capacitive-based step-up DC-DC converter for RFEH system.

Eliminating all losses is an impractical endeavour. Intuitive circuit design techniques are required to achieve optimal performance for the targeted application. This will be a significant challenge in the research and development of capacitive-based step-up DC-DC converter for RFEH systems to minimize losses and maximize the PCE. For designing an RFEH system, Fig.8(b) provides a systematic approach to Fig. 8(a) for effective design as a guide for designers to understand the trade-offs associated in the charge-pump circuit. Starting with the technology node, rectifier, and IMN, the charge-pump topology and technique are selected according to the design requirements of the RFEH System. The VCO and peripheral circuits are selected according to the requirement of the charge-pump. If the performance of the system could not attain the desired performance specifications, the VCO topology and/or peripheral circuits are reconsidered. Once the performances are met, further optimization in the layout are required prior to IC fabrication and validation.

### **V. CONCLUSION**

In conclusion, this paper has provided an overview of the charge-pump circuit for RFEH systems. A summary of stateof-art charge-pump design for EH application, specifically in RFEH systems has been considered. A review of charge-pump circuits has been presented which has discussed various prior state-of-art architectures in the aspect of losses, design techniques for charge-pump in the development for RFEH system utilizing a capacitive-based step-up DC-DC converter. Considering the characteristics for wide range of charge-pump circuit designs, a methodology is proposed to visualize design aspects and performance trade-offs of EH charge-pump in which designers have to consider to realize a highly efficient step-up DC-DC converter in RFEH systems for the next generation of miniaturized IoT devices.

#### REFERENCES

- [1] A. L. Mansano, Y. Li, S. Bagga, and W. A. Serdijn, "An Autonomous Wireless Sensor Node With Asynchronous ECG Monitoring in 0.18 μ m CMOS," *IEEE Transactions on biomedical circuits and systems*, vol. 10, no. 3, pp. 602-611, 2016.

- [2] R. Shigeta et al., "Ambient RF energy harvesting sensor device with capacitor-leakage-aware duty cycle control," *IEEE Sensors Journal*, vol. 13, no. 8, pp. 2973-2983, 2013.

- [3] M. Ashraf and N. Masoumi, "A thermal energy harvesting power supply with an internal startup circuit for pacemakers," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 24, no. 1, pp. 26-37, 2015.

- [4] C. J. Deepu, X. Xu, D. Wong, C.-H. Heng, and Y. Lian, "A 2.3 µW ECG-On-Chip for Wireless Wearable Sensors," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 65, no. 10, pp. 1385-1389, 2018.

- [5] M. Taghadosi, L. Albasha, N. A. Quadir, Y. A. Rahama, and N. Qaddoumi, "High efficiency energy harvesters in 65nm CMOS process for autonomous IoT sensor applications," *IEEE Access, vol. 6*, pp. 2397-2409, 2017.

- [6] Y. Wang, N. Yan, H. Min, and C.-J. R. Shi, "A high-efficiency splitmerge charge pump for solar energy harvesting," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 5, pp. 545-549, 2016.

- [7] T. Ozaki, T. Hirose, H. Asano, N. Kuroki and M. Numa, "Fully-Integrated High-Conversion-Ratio Dual-Output Voltage Boost Converter With MPPT for Low-Voltage Energy Harvesting," in *IEEE Journal of Solid-State Circuits*, vol. 51, no. 10, pp. 2398-2407, 2016.

- [8] Y. K. Ramadass and A. P. Chandrakasan, "A battery-less thermoelectric energy harvesting interface circuit with 35 mV startup voltage," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 1, pp. 333-341, 2010.

- [9] S. Bandyopadhyay and A. P. Chandrakasan, "Platform architecture for solar, thermal, and vibration energy combining with MPPT and single inductor," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 9, pp. 2199-2215, 2012.

- [10] K. R. Sadagopan, J. Kang, Y. Ramadass, and A. Natarajan, "A cm-scale 2.4-GHz wireless energy harvester with nanowatt boost converter and antenna-rectifier resonance for WiFi powering of sensor nodes," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 12, pp. 3396-3406, 2018.

- [11] D. De Donno, L. Catarinucci and L. Tarricone, "An UHF RFID Energy-Harvesting System Enhanced by a DC-DC Charge Pump in Silicon-on-Insulator Technology," *in IEEE Microwave and Wireless Components Letters*, vol. 23, no. 6, pp. 315-317, June 2013.

- [12] D. Al-Shebanee, R. Wunderlich and S. Heinen, "Design of highly sensitive CMOS RF energy harvester using ultra-low power charge pump," 2015 IEEE Wireless Power Transfer Conference (WPTC), Boulder, CO, 2015, pp. 1-4.

- [13] K. You, H. Kim, M. Kim and Y. Yang, "900 MHz CMOS RF-to-DC converter using a cross-coupled charge pump for energy

Access

harvesting," 2011 IEEE International Symposium on Radio-Frequency Integration Technology, Beijing, pp. 149-152, 2011.

- [14] D. De Donno, L. Catarinucci and L. Tarricone, "RAMSES: RFID Augmented Module for Smart Environmental Sensing," in *IEEE Transactions on Instrumentation and Measurement*, vol. 63, no. 7, pp. 1701-1708, July 2014.

- [15] R. Colella, L. Tarricone and L. Catarinucci, "SPARTACUS: Self-Powered Augmented RFID Tag for Autonomous Computing and Ubiquitous Sensing," in *IEEE Transactions on Antennas and Propagation*, vol. 63, no. 5, pp. 2272-2281, May 2015.

- [16] H. T. Friis, "A note on a simple transmission formula," *Proceedings of the IRE*, vol. 34, no. 5, pp. 254-256, 1946.

- [17] Y. Lu et al., "A wide input range dual-path CMOS rectifier for RF energy harvesting," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 2, pp. 166-170, 2016.

- [18] A. Shrivastava, N. E. Roberts, O. U. Khan, D. D. Wentzloff, and B. H. Calhoun, "A 10 mV-Input Boost Converter With Inductor Peak Current Control and Zero Detection for Thermoelectric and Solar Energy Harvesting With 220 mV Cold-Start and -14.5 dBm, 915 MHz RF Kick-Start," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 8, pp. 1820-1832, 2015.

- [19] S. Dehghani, A. Clements, and T. Johnson, "An Inverter-Based Bidirectional and Reconfigurable RF Energy Harvesting Circuit with Rectifier and Oscillator Modes," in 2018 IEEE/MTT-S International Microwave Symposium-IMS, 2018: IEEE, pp. 1138-1140.

- [20] O. Elsayed, M. Abouzied, V. Vaidya, K. Ravichandran, and E. Sánchez-Sinencio, "An Ultralow-Power RF Wireless Receiver With RF Blocker Energy Recycling for IoT Applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 11, pp. 4927-4942, 2018.

- [21] U. Karthaus and M. Fischer, "Fully integrated passive UHF RFID transponder IC with 16.7- μW minimum RF input power," *IEEE Journal of solid-state circuits*, vol. 38, no. 10, pp. 1602-1608, 2003.

- [22] K. Kotani and T. Ito, "High efficiency CMOS rectifier circuit with self-Vth-cancellation and power regulation functions for UHF RFIDs," in 2007 IEEE Asian Solid-State Circuits Conference, 2007: IEEE, pp. 119-122.

- [23] F. Mazzilli, P. E. Thoppay, N. Jöhl, and C. Dehollain, "Design methodology and comparison of rectifiers for UHF-band RFIDs," in 2010 IEEE Radio Frequency Integrated Circuits Symposium, 2010: IEEE, pp. 505-508.

- [24] M. A. Abouzied, K. Ravichandran, and E. Sánchez-Sinencio, "A fully integrated reconfigurable self-startup RF energy-harvesting system with storage capability," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 3, pp. 704-719, 2016.

- [25] P. Xu, D. Flandre, and D. Bol, "Design of a 2.45-GHz RF energy harvester for SWIPT IoT smart sensors," in 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2018: IEEE, pp. 107-110.

- [26] Z. Liu, Y.-P. Hsu, B. Fahs, and M. M. Hella, "An RF-DC Converter IC With On-Chip Adaptive Impedance Matching and 307-µW Peak Output Power for Health Monitoring Applications," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 26, no. 8, pp. 1565-1574, 2018.

- [27] P.-H. Hsieh, C.-H. Chou, and T. Chiang, "An RF energy harvester with 44.1% PCE at input available power of-12 dBm," *IEEE Transactions* on Circuits and Systems I: Regular Papers, vol. 62, no. 6, pp. 1528-1537, 2015.

- [28] M. A. Karami and K. Moez, "Systematic Co-Design of Matching Networks and Rectifiers for CMOS Radio Frequency Energy Harvesters," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 8, pp. 3238-3251, 2019.

- [29] J. Kang, S. Rao, P. Chiang and A. Natarajan, "Design and Optimization of Area-Constrained Wirelessly Powered CMOS UWB SoC for Localization Applications," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 4, pp. 1042-1054, 2016.

- [30] B. Li, X. Shao, N. Shahshahan, N. Goldsman, T. Salter and G. M. Metze, "An Antenna Co-Design Dual Band RF Energy Harvester," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 12, pp. 3256-3266, 2013.

- [31] M. Stoopman, S. Keyrouz, H. J. Visser, K. Philips, and W. A. Serdijn, "Co-design of a CMOS rectifier and small loop antenna for highly sensitive RF energy harvesters," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 3, pp. 622-634, 2014.

- [32] H. Lyu, X. Liu, Y. Sun, Z. Jian, and A. Babakhani, "A 915-MHz Far-Field Energy Harvester With- 22-dBm Sensitivity and 3-V Output

Voltage Based on Antenna-and-Rectifier Codesign," *IEEE Microwave and Wireless Components Letters*, vol. 29, no. 8, pp. 557-559, 2019.

- [33] H. Gonçalves, M. Martins, and J. Fernandes, "Fully integrated energy harvesting circuit with- 25-dBm sensitivity using transformer matching," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 62, no. 5, pp. 446-450, 2015.

- [34] Z. Wang and S. Mirabbasi, "A low-voltage CMOS rectifier with onchip matching network and a magnetic field focused antenna for wirelessly powered medical implants," *IEEE transactions on biomedical circuits and systems*, vol. 13, no. 3, pp. 554-565, 2019.

- [35] N. Soltani and F. Yuan, "A high-gain power-matching technique for efficient radio-frequency power harvest of passive wireless microsystems," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 10, pp. 2685-2695, 2010.

- [36] N. Soltani and F. Yuan, "A step-up transformer impedance transformation technique for efficient power harvesting of passive transponders," *Microelectronics journal*, vol. 41, no. 2-3, pp. 75-84, 2010.

- [37] M. A. Abouzied and E. Sánchez-Sinencio, "Low-Input Power-Level CMOS RF Energy-Harvesting Front End," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 11, pp. 3794-3805, Nov. 2015.

- [38] G. Papotto, F. Carrara, and G. Palmisano, "A 90-nm CMOS thresholdcompensated RF energy harvester," *IEEE Journal of solid-state circuits*, vol. 46, no. 9, pp. 1985-1997, 2011.

- [39] A. Zolfaghari, A. Chan and B. Razavi, "Stacked inductors and transformers in CMOS technology," in *IEEE Journal of Solid-State Circuits*, vol. 36, no. 4, pp. 620-628, April 2001.

- [40] S. S. Kudva and R. Harjani, "Fully integrated on-chip DC-DC converter with a 450x output range," *IEEE Custom Integrated Circuits Conference 2010*, San Jose, CA, pp. 1-4, 2010.

- [41] J. Kang, P. Chiang and A. Natarajan, "Bootstrapped Rectifier–Antenna Co-Integration for Increased Sensitivity in Wirelessly- Powered Sensors," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 11, pp. 5031-5041, Nov. 2018.

- [42] Y.-C. Shih and B. P. Otis, "An Inductorless DC–DC Converter for Energy Harvesting With a 1.2- μW Bandgap-Referenced Output Controller," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 58, no. 12, pp. 832-836, 2011.

- [43] G. Saini, L. Somappa and M. S. Baghini, "A 500 nW to 1 mW Input Power Inductive Boost Converter with MPPT for RF Energy Harvesting System," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Early Access.

- [44] E. Ferro, V. M. Brea, P. López, and D. Cabello, "Micro-Energy Harvesting System Including a PMU and a Solar Cell on the Same Substrate With Cold Startup From 2.38 nW and Input Power Range up to 10 μW Using Continuous MPPT," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5105-5116, 2018.

- [45] Y. Tsuji, T. Hirose, T. Ozaki, H. Asano, N. Kuroki, and M. Numa, "A 0.1–0.6 V input range voltage boost converter with low-leakage driver for low-voltage energy harvesting," in 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2017: IEEE, pp. 502-505.

- [46] Wing-Hung Ki, Feng Su and Chi-Ying Tsui, "Charge redistribution loss consideration in optimal charge pump design," 2005 IEEE International Symposium on Circuits and Systems, Kobe, pp. 1895-1898 Vol. 2, 2005.

- [47] M. H. Eid and E. Rodriguez-Villegas, "Analysis and design of crosscoupled charge pump for low power on chip applications," *Microelectronics journal*, vol. 66, pp. 9-17, 2017.

- [48] Chi-Chang Wang and Jiin-Chuan Wu, "Efficiency improvement in charge pump circuits," in *IEEE Journal of Solid-State Circuits*, vol. 32, no. 6, pp. 852-860, June 1997.

- [49] J. Cha, M. Ahn, C. Cho, C. Lee, H. Kim and J. Laskar, "Analysis and Design Techniques of CMOS Charge-Pump-Based Radio-Frequency Antenna-Switch Controllers," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, no. 5, pp. 1053-1062, May 2009.

- [50] R. Pelliconi, D. Iezzi, A. Baroni, M. Pasotti, and P. L. Rolandi, "Power efficient charge pump in deep submicron standard CMOS technology," in Proceedings of the 27th European Solid-State Circuits Conference, 2001: IEEE, pp. 73-76.

- [51] M. H. Eid and E. Rodriguez-Villegas, "Analysis of reversion losses in charge pumps and its impact on efficiency for low power design," 2017 15th IEEE International New Circuits and Systems Conference (NEWCAS), Strasbourg, pp. 9-12, 2017.

Access

- [52] J. Kim, S. Park, K. Kwon, B. Kong, J. Choi and Y. Jun, "CMOS Charge Pump With No Reversion Loss and Enhanced Drivability," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 22, no. 6, pp. 1441-1445, June 2014.

- [53] J. Kim, Y. Jun and B. Kong, "CMOS Charge Pump With Transfer Blocking Technique for No Reversion Loss and Relaxed Clock Timing Restriction," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 56, no. 1, pp. 11-15, Jan. 2009.

- [54] J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," *IEEE Journal of solid-state circuits*, vol. 11, no. 3, pp. 374-378, 1976.

- [55] K.-H. Choi, J.-M. Park, J.-K. Kim, T.-S. Jung, and K.-D. Suh, "Floating-well charge pump circuits for sub-2.0 V single power supply flash memories," *in Symposium 1997 on VLSI Circuits*, 1997: IEEE, pp. 61-62.

- [56] J.-T. Wu and K.-L. Chang, "MOS charge pumps for low-voltage operation," *IEEE Journal of solid-state circuits*, vol. 33, no. 4, pp. 592-597, 1998.

- [57] M.-D. Ker, S.-L. Chen, and C.-S. Tsai, "Design of charge pump circuit with consideration of gate-oxide reliability in low-voltage CMOS processes," *IEEE Journal of solid-state circuits*, vol. 41, no. 5, pp. 1100-1107, 2006.

- [58] Y. Nakagome et al., "An experimental 1.5-V 64-Mb dram," IEEE Journal of Solid-State Circuits, vol. 26, no. 4, pp. 465-472, 1991.

- [59] P. Favrat, P. Deval, and M. J. Declercq, "A high-efficiency CMOS voltage doubler," *IEEE Journal of solid-state circuits*, vol. 33, no. 3, pp. 410-416, 1998.

- [60] C. Lauterbach, W. Weber, and D. Romer, "Charge sharing concept and new clocking scheme for power efficiency and electromagnetic emission improvement of boosted charge pumps," *IEEE Journal of solid-state circuits*, vol. 35, no. 5, pp. 719-723, 2000.

- [61] F. Su, W.-H. Ki, and C.-Y. Tsui, "Gate control strategies for high efficiency charge pumps," in 2005 IEEE International Symposium on Circuits and Systems, 2005: IEEE, pp. 1907-1910.

- [62] F. Su, W.-H. Ki, and C.-Y. Tsui, "High efficiency cross-coupled doubler with no reversion loss," in 2006 IEEE International Symposium on Circuits and Systems, 2006. IEEE, pp. 4 pp.-2764.

- [63] B. Zhai, D. Blaauw, D. Sylvester, and K. Flautner, "The limit of dynamic voltage scaling and insomniac dynamic voltage scaling," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 13, no. 11, pp. 1239-1252, 2005.

- [64] H. Yi, J. Yin, P.-I. Mak, and R. P. Martins, "A 0.032-mm<sup>2</sup> 0.15-V three-stage charge-pump scheme using a differential bootstrapped ring-VCO for energy-harvesting applications," *IEEE Transactions* on Circuits and Systems II: Express Briefs, vol. 65, no. 2, pp. 146-150, 2017.

- [65] P.-H. Chen et al., "0.18-V input charge pump with forward body biasing in startup circuit using 65nm CMOS," in IEEE Custom Integrated Circuits Conference 2010, 2010: IEEE, pp. 1-4.

- [66] P.-H. Chen et al., "A 120-mV input, fully integrated dual-mode charge pump in 65-nm CMOS for thermoelectric energy harvester," in 17th Asia and South Pacific Design Automation Conference, 2012: IEEE, pp. 469-470.

- [67] X. Zhang and H. Lee, "Gain-enhanced monolithic charge pump with simultaneous dynamic gate and substrate control," *IEEE* transactions on very large scale integration (VLSI) systems, vol. 21, no. 3, pp. 593-596, 2012.

- [68] X. Jiang, X. Yu, K. Moez, D. G. Elliott, and J. Chen, "Highefficiency charge pumps for low-power on-chip applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 3, pp. 1143-1153, 2017.

- [69] Y.-S. Hwang, D.-S. Wu, H.-C. Lin, J.-J. Chen, and C.-C. Yu, "A new inverter-based charge pump circuit with high conversion ratio and high power efficiency," *Microelectronics journal*, vol. 42, no. 8, pp. 982-987, 2011.

- [70] H. Peng, N. Tang, Y. Yang, and D. Heo, "CMOS startup charge pump with body bias and backward control for energy harvesting step-up converters," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 6, pp. 1618-1628, 2014.

- [71] A. Mahmoud, M. Alhawari, B. Mohammad, H. Saleh and M. Ismail, "A Charge Pump Based Power Management Unit With 66%-Efficiency in 65 nm CMOS," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, pp. 1-4, 2018.

- [72] A. Ballo, A. D. Grasso and G. Palumbo, "A High-Performance Charge Pump Topology for Very-Low-Voltage Applications," *in IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 7, pp. 1304-1308, July 2020.

- [73] H. Fuketa and T. Matsukawa, "Fully integrated, 100-mV minimum input voltage converter with gate-boosted charge pump kick-started by LC oscillator for energy harvesting," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 4, pp. 392-396, 2016.

[74] Z. Chen, W. Wang, and H. Wong, "Low-voltage CMOS DC-DC

- [74] Z. Chen, W. Wang, and H. Wong, "Low-voltage CMOS DC-DC converters for energy harvesting applications," in 2015 IEEE 11th International Conference on ASIC (ASICON), 2015: IEEE, pp. 1-4.

- [75] J. Kim, P. K. T. Mok, C. Kim and Y. K. Teh, "A low-voltage highefficiency voltage doubler for thermoelectric energy harvesting," 2013 IEEE International Conference of Electron Devices and Solid-state Circuits, Hong Kong, 2013, pp. 1-2.

- [76] G. Bassi, L. Colalongo, A. Richelli, and Z. M. Kovacs-Vajna, "100 mV-1.2 V fully-integrated DC-DC converters for thermal energy harvesting," *IET Power Electronics*, vol. 6, no. 6, pp. 1151-1156, 2013.

- [77] M. Pasca, S. D'Amico, and A. Baschirotto, "A 0.23 μW, 96 mV Input Voltage DC–DC Converter for Body Sensor Nodes," *IEEE Sensors Journal*, vol. 15, no. 10, pp. 5677-5682, 2015.

- [78] S. M. Noghabaei and M. Sawan, "A fully integrated high-efficiency step-up DC-DC converter for energy harvesting applications," *in 2016 International SoC Design Conference (ISOCC), 2016: IEEE*, pp. 121-122.

- [79] A. Ballo, A. D. Grasso, G. Giustolisi, and G. Palumbo, "Optimized charge pump with clock booster for reduced rise time or silicon area," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 12, pp. 1977-1981, 2019.

- [80] J. Shin, I.-Y. Chung, Y. J. Park, and H. S. Min, "A new charge pump without degradation in threshold voltage due to body effect [memory applications]," *IEEE Journal of solid-state circuits*, vol. 35, no. 8, pp. 1227-1230, 2000.

- [81] J. Kim, P. K. Mok, and C. Kim, "A 0.15 V input energy harvesting charge pump with dynamic body biasing and adaptive dead-time for efficiency improvement," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 2, pp. 414-425, 2014.

- [82] S. Fan, J. Dong, R. Zhang, Z. Xue, and L. Geng, "A reconfigurable multi-ratio charge pump with wide input/output voltage range for wireless energy harvesting system," in 2018 IEEE MTT-S International Wireless Symposium (IWS), 2018: IEEE, pp. 1-3.

- [83] X. Liu, L. Huang, K. Ravichandran, and E. Sánchez-Sinencio, "A highly efficient reconfigurable charge pump energy harvester with wide harvesting range and two-dimensional MPPT for Internet of Things," *IEEE Journal of Solid-State Circuits*, vol. 51, no. 5, pp. 1302-1312, 2016.

- [84] A. H. Alameh, A. Robichaud, and F. Nabki, "A reconfigurable charge pump in 0.13 μm CMOS for agile MEMS actuation," in 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2014: IEEE, pp. 670-673.

- [85] A. Ballo, A. D. Grasso and G. Palumbo, "Charge Pump Improvement for Energy Harvesting Applications by Node Pre-Charging," in IEEE Transactions on Circuits and Systems II: Express Briefs, early access.

- [86] C. Ulaganathan, B. J. Blalock, J. Holleman, and C. L. Britton, "An ultra-low voltage self-startup charge pump for energy harvesting applications," in 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), 2012: IEEE, pp. 206-209.

- [87] D. Suvakovic and C. Salama, "Two phase non-overlapping clock adiabatic differential cascode voltage switch logic (ADCVSL)," in 2000 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No. 00CH37056), 2000: IEEE, pp. 364-365.

- [88] W. C. Athas, L. J. Svensson, J. G. Koller, N. Tzartzanis, and E. Y.-C. Chou, "Low-power digital systems based on adiabatic-switching principles," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 2, no. 4, pp. 398-407, 1994.

- [89] E. Carlson, K. Strunz, and B. Otis, "20mV input boost converter for thermoelectric energy harvesting," in 2009 Symposium on VLSI Circuits, 2009: IEEE, pp. 162-163.

- [90] Y. Ho, Y.-S. Yang, and C. Su, "A 0.2–0.6 V ring oscillator design using bootstrap technique," in IEEE Asian Solid-State Circuits Conference 2011, 2011: IEEE, pp. 333-336.

- [91] Y. Ho, Y.-S. Yang, C. Chang, and C. Su, "A near-threshold 480 MHz 78 μW all-digital PLL with a bootstrapped DCO," *IEEE journal of solid-state circuits*, vol. 48, no. 11, pp. 2805-2814, 2013.

Access

- [92] T. Jiang, J. Yin, P.-I. Mak, and R. P. Martins, "A 0.5-V 0.4-to-1.6-GHz 8-Phase Bootstrap Ring-VCO Using Inherent Non-Overlapping Clocks Achieving a 162.2-dBc/Hz FoM," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 2, pp. 157-161, 2018.

- [93] N. Lotze and Y. Manoli, "A 62 mV 0.13 µm CMOS Standard-Cell-Based Design Technique Using Schmitt-Trigger Logic," *IEEE journal of solid-state circuits*, vol. 47, no. 1, pp. 47-60, 2011.

- [94] M. Dezyani, H. Ghafoorifard, S. Sheikhaei, and W. A. Serdijn, "A 60 mV input voltage, process tolerant start-up system for thermoelectric energy harvesting," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 65, no. 10, pp. 3568-3577, 2018.

- [95] F. Frustaci, M. Alioto and P. Corsonello, "Tapered-Vth Approach for Energy-Efficient CMOS Buffers," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 11, pp. 2698-2707, Nov. 2011.

- [96] J. A. Starzyk, Ying-Wei Jan and Fengjing Qiu, "A DC-DC charge pump design based on voltage doublers," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48, no. 3, pp. 350-359, March 2001.

- [97] G. Palumbo, D. Pappalardo and M. Gaibotti, "Charge-pump circuits: power-consumption optimization," in *IEEE Transactions* on Circuits and Systems I: Fundamental Theory and Applications, vol. 49, no. 11, pp. 1535-1542, Nov. 2002.

- [98] G. Palumbo and D. Pappalardo, "Charge pump circuits with only capacitive loads: optimized design," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 53, no. 2, pp. 128-132, Feb. 2006.

- [99] D. Matoušek, J. Hospodka and O. Šubrt, "Output voltage and efficiency of novelty architecture of charge pump versus clock frequency and MOSFETs sizes," 2016 International Conference on Applied Electronics (AE), Pilsen, 2016, pp. 169-172.

[100] T. Tanzawa and T. Tanaka, "A dynamic analysis of the Dickson

- [100] T. Tanzawa and T. Tanaka, "A dynamic analysis of the Dickson charge pump circuit," in *IEEE Journal of Solid-State Circuits*, vol. 32, no. 8, pp. 1231-1240, Aug. 1997.

- [101] G. DiCataldo and G. Palumbo, "Design of an nth order Dickson voltage multiplier," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 43, no. 5, pp. 414-, May 1996.

- [102] C. Lu, S. P. Park, V. Raghunathan and K. Roy, "Analysis and design of ultra low power thermoelectric energy harvesting systems," 2010 ACM/IEEE International Symposium on Low-Power Electronics and Design (ISLPED), Austin, TX, USA, 2010, pp. 183-188.