The University of Manchester

The University of Manchester Research

# Low-Voltage, Full-Swing InGaZnO-Based Inverters Enabled by Solution-Processed, Ultra-Thin Alx Oy

# DOI:

10.1109/LED.2019.2924714

## **Document Version**

Accepted author manuscript

Link to publication record in Manchester Research Explorer

Citation for published version (APA):

Cai, W., Zhang, J., Wilson, J., & Song, A. (2019). Low-Voltage, Full-Swing InGaZnO-Based Inverters Enabled by Solution-Processed, Ultra-Thin Alx Oy. *IEEE Electron Device Letters*, *40*(8), 1285-1288. https://doi.org/10.1109/LED.2019.2924714

## Published in:

**IEEE Electron Device Letters**

Citing this paper

Please note that where the full-text provided on Manchester Research Explorer is the Author Accepted Manuscript or Proof version this may differ from the final Published version. If citing, it is advised that you check and use the publisher's definitive version.

General rights

Copyright and moral rights for the publications made accessible in the Research Explorer are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Takedown policy

If you believe that this document breaches copyright please refer to the University of Manchester's Takedown Procedures [http://man.ac.uk/04Y6Bo] or contact uml.scholarlycommunications@manchester.ac.uk providing relevant details, so we can investigate your claim.

# Low-Voltage, Full-Swing InGaZnO-Based Inverters Enabled by Solution-Processed, Ultra-Thin Al<sub>x</sub>O<sub>y</sub>

Wensi Cai, Jiawei Zhang, Joshua Wilson and Aimin Song, Senior Member, IEEE

Abstract—High-performance, full-swing inverters implemented with InGaZnO thin-film transistors (TFTs) have been demonstrated capable of operating at a very low voltage. The threshold voltage of the load and drive TFTs were modified through careful change of the gate dielectric anodization voltage. Both the load and drive TFTs show excellent electrical properties including a current on/off ratio >  $10^6$  and a subthreshold swing close to the theoretical limit. As a result, the inverters show high voltage gains up to 34 at a supply voltage of only 1 V as well as high noise margins > 92% of the theoretical maximum. The devices and the fabrication process might have potential applications in future wearable and disposable electronics where low cost and low power are vital.

Index Terms—full-swing inverters, InGaZnO, one-volt operation, high voltage gain and noise margins

## I. INTRODUCTION

OXIDE-SEMICONDUCTOR-BASED thin-film transistors (TFTs) have been shown to be one of most promising candidates for large-area, wearable, and disposable electronics [1, 2]. InGaZnO (IGZO) in particular, has been regarded as an emerging material for active-matrix backplane technology due to its high electron mobility and excellent uniformity over large areas [1]. For battery powered portable electronics, such as wearable devices, low operating voltage and low power consumption are crucial due to the limited lifespan of batteries [3]. For a circuit to operate at an ultralow voltage, i.e., within 1 V, it requires all the integrated components to operate at

This paragraph of the first footnote will contain the date on which you submitted your paper for review. This work was supported in part by the Engineering and Physical Sciences Research Council (EPSRC) under Grant EP/N021258/1, in part by the North-West Nanoscience Doctoral Training Centre, EPSRC under Grant EP/G03737X/1, in part by the UMIP Proof of Principle project, in part by the National Key Research and Development Program of China under Grant 2016YFA0301200, and in part by the National Natural Science Foundation of China under Grant 11374185 and Grant 11304180.

such a voltage. However, it is still challenging to achieve oxide TFTs with both an ultralow operating voltage and excellent electrical performances at the same time. Hence, to date, the supply voltages of the reported oxide-TFT-based circuits are generally  $\geq 5~V$  [4-7].

Due to the difficulties in accomplishing high performance p-type operation in oxide TFTs, especially under an ultralow operating voltage, most oxide-TFT-based logic circuits have been implemented with only *n*-type oxide TFTs. Two types of inverters can be designed based on n-type TFTs, i.e., enhancement-mode load and depletion-mode load inverters. Depletion-mode load inverters are preferable owing to their higher voltage gain and larger output voltage swing than enhancement-mode ones [8]. To realize an IGZO-based depletion-mode inverter, TFTs with different threshold voltages are required. Several techniques can be used to achieve different threshold voltages for two TFTs in one inverter, such as by varying the channel thickness [9], and by treating the top surface with different methods [7, 10]. However, increase of channel layer thickness may result in worsening of subthreshold swing, and different treatments for the top surface might complicate the deposition and potentially damage the channel layer underneath.

The threshold voltage difference can also be created using gate dielectrics with different thicknesses for the load and drive TFTs. However, this typically requires vacuum-based methods, such as sputtering and atomic-layer deposition (ALD), including a break of vacuum and an additional step of patterning, which are not cost-friendly and inefficient. Alternatively, one can use anodization, which is a solutionprocessed, vacuum-free method that can deposit conformal, reliable, ultra-thin oxide layers at room temperature in a very short time [11]. Recently, one-volt IGZO TFTs have been demonstrated by us using anodized, ultra-thin Al<sub>x</sub>O<sub>y</sub> as gate dielectrics [11, 12]. With our anodization method, the thickness of the gate oxide layers can be easily controlled by varying the anodization voltage on the same substrate, enabling the creation of inverters based on solutionprocessing.

Unlike our previous publications on individual TFTs, in this letter, we report full-swing amorphous IGZO (a-IGZO)-based inverters that are capable of operating at low voltages (1 and 0.8 V). Different threshold voltages for the load and drive TFTs were achieved through the modification of anodization

W. Cai, J. Zhang and J. Wilson are with the School of Electrical, Electronic Engineering, The University of Manchester, Manchester M13 9PL, ITK

A. Song is with the School of Electrical, Electronic Engineering, The University of Manchester, Manchester M13 9PL, U.K, and also with the Center of Nanoelectronics, State Key Laboratory of Crystal Materials, and School of Microelectronics, Shandong University, Jinan 250100, China (email: a.song@manchester.ac.uk).

voltages on the same substrate. The excellent electrical properties of both the load and drive TFTs ensure a voltage gain up to 34 at a supply voltage of 1 V with very high noise margins. Such a simple and time efficient method might have potential applications in future low-cost, low-power electronic applications.

## II. EXPERIMENTAL PROCEDURES

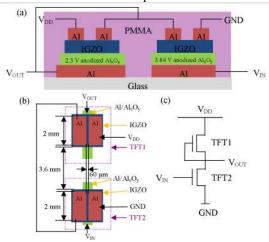

Figs. 1(a) and (b) show schematic diagrams of an IGZO inverter circuit. First, a 200 nm thick layer of Al was thermally evaporated onto a glass substrate through a shadow mask as the gate electrode. Then, the Al gate lines were immersed into a 1 mM citric acid solution to be anodized at 2.3 V, followed by rinsing with IPA and careful drying using a N<sub>2</sub> jet. After that, the gate lines on the bottom half of the substrate were reimmersed into the same solution to be anodized at 3.84 V, followed by the same drying process. With an anodization ratio of 1.3 nm/V for Al [13], approximately 3 and 5 nm thick Al<sub>x</sub>O<sub>y</sub> films were formed on the top and bottom halves of the substrate respectively. The gate lines were then wet etched to break the connection between top and bottom sections.

Fig. 1. Schematic diagrams of (a) cross-sectional and (b) top-view of an IGZO inverter on a glass substrate. (c) Schematic circuit diagram of the inverter. The anodization voltages of the  $Al_xO_y$  in TFT1 and TFT2 are 2.3 and 3.84 V, respectively.

To fabricate the TFTs, a 30 nm thick a-IGZO layer was sputtered on top of the  $Al_xO_y$  using RF magnetron sputtering with a power of 50 W in a pure argon atmosphere followed by thermal evaporation of 200 nm thick Al source/drain electrodes. Both layers were patterned using shadow masks, and the channel width and length were 2 mm and 60  $\mu$ m, respectively. A distance of 3.6 mm was kept between the top and bottom transistors. Finally, a 200 nm thick PMMA layer was spin-coated and baked in  $N_2$  at 90 °C for 30 minutes to form the top encapsulation layer. The electrical performance of the devices was measured in dark at room temperature using an Agilent E5270B semiconductor analyzer and an Agilent E4980A LCR meter. The inverters were measured by connecting the drive and load TFTs externally. The schematic circuit diagram of the inverter is shown in Fig. 1(c).

## III. RESULTS AND DISCUSSIONS

The gate capacitances of the 2.3 and 3.84 V anodized  $Al_xO_y$  were measured using an Al/anodized  $Al_xO_y/Al$  structure and found to be  $\sim 1000$  and  $\sim 775$  nF/cm<sup>2</sup>, respectively.

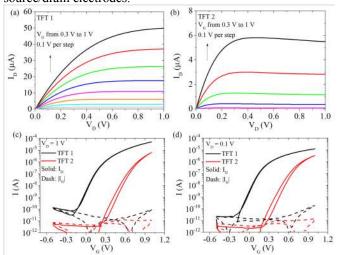

Figs. 2(a) and (b) show the output characteristics of the IGZO TFTs gated with 2.3 V (TFT1) and 3.84 V (TFT2) anodized Al<sub>x</sub>O<sub>y</sub>. Both devices work in *n*-type mode with linear, pinch-off and saturation regimes clearly seen, suggesting a good Ohmic contact between IGZO and Al source/drain electrodes.

Fig. 2. Electrical properties of IGZO TFTs. Output characteristics of (a) TFT1 and (b) TFT2. Transfer characteristics of TFT1 and TFT2 at (c)  $V_D = 1 \text{ V}$  and (d)  $V_D = 0.1 \text{ V}$ . The anodization voltages of the Al<sub>x</sub>O<sub>y</sub> in TFT1 and TFT2 are 2.3 and 3.84 V, respectively.

The corresponding transfer characteristics of TFT1 and TFT2 at different drain voltages are shown in Figs. 2(c) and (d). Both devices exhibit a high current on/off ratio > 10<sup>6</sup> at both  $V_D = 1 \text{ V}$  (saturation regime) and  $V_D = 0.1 \text{ V}$  (linear regime). A lower gate leakage current,  $I_G$ , is found for TFT2, which is due to the slightly thicker Al<sub>x</sub>O<sub>y</sub> formed through anodization (approximately 3 and 5 nm thick Al<sub>x</sub>O<sub>y</sub> films for TFT1 and TFT2, respectively). The subthreshold swing, SS, is found to be 82 and 87 mV/dec for TFT1 and TFT2, respectively, both of which are close to the theoretical limit of SS at 300 K [14]. A small clockwise hysteresis is found in the transfer characteristics of TFT2, which is likely due to the charge trapping effects at the dielectric/channel interface [15] and is considered as the reason for the slightly drop of drain current,  $I_D$ , in the output characteristics shown in Fig. 2(b). The turn-on voltage,  $V_{\rm ON}$ , is -0.2 V for TFT1 and 0.2 V for TFT2. The threshold voltage difference between TFT1 and TFT2 is found to be  $\sim 0.4$  V. The linear mobility,  $\mu_{lin}$ , and saturation mobility,  $\mu_{sat}$ , are calculated to be 6.6 and 6.1 cm<sup>2</sup>/Vs for TFT1, and 5.4 and 5 cm<sup>2</sup>/Vs for TFT2. The electrical properties of both devices are comparable to or even better than most of the low-voltage IGZO TFTs reported previously [11, 16-19], demonstrating the potential for embedding in circuits with low-voltage operations.

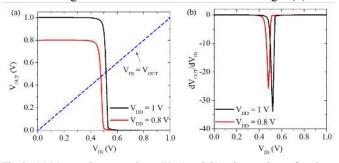

Voltage transfer characteristics of the inverter are shown in Fig. 3(a). For both supply voltages, output voltage at low-states,  $V_{\rm OL}$ , is always 0 V and output voltage at high-states,  $V_{\rm OH}$ , is always the same as the supply voltage,  $V_{\rm DD}$ , suggesting that this is a full swing inverter. The input high voltage ( $V_{\rm IH}$ )

and input low voltage  $(V_{\rm IL})$  are defined as the voltages where the input/output curve has a slope of -1. For  $V_{\rm DD} = 1$  V,  $V_{\rm IL}$ and  $V_{\rm IH}$  are found to be 0.48 and 0.54 V, respectively, showing a narrow transition width  $(V_{IH} - V_{IL})$  of 0.06 V. Narrow transition widths, such as this, can enable improved response times in logic circuits. The noise margin high, N<sub>MH</sub>, is 0.46 V by using  $(V_{OH} - V_{IH})$ , and the noise margin low,  $N_{ML}$ , is 0.48 V which equals  $V_{\rm IL} - V_{\rm OL}$ . For a circuit operation, ideally a balanced noise margin,  $N_{\rm MH} = N_{\rm ML} = V_{\rm DD}/2$ , is achieved. Hence, the achieved values are 92% of the optimal value of  $N_{\rm MH}$  and 96% of the optimal value of  $N_{\rm ML}$ , indicating that the inverter could withstand a high noise level. The switching threshold voltages,  $V_{\rm M}$ , of the inverter, where  $V_{\rm OUT} = V_{\rm IN}$ , are found to be 0.48 and 0.51 V, at  $V_{DD}$  of 0.8 and 1 V, respectively, which are both very close to their ideal value,  $V_{\rm DD}/2$ . As shown in Fig. 2 (c), the bias current gave by the depletion load ( $I_D$  of TFT1 at  $V_G = 0$  V) matches the current of the drive transistor (TFT2) at  $V_G \approx 0.5$  V. Therefore, it is expected that the peak gain occurs at a  $V_{\rm IN}$  of around 0.5 V, which is in agreement with the results shown in Fig. 3(b).

Fig. 3. (a) Measured output voltage ( $V_{\rm OUT}$ ) and (b) voltage gains as functions of input voltage ( $V_{\rm IN}$ ) at different supply voltages ( $V_{\rm DD}$ ).

Fig. 3(b) also shows that high voltage gains of 26 and 34 are achieved at  $V_{\rm DD} = 0.8$  and 1 V respectively, even if the load and drive TFTs have the same channel width to length ratio. These voltage gains are comparable to or even surpass the values reported previously in n-type oxide-TFT-based inverters under similar supply voltages (Table I). The electrical performance of the inverter might be further optimized by modifying the width to length ratio of the load and drive TFTs [20].

A comparison with previously reported *n*-type oxide-TFT-based, low-voltage inverters is shown in Table I. Clearly, all the key parameters of our devices are among the best to date.

Table I: Performance of low-voltage inverters based on  $\textit{N}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-}\textsc{-$

| OXIDE TFTS |            |      |             |             |                   |              |                   |

|------------|------------|------|-------------|-------------|-------------------|--------------|-------------------|

| Ref.       | Channel    | Gain | $V_{ m DD}$ | $V_{\rm M}$ | $N_{\mathrm{MH}}$ | $N_{\rm ML}$ | V <sub>IH</sub> - |

|            | Load/Drive |      | (V)         | (V)         | $V_{ m DD}$       | $V_{ m DD}$  | $V_{\mathrm{IL}}$ |

|            |            |      |             |             |                   |              | (V)               |

| This       | IGZO/IGZO  | 34   | 1           | 0.51        | 46%               | 48%          | 0.06              |

| work       |            | 26   | 0.8         | 0.48        | 38%               | 53%          | 0.07              |

| [8]        | IGZO/IGZO  | 24   | 1           | /           | 59%               | 29%          | 0.12              |

| [21]       | IZO/IGZO   | 43.9 | 2           | /           | /                 | /            | < 0.2             |

| [22]       | ZnO/ZnO    | 32   | 5           | 1.57        | 63%               | 23%          | 0.69              |

| [23]       | SZTO/ZTO   | 6    | 5           | /           | /                 | /            | /                 |

| [24]       | ZnO/ZnO    | 2    | 5           | /           | /                 | /            | /                 |

| [25]       | IGZO/IGZO  | 15.5 | 5           | 15.2        | /                 | /            | /                 |

|            |            | 5.9  | 5           | 4.25        | /                 | /            | /                 |

| [26]       | IGZO/IGZO  | 14   | 5           | /           | 71%               | 12%          | 0.85              |

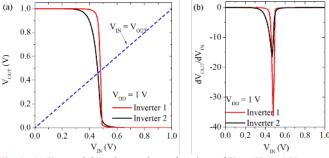

Fig. 4 shows a comparison between the inverters loaded by TFT1 (Inverter 1) and inverters loaded by a 100 M $\Omega$  resistor (Inverter 2). Although both types of inverters show full voltage swings, the comparisons in terms of voltage gains, transition widths and noise margins clearly show that the proposed depletion-load inverters exhibit huge advantages over resistor-load inverters.

Fig. 4. (a)  $V_{\text{OUT}}$  and (b) voltage gains as functions of  $V_{\text{IN}}$  at  $V_{\text{DD}} = 1 \text{ V}$ .

To investigate the long-term stability of the inverter, the devices were measured again after storing in air for 90 days. The superb air stability of the anodized Al<sub>x</sub>O<sub>y</sub>/IGZO TFTs ensures the fabricated inverters to exhibit very small changes of voltage swings, voltage gains, transition widths and switching threshold voltages after the storage, as can be seen in Fig. 5.

Fig. 5. (a)  $V_{\text{OUT}}$  as functions of  $V_{\text{IN}}$  at  $V_{\text{DD}} = 1$  V before and after the storage.

In conclusion, high-performance, full-swing IGZO inverters have been demonstrated to be capable of operating at a very low voltage. The threshold voltage difference for the load and drive IGZO TFTs was achieved by simply varying the anodization voltages for the Al<sub>x</sub>O<sub>y</sub> gate dielectrics on different parts of the substrate. The inverters show a voltage gain of up to 34 and a noise margin close to the ideal value at a low supply voltage of 1 V. Such a method might have potential applications in future low-cost, low-power electronics.

## IV. REFERENCES

- [1] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *nature*, vol. 432, pp. 488-492, 2004. DOI: 10.1038/nature03090

- [2] E. Fortunato, P. Barquinha, and R. Martins, "Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances," Adv. Mater., vol. 24, pp. 2945-2986, 2012. DOI: 10.1002/adma.201103228

- [3] H. Nishide and K. Oyaizu, "Toward flexible batteries," science, vol. 319, pp. 737-738, 2008. DOI: 10.1126/science.1151831

- [4] J. Zhang, J. Yang, Y. Li, J. Wilson, X. Ma, Q. Xin, and A. Song, "High performance complementary circuits based on p-SnO and n-

- IGZO thin-film transistors," *Materials,* vol. 10, p. 319, 2017. DOI: 10.3390/ma10030319

- [5] R. Martins, A. Nathan, R. Barros, L. Pereira, P. Barquinha, N. Correia, R. Costa, A. Ahnood, I. Ferreira, and E. Fortunato, "Complementary metal oxide semiconductor technology with and on paper," *Adv.Mater.*, vol. 23, pp. 4491-4496, 2011. DOI: 10.1002/adma.201102232

- [6] M. Ofuji, K. Abe, H. Shimizu, N. Kaji, R. Hayashi, M. Sano, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, "Fast thin-film transistor circuits based on amorphous oxide semiconductor," IEEE Electron Device Lett., vol. 28, pp. 273-275, 2007. DOI: 10.1109/LED.2007.893223

- [7] M. Wang, L. Liang, H. Luo, S. Zhang, H. Zhang, K. Javaid, and H. Cao, "Threshold voltage tuning in a-IGZO TFTs with ultrathin SnO<sub>x</sub> capping layer and application to depletion-load inverter," *IEEE Electron Device Lett.*, vol. 37, pp. 422-425, 2016. DOI: 10.1109/LED.2016.2525761

- [8] L.-J. Chi, M.-J. Yu, Y.-H. Chang, and T.-H. Hou, "1-V full-swing depletion-load a-In-Ga-Zn-O inverters for back-end-of-line compatible 3D integration," *IEEE Electron Device Lett.*, vol. 37, pp. 441-444, 2016. DOI: 10.1109/LED.2016.2535124

- [9] J.-M. Lee, I.-T. Cho, J.-H. Lee, and H.-I. Kwon, "Full-swing InGaZnO thin film transistor inverter with depletion load," *Jpn. J. Appl. Phys.*, vol. 48, p. 100202, 2009. DOI: 10.1143/JJAP.48.100202

- [10] H.-W. Zan, W.-T. Chen, C.-C. Yeh, H.-W. Hsueh, C.-C. Tsai, and H.-F. Meng, "Dual gate indium-gallium-zinc-oxide thin film transistor with an unisolated floating metal gate for threshold voltage modulation and mobility enhancement," *Appl. Phys. Lett.*, vol. 98, p. 153506, 2011. DOI: 10.1063/1.3578403

- [11] W. Cai, S. Park, J. Zhang, J. Wilson, Y. Li, Q. Xin, L. Majewski, and A. Song, "One-Volt IGZO Thin-Film Transistors with Ultra-Thin, Solution-Processed Al<sub>x</sub>O<sub>y</sub> Gate Dielectric," *IEEE Electron Device Lett.*, vol. 39, pp. 375-378, 2018. DOI: 10.1109/LED.2018.2798061

- [12] W. Cai, J. Wilson, J. Zhang, S. Park, L. Majewski, and A. Song, "Low-Voltage, Flexible InGaZnO Thin-Film Transistors Gated with Solution-Processed, Ultra-Thin Al<sub>x</sub>O<sub>y</sub>," *IEEE Electron Device Lett.*, vol. 40, pp. 36-39, 2019. DOI: 10.1109/LED.2018.2882464

- [13] L. A. Majewski, R. Schroeder, and M. Grell, "Flexible high capacitance gate insulators for organic field effect transistors," J. Phys. D: Appl. Phys., vol. 37, p. 21, 2003. DOI: 10.1088/0022-3727/37/1/005

- [14] L.-Y. Su, H.-Y. Lin, H.-K. Lin, S.-L. Wang, L.-H. Peng, and J. Huang, "Characterizations of amorphous IGZO thin-film transistors with low subthreshold swing," *IEEE Electron Device Lett.*, vol. 32, pp. 1245-1247, 2011. DOI: 10.1109/LED.2011.2160931

- [15] Z. Ye, Y. Yuan, H. Xu, Y. Liu, J. Luo, and M. Wong, "Mechanism and origin of hysteresis in oxide thin-film transistor and its application on 3-D nonvolatile memory," *IEEE Trans. Electron Devices*, vol. 64, pp. 438-446, 2017. DOI: 10.1109/TED.2016.2641476

- [16] Y. Shao, X. Xiao, X. He, W. Deng, and S. Zhang, "Low-voltage a-InGaZnO thin-film transistors with anodized thin HfO<sub>2</sub> gate dielectric," *IEEE Electron Device Lett.*, vol. 36, pp. 573-575, 2015. DOI: 10.1109/LED.2015.2422895

- [17] E. Carlos, R. Branquinho, A. Kiazadeh, P. Barquinha, R. Martins, and E. Fortunato, "UV-Mediated Photochemical Treatment for Low-Temperature Oxide-Based Thin-Film Transistors," ACS Appl. Mater. Interfaces, vol. 8, pp. 31100-31108, 2016. DOI: 10.1021/acsami.6b06321

- [18] P. Ma, J. Sun, G. Liang, Y. Li, Q. Xin, Y. Li, and A. Song, "Half-volt operation of IGZO thin-film transistors enabled by ultrathin HfO<sub>2</sub> gate dielectric," *App. Phys. Lett.*, vol. 113, p. 063501, 2018. DOI: 10.1063/1.5037410

- [19] W. Cai, J. Zhang, J. Wilson, X. Ma, H. Wang, X. Zhang, Q. Xin, and A. Song, "Oxide-Based Electric-Double-Layer Thin-Film Transistors on a Flexible Substrate," *IEEE Electron Device Letters*, vol. 38, pp. 1680-1683, 2017. DOI: 10.1109/LED.2017.2768822

- [20] M. J. Seok, M. H. Choi, M. Mativenga, D. Geng, D. Y. Kim, and J. Jang, "A full-swing a-IGZO TFT-based inverter with a top-gate-bias-induced depletion load," *IEEE Electron Device Lett.*, vol. 32, pp. 1089-1091, 2011. DOI: 10.1109/LED.2011.2157798

- H. Xiao, L. Q. Zhu, C. J. Wan, Y. H. Liu, and R. Liu, "Low-Voltage Depletion-Load Inverter Using Solid-State Electrolyte Gated Oxide Transistors," *IEEE Electron Device Lett.*, vol. 37, pp. 591-594, 2016. DOI: 10.1109/LED.2016.2536699

- [22] H. Xu, Z. Ye, N. Liu, Y. Wang, N. Zhang, and Y. Liu, "Low-Power Transparent RFID Circuits Using Enhancement/Depletion Logic Gates Based on Deuterium-Treated ZnO TFTs," *IEEE Electron Device Lett.*, vol. 38, pp. 1383-1386, 2017. DOI: 10.1109/LED.2017.2737583

- [23] S. Han and S. Y. Lee, "High performance of full swing logic inverter using all n-types amorphous ZnSnO and SiZnSnO thin film transistors," *Appl. Phys. Lett.*, vol. 106, p. 212104, 2015. DOI: 10.1063/1.4921791

- [24] K. Lee, K.-t. Kim, K. H. Lee, G. Lee, M. S. Oh, J.-M. Choi, S. Im, S. Jang, and E. Kim, "ZnO-based low voltage inverter with lowk/high-k double polymer dielectric layer," *Appl.Phys. Lett.*, vol. 93, p. 193514, 2008. DOI: 10.1063/1.3028093

- [25] L. Liang, J. Yu, M. Wang, and H. Cao, "NMOS Logic Inverters Based on Threshold Voltage-Tunable IGZO Transistors," *ECS Trans.*, vol. 75, pp. 261-268, 2016. DOI: 10.1149/07510.0261ecst

- [26] R.-J. Lyu, H.-C. Lin, P.-W. Li, and T.-Y. Huang, "A film-profile-engineered 3-D InGaZnO inverter technology with systematically tunable threshold voltage," *IEEE Trans. Electron Devices*, vol. 63, pp. 3533-3539, 2016. DOI: 10.1109/TED.2016.2585519