The University of Manchester Research

## Low Voltage Operation of IGZO Thin Film Transistors Enabled by Ultrathin Al2O3 Gate Dielectric

**DOI:** 10.1063/1.5003662

#### **Document Version**

Accepted author manuscript

Link to publication record in Manchester Research Explorer

#### Citation for published version (APA):

Ma, P., Du, L., Wang, Y., Jiang, R., Xin, Q., Li, Y., & Song, A. (2018). Low Voltage Operation of IGZO Thin Film Transistors Enabled by Ultrathin Al<sub>2</sub>O<sub>3</sub> Gate Dielectric. *Applied Physics Letters*, *112*, [023501]. https://doi.org/10.1063/1.5003662

Published in: Applied Physics Letters

### Citing this paper

Please note that where the full-text provided on Manchester Research Explorer is the Author Accepted Manuscript or Proof version this may differ from the final Published version. If citing, it is advised that you check and use the publisher's definitive version.

#### **General rights**

Copyright and moral rights for the publications made accessible in the Research Explorer are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

#### **Takedown policy**

If you believe that this document breaches copyright please refer to the University of Manchester's Takedown Procedures [http://man.ac.uk/04Y6Bo] or contact uml.scholarlycommunications@manchester.ac.uk providing relevant details, so we can investigate your claim.

# Low Voltage Operation of IGZO Thin Film Transistors Enabled by Ultrathin Al<sub>2</sub>O<sub>3</sub> Gate Dielectric

Pengfei Ma,<sup>1</sup> Lulu Du,<sup>1</sup> Yiming Wang,<sup>1</sup> Ran Jiang,<sup>1</sup> Qian Xin,<sup>1</sup> Yuxiang Li,<sup>1a)</sup> and Aimin Song<sup>1, 2 a)</sup> <sup>1</sup>Center of Nanoelectronics and School of Microelectronics, Shandong University, Jinan 250100, China <sup>2</sup>School of Electrical and Electronic Engineering, University of Manchester, Manchester M13 9PL, United Kingdom

An ultrathin, 5 nm, Al<sub>2</sub>O<sub>3</sub> film grown by atomic-layer deposition (ALD) was used as a gate dielectric for amorphous indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFTs). The Al<sub>2</sub>O<sub>3</sub> layer showed a low surface roughness of 0.15 nm, a low leakage current and a high breakdown voltage of 6 V. In particular, a very high gate capacitance of 720 nF/cm<sup>2</sup> was achieved, making it possible for the a-IGZO TFTs to not only operate at a low voltage of 1 V, but also exhibit desirable properties including a low threshold voltage of 0.3 V, a small subthreshold swing of 100 mV/decade, and a high on/off current ratio of  $1.2 \times 10^7$ . Furthermore, even under an ultralow operation voltage of 0.6 V, well-behaved transistor characteristics were still observed with an on/off ratio as high as  $3 \times 10^6$ . The electron transport through the Al<sub>2</sub>O<sub>3</sub> layer has also been analyzed, indicating the Fowler–Nordheim tunneling mechanism.

Amorphous indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFTs) have received much attention because of their excellent performance, including high electron mobility, excellent uniformity and stability, optical transparency, and low process temperature.<sup>1-3</sup> As such, a-IGZO TFTs have started replacing amorphous-silicon transistors in large-area displays.<sup>4</sup> A wide variety of applications can also greatly benefit from the ease of deposition of IGZO on flexible substrates, such as wearable electronics<sup>5</sup> and thin-film circuits<sup>6</sup>. These portable electronic products are typically battery hungry, hence making low-voltage operations highly desirable and even necessity. However, most IGZO TFTs reported to date have to be driven by large voltages in order to achieve high mobility and high on/off current ratios.

The simplest method to reduce the operation voltage is reducing the thickness of the gate dielectric layer. However, the thickness reduction of the conventional  $SiO_2$  gate dielectric layer

is limited since the gate leakage current would become severe when the dielectric is too thin. Many researchers have tried to use high-dielectric-constant (high-k) gate dielectrics to reduce the TFT operation voltage. Various high-k materials, e.g., HfLaO,<sup>7, 8</sup> Ta<sub>2</sub>O<sub>5</sub>,<sup>9</sup> BaSrTiO<sub>3</sub>,<sup>10</sup>  $Y_2O_3$ , <sup>11</sup> Al<sub>2</sub>O<sub>3</sub>, <sup>12-16</sup> HoTiO<sub>3</sub>, <sup>17</sup> LaLuO<sub>3</sub>, <sup>18</sup> HfO<sub>2</sub>, <sup>19, 20</sup> LaAlO<sub>3</sub>, <sup>21</sup> have been applied because they simultaneously enable a low leakage current and a low-voltage operation. Shao et al reported low-operation-voltage a-IGZO TFTs using a 20 nm HfO<sub>2</sub> gate dielectric layer.<sup>20</sup> Cheng et al. also demonstrated that 15.5 nm LaAlO<sub>3</sub> a-IGZO TFTs exhibited excellent electrical performances.<sup>21</sup> In addition to these solid-state dielectrics, ionic liquids such as water have also been used as dielectrics to reduce operation voltage.<sup>22,23</sup> For high- k materials, there is a general phenomenon that the bandgap decreases with the increase of k value.<sup>24</sup> Therefore, a highquality dielectric film is necessary to avoid a large leakage current. Among the well-known high-k materials, Al<sub>2</sub>O<sub>3</sub> has a large band gap ( $E_g = 8 \text{ eV}$ ), a high dielectric constant (k = 9.0), a high breakdown field (5-10 MV/cm), strong adhesion to dissimilar materials, and superior thermal and chemical stability.<sup>24</sup> The growth of Al<sub>2</sub>O<sub>3</sub> film is usually done using atomic-layer deposition (ALD) technology which allows highly conformal, pinhole-free films with precise thickness control.

In this work, we fabricate a-IGZO TFTs with Al<sub>2</sub>O<sub>3</sub> layer grown by ALD as the gate dielectric. The Al<sub>2</sub>O<sub>3</sub> films were deposited at 150 °C using alternating precursors of trimethyl aluminum [Al(CH<sub>3</sub>)<sub>3</sub>] (TMA) and H<sub>2</sub>O vapor at a deposition rate of approximately 0.1 nm per cycle. One deposition cycle of Al<sub>2</sub>O<sub>3</sub> consisted of an exposure of TMA for 0.03 s, a purge period with N<sub>2</sub> for 30 s, and an exposure of H<sub>2</sub>O vapor for 0.015 s, followed by a final purge period with N<sub>2</sub> for 30 s. Each deposition cycle lasted about 60 s. The carrier gas was N<sub>2</sub> and the pressure in chamber was 0.015 torr during the deposition. A longer purge time than typical ones in the literature was used here to ensure the quality of the very thin Al<sub>2</sub>O<sub>3</sub> films. Different thicknesses, 30, 10, and 5 nm, have been experimented to study their effects on a-IGZO TFT operations. We show that even a very thin 5 nm Al<sub>2</sub>O<sub>3</sub> film can be a highly reliable dielectric with low leakage. The obtained TFTs exhibit desirable properties for low power operations, including a low threshold voltage ( $V_{\rm T}$ ), a high mobility ( $\mu$ ), a small subthreshold swing (*SS*), and a high on/off current ratio ( $I_{on}/I_{off}$ ). In particular, we are able to operate our a-IGZO TFTs at an extremely low voltage of 0.6 V. This is the lowest operating voltage reported to date,

which may have implications for thin-film technology based low-power electronics.

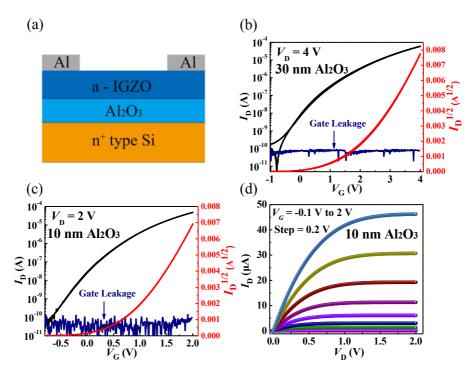

The fabricated IGZO TFT structure is shown in Fig. 1(a). Firstly, the Al<sub>2</sub>O<sub>3</sub> layer (30, 10, and 5 nm) was grown by ALD on n-type heavily doped Si wafers. Then, a 24-nm IGZO was deposited by radio-frequency (RF) sputtering through a shadow mask at room temperature to form the active layer. A 3-in. circular target was used with  $In_2O_3$ :Ga<sub>2</sub>O<sub>3</sub>:ZnO = 1:1:1 mol. %. During the sputtering, the RF power and Ar pressure were maintained at 90 W and 3.65 mTorr, respectively. Finally, Al source and drain contact electrodes were formed by thermal evaporation through a shadow mask. The active channel length (*L*) and channel width (*W*) of the fabricated a-IGZO TFTs are 60 µm and 2000 µm, respectively. Prior to IGZO TFT fabrication, metal-insulator-semiconductor (Al/Al<sub>2</sub>O<sub>3</sub>/n-Si) capacitors were made to investigate the capacitance of the gate dielectric. These devices were characterized by current-voltage (*I-V*) and capacitance-voltage (*C-V*) measurements using the Agilent B2900 Precision Source/Measure Unit (SMU) and E4980A Precision LCR Meter. To further ensure the quality of Al<sub>2</sub>O<sub>3</sub> layer, the surface morphology of the Al<sub>2</sub>O<sub>3</sub> film was investigated by atomic-force microscopy (AFM).

Fig. 1. (a) Schematic cross-sectional view of the a-IGZO TFTs. Transfer characteristics of a-IGZO TFTs with 30 nm (b), and 10 nm (c) Al<sub>2</sub>O<sub>3</sub> gate dielectrics. Output (d) characteristic of an a-IGZO TFT with 10 nm Al<sub>2</sub>O<sub>3</sub> gate dielectrics.

Figures 1(b) and (c) show the transfer characteristics of a-IGZO TFTs with 30 nm and 10

nm Al<sub>2</sub>O<sub>3</sub> gate dielectrics, respectively. After 150 °C thermal annealing in air for 1 h, very little hysteresis is observed in drain current versus gate voltage ( $I_D-V_G$ ) curves. This indicates that no significant mobile bulk oxide charge is present and that the density of slow interface traps is very low, suggesting a high quality of Al<sub>2</sub>O<sub>3</sub> dielectrics.<sup>21</sup> Figure 1(d) shows the output characteristics of an a-IGZO TFT with a 10 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric, exhibiting a well-defined pinch-off behavior. When the Al<sub>2</sub>O<sub>3</sub> thickness was decreased from 30 to 10 nm,  $V_T$  decreased from 1.9 to 0.8 V, and *SS* decreased from 0.39 to 0.26 V/decade. The lower *SS* value in the 10 nm Al<sub>2</sub>O<sub>3</sub> TFT is a result of the increased gate capacitance. The gate leakage of the Al<sub>2</sub>O<sub>3</sub> gate dielectric is below 1 × 10<sup>-8</sup> A/cm<sup>2</sup>, which is among the lowest in reported high-*k* dielectric based TFTs.<sup>8, 12, 18, 21</sup> Importantly, with the decrease of the Al<sub>2</sub>O<sub>3</sub> thickness, the operation voltage reduces from 4 V to 2 V.

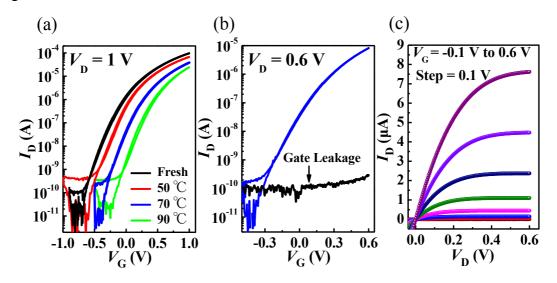

Fig. 2. (a) Transfer characteristics of devices after 1 h thermal annealing with different temperatures. Transfer (b) and output (c) characteristics of a-IGZO TFTs with 5 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric layer under 0.6 V operation voltage.

Given that the gate leakage current remained low as shown in both Figs. 1(b) and (c), we have explored the possibility to further reduce the  $Al_2O_3$  dielectric thickness to 5 nm in order to reduce the operation voltage to 1 V. The as-fabricated devices with 5 nm  $Al_2O_3$  and 10 nm a-IGZO indeed operated under 1 V with a large on/off ratio well beyond  $10^6$  as shown in Fig. 2(a). However, the device needs to be turned off at a gate voltage of - 0.7 V. Unlike  $Al_2O_3$  which was deposited chemically by ALD, sputtered films often have unbalanced stoichiometry due to the high-energy ion bombardment. In the case of oxide deposition, it is common for the sputtered film to contain a large number of oxygen vacancies, resulting in a rather conductive

film. Thermal annealing in air is an effective method to reduce such vacancies.<sup>??</sup> With increase of the annealing temperature,  $V_{\rm T}$  was found to shift in the positive direction (0 V  $\rightarrow$  0.1 V  $\rightarrow$  0.3 V  $\rightarrow$  0.4 V) as shown in Fig. 2(a). To maintain a good carrier mobility and high on/off ratio, we choose 70 °C as the optimum annealing temperature.

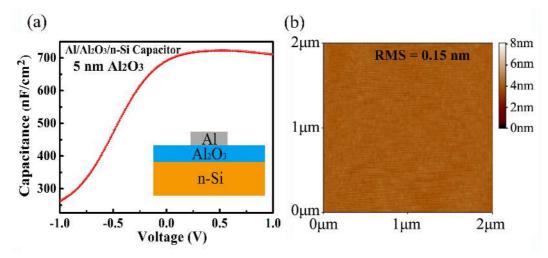

Fig. 3. (a) *C-V* characteristics (main graph) and schematic diagram (inset) of an Al/Al<sub>2</sub>O<sub>3</sub>(5 nm)/n-Si MOS capacitor. (b) AFM image of 5 nm Al<sub>2</sub>O<sub>3</sub> film.

Very thin gate dielectrics have been found to show different dielectric properties from thick ones.<sup>25, 26</sup> To make our calculation of carrier mobility accurate, metal-insulator-semiconductor capacitors were made to determine the capacitance of the gate dielectric ( $C_{ox}$ ). Figure 3(a) and the inset show the C-V characteristics and schematic diagram of an Al/Al<sub>2</sub>O<sub>3</sub> (5 nm)/n-Si capacitor, respectively. A very high capacitance of  $C_{ox} = 720 \text{ nF/cm}^2$  is determined, which is equivalent to the capacitance of a 3.3 nm standard SiO<sub>2</sub> dielectric. The latter, however, would be much more susceptible to leakage current. The surface morphology of the 5 nm  $Al_2O_3$ dielectric film was also studied by AFM, showing a very low root-mean-square (RMS) roughness of 0.15 nm in Fig. 3(b), smaller than the roughness of thicker films which are 0.25 and 0.28 nm for 10 nm and 30 nm Al<sub>2</sub>O<sub>3</sub>, respectively. The interface trap density is known to directly associate with interface roughness between IGZO and gate dielectric. The quality of gate dielectric can also be manifested by the TFT subthreshold swing. Under 1 V operation voltage, the 5 nm Al<sub>2</sub>O<sub>3</sub> based device exhibits a very low SS of 100 mV/decade, which is quiet desirable in order to turn on the transistor effectively at a low power. Furthermore, a low  $V_{\rm T}$  of 0.3 V and a high mobility  $\mu$  of 6.3 cm<sup>2</sup>/Vs were achieved. The extremely small hysteresis indicates very low density of trapping states  $(N_t)$  at the gate dielectric interface, which also

correlates well with the low  $Al_2O_3$  surface roughness. The value of  $N_t$  can be determinate by:

$$SS = \frac{k_{\rm B}T \ln 10}{q} \left[ 1 + \frac{q^2}{C_{ox}} N_t \right]$$

(1)

where  $k_{\rm B}$  is Boltzmann's constant, *T* is the temperature in Kelvin, and *q* is the electron charge. Taking the *SS* value of the 5 nm Al<sub>2</sub>O<sub>3</sub> IGZO TFTs, the interface trap density  $N_{\rm t}$  is found to be  $3.0 \times 10^{12} \,{\rm eV}^{-1} {\rm cm}^{-2}$ , which is among the lowest values in reported Al<sub>2</sub>O<sub>3</sub> TFTs to date.<sup>27</sup>

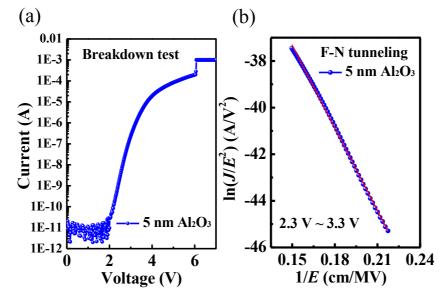

Fig. 4. (a) Breakdown tests for Al/Al<sub>2</sub>O<sub>3</sub>/n-Si MOS devices with 5 nm Al<sub>2</sub>O<sub>3</sub> layer. (b)The liner fitting for leakage current of 5 nm Al<sub>2</sub>O<sub>3</sub> layer by F-N tunneling model.

To test the robustness of the 5-nm-thin  $Al_2O_3$  and study the vertical carrier transport mechanism (related to leakage current), we applied large voltages to the metal-insulatorsemiconductor capacitors. It is quite surprising to discover that the breakdown voltage of 5 nm  $Al_2O_3$  is as high as about 6 V as shown in Fig.4 (a). This again confirms the high quality of the 5 nm  $Al_2O_3$  dielectric film. There are a few possible electron transport mechanisms including direct tunneling, Fowler–Nordheim (F-N) tunneling, Poole-Frenkel emission, and Schottky emission, etc. The F-N tunneling current is given by

$$\frac{J}{E^2} = C_1 \, e^{-C_2/E} \tag{2}$$

where J is the current density and E is the electric field across the oxide.  $C_1$  and  $C_2$  are given by

$$C_1 = q^3 m / 16\pi^2 \hbar m_{ox} \phi_o \tag{3}$$

$$C_2 = \frac{4}{3} \frac{(2m_{ox})^{1/2}}{q\hbar} \phi_0^{\frac{3}{2}}$$

(4)

where q is the electron charge, m and  $m_{ox}$  are the electron mass in free space and in the oxide respectively,  $2\pi\hbar$  is Planck's constant, and  $\phi_o$  is the barrier height. Figure 4 (b) show a liner fitting of the leakage current according to Eq. 2. The dotted line is the experiment result and the red solid line is the fitting. Other transport models do not provide such a good agreement. The fitting in Fig. 4(b) hence indicates that the vertical transport mechanism in our thin Al<sub>2</sub>O<sub>3</sub> dielectrics is F-N tunneling.

We also further tested the TFTs based on 5 nm Al<sub>2</sub>O<sub>3</sub> under lower operation voltages. Even under a 0.6 V bias, a high  $I_{on}/I_{off}$  ratio and well behaved transistor output characteristics were achieved, as shown in transfer and output characteristics in Figs. 2(b) and (c). The mobility is 3.8 cm<sup>2</sup>/Vs, somewhat lower than that at 1 V (6.3 cm<sup>2</sup>/Vs). This is not unusual because carrier trapping by interface states becomes more dominated at low gate voltages. Importantly, even under such low operation voltage, the on current is still about 5 orders of magnitude higher than the leakage current. In Table I, we have compared the key device parameters of our a-IGZO TFTs with previously reported devices, where  $T_{ox}$  is the thickness of gate dielectrics and  $V_{ON}$  represents the operation voltage. Our devices show the lowest operating voltages in oxide semiconductor TFTs, which is favorable for low-power electronics applications.

| Gate                               | Tox  | Von | VT  | SS       | μ                     | $I_{\rm on}/I_{\rm off}$ |

|------------------------------------|------|-----|-----|----------|-----------------------|--------------------------|

| dielectrics                        | (nm) | (V) | (V) | (mV/dec) | (cm <sup>2</sup> /Vs) | Lon/Loff                 |

| $HfLaO^{7}$                        | 300  | 2   | 0.2 | 76       | 25                    | $5 	imes 10^7$           |

| $Ta_2O_5^9$                        | 200  | 3   | 0.3 | 610      | 61.5                  | $1 \times 10^5$          |

| BaSrTiO <sub>3</sub> <sup>10</sup> | 170  | 3   | 0.5 | 60       | 10                    | $8 	imes 10^7$           |

| $Y_2O_3^{11}$                      | 140  | 6   | 1.4 | 200      | 12                    | $1 \times 10^{8}$        |

| $Al_2O_3^{12}$                     | 100  | 5   | 0.4 | 100      | 8                     | $6 	imes 10^7$           |

| $\mathrm{HfO_{2}}^{19}$            | 60   | 0.8 | 0.2 | 90       | 5.9                   | $2.4 	imes 10^7$         |

| HoTiO <sub>3</sub> <sup>17</sup>   | 60   | 8   | 0.1 | 160      | 21.4                  | $1.3 	imes 10^8$         |

| HfLaO <sup>8</sup>                 | 40   | 1.5 | 0.1 | 180      | 22.1                  | $2 	imes 10^5$           |

| LaLuO3 <sup>18</sup>               | 20   | 2   | 0.3 | 310      | 6.6                   | $1 \times 10^3$          |

| $\mathrm{HfO_{2}}^{20}$            | 20   | 2   | 0.2 | 109      | 8.1                   | $1 \times 10^7$          |

| LaAlO <sub>3</sub> <sup>21</sup>   | 15.5 | 1.4 | 0.4 | 68       | 4.1                   | $1 \times 10^5$          |

| (This work)                        | 5    | 0.6 | 0.2 | 100      | 3.8                   | 3 × 10 <sup>6</sup>      |

| Al <sub>2</sub> O <sub>3</sub>     | 5    | 1   | 0.3 | 100      | 6.3                   | $1.2 \times 10^{7}$      |

TABLE I. Comparison of a-IGZO TFTs with different gate dielectrics

In summary, a-IGZO TFTs with an ultrathin 5 nm Al<sub>2</sub>O<sub>3</sub> layer have been demonstrated to be

capable of operating not only at 1 V but also at 0.6 V. Importantly, the TFTs exhibit desirable properties despite the low driving voltages, including a steep subthreshold slope, negligible hysteresis, and high  $I_{on}/I_{off}$  ratio. We also discovered that the breakdown voltage of the 5 nm-thin Al<sub>2</sub>O<sub>3</sub> film is as high as 6 V and the electron transport mechanism through the Al<sub>2</sub>O<sub>3</sub> layer has been analyzed. The results indicate that our low-voltage-driven a-IGZO TFTs may have a great promise for future low-power electronics applications.

This work was financed by the National Key Research and Development Program of China (Grant Nos. 2016YFA0201800 and 2016YFA0301200), the National Natural Science Foundation of China (Grant Nos. 11374185, 11304180 and 11374182), Engineering and Physical Sciences Research Council (EPSRC) (Grant No. EP/N021258/1), China Postdoctoral Science Foundation (2015M582073 and 2016M590634), the Natural Science Foundation of Shandong Province (ZR2013EMQ011), the Natural Science Foundation of Jiangsu Province (BK20151255), Suzhou Planning Projects of Science and Technology (SYG201527 and SYG201616), and the Fundamental Research Funds of Shandong University (2013TB008, 2014QY005 and 2016WLJH44).

## References

<sup>1</sup>B. Zhang, H. Li, X. Zhang, Y. Luo, Q. Wang, and A. Song, Appl. Phys. Lett. 106, 093506 (2015).

<sup>2</sup>L. Du, H. Li, L. Yan, J. Zhang, Q. Xin, Q. Wang, and A. Song, Appl. Phys. Lett. 110, 011602 (2017).

<sup>3</sup>Q. Xin, L. Yan, L. Du, J. Zhang, Y. Luo, Q. Wang, and A. Song, Thin Solid Films 616, 569-572 (2016).

<sup>4</sup>K. Fukuda, Y. Takeda, Y. Yoshimura, R. Shiwaku, L. T. Tran, T. Sekine, M. Mizukami, D. Kumaki, and S. Tokito, Nat. Commun.5, 8 (2014).

<sup>5</sup>Y. S. Rim, S.-H. Bae, H. Chen, N. De Marco, and Y. Yang, Adv. Mater. 28, 4415-4440 (2016).

<sup>6</sup>J. I. Leon, S. Kouro, L. G. Franquelo, J. Rodriguez, and B. Wu, IEEE Trans. Electron Devices 63, 2688-2701 (2016).

<sup>7</sup>N. C. Su, S. J. Wang, and A. Chin, IEEE Electron Device Lett. 30, 1317-1319 (2009).

<sup>8</sup>S. Nai-Chao, W. Shui-Jinn, H. Chin-Chuan, C. Yu-Han, H. Hao-Yuan, C. Chen-Kuo, and A. Chin, IEEE Electron Device Lett. 31, 680-682 (2010).

- <sup>9</sup>C. J. Chiu, S. P. Chang, and S. J. Chang, IEEE Electron Device Lett. 31, 1245-1247 (2010).

- <sup>10</sup>J. B. Kim, C. Fuentes-Hernandez, and B. Kippelen, Appl. Phys. Lett. 93, 242111 (2008).

- <sup>11</sup>H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett. 89, 112123 (2006).

- <sup>12</sup>J. B. Kim, C. Fuentes-Hernandez, W. J. Potscavage, X. H. Zhang, and B. Kippelen, Appl. Phys. Lett. 94, 142107 (2009).

- <sup>13</sup>A. Suresh, P. Wellenius, V. Baliga, H. Luo, L.M. Lunardi, and J.F. Muth, IEEE Electron Device Lett. 31,317-319 (2010).

- <sup>14</sup>C.H. Wu, K.M. Chang, S.H Huang, I.C. Deng, C.J. Wu, W.H. Chiang, and C.C. Chang, IEEE Electron Device Lett. 33, 552-554 (2012).

- <sup>15</sup>C.R. Park, J.H. Hwang, Ceramics International. 40, 12917–12922 (2014).

- <sup>16</sup>X.W Ding, H. Zhang, J.H. Zhang, J. Li, W.M. Shi, X.Y. Jiang, Z.L. Zhang, Materials Science in Semiconductor Processing. 29, 69–75 (2015).

- <sup>17</sup>T.-M. Pan, C.-H. Chen, J.-H. Liu, J.-L. Her, and K. Koyama, IEEE Electron Device Lett. 35, 66-68 (2014).

- <sup>18</sup>I.C. Kun, H. Hsiao-Hsuan, C. Chun-Hu, L. Kai-Yu, L. Shang-Rong, and A. Chin, IEEE Electron Devices and Solid-State Circuits. 1-2, (2013).

- <sup>19</sup>C. H. Lu, T. H. Hou, and T. M. Pan, IEEE Trans. Electron Devices. 63, 5060-5063 (2016).

- <sup>20</sup>Y. Shao, X. Xiao, X. He, W. Deng, and S. D. Zhang, IEEE Electron Device Lett. 36, 573-575 (2015).

- <sup>21</sup>C. H. Cheng, K. I. Chou, and H. H. Hsu, Journal of Nanoscience and Nanotechnology. 15, 1486-1489 (2015).

- <sup>22</sup>Y. Huang, E. Sutter, J.T. Sadowski, M. Cotlet, O.L.A. Monti, D.A. Racke, M.R. Neupane, D.

Wickramaratne, R.K. Lake, P. Sutter, et al. ACS Nano. 8, 10743–10755 (2014).

- <sup>23</sup>Y. Huang, J.S. Qiao, K. He, S. Bliznakov, E. Sutter, X.J. Chen, D. Luo, F.K. Meng, D. Su, P. Sutter, et al. Chem. Mater. 28, 8330–8339 (2016).

- <sup>24</sup>J. Robertson, R.M. Wallace, Mater. Sci. Eng. R, 88 (12), 1-41 (2015).

- <sup>25</sup>M.D. Gronera, J.W. Elama, F.H. Fabreguettea, S.M. Georgea, Thin Solid Films, 413, 186-

197 (2002).

- <sup>26</sup>A. Daus, C. Vogt, N. Münzenrieder, L. Petti, S. Knobelspies, G. Cantarella, M. Luisier, G.A. Salvatore, and G. Tröster, IEEE Trans. Electron Devices. 64, 2789-2796 (2017).

- <sup>27</sup>X. Ding, J. Zhang, W. Shi, H. Ding, H. Zhang, J. Li, X. Jiang, Z. Zhang, and C. Fu, Mater. Sci. Semicond. Process. 29, 326-330 (2015).