# Macro-model of Spin-Transfer Torque based Magnetic Tunnel Junction device for hybrid Magnetic-CMOS design

#### Weisheng Zhao, Eric Belhaire, Quentin Mistral, Claude Chappert

Institut d' Electronique Fondamentale CNRS / University of Paris South, France

Virgile Javerliac, Bernard Dieny

SPINTEC, CEA, France

**Elsa Nicolle** STMicroelectronics Grenoble, France

IEEE BMAS-- San Jose, California, USA 14-15/09/2006

# Hybrid Magnetic-CMOS design

- MRAM (Magnetic RAM)

- Applications : Magnetic logic, FPGAs,

# STT (Spin-Transfer Torque) based MRAM

- STT based Magnetic Tunnel Junction (MTJ) introduction

- Model presentation : three main equations

- Electrical Macro model development and Simulations

- Conclusion and perspective

# **MRAM Introduction**

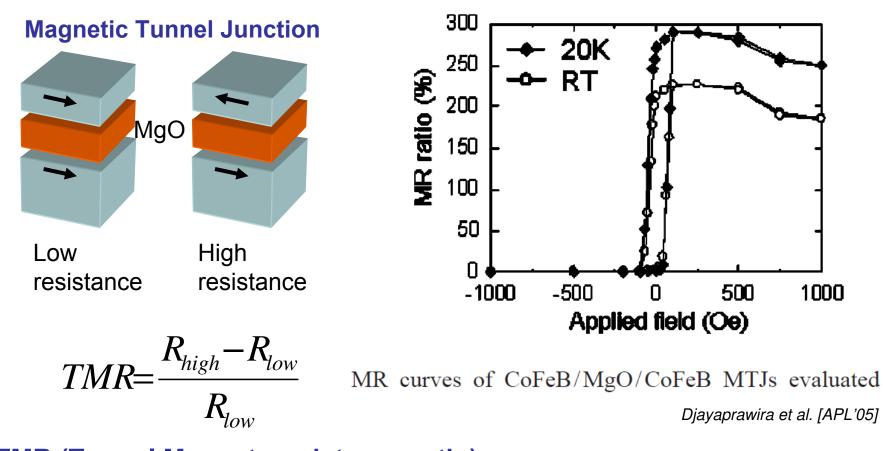

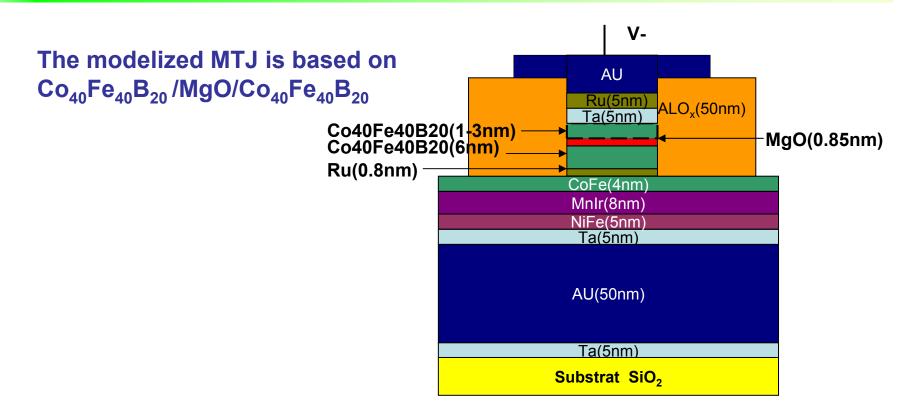

TMR (Tunnel Magnetoresistance ratio)  $\rightarrow$  70% with Al<sub>x</sub>O<sub>y</sub> barrier  $\rightarrow$  230% with MgO barrier

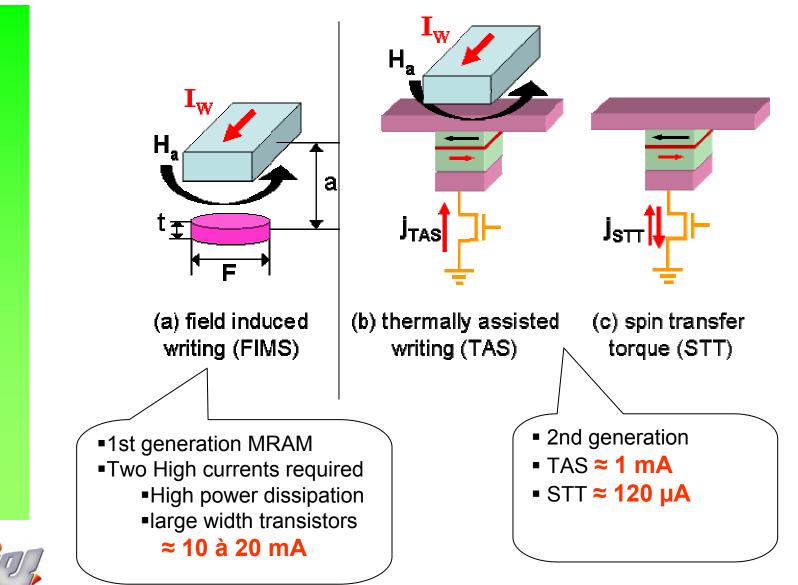

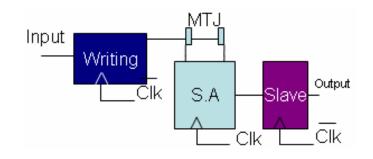

### Hybrid Magnetic-CMOS design Writing a MTJ : 3 technologies

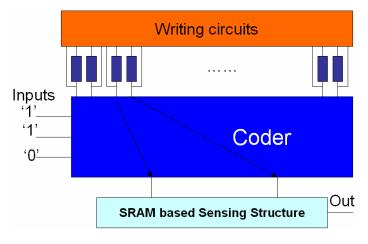

# Hybrid Magnetic-CMOS design

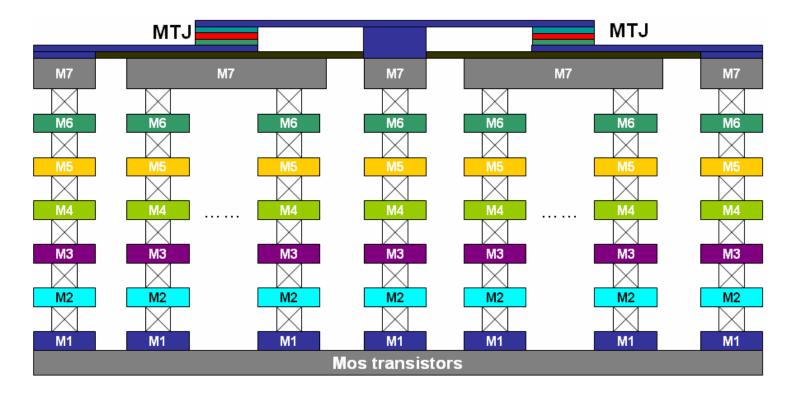

#### MTJs are implemented on top of the CMOS layers

# **Advantages**

- □ Bring non-volatility property to CMOS

- □ High reading speed (10-20ns)

- □ High writing speed (<1ns)

- □ Large retention time more than 10 years

- □ High density (MTJ : 113nm\*75nm)

- □ More than 10<sup>12</sup> re-programming cycles

## Constraints

More fabrication masks than standard CMOS

Power dissipation with 1st gen writing techno.

# Hybrid Magnetic-CMOS design APPLICATIONS

• MRAM memory: IBM, Freescale, ...

• Secured FPGA:

Non volatile FLIP-FLOP (presented at ICICDT06, Italy)

3-input LUT with non-volatile connfiguration (will be presented at ICSICT06, Shanghai)

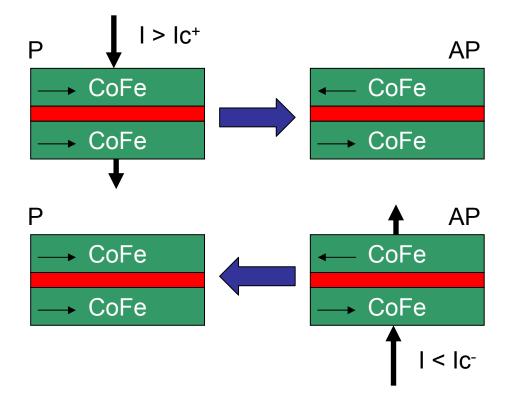

# STT (Spin-Transfer Torque) based MTJ

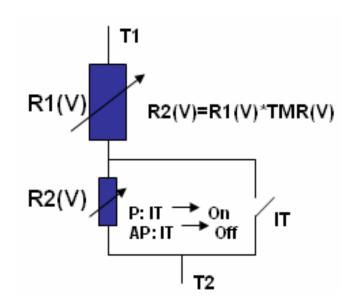

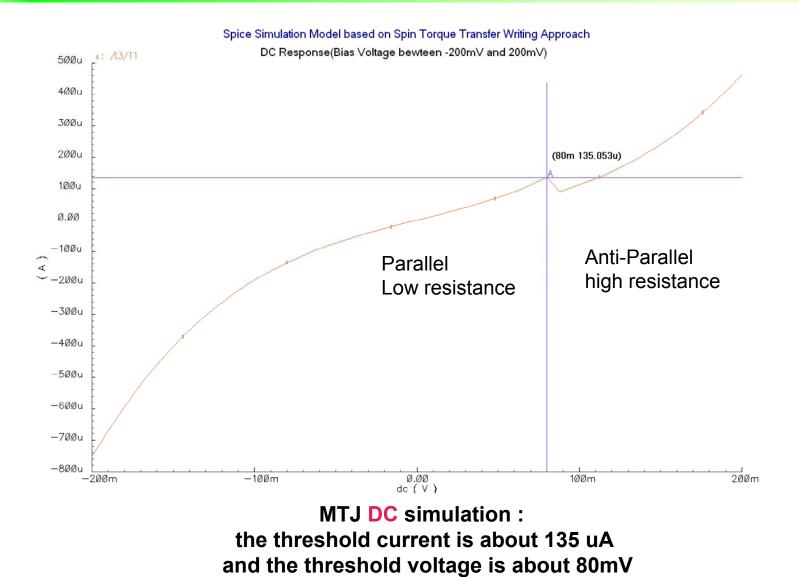

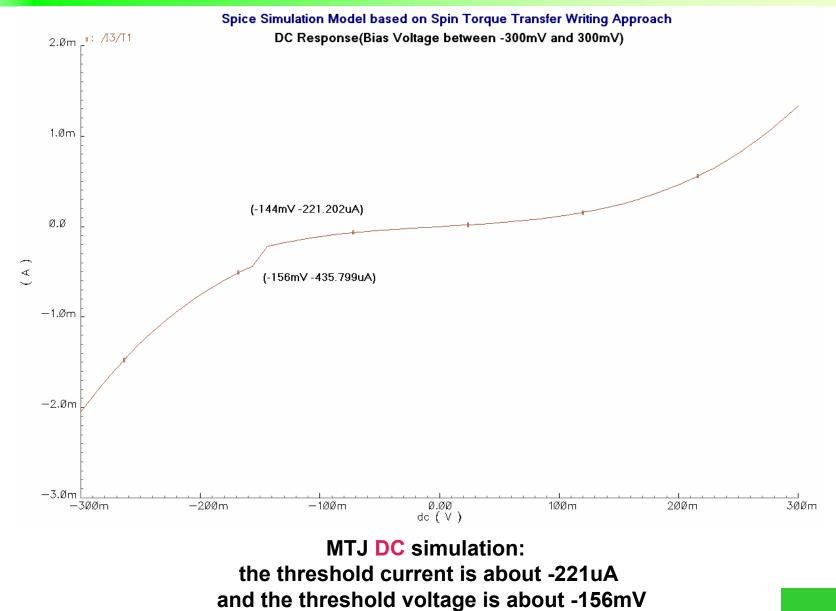

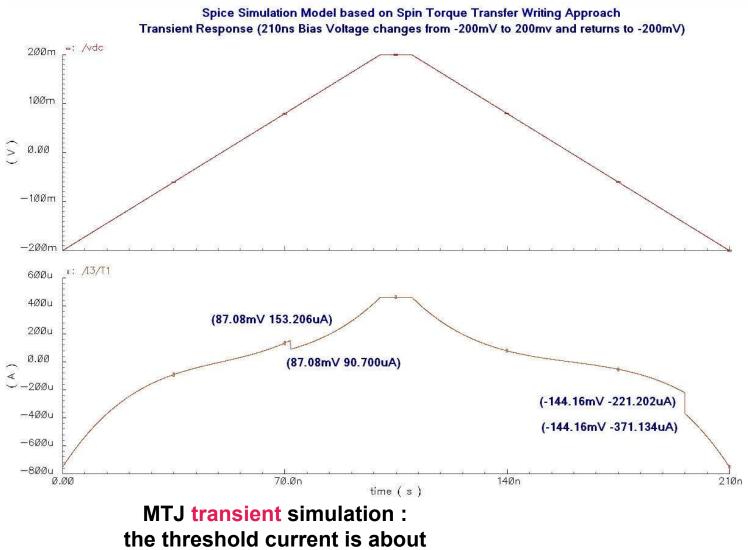

The MTJ state changes :

- from Parallel (P) to Anti-parallel (AP) if current density I >  $I_c^+$

- from AP to P if  $I < -I_c^-$

# STT (Spin-Transfer Torque) based MTJ

#### 3 equation sets are implemented in the behavioral model :

- 1. Slonczewski critical model

- 2. Brinkman resistance model

- 3. TMR effect bias-voltage dependence model

# STT (Spin-Transfer Torque) based MTJ 1st eq set : Slonczewski model

$$J_{C} = J_{C0} \left\{ 1 - \left(\frac{k_{B} \times T}{E}\right) \ln(\tau_{m} \times f_{0}) \right\}$$

$$J_{C0} = \alpha \times \gamma \times e \times M_{s} \times t \times (H_{ext} \pm H_{ani} \pm H_{d} / 2) / u_{B} \times g$$

$$E = \frac{M_{s} \times V \times H_{c}}{2}$$

$$g = \left[ -4 + (P^{-1/2} + P^{1/2}) \times (3 + \cos\theta) / 4 \right]^{-1}$$

Hext: the external field: -190e

Hani: the in-plane uniaxial magnetic anisotropy field 100 Oe

Hd: the out-of-plane magnetic anisotropy induced by the demagnetization field 13000 Oe

ζm: the measurement time 1s

α: Gilbert damping coefficient 0,01

kB: Boltzmann constant, 1.38×10-23J/K

e: An elementary charge 1.60 x 10-19 C

f0: the attempt frequency 109Hz

Hc: coercive field

#### **Parameters:**

t: height of the free layer(1-3nm)

uB: Bohr magneton constant, 9.27×10-28J/Oe •Θ: parallel: 0 and anti-parallel: π Ms: 1.3 T (CoFe) =13000 Oe

- •V: volume of the free layer (80×240 nm2 ×t)

- y: gyromagnetic constant =221000/2\*pi

# STT (Spin-Transfer Torque) based MTJ 2nd eq set : Brinkman conductance model

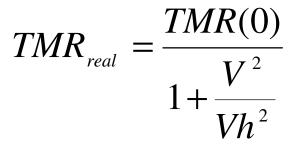

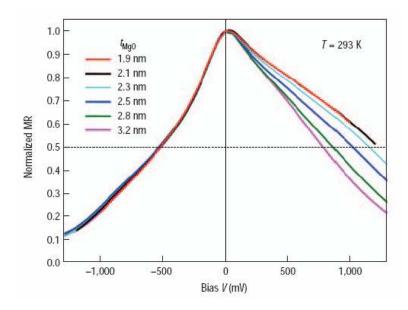

#### STT (Spin-Transfer Torque) based MTJ 3rd eq set : TMR bias-voltage dependence model

TMR (0): Resistance Ratio between low and high resistance with 0V bias-voltage. Vh: the bias voltage where TMRreal =0.5\*TMR (0)

Relation between bias voltage *V* and the normalized MR ratio at room temperature

Yuasa et al, Nature Materials

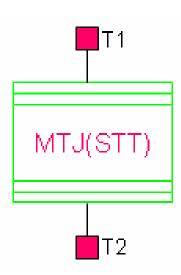

#### Simulation Environment:

- 1. STmicroelectronics 90nm design kit

- 2. Cadence spectre simulator

- 3. Verilog-A language

Simulation model symbol

#### **Resistance equivalent circuit**

- The model has been developed to simulate hybrid MTJ/CMOS architectures

- The model is based on next generation Spin-Transfer Torque (STT) writing technique

- The current model is in the static writing mode and is sufficient for the magnetic FPGA simulation

- The dynamical switching behavior will be presented in the future.

- The main applications are the design of MRAM and Magnetic FPGA