### Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

July 2008

## Main determinants for III-V metal-oxidesemiconductor field-effect transistors (invited)

P.D.Ye

Birck Nanotechnology Center and School of Electrical and Computer Engineering, Purdue University, yep@purdue.edu

Follow this and additional works at: http://docs.lib.purdue.edu/nanopub

Ye, P. D., "Main determinants for III-V metal-oxide-semiconductor field-effect transistors (invited)" (2008). *Birck and NCN Publications*. Paper 134. http://docs.lib.purdue.edu/nanopub/134

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# Main determinants for III–V metal-oxide-semiconductor field-effect transistors (invited)

Peide D. Ye<sup>a)</sup>

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907

(Received 2 December 2007; accepted 10 March 2008; published 30 June 2008)

Lacking a suitable gate insulator, practical GaAs metal-oxide-semiconductor field-effect transistors (MOSFETs) have remained all but a dream for more than four decades. The physics and chemistry of III–V compound semiconductor surfaces or interfaces are problems so complex that our understanding is still limited even after enormous research efforts. Most research is focused on surface pretreatments, oxide formation, and dielectric materials; less attention is paid to the III–V substrate itself. The purpose of this article is to show that device physics more related to III–V substrates is as important as surface chemistry for realizing high-performance III–V MOSFETs. The history and present status of III–V MOSFET research are briefly reviewed. A model based on the charge neutrality level is proposed to explain all experimental work he performed on III–V MOSFETs using *ex situ* atomic-layer-deposited high-*k* dielectrics. This model can also explain all reported experimental observations on III–V MOSFETs using *in situ* molecular-beam-expitaxy-grown  $Ga_2O_3(Gd_2O_3)$  as a gate dielectric. Related perspectives are also discussed to understand III–V MOS capacitance-voltage measurements. © 2008 American Vacuum Society. [DOI: 10.1116/1.2905246]

#### **I. INTRODUCTION**

GaAs metal-oxide-semiconductor field-effect transistors (MOSFETs) have been a subject of study for several decades. The renewed research thrust is for advanced ultralarge-scale-integration digital applications or complementary metal-oxide-semiconductor (CMOS) technology beyond the 22 nm node by using III-V compound semiconductors as conduction channels to replace traditional Si or strained Si, integrating novel high-k dielectrics with these high-mobility materials, and heterogeneously incorporating them on Si or silicon on insulator. The main obstacle to realizing a GaAs MOSFET technology with commercial value is the lack of high-quality, thermodynamically stable gate dielectric insulators on GaAs or III-V that can match device criteria similar to SiO<sub>2</sub> on Si. Our understanding of the interface physics and chemistry of III-V's is still quite limited, though enormous research efforts have been invested in this field. The literature on this subject covers the past 40 years and appears in many journals and conference proceedings. Understanding these studies requires considerable effort by seasoned researchers, and even more for those new in the field. The purpose of this article is to (i) provide readers with a brief overview on the history and current status of III-V MOSFET research, (ii) propose the charge-neutralitylevel (CNL) based model to explain all experimental work on III-V MOSFETs using ex situ atomic-layer-deposited (ALD) high-k dielectrics and also in situ molecular-beamexpitaxy (MBE) grown Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) gate dielectric, and (iii) provide some guidelines for III-V MOS interface studies.

#### **II. HISTORY AND CURRENT STATUS**

The advantage of GaAs MOSFET over its Si counterpart has long been recognized because the electron mobility in GaAs is five or more times higher than that in Si. The GaAs MOSFET research has its own phenomenal cycles coincidently with the well-known ten-year semiconductor industrial business cycles. The first GaAs MOSFET work was reported by Becke and White by the Radio Corporation of America in 1965.<sup>1,2</sup> Although deposited SiO<sub>2</sub> is used as the gate dielectric with a large amount of interface traps, the devices are successfully operated in the several-hundredmegahertz frequency range showing the feasibility of this approach. It was quickly realized that SiO<sub>2</sub> is not the right gate dielectric for GaAs, which sparked an enormous research effort in the following decades with a search for a low-defect, thermal-dynamically stable gate dielectric for GaAs. The efforts can be divided into two sceneries: deposited oxide and native oxide.

A variety of dielectrics and techniques have been investigated. The well-studied dielectrics on GaAs include pyrolytically deposited silicon dioxide,<sup>1</sup> silicon nitride,<sup>2</sup> silicon oxynitride,<sup>3</sup> and aluminum oxide.<sup>4</sup> All these processes require relatively high temperatures ranging from ~350 to ~600 °C. The chemical reaction between GaAs and oxygen in gas ambient is expected to form Ga oxide, As oxide, and even a large number of vacancies due to the high volatility of As. A low-temperature process is believed to be essential for obtaining a high-quality interface.<sup>5</sup> Plasma-enhanced deposition with the process temperature lower than 200 °C was attempted,<sup>6</sup> though it could potentially induce more defects or fixed charges on the GaAs surface or interface due to the induction of plasma.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: yep@purdue.edu

In addition to conventional physical vapor deposition and chemical vapor deposition (CVD), MBE approach was also used to form insulating films on GaAs after it began to be widely used to grow III-V compound semiconductor heterostructures at the end of 1970s. For example, high-resistive AlGaAs (Ref. 7) or low-temperature-grown GaAs (Ref. 8) were used as an insulating layer for the GaAs channel. However, relatively high gate leakage current limits the wide application of these approaches. To improve the barrier heights at the heterojunction interface, thermal oxidation of AlAs epilayers grown on GaAs using MBE was also investigated.<sup>9</sup> The difficulty of this approach is to control the oxidation process to terminate at the AlAs-GaAs interface, though the large difference exhibits in the rate of oxide formation of AlAs and GaAs. The research in this direction is still currently active.<sup>10</sup>

Motivated by the success of thermally oxidized SiO<sub>2</sub> on Si, using native oxides on GaAs as gate dielectrics was also intensively studied at the very beginning. Some representative approaches include thermal oxidation,<sup>11</sup> wet-chemical anodization,<sup>12,13</sup> dc and rf plasma oxidation,<sup>14-18</sup> laserassisted oxidation,<sup>19</sup> vacuum ultraviolet photochemical oxidation,<sup>20</sup> and photowash oxidation.<sup>21</sup> None is optimistic as a feasible approach leading to a commercial GaAs MOS-FET technology. One general observation is that the native oxide is not stable, mostly leaky with low dielectric breakdown strength, and cannot be forward biased beyond a few volts. All these studies are essential to enrich our understanding of chemistry and physics properties of III-V interfaces. Although some controversies exist within much experimental data, there is consensus that a significant amount of  $As_2O_3$ ,  $As_2O_5$ , and elemental As in native oxides pin the Fermi level of GaAs and are not favorable for an ideal gate dielectric. The book Physics and Chemistry of III-V Compound Semiconductor Interfaces, edited by C.W. Wilmsen and published in 1985, summarizes most of the experimental work of the 1970s and early 1980s.<sup>22</sup>

A variety of models on semiconductor interfaces were also developed at the same time beyond the Mott-Schottky model (1938), Bardeen's surface states model (1947) and Anderson's electron affinity model (1962). Some representative works include Cowley and Sze's interfacial layer model (1965),<sup>23</sup> Heine's metal induced gap state model (1965),<sup>24</sup> Tejedor and Flores' model on line-up at CNL (1978),<sup>25</sup> Spicer's unified defect model (UDM) (1980),<sup>26</sup> Hasegawa and Ohno's disorder-induced gap state (DIGS) model (1986),<sup>27</sup> and Tersoff's dielectric midgap energy model (1984 and 1985).<sup>28,29</sup> All these works strongly influenced semiconductor device research, including III-V MOS. For example, Spicer's extensive experiments, published in 1980, concluded that the Schottky-barrier formation on III-V semiconductors is due to defects formed near the interface by deposition of the metal or any chemisorption of oxygen.<sup>30</sup> This model also applies to the formation of states at III-V oxide interface states. Fermi-level position in GaAs is pinned at the midgap whether or not it is a metal-semiconductor or oxidesemiconductor interface.

in large-scale integrated circuits. However, significant progress was made on high-performance microwave GaAs metal-semiconductor field-effect transistors, pioneered by Hooper and Lehrer,<sup>31</sup> using a GaAs Schottky barrier directly. The development of MBE and metal-organic CVD technologies in the 1970s made heterojunctions, quantum wells, and superlattices practical. In Bell Labs, Dingle et al. first demonstrated enhanced mobility in the AlGaAs/GaAs modulation-doped superlattice in 1978.<sup>32</sup> Stormer *et al.* subsequently reported a similar effect using a single AlGaAs/GaAs heterojunction,<sup>33</sup> which led to the discovery of the fractional quantum Hall effect in 1981. In 1980, a Japanese group led by Mimura applied a similar concept and invented the high-electron-mobility transistor (HEMT).<sup>34</sup> Similar work was also reported later the same year by Delagebeaudeuf and others.<sup>35</sup> GaAs HEMT eventually became a commercialized technology, finding broad applications in the communication, military, and aerospace industries today. GaAs MOSFET research did not continue on a large scale after the successful introduction of GaAs HEMT. The search for suitable dielectrics or passivation layers on

Fermi-level pinning in III-V semiconductors dampened

the enthusiasm among III-V researchers to compete with Si

GaAs continues. In 1987, researchers at Bell Labs discovered that a class of sulfides [e.g.,  $Li_2S$ ,  $(NH_4)_2S$ ,  $Na_2S \cdot 9H_2O$ ] was able to passivate the GaAs surface and provide excellent electronic properties to GaAs surfaces.<sup>36,37</sup> The work generated new interest in GaAs MOSFETs using sulfur passivation before dielectric deposition. Hundreds of papers were published related to GaAs sulfur passivation. However, sulfur passivation did not become a technology because sulfur is an unstable material with very low thermal budget. Nevertheless, it is still very scientifically interesting. Sulfur, as a group VI element next to oxygen, has the same electron number in its outer shell as oxygen, but is less chemically reactive. A few monolayers of sulfur can passivate a pristine GaAs surface in certain conditions and prevent GaAs from oxidation to form As oxides. Sulfur passivation is still used in today's research. Other work on effective passivation of GaAs using hydrogen or nitrogen plasma was also reported by the IBM group.<sup>38</sup> Another interesting approach uses a very thin amorphous or crystalline Si layer as an interfacial control layer (ICL) between GaAs and SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>.<sup>39-42</sup> This approach was intensively studied in the  $1990s^{43-45}$  and was recently adopted to integrate with high-k HfO<sub>2</sub> gate dielectrics on GaAs.<sup>46-49</sup> The real effect of this Si ICL, in particular, on capacitance-voltage (C-V) characteristics, needs further investigation.

In 1995, Passlack and Hong at Bell Labs reported that *in* situ deposition of  $Ga_2O_3(Gd_2O_3)$  dielectric film on a GaAs surface by electron-beam evaporation from single-crystal  $Ga_5Gd_3O_{12}$  produced MOS structures on GaAs with a low interface trap density  $(D_{it})$ .<sup>50–52</sup> Because the experiment is realized in an ultrahigh-vacuum (UHV) connected multi-chamber MBE system, it is usually called MBE-grown  $Ga_2O_3(Gd_2O_3)$ . A series of device work, mainly led by Hong and Ren, was done at Bell Labs after this breakthrough in

materials science. It included GaAs depletion-mode (D-mode) and enhancement-mode (E-mode) MOSFETs,<sup>53,54</sup> InGaAs enhancement-mode MOSFETs,<sup>55</sup> GaAs complementary MOSFETs,<sup>56</sup> and GaAs power MOSFETs.<sup>57</sup> This Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) dielectric device work continues at Agere Systems,<sup>58</sup> a spin-off from Bell Labs and Lucent Technologies, and National Tsinghwa University in Taiwan. In 2003, Passlack et al. at Motorola/Freescale began reporting on series of work modifying the previous  $Ga_2O_3(Gd_2O_3)$ dielectric process and using a Ga2O3 template in Gd<sub>x</sub>Ga<sub>0.4-x</sub>O<sub>0.6</sub>/Ga<sub>2</sub>O<sub>3</sub> dielectric stacks on GaAs.<sup>59</sup> An implant-free enhancement-mode device concept was introduced, and good device performance was demonstrated in 2006 to eliminate the difficulty in realizing the inversion operation due to the relative low thermal budget of III-V and gate dielectric stacks.<sup>60</sup> UHV scanning tunneling microscopy reveals that the unpinning of the GaAs Fermi level results from Ga<sub>2</sub>O restoring the surface As and Ga atoms to nearbulk charge.<sup>61</sup>

The strong investment in research on deposited high-k dielectrics for Si CMOS technologies began in the late 1990s.<sup>62</sup> High-k research has since flourished, in particular, the use of ALD method for fabricating Si-based high-k MOS devices. At the end of 2001, Ye and Wilk at Bell Labs/Agere Systems started to work on ALD high-k Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> on GaAs and other III-V materials. A series of D-mode MOS-FETs on GaAs, InGaAs, and GaN using ALD Al<sub>2</sub>O<sub>3</sub> as gate dielectrics was demonstrated.<sup>63-67</sup> ALD is an *ex situ*, robust, and manufacturable process that attracts wider interest in academia and industry. The work on ALD integration with high-mobility channel materials continues and has been enhanced by Ye's group at Purdue University. Detailed interface studies were carried out to demonstrate the unpinning of the Fermi level in III-V semiconductors using ALD high-k dielectrics,<sup>68–73</sup> including the fundamental understanding of the ALD chemical process on GaAs reported by other groups.<sup>74-76</sup> High-performance inversion-mode III-V MOS-FETs were demonstrated with unprecedented drain current as high as 1.05 A/mm and transcondcutance as high as 0.35 S/mm.<sup>77–81</sup> This is the first surface-channel device in III-V with drain current beyond 500 mA/mm. In-rich In-GaAs is identified as the potential channel material for the future 22 nm technology node or beyond with higher effective mobility and manageable band gap for low drain voltage. The fundamental understanding on this successful demonstration is discussed in Sec. III. Currently, many research groups are working on ALD III-V MOSFETs.<sup>82-85</sup>

The new cycle of interest in III–V MOSFETs was initiated by Intel in 2005. Intel is starting to look seriously for alternative device technologies beyond Si CMOS. III–V is one of its main focuses, with the excellent publications on InSb-based quantum well transistors in collaboration with QinetiQ.<sup>86,87</sup> We are hoping that the current III–V research in the Si CMOS community is at the similar stage as when the high-*k* concept was introduced at the end of 1990s. After collective efforts in academia and industry, we were able to

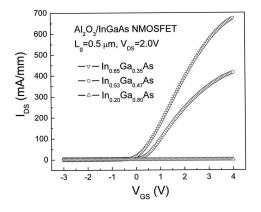

FIG. 1.  $I_{ds}$  vs  $V_{gs}$  at  $V_{ds}=2$  V for In<sub>0.20</sub>Ga<sub>0.80</sub>As, In<sub>0.53</sub>Ga<sub>0.47</sub>As, and In<sub>0.65</sub>Ga<sub>0.35</sub>As MOSFETs using Al<sub>2</sub>O<sub>3</sub> as gate dielectrics.

make this long-standing GaAs MOSFET dream become a real commercial technology as the successful story of high-k in Si CMOS.

#### III. CHARGE-NEUTRALITY-LEVEL MODEL FOR III-V MOSFETS

For the 22 nm technology node or beyond, only the inversion-type enhancement-mode III-V MOSFET is of interest. Inversion-mode surface-channel In<sub>x</sub>Ga<sub>1-x</sub>As MOS-FETs with In concentrations of 20%, 53%, 65%, and 75% integrated with ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and HfAlO were systematically studied at Purdue University. The details of device fabrication are described in Refs. 77-81. Figure 1 shows the comparison of dc transfer characteristic at  $V_{ds}=2$  V on In<sub>0.20</sub>Ga<sub>0.80</sub>As, In<sub>0.53</sub>Ga<sub>0.47</sub>As, and In<sub>0.65</sub>Ga<sub>0.35</sub>As MOSFETs using Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. The device performance has a significant jump to 430 mA/mm drain current on In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET, compared to 0.2 mA/mm on In<sub>0.20</sub>Ga<sub>0.80</sub>As MOSFET, and continues improving to 670 mA/mm drain current on In<sub>0.65</sub>Ga<sub>0.35</sub>As MOSFET. The gate length of all three devices is 0.5  $\mu$ m. The maximum drain current has the potential to increase further by reducing gate length and/or implementing InGaAs channels with more In concentration.<sup>80</sup> Note that most commercial GaAs technology, such as pseudomorphic HEMT (pHEMT), has a maximum drain current around 400 mA/mm at 0.25  $\mu$ m gate length. For GaAs pHEMT, due to its high low-field mobility, the maximum drain is mainly limited by the saturation velocity, modulation doping concentration, and heterostructure itself. The maximum drain current saturates at  $5-10 \ \mu m$  gate length and does not scale with gate length for short gate-length devices. In contrast to GaAs pHEMT, the demonstrated surface-channel InGaAs MOSFET, similar to real Si MOSFET, has gate-length scalability down to the submicron scale.<sup>77–81</sup> Record high maximum drain current of 1.05 A/mm is demonstrated by reducing gate length to 0.4  $\mu$ m.<sup>81</sup> The maximum inversion current is also related to electrical-field-induced surface potential or band bending. With further improved interface quality and improved het-

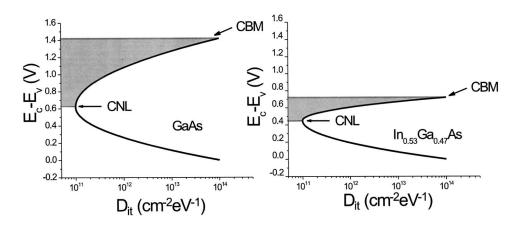

FIG. 2. Schematic for the parabolic  $D_{it}$  distribution within energy band of GaAs and  $In_{0.53}Ga_{0.47}As$ . The CNL is aligned 0.8 eV below CBM for GaAs and 0.27 eV below CBM for  $In_{0.53}Ga_{0.47}As$ . The shadow area shows the built-up negative charges in interface traps after Fermi level moves from CNL to CBM. All calculated values are listed in Table I.

erostructure design, the maximum drain current could be much higher than the value offered by the doped GaAs pHEMT technology.

We ascribe this improvement to two determinants. First, the ALD dielectric process, in particular, trimethylaluminumrelated Al<sub>2</sub>O<sub>3</sub>, enables unpinning the Fermi levels on III-V semiconductors, in general. The simplified surface preparation for ALD on III-V is as follows.<sup>88</sup> Before surface treatment, all wafers underwent standard degrease process using acetone, methanol, and isopropanol. The NH<sub>4</sub>OH treatment is carried out by soaking the samples in NH<sub>4</sub>OH (29%) solution for 3 min to remove native oxide and rinsing in flowing de-ionized water followed by gently drying the surface using N<sub>2</sub> blow gun. The NH<sub>4</sub>OH etching step removes most of arsenic and gallium oxides from the surface. The further ALD process results on the disappearance of arsenic oxides and self-cleaning of GaAs surface.<sup>64,74–76,89</sup> The interface quality could be further improved sometimes by (NH<sub>4</sub>)<sub>2</sub>S treatment. The process is to soak the sample in  $(NH_4)_2S$  for 10 min in room temperature and dry using N<sub>2</sub> gun. With these appropriate surface pretreatments, the interface trap density in the range of low 10<sup>11</sup>-low 10<sup>12</sup>/cm<sup>2</sup> eV can be realized and the inversion-type enhancement-mode MOS-FETs can be demonstrated, as shown in Fig. 1. During the past decades, the research community mainly focused on dielectric materials and III-V surface chemistry study, and paid less attention to device physics of III-V MOSFET. We emphasize that device physics is also extremely important as the second determinant for realizing high inversion current due to the smaller energy-level separation between the CNL of In-rich InGaAs and the conduction-band minimum (CBM), compared to GaAs. The simple CNL-based model below can explain all experimental works on III-V MOSFETs using ex situ ALD high-k dielectrics and also in situ MBE-grown  $Ga_2O_3(Gd_2O_3)$  gate dielectric.

A difficult problem with III–V MOSFETs results from the unpassivated dangling bonds on III–V free surfaces. The energy locations of the dangling bonds are directly related to the bulk band structures of different III–V semiconductors. However, in the tight-binding formalism, the conduction and valence bands are formed as bonding and antibonding combinations of the atomic  $sp^3$  hybrids. That is why the

dangling-bond energy is typically located in the middle of the band gap.<sup>90</sup> There are many experimental studies that quantitatively measure the midgap energies of various semiconductors. There are also many theoretical studies using sophisticated techniques (such as metal induced gap state model, unified defect model, and disorder-induced gap state model) to quantitatively calculate the electronic energies. To simplify our explanation, we choose one internal reference level called CNL, as illustrated in Fig. 2, to phenomenologically explain all our experimental observations. Presumably, every interface has donor-type and acceptor-type interface traps. A convenient notation is to interpret the sum of these by an equivalent  $D_{it}$  distribution, with an energy level called charge-neutrality level  $E_{CNL}$ . If Fermi level  $E_F$  is above  $E_{\rm CNL}$ , the states are of acceptor type and negatively charged if the states are occupied. If Fermi level  $E_F$  is below  $E_{CNL}$ , the states are of donor type and positively charged if the states are occupied.<sup>91</sup> A recent review on CNL relevant for III-V materials can be found in Ref. 92. CNL concept is also applied to explain the experimental results from Ge MOSFETs.<sup>93</sup>

Figure 2 illustrates the basic idea to qualitatively understand the transistor output characteristic of Fig. 1. The model is extremely simplified to highlight the fundamental point with a few assumptions. First, the  $D_{it}$  distribution from valence-band maximum to CBM is parabolic in a logarithm scale. This is a reasonable assumption because the interface traps at III-V interfaces are more significant, compared to the SiO<sub>2</sub>/Si interface with a U-shaped distribution. Second, the  $D_{\rm it}$  value at CBM is fixed at  $10^{14}/{\rm cm}^2$  eV for simplification. Third, Fermi-level stabilization energy<sup>94</sup> is chosen as CNL energy with values listed in Table I. Assuming the strong electron inversion occurs when the Fermi level reaches CBM, the number of interface-trapped negative charges can easily be calculated by integrating  $D_{it}$  from CNL to CBM and are listed in Table I with different  $D_{it}$  values at CNL. It is obvious now that the dominant factor is the energy difference between CNL and CBM. For GaAs, with the CNL and CBM difference as large as  $\sim 0.8$  eV, it builds up 1.02  $\times 10^{-6}$  C/cm<sup>2</sup> negative charges to prevent a strong inversion charge to participate in transport. In contrast, the CNL and CBM potential difference for  $In_{0.65}Ga_{0.35}As$  is only 0.15 eV

TABLE I. Calculated built-in negative charges  $Q_{it}$  from CNL to CBM on different III-V substrates. In most cases of interest, the Fermi level in the semiconductor is above the CNL, resulting in a large buildup of fixed negative charge  $(Q_{it})$  at the interface due to fillingup of acceptorlike states.  $Q_{it}^{(1)}$  is for calculated built-in negative charges from CNL to CBM with  $D_{it}=1\times 10^{11}/\text{cm}^2 \text{ eV}$  at CNL;  $Q_{it}^{(2)}$  is for  $D_{it}=2\times 10^{11}/\text{cm}^2 \text{ eV}$  at CNL;  $Q_{it}^{(3)}$  is for  $D_{it}=5\times 10^{11}/\text{cm}^2 \text{ eV}$  at CNL;  $Q_{it}^{(4)}$  is for  $D_{it}=1\times 10^{12}/\text{cm}^2 \text{ eV}$  at CNL.

|                                          | $E_g$ (eV) | $E_{\rm CBM}$ - $E_{\rm CNL}$ (eV) | $Q_{\mathrm{it}}^{(1)}$<br>(C/cm <sup>2</sup> ) | $Q_{ m it}^{(2)}$<br>(C/cm <sup>2</sup> ) | $Q_{ m it}^{(3)}$<br>(C/cm <sup>2</sup> ) | $Q_{ m it}^{(4)}$<br>(C/cm <sup>2</sup> ) |

|------------------------------------------|------------|------------------------------------|-------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| GaAs                                     | 1.42       | 0.80                               | $1.02 \times 10^{-6}$                           | $1.15 \times 10^{-6}$                     | $1.38 \times 10^{-6}$                     | $1.63 \times 10^{-6}$                     |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 0.73       | 0.27                               | $3.44 \times 10^{-7}$                           | $3.88 \times 10^{-7}$                     | $4.67 \times 10^{-7}$                     | $3.44 \times 10^{-7}$                     |

| In <sub>0.65</sub> Ga <sub>0.35</sub> As | 0.61       | 0.15                               | $1.91 \times 10^{-7}$                           | $2.16 \times 10^{-7}$                     | $2.59 \times 10^{-7}$                     | $3.06 \times 10^{-7}$                     |

| In <sub>0.75</sub> Ga <sub>0.25</sub> As | 0.52       | 0.06                               | 6.37×10 <sup>-8</sup>                           | $7.19 \times 10^{-8}$                     | $8.65 \times 10^{-8}$                     | $1.02 \times 10^{-7}$                     |

assuming a linear extrapolation exhibited in  $In_xGa_{1-x}As$  bi-nary and ternary alloys<sup>95</sup> and CNL for InAs is at 0.2 eV above CBM.<sup>96</sup> The built-up negative charge is only 1.91  $\times 10^{-7}$  C/cm<sup>2</sup>, a factor of 5 smaller than that in GaAs. That explains why an Al<sub>2</sub>O<sub>3</sub>/In<sub>0.20</sub>Ga<sub>0.80</sub>As MOSFET (Ref. 68) has much less maximum drain current than an  $Al_2O_3/In_{0.53}Ga_{0.47}As$ MOSFET (Refs. 77-79) and  $Al_2O_3/In_{0.65}Ga_{0.35}As$  MOSFET.<sup>80,81</sup> It also explains why Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/GaAs MOSFETs have only less than 1 mA/mm drain current<sup>53</sup> and Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET has 360 mA/mm drain current.<sup>55</sup> InP is another interesting material to double check the applicability of the above model. InP has a band gap of 1.35 eV, which is very similar to 1.42 eV of GaAs. However, the potential difference between CNL and CBM for InP is only  $\sim 0.5 \text{ eV}$ .<sup>28,29,90</sup> It is much easier to realize an inversion-mode InP MOSFET than a GaAs MOSFET. 100 mA/mm drain current InP MOSFETs have been demonstrated using ALD high-k dielectrics.<sup>97,98</sup> The interface quality of Al<sub>2</sub>O<sub>3</sub>/III-V is better than that of HfO<sub>2</sub>/III-V, in general. However, the built-in charge increases less than a factor of 2 from the midgap  $D_{\rm it}$  of  $10^{11} - 10^{12}$ /cm<sup>2</sup> eV, as shown in Table I. That explains why Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, HfAlO, and even in situ grown  $Ga_2O_3(Gd_2O_3)$  have similar device performance on the same III-V substrate. The ALD process is obviously much more favorable, because it is ex situ, robust, manufacturable, and widely used in the Si industry. Compared to Hasegawa DIGS model,<sup>27</sup> Spicer's UDM,<sup>30</sup> and Brillson's work,<sup>99</sup> this phenomenological CNL model is more related to the band structures of III-V substrates. The interface control, which is mainly determined by dielectric materials, surface preparation, and oxide formation, is very important. However, the high-mobility substrate itself plays the most important role here.

A similar conclusion can also be reached by calculating the surface-potential or band-bending condition for strong inversion on different substrates. The strong inversion requires

$$\psi_s \approx 2\psi_B \approx \frac{2kT}{q} \ln\left(\frac{N_A}{n_i}\right).$$

(1)

With  $N_A$  of  $1 \times 10^{17}$ /cm<sup>3</sup>,  $n_i$  (GaAs) of  $2 \times 10^6$ /cm<sup>3</sup>, and  $n_i$  (InAs) of  $1 \times 10^{15}$ /cm<sup>3</sup>, it is clear that it requires much less

band-bending or surface-potential movement to realize strong inversion in In-rich InGaAs than in GaAs.

The conclusion is that with decent interface quality as the precondition, the energy difference between CNL and CBM is the most important determinant for high-performance inversion-type *E*-mode III–V MOSFETs.

#### IV. ELECTRICAL CHARACTERIZATION METHODOLOGY FOR III-V MOS CAPACITORS

III–V MOS *C-V* measurement is widely used to characterize III–V MOS structures. It is commonly accepted that the observation of the inversion of minority carriers is conclusive evidence of whether or not the Fermi level is pinned. Most previous studies concentrated on GaAs, so quasistatic *C-V* was used to evaluate interface properties. Fermi-level pinning was considered the reason for failing to observe inversion features in GaAs MOS capacitors (MOSCAPs). Here, we discuss this concept from a device physics perspective to clarify some controversies.

The determinant for the III-V MOSCAP characteristic is surface recombination velocity S at the MOS interface. Recombination strongly depends on doping type and concentration through the dependence of defect occupation on the Fermi level. The rate of carrier recombination U is given by the Shockley-Hall-Read statistics

$$=\frac{N_i\sigma_n\sigma_p v_{\rm th}(np-n_i^2)}{\sigma_n[n+n_i\exp(E_t-E_i/kT)]+\sigma_p[p+n_i\exp(E_i-E_t/kT)]}$$

(2)

where  $N_t$  is the number of deep traps at a given energy,  $\sigma_n$ and  $\sigma_p$  are the carrier capture cross sections,  $v_{\text{th}}$  is the average thermal velocity, n and p are the carrier concentrations,  $n_i$  is the intrinsic concentration, and  $E_i$  is the energy level of the deep traps. For p-type GaAs or III-V for n-channel MOS-FET, Eq. (2) can be rewritten to give the Stevenson-Keyes expression<sup>100</sup> or the surface recombination velocity S of electrons:

$$S = \frac{U}{\Delta n} = \frac{N_s \sigma_n \sigma_p v_n v_p p_0}{\sigma v N_b \exp(-E_{\min}/kT)},$$

(3)

where  $N_s$  is the number of defects per area at the interface at a given energy,  $p_0$  is the hole concentration,  $\Delta n$  is the deviation of electron density from equilibrium,  $N_b$  is the effective density of states, and  $E_{\min}$  is the smaller of  $E_c$ - $E_{CNL}$  or  $E_{\rm CNL}$ - $E_v$ .<sup>90</sup> For GaAs,  $E_{\rm CNL}$  or  $E_F$  are both near midgap and have the highest recombination velocity. For In<sub>0.53</sub>Ga<sub>0.47</sub>As,  $E_{\text{CNL}}$  is only 0.27 eV below CBM, whose theoretical S value could be several orders of magnitude lower. It is not surprising that a recent photoluminescence experiment shows that the native oxide on an In<sub>0.15</sub>Ga<sub>0.85</sub>As film has one order of magnitude lower surface recombination velocity than the native oxide on a GaAs film.<sup>101</sup> The microscopic structures of different III-V surfaces, dielectrics, and processes play a significant role in surface recombination through the number of surface states  $N_{\rm s}$ . This simple calculation provides only a qualitative trend to understand the general behavior of C-Vcharacteristics.

According to the Shockley-Read-Hall statistics and the low intrinsic carrier concentration  $(n_i)$  of  $10^6/\text{cm}^3$  in GaAs, the expected ac frequency to observe inversion C-V in the dark and at room temperature is very low ( $\sim 0.002$  Hz).<sup>102</sup> The condition for reliable quasistatic C-V measurements with leakage current density of less than  $10^{-8}$  A/cm<sup>2</sup> is also difficult to meet on ultrathin high-k dielectrics. After understanding the principle of surface recombination velocity and frequency response of minority carrier to the ac signals by C-V measurements, we recommend three approaches to study inversion C-V on III-V in general: (i) inversion-type MOSFET with implanted source and drain, where minority carriers could be injected into the surface channel at a low drain bias; (ii) photoillumination to increase the minoritycarrier concentration; and (iii) elevated temperature to increase the generation and recombination rates of minority carriers in GaAs. All these approaches are used to increase the minority carriers and reduce the recombination velocity, as shown in Eq. (3).

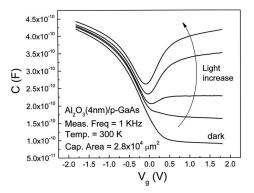

The minority carriers (electrons) in *p*-type GaAs cannot keep up with the low-frequency C-V measurement even at frequencies as low as 1 Hz in the dark and at room temperature. However, at higher temperatures or under photo- (light) illumination, more carriers are generated and their response time is significantly reduced so that the minority-carrier contribution to the capacitance can be profound. Full inversion could be observed at the Al2O3/GaAs interface with increasing light intensity, as shown in Fig. 3, by implementing indium tin oxide (ITO) as metal gate.<sup>73</sup> The conductive and transparent ITO gate enables homogenous photoillumination on the whole MOS capacitor area, such that one can easily observe the low-frequency C-V on GaAs at room temperature. We assume that the interface quality of Al<sub>2</sub>O<sub>3</sub>/GaAs is similar with or without light. The light-induced minoritycarrier concentration and its response time for thermal generation/recombination play a more important role on inversion than the interface trap density. It is not very clear that

FIG. 3. Capacitance measurement at 1 kHz as a function of gate bias with increased light intensity from the microscope. Indium tin oxide is used as transparent conducting electrodes to improve light illumination on GaAs. The light intensity is simply controlled by the electrical power supplied to the microscope lamp.

the conclusive evidence for Fermi-level unpinning is the inversion or low-frequency feature in C-V measurement, or even in quasistatic C-V measurement in dark and at room temperature.

A good exercise is to integrate low-frequency capacitance and obtain the  $\psi_s$ -V relationship, a method first developed by Berglund in 1966.<sup>103</sup> Here,  $\psi_s$  is the surface potential and V is the gate bias. The  $\psi_s$ -V relationship is very important in interface studies since  $D_{it}$  can be directly obtained from it. The change in surface potential due to a change in applied MOS voltage from  $V_1$  to  $V_2$  is

$$\psi_{s}(V_{2}) - \psi_{s}(V_{2}) = \int_{V_{1}}^{V_{2}} \left[1 - \frac{C_{\rm LF}(V)}{C_{\rm OX}}\right] dV.$$

(4)

Using the Berglund equation, the surface-potential change on GaAs of Fig. 3 is as large as 1.1 eV, which is comparable to the GaAs band gap itself. This is a convincing experimental evidence that the Fermi level at the ALD  $Al_2O_3/GaAs$  interface is not pinned. Similar results are also obtained in In-GaAs, where the band gap is even smaller. Surface-potential movement or band-bending value could be used to quantitatively study the Fermi-level pinning issue.

Similar to MOSFETs, interface trap density  $D_{it}$  or  $N_s$  in Eq. (3) is not the only determinant for *C*-*V* characteristics. The high-mobility substrate itself also plays an important role here through band gap, intrinsic carrier concentration, doping concentration, and other features. Device physics is also very important in guiding III-V MOS studies and interpreting the experimental data.

#### **V. CONCLUSION**

In summary, we briefly reviewed the history over the past 40 years and current status of III-V MOSFET research to help those new in the field to have easy access to the many existing publications. We use a simple CNL-based model to explain all reported experimental observations on inversion-type enhancement-mode ALD high-*k*/III-V MOSFETs and MBE Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/III-V MOSFETs. Conclusive evidence

on GaAs Fermi-level unpinning using ALD  $Al_2O_3$  is presented by inversion features in *C-V* measurements and surface-potential calculations using the Berglund low-frequency capacitance method.

#### ACKNOWLEDGMENTS

The author would like to thank Yi Xuan, Tian Yang, and Tian Shen for the experimental results used in this article, and J. M. Woodall, H. Hasegawa, M. Hong, R. M. Wallace, G. D. Wilk, M. S. Lundstrom, and Yanqing Wu for valuable discussions. The work is supported in part by the National Science Foundation (Grant No. ECS-0621949) and the SRC FCRP MSD Focus Center.

- <sup>1</sup>H. Becke, R. Hall, and J. White, Solid-State Electron. 8, 813 (1965).

- <sup>2</sup>H. W. Becke and J. P. White, Electronics **40**, 82 (1967).

- <sup>3</sup>L. Messick, Solid-State Electron. **22**, 71 (1979).

- <sup>4</sup>K. Kamimura and Y. Sakai, Thin Solid Films 56, 215 (1979).

- <sup>5</sup>T. Mimura and M. Fukuta, IEEE Trans. Electron Devices **27**, 1147 (1980).

- <sup>6</sup>B. Bayraktaroglu, W. M. Theis, and F. L. Schuermeyer, *37th Device Research Conference, Abstracts*, 1979 (unpublished), p. WP-A3.

- <sup>7</sup>H. C. Casey, Jr., A. Y. Cho, and E. H. Nicollian, Appl. Phys. Lett. **32**, 678 (1978).

- <sup>8</sup>M. R. Melloch, N. Otsuka, J. M. Woodall, A. C. Warren, and J. L. Freeouf, Appl. Phys. Lett. **57**, 1531 (1990).

- <sup>9</sup>W. T. Tsang, Appl. Phys. Lett. 33, 429 (1979).

- <sup>10</sup>X. Li, Y. Cao, D. C. Hall, P. Fay, B. Han, A. Wibowo, and N. Pan, IEEE Electron Device Lett. **25**, 772 (2004).

- <sup>11</sup>D. N. Butcher and B. J. Sealy, Electron. Lett. **13**, 558 (1977).

- <sup>12</sup>H. Hasegawa, K. W. Forward, and H. L. Hartnagal, Appl. Phys. Lett. 26, 567 (1975).

- <sup>13</sup>R. A. Logan, B. Schwartz, and W. J. Sandburg, J. Electrochem. Soc. **120**, 1385 (1973).

- <sup>14</sup>O. A. Weinreich, J. Appl. Phys. **37**, 2924 (1966).

- <sup>15</sup>K. Yamasaki and T. Sugano, Jpn. J. Appl. Phys. 17, 321 (1978).

- <sup>16</sup>N. Yokoyama, T. Mimura, K. Odani, and M. Fukuta, Appl. Phys. Lett. 32, 58 (1978).

- <sup>17</sup>L. A. Chesler and G. Y. Robinson, Appl. Phys. Lett. **32**, 60 (1978).

- <sup>18</sup>R. P. H. Chang and A. K. Sinha, Appl. Phys. Lett. **29**, 56 (1976).

- <sup>19</sup>V. M. Bermudez, J. Appl. Phys. 54, 6795 (1983).

- <sup>20</sup>C. F. Yu, M. T. Schmidt, D. V. Podlesnik, E. S. Yang, and R. M. Osgood, Jr., J. Vac. Sci. Technol. A **6**, 754 (1988).

- <sup>21</sup>S. D. Offsey, J. M. Woodall, A. C. Warren, P. D. Kirchner, T. I. Chappell, and G. D. Pettit, Appl. Phys. Lett. **48**, 475 (1986).

- <sup>22</sup>C. W. Wilmsen, *Physics and Chemistry of III-V Compound Semiconduc*tor Interfaces (Plenum, New York, 1985).

- <sup>23</sup>A. M. Cowley and S. M. Sze, J. Appl. Phys. **36**, 3212 (1965).

- <sup>24</sup>V. Heine, Phys. Rev. **138**, 1689 (1965).

- <sup>25</sup>C. Tejedor and F. Flores, J. Phys. C 11, L19 (1978).

- <sup>26</sup>W. E. Spicer, P. W. Chye, P. R. Skeath, C. Y. Su, and I. Lindau, J. Vac. Sci. Technol. **16**, 1422 (1979).

- <sup>27</sup>H. Hasegawa and H. Ohno, J. Vac. Sci. Technol. B **4**, 1130 (1986).

- <sup>28</sup>J. Tersoff, Phys. Rev. Lett. **52**, 465 (1984).

- <sup>29</sup>J. Tersoff, Phys. Rev. B **32**, 6968 (1985).

- <sup>30</sup>W. E. Spicer, I. Lindau, P. Skeath, C. Y. Su, and P. Chye, Phys. Rev. Lett. **44**, 420 (1980).

- <sup>31</sup>W. W. Hooper and W. I. Lehrer, Proc. IEEE **55**, 1237 (1967).

- <sup>32</sup>R. Dingle, H. L. Stromer, A. C. Gossard, and W. Wiegmann, Appl. Phys. Lett. **33**, 665 (1978).

- <sup>33</sup>H. L. Stromer, R. Dingle, A. C. Gossard, W. Wiegmann, and M. D. Sturge, Solid State Commun. **29**, 705 (1979).

- <sup>34</sup>T. Mimura, S. Hiyamizu, T. Fujii, and K. Nanbu, Jpn. J. Appl. Phys. 19, L225 (1980).

- <sup>35</sup>D. Delagebeaudeuf, P. Delescluse, P. Etienne, M. Laviron, J. Chaplart, and N. T. Linh, Electron. Lett. **16**, 667 (1980).

- <sup>36</sup>B. J. Skromme, C. J. Sandroff, E. Yablonovitch, and T. Gmitter, Appl. Phys. Lett. **51**, 2022 (1987).

- <sup>37</sup>E. Yablonovitch, C. J. Sandroff, R. Bhat, and T. Gmitter, Appl. Phys. Lett. 51, 439 (1987).

- <sup>38</sup>A. Callegari, P. D. Hoh, D. A. Buchanan, and D. Lacey, Appl. Phys. Lett. 54, 332 (1989).

- <sup>39</sup>H. Hasegawa, M. Akazawa, K. I. Matsuzaki, H. Ishii, and H. Ohno, Jpn. J. Appl. Phys., Part 2 L27, L2265 (1988).

- <sup>40</sup>S. Tiwari, S. L. Wright, and J. Batey, IEEE Electron Device Lett. 9, 488 (1988).

- <sup>41</sup>G. G. Fountain, S. V. Hattangady, D. J. Vitkavage, R. A. Rudder, and R. J. Markunas, Electron. Lett. **24**, 1134 (1988).

- <sup>42</sup>G. G. Fountain, R. A. Rudder, S. V. Hattangady, R. J. Markunas, and J. A. Hutchby, Tech. Dig. Int. Electron Devices Meet. **1989**, 887.

- <sup>43</sup>M. Akazawa, H. Ishii, and H. Hasegawa, Jpn. J. Appl. Phys., Part 1 30, 3744 (1991).

- <sup>44</sup>D. S. L. Mui, H. Liaw, A. L. Demirel, S. Strite, and H. Morkoc, Appl. Phys. Lett. **59**, 2847 (1991).

- <sup>45</sup>A. Callegari, D. K. Sadana, D. A. Buchanan, A. Paccagnella, E. D. Marshall, M. A. Tischler, and M. Norcott, Appl. Phys. Lett. **58**, 2540 (1991).

- <sup>46</sup>S. Koveshnikov, W. Tsai, I. Ok, J. C. Lee, V. Torkanov, M. Yakimov, and S. Oktyabrsky, Appl. Phys. Lett. **88**, 022106 (2006).

- $^{47}$ I. Ok *et al.*, IEEE Electron Device Lett. **27**, 145 (2006).

- <sup>48</sup>S. J. Koester et al., Appl. Phys. Lett. **89**, 042104 (2006).

- <sup>49</sup>D. Shahrjerdi, M. M. Oye, A. L. Holmes, and S. K. Banerjee, Appl. Phys. Lett. **89**, 043501 (2006).

- <sup>50</sup>M. Passlack, M. Hong, and J. P. Mannaerts, Appl. Phys. Lett. **68**, 1099 (1996).

- <sup>51</sup>M. Passlack, M. Hong, J. P. Mannaerts, R. L. Opila, S. N. G. Chu, N. Moriya, F. Ren, and J. R. Kwo, IEEE Trans. Electron Devices **44**, 214 (1997).

- <sup>52</sup>M. Hong, J. Kwo, A. R. Kortan, J. P. Mannaerts, and A. M. Sergent, Science **283**, 1897 (1999).

- <sup>53</sup>F. Ren *et al.*, Solid-State Electron. **41**, 1751 (1997).

- <sup>54</sup>Y. C. Wang et al., IEEE Electron Device Lett. 20, 457 (1999).

- <sup>55</sup>F. Ren et al., IEEE Electron Device Lett. **19**, 309 (1998).

- <sup>56</sup>M. Hong, J. N. Bailargeon, J. Kwo, J. P. Mannaerts, and A. Y. Cho, Proceedings of IEEE International Symposium on Compound Semiconductors, 2000 (unpublished), pp. 345–350.

- <sup>57</sup>Y. C. Wang *et al.*, Electron. Lett. **35**, 667 (1999).

- <sup>58</sup>B. Yang *et al.*, J. Cryst. Growth **251**, 837 (2003).

- <sup>59</sup>M. Passlack, N. Medendorp, R. Gregory, and D. Braddock, Appl. Phys. Lett. 83, 5262 (2003).

- <sup>60</sup>K. Rajagopalan, J. Abrokwah, R. Droopad, and M. Passlack, IEEE Electron Device Lett. **27**, 959 (2006).

- <sup>61</sup>M. J. Hale, S. I. Yi, J. Z. Sexton, A. C. Kummel, and M. Passlack, J. Chem. Phys. **119**, 6719 (2003).

- <sup>62</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

- <sup>63</sup>P. D. Ye *et al.*, IEEE Electron Device Lett. **24**, 209 (2003).

- <sup>64</sup>P. D. Ye et al., Appl. Phys. Lett. 83, 180 (2003).

- <sup>65</sup>P. D. Ye, G. D. Wilk, B. Yang, J. Kwo, H.-J. L. Gossmann, M. Hong, K. Ng, and J. Bude, Appl. Phys. Lett. **84**, 434 (2004).

- <sup>66</sup>P. D. Ye, G. D. Wilk, B. Yang, S. N. G. Chu, K. K. Ng, and J. Bude, Solid-State Electron. **49**, 790 (2005).

- <sup>67</sup>P. D. Ye, B. Yang, K. Ng, J. Bude, G. D. Wilk, S. Halder, and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

- <sup>68</sup>Y. Xuan, H. C. Lin, P. D. Ye, and G. D. Wilk, Appl. Phys. Lett. 88, 263518 (2006).

- <sup>69</sup>Y. Xuan, H. C. Lin, and P. D. Ye, ECS Trans. **3**, 59 (2006).

- <sup>70</sup>Y. Xuan, H. C. Lin, and P. D. Ye, IEEE Trans. Electron Devices **54**, 1811 \_\_\_(2007).

- <sup>71</sup>Y. Q. Wu, T. Shen, P. D. Ye, and G. D. Wilk, Appl. Phys. Lett. **90**, 143504 (2007).

- <sup>72</sup>T. Yang *et al.*, Appl. Phys. Lett. **91**, 142122 (2007).

- <sup>73</sup>T. Yang, Y. Xuan, P. D. Ye, and M. S. Lundstrom (unpublished).

- <sup>74</sup>M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J.

- Chabal, J. Grazul, and D. A. Muller, Appl. Phys. Lett. **86**, 152904 (2005). <sup>75</sup>M. L. Huang, Y. C. Chang, C. H. Chang, Y. J. Lee, P. Chang, J. Kwo, T.

- B. Wu, and M. Hong, Appl. Phys. Lett. 87, 252104 (2005).

- <sup>76</sup>C. H. Chang, Y. K. Chiou, Y. C. Chang, K. Y. Lee, T. D. Lin, T. B. Wu, M. Hong, and J. Kwo, Appl. Phys. Lett. **89**, 242911 (2006).

- <sup>77</sup>Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, *Proceeding of 65th Device Research Conference*, Notre Dame, 2007 (unpublished).

- 78Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, IEEE Electron

Device Lett. 28, 935 (2007).

- <sup>79</sup>Y. Xuan, Y. Q. Wu, T. Shen, T. Yang, and P. D. Ye, Tech. Dig. Int. Electron Devices Meet. Dec. 2007, pp. 637–640.

- <sup>80</sup>Y. Xuan, P. D. Ye, and T. Shen, Appl. Phys. Lett. **91**, 232107 (2007).

- <sup>81</sup>Y. Xuan, Y. Q. Wu, and P. D. Ye, IEEE Electron Device Lett. **29**, 294 (2008).

- <sup>82</sup>M. Zhu, C. H. Tung, and Y. C. Yeo, Appl. Phys. Lett. **89**, 202903 (2006).

- <sup>83</sup>H. L. Lu, L. Sun, S. J. Ding, M. Xu, D. W. Zhang, and L. K. Wang, Appl. Phys. Lett. **89**, 152910 (2006).

- <sup>84</sup>G. K. Dalapati, Y. Tong, W. Y. Loh, H. K. Mun, and B. J. Cho, IEEE Trans. Electron Devices **54**, 1831 (2007).

- <sup>85</sup>D. Shahrjerdi, E. Tutuc, and S. Banerjee, Appl. Phys. Lett. **91**, 063501 (2007).

- <sup>86</sup>R. Chau, S. Datta, and A. Majumdar, *Proceedings of IEEE CSIC Digest*, 2005 (unpublished), pp. 17–20.

- <sup>87</sup>S. Datta *et al.*, Tech. Dig. Int. Electron Devices Meet. **2005**, 763.

- <sup>88</sup>Y. Xuan, H. C. Lin, and P. D. Ye, IEEE Trans. Electron Devices **54**, 1811 (2007).

- <sup>89</sup>R. M. Wallace (private communication).

- <sup>90</sup>D. D. Nolte, Solid-State Electron. **33**, 295 (1990).

- <sup>91</sup>S. M. Sze and K. K. Ng, Physics of Semiconductor Devices 3rd ed.

- (Wiley-Interscience, Hoboken, New Jersey, 2007), pp. 213–216.

- <sup>92</sup>J. Robertson and B. Falabretti, J. Appl. Phys. **100**, 014111 (2006).

- <sup>93</sup>A. Dimoulas, P. Tsipas, A. Sotiropoulos, and E. K. Evangelou, Appl. Phys. Lett. **89**, 252110 (2006).

- <sup>94</sup>W. Walukiewicz, Phys. Rev. B **37**, 4760 (1988).

- <sup>95</sup>H. H. Wieder, J. Vac. Sci. Technol. B **21**, 1915 (2003).

- <sup>96</sup>M. J. Lowe, T. D. Veal, C. F. McConville, G. R. Bell, S. Tsukamoto, and N. Koguchi, J. Cryst. Growth 237, 196 (2002).

- <sup>97</sup>Y. Q. Wu, Y. Xuan, T. Shen, P. D. Ye, Z. Cheng, and A. Lochtefeld, Appl. Phys. Lett. **91**, 022108 (2007).

- <sup>98</sup>Y. Q. Wu, Y. Xuan, P. D. Ye, Z. Cheng, and A. Lochtefeld, in *Proceeding* of 65th Device Research Conference, 2007 (unpublished), pp. 117–118.

- <sup>99</sup>L. J. Brillson and C. F. Brucker, Phys. Rev. Lett. **46**, 838 (1981).

- <sup>100</sup>D. E. Aspens, Surf. Sci. **132**, 406 (1983).

- <sup>101</sup>G. Brammertz et al., Appl. Phys. Lett. 90, 134102 (2007).

- <sup>102</sup>S. R. Hofstein and G. Warfield, Solid-State Electron. 8, 321 (1965).

- <sup>103</sup>C. N. Berglund, IEEE Trans. Electron Devices **ED-13**, 701 (1966).