### Making HLS A Bit Wiser: From Standard High-Level Datatypes to Arbitrary Low-Level Bitwidths

by

Hsuan Hsiao

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright 2017 by Hsuan Hsiao

#### Abstract

Making HLS A Bit Wiser:

From Standard High-Level Datatypes to Arbitrary Low-Level Bitwidths

Hsuan Hsiao

Master of Applied Science Graduate Department of Electrical and Computer Engineering

University of Toronto

2017

High-level synthesis provides an easy-to-use abstraction for designing hardware circuits. However, standard datatypes available in high-level languages are over provisioned for typical applications, incurring unnecessary area overhead since the underlying FPGA hardware can support arbitrary bitwidths. We provide a bitwidth minimization (BWM) framework that analyzes and eliminates unused bits in the circuit's datapath and allows for the use of arbitrary width datatypes in the high-level source code. We then propose *Sensei*, an advisor that predicts the post-synthesis area savings brought about by reducing bitwidth and presents users with a ranking of program variables based on area impact. Together, these two contributions aim to bridge the gap between the over-provisioned datapaths of high-level languages and the arbitrary-width datapaths of low-level circuits.

### Acknowledgements

First, I would like to thank my advisor, Professor Jason Anderson, for his constant guidance and support. I would not have reached this point if not for his encouragement, inspiration and endless advices. He has been a great motivator for my academic and personal development, and will always be a role model.

Second, I would like to thank my parents and my brother for their unconditional love and support. Their patience and trust in me has helped immensely in this journey. It would not be the same without them constantly humouring me whenever I decide to do random things.

A big thank you to Josh, for always being there for me, supporting and inspiring me to strive for higher. All the thoughtful rants and encouraging outlooks on life have helped me in shaping my own perspective on many things.

Last but not least, I am fortunate to have been surrounded by lots of wonderful people during these years. The current and past graduates in our research team: Joy, Jin Hee, Xander, Steven, Brett, Blair, Andrew, James, Lanny, Bain and Safeen; as well as fellow labmates of PT477: Karthik, Fernando, Mario, Nariman, Naif, Charles and Shehab. Thank you all for the invaluable feedback and suggestions on both research and many aspects of personal development. Above all, thank you all for creating such a fun and supportive environment for me to learn and grow.

# Contents

| 1        | Intr              | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                  |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|          | 1.1               | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                  |

|          | 1.2               | Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                  |

| <b>2</b> | Bac               | ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>5</b>                                                                           |

|          | 2.1               | The LegUp High-Level Synthesis Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                  |

|          | 2.2               | The LLVM Intermediate Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                  |

|          | 2.3               | Quartus II CAD Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                 |

|          | 2.4               | Cyclone V Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                 |

|          | 2.5               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                                                                                 |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                    |

| 3        | Bity              | idth Minimization Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                 |

| 3        | <b>Bit</b><br>3.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>13</b><br>14                                                                    |

| 3        |                   | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

| 3        | 3.1               | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                                                 |

| 3        | 3.1<br>3.2        | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14<br>15                                                                           |

| 3        | 3.1<br>3.2        | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14<br>15<br>16                                                                     |

| 3        | 3.1<br>3.2        | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14<br>15<br>16<br>16                                                               |

| 3        | 3.1<br>3.2        | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ol> <li>14</li> <li>15</li> <li>16</li> <li>16</li> <li>20</li> </ol>             |

| 3        | 3.1<br>3.2        | Background       Image: Second S | <ol> <li>14</li> <li>15</li> <li>16</li> <li>16</li> <li>20</li> <li>23</li> </ol> |

|              |      | 3.4.2   | Bit Savings                                        | 31 |

|--------------|------|---------|----------------------------------------------------|----|

|              |      | 3.4.3   | Resource Utilization                               | 33 |

|              |      | 3.4.4   | Bit and Resource Savings with Default HLS Settings | 36 |

|              |      | 3.4.5   | Case Study of User-Declared Bitwidths              | 37 |

|              | 3.5  | Conclu  | usion                                              | 38 |

| 4            | Sen  | sei: Ai | rea Reduction Advisor                              | 40 |

|              | 4.1  | Overv   | iew                                                | 41 |

|              | 4.2  | Relate  | ed Work                                            | 44 |

|              | 4.3  | Convo   | lutional Neural Networks                           | 44 |

|              |      | 4.3.1   | Architectural Components                           | 45 |

|              |      | 4.3.2   | Runtime Parameters of a CNN                        | 47 |

|              | 4.4  | Sensei  | Predictor                                          | 48 |

|              |      | 4.4.1   | Analytical Predictor                               | 49 |

|              |      | 4.4.2   | CNN-Based Predictor                                | 50 |

|              | 4.5  | Metho   | odology                                            | 57 |

|              |      | 4.5.1   | Experimental Setup                                 | 57 |

|              |      | 4.5.2   | Evaluation Criteria                                | 58 |

|              | 4.6  | Result  | 55                                                 | 60 |

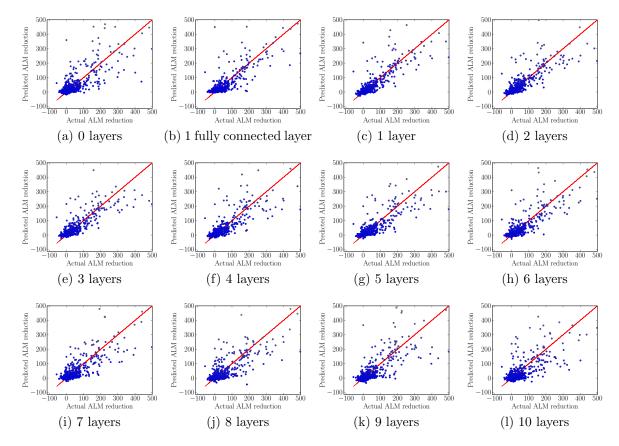

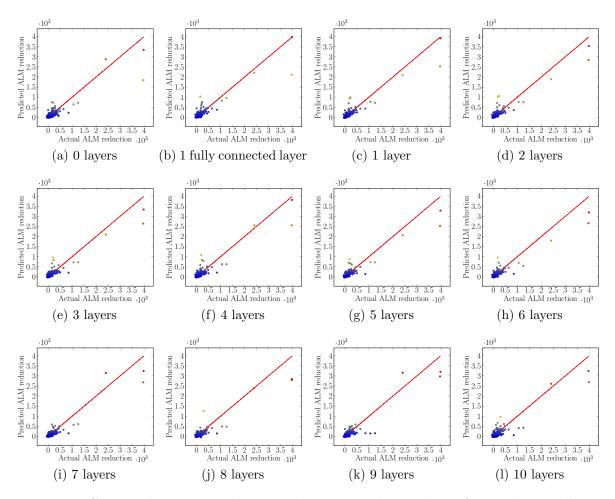

|              |      | 4.6.1   | CNN Model Selection                                | 60 |

|              |      | 4.6.2   | Impact of Input Dataset Configuration              | 64 |

|              |      | 4.6.3   | Impact of CNN Hyperparameters                      | 65 |

|              |      | 4.6.4   | Comparison of Analytical to CNN-based Predictor    | 72 |

|              | 4.7  | Conclu  | usion                                              | 75 |

| <b>5</b>     | Cor  | nclusio | n                                                  | 76 |

|              | 5.1  | Future  | e Work                                             | 77 |

| $\mathbf{A}$ | ppen | dices   |                                                    | 79 |

| Α  | Bitwidth Minimization Framework Data                                     | 80 |

|----|--------------------------------------------------------------------------|----|

|    | A.1 Raw Data for different Components of Bitwidth Minimization Framework | 80 |

| в  | Advisor Framework Data                                                   | 83 |

| Bi | bliography                                                               | 84 |

# Chapter 1

# Introduction

As a result of the continued technology scaling arising from Moore's Law, circuit designers are able to incorporate more and more functionality onto a single chip. However, a larger system with more functionality comes with a trade-off of increased design complexity and increased time and effort required for circuit verification and modification. High-level synthesis (HLS) seeks to reduce these burdens by enabling the automated synthesis of a hardware circuit from a software program. Hardware design and verification can proceed at a higher level of abstraction and with greater ease, thereby reducing design time and cost. HLS has become a mainstream design methodology for field-programmable gate arrays (FPGAs), with both Xilinx and Intel offering commercial HLS solutions. The importance of HLS is underscored by the fact that the vendors themselves now use their own HLS solutions to produce compute accelerators for specific application domains, such as machine learning [7, 40].

As with any design methodology, whether it be for hardware or software, the introduction of an abstraction layer trades off optimality and customizability for increased usability. With HLS, the ability to allow designers to use a familiar software language to specify hardware designs trades off *some* of the designer's ability to fine-tune circuits for higher performance and area efficiency. While much easier to design, verify, and modify, the area footprint and circuit performance of HLS-generated circuits may be far from those produced by manual RTL design [34, 43], particularly in specific circumstances where there exists a "known good" hardware implementation (e.g. an FFT circuit implementation). Ongoing research efforts in both academia and industry have sought to improve various aspects of the HLS design methodology [17,29,42]. For the scope of this thesis, we focus on reducing the area footprint of HLS-generated circuits and providing new design methodologies for fine-tuning the area of circuits produced by HLS. In particular, we explore a unique source of area inefficiency encountered only in HLS due to its high-level abstraction.

One attractive feature of HLS is that it allows designers to use a familiar software language to specify a hardware design. We make the observation that software languages designed for typical processor architectures may incorporate processor-specific features into the language. However, such processor-specific features are not necessarily transferable to custom hardware circuitry. Thus, these "features" in the software language can limit (or even negatively impact) the performance and efficiency of the generated circuit when the same language is used for specifying a hardware design. In this thesis, we take an in-depth look at one such language feature: standard datatype width.

In a standard processor, the pipeline and execution units are all fixed at widths of 8, 16, 32 or 64 bits in order to simplify memory accesses and alignment. Datatypes with arbitrary widths would not improve performance, so software languages typically only provide primitive datatypes quantized to 8, 16, 32, and 64 bits. On the other hand, a key advantage of using custom hardware versus a microprocessor is that datapath widths can be tailored in hardware to match the application at hand for better performance and area efficiency. The use of software languages to specify hardware in HLS presents a unique dilemma faced by the HLS design methodology: it is challenging for HLS users to produce circuits with custom-width datapaths.

To address this shortcoming, we implement a compiler pass that analyzes the in-

#### CHAPTER 1. INTRODUCTION

put program's dataflow graphs and, through static analysis, automatically drops unused bits and replaces known constant (non-toggling) bits with their respective constant signals. This provides a convenient, automatic reduction of datapath widths for the HLS user. However, compiler passes are conservative, primarily because they execute without knowledge of program input data. Consequently, there often exist further opportunities that compilers are not able to leverage. To compensate for this, we introduce the notion of an arbitrary-width datatype in the software language to allow the HLS user to specify a reduced width datapath in the source code itself. This is done by attaching special attributes to the standard software datatypes, such that they are captured only by HLS tools and ignored by standard compilers. These two contributions together constitute our bitwidth minimization (BWM) framework.

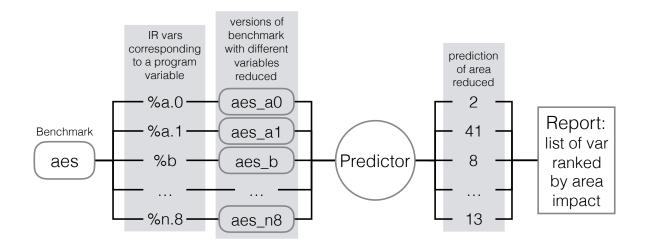

In order to make it easier for HLS users to construct circuits with reduced-width datapaths, we further enhance the BWM framework by introducing *Sensei*, an advisor framework that guides HLS users on when and where to reduce datapath widths for maximum benefit. We observe that a key research challenge in HLS is tied to its "black box" nature and the consequent disconnect between the software program (input) and the generated circuit (output). This disconnect significantly impedes HLS usability and leads to the question of how should a software developer *change* their program to produce a better-quality HLS-generated circuit? Sensei takes a step to address this question for the user. It accurately estimates the area impact of reducing the bitwidth of each program variable and provides the programmer with a list of key variables to focus on. The reductions in the widths of these variables are likely to have the most impact on final circuit area. Area-reduction predictions are made using two predictor approaches: one analytical and one based on a convolutional neural network (CNN). Both predictors only require information available at the HLS compiler stage, ensuring portability across different hardware platforms.

### **1.1** Contributions

The contributions of this thesis are as follows:

- We present the BWM framework, a compiler pass implemented within the LegUp HLS tool [10] that automatically infers reduced datapaths in the generated circuit. We also introduce arbitrary-precision datatypes to the software language to enable the specification of reduced-width datapaths in the HLS-synthesized circuits.

- We present *Sensei*, an area-reduction advisor for HLS users that uncovers opportunities for area savings via bitwidth reduction of program variables.

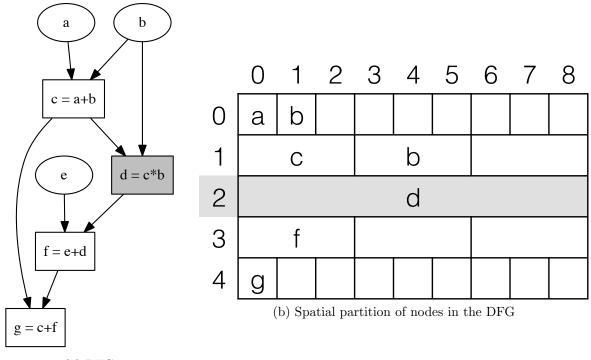

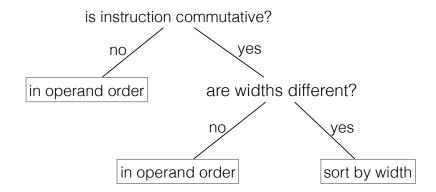

- We explore the use of CNNs in Sensei to predict the area impact of source-code bitwidth changes. We introduce a novel transformation of the compiler's dataflow graph (DFG) into a spatial representation well-suited to CNNs.

- We implement Sensei on top of the LegUp HLS tool and perform an experimental study of a range of CNN models compared against a traditional analytical approach. Our promising results showcase the strong potential for CNNs in HLS.

### **1.2** Thesis Outline

In Chapter 2, we provide background information on what HLS is and the key steps involved in the HLS tool flow. We also provide a high-level overview of the LLVM compiler framework that LegUp is built on top of, as well as a brief overview of the steps in the Quartus II CAD flow. Chapter 3 describes the BWM framework, discussing how our compiler analysis infers narrower widths and how the addition of arbitrary-width datatypes is made possible. Chapter 4 dives into the detailed implementation of Sensei, our area-reduction advisor. We conclude with Chapter 5 and touch on some interesting extensions and modifications for future work.

## Chapter 2

# Background

In this chapter, we review background material necessary for understanding the main contributions of this thesis. We first give a high-level overview of the LegUp HLS tool, with emphasis on aspects affecting area and bitwidth. We then move on to discuss the LLVM compiler (within which LegUp is built), and its internal representation of programs, on which all compiler optimizations are applied. The final two sections of the chapter briefly describe the Intel Cyclone V FPGA architecture, and the associated Quartus II CAD tools, as the tools and FPGA family are used for all experiments in this research.

#### 2.1 The LegUp High-Level Synthesis Tool

LegUp [10] is an open-source HLS tool developed at the University of Toronto. It takes a software program written in C as input and automatically generates an RTL circuit description in *Verilog HDL*. HLS tools typically implement three major phases of transformation in order to generate a hardware design from a software description: allocation, scheduling, and binding [12, 14–16]. Allocation refers to the process of determining how many functional units of each type to create for the program's hardware implementation (e.g. how many multiplier units are permitted in the hardware?). In LegUp, allocation is

#### CHAPTER 2. BACKGROUND

performed first and defines the resource constraints that are used in the scheduling and binding steps. For example, the HLS tool can choose to create only one multiplier unit and force all multiply operations in the program to be serialized so that only one multiply can proceed at a particular point in time. Alternatively, it can choose to create as many multiplier units as there are multiply operations in the program so that all multiplies can proceed at the same time in the absence of data dependencies. Scheduling refers to the step at which operations are assigned to specific clock cycles. This step defines when an operation will be executed, which impacts the number of cycles the program will take to finish and the maximum operating frequency of the circuit. For example, if the operands of a multiplication are ready but the product is not used until much later, the HLS tool can choose to schedule the multiplication anytime from now until then. The binding step examines the scheduled operations to determine which functional unit in the hardware should be used to implement the operation. There are typically less functional units than the number of operations that require them: the binding algorithm therefore determines how functional units are shared. As the number of operations bound to a functional unit increases, the area incurred by the multiplexer on each of the inputs of the functional unit also increases. For example, if there are two adder units where adder A has 2 operations bound to it and adder B has 6 operations bound to it, the binding algorithm will assign the next addition to adder A since the increase in area of the multiplexer is less.

LegUp's design tool flow is shown on Figure 2.1. The LegUp HLS tool is built on top of the LLVM (low-level virtual machine) compiler framework [26], discussed further in Section 2.2. The input C program is parsed and transformed into a platform-independent *intermediate representation* (IR) by Clang [3], LLVM's C frontend. Various standard compiler optimizations and HLS-specific optimizations are applied to the IR; the optimizations improve the quality of the generated hardware circuit. Using the final optimized IR, the three main steps of HLS (as overviewed above) are implemented as a backend pass of the LLVM framework, producing a Verilog HDL file as output. The Verilog can

Figure 2.1: Design flow using LegUp

then be pushed through Intel's Quartus II CAD tool to map the circuit onto an FPGA and obtain area and performance numbers. The functional correctness of the design can be verified through simulation with Mentor Graphics's ModelSim RTL simulator.

### 2.2 The LLVM Intermediate Representation

In the LLVM compiler framework, all optimizations, code transformations and information transfer are done through the platform-independent IR. In this section, we highlight a few characteristics of the IR that are important to our framework, some that we leverage and some that we overcome. Details of how we leverage and overcome each characteristic is discussed further in Chapter 3.

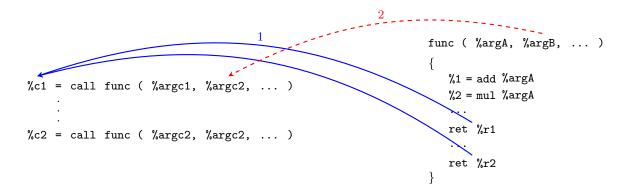

LLVM's IR is based on a static single assignment (SSA) paradigm, meaning that every variable in the IR is assigned exactly once and is defined before it is used. For example, in the simple C code shown in Listing 1, a is assigned two values: A1[1] on line 4 and A1[4] on line 8. The LLVM IR representation of this code is shown in Listing 2, where the first assignment to a is on line 5 (assigned to %1) and the second assignment on line 8 (assigned to %4). In a similar fashion to this, if a C variable is assigned a value *n* times, there will be *n* LLVM IR variables that correspond to the single C variable. For our BWM framework that allows the HLS user to specify a variable as a reduced-width datatype, this characteristic of the IR requires us to maintain the mapping between a program variable and its corresponding IR variables in order to reduce the width of all instances of it.

To aid in the many-to-one mapping between IR variables and C program variables,

LLVM provides debug information that can be enabled by compiling the source code with the -g option. In the IR annotated with debug information, extra calls to intrinsic functions (i.e. special functions provided and implemented by the compiler) llvm.dbg.declare and llvm.dbg.value are added whenever a value is assigned to a variable. llvm.dbg.declare is called when a variable is declared, and llvm.dbg.value is called when a variable is assigned a new value. *Metadata* in LLVM refers to optional information that is contained within the IR specification of the program, but can be

```

volatile int A1[10] = {0, 1, 2, 3, 4, 5, 6, 7, 8, 9};

1

\mathbf{2}

int main(void) {

3

int a = A1[1]; // 1st assignment to a

4

int b = A1[3];

5

int c = a + b;

6

7

a = A1[4];

// 2nd assignment to a

8

b = A1[5];

9

10

return a + b + c;

11

}

12

```

Listing 1: Example C source code for demonstrating SSA form.

```

@A1 = internal global [10 x i32] [i32 0, i32 1, i32 2, i32 3, i32 4, i32 5, i32 6,

1

\rightarrow i32 7, i32 8, i32 9], align 4

2

; Function Attrs: nounwind

3

define i32 @main() #0 {

4

%1 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 1),

\mathbf{5}

\rightarrow align 4, !dbg !22, !tbaa !23

; 1st assignment to a

%2 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 3),

6

\rightarrow align 4, !dbg !28, !tbaa !23

%3 = add nsw i32 %2, %1, !dbg !30

\overline{7}

%4 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 4),

8

\rightarrow align 4, !dbg !32, !tbaa !23

; 2nd assignment to a

%5 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 5),

9

\rightarrow align 4, !dbg !33, !tbaa !23

%6 = add i32 %3, %4, !dbg !34

10

%7 = add i32 %6, %5, !dbg !34

11

ret i32 %7, !dbg !34

12

}

13

```

Listing 2: LLVM IR for Listing 1 demonstrating SSA form.

```

@A1 = internal global [10 x i32] [i32 0, i32 1, i32 2, i32 3, i32 4, i32 5, i32 6,

1

\rightarrow i32 7, i32 8, i32 9], align 4

2

; Function Attrs: nounwind

3

define i32 @main() #0 {

4

%1 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 1),

5

\rightarrow align 4, !dbg !22, !tbaa !23

; 1st assignment to a

tail call void @llvm.dbg.value(metadata !{i32 %1}, i64 0, metadata !10), !dbg !27

6

\rightarrow ; debug info for %1

%2 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 3),

7

\rightarrow align 4, !dbg !28, !tbaa !23

tail call void @llvm.dbg.value(metadata !{i32 %2}, i64 0, metadata !11), !dbg !29

8

%3 = add nsw i32 %2, %1, !dbg !30

9

tail call void @llvm.dbg.value(metadata !{i32 %3}, i64 0, metadata !12), !dbg !31

10

%4 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 4),

11

; 2nd assignment to a

\rightarrow align 4, !dbg !32, !tbaa !23

tail call void @llvm.dbg.value(metadata !{i32 %4}, i64 0, metadata !10), !dbg !27

12

\rightarrow ; debug info for %4

%5 = load volatile i32* getelementptr inbounds ([10 x i32]* @A1, i32 0, i32 5),

13

\rightarrow align 4, !dbg !33, !tbaa !23

tail call void @llvm.dbg.value(metadata !{i32 %5}, i64 0, metadata !11), !dbg !29

14

%6 = add i32 %3, %4, !dbg !34

15

%7 = add i32 %6, %5, !dbg !34

16

ret i32 %7, !dbg !34

17

}

18

19

20

. . .

21

!10 = metadata !{i32 786688, metadata !4, metadata !"a", metadata !5, i32 4,

22

→ metadata !8, i32 0, i32 0}; [ DW_TAG_auto_variable ] [a] [line 4]

!11 = metadata !{i32 786688, metadata !4, metadata !"b", metadata !5, i32 5,

23

→ metadata !8, i32 0, i32 0}; [ DW_TAG_auto_variable ] [b] [line 5]

!12 = metadata !{i32 786688, metadata !4, metadata !"c", metadata !5, i32 6,

^{24}

\rightarrow metadata !8, i32 0, i32 0}; [DW_TAG_auto_variable] [c] [line 6]

```

Listing 3: LLVM IR for Listing 1 with debug information.

discarded without affecting the program's correctness. In both of the llvm.dbg functions, the first argument specifies metadata that wraps the IR variable this function call pertains to, and the last argument specifies metadata that contains information about the source code variable. For example, in Listing 3, we see that lines 6 and 12 are added to provide extra information about the value assignments that happen on lines 5 and 11, respectively. Looking at line 6, we see that the call to llvm.dbg.value maps IR variable %1 to metadata !10, shown on line 22. We leverage this existing infrastructure in LLVM to simplify the effort required in constructing our BWM framework.

Another characteristic of the LLVM IR is that it requires all operands to have the same data type and width as the result. In the case of the simple example in Listing 2, all of %1 through %7 are 32-bit integers. However, if there are any instances where two variables of different width are used in an operation, an extra sign extend or zero extend instruction is needed before the operation to conform to this LLVM IR requirement. This poses a challenge to the flexibility of our framework, imposing a wider datapath and functional unit than what is really necessary; we discuss how we overcome this in Section 3.3.4.

LLVM provides a hierarchical structure for the different components of the IR representation of a program. At the highest level, a *module* encapsulates the entire program. Within a module, several components can exist, including global variables, functions and metadata. In addition to variables declared as globals in the source code, all arrays are considered global variables in the LLVM IR.

### 2.3 Quartus II CAD Tool

Quartus II is software for programmable logic design provided by Intel [5]. To synthesize a Verilog HDL design into a bitstream for configuring an FPGA, Quartus II performs two major steps: 1) analysis and synthesis, and 2) place and route. In the first step, the compiler checks the Verilog HDL design for syntax errors and performs technology mapping of the design. This step infers structures such as flip-flops and state machines from the Verilog HDL and performs analysis and optimization to remove redundant logic, minimize resource usage and map logic onto the device architecture as efficiently as possible. In the place and route step, logic functions are assigned to cell locations on the device. Various optimizations are performed to improve resource usage and timing performance, and the user can additionally set options such as enabling register packing and limiting length of carry chains. In either step of the CAD flow, Quartus II performs a variety of optimizations that can influence the effectiveness of our BWM framework.

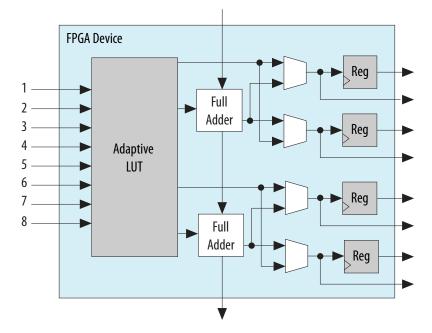

#### 2.4 Cyclone V Resources

FPGAs have a variety of building block resources on board, with adaptive logic modules (ALMs), registers, memory blocks and DSPs being the resources used for implementing logic. We briefly describe each resource type that is relevant to the evaluation of our framework and highlight how they may trade off with each other. An ALM in the Cyclone V family of FPGAs is composed of an 8-input fracturable look-up table (LUT), as shown in Figure 2.2 [4]. Each ALM is able to implement either one 6-input function, two independent 4-input functions, or a 5-input and a 3-input function with independent inputs. Within the ALM, there are also four registers and two full adders to enable higher density and arithmetic capability. For a design implemented on the FPGA, an ALM may be used either for its LUTs, or registers, or both.

Figure 2.2: Components inside a Cyclone V ALM [4].

Each DSP block in a Cyclone V device is capable of being configured as three  $9 \times 9$  multipliers, two  $18 \times 18$  multipliers or one  $27 \times 27$  multiplier. The Quartus compiler may choose to use DSPs to implement certain logic instead of ALMs, and vice versa, to enable higher performance and area efficiency.

Cyclone V devices contain two types of memory blocks: 10 kb dedicated memory blocks (M10K) and 640 b memory logic array blocks (MLAB). Each MLAB is made up of ten ALMs and are ideal for wide and shallow memory arrays.

### 2.5 Summary

This chapter provides background information on the tools and frameworks that we build upon in this thesis. We first describe the typical design flow of the LegUp HLS tool. We then discuss the relevant features and limitations of the LLVM IR, the Quartus II CAD tool and the Cyclone V FPGA architecture that we use in our framework.

# Chapter 3

# **Bitwidth Minimization Framework**

Applications written in high-level programming languages, like C, typically use standard datatypes, which are 8, 16, 32 or 64 bits. However, this set of standard bitwidths is often too coarse-grained for optimal representation of most data values. While this inefficiency in bit usage is inherent to software programming, it can be alleviated when the application is synthesized in hardware, where the datapaths can be specified to arbitrary widths. Several prior works have explored the idea of synthesizing a reduced-area circuit based on the analysis of the widths of software variables, demonstrating promising results [13, 19, 39, 44]. Some HLS tools available today also allow users to specify the exact width of a software variable using special arbitrary-precision datatypes [1, 2, 6, 41].

In this chapter, we describe our bitwidth minimization (BWM) framework in the LegUp HLS tool, which is aimed at eliminating any static bits (i.e. constant 1 or 0) or unused bits from the circuit's datapath. The framework consists of two components: 1) a custom compiler optimization pass that identifies static and unused bits in the program's dataflow graph; and 2) an infrastructure that allows users of LegUp to declare non-standard widths for C program variables and propagates this custom bitwidth information to the Verilog code. The compiler pass is an updated implementation of the bitmask analysis first proposed by Gort and Anderson [19]. We also introduce optimizations

for function calls and memory operations to enable further circuit area savings. The infrastructure that allows users to declare C program variables as non-standard datatypes provides a means to overcome the overly conservative nature of compiler analysis. We leverage the fact that designers often have knowledge of the range of values that certain variables can take; feeding such information to the HLS tool can aid in generating a more optimized circuit.

In Section 3.1, we describe the main concept behind the core bitmask analysis by Gort and Anderson, which lays the foundation for our BWM framework. Section 3.2 provides a brief overview of other related techniques in literature. In Section 3.3, we describe our BWM framework in detail, which includes the updated implementation of the core bitmask analysis, the addition of two new optimizations, and the support for user-defined non-standard widths in the C source code. In Section 3.4, we present area numbers to quantify the effectiveness of the different parts of our framework. Finally, Section 3.5 summarizes the contributions described in this chapter.

### 3.1 Background

In the work by Gort and Anderson [18, 19], range analysis and bitmask analysis are combined to obtain the minimal width required for the datapaths in the HLS-generated circuit. In this technique, every variable and its intermediate state in the datapath is associated with a *bitmask*. Each value's bitmask determines which bits of that value can and cannot be safely removed without affecting the circuit's functionality. To set the initial bitmask, the range analysis from Campos et al. [9] is first applied to establish the upper and lower bound of every LLVM IR variable. Gort and Anderson devise a set of bitmask propagation rules to propagate static bits throughout the dataflow graph of the programs. These bitmask propagation rules are based on instruction type and account for all bitwise and integer arithmetic instructions. The algorithm iteratively traverses through the program's instruction stream, applying the propagation rules until all bitmasks converge. The authors implement this framework in LegUp and observe a reduction of 18% in post-synthesis LUT usage when evaluated on an Intel Cyclone II device. The benchmarks used in their evaluation includes the CHStone benchmark suite [22] (arithmetic circuits were omitted), fft and dhrystone.

#### 3.2 Related Work

Several earlier works have evaluated the effectiveness of using bitwidth information to reduce circuit area. Stephenson et al. [39] propose the *Bitwise Compiler*, which propagates value ranges through the program's control flow graph. They use program constructs to establish constraints on a variable's value range and define a set of forward and backward transit functions to propagate the ranges. When integrated with the *DeepC Silicon compiler* [8], silicon area savings ranging from 15% to 86% are achieved on Xilinx's 4000 series FPGAs. The focus of this work is on propagating value ranges, which is able to capture reduction of the most significant bits of a variable. Our bitmask based approach described in this chapter complements the range analysis and is able to capture reduction in any bit within the variable.

Cong et al. [13] apply Stephenson's algorithm to annotate the dataflow graph with bitwidth information. The scheduling and binding algorithms of the HLS tool utilize this information to minimize the total number of bits required in the functional units of the circuit. Area reduction of 36% is achieved when synthesized with Intel's Quartus II CAD tool onto Stratix FPGA boards. While this work does not propose new ways to reduce the width of a variable, it brings the range information into the different steps involved in HLS, showcasing the potential area reduction of a bitwidth aware HLS flow. Similar to this work, we also bring bitwidth information into the HLS flow, affecting mainly the allocation and binding of functional units. However, we do not modify any of the HLS algorithms to specifically optimize for area, thus evaluating the impact of bitwidth reduction on overall circuit area under a performance and area balanced situation.

Mahlke et al. [32] create a framework for *PICO* (an early HLS tool) to iteratively propagate bitwidth constraints throughout the program's instruction stream. They leverage range analysis and focus on tight loop nests. This approach yields a mean reduction of 49% in total gate count. Unlike our work in this chapter, which targets FPGAs with a fixed architecture, they target the synthesis of nonprogrammable hardware accelerators that are pipelined units more similar to ASICs.

#### 3.3 Bitwidth Minimization Framework in LegUp

The following sections present the four major components that make up the BWM framework in the LegUp HLS tool:

- 1. Updated implementation of the core bitmask analysis

- 2. Bitmask propagation for functions

- 3. Bitmask propagation for memory operations

- 4. Support for user-defined arbitrary bitwidth

We describe the details of each component in this section, and evaluate their effectiveness in Section 3.4.

#### 3.3.1 Updated Implementation of Core Bitmask Analysis

The core compiler pass that determines which bits in a variable are safe to remove is based on the algorithm initially proposed by Gort and Anderson [19]. In this pass, every LLVM value is associated with a bitmask. Each bit in the bitmask can take on one of three states in the following precedence order: a known bit (static-0 or static-1), an extension bit (E), or an unknown bit (?). For example, the bitmask of an 8-bit variable that is assigned only even numbers from -4 to 3 would be EEEEE??0. The known bits and the extension bits are both opportunities for reduction in the datapath width since they can be replaced by constants or easily inferred from the sign bit; whereas, an unknown bit represents true datapath hardware. The goal of the compiler pass is to statically assign as many of the bits in a variable's bitmask to be a known bit or an extension bit as possible.

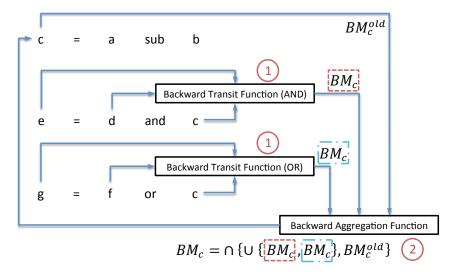

In Gort and Anderson's algorithm, constants are propagated through the program's dataflow graph at the bit level via a series of forward and backward passes on the program's variables. Their algorithm alternates between the forward propagation phase, which performs a forward pass on all variables, and the backward propagation phase, which performs a backward pass on all variables, until the bitmasks for all variables converge.

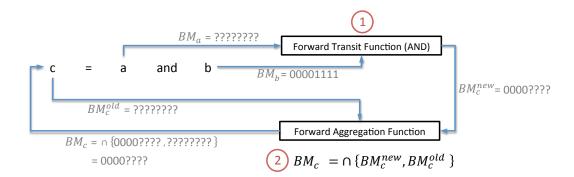

The forward propagation phase of the algorithm performs assignment analysis, which looks at how a variable is defined and generates its bitmask based on that. In this phase, each instruction's output value is visited once and put through a forward pass. A forward pass of a value involves using the *forward transit function* pertaining to the specific instruction type that produces that value and using the bitmasks of the operands to generate a reduced bitmask of that value. Like the values themselves, bitmasks traverse through the program's dataflow graph. Along the way, each instruction type dictates how the bitmasks are transformed. Once a reduced-bitmask is generated, it is put through the *forward aggregation function* along with the variable's bitmask from previous passes to generate the new bitmask resulting from the forward pass of the instruction.

00001111, applying the forward transit function of **and** states that **c** will have a bitmask of 0000????. Using the bitmask generated through the forward transit function and **c**'s original (i.e. from previous passes) bitmask, the forward aggregation function produces the final bitmask by taking the intersection of the two masks (Figure 3.1a equation). This final bitmask is the result of applying a forward pass on this instruction and reflects the actual useful toggling bits of this variable.

Table 3.2 and Table 3.3 show the definition of the *intersection* and the *union* of bitmask values. Taking the intersection of two bitmasks corresponds to finding the most optimized mask for each bit. A known bit will dominate both an extension bit and an unknown bit; an extension bit will dominate an unknown bit; but, two different-valued known bits will result in an unknown bit. Opposite to the intersection is the union of two bitmasks, which produces the least optimized mask for each bit since it has to accommodate both masks. An unknown bit will dominate both an extension bit and a known bit; an extension bit will dominate a known bit; and, two different valued known bits will result in an unknown bit. The intersection is used wherever we update a variable's old bitmask to a new reduced-width bitmask, while the union is used wherever we aggregate bitmasks from multiple variables, since we need to be conservative.

| and | 1 | 0 | ? | Е |

|-----|---|---|---|---|

| 1   | 1 | 0 | ? | Е |

| 0   | 0 | 0 | 0 | 0 |

| ?   | ? | 0 | ? | ? |

| Е   | Е | 0 | ? | Е |

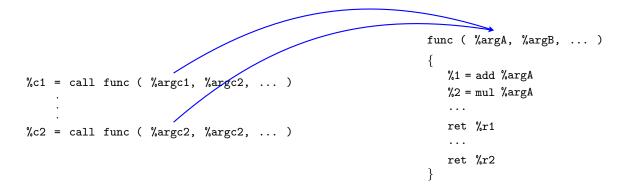

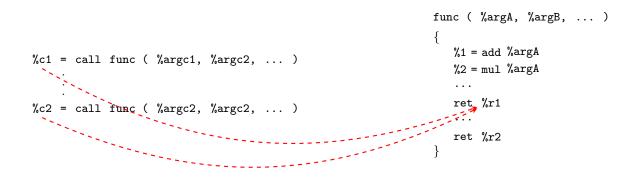

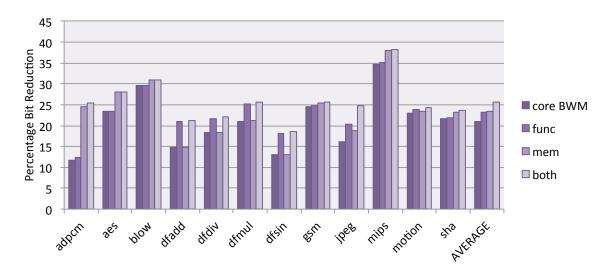

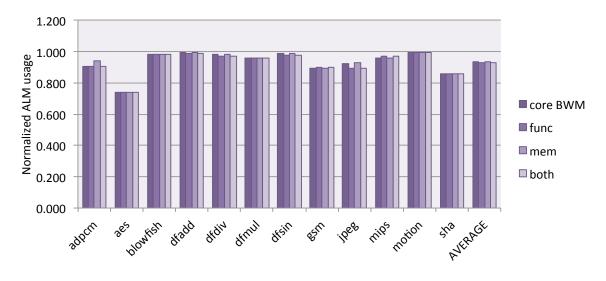

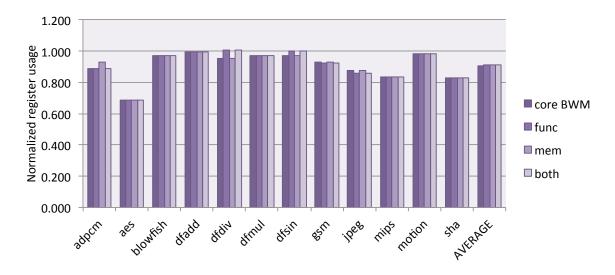

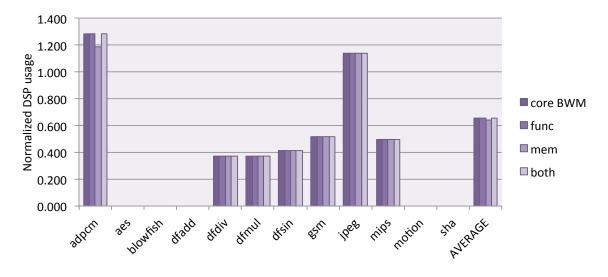

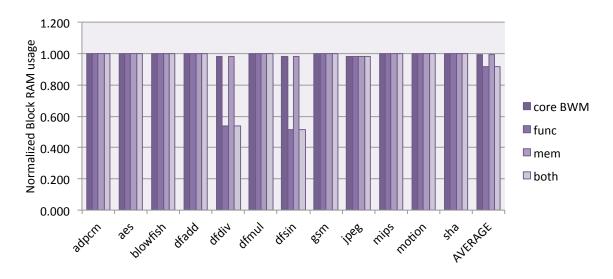

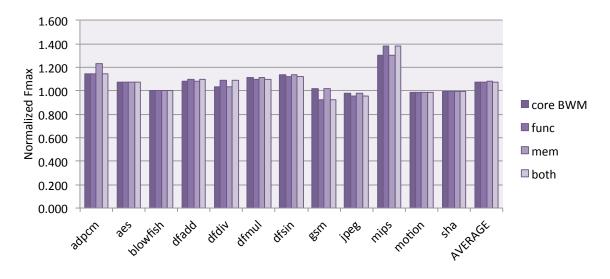

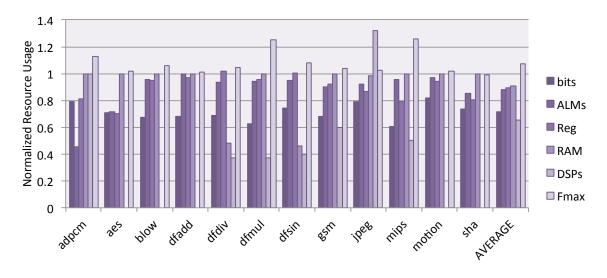

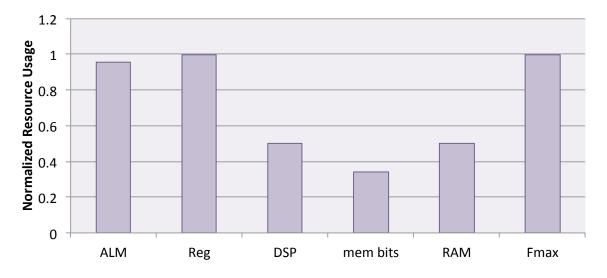

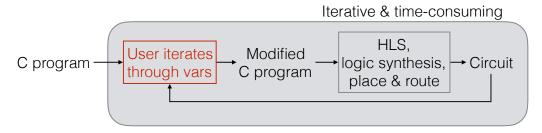

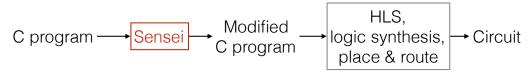

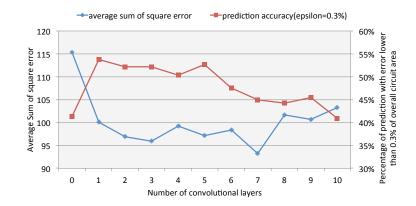

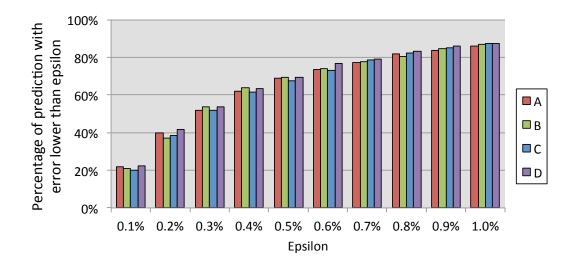

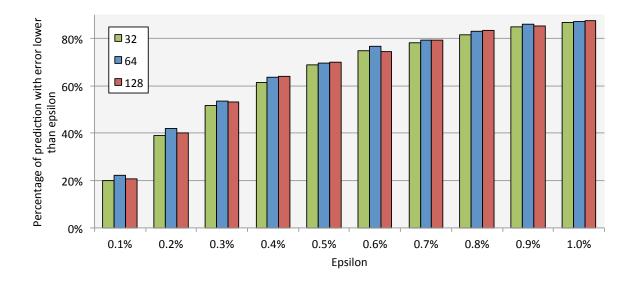

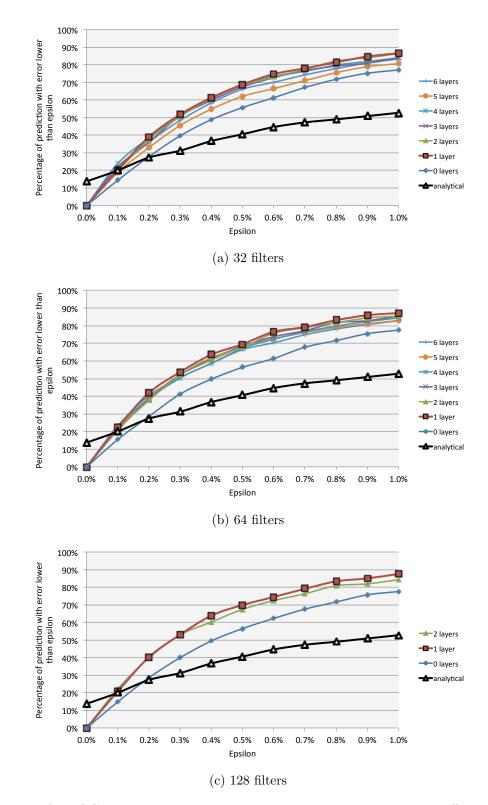

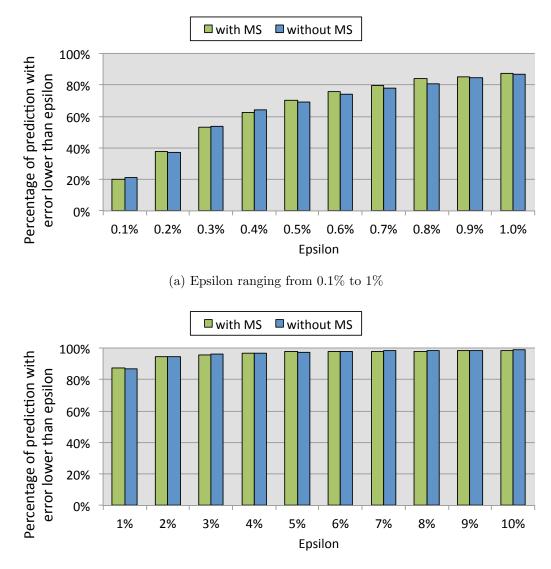

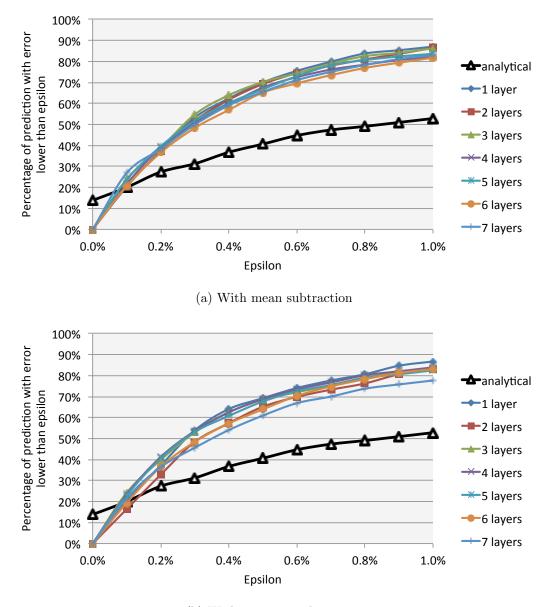

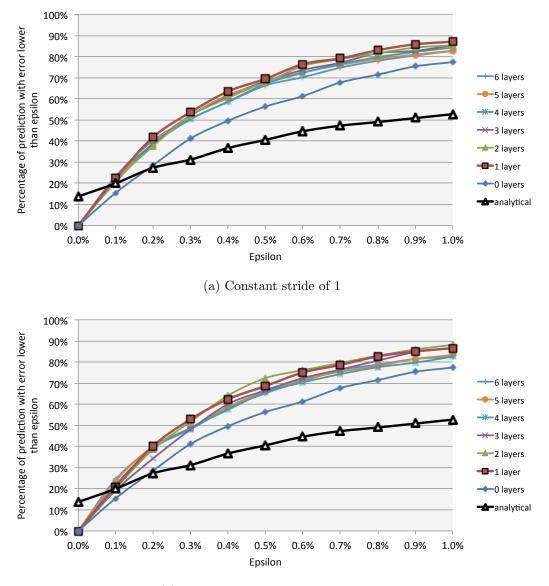

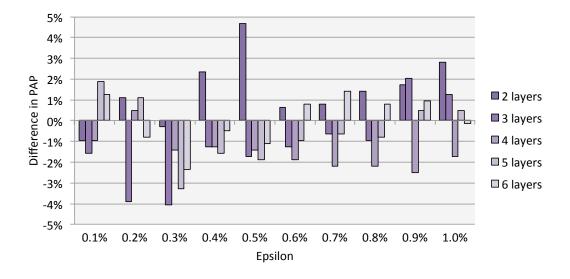

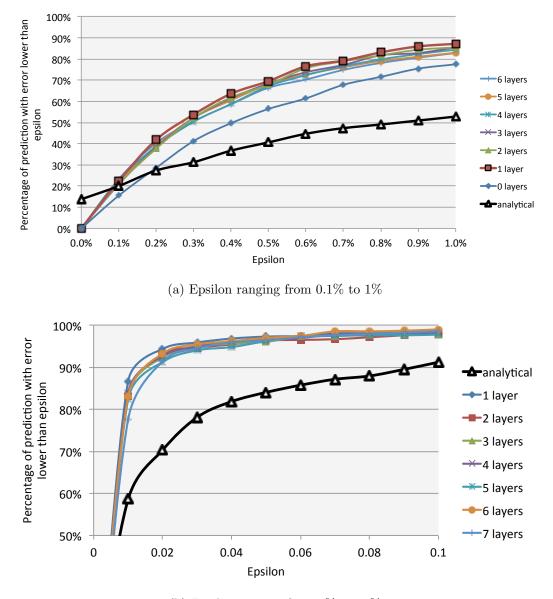

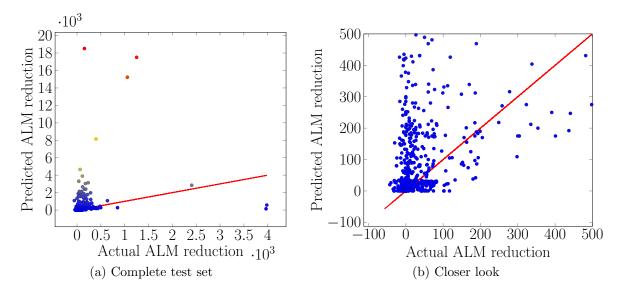

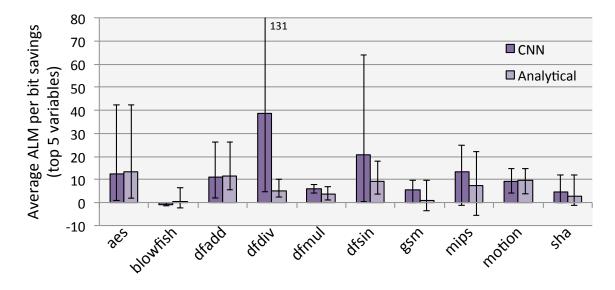

Table 3.1: Forward transit function for the **and** instruction. The row and column headings represent the bitmask of the first and second operand respectively. The entries represent the resultant bitmask given the specific operand bitmask values.