Open access · Journal Article · DOI:10.1109/LED.2010.2049092

# Memristive Behavior in Thin Anodic Titania — Source link 🗹

Kyle Miller, Kanwar S. Nalwa, Amy Bergerud, Nathan M. Neihart ...+1 more authors

Institutions: Iowa State University

Published on: 27 May 2010 - IEEE Electron Device Letters (IEEE)

Topics: Thin film, Atomic layer deposition, Ohmic contact and Titanium dioxide

# Related papers:

- The missing memristor found

- · Memristor-The missing circuit element

- · Memristive switching mechanism for metal/oxide/metal nanodevices.

- Nanoscale Memristor Device as Synapse in Neuromorphic Systems

- A Flexible Solution-Processed Memristor

# Memristive Behavior in Thin Anodic Titania

Kyle Miller, Kanwar S. Nalwa, Amy Bergerud, Nathan M. Neihart, *Member, IEEE*, and Sumit Chaudhary, *Member, IEEE*

Abstract—A common material in creating memristors is titanium dioxide (TiO<sub>2</sub>), grown by atomic layer deposition, sputtering, or sol-gel process. In this letter, we study the memristive behavior in thin TiO<sub>2</sub> films fabricated by brief electrochemical anodization of titanium. The effects of different anodization times and annealing are explored. We discover that inherent oxygenvacancies at the bottom Ti/TiO<sub>2</sub> interface naturally lead to memristive switching in nonannealed films. Annealing induces extra oxygen vacancies near the top metal/oxide interface, which leads to symmetric and ohmic current–voltage characteristics with a collapse of memristive switching. No clear dependence on anodization time was observed for times between 1 s and 1 min.

Index Terms—Electrochemical anodization, memristor, titanium dioxide.

### I. INTRODUCTION

I N 1971, using the theory of symmetry, Leon Chua predicted the existence of a fourth basic circuit element which he termed the memristor [1]. A memristor is a nonlinear, passive, and two-terminal device that maintains a functional relationship between the time integrals of voltage and current. While memristive behavior has been observed as far back as the early 1960s [2], it was not well understood until 2008 when Williams *et al.* experimentally demonstrated the natural existence of memristance in nanoscale systems where electronic and ionic transports are coupled under an external bias voltage [3].

Memristors have a wide range of potential applications. One such application is their use in ultracompact crossbar architectures [4] that can provide the same functionality as the transistor, with a greater facility of scaling down. Moreover, memories made from memristors could potentially allow greater data density than hard drives with access times potentially similar to DRAM. Additionally, memristors can also be used to model biological systems such as single-cell organisms and neurons [5].

In light of the various applications in which memristors could prove useful, it becomes necessary to explore different methods and materials that can be used to fabricate these devices. Memristors can be fabricated from a wide range of materials including organic monolayers [6], amorphous silicon [7], and

Manuscript received February 9, 2010; revised April 5, 2010; accepted April 7, 2010. Date of publication May 27, 2010; date of current version June 25, 2010. This work was supported by the National Science Foundation under Grant 0926833. The review of this letter was arranged by Editor A. Chatterjee.

The authors are with the Department of Electrical and Computer Engineering, Iowa State University, Ames, IA 50014 USA (e-mail: milleky@iastate. edu; ksnalwa@iastate.edu; aberg@iastate.edu; neihart@iastate.edu; sumitc@ iastate.edu).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2010.2049092

titanium dioxide  $(TiO_2)$ , [3], [8]–[10], with  $TiO_2$  being the most popular material for use in memristor fabrication.

Current fabrication techniques are rather less varied. A popular method in fabricating memristors involves atomic layer deposition or sputtering of TiO<sub>2</sub> [8], [10]. These deposition methods are expensive, and they require an additional high-temperature step (i.e., annealing) to create the necessary oxygen vacancies in the TiO<sub>2</sub>. Recently, researchers have demonstrated that TiO<sub>2</sub> memristors can also be fabricated by a spin-on sol-gel process [9].

This letter explores the fabrication of  $TiO_2$  memristors through electrochemical anodization of titanium, which is a simple and room-temperature process. Different anodization durations as well as the effect of post-fabrication annealing are investigated.

### **II. MEMRISTOR FABRICATION**

The fabrication procedure starts with E-beam evaporation of a  $\sim$ 500-nm-thick Ti film onto glass substrates. An area of approximately 1  $\text{cm}^2$  was then exposed to electrolyte (0.27 M NH<sub>4</sub>F in a mixture of DI water and glycerol in a volumetric ratio of 16.7:83.3). Anodization was performed at a constant potential of 30 V using a Princeton Applied Research Parstat 2273 electrochemical system. The two-electrode cell consisted of the Ti thin film as the anode and a platinum mesh as the cathode. Samples were anodized for 1, 3, 10, and 60 s. The choice of anodization times was inspired by our intention to keep the oxide thickness in the nanoscale regime, as memristance is inversely proportional to the square of the oxide thickness [3]. The exact thicknesses of the oxide films was not measured, but atomic force microscopy revealed a nonporous nature with sub-100-nm grain sizes (image not shown). Literature also predicts a growth rate of tens of nanometers per minute in similar anodization conditions [11].

Two sets of identical samples were made. One set was annealed at 550 °C for 1 h in an atmosphere of 96% N<sub>2</sub> and 4% H<sub>2</sub>, while the other set was not annealed. This created a total of eight samples which will be referred to as A1, A3, A10, A60, N1, N3, N10, and N60, where "A" refers to the annealed samples and "N" refers to the nonannealed samples. The numbers 1, 3, 10, and 60 refer to the anodization time of that particular sample in seconds.

# III. MEMRISTOR CHARACTERIZATION

Each sample was characterized using a Keithley 4200 semiconductor characterization system connected to a probe station. The bottom Ti contact was grounded for all measurements. A silver paste creates the top metallic contact.

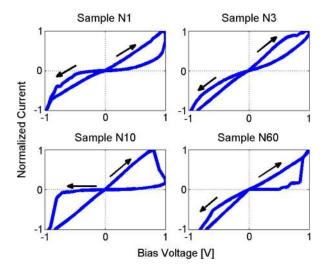

Fig. 1. Memristive switching curves for the nonannealed samples N1, N3, N10, and N60. All currents have been normalized. The arrows denote the direction of the sweep.

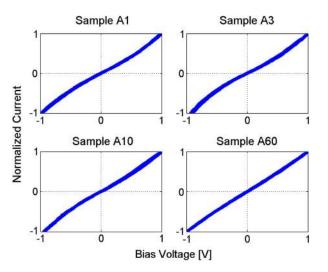

Fig. 2. Current–voltage curves for the annealed samples A1, A3, A10, and A60. All currents have been normalized.

# A. Memristive Switching Behavior

To test for memristive behavior, each sample was characterized by sweeping the bias voltage from -1 to 1 V and back to -1 V while simultaneously measuring the current. Each sweep consisted of 83 data points taken over approximately 10 s, resulting in 120 ms between each data point. Before the sweep was performed, a forming voltage of 8 V was first applied to each sample. Fig. 1 shows the results for the nonannealed samples, and Fig. 2 shows the results for the annealed samples. The magnitude of the measured current varies from one sample to the next by as much as an order of magnitude. In order to provide a clear comparison between the various samples, the measured current for each sample was normalized by the maximum value for that particular sample.

From Fig. 1, it is seen that all nonannealed samples have the bias-dependent bipolar switching characteristics that are indicative of memristors, as opposed to the filament-controlled unipolar switching characteristics of fuse-antifuse-type resistive memory elements [12]. Also, with the exception of sample

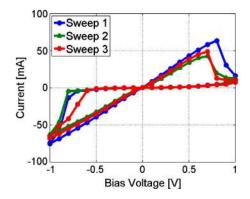

Fig. 3. Current-voltage curves for nonannealed sample N10, showing three consecutive sweeps.

N60, all samples have a high degree of symmetry with respect to the origin. There are, however, differences in the normalized conductivity of the respective high- and low-conductivity states (referred to as the ON and OFF states, respectively).

The normalized conductivity of the ON and OFF states for sample N1 is 890.2 and 61.6 mS, respectively. The normalized conductivity of the ON and OFF states for sample N3 is 1.231 S and 438.5 mS, respectively. The normalized conductivity of the ON and OFF states of sample N10 is 1.2560 S and 22.4 mS, respectively. The conductivity of the ON and OFF states could not be accurately estimated for sample N60 due to asymmetric I-V characteristic.

The reproducibility of the memristive switching characteristics was also studied. Fig. 3 shows three consecutive sweeps for sample N10. The sweep rate was mentioned earlier, and while it was not tested, it is expected that the curves in Fig. 3 would collapse to resemble the curves in Fig. 2 if the sweep rate was to be greatly increased [3].

All other nonannealed samples showed similar levels of reproducibility when consecutive measurements were taken at the same spot as well as when measurements were taken at different points on the sample. Slight variations in the current levels across different sweeps, as shown in Fig. 3, are expected and have been previously observed (e.g., see [10]). The current flowing through the memristor is higher than previously reported devices (e.g., see [3] and [10]), but this is due to the larger cross-sectional area of our devices ( $\sim 1 \text{ cm}^2$  as compared to  $\sim 2500 \text{ nm}^2$  for the devices in [10]).

No memristive behavior was observed for the annealed samples (Fig. 2). The I-V characteristics for all annealed samples resembled a single ohmic state with a slight nonrectifying Schottky barrier nature, as can be seen by a slight deviation of the I-V characteristics from a straight line.

#### B. Soft-Switching Behavior

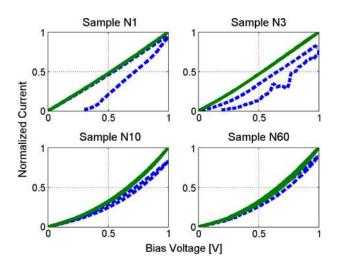

We also characterized our samples for "soft switching," which is the regime in which consecutive bias sweeps of the same polarity lead to changes in conductivity with each sweep [9]. No forming voltage was applied prior to performing this characterization, and each sweep consisted of 41 data points, taking approximately 5 s. The bias voltage for each sample was repeatedly swept from 0 to 1 V and back to 0 V. Fig. 4 shows the measured curves for the nonannealed samples, and Fig. 5 shows

Fig. 4. Soft-switching curves for the nonannealed samples N1, N3, N10, and N60. All currents have been normalized. The dashed and solid curves represent the first and sixth sweeps, respectively.

Fig. 5. Soft-switching curves for the annealed samples A1, A3, A10, and A60. All currents have been normalized. The dashed and solid curves represent the first and sixth sweeps, respectively.

the measured curves for the annealed samples. The dashed and solid curves are the first and last sweeps, respectively, in a series of six sweeps.

# IV. DISCUSSION

One possible reason for the superior performance of sample N10 among the nonannealed samples may come from the thickness of the oxide layer. Samples N1 and N3 used relatively short anodization times, resulting in thinner oxide layers. It is known that the Ti/TiO<sub>2</sub> interface generates oxygen vacancies [10]. If it is assumed that the quantity of vacancies is roughly equal (due to equal size of the samples), then as the oxide layer becomes thinner, the insulating nature of the oxide degrades, and the ON–OFF ratio deteriorates. The reason behind the asymmetry in the I-V curve of sample N60 is not clear, but such asymmetries have also been observed by other investigators [9], [10]. Our results show that among the anodization times studied, anodization for 10 s results in the best memristive switching. However, more anodization durations need to be done in order to establish

stronger correlation between memristance and the duration of anodization. Optimal durations will obviously be different for different electrolytes and anodization voltages.

In the case of the annealed samples, extra oxygen vacancies are created at the top of the  $TiO_2$  layer by annealing, in addition to already existing vacancies at the bottom  $Ti/TiO_2$ interface. This creates ohmic contacts at both terminals, thus leading to the collapse of both memristive and soft switchings. This argument is in line with the switching mechanism established recently, according to which one nonohmic metal/oxide electronic barrier is essential for memristive switching in metal/oxide/metal memristors [10].

Finally, we expect that the yield of memristors fabricated using our method would be potentially high because anodization is a one-step process, and no additional high-temperature steps are required.

### V. CONCLUSION

In conclusion, a brief electrochemical anodization of titanium has been presented as an inexpensive, simple, and roomtemperature alternative in fabricating  $TiO_2$  memristors. It has been demonstrated that no annealing step is required due to the inherent existence of oxygen vacancies at the  $Ti/TiO_2$ interface. Also, while it is expected that these devices will show a frequency-dependent and pinched-hysteresis curve, it should be mentioned that this is the only way to definitively prove that the devices are "ideal" memristors, where an "ideal" memristor is one whose input/output relations are described by the time integrals of the voltage and current [1], [3].

#### REFERENCES

- L. O. Chua, "Memristor—The missing circuit element," *IEEE Trans. Circuit Theory*, vol. CT-18, no. 5, pp. 507–519, Sep. 1971.

- [2] T. W. Hickmott, "Low-frequency negative resistance in thin anodic oxide films," J. Appl. Phys., vol. 33, no. 9, pp. 2669–2682, Sep. 1962.

- [3] D. B. Strukov, G. S. Sniker, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 179, pp. 80–83, May 2008.

- [4] S. H. Jo, K. H. Kim, and W. Lu, "High-density crossbar arrays based on Si memristive system," *Nano Lett.*, vol. 9, no. 2, pp. 870–874, Feb. 2009.

- [5] Y. V. Pershin, S. La Fontain, and M. Di Ventra, "Memristive model of amoeba's learning," *Phys. Rev. E, Stat. Phys. Plasmas Fluids Relat. Interdiscip. Top.*, vol. 80, no. 2, pp. 021 926-1–021 926-6, Aug. 2009.

- [6] D. R. Stewart, D. A. A. Ohlberg, P. A. Beck, Y. Chen, R. S. Williams, J. O. Jeppesen, K. A. Nielsen, and J. F. Stoddart, "Molecule-independent electrical switching in Pt/organic monolayer/Ti devices," *Nano Lett.*, vol. 4, no. 1, pp. 133–136, Jan. 2004.

- [7] S. H. Jo and W. Lu, "CMOS compatible nanoscale nonvolatile resistance switching memory," *Nano Lett.*, vol. 8, no. 2, pp. 392–397, Feb. 2008.

[8] B. J. Choi, D. S. Jeong, S. K. Kim, C. Rohde, S. Choi, J. G. Oh,

- [8] B. J. Choi, D. S. Jeong, S. K. Kim, C. Rohde, S. Choi, J. G. Oh, H. J. Kim, C. S. Hwang, K. Szot, R. Waser, B. Reichenberg, and S. Tiedke, "Resistive switching mechanism of TiO<sub>2</sub> thin films grown by atomiclayer deposition," *J. Appl. Phys.*, vol. 98, no. 3, pp. 033 715-1–033 715-10, Aug. 2005.

- [9] N. G. Hackett, B. Hamadani, B. Dunlap, J. Suehle, C. Richter, C. Hacker, and D. Gundlach, "A flexible solution-processed memristor," *IEEE Electron Device Lett.*, vol. 30, no. 7, pp. 706–708, Jul. 2009.

- [10] J. J. Yang, M. D. Pickett, X. Li, D. A. A. Ohlberg, D. R. Steward, and R. S. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," *Nat. Nanotechnol.*, vol. 3, no. 7, pp. 429–433, Jul. 2008.

- [11] J. M. Macak, H. Tsuchiya, L. Taveira, S. Aldebergerova, and P. Schmuki, "Smooth anodic TiO2 nanotubes," *Angew. Chem. Int. Ed.*, vol. 44, no. 45, pp. 7463–7465, Dec. 2005.

- [12] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," *Nat. Mater.*, vol. 6, no. 11, pp. 833–840, Nov. 2007.