# **Portland State University**

# **PDXScholar**

Dissertations and Theses

**Dissertations and Theses**

Spring 1-1-2012

# **Memristor-based Reservoir Computing**

Manjari S. Kulkarni Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Artificial Intelligence and Robotics Commons, Electrical and Electronics Commons, and the Nanotechnology Fabrication Commons

# Let us know how access to this document benefits you.

#### **Recommended Citation**

Kulkarni, Manjari S., "Memristor-based Reservoir Computing" (2012). *Dissertations and Theses.* Paper 899.

https://doi.org/10.15760/etd.899

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

# Memristor-based Reservoir Computing

by

Manjari S. Kulkarni

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science in Electrical and Computer Engineering

Thesis Committee: Christof Teuscher, Chair Dan Hammerstrom Roy Kravitz

Portland State University 2012

#### Abstract

In today's nanoscale era, scaling down to even smaller feature sizes poses a significant challenge in the device fabrication, the circuit, and the system design and integration. On the other hand, nanoscale technology has also led to novel materials and devices with unique properties. The memristor is one such emergent nanoscale device that exhibits non-linear current-voltage characteristics and has an inherent memory property, i.e., its current state depends on the past. Both the nonlinear and the memory property of memristors have the potential to enable solving spatial and temporal pattern recognition tasks in radically different ways from traditional binary transistor-based technology. The goal of this thesis is to explore the use of memristors in a novel computing paradigm called "Reservoir Computing" (RC). RC is a new paradigm that belongs to the class of artificial recurrent neural networks (RNN). However, it architecturally differs from the traditional RNN techniques in that the pre-processor (i.e., the reservoir) is made up of random recurrently connected non-linear elements. Learning is only implemented at the readout (i.e., the output) layer, which reduces the learning complexity significantly. To the best of our knowledge, memristors have never been used as reservoir components. We use pattern recognition and classification tasks as benchmark problems. Real world applications associated with these tasks include process control, speech recognition, and signal processing. We have built a software framework, RCspice (Reservoir Computing Simulation Program with Integrated Circuit Emphasis), for this purpose. The framework allows to create random memristor networks, to simulate and evaluate them in Ngspice, and to train the readout layer by means of Genetic Algorithms (GA). We have explored reservoir-related parameters, such as the network connectivity and the reservoir size along with the GA parameters.

Our results show that we are able to efficiently and robustly classify time-series patterns using memristor-based dynamical reservoirs. This presents an important step towards computing with memristor-based nanoscale systems.

## Acknowledgements

Completion of this thesis has been a journey with unforgettable moments of stress, anxiety and final moments of my thesis defense has molded into sense of accomplishment and success. I take this opportunity to thank all those who have provided invaluable support and guidance throughout this journey.

First and foremost I would like to thank my adviser, Professor Christof Teuscher, for generously providing guidance on the thesis topic, continuously encouraging me even when at times the results were not as expected, and for all the patience and support given to me since day one for my thesis completion. I would also like to thank Professor Dan Hammerstrom and Professor Roy Kravitz for serving on my defense committee. Your insights and comments are very much appreciated.

I would like to sincerely thank my husband for his support throughout my Master's at Portland State University. Support of my family and their interest in "Reservoir Computing and Memristor" has led to various discussions that have enabled me to think and understand this topic in a different light.

This work was partly sponsored by the National Science Foundation, (grant number 1028378) and the Sigma Xi Grants-in-Aid of Research program.

# Contents

| $\mathbf{A}$ | bstra | et                                   | j   |

|--------------|-------|--------------------------------------|-----|

| $\mathbf{A}$ | ckno  | vledgements                          | iii |

| Li           | st of | Tables v                             | iii |

| Li           | st of | Figures                              | ix  |

| 1            | Ove   | rview                                | 1   |

|              | 1.1   | Introduction and Motivation          | 1   |

|              | 1.2   | Challenges                           | 2   |

|              | 1.3   | Research Questions                   | 4   |

|              | 1.4   | Our Approach in a Nutshell           | 4   |

|              | 1.5   | Thesis Organization                  | 6   |

| 2            | Bac   | ground                               | 7   |

|              | 2.1   | Non-classical Computing Paradigms    | 7   |

|              | 2.2   | Artificial Neural Networks           | 7   |

|              | 2.3   | Reservoir Computing                  | 8   |

|              |       | 2.3.1 Liquid State Machines          | 9   |

|              |       | 2.3.2 Echo State Network             | 10  |

|              |       | 2.3.3 Types of Reservoirs            | 11  |

|              | 2.4   | Memristor                            | 13  |

|              |       | 2.4.1 Modeling Memristor using SPICE | 16  |

| 3 | Sim | ulation                  | r Framework                                                | 19 |

|---|-----|--------------------------|------------------------------------------------------------|----|

|   | 3.1 | Main I                   | Modules of the Framework                                   | 20 |

| 4 | Mer | $\operatorname{mristor}$ | -based Reservoir Computing Architecture                    | 26 |

|   | 4.1 | Input                    | Layer                                                      | 27 |

|   | 4.2 | Memri                    | stor Reservoir                                             | 27 |

|   |     | 4.2.1                    | Graph Based Approach for Representing Memristor Reservoirs | 27 |

|   |     | 4.2.2                    | Adjacency Matrix Representation                            | 28 |

|   |     | 4.2.3                    | Template Structure for Memristor Reservoir                 | 29 |

|   |     | 4.2.4                    | Generating a Memristor Reservoir                           | 30 |

|   | 4.3 | Reado                    | ut Layer                                                   | 36 |

|   | 4.4 | Trainin                  | ng Algorithm                                               | 36 |

| 5 | Eva | luation                  | n Methodology                                              | 38 |

|   | 5.1 | Reserv                   | roir Evaluation using Ngspice                              | 38 |

|   | 5.2 | Reado                    | ut Training using Genetic Algorithms                       | 39 |

|   |     | 5.2.1                    | Population Representation and Initialization               | 42 |

|   |     | 5.2.2                    | Decoding the Chromosomes                                   | 43 |

|   |     | 5.2.3                    | Fitness Function                                           | 45 |

|   |     | 5.2.4                    | Population Selection and Diversity                         | 46 |

|   |     | 5.2.5                    | Population Reinsertion and Termination                     | 47 |

| 6 | Mer | $\operatorname{mristor}$ | Reservoirs                                                 | 49 |

|   | 6.1 | 6-Node                   | e Reservoirs                                               | 49 |

|   | 6.2 | 10-Noc                   | de Reservoirs                                              | 53 |

|   | 6.3 | 15-Noc                   | de Reservoirs                                              | 58 |

|   | 6.4 | 30-Noc                   | de Reservoirs                                              | 63 |

|   |     |                          |                                                            |    |

|              | 6.5           | 40-Node Reservoirs                                                     | 68         |

|--------------|---------------|------------------------------------------------------------------------|------------|

| 7            | Exp           | periments and Results                                                  | <b>7</b> 3 |

|              | 7.1           | Experiment 1: Reservoir and GA Parameter Exploration                   | 74         |

|              | 7.2           | Experiment 2: Pattern Recognition for Triangular-Square Signal $ . $ . | 80         |

|              | 7.3           | Experiment 2a: Input Variation for Triangular-Square Pattern $\ .$     | 86         |

|              | 7.4           | Experiment 3: Pattern Recognition for Frequency Modulated Signal       | 88         |

|              | 7.5           | Experiment 4: Pattern Recognition for Amplitude Modulated Signal       | 93         |

|              | 7.6           | Experiment 5: Associative Memory                                       | 96         |

|              | 7.7           | Experiment 6: Logical Computation                                      | 101        |

| 8            | Cor           | nclusion and Future Work                                               | 106        |

| $\mathbf{R}$ | References 11 |                                                                        |            |

# List of Tables

| 5.1 | An example of encoding node, weight and bias variables into a chro-   |    |

|-----|-----------------------------------------------------------------------|----|

|     | mosome                                                                | 43 |

| 5.2 | Decoded chromosome range and type definition                          | 44 |

| 5.3 | An example of decoded chromosome representing decoded values for      |    |

|     | variables node, weight and bias                                       | 44 |

| 5.4 | An example of non-linear ranking scheme used for evaluating raw       |    |

|     | fitness values                                                        | 46 |

| 5.5 | An example of fitness-based reinsertion scheme in which offspring     |    |

|     | replace the least fit parents with $80\%$ of reinsertion rate. Here,  |    |

|     | the number of individuals for the original population is 8 and the    |    |

|     | selected population is 6. For the reinsertion rate of 80%, a total    |    |

|     | of 5 individuals from the selected population replace the least fit   |    |

|     | individuals in the original population. The new fitness values are    |    |

|     | copied according to the inserted selected population [1]              | 48 |

| 6.1 | Reservoir size and the memristor count $(MC)$                         | 50 |

| 7.1 | Reservoir fitness averaged over 5 simulations for population size 50, |    |

|     | reinsertion rate of 0.08                                              | 79 |

| 7.2 | Simulation results obtained for the triangular-square signal with     |    |

|     | amplitude of $(\pm 0.6V)$                                             | 80 |

| 7.3 | Simulation results obtained for the triangular-square input pattern   |    |

|     | as a function of amplitude variation and reservoir sizes              | 86 |

| 7.4 | Fitness results obtained for SFFM input signal with $MI = 5$ and                                                       |     |

|-----|------------------------------------------------------------------------------------------------------------------------|-----|

|     | $MI = 4. \dots $ | 89  |

| 7.5 | Simulation results obtained for amplitude modulated signal                                                             | 93  |

| 7.6 | Fitness values obtained for the associative memory experiment                                                          | 97  |

| 7.7 | Table summarizes the simulation results obtained for logical OR                                                        |     |

|     | operation                                                                                                              | 102 |

# List of Figures

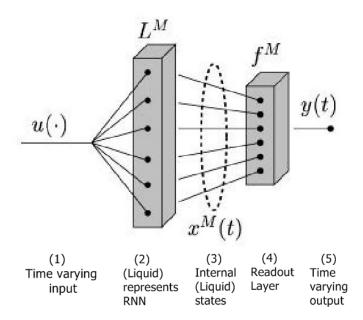

| 2.1 | Architecture of a <i>Liquid State Machine</i>                                   | 10 |

|-----|---------------------------------------------------------------------------------|----|

| 2.2 | In [2], Fernando et al. used water as a pre-processor ('liquid') for            |    |

|     | LSM implementation. (Source: [3])                                               | 12 |

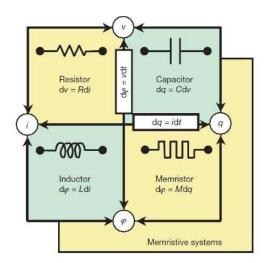

| 2.3 | Four fundamental variables, charge, flux, voltage and current defin-            |    |

|     | ing the circuit elements resistance, memristance, inductor and ca-              |    |

|     | pacitor. The memristor is equivalent to the resistor when the rate              |    |

|     | of change of flux $\phi$ with respect to charge $q$ is constant. (Source: [4]). | 14 |

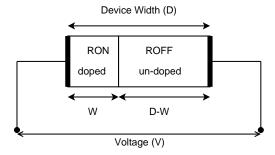

| 2.4 | Representation of the $TiO_2$ memristor device. The doped region                |    |

|     | represents low resistance $R_{on}$ and the un-doped region represents           |    |

|     | high resistance $R_{off}$ . (Source: redrawn from [4].)                         | 14 |

| 2.5 | Memristor's hysteretic $I-V$ characteristic. (Source: [4]). (top)               |    |

|     | Nonlinear change in the current with respect to the applied voltage             |    |

|     | $Vsin(\omega_0 t)$ . (middle) The change in the internal state is measured as   |    |

|     | the ration of the doped width $w$ to total device width $D$ . (bottom)          |    |

|     | Frequency dependent hysterysis $I-V$ curve. The memristor is a                  |    |

|     | frequency-dependent device, it can be seen that as the frequency                |    |

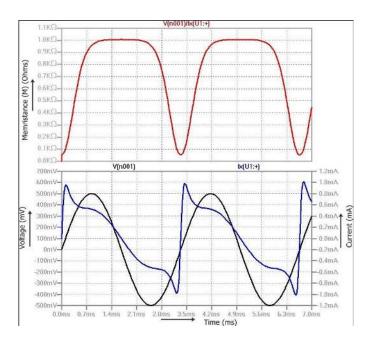

|     | changes from $\omega_0$ to $10\omega_0$ , it shows linear characteristics       | 16 |

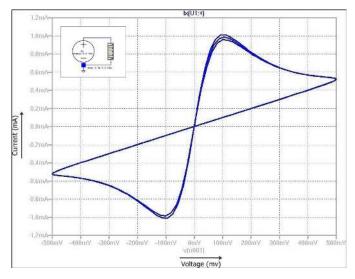

| 2.6 | Simulation of the memristor SPICE model [5] with a sinusoid of         |    |

|-----|------------------------------------------------------------------------|----|

|     | 300Hz and 0.5V amplitude. (top) Change in the memristance with         |    |

|     | respect to the applied input. Memristance increases for a positive     |    |

|     | going input and decrease for a negative going input. (bottom) Non-     |    |

|     | linear change in the current with respect to the applied sinusoid      |    |

|     | input                                                                  | 18 |

| 2.7 | Memristor's hysteretic $I-V$ characteristic for applied sinusoid of    |    |

|     | 300Hz and 0.5V amplitude.                                              | 18 |

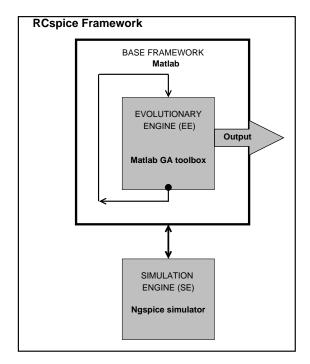

| 3.1 | RCspice Framework overview                                             | 20 |

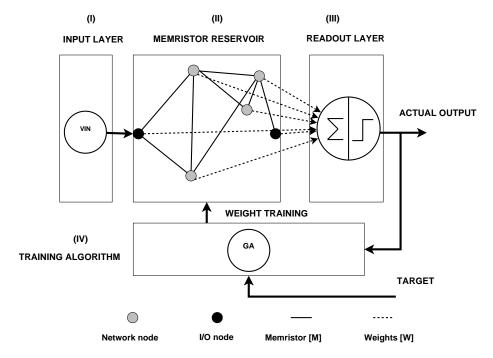

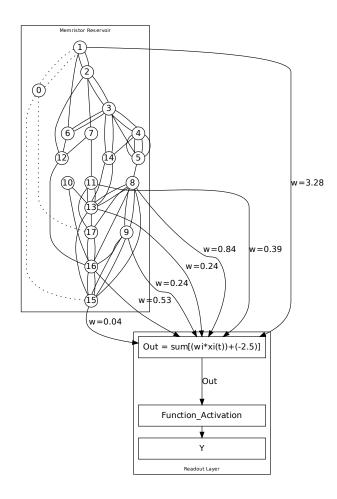

| 4.1 | Architecture overview of memristor-based reservoir computing. (I)      |    |

|     | The input layer, (II) memristor reservoir and (III) readout layer.     |    |

|     | GAs are used for training the weights of the readout layer             | 26 |

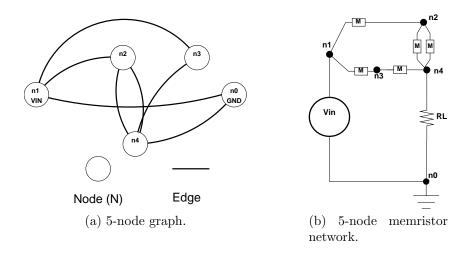

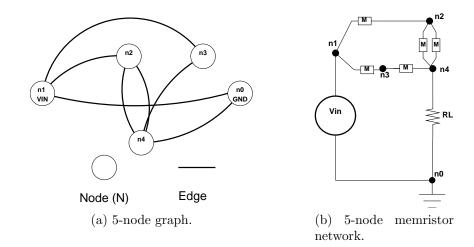

| 4.2 | A 5-node undirected bi-connected graph and its equivalent memris-      |    |

|     | tor network                                                            | 28 |

| 4.3 | A 5-node undirected bi-connected graph and its equivalent memris-      |    |

|     | tor network                                                            | 30 |

| 4.4 | A $5\times5$ adjacency matrix representation of the 5-node graph shown |    |

|     | in Figure 4.3a                                                         | 30 |

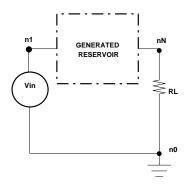

| 4.5 | Template circuit for generating the memristor-reservoir. (Source:      |    |

|     | adapted from [6])                                                      | 31 |

| 4.6 | A 3×3 template adjacency matrix representation                         | 31 |

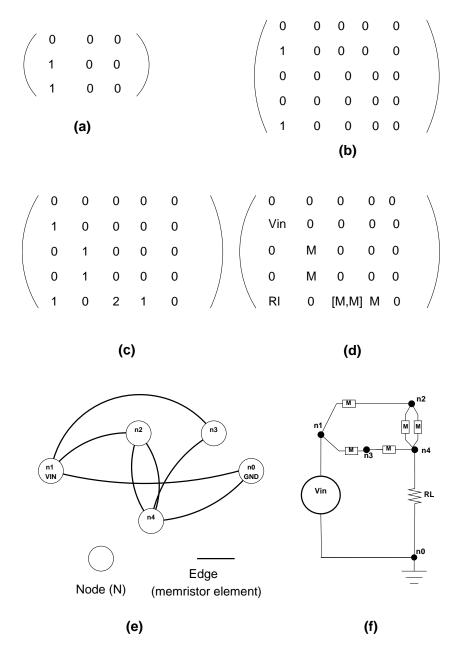

- 4.7 Steps for generating a memristor reservoir by using an adjacency matrix. (a) A 3×3 template adjacency matrix T. (b) The template adjacency matrix expanded to add N user defined nodes. Here, (N = 2) creating a 5×5 adjacency matrix. (c) Using procedure in step (3), random edges are added between the row and columns of the adjacency matrix representing memristor element. (d) An equivalent component matrix define components used. (e) Graph representation of the adjacency matrix in sub-figure (e). (f) Fully connected memristor reservoir with component values. . . . . . . . .

34

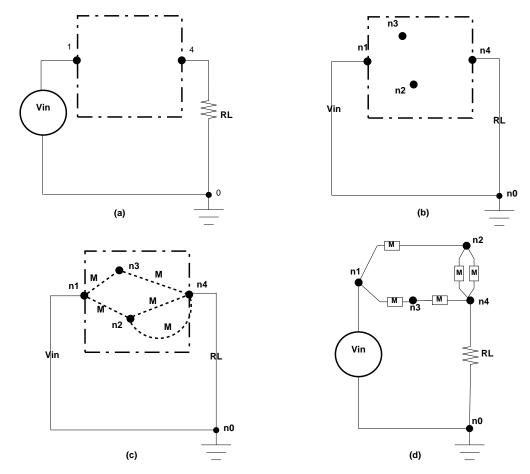

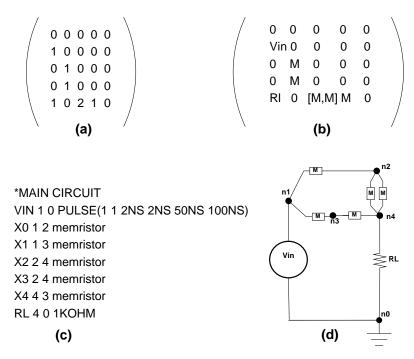

5.1 An example of the netlist formation. (a) Adjacency matrix representing the reservoir connectivity. (b) Component matrix defining the components used. (c) Ngspice netlist extracted from the component matrix. (d) Reservoir representation of the extracted netlist. 39

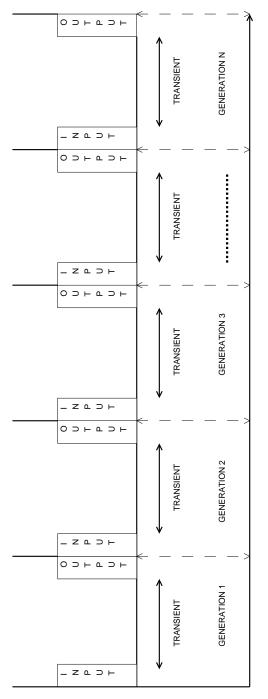

| 5.2 | An input signal is evaluated at every generation. The transient             |    |

|-----|-----------------------------------------------------------------------------|----|

|     | time is task specific. The genetic algorithm evaluates the output           |    |

|     | response at the end of the transient analysis. The output response          |    |

|     | is evaluated with respect to the evolved weights, nodes and the bias        |    |

|     | values                                                                      | 41 |

| 5.3 | Population matrix of size $Nind \times Lind$ . The number of rows corre-    |    |

|     | sponds to the number of individuals, the number of columns from             |    |

|     | (1 to $N-1$ ) represents the node-weight chromosome, and the $N^{th}$       |    |

|     | column is the bias chromosome                                               | 43 |

| 5.4 | An example of an encoded population matrix for a 5-node reservoir.          |    |

|     | First [1 to $N-1$ ] columns represents the $NW$ chromosome. In              |    |

|     | each 9-bit $NW$ chromosome, the $1^{st}$ -bit is node $n$ and bit [2 to 8]  |    |

|     | represents weight $W.$ The $N^{th}$ column represents the 8-bit bias $B.$ . | 45 |

| 5.5 | An example decoded population matrix for a 5-node reservoir. The            |    |

|     | first [1 to $N-1$ ] columns represents $NW$ chromosome. From the 9-         |    |

|     | bit $NW$ chromosome, the $1^{st}$ -bit decoded as an integer representing   |    |

|     | reservoir node $n$ and binary bits from [2 to 8] represents the node        |    |

|     | weight $W$ , which is decoded to be a real value. The $N^{th}$ column       |    |

|     | represents 8-bit bias $B$ decoded to be a real value                        | 45 |

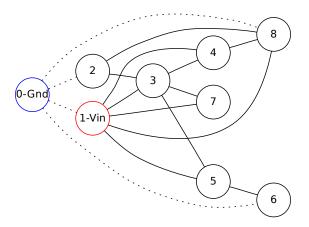

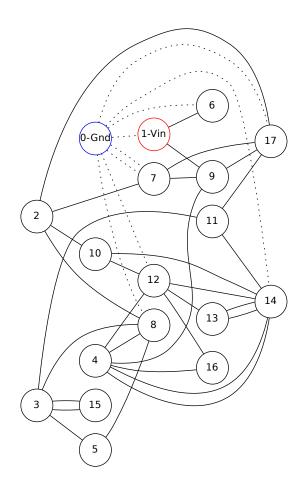

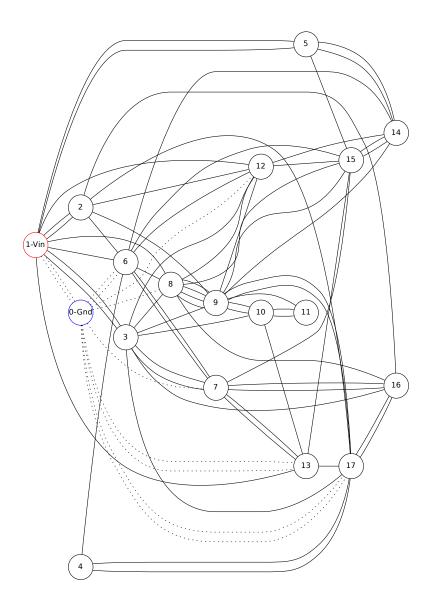

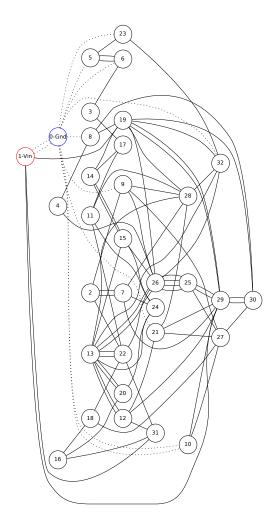

| 6.1 | <b>6-node reservoir 1</b> . The red node represents the input node (VIN)    |    |

|     | and the blue node is the ground node (GND). The dotted and solid            |    |

|     | lines represent memristors                                                  | 49 |

| 6.2 | <b>6-node reservoir 2</b> . The red node represents the input node (VIN)    |    |

|     | and the blue node is the ground node (GND). The dotted and solid            |    |

|     | lines represent memristors                                                  | 51 |

| <b>6-node reservoir 3</b> . The red node represents the input node (VIN) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and the blue node is the ground node (GND). The dotted and solid         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| lines represent memristors                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

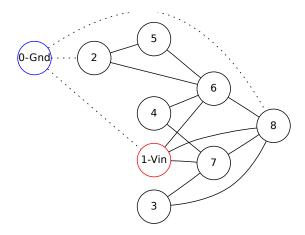

| 6-node reservoir 4. The red node represents the input node (VIN)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and the blue node is the ground node (GND). The dotted and solid         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| lines represent memristors                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6-node reservoir 5. The red node represents the input node (VIN)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and the blue node is the ground node (GND). The dotted and solid         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| lines represent memristors                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

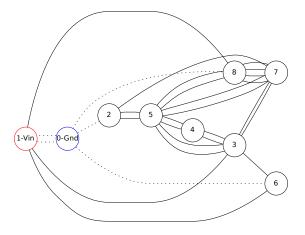

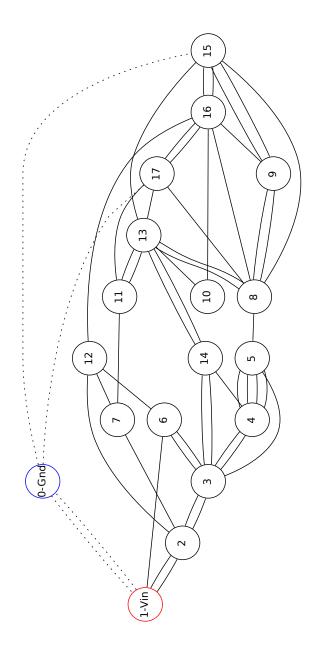

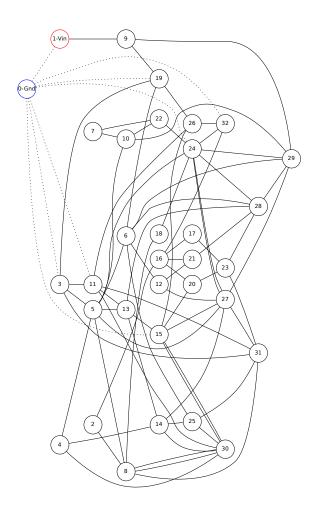

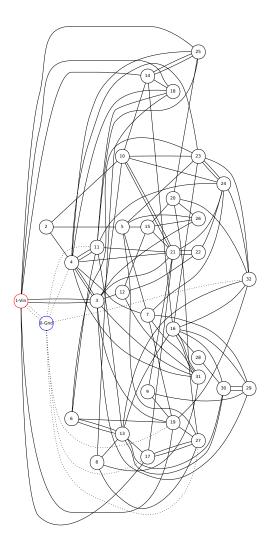

| 10-node reservoir 1. The red node represents the input node              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (VIN) and the blue node is the ground node (GND). The dotted             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and solid lines represent memristors                                     | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

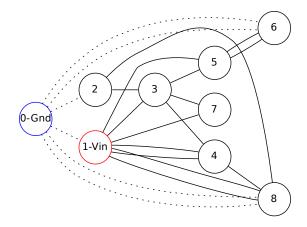

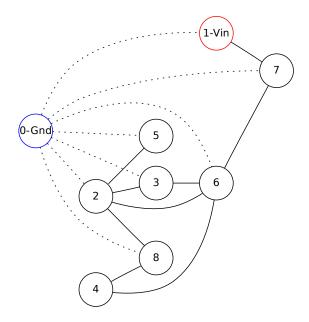

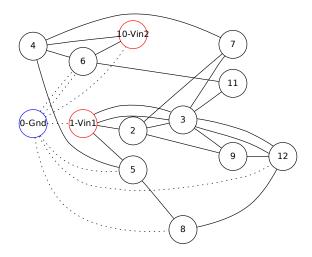

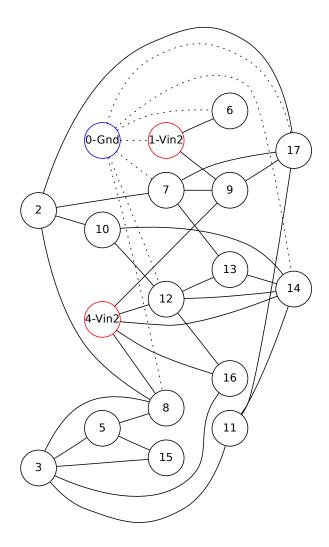

| 10-node reservoir 2. The red node represents two inputs (VIN1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and VIN2) and the blue node is the ground node (GND). The dotted         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and solid lines represent memristors.                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

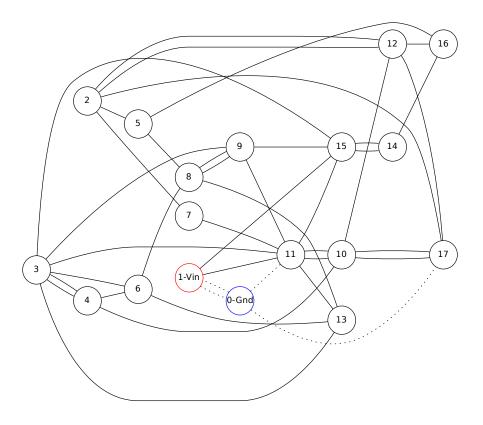

| 10-node reservoir 3. The red node represents the input node              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (VIN) and the blue node is the ground node (GND). The dotted             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and solid lines represent memristors                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

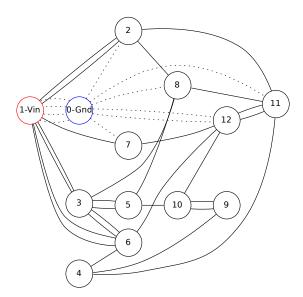

| 10-node reservoir 4. The red node represents the input node              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (VIN) and the blue node is the ground node (GND). The dotted             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                          | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                          | and the blue node is the ground node (GND). The dotted and solid lines represent memristors.  6-node reservoir 4. The red node represents the input node (VIN) and the blue node is the ground node (GND). The dotted and solid lines represent memristors.  6-node reservoir 5. The red node represents the input node (VIN) and the blue node is the ground node (GND). The dotted and solid lines represent memristors.  10-node reservoir 1. The red node represents the input node (VIN) and the blue node is the ground node (GND). The dotted and solid lines represent memristors.  10-node reservoir 2. The red node represents two inputs (VIN1 and VIN2) and the blue node is the ground node (GND). The dotted and solid lines represent memristors.  10-node reservoir 3. The red node represents the input node (VIN) and the blue node is the ground node (GND). The dotted and solid lines represent memristors. |

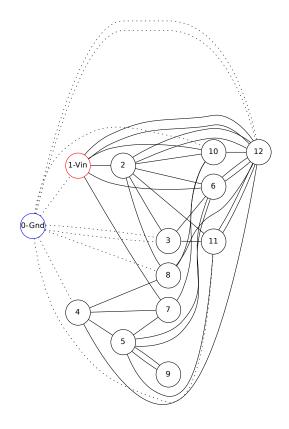

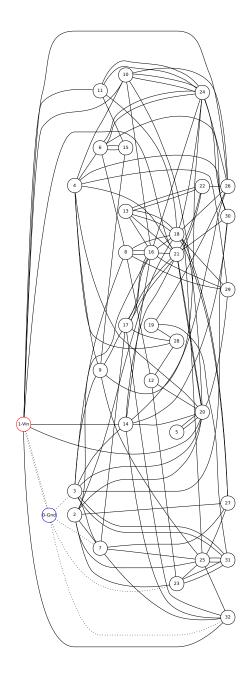

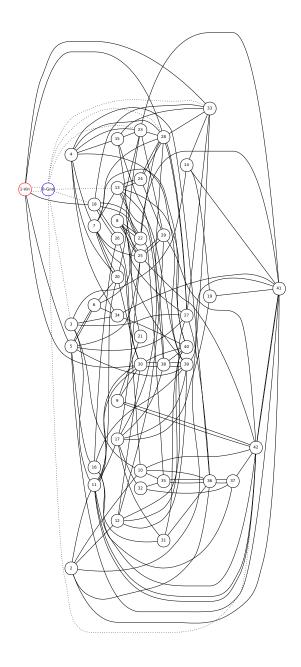

| 6.11 | 15-node reservoir 1. The red node represents the input node      |    |

|------|------------------------------------------------------------------|----|

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors                             | 58 |

| 6.12 | 15-node reservoir 2. The red node represents the input node      |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors.                            | 59 |

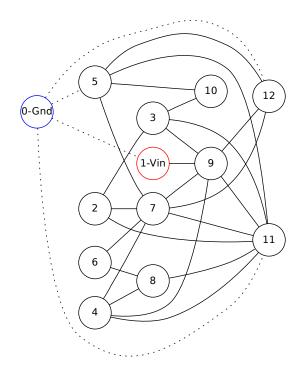

| 6.13 | 15-node reservoir 3. The red node represents two the input sig-  |    |

|      | nals (VIN1 and VIN2) and the blue node is the ground node (GND). |    |

|      | The dotted and solid lines represent memristors                  | 60 |

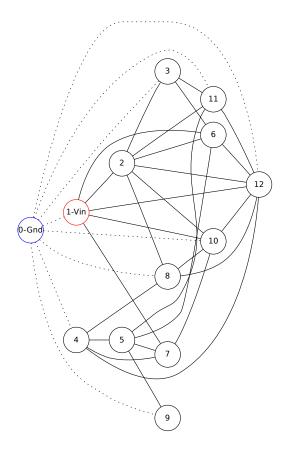

| 6.14 | 15-node reservoir 4. The red node represents the inputs (VIN)    |    |

|      | and the blue node is the ground node (GND). The dotted and solid |    |

|      | lines represent memristors                                       | 61 |

| 6.15 | 15-node reservoir 5. The red node represents the input node      |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors.                            | 62 |

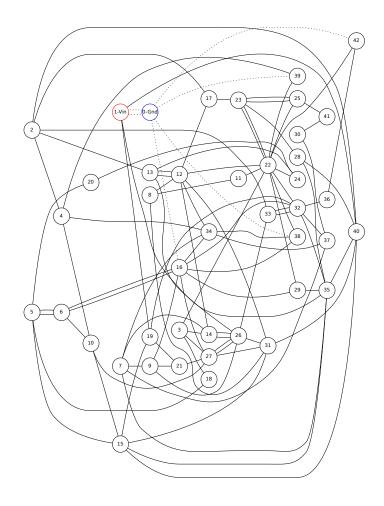

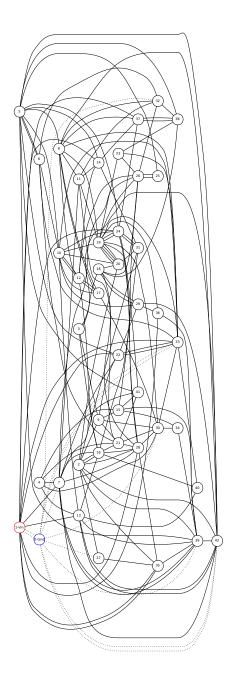

| 6.16 | 30-node reservoir 1. The red node represents the input node      |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors.                            | 63 |

| 6.17 | 30-node reservoir 2. The red node represents the input node      |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors.                            | 64 |

| 6.18 | 30-node reservoir 3. The red node represents the input node      |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted     |    |

|      | and solid lines represent memristors.                            | 65 |

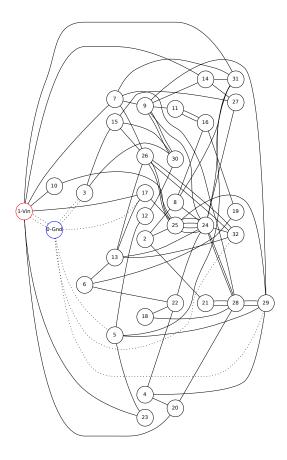

| 6.19 | <b>30-node reservoir 4</b> . The red node represents the input node |    |

|------|---------------------------------------------------------------------|----|

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors.                               | 66 |

| 6.20 | <b>30-node reservoir 5</b> . The red node represents the input node |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors.                               | 67 |

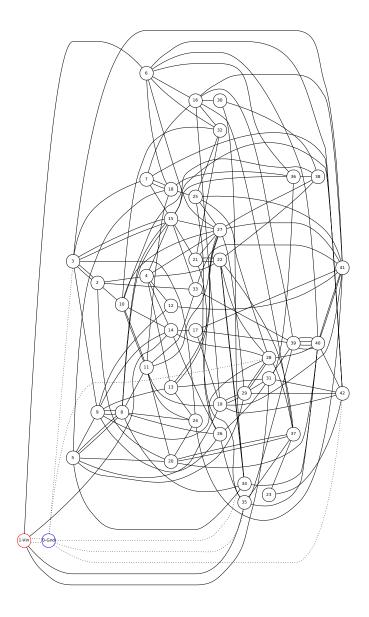

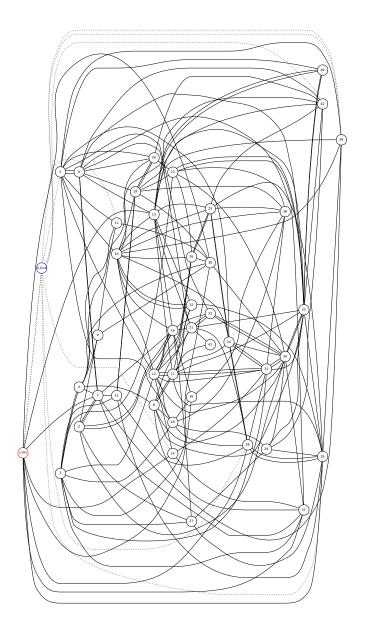

| 6.21 | 40-node reservoir 1. The red node represents the input node         |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors.                               | 68 |

| 6.22 | 40-node reservoir 2. The red node represents the input node         |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors                                | 69 |

| 6.23 | 40-node reservoir 3. The red node represents the input node         |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors                                | 70 |

| 6.24 | 40-node reservoir 4. The red node represents the input node         |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors                                | 71 |

| 6.25 | 40-node reservoir 5. The red node represents the input node         |    |

|      | (VIN) and the blue node is the ground node (GND). The dotted        |    |

|      | and solid lines represent memristors                                | 72 |

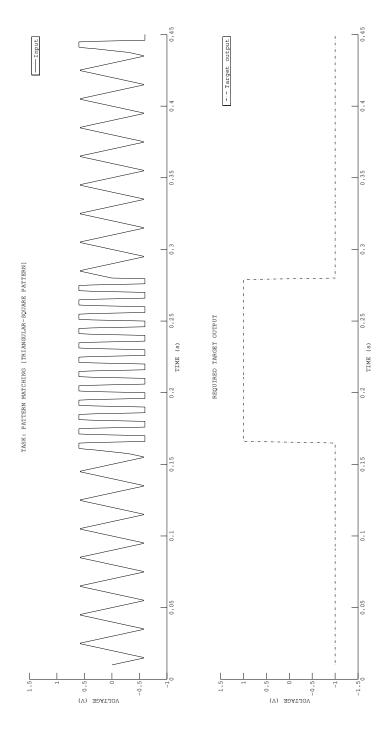

| 7.1  | (Top) Input triangular-square wave signal; (Bottom) desired target  |    |

|      | response                                                            | 77 |

|      |                                                                     |    |

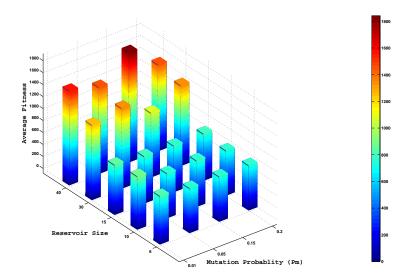

| 7.2 | Fitness averaged over 5 simulations for the task shown in Figure 7.1.         |    |

|-----|-------------------------------------------------------------------------------|----|

|     | The $y$ -axis shows the reservoir size $N$ , the $x$ -axis shows the mutation |    |

|     | rate, and the $z$ -axis shows the average fitness. Fitness plotted for        |    |

|     | population size of 50. The minimum fitness values are observed for            |    |

|     | the mutation rate of 0.05 across all reservoirs and the reservoirs of         |    |

|     | sizes 6, 10 and 15 showed minimum fitness                                     | 78 |

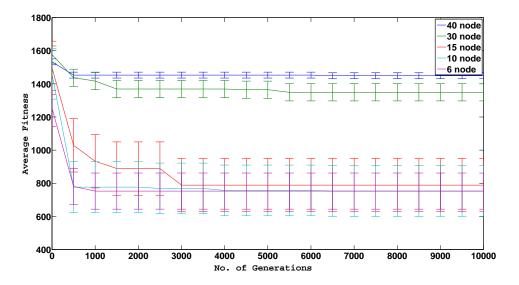

| 7.3 | Best average fitness for population size 50, mutation rate 0.05 and           |    |

|     | reinsertion rate 0.8. Small size reservoirs with 6, 10 and 15 nodes,          |    |

|     | converge at a faster rate towards a minimum fitness value. The 30-            |    |

|     | node and 40-node reservoirs take more generation, i.e., simulation            |    |

|     | time to converge                                                              | 78 |

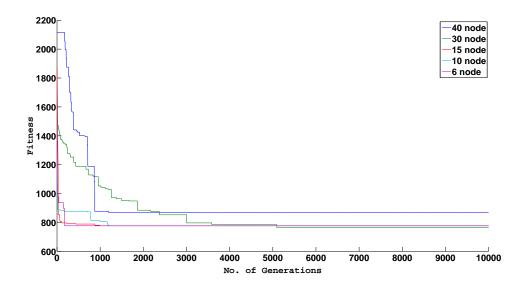

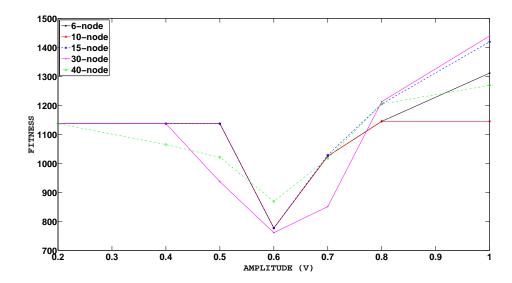

| 7.4 | Fitness as a function of reservoir size. Higher node reservoirs require       |    |

|     | more generations to converge towards minimum fitness                          | 81 |

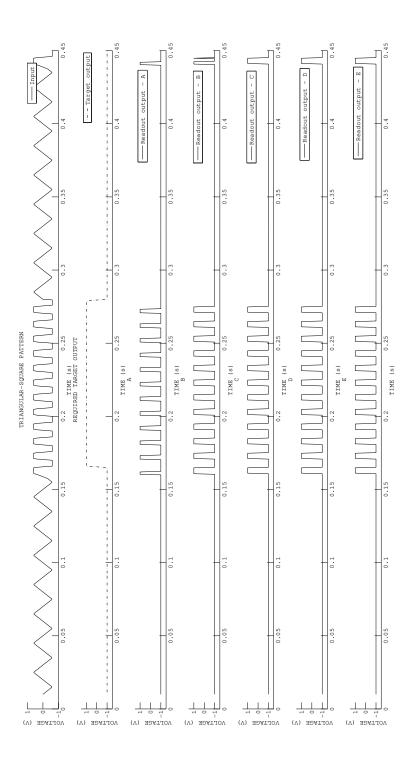

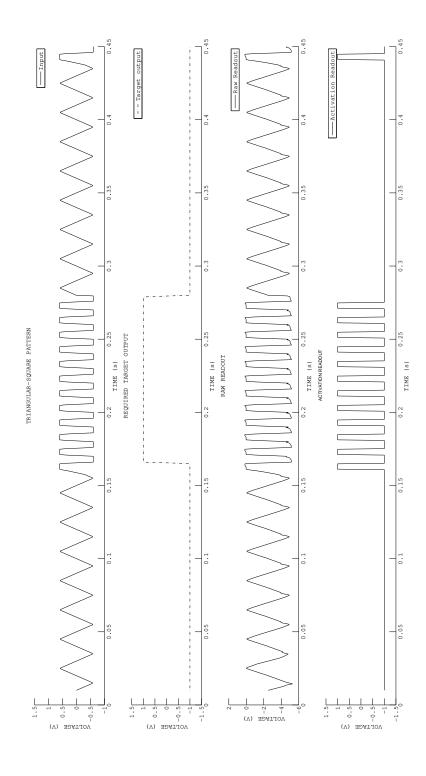

| 7.5 | Simulation response for the reservoirs listed in Table 7.2. Describ-          |    |

|     | ing the plot from (top to bottom). $(first)$ Input to the reservoir;          |    |

|     | (second) the desired output response. Next, the readout responses             |    |

|     | for 40-node, 30-node, 15-node, 10-node and 6-node reservoirs are              |    |

|     | shown from $A$ to $E$ respectively. For the triangular input, the read-       |    |

|     | out response for all the reservoirs converge to logic $-1$ and for the        |    |

|     | square input the response is seen as pulses of logic 1. For the 40-           |    |

|     | node readout response as shown in $A$ , it can be observed that the           |    |

|     | response for the square input has a smaller pulse width as compared           |    |

|     | to rest of the reservoir responses. This is reflected as a higher mean        |    |

|     | squared error value of 868.79. Clearly, all the reservoirs are able to        |    |

|     | distinguish between the square and the triangular input                       | 83 |

| 7.6 | A representation of the readout $Out$ , which maps the 15-node reser-                            |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | voir states $\mathbf{x}(\mathbf{t})$ for nodes $1, 9, 11, 13, 16$ and $15$ with weights $w$ rep- |    |

|     | resented for each node. A single bias of (-2.5) is used towards the                              |    |

|     | final output $Y$ . $sign$ activation is used in this example. The raw                            |    |

|     | readout response $Out$ and the final readout response $Y$ is shown in                            |    |

|     | Figure 7.7                                                                                       | 84 |

| 7.7 | Readout $Out$ response for the 15 node reservoir as shown in Figure                              |    |

|     | 7.6. Describing the plot from (top to bottom). (first) Input to the                              |    |

|     | reservoir; $(second)$ The desired output response; $(third)$ The raw                             |    |

|     | readout response (before the activation function). We observed that                              |    |

|     | for the triangular input the reservoir response converged towards a                              |    |

|     | negative voltage and for the square signal the reservoir response                                |    |

|     | shows positive spikes; $(fourth)$ The final readout response after the                           |    |

|     | sign activation function. The raw readout response is transformed                                |    |

|     | by the $sign$ function, whose response is $-1$ for a negative signal and                         |    |

|     | +1 for a positive signal. Thus, for the triangular wave we observe a                             |    |

|     | -1 logic and $+1$ logic spikes for the square input                                              | 85 |

| 7.8 | Fitness plot for triangular-square input pattern as a function of                                |    |

|     | amplitude variation. The reservoir was trained for $0.6V$ amplitude.                             | 87 |

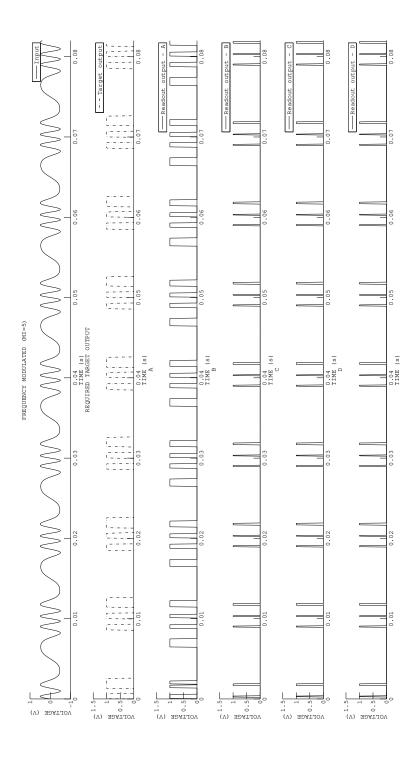

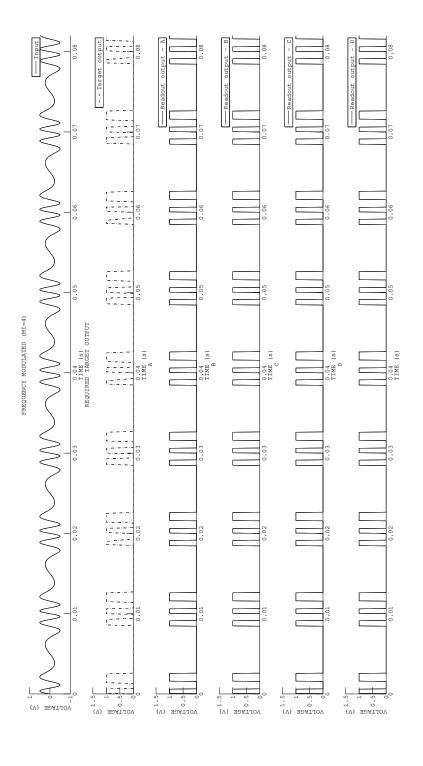

| 7.9  | Simulation response for $MI = 5$ . Describing the plot from (top to      |    |

|------|--------------------------------------------------------------------------|----|

|      | bottom). $(first)$ Input to the reservoir; $(second)$ the desired output |    |

|      | response. Next, the readout responses for 30-node, 15-node, 10-node      |    |

|      | and 6-node reservoirs are shown from $A$ to $D$ respectively. For the    |    |

|      | high frequency input, the readout response for all the reservoirs        |    |

|      | converge to logic 1 and for the slow frequency input the response        |    |

|      | is logic 0 for all the reservoirs except for the 30-node. The logic      |    |

|      | 1 going pulses for 6-node, 10-node and 15-nodes are narrow pulses.       |    |

|      | Clearly, except for the 30-node reservoir, all other reservoirs are able |    |

|      | to distinguish between the two signals                                   | 91 |

| 7.10 | Simulation response for $MI = 4$ . Describing the plot from (top to      |    |

|      | bottom). $(first)$ Input to the reservoir; $(second)$ the desired output |    |

|      | response. Next, the readout responses for 30-node, 15-node, 10-node      |    |

|      | and 6-node reservoirs are shown from $A$ to $D$ respectively. For the    |    |

|      | high frequency input, the readout response for all the reservoirs        |    |

|      | converge to logic 1 and for the slow frequency input the response is     |    |

|      | logic 0. All the reservoirs are able to distinguish between the two      |    |

|      | signals                                                                  | 92 |

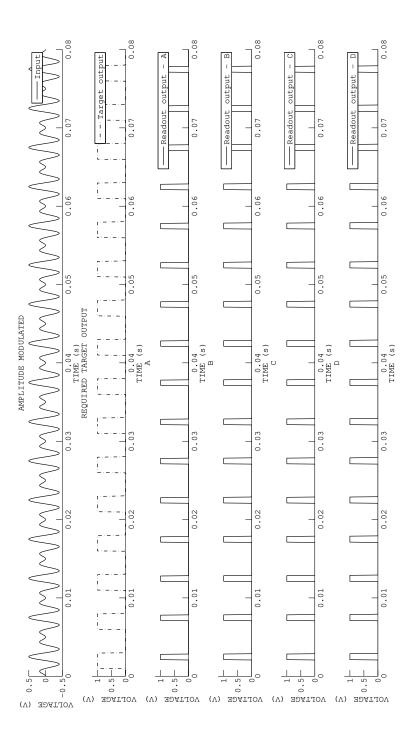

| 7.11 | Simulation response for the amplitude modulated experiment. De-              |    |

|------|------------------------------------------------------------------------------|----|

|      | scribing the plot from (top to bottom). $(top)$ Input to the reservoir;      |    |

|      | (second) The desired output response. Next, the readout responses            |    |

|      | for 30-node, 15-node, 10-node and 6-node reservoirs are shown from           |    |

|      | A to $D$ respectively. For the high amplitude signal, the readout            |    |

|      | response should converge to logic 1 and for the low amplitude signal         |    |

|      | input the response is seen as pulses of logic 0. The readout uses the        |    |

|      | step function, whose response is 0 for a negative signal and +1 for          |    |

|      | a positive signal. Clearly, all the reservoirs are able to distinguish       |    |

|      | between the high and low amplitude for the input                             | 95 |

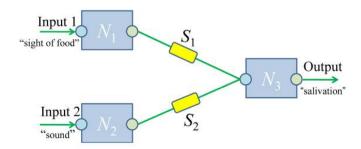

| 7.12 | Simple neural network. Here, $N_1$ , $N_2$ , and $N_3$ represent neurons and |    |

|      | $S_1$ and $S_2$ represent synapse. (Source: [7])                             | 96 |

| 7.13 | Output response from the electrical circuit emulating associative            |    |

|      | memory using a neural network [7]. Input1 represents (sight of               |    |

|      | food), $Input 2$ represents (sound) and the probing phase of the out-        |    |

|      | put represents salivation which indicated the learning behavior when         |    |

|      | the only input present is the sound. (Source: [7])                           | 96 |

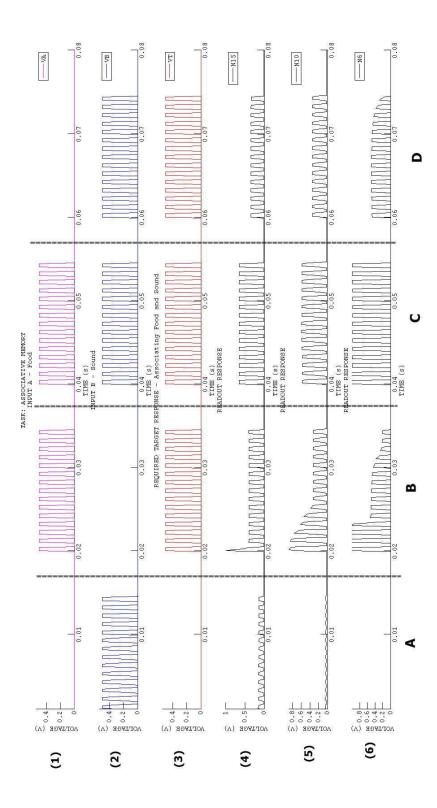

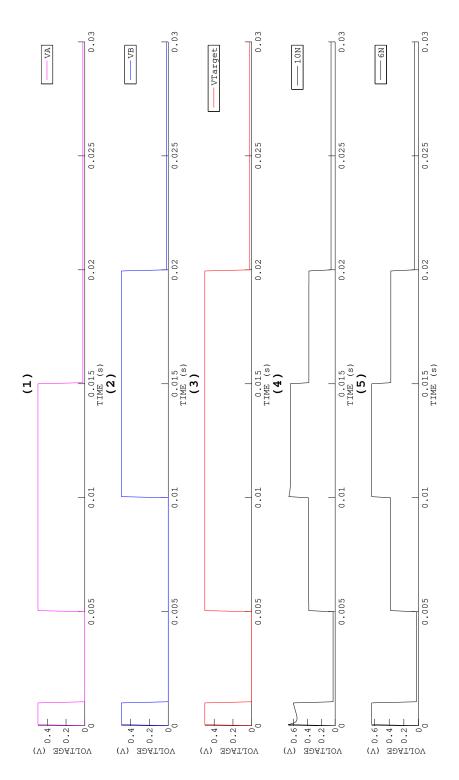

| 7.14 | Describing the plots from top to the bottom. (1) shows the first            |

|------|-----------------------------------------------------------------------------|

|      | input signal $V_A$ representing the $food$ signal; (2) shows the second     |

|      | input signal $V_B$ representing the $sound$ ; (3) is the required target    |

|      | response. The response for the associative memory is marked with            |

|      | 4 phases from $A - D$ . In <i>PhaseA</i> , when only input $V_B$ presented, |

|      | the output should not show any response. In $phaseB$ , when only            |

|      | input $V_A$ is presented, the output should show a strong response. In      |

|      | $PhaseC$ , which is the training phase when both inputs $V_A$ and $V_B$     |

|      | are presented, the output should respond. In $phaseD$ , when only           |

|      | input $V_B$ is presented, the output should show response, indicating       |

|      | the system has learned to respond in absence of the main input $V_A$ .      |

|      | (4-6) is the readout response obtained for the 15-node, 10-node             |

|      | and 6-node reservoirs respectively. We observe that all the resvoirs        |

|      | respond to the required target response, except for some noise in           |

|      | Phase A which is within an acceptable range                                 |

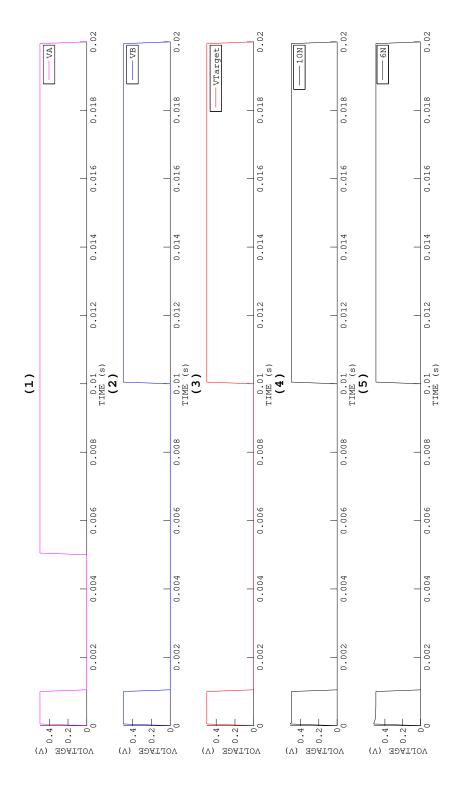

| 7.15 | Simulation response for logical OR operation. Here, $(1)$ and $(2)$ are     |

|      | inputs A and B respectively with amplitude of 0.5V. The desired             |

|      | output response is shown in (3) and the readout output response             |

|      | for 10-node and 6-node is shown in (4) and (5) respectively $103$           |

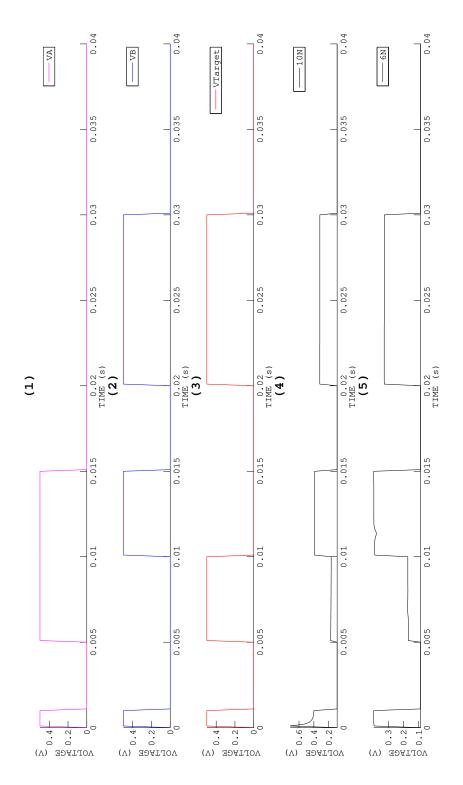

| 7.16 | Simulation response for logical AND operation. Here, $(1)$ and $(2)$        |

|      | are inputs A and B respectively with amplitude of 0.5V. The desired         |

|      | output response is shown in (3) and the readout output response for         |

|      | 10-node and 6-node is shown in (4) and (5) respectively 104                 |

7.17 Simulation response for logical XOR operation. Here, (1) and (2) are inputs A and B respectively with amplitude of 0.5V. The desired output response is shown in (3) and the readout output response for 10-node and 6-node is shown in (4) and (5) respectively. . . . . . . . 105

### Overview

### 1.1 Introduction and Motivation

Ongoing technology scaling not only results in increased silicon and system complexity but also in nanoscale devices with interesting new properties. The current *International Technology Roadmap for Semiconductors* (ITRS) [8], highlights advancements in non-silicon nanoelectronic devices, which include carbon nanotube field-effect transistors (FETs), graphine nanoribbion FETs, nanowires and molecular electronics. In the area of memory devices, the research is focused on Ferroelectric FET memories (capacitance based), spin torque, nanomechanical and nanoionic, and redox reaction based memories (resistance based) [8].

The fabrication and circuit design of these nanoscale devices is a challenge as it is increasingly difficult to control their exact orientation and assembly. Designing complex circuit topologies using these nanodevices or materials requires a major shift from conventional design techniques and fabrication methods to new techniques. The semiconductor industry is considering exploring alternative ways of computing, for example by implementing stochastic computing techniques [8] and using self-assembly processes instead of top-down lithography [9]. A hybrid architecture approach that uses conventional silicon with non-conventional nanoscale storage devices, and application-based reconfigurable nanoelectronic circuits is discussed in [10, 11]. An adaptive programming technique of randomly assembled computer (RAC) built from diodes as a computational element is explored in [12].

Liquid State Machines (LSMs) and Echo State Network (ESN) are biologically-inspired computation architectures, which are explored in [13, 14].

Applications for nanoscale devices range from signal processing, low power reconfigurable logic to non-volatile logic [8]. Another application consists in implementing dense circuit architectures that can mimic a certain brain functionality. This particular application is possible due to a novel nanodevice, which is functionally equivalent to a 'synapse' [15].

# 1.2 Challenges

Although complementary metal-oxide-semiconductor (CMOS) technology has well-established design and fabrication techniques, it is also facing challenges with device reliability, lifetime and an ongoing increase in non-recurring engineering (NRE) fabrication cost as a result of technology scaling [8,10]. Nanoelectronic, as an emerging technology naturally comes with a set of challenges due to the lack of well-established design and fabrication methodologies. The challenges can be summarized as follows:

- At nanoscale, it is less likely that every device fabricated will have the exact predefined tolerance and precision. Hence, one of the challenges lies in developing low-cost and tolerance-driven fabrication techniques, which can be applied to a wide range of nanoscale devices.

- 2. Designing circuit topologies and architectures to tolerate high variation due to device fabrication techniques [10].

- 3. Defining new computing techniques that will help to harness the novel device characteristics.

- 4. Defining accurate device characteristic models which allow multi-level simulation and abstraction [8].

- 5. Integration complexity in nanoelectronic results due to hierarchical and hybrid architecture approach. Thus, defining a suitable interconnect technology compatible across platforms is a challenge [8].

- 6. Keeping power consumption to a minimum and employing effective heat dissipation techniques.

## 1.3 Research Questions

Based on the challenges outlined in Section 1.2, we formulated the following research questions:

- 1. Using self-assembly as one of the nanoscale fabrication techniques, researchers have demonstrated the fabrication of two terminal nanodevices [10]. These individual self-assembled devices can be assembled to form a random network topology. If we are given such a random self-assembled network of two terminal nanodevices, how can we extract meaningful computation from such a network?

- 2. Which computational architecture should be implemented to explore the computational capability of emerging nanodevices?

- 3. Which application areas can benefit from a random network of nanodevices?

### 1.4 Our Approach in a Nutshell

To design optimal circuits, well-established evolutionary computing techniques have been used in areas ranging from analog filter circuit design [6] to evolving memristor-based circuits [16]. In recent years, a novel computing technique called Reservoir Computing (RC) [14] has been explored for real time computation with dynamical systems. This approach uses randomly generated networks as the compute core. The uniqueness of this approach is that the compute core, i.e., the network, does not have to be trained for specific tasks. Rather, the network dynamics are interpreted by a simple output layer. This approach allows performing computations with circuits that do not require a well-defined topology and also enables spatial computing [13, 14].

My contributions in this thesis are as following:

- 1. We proposed that memristors can be used as a dynamical element in reservoir computing (RC).

- 2. We experimentally showed that a memristor-based reservoir can be used to perform non-trivial tasks, such as pattern recognition.

- 3. We developed *RCspice*, a Matlab-based framework to implement memristor based reservoir computing (see Chapter 3 and 4 for details).

- 4. We use Ngspice [17] simulator to simulate memristor-based reservoirs.

- 5. We optimized the reservoir performance by exploring reservoir parameters (see Chapter 7.1 for details).

- 6. We performed experiments to evaluate the proposed memristor-based reservoir with different network sizes (see Chapter 7.1 for details).

- 7. We performed various pattern recognition experiments with different inputs signals, such as triangular-square, frequency modulated, and amplitude modulated signals. Our experiments showed that the memristor reservoir is able to distinguish between signal variation in the input (see Section 7.2, 7.4 and 7.5 for details).

- 8. We performed an associative memory experiment that demonstrated learning behavior related to specific input events (see Section 7.6 for details).

- 9. We published a paper titled "Evolving nanoscale associative memories with memristors" at the IEEE NANO 2011 conference [16].

## 1.5 Thesis Organization

In this thesis we implement RC architecture for exploring the computation abilities of random memristor networks. The thesis organization is as follows:

We start with the introduction, Chapter 2.2 gives background information on the reservoir computing (RC) by establishing its links to Artificial Neural Networks (ANNs). The literature review under Section 2.3 gives a brief introduction to the RC architecture. Section 2.4 gives an overview of our choice of a novel nanoscale device, the memristor, and states its properties that makes it an ideal candidate for RC.

Chapter 3 describes our Matlab-based Reservoir Computing Simulation Program with Integrated Circuit Emphasis (RCspice) simulation framework. The framework's sub-modules are described in the Chapter 4. In the Chapter 5 we describe the reservoir evaluation using Ngspice and the genetic algorithms.

Chapter 7 explains the experiments. Section 7.1 shows the parameter exploration relating to the memristor reservoir and the genetic algorithms. Sections 7.2, 7.4 and 7.5 explain the experiments conducted for the pattern recognition experiment. Section 7.6 and 7.7 covers the associative memory experiment and the logic computation experiment respectively. The final Chapter 8 concludes the thesis and discusses future work.

# Background

# 2.1 Non-classical Computing Paradigms

### 2.2 Artificial Neural Networks

The field of neurocomputing is inspired from the very idea of our brain's ability to process information. The fundamental computing units of our nervous system are *neurons* and the *synapses* are the channels via which they communicate to other neurons. Our brain is a dynamic computational core, i.e., it is not wired for a specific task but in fact, reusing, rearranging and modifying the given existing brain structure gives rise to varied computational ability [18, 19].

The area of Artificial Neural Networks (ANNs), or simply neural networks, is inspired from our brain's computational ability. ANNs mimic biological neural networks that are capable of performing numerous computational tasks. There exist various mathematical models that approximate the behavior of the basic biological computing unit (i.e., the neuron). In ANN's terminology, each mathematical modeled neuron is called a 'unit' [20]. One of the first artificial neuron model proposed by McCulloch-Pitts is a simple two-state neuron model [21]. More realistic integrate-and-fire models, also called spiking neuron models, are designed to describe and predict biological processes (a more detailed description of these models can be found in [18, 19]).

A single 'unit' can transform an incoming signal into an output signal, but solving computational tasks requires arranging the units in a particular network topology. Neural circuits in our brain are recurrently connected and the information processing is typically of temporal nature (i.e., the outcome due to a particular stimuli is its integration over a time period) [22]. Thus, in ANNs, the units are arranged to form networks, such as the feedforward and recurrent neural networks (RNNs). In the feedforward network, the flow of information takes place only in one direction (i.e., connections are directed only from the input to the output). In RNNs, the network topology forms feedback connections. An important characteristic of RNNs is that due to the feedback associated with the network topology, they develop internal temporal dynamics (i.e., memory).

ANNs can solve tasks ranging from basic logical operations, such as AND, OR and XOR to more complex tasks, such as associative computation, pattern recognition and content addressable memory [18, 19, 21].

# 2.3 Reservoir Computing

Recently, two new computing paradigms were introduced: Liquid State Machines (LSMs) [23] by Wolfgang Maass and the Echo State Network (ESN) [14] by Herbert Jaeger. Both models represent a new class of computing models inspired by RNNs. The overarching term for these paradigms is Reservoir Computing (RC) [14,23,24].

The major difference between these two architectures is the mathematical modeling of the basic computing 'unit' (i.e., neuron). In LSMs, the 'unit' is modeled as a *spiking integrate-and-fire* neuron while the ESN architecture implements 'unit' as sigmoid (i.e., as *tanh* transfer function). The spiking neuron model closely resembles the spiking nature of biological neurons and thus retains the essential neuron-behavior. Hence, LSM applications are mainly focused to provide

a biologically-plausible architecture for generic cortical microcircuits computations [24, 25]. While tanh being a non-linear function, ESN finds applications in a number of engineering tasks [14, 24]. Although both these architectures find their applications in different research areas, an important attribute is that the computation is performed on a large non-linear dynamic recurrent network. These dynamical networks need not be strictly RNNs, but any medium which contains dynamical properties can be used for implementing LSMs and ESNs. Section 2.3.3 gives an overview of the various dynamical mediums used as reservoirs. The following Sections (2.3.1 and 2.3.2) will give a brief overview of the LSM and ESN architectures respectively.

# 2.3.1 Liquid State Machines

Liquid State Machines (LSMs) are a novel computational framework recently introduced in [23]. The computing core is a recurrent neural network (RNN). The computing core is referred to as the 'liquid'; the term liquid is a symbolic representation of the RNN's dynamic nature. In the 'liquid', each computing 'unit' is defined as a mathematical model of spiking integrate-and-fire neuron. These neuron models closely resemble functioning of the biological neurons. Thus, the LSM framework is capable of performing real-time computations on time-varying inputs. Its applications are mainly focused in the area of neural microcircuits [13,23]. The LSM's architecture can be divided into three distinct sections namely; (i) the preprocessor unit called as the 'liquid', (ii) the liquid's state space (i.e., memory), and (iii) the processing layer called the 'readout layer'.

A diagrammatic representation of the LSM framework is shown in Figure 2.1. The striking feature of the LSM's architecture is that the 'liquid' itself does not have to be trained for particular tasks, but only the readout layer is trained to extract the time-varying information from the liquid. Mass experimentally shows that the readout layer can be trained to perform a temporal pattern recognition task [23].

Figure 2.1: Architecture of a Liquid State Machine. The input u(.)(1), is a time varying input applied to the liquid  $L^M(2)$ . The internal liquid states at time(t) are represented by  $x^M(t)(3)$ . These states are transformed by a readout layer  $f^M(4)$  to produce output y(t)(5) [23].

### 2.3.2 Echo State Network

Echo State Network (ESN) is a recently introduced architecture based on recurrent neural networks (RNN) [14]. The ESN is architecturally similar to LSM and can similarly be divided into three distinct sections; (i) the pre-processor unit called the 'reservoir', (ii) the internal state space (i.e., memory) of the reservoir and, (iii) the output layer or the 'readout' layer. Each computing 'unit' in the 'reservoir' is defined as mathematical model of tanh function. Similar to LSMs, the readout

layer is trained for a given task. The architecture of the *Echo State Network* is similar to LSM as represented in Figure 2.1.

## 2.3.3 Types of Reservoirs

After a brief introduction to the LSM and the ESN architectures (see Section 2.3.1 and 2.3.2 for details), two questions that remain to be answered are:

- 1. What makes a good dynamical reservoir?

- 2. What tasks can be solved by a *liquid* or *reservoir*?

This section answers the above questions by summarizing recently published articles that use unique dynamical reservoirs or liquids (i.e., compute cores) for implementing LSMs or ESNs. Fernando et al. in [2] literally used water as a 'liquid'. Water as dynamical medium is a natural agent, which incorporates information over time without the use of any mathematical model required to store information over time. Figure 2.2 shows water as a unique pre-processor. Here, the water is placed in a glass tank, which is simulated using an electric motor. This motor action causes ripples in the water, which are read using the optical setup and are transformed by the output layer to solve tasks, such as XOR and the speech recognition [2]. In contrast to water as a liquid, one of the recent publication [26] implements a hard-liquid, i.e., a general purpose mixed-mode artificial neural network as a Application Specific Integrated Circuit (ASIC) is configured as a liquid. In [27], Jones et al. implement a LSM using a model of the Gene Regulation Network (GRN) of Escherichia Coli as a 'liquid'. Photonic reservoir computing is implemented by configuring a network of coupled Semiconductor Optical Amplifiers (SOA) as a 'reservoir' in [28]. One recently published article [29] implements optoelectronic reservoir computing.

Figure 2.2: In [2], Fernando *et al.* used water as a pre-processor ('liquid') for LSM implementation. (Source: [3])

From the recent flurry of publications in the area of reservoir computing, the platforms that can be used as *reservoir* or *liquid* range from ANN, optoelectronic, optics, real water to VLSI [2,14,26–30]. Reservoir computing is capable of solving non-trivial tasks like speech recognition and robot control [30].

As seen from the above applications, reservoir computing is a powerful computational tool for performing complex real time computations on continuous input streams. Their performance measure is based on two properties, separation and approximation. If LSM or ESN, have different internal states for two different input sequences then the liquid or the reservoir is said to have the *separation property*. The distance between different states is generally measured using eucidian distance [23] or using hamming distance [20]. This property determines how well can a liquid classify between inputs with different input history. An *approximation property* is the measure of the readout capability to produce a desired output from the given liquid states [14, 23].

#### 2.4 Memristor

This section presents a brief overview of the nanoscale memristor device, which we use as a building block in this thesis. *Memristor*, short for memory resistor [31], is a passive two-terminal circuit element which was theoretically postulated in 1971 by Professor Leon Chua. He also demonstrated memristive behavior using active circuits in his seminal paper on memristors [31].