# Sussex Research Online

# Metal oxide semiconductor thin-film transistors for flexible electronics

Article (Published Version)

Petti, Luisa, Münzenrieder, Niko, Vogt, Christian, Faber, Hendrik, Büthe, Lars, Cantarella, Giuseppe, Bottacchi, Francesca, Anthopoulos, Thomas D. and Tröster, Gerhard (2016) Metal oxide semiconductor thin-film transistors for flexible electronics. Applied Physics Reviews, 3 (2). 021303. ISSN 1931-9401

This version is available from Sussex Research Online: http://sro.sussex.ac.uk/id/eprint/61869/

This document is made available in accordance with publisher policies and may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the URL above for details on accessing the published version.

# **Copyright and reuse:**

Sussex Research Online is a digital repository of the research output of the University.

Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners. To the extent reasonable and practicable, the material made available in SRO has been checked for eligibility before being made available.

Copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational, or not-for-profit purposes without prior permission or charge, provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

# Metal oxide semiconductor thin-film transistors for flexible electronics

Luisa Petti, Niko Münzenrieder, Christian Vogt, Hendrik Faber, Lars Büthe, Giuseppe Cantarella, Francesca Bottacchi, Thomas D. Anthopoulos, and Gerhard Tröster

Citation: Applied Physics Reviews 3, 021303 (2016); doi: 10.1063/1.4953034

View online: http://dx.doi.org/10.1063/1.4953034

View Table of Contents: http://scitation.aip.org/content/aip/journal/apr2/3/2?ver=pdfcov

Published by the AIP Publishing

#### Articles you may be interested in

Selective wet-etch processing of optically transparent flexible InGaZnO thin-film transistors Appl. Phys. Lett. **107**, 193502 (2015); 10.1063/1.4934869

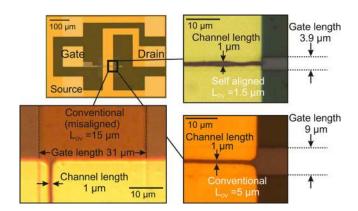

Contact resistance and overlapping capacitance in flexible sub-micron long oxide thin-film transistors for above 100 MHz operation

Appl. Phys. Lett. 105, 263504 (2014); 10.1063/1.4905015

Effect of In-Ga-Zn-O active layer channel composition on process temperature for flexible oxide thin-film transistors

J. Vac. Sci. Technol. B 30, 041208 (2012); 10.1116/1.4731257

Scaling down of amorphous indium gallium zinc oxide thin film transistors on the polyethersulfone substrate employing the protection layer of parylene-C for the large-scale integration

Appl. Phys. Lett. 96, 243504 (2010); 10.1063/1.3454775

A model of electrical conduction across the grain boundaries in polycrystalline-silicon thin film transistors and metal oxide semiconductor field effect transistors

J. Appl. Phys. **106**, 024504 (2009); 10.1063/1.3173179

# APPLIED PHYSICS REVIEWS

# Metal oxide semiconductor thin-film transistors for flexible electronics

Luisa Petti,<sup>1</sup> Niko Münzenrieder,<sup>1,2</sup> Christian Vogt,<sup>1</sup> Hendrik Faber,<sup>3</sup> Lars Büthe,<sup>1</sup> Giuseppe Cantarella,<sup>1</sup> Francesca Bottacchi,<sup>3</sup> Thomas D. Anthopoulos,<sup>3</sup> and Gerhard Tröster<sup>1</sup>

<sup>1</sup>Electronics Laboratory, Swiss Federal Institute of Technology, Zürich, Switzerland

(Received 7 April 2016; accepted 15 April 2016; published online 9 June 2016)

The field of flexible electronics has rapidly expanded over the last decades, pioneering novel applications, such as wearable and textile integrated devices, seamless and embedded patch-like systems, soft electronic skins, as well as imperceptible and transient implants. The possibility to revolutionize our daily life with such disruptive appliances has fueled the quest for electronic devices which yield good electrical and mechanical performance and are at the same time light-weight, transparent, conformable, stretchable, and even biodegradable. Flexible metal oxide semiconductor thin-film transistors (TFTs) can fulfill all these requirements and are therefore considered the most promising technology for tomorrow's electronics. This review reflects the establishment of flexible metal oxide semiconductor TFTs, from the development of single devices, large-area circuits, up to entirely integrated systems. First, an introduction on metal oxide semiconductor TFTs is given, where the history of the field is revisited, the TFT configurations and operating principles are presented, and the main issues and technological challenges faced in the area are analyzed. Then, the recent advances achieved for flexible n-type metal oxide semiconductor TFTs manufactured by physical vapor deposition methods and solution-processing techniques are summarized. In particular, the ability of flexible metal oxide semiconductor TFTs to combine low temperature fabrication, high carrier mobility, large frequency operation, extreme mechanical bendability, together with transparency, conformability, stretchability, and water dissolubility is shown. Afterward, a detailed analysis of the most promising metal oxide semiconducting materials developed to realize the state-of-the-art flexible p-type TFTs is given. Next, the recent progresses obtained for flexible metal oxide semiconductor-based electronic circuits, realized with both unipolar and complementary technology, are reported. In particular, the realization of large-area digital circuitry like flexible near field communication tags and analog integrated circuits such as bendable operational amplifiers is presented. The last topic of this review is devoted for emerging flexible electronic systems, from foldable displays, power transmission elements to integrated systems for large-area sensing and data storage and transmission. Finally, the conclusions are drawn and an outlook over the field with a prediction for the future is provided. Published by AIP Publishing. [http://dx.doi.org/10.1063/1.4953034]

# **TABLE OF CONTENTS**

| I. INTRODUCTION                            | 2  | IV. METAL OXIDE SEMICONDUCTOR-BASED    |    |

|--------------------------------------------|----|----------------------------------------|----|

| A. Historical perspective                  | 2  | CIRCUITS                               | 36 |

| B. TFT configuration and operation         | 3  | A. Circuit configuration and operation | 36 |

| C. Present issues and challenges           | 6  | B. Flexible unipolar circuits          | 38 |

| II. N-TYPE METAL OXIDE SEMICONDUCTOR       |    | C. Flexible complementary circuits     | 41 |

| TFTS                                       | 7  | V. METAL OXIDE SEMICONDUCTOR-BASED     |    |

| A. N-type metal oxide semiconductors       | 7  | SYSTEMS                                | 43 |

| B. Flexible n-type vacuum-processed TFTs   | 8  | A. Optical display systems             | 43 |

| C. Flexible n-type solution-processed TFTs | 25 | B. Sensoric systems                    | 44 |

| III. P-TYPE OXIDE SEMICONDUCTOR TFTS       | 32 | C. Power transmission systems          | 45 |

| A. P-type metal oxide semiconductors       | 32 | D. Data transmission systems           | 46 |

| B. Flexible p-type vacuum-processed TFTs   | 33 | E. Data storage systems                | 46 |

| C. Flexible p-type solution-processed TFTs | 34 | VI. CONCLUSIONS                        | 46 |

<sup>&</sup>lt;sup>2</sup>Sensor Technology Research Centre, University of Sussex, Falmer, United Kingdom

$<sup>^3</sup>$ Department of Physics and Centre for Plastic Electronics, Imperial College London, London, United Kingdom

#### I. INTRODUCTION

Electronics today is facing a disruptive evolution, advancing from heavy, bulky, and rigid devices to light-weight, soft, and flexible appliances. Emerging new applications like smart labels<sup>1</sup> and intelligent packaging,<sup>2</sup> wearable<sup>1-4</sup> and textile integrated systems,<sup>5–7</sup> seamless and embedded patch-like electronics,<sup>8,9</sup> epidermal devices,<sup>10–16</sup> artificial skins for robots,<sup>17–19</sup> imperceptible<sup>20–22</sup> biomimetic<sup>23</sup> and transient<sup>24–26</sup> medical implants, as well as advanced surgical tools 13,15,27,28 promise to revolutionize our daily life. To enable all these applications, electronic devices have to become flexible, lightweight, transparent, conformable, stretchable, and even biocompatible and biodegradable. Flexible thin-film transistors (TFTs) are able to fulfill all these requirements and are thus becoming increasingly important to realize next-generation electronic device platforms. Among the state-of-the-art flexible TFT technologies, metal oxide semiconductors are especially suitable, owing to their high optical transparency,<sup>29</sup> good electrical performance [electron carrier mobility of  $\geq 10 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$  even if processed at room temperature (RT)],<sup>29</sup> as well as excellent mechanical properties (large bendability down to 25 µm radii and good insensitivity to strain). 23,30 Table I provides a summary and a comparison of the most important device properties for the established flexible TFT technologies: amorphous silicon (a-Si), 31,32 organic semiconductors, <sup>14,33</sup> low temperature poly-crystalline silicon (LTPS), 34,35 and metal oxide semiconductors. As evident from Table I, metal oxide semiconducting technology presents several advantages typical of a-Si and organic materials, such as low cost, low process complexity and temperature, and large-area scalability, but at the same time yields a larger carrier mobility.<sup>36</sup> Compared with LTPS, metal oxide semiconductors present slightly lower carrier mobility, but also larger scalability, smaller manufacturing cost, as well as process complexity and temperature.<sup>36</sup> Furthermore, metal oxide semiconductor TFTs show a larger resistance to mechanical strain if compared with LTPS devices. 30 This is why metal oxide semiconductors are considered the most prominent candidate for next-generation flexible high-resolution active matrix organic light emitting diode (AMOLED) display backplanes, <sup>38–41</sup> as well as the most suitable technology to fuel the realization of tomorrow's ubiquitous electronics. Main aim of this review is to report the recent advances obtained in the field of flexible metal oxide semiconductor TFTs: from single devices (Sections II and III), large-area circuits (Section IV) up to entirely integrated systems (Section V). Before reviewing the state-of-the-art of flexible metal oxide semiconductor

technology in the Sections II–V, in this section an introduction on the topic is given. First, in Sec. IA, a historical overview on TFTs based on metal oxide semiconductors is presented. Subsequently, in Sec. IB, the operating principle of TFTs together with the available device configurations are reported. Finally, in Sec. IC, the main issues and technological challenges faced in the field are analyzed.

#### A. Historical perspective

TFTs find their origin back in the 1930 when the fieldeffect transistor (FET) was proposed and patented by Lilienfeld. 42-44 In these reports, Lilienfeld described the concept of a device in which the current flow is controlled by the application of a transversal electric field. Even if TFTs and FETs share the same operating principle, the first TFT was realized only in 1962 by Weimer at RCA laboratory. 45 In his work, Weimer used a vacuum technique (evaporation) and high-precision shadow masking to deposit and structure a gold (Au) source/drain (S/D) electrodes, a microcrystalline cadmium sulfide (CdS) n-type (electron conducting) semiconductor, a silicon monoxide gate dielectric, and an Au gate contact on an insulating glass substrate (Fig. 1). Interestingly, Weimer already showed a preliminary evaluation of thin-film circuits, such as flip-flops, AND, and NOR gates. His proceeding of IRE "The TFT - a new Thin-Film Transistor" draws worldwide attention, 45 opening the way to a new field of study. Few years later in 1964, the first TFT with a metal oxide semiconductor was demonstrated by Klasens and Koelmans. 46 The device was manufactured by photolithographic techniques and comprised aluminum (Al) electrodes, anodized aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) gate dielectric, evaporated n-type tin oxide (SnO<sub>2</sub>) semiconductor, and source/drain contacts on a glass substrate. For the first time, the transparency of substrate, semiconductor, and gate dielectric allowed realizing a self-aligned (SA) lithographic lift-off process, where the source/drain contacts were defined by exposing the photoresist to ultraviolet (UV) light penetrating from the back of the substrate. In this way, the opaque Al gate electrode could act as a shielding layer for the UV light. 46 Subsequently, TFTs with single crystal lithiumdoped zinc oxide (ZnO:Li) hydrotermically grown from solution, 47 as well as SnO<sub>2</sub> deposited from vapor phase reaction, were presented.<sup>48</sup> Nevertheless, none of these two devices outperformed the results shown by Klasens and Koelmans. After a few decades of silence, in 1996 metal oxide semiconductors gained new attention as active layers in ferroelectric memory TFTs. 49,50 The pioneering work of

TABLE I. Comparison between metal oxide semiconductors and other established flexible TFT technologies. 8,35–37

|                                          | Microstructure          | Carrier mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | Manufacturing cost | Process complexity | Process temperature (°C) | Large-area scalability | Device type   |

|------------------------------------------|-------------------------|------------------------------------------------------------------------|--------------------|--------------------|--------------------------|------------------------|---------------|

| Metal oxide semiconductors               | Mainly amorphous        | 10–100                                                                 | Low                | Low                | RT to 350                | High                   | Mainly n-type |

| Amorphous silicon                        | Amorphous               | 1                                                                      | Low                | Low                | 150-300                  | High                   | N-type        |

| Low temperature poly-crystalline silicon | Poly-crystalline        | 50–100                                                                 | High               | High               | 350–500                  | Low                    | N- and p-type |

| Organic semiconductors                   | Mainly poly-crystalline | 0.1–10                                                                 | Low                | Low                | RT to 250                | High                   | Mainly p-type |

FIG. 1. (a) Device cross-section, top view and (b) photograph of the first thin-film transistor (TFT) reported in 1962. Reproduced with permission from P. Weimer, Proc. IRE **50**, 1942 (1962). Copyright 1962 Institute of Electrical and Electronic Engineers.

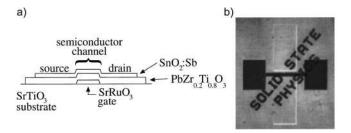

Prins et al. demonstrated the first fully transparent and metal oxide-based TFT with antimony-doped SnO<sub>2</sub> (SnO<sub>2</sub>:Sb) semiconductor grown by pulsed layer deposition (PLD) (Fig. 2). 49 At the same time, Seager et al. showed the first indium oxide (In<sub>2</sub>O<sub>3</sub>) non-volatile memory TFT with ferroelectric gate dielectric.<sup>50</sup> Following the success of these works, from 2003 metal oxide semiconductors gained an increasingly interest. The majority of the attention was initially directed to zinc oxide (ZnO) TFTs,  $^{51-59}$  resulting in an electron mobility above  $1\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$ ,  $^{51,52,54,55,57-59}$  Such values highlighted the suitability of this technology as a replacement for a-Si, commonly employed in TFT display backplanes. In this context, Hoffman, Norris, and Wager reported fully transparent ZnO TFTs yielding a carrier mobility of 2.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and current on/off ratio of 10<sup>7.51</sup> In this case, the ZnO layer was deposited by ion-beam sputtering (IBS) and annealed between 600 and 800 °C. A few months later, Carcia et al. presented TFTs with ZnO radio-frequency (RF) sputtered at room temperature exhibiting similarly good performance.<sup>52</sup> At the same time, also Norris et al. showed the first TFT with spin coated ZnO active layer, yielding a satisfactory carrier mobility of  $0.2 \,\mathrm{cm^2~V^{-1}~s^{-1}}$  Subsequently, Fortunato et al. reported fully transparent TFTs with ZnO RF sputtered at room temperature presenting an electron mobility of  $20\,\mathrm{cm}^2~\mathrm{V}^{-1}~\mathrm{s}^{-1}$ ,58 whereas Carcia, McLean, and Reilly demonstrated how semiconductor engineering during ZnO sputtering can lead to TFTs with a carrier mobility as high as  $42 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1.59}$ Additionally, also TFTs with other binary metal oxide semiconductors like In<sub>2</sub>O<sub>3</sub> and SnO<sub>2</sub> were reported, yielding also good performance. 61,62 Main breakthrough in the field was achieved in 2003 by Nomura et al. who demonstrated a multicomponent indium gallium zinc oxide (IGZO) singlecrystalline active layer epitaxially grown at 1400 °C on an yttria-stabilized zirconium (YSZ) substrate.<sup>63</sup> The resulting TFT presented an electron mobility of  $80 \, \mathrm{cm}^2 \, \mathrm{V}^{-1} \, \mathrm{s}^{-1}$  and a current on/off ratio of 106, demonstrating that highperformance TFTs can be realized with metal oxide semiconductors. Continuing their work, in 2004 Nomura et al. reported transparent TFTs with amorphous IGZO layers grown at room temperature by PLD on flexible polyethylene terephthalate (PET) foils (Fig. 3).<sup>29</sup> The results were impressive (especially considering the low temperature process): an electron mobility

FIG. 2. (a) Device cross-section and (b) photograph of the first fully transparent metal oxide-based TFT reported in 1996. Reproduced with permission from Appl. Phys. Lett. **68**, 3650 (1996). Copyright 1996 AIP Publishing LLC.

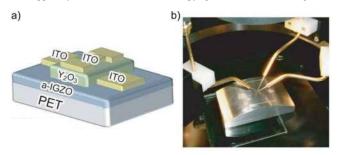

FIG. 3. First flexible TFT with indium gallium zinc oxide (IGZO) active layer reported in 2004: (a) cross-section and (b) photograph of TFT bent to 30 mm tensile radius. Reproduced with permission from Nomura *et al.*, Nature **432**, 488 (2004). Copyright 2004 Nature Publishing Group.

of  $9 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and a current on/off ratio of  $10^3$ . Furthermore, first mechanical bending tests of the devices at 30 mm radius were demonstrated. Nomura's report paved the way to an impressive number of publications on metal oxide semiconductor TFTs. In the following years, several multicomponent metal oxide semiconductors, ranging from zinc tin oxide (ZTO), <sup>64,65</sup> indium zinc oxide (IZO) <sup>66</sup> to IGZO (the most common), 67-69 were investigated. From 2005, also the first reports on hole transporting (p-type) metal oxide semiconductors appeared. First, Chang et al. demonstrated p-type behavior in gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) nanowire (NW) TFTs,<sup>70</sup> followed by other works on p-type tin monoxide (SnO),<sup>71,72</sup> cuprous oxide (Cu<sub>2</sub>O),<sup>73,74</sup> and nickel oxide (NiO)<sup>75</sup> devices all presenting low carrier mobility and high process temperatures. Remarkably, in 2007 Ju et al. showed the first flexible and solution-processed metal oxide semiconductor TFTs based on ZnO and In<sub>2</sub>O<sub>3</sub> NWs. <sup>76</sup> From 2008, tremendous advances were made in the field of flexible devices, from IGZO TFTs on cellulose fiber-based paper,77 stretchable and transparent ZnO TFTs, <sup>78</sup> complementary inverters based on n-type IGZO and ptype SnO TFTs with and on paper, 79 ultraflexible and transparent IGZO TFTs, 80 three-dimensionally (3D) conformable IGZO TFTs and circuits, 81 water soluble IGZO TFTs, 82 to mechanically active biomimetic IGZO TFTs.<sup>23</sup> Nowadays, the state-of-the-art flexible IGZO TFTs yield excellent electrical performance with carrier mobility values up to 84 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (Ref. 83) and current on/off ratio above  $10^{10.84}$  depending on the semiconductor composition and device configuration.

# B. TFT configuration and operation

In this subsection, the most common TFT configurations are presented, followed by a short explanation of the basic TFT operating principle.

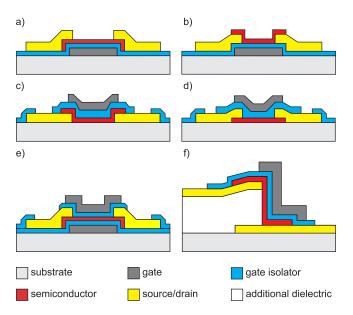

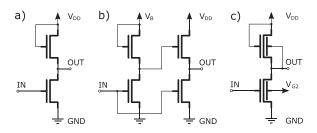

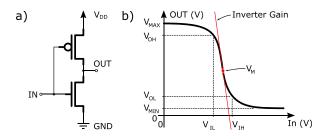

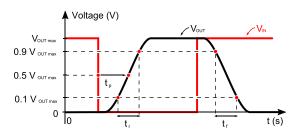

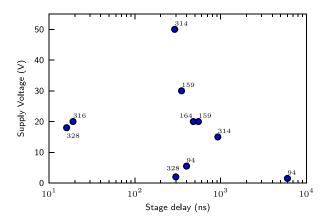

FIG. 4. Most common device configurations: (a) bottom-gate (BG) staggered TFT, (b) BG coplanar TFT, (c) top-gate (TG) staggered TFT, (d) TG coplanar TFT, (e) double-gate (DG) TFT, and (f) vertical TFT (VTFT).

#### 1. TFT configuration

TFTs are three terminal field-effect devices, whose working principle is similar to those of metal oxide semiconductor field-effect transistors (MOSFETs) used in conventional Silicon (Si) electronics.<sup>85</sup> However, in MOSFET technology, the substrate is a single crystal Si wafer (representing also the active layer) and device functionality is added through a large variety of complex, high temperature (>1000 °C) and expensive processes (e.g., diffusion/implantation of dopants, lithography, and etching). 86 On the other hand, TFTs are fabricated typically on insulating substrates (glass and plastic), on which all the device layers are grown at lower temperature (<650 °C) by vacuum- or solution-processing deposition techniques. Given the different manufacturing processes, the active layers of TFTs are typically poly-crystalline or amorphous materials, which are both characterized by a reduced charge carrier transport (if compared with single-crystal Si). 36,87 Like in MOSFETs, TFT functionality is achieved through the following components: a dielectric layer inserted between the semiconductor and a transversal gate contact, together with two source/drain electrodes directly in contact with the semiconductor. Current modulation between source/ drain is achieved through the semiconducting layer by the capacitive injection of carriers close to the dielectric/semiconductor interface (the so-called field-effect).85 Even if both MOSFETs and TFTs rely on the field-effect to modulate the conductance of the active layer, in TFTs this is achieved by an accumulation layer (and not an inversion region like in MOSFETs). TFTs can be fabricated using a wide range of device configurations. Most peculiar planar TFT structures are: bottom-gate (BG) (Figs. 4(a) and 4(b)) and top-gate (TG) (Figs. 4(c) and 4(d)) architectures, depending on whether the gate electrode is deposited before or after the active layer. BG and TG devices can be either staggered or coplanar, depending if the source/drain contacts are on the opposite or on the same side of the semiconductor/dielectric interface. 85 BG structures,

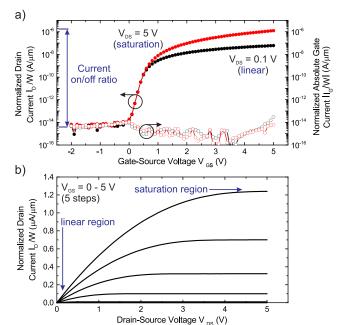

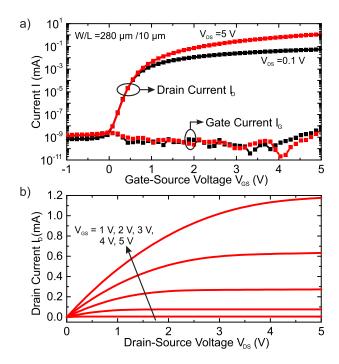

FIG. 5. Typical current-voltage characteristics of an n-type metal oxide semiconductor TFT (channel length  $L=30\,\mu\text{m}$ ): width (W) normalized transfer (a) and output (b) curves.

especially staggered (Fig. 4(a)), have been widely used for a-Si TFTs, as well as in most display prototypes due to easier processing and enhanced performance. 36,88 Nevertheless, BG structures require an additional layer (passivation) that protects the back channel from air exposure and therefore hinders undesired instability effects. 36,88 TG structures, especially coplanar (Fig. 4(d)), are mainly used for LTPS technology. With such a configuration indeed, the semiconductor can be deposited and crystallized at high temperatures without any damage to other materials/interfaces that are realized in successive steps.<sup>34</sup> In TG TFTs, the gate dielectric can also act as a passivation layer, reducing thus the number of patterning steps.<sup>29,88</sup> To improve the static (DC) performance, double-gate (DG) TFT structures (Fig. 4(e)) can be employed. 89,90 In DG TFTs, an additional gate is utilized to effectively control a larger portion of the semiconductor channel. Recently, the quest for small device footprint and nanoscaled channel lengths has led to the development of alternatives to planar geometries, such as vertical TFTs (VTFTs) (Fig. 4(f)) or quasi-vertical TFTs (QVTFTs), where the channel is not anymore defined by a photolithographic patterning step, but rather by the thickness of a device laver. 91,92 In the most common VTFT structures, the channel is formed on a multi-layer stack of source-dielectric-drain (Fig. 4(e)). 91–93 Nevertheless, alternative VTFT configurations with the channel defined by the gate or the semiconductor thickness have also been proposed and realized. 94-96

#### 2. TFT operation

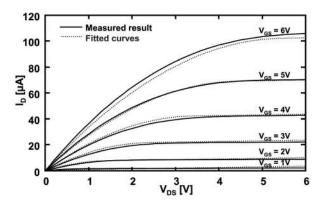

The most important DC performance parameters are extracted from the current-voltage (I-V) characteristics in compliance with the gradual channel approximation. <sup>97</sup> As shown in the transfer  $I_D$ - $V_{GS}$  (Fig. 5(a)) and output  $I_D$ - $V_{DS}$  (Fig. 5(b)) curves, there are two main operating regimes: linear and saturation. For small values of the drain-source

voltage  $V_{DS}$  ( $V_{DS} \ll V_{GS} - V_{TH}$ , where  $V_{GS}$  is the gate-source voltage and  $V_{TH}$  is the threshold voltage), the device operates in linear regime and the drain current  $I_D$  is approximated by the simplified Shichman - Hodges FET model<sup>98</sup>

$$I_{D,lin} = \frac{W \cdot \mu \cdot C_{ox}}{I_{c}} \cdot (V_{GS} - V_{TH}) \cdot V_{DS}, \qquad (1.1)$$

where W is the channel width,  $\mu$  is the channel mobility,  $C_{ox}$  is the specific capacitance of the gate dielectric per unit area, and L is the channel length. When  $V_{DS} \ge V_{GS} - V_{TH}$ , the device operates in saturation regime and  $I_D$  equals

$$I_{D,sat} = \frac{W \cdot \mu \cdot C_{ox}}{2 \cdot L} \cdot (V_{GS} - V_{TH})^2. \tag{1.2}$$

Equations (1.1) and (1.2) can be used to extract the TFT DC parameters: carrier mobility, threshold voltage, current on/off ratio, sub-threshold swing (SS), and contact resistance.<sup>97</sup>

a. Carrier mobility. This parameter describes the efficiency of charge carrier transport in a material, which affects directly the maximum drain current and the operating frequency (the so-called transit frequency  $f_T$ ) of a device.<sup>99</sup> In a material,  $\mu$  depends on several scattering mechanisms (e.g., lattice vibrations, impurities, and grain boundaries). 99,100 The most common way to characterize the intrinsic mobility of a bulk material is to extract the Hall mobility ( $\mu_H$ ) from the Hall effect. 100 The mobility in a TFT is typically different from the intrinsic mobility of its semiconductor, since charge transfer is now limited to a narrow region close to the gate dielectric/ semiconductor interface and further sources of scattering (e.g., Coulomb scattering from dielectric charges and interface states, and surface roughness scattering) need to be considered. 100 According to Schroder, 100 several TFT mobilities can be extracted: the effective mobility  $\mu_{\text{eff}}$ , the field-effect mobility  $\mu_{\rm FE}$ , and the saturation mobility  $\mu_{\rm sat}$ . Most common mobilities are  $\mu_{FE}$  (also known as linear mobility  $\mu_{lin}$ )

$$\mu_{FE} = \mu_{lin} = \frac{L}{W \cdot C_{ox} \cdot V_{DS}} \cdot \frac{dI_D}{dV_{GS}}, \tag{1.3}$$

and

$$\mu_{sat} = \frac{2 \cdot L}{W \cdot C_{ox}} \cdot \frac{d^2 I_D}{dV_{GS}^2} = \frac{2 \cdot L}{W \cdot C_{ox}} \cdot \left(\frac{d\sqrt[2]{I_D}}{dV_{GS}}\right)^2. \tag{1.4}$$

b. Threshold voltage. The threshold voltage  $V_{TH}$  corresponds to the gate-source voltage at which a conductive channel is formed at the dielectric/semiconductor interface. In n-type TFTs, if  $V_{TH}$  is positive/negative, the devices are designated to operate in enhancement/depletion mode. There are several methods used to extract  $V_{TH}$ . If not explicitly specified, the most employed methodology is represented by the linear extrapolation of the  $I_D$ - $V_{GS}$  plot (linear regime) or  $I_D^{1/2}$ - $V_{GS}$  plot (saturation regime).

c. Current on/off ratio. The current on/off ratio  $I_{ON}/I_{OFF}$  is extracted from the transfer curve (Fig. 5(a)), dividing the

maximum with the minimum drain current (typically in saturation regime).  $^{97}$  A value of  $10^6$  or higher is desirable for digital circuits.  $^{102}$  Nevertheless, smaller  $I_{ON}/I_{OFF}$  can also result in successful switching operation.  $^{103}$  For analog circuits, a current on/off ratio of  $>10^4$  is typically sufficient.  $^{80}$

d. Sub-threshold swing. Another important parameter is the sub-threshold swing (SS), which is a measure of how efficiently the transistor can turn on and off. SS is directly related to the quality of the interface dielectric/semiconductor. The sub-threshold swing is defined as the inverse of the maximum slope of the  $I_D$ - $V_{GS}$  plot and indicates the gate-source voltage needed to increase the drain current by one decade

$$SS = \left(\frac{dV_{GS}}{d\log_{10}(I_D)}\bigg|_{max}\right). \tag{1.5}$$

A low sub-threshold swing  $<100\,\mathrm{mV/dec}$  (together with a threshold voltage close to  $0\,\mathrm{V}$ ) is desirable to reduce the power consumption and the operating voltage in circuit applications.  $^{102,104}$

e. Contact resistance. Beside the above mentioned parameters, a less cited (but still important) parameter is given by the contact resistance ( $R_C$ ) between the source/drain electrodes and the semiconductor. Controlling the contact resistance is especially important in short-channel devices ( $L \lesssim 5\,\mu\text{m}$ ), since a high  $R_C$  value can lead to the degradation of both the device  $\mu_{FE}$  and  $f_T$ .  $^{105,106}$  In a TFT, the contact resistance depends on the source/drain electrodes,  $^{107,108}$  the interface metal/semiconductor,  $^{107}$  the source/drain to gate contact area,  $^{106,108}$  as well as specific contact treatments (plasma, temperature, etc.) performed.  $^{109}$  A well-known and utilized indirect method to extract  $R_C$  is the transmission-line method (TLM), which requires the linear  $I_D$ - $V_{GS}$  curves of a series of TFTs with different channel lengths.  $^{108}$  More specifically,  $R_C$  can be extracted from the total TFT resistance ( $R_T$ )

$$R_T = r_{CH} \cdot L + R_C, \tag{1.6}$$

where  $r_{CH}$  is the channel resistance per unit channel length. <sup>108</sup> By fitting the experimental values of the  $R_T$ -L plot for different  $V_{GS}$  with a linear curve, the total contact resistance can be estimated. Alternatively, the  $R_C$  can also be extracted from the ratio of two linear  $I_D$ - $V_{GS}$  measurements taken on the same device (at two different  $V_{DS}$ ), as explained by Campbell *et al.* <sup>110</sup>

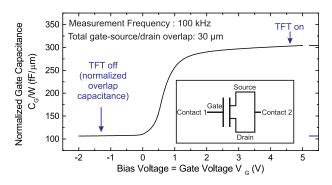

f. Overlap capacitance. Besides the contact resistance, also the overlap capacitance  $C_{OV}$  between the gate contact and the source/drain electrodes is an important parameter, since it directly influences the TFT's transit frequency.  $^{97}$   $C_{OV}$  can be extracted from the capacitance-voltage (C-V) characteristics (Fig. 6), from which the total gate capacitance  $C_G$  can be estimated

$$C_G = C_{GS} + C_{GD} = C_{ox} \cdot W \cdot (L + L_{OV,TOT}), \tag{1.7}$$

FIG. 6. Typical width normalized capacitance-voltage (C-V) characteristics of an n-type metal oxide semiconductor TFT (channel length  $L\!=\!30\,\mu\text{m})$  measured at  $100\,\text{kHz}$ . Inset: used measurement configuration.

where  $C_{GS}$  is the gate-source capacitance,  $C_{GD}$  is the gate-drain capacitance, and  $L_{OV,TOT}$  is the total overlap length between the gate and the source/drain electrodes  $(L_{OV,TOT} = L_{OV,S} + L_{OV,D})^{.97}$  The overlap capacitance  $C_{OV} = C_{ox} \cdot W \cdot L_{OV,TOT}$  and can be extracted from the C-V plot (Fig. 6) as the minimum  $C_G$  value.

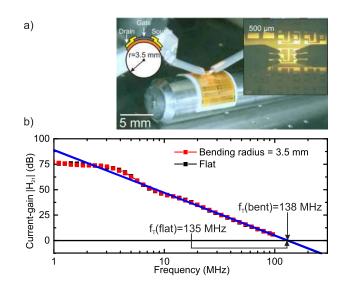

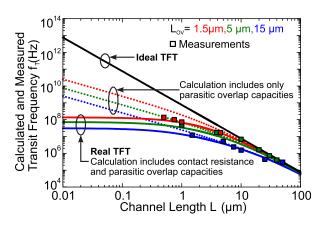

g. Transit frequency. The most important small signal (AC) parameter of a TFT is the transit frequency ( $f_T$ ), which quantifies the speed of the device. <sup>97</sup> The  $f_T$  is given by the following formula: <sup>111</sup>

$$f_T = \frac{1}{2 \cdot \pi} \cdot \frac{g_m}{C_G} \propto \frac{\mu \cdot (V_{GS} - V_{TH})}{L \cdot (L + L_{OV,TOT})},$$

(1.8)

where  $g_m$  is the transconductance  $(g_m = \frac{dl_D}{dV_{GS}})$  calculated in the saturation regime. A first value of the transit frequency can be estimated from the  $g_m$  and  $C_G$  values extracted from the  $I_D$ - $V_{GS}$  and  $C_G$ - $V_{GS}$  data, respectively. A more precise value of the transit frequency can be calculated by measuring the TFT's S-parameters, i.e., by applying a low voltage RF voltage on top of the  $V_{GS}$  bias and subsequently measuring the  $I_{DS,sat}$  of the devices. From the device S-parameter measurement, the corresponding small signal current gain  $H_{21}$  can be calculated as a function of the frequency. The  $I_T$  is then given by the value where  $I_T$  equals 1 (see Fig. 13 for a practical example).  $I_T$

# C. Present issues and challenges

From 2003 onwards with the work of Hosono, <sup>29,63</sup> Wager, <sup>51,60</sup> Carcia, <sup>52,59</sup> and Fortunato, <sup>57,58</sup> metal oxide semiconductor TFTs have gained an increasingly interest, especially in view of their application in optical display backplanes. At the beginning, the attention has been mainly focused on the realization of metal oxide semiconductor TFT yielding high carrier mobility, as well as good stability under bias and illumination stress. In particular, the influence of semiconductor composition, passivation layer, gate dielectric, and source/drain electrodes on the device performance and stability have been extensively investigated, as reported in several reviews. <sup>36,88,115</sup> The enormous progresses achieved in the last ten years in these areas have directed current research efforts towards new directions and challenges. <sup>36,88</sup> In particular, the possibility to replace vacuum-

processing techniques with higher throughput continuous processes is especially attractive in view of novel large-area and cost-effective applications, such as foldable and printable displays, disposable smart labels, and intelligent packaging. 87,116 To this aim, solution-processing techniques, especially spray pyrolysis (SP) or digitally controlled ondemand deposition methods like ink-jet printing, are gaining an increasing interest.<sup>87</sup> Another open issue is represented by the development of metal oxide semiconductor TFTs with good p-type conduction. Even if notable advances have been made in this direction, p-type metal oxide semiconductor devices can hardly yield performance levels similar to their n-type counterpart. 36,87 As explained later in this review, this is due to the specific charge transport characteristics of metal oxide semiconductors. 115,117 Due to the scarce availability of good p-type devices, the majority of the reported metal oxide semiconductor-based circuits are thus unipolar, employing only n-type TFTs. Even if complex large-area and high TFT count digital and analog electronic circuits have been demonstrated by employing only n-type metal oxide semiconductor TFTs, the development of a complementary technology based on both n- and p-type devices is essential to realize compact and low-power circuits. 118 To this purpose, research on complementary circuits based on hybrid metal oxide/organic or fully metal oxide semiconducting materials has expanded.<sup>36</sup>

All of the above mentioned topics apply for both rigid and flexible metal oxide semiconductor TFTs. Nevertheless, in the case of flexible substrates, the solution of the previously listed issues is even more challenging, due to the generally more complicated processing conditions (i.e., low temperature fabrication, substrate dimensional instability during TFT fabrication, and circuit integration). Furthermore, in the case of flexible TFTs, special care needs to be taken also on the mechanical properties of the devices (e.g., induced strain, maximum strain resistance, influence of strain on the TFT performance, and role of mechanical fatigue). Additionally, novel device features such as transparency, conformability, stretchability, biocompatibility, and biodegradability (with their related challenges) need also to be taken into account. In this review, we tackle all of the above mentioned issues and challenges, focusing only on devices fabricated on flexible substrates. To date and to the best of our knowledge, no report has specifically targeted this topic. We are only aware of a book chapter dealing with flexible solution-processed metal oxide semiconductor TFTs, 119 as well as two review articles, respectively, on the mechanical and electronic properties of flexible TFTs (all technologies)<sup>30</sup> and on p-type metal oxide semiconductor materials and devices (rigid and flexible). 120 For this reason, this paper presents the recent progresses in the field of flexible TFTs and circuits, based on both n- and p-type metal oxide semiconductors grown by vacuum- and solutionprocessing techniques. Main aim of this review is to underline the process/material/device/circuit requirements that are specific to flexible substrates compared with rigid ones and provide at the same time guidelines for the realization of flexible devices with good electrical and mechanical properties, using metal oxide semiconductor technology. The reviews are structured as follows:

- In Section II, the state-of-the-art flexible n-type metal oxide semiconductor TFTs are presented. First, in Sec. II A, a short overview of the available metal oxide semiconductors is given. Then, in Sec. II B, flexible devices based on vacuum-processed metal oxide semiconductors are reviewed. Finally, in Sec. II C, flexible TFTs with novel solution-deposited metal oxide semiconductors are reported.

- Section III deals with the recent progresses in the field of

flexible p-type metal oxide semiconductor TFTs. As for

Section II, also in this case first a brief overview on the

available materials is given Sec. III A; then in Sec. III B,

flexible devices based on vacuum-processed metal oxide

semiconductors are reviewed; finally in Sec. III C,

solution-processed flexible TFTs are analyzed.

- Section IV reviews the state-of-the-art flexible circuits based on metal oxide semiconductors. Section IV A provides a basic explanation of the possible configurations, as well as of the basic operating principle of both digital and analog circuits. Then, in Sec. IV B, flexible unipolar digital and analog electronic circuits based on metal oxide semiconductors are presented. Finally, in Sec. IV C, flexible complementary metal oxide semiconductor-based circuits are reviewed.

- Section V deals with novel flexible electronic systems based on metal oxide semiconductor TFTs.

- In Section VI, the conclusions are drawn and an outlook over the field is given.

In order to provide a broad overview of the field, the first subsections of each section (II A, III A, and IV A) reference reports on both rigid and flexible substrates. However, the main subsections of this review (II B, II C, III B, III C, IV B, and IV C) deal only with flexible TFTs and circuits based on metal oxide semiconducting materials. We have done an exhaustive literature review on the topic and have tried to include all the relevant works until the submission of this review (April 2016). If there is some work not referenced, we apologize the authors in advance.

# II. N-TYPE METAL OXIDE SEMICONDUCTOR TFTs

In this section, flexible n-type metal oxide semiconductor TFTs are presented. In particular, in Sec. II A, binary and multicomponent metal oxide semiconducting compounds are reported, together with a short explanation on the theory of these materials. Then in Sec. II B, a detailed description of the recent progresses obtained for flexible vacuum-processed metal oxide semiconductor TFTs is given, with a special focus on materials, fabrication techniques, electrical performance, and bendability. Finally, in Sec. II C, novel solution-processing methods to realize flexible metal oxide semiconductor TFTs are shown.

# A. N-type metal oxide semiconductors

The first reported metal oxide semiconductors were binary compounds, such as SnO<sub>2</sub>, ZnO, In<sub>2</sub>O<sub>3</sub>, and Ga<sub>2</sub>O<sub>3</sub>, in

either a pure composition or with an impurity dopants. These binary materials are characterized by wide band gap  $E_o > 3 \text{ eV}$  and large transmission in the visible range (above 80%). 115,121 The resulting films are n-type semiconducting, yielding a high carrier concentration (N) in the order of 10<sup>16</sup> cm<sup>-3</sup>-10<sup>21</sup> cm<sup>-3</sup>, which is attributed to native donors, e.g., oxygen  $(O_2)$  vacancies and/or metal atoms. <sup>115,121</sup> Additionally, even if these films present an amorphous phase, they yield large  $\mu_{\rm FE} > 10 \, {\rm cm}^2 \, {\rm V}^{-1} \, {\rm s}^{-1},^{115}$  due to their unique electronic structure. 117 Indeed, in contrast to covalent semiconductors like Si, metal oxide semiconductors are valence compounds with a strong degree of ionicity within their chemical bonding. 87,117 In metal oxide semiconductors, charge transfer occurs from the metal orbitals (s) to the oxygen orbitals (2p). The conduction band minimum (CBM) is indeed formed by highly dispersive unoccupied metal orbitals, whereas the valence band maximum (VBM) is constituted by fully occupied and localized oxygen orbitals. 87,117 Those vacant metal orbitals are spherical (i.e., non directional) and exhibit large spatial spread. 115,117 As a consequence, electron transport can easily occur through the direct overlap of the metal orbitals in neighboring metal cations. <sup>87,115,117</sup> This explains why the majority of existing metal oxide semiconductors yield n-type conductivity, and hole transport is intrinsically hindered by a larger effective mass.<sup>87</sup> By employing binary metal oxide semiconducting materials (SnO<sub>2</sub>, ZnO, In<sub>2</sub>O<sub>3</sub>, and Ga<sub>2</sub>O<sub>3</sub>) as active layers in TFTs, large differences in carrier mobility and current on/off ratios can be achieved. For example,  $In_2O_3$  TFTs can lead to high  $\mu_{FE}$  up to  $100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , but at the same time also large  $I_{OFF}$  (due to high  $N>10^{18}\,{\rm cm}^{-3}$ ).  $^{36,122}$   $Ga_2O_3$  films possess large resistivity (due to low carrier density and large density of empty traps), resulting thereby in poor device performance ( $\mu_{FE} = 0.05 \, \text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1}$ ). Similar to  $\text{In}_2\text{O}_3$ ,  $\text{SnO}_2$ TFTs can reach higher carrier mobility, as well as larger off current.<sup>62</sup> The best-known and most performing binary metal oxide semiconductor is ZnO, which can lead to high  $\mu_{\rm FE}$  and  $I_{ON}/I_{OFF}$ . <sup>36,88</sup> However, most binary metal oxide semiconductors (especially ZnO) tend to form poly- or nano-crystalline structures, which lead to the creation of grain boundary defects and therefore non-uniform TFT performance over larger areas. 88,115 Compared with binary compounds, multicomponent metal oxide semiconductors, in general, result in better TFT performance. 36,115 In multicomponents, a stable amorphous phase can be achieved by mixing two or more metal cations with different ionic charges and sizes, whereas the incorporation of a stabilizer metal cation can be used to better control the carrier concentration. 117 For example, IZO presents a stable amorphous phase, which results in TFTs with good uniformity and  $\mu_{\rm FE}$ . Nevertheless, the high N >  $10^{17}$  cm<sup>-3</sup> leads to high  $I_{OFF}$  and low  $I_{ON}/I_{OFF}$ . <sup>36,115,124</sup> Given the stronger bonds of gallium (Ga) with O2, indium gallium oxide (IGO) leads to a lower carrier density, but at the same time also smaller  $\mu_{\rm FE}$ . To realize an amorphous oxide semiconductor with large  $\mu_{\rm FE}$  and  $I_{ON}/I_{OFF}$ , in 2004 Nomura et al. proposed the introduction of Ga into IZO, developing IGZO, the most widely used metal oxide semiconductor nowadays.<sup>29</sup> IGZO

TFTs allow  $\mu_{FE} \gg 10 \, \mathrm{cm^2 \, V^{-1} \, s^{-1}}$  with N <  $10^{17} \, \mathrm{cm^{-3}}.^{29,115}$  Alternatives to Ga doping in IZO have also been developed, using tin (Sn), hafnium (Hf), and zirconium (Zr).  $^{88,125-127}$  At the same time, indium-free (and therefore cheaper) multicomponent metal oxide semiconductors (employing, for example, Sn, Al, or Zr) have also been demonstrated. Finally, also other multicomponent materials like ZnON have been recently reported.  $^{128-131}$

#### 1. Metal oxide semiconductors for flexible TFTs

Not all of the above mentioned metal oxide semiconducting materials have been employed as active layers in flexible TFTs.

a. Vacuum-processed metal oxide semiconductors. In the case of flexible vacuum-processed metal oxide semiconductor TFTs, amorphous IGZO is the most widely used material. 23,29,38,41,69,77,79–81,84,90,92,96,106,113,114,132–174 Flexible IGZO TFTs exhibit  $\mu_{FE}$  up to  $76 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , depending on the stoichiometric composition employed. Also, c-axis aligned crystalline (CAAC) IGZO TFTs on plastic foils have been demonstrated. 39,175,176 Crystalline ZnO is the second most used metal oxide semiconductor in flexible TFTs, with  $\mu_{\rm FE}$  up to  $50\,{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1.59,78,177-183}$  Other metal oxide semiconducting materials used are: IZO with  $\mu_{\rm FE}$  up to  $60\,{\rm cm^2\,V^{-1}\,s^{-1}},^{173,184-187}$  gallium zinc oxide (GZO) with  $\mu_{\rm FE}$  up to  $20.7\,{\rm cm^2\,V^{-1}\,s^{-1}},^{188}$  and ZTO with  $\mu_{\rm FE}$  up to 14 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>64</sup> Despite being considered a conductor, in general, thin layers of indium tin oxide (ITO) can also be used, yielding a  $\mu_{FE}$  of 28.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. 189

b. Solution-processed metal oxide semiconductors. Most used solution-processed semiconductors are crystalline  $\rm In_2O_3$  and ZnO. For  $\rm In_2O_3$  TFTs,  $\mu_{\rm FE}$  up to  $120\,\rm cm^2\,V^{-1}\,s^{-1}$  have been reported,  $^{76}$  including neat layers, nanoparticle (NP), or nanowire (NW) films, as well as blends of  $\rm In_2O_3$  and polyvinylpyrrolidon (PVP).  $^{76,145,190-192}$  In the case of ZnO, the highest  $\mu_{\rm FE}$  values reached are of  $7\,\rm cm^2\,V^{-1}\,s^{-1}$ .  $^{193-195}$  Other solution-deposited metal oxide semiconductors include IZO with  $\mu_{\rm FE}$  around  $4\,\rm cm^2\,V^{-1}\,s^{-1}$ ,  $^{196,197}$  ZTO with  $\mu_{\rm FE}$  of  $0.04\,\rm cm^2\,V^{-1}\,s^{-1}$ ,  $^{198}$  and IGO with  $\mu_{\rm FE}$  of  $0.4\,\rm cm^2\,V^{-1}\,s^{-1}$ ,  $^{199}$  Furthermore, solution-processed IGZO TFTs have shown excellent results with extremely high  $\mu_{\rm FE}$  values up to  $84\,\rm cm^2\,V^{-1}\,s^{-1}$ ,  $^{83}$  either in the form of neat IGZO or in blends of IGZO and graphene nanosheets.  $^{83,200,201}$

#### B. Flexible n-type vacuum-processed TFTs

In this subsection, the recent advances in the field of flexible n-type vacuum-processed metal oxide semiconductor TFTs are reviewed. In particular, the materials and the fabrication techniques employed are first presented. Then, the electrical performance and the mechanical properties of the resulting devices are discussed. Finally, additional features such as dissolubility, mechanical activity, stretchability, and transparency are tackled.

#### 1. Materials

The materials needed for the fabrication of flexible ntype vacuum-processed TFTs include flexible substrates, conducting materials to realize the source/drain and gate electrodes, dielectric materials for buffer, passivation and/or insulating layers, and most importantly metal oxide semiconducting active layers.

- a. Substrates. In contrast to standard Si MOSFET technology, the substrate used for the realization of TFTs is, in general, not a part of the active device itself, since it only provides a surface for the fabrication process. Nevertheless, the substrate, especially if flexible, has a significant influence on the final TFT properties, as well as on the manufacturing process. The key requirements concerning the substrate are:

- (I) The surface has to be compatible with standard thinfilm fabrication technology, which calls for roughness values in the nanometer regime.

- (II) The melting or glass transition temperature ( $T_m$  or  $T_G$ ) of the substrate has to be high enough to be compatible with the chosen fabrication process.

- (III) The substrate has to be bendable enough (in line with the mechanical requirements of the final devices) and at the same time has to provide sufficient stability for the manufacturing process.

- (IV) The deformation of the substrate caused by temperature gradients, mechanical load, as well as absorption or desorption of gasses or liquids during the fabrication has to be smaller than the minimum device feature size.

- (V) Vacuum-processing techniques call for small outgassing rates, compatible with the available deposition tools.

- (VI) Concerning a future mass production and commercialization, the substrates should be at least potentially available in large quantities and sizes, as well as cheap.

- (VII) Furthermore, the substrate needs to be resistant to the chemicals used during the fabrication process, especially photoresists and developers.

- (VIII) Finally, specific applications require substrates which are transparent, light-weight, conformable, stretchable, biocompatible, and even biodegradable.

All these requirements have led to the evaluation of a large variety of different substrates. Due to their properties and their availability, polymers are the natural choice and the most commonly used substrate materials. Among the different polymers, polyimide (PI) foils with thicknesses ( $t_s$ ) between 5  $\mu$ m and 125  $\mu$ m are the most frequently utilized substrates, <sup>135,145,152,157,158,160,165,172,177,180,184,188,189</sup> together with PI and nano silica. <sup>142,144</sup> This is because of the numerous advantages of PI (commercially known as Kapton®), like a small coefficient of thermal expansion (CTE) of  $12 \times 10^{-6}$  K, a small humidity expansion coefficient (HEC)  $(9 \times 10^{-6}\%$ RH), a high  $T_G$  of  $\approx 360$  °C, and a surface roughness in the nanometer range. <sup>114,155</sup> Since standard PI exhibits a yellowish to brownish color, other polymeric substrates have been introduced to benefit from their transparency in the visual wavelength range. These materials, which

are, in general, also cheaper and more easily available, include PET, 29,69,96,165,171,180,184,188 PET, <sup>29,69,96,165,171,180,184,188</sup> polyethylene na (PEN), <sup>38,40,41,134,136,139,149,153,158,163,166–168,173,181,202</sup> naphthalate theretherketone (PEEK),<sup>203</sup> polycarbonate (PC),<sup>154,157</sup> propylene (PP) based synthetic paper, 204 parylene, 80,141 (PES), 178 polyethersulfone water-soluble polyvinyl alcohol (PVA),<sup>82</sup> well as polydimethylsiloxane (PDMS). 78,132,147,205–207 In particular, PDMS is also stretchable and biocompatible, but at the same time hard to process using standard fabrication techniques. 78,132,147,205 An alternative to polymers is constituted by metal foils, such as Al foils, 156 and stainless steel substrates. 148 The main benefit of metal foils is the high  $T_m$  (above 1000 °C in the case of stainless steel). 155 Nevertheless, metallic substrates are conductive and thus require additional insulating buffer layers, which further increase weight and decrease flexibility. Other typologies of supports include flexible and transparent glass substrates (with high temperature resistance), 160,174 glassfabric reinforced composites, 93,169 cheap and biodegradable cellulose fiber-based paper, <sup>77,79,189,208</sup> as well as nontoxic biological paper like beeswax. 186 Additionally, also standard tracing paper (STP) and lab paper samples (LPS) have been employed. Finally, mechanically active multilayer substrates using a highly cross-linked hydrogel swelling layer and a stiff PI have been shown.<sup>23</sup>

b. Barrier layers. Before starting the effective TFT fabrication, often buffer or encapsulation layers are deposited on top of the substrate itself. Although there are numerous examples of flexible n-type vacuum-processed metal oxide semiconductor TFTs manufactured without barrier layers, there are several reasons why an encapsulation of the substrate is beneficial, including:

- (I) The need to electrically insulate a conductive substrate (e.g., Al or stainless steel).

- (II) A reduction of the substrate surface roughness by the deposition of a smoothing layer. 41

- (III) A reduction of the absorption and desorption of solvents during the fabrication process by decreasing the effective humidity expansion coefficient (HEC).

- (IV) An improvement of the adhesion between the substrate and the device layers.

- (V) A reduction of the substrate outgassing in low pressure environments to speed up the pumping steps during the deposition process.

- (VI) A decrease of the substrate permeability by decreasing the effective water vapor transmission ratio (WVTR).

Typical adhesion or buffer layers are made of silicon nitride  $(SiN_x)$ ,  $^{92,106,113,114,140,143-146,150,151,173,182,183}$  silicon oxide  $(SiO_x)$ ,  $^{78,82,135,148,154,157,168,170,181,205}$  and photoresist sandwiched between  $SiN_x$  and  $SiO_x$ .  $^{158}$  Organic materials,  $^{78,82,136,148,154,157,168,170,181,205}$  in particular, SUB,  $^{153}$  or PVP is especially well-suited as smoothing layers.  $^{152,172}$  A direct comparison of the influence of different buffer layers (50 nm  $SiO_x$ , 50 nm  $SiN_x$ , or 50 nm  $SiN_x$  in combination with 10 nm or 100 nm  $AlO_x$ ) on the performance of TG IGZO TFTs on PI substrate is given by Ok et al., as shown in Fig. 7.  $^{155}$  The buffer layer with the smallest WVTR = 0.033 g/(cm<sup>2</sup> day) is

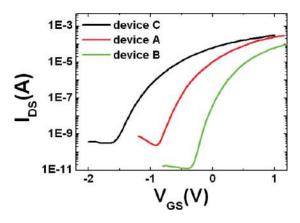

FIG. 7. Transfer characteristics of flexible IGZO TFTs with 50 nm silicon nitride  $(\mathrm{SiN_x})/10\,\mathrm{nm}$  aluminum oxide  $(\mathrm{AlO_x})$  (Device B), 50 nm  $\mathrm{SiN_x}/100\,\mathrm{nm}$  AlO<sub>x</sub> (Device C), or 50 nm silicon oxide (SiO<sub>x</sub>) (Device D) barrier layers on PI substrate. The inset shows a TFT (Device A) with a 50 nm  $\mathrm{SiN_x}$  buffer layer. All measurements are for pristine (dashed line) and 250 °C-annealed TFTs (solid line). Reproduced with permission from Appl. Phys. Lett. 104, 063508 (2014). Copyright 2014 AIP Publishing LLC.

given by  $50 \, \mathrm{nm} \, \mathrm{SiN_x} + 100 \, \mathrm{nm} \, \mathrm{AlO_x}$ . As shown by Ok *et al.*, this buffer layer is able to reduce the carrier trapping at water related defects and results in the best device performance and stability (Fig. 7). Consequently, several groups have published the use of multi-layers which can potentially combine the advantages of different materials. These layer stacks include organic TR-8857-SA7 with  $\mathrm{Al_2O_3}$ ,  $^{139,202,204}$  undefined organic layers in combination with  $\mathrm{Al_2O_3}$ ,  $^{93,167}$  as well as  $\mathrm{SiO_2}$ . The most complex published structure is a  $\mathrm{SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/SiO_2/SiN_x/S$

*c. Gate dielectrics.* Together with the metal oxide semiconductor, also the gate dielectric plays a fundamental role. This is mainly due to the following reasons:

- (I) As visible from Equation (1.1), the drain current  $I_D$  is directly proportional to  $C_{ox} = \frac{\epsilon_R}{t_{ox}}$ , where  $\epsilon_R$  and  $t_{ox}$  are, respectively, the dielectric constant and the thickness of the gate dielectric. For low-voltage TFT operation, thin gate dielectric materials with high  $\epsilon_R$  are desirable.

- (II) The insulation properties, correlated with the specific resistance and the pinhole density (and therefore the layer deposition quality) of the dielectric material, define the gate leakage of the device (the so called gate current  $I_G$ ).

- (III) The quality of the interface between the gate dielectric and the semiconductor can strongly influence the carrier mobility, as well as the stability of the TFT, by determining the interface trap density.

The most widely used gate dielectric is aluminum oxide in different forms, such as  $Al_2O_3$ ,  $^{23,41,59,80,81,93,96,145,147,162,169,178,179,183,202}$   $AlO_x$ ,  $^{155}$  and also anodized  $Al_2O_3$  on Al gates.  $^{153,168}$  Additionally, anodic neodymium-doped  $AlO_x$  ( $AlO_x$ :Nd) on aluminum

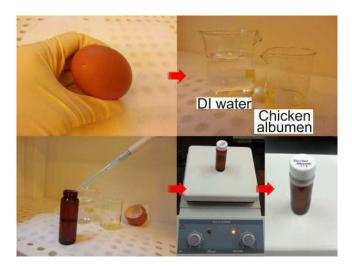

FIG. 8. Chicken albumen ferroelectric gate dielectric: preparation procedure for diluted chicken albumen solution. Reproduced with permission from Kim *et al.*, Appl. Mater. Interfaces 7, 4869 (2015). Copyright 2015 American Chemical Society.

neodymium (AlNd) gates has been used. 158 The advantages of aluminum oxide are comparably high  $\epsilon_R$  around 9.5, low pinhole density if deposited by atomic layer deposition (ALD), and, especially in combination with IGZO, a good interface quality. Employed materials with a higher  $\epsilon_R$  include hafnium oxide (HfO<sub>2</sub>), <sup>177,180,181</sup> hafnium lanthanum oxide (HfLaO), 170 titanium oxide (TiO<sub>2</sub>), 154 and yttrium oxide  $(Y_2O_3)^{29,69}$  The drawback of these dielectrics is a scarcer availability, a worst interface quality, as well as a reduced compatibility with the TFT fabrication process. silicon time, oxide  $SiO_2^{40,78,133,137,138,148,163,164,166,173,174,188,205}$  or  $SiO_x$ ) is a more established material but results in a reduced specific gate dielectric capacitance  $C_{ox}$  ( $\epsilon_R \approx 3.9$ ). <sup>82,156</sup> Even if a direct comparison between SiO<sub>2</sub> and SiN<sub>x</sub> by Lim et al. showed that IGZO TFTs with SiN<sub>x</sub> dielectric exhibit slightly better performance than those with  $SiO_2$ , <sup>171</sup>  $SiN_x$  is only rarely used in the community. <sup>134,142,159,160</sup> Besides metal oxide dielectrics, also organic materials have been used as gate dielectric, such as layers made from olefin polymers,<sup>38</sup> or cross-linked PVP (c-PVP). 165 To this regard, a direct comparison of c-PVP and SiO2 showed that both materials have a comparable  $\epsilon_R$  and result in flexible IGZO TFTs with similar performance parameters, <sup>165</sup> although the thick c-PVP layer ( $t_{ox} = 280 \text{ nm}$ ) reduces  $C_{ox}$  if compared with the thinner  $SiO_2$  (t<sub>ox</sub> = 170 nm). A third class of gate dielectrics is ferroelectric materials, in particular, poly(vinylidene fluoridetrifluoroethylene) [P(VDF-TrFE)]. 132,136,149,167 P(VDF-TrFE) can be reversibly polarized and hence used for the fabrication of non-volatile memory TFTs. Interestingly, recently also chicken albumen ferroelectric gate dielectrics have been demonstrated, as shown in Fig. 8.<sup>204</sup> A fourth class of gate dielectric materials is constituted by solid electrolytes (e.g., phosphorus (P)-doped SiO<sub>2</sub>), which are characterized by high specific gate dielectric capacitance per unit area ( $C_{ox}$ ) and therefore low-voltage device operation. This improvement is generally ascribed by a redistribution of mobile ions with the applied voltage. Fig. 9 illustrates how P-doped SiO<sub>2</sub>

FIG. 9. Phosphorus-doped  $SiO_2$  solid electrolyte dielectric: (a) total gate capacitance ( $C_G$ ) and ionic conductivity, as well as (b) leakage current ( $I_G$ ) through the electrolyte. Reproduced with permission from Jiang *et al.*, IEEE Electron Device Lett. **33**, 65 (2012). Copyright 2012 Institute of Electrical and Electronic Engineers.

gate dielectrics allow achieving high Cox values of up to  $13 \,\mu\text{F cm}^{-2}$ . To combine the advantageous properties of different dielectric materials, a variety of hybrid and multi-layer materials have been utilized as gate dielectrics for flexible n-type vacuum-processed metal oxide semiconductor TFTs. These include: TiO<sub>2</sub> with HfO<sub>2</sub>, <sup>157</sup> PVP-Al<sub>2</sub>O<sub>3</sub>, <sup>152</sup> or PVP with methylcyclohexane (pp-MCH) and  $Al_2O_3$ , <sup>172</sup>  $SiN_x$  with SiO<sub>x</sub>, 135,144 tri-layer stacks like TiO<sub>2</sub> sandwiched between SiO<sub>2</sub> or TiO<sub>2</sub> sandwiched between HfO<sub>2</sub>, <sup>154</sup> as well as P(VDF-TrFE) with Al<sub>2</sub>O<sub>3</sub>. <sup>146</sup> Finally, an interesting approach is constituted by the use of a paper substrate as gate dielectric.  $^{77,79,186,208}$  Although the paper thickness is as high as 75  $\mu$ m, a  $C_{ox}$  value of  $4 \times 10^{-4}$  F m<sup>-2</sup> was achieved.  $^{79}$  This is because the dielectric properties are determined by an arbitrary serial and parallel combination of discrete fiber capacitors within the paper substrate. The large choice concerning possible dielectrics results in a big variety of published  $C_{ox}$ values ranging from  $1.2 \times 10^{-4}$  F m<sup>-2</sup> measured for an organic layer<sup>165</sup> up to  $1.3 \times 10^{-1}$  F m<sup>-2</sup> for a solid electrolyte. 184 Finally, ZnO was sandwiched between two layers of Al<sub>2</sub>O<sub>3</sub> to create a charge trapping layer in the gate dielectric, leading to non-volatile memory TFTs. 139

d. Contacts. This class of materials includes metals and other conductors employed to fabricate gate and source/drain electrodes. Since the gate contact of a TFT (and in general of a FET) does not need to conduct a significant amount of current, the material is, in general, selected to achieve a high

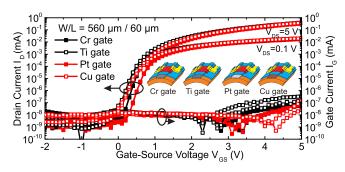

FIG. 10. Transfer characteristics of flexible IGZO TFTs fabricated using different gate metals: chrome (Cr), titanium (Ti), copper (Cu), and platinum (Pt), all exhibiting similar electrical performance. Reproduced with permission from Münzenrieder *et al.*, in *Proc. of Eur. Solid-State Device Res. Conf. (ESSDERC)* (2013), pp. 362–365. Copyright 2013 Institute of Electrical and Electronic Engineers.

compatibility with the TFT fabrication process. This issue was also addressed by a direct comparison between different gate metals like chromium (Cr), titanium (Ti), copper (Cu), and platinum (Pt).<sup>84</sup> Fig. 10 displays the corresponding transfer characteristics showing that although the work function of the various gate metals is different, their influence on the electrical performance of IGZO TFTs is minor. <sup>84</sup> Consequently, a variety of different metals: silver (Ag), <sup>189</sup> Al, <sup>59,132,149,153,174,178,202,204</sup> Au, <sup>38,136,167</sup> Cr, <sup>23,81,84,113,140,141,143,150,151,179,182,183</sup> Au, 38,136,167 Cu. 84,92,145,146 (Mo), 41,82,132,137,138,148,163,164,166,173 nickel (Ni), 152,172 Pt, 84 Ti, <sup>84,90,106,114,144,147,169</sup> as well as AlNd, <sup>156,158,168</sup> molybdenum titanium (MoTi), 155 and tantalum nitride (TaN) metal alloys have been used as gate contacts. 154,157,170 Especially for BG TFTs, the adhesion of the gate contact to the flexible substrate appears to be the main concern. To this aim, Cr and Ti show good results, whereas Cr often suffers from a high built-in strain.<sup>90</sup> Multi-layer metals offer, in general, a compromise between good adhesion and high conductivity, especially in the case of Ti/Au, <sup>23,96,181</sup> Ti/Cu, <sup>135</sup> Cr/Au, <sup>174</sup> or Ti/Au/Ti stacks. 162 gate Besides metals and metal IZO,<sup>77,79,133,160,208</sup> ITO, <sup>29,69,78,80,135,139,165,177,180,184,188,205</sup> In<sub>2</sub>O<sub>3</sub>, <sup>171</sup> and aluminum zinc oxide (AZO) have been used to fabricate transparent gate contacts. 93,134 Furthermore, duallayers of metal and ITO<sup>40</sup> or IZO have also been employed. 142 As regards source/drain electrodes, the material has to provide a high conductivity and at the same time a small contact resistance with the active layer. Moreover, also other properties like adhesion or transparency need to be considered. These requirements resulted in the use of different metals: Al, 77,149,152,154,157,165,170,172,179,208 Au, 38,167 Mo, 41,82,137,138,148,164,168 palladium (Pd), 145 and Ti, 90,93,144,169 whereas Mo and Ti seem to exhibit the lowest specific contact resistance  $R_C$ . At the same time, a big variety of multi-layer contacts have been developed to combine the advantageous properties of different materials; recent examples are: Ti/ Au, 59,69,81,84,113,140,141,143,146,150,151,181–183 Ni/Au,<sup>79</sup> Al, <sup>166,173</sup> Cr/Au, <sup>114</sup> Mo/AlNd, <sup>156</sup> Cr/Au/Cr, <sup>92</sup> Mo/Al/Mo, <sup>153</sup> Ti/Au/Ti, 162 or Ti/IZO. 142 Regarding transparent source/drain contacts, only ITO<sup>29,78,80,106,139,155,158,177,180,188,189,202,204,20</sup> and IZO have been used. 160,171,184 Finally, contacts based on Ti (drain) and graphene (source) in combination with a VTFT structure have been published.<sup>96</sup>

- *e. Passivation layers.* The performance of BG TFTs can be improved by depositing a final back channel passivation layer. This can lead to the following advantages:

- (I) An increase of the environmental and electrical stability of the TFTs by a reduced interaction between semiconductor and atmosphere (in particular, less interaction of the active layer with oxygen and water).

- (II) An encapsulation of the TFTs from a mechanical point of view.

- (III) A protection of the devices during post-processing steps like the fabrication of additional devices, such as organic light emitting diodes (OLEDs) or touch screens.

To simplify the fabrication process, it is quite common to passivate the device using the same material already used for the gate dielectric. Furthermore,  $Al_2O_3$  passivation layers are widely used because of the low oxygen transmission rate (OTR) of  $\approx 1.26 \times 10^{-4}\,\mathrm{mol/(m^2}$  day) and WVTR rate of  $\approx 6.61 \times 10^{-2}\,\mathrm{mol/(m^2}$  day) (both measured for a 8 nm thick  $Al_2O_3$  layer on PET). Al $_2O_3$  passivation layers result in BG metal oxide semiconductor TFTs with significantly improved stability, compared with unpassivated devices. 80.81,84,113,114,140,143,150,151,179 For similar reasons, also  $SiO_2$ , 164,166,168,173  $SiO_x$ , 133,156 and  $TiO_2$  have been used. 157 Additionally, organic layers such as photoresist, 103,153 SU8, 78,158,205 tetratetracontane, 152 and polychloroprene in combination with  $Al_2O_3$  have been utilized to passivate flexible n-type vacuum-processed metal oxide semiconductor TFTs. 23

# 2. Fabrication techniques

The fabrication of flexible n-type vacuum-processed metal oxide semiconductor TFTs employs standard semiconductor fabrication tools. Nevertheless, the large variety of available substrates with different physical and chemical properties has led to the use of a wide range of different techniques. These include several approaches to handle the flexible substrates, as well as to deposit and structure the various device layers.

a. Substrate preparation. The choice of the substrate is important, since it limits the maximum allowed temperature, as well as the typology of chemicals that can be used during the fabrication process. At the same time, the mechanical properties of the flexible support also determine the way how the substrate can be handled. Up to now, free-standing flexible substrates have been widely employed. 93,96,134,145,154,156,157,165,172,178,180,184,188,189,209 Free-standing foils are a natural choice for the fabrication of flexible devices because they are compatible with large-scale substrates and future roll-to-roll processes. Furthermore, the mechanical robustness of free-standing foils results in an insensitivity against mechanical shocks. At the same time, free-standing substrates also present the following drawbacks:

(I) They have to be sufficiently thick and stable to be mechanically handled with tweezers.

- (II) They can suffer from expansion caused by temperature gradients or by the absorption of solvents.

- (III) They have to be temporarily attached to a rigid carrier at least during the use of standard photolithographic tools.

One way to simplify the use of photolithographic tools like mask aligners or spinners is to bond the flexible foil to a glass or silicon wafer for the complete fabrication process. 40,41,132,136,139,153,158–160,163,166–170,173,174,202,204 can either be done using native adhesion forces or utilizing an additional adhesive. Alternatively, a flexible foil can also be mechanically fixed on particularly designed holders using metallic clamps. 162 In alternative to flexible substrates manufactured independently from the TFTs, it is also possible to create the flexible substrate by covering a host substrate with a polymer using either evaporation, <sup>80,81,141</sup> spin, slot or blade coating techniques. <sup>23,39,133,135,137,142,144,147,155,161,164,179</sup> The advantages of these fabrication techniques based on a rigid support are a high compatibility with the standard fabrication processes on Si or glass wafers, a reduction of the expansion of the substrate during the manufacturing process, as well as the possibility to realize devices on very thin ( $\approx 1 \,\mu m$ ) substrates. After the TFT fabrication is completed, the flexible foils or thin deposited polymer layers carrying the devices can be separated from the rigid support using: (1) mechanical peeling, 38,142,155,158,161,164,166,168,179 (2) a low adhesion releasing layer, <sup>133,144</sup> (3) a supporting laser, <sup>137</sup> or (4) a sacrificial layer between the host carrier and the polymer. 78,80,81,141,147 To this regard, a direct comparison of different releasing methods by Lin et al. showed that mechanical peeling of the flexible substrate from the hosting carrier wafer can lead to deformation and cracking of the TFTs in case of high adhesion forces between the polymer and the carrier. 144 To increase the mechanical stability or to realize electronic devices on alternative surfaces, thin flexible substrates have also been transferred and attached to a new carrier like PI or organic tissues. 38,39,78,80,81,141 Finally, it is also possible to fabricate TFTs directly on a rigid carrier coated with a sacrificial layer and subsequently transfer only the devices onto a flexible substrate. 38,78,82,205 In addition to the different handling possibilities, the substrate preparation typically includes a heat treatment step prior to the device fabrication itself. In the case of fabrication on free-standing plastic foil or foil bonded to a host substrate, the substrate is backed at high temperatures (around 200 °C) for several hours, to remove trapped residualliquids.  $^{84,90,92,106,113,114,132,143,145,146,151,152,170,172,182,209}$ This step allows also pre-shrinking flexible substrates which are not permanently attached to a rigid support.

- b. Deposition methods. Besides the standard criteria used for thin-film deposition techniques on Si or glass wafer (e.g., homogenous and dense layers), there are extra requirements which are especially important for the realization of flexible devices. These include:

- (I) Low temperatures, compatible with the thermal resistance of the employed flexible substrates.

- (II) A sufficient adhesion of the deposited materials to the substrate, in order to prevent a possible delimitation of the layers, especially when the substrate is bent.

- (III) Finally, the strain built in the deposited materials has to be small enough to allow good mechanical properties (e.g., bendability) of the final devices.

The predominant technique to deposit n-type vacuumprocessed metal oxide semiconductors is sputtering. RF and RF-magnetron sputtering have been used to deposit IGZO, <sup>23,80</sup>–82,96,132,134–136,139,145,147,152,155,156,202,208</sup> IZO, <sup>184</sup> GZO, <sup>188</sup> and ZnO. <sup>59,78,177,178,180</sup> Furthermore, IGZO was also deposited by DC sputtering <sup>133,137,153,160,168</sup> and pulsed DC sputtering. 40 The advantages of sputtering are the large availability of sputter tools, the low temperature (typically room temperature) deposition, as well as the good adhesion and dense structure of the final layers. Additionally, sputter tools offer several opportunities to optimize the layer properties, by adjusting the power and/or the sputtering pressure. Also, reactive sputtering using different concentrations of Argon (Ar) and O<sub>2</sub> has been used to adjust the oxygen content in the metal oxide semiconducting active layer. 41,59,69,79,133,134,136,142,144,149,154–157,159,170 An even better control of the stoichiometric composition of IGZO is possible by using co-sputtering techniques based on an IZO and a Ga<sub>2</sub>O<sub>3</sub> target.<sup>158</sup> Among all the n-type metal oxide semiconductors, ZnO is the only one that can be deposited by ALD, 93,139,182,183 plasma enhanced atomic layer deposition (PEALD), <sup>179</sup> and PLD. <sup>29,181</sup> Even if ALD has the advantage that the layers are conformal, the process is slow and less prone to variations of the chemical composition.

The deposition of insulating layers to realize gate dielectrics, passivation, or barrier layers aims at a high  $\epsilon_R$ , a low pinhole density, and a good sidewall coverage. This is why conformal deposition techniques are particularly well-suited: ALD<sup>23,41,80,81,139,140,145–147,152,155,162,172,178,183,202,204,209</sup> and PEALD of Al<sub>2</sub>O<sub>3</sub>, <sup>179</sup> ALD of HfO<sub>2</sub>, <sup>177</sup> as well as plasma-enhanced chemical vapor deposition (PECVD) of SiO<sub>2</sub>, 78,82,133,135,137,144,148,156,164,165,171,173,188,205  $SiO_{x}$ ,  $^{134,135,142,144,159,160,171}$   $SiO_{2}$ :P,  $^{184,189}$  but also organic pp-MCH.<sup>172</sup> These depositions are, in general, done at temperatures between 150 °C and 200 °C. Sputtering also results in comparably conformal layers and has therefore been used to deposit Y<sub>2</sub>O<sub>3</sub>,<sup>69</sup> SiO<sub>2</sub>,<sup>40,174</sup> and HfO<sub>2</sub>,<sup>180</sup> whereas PLD has only been employed to grow Y<sub>2</sub>O<sub>3</sub>.<sup>29</sup> Although evaporation of metal oxides requires high temperatures, different dielectrics (Al<sub>2</sub>O<sub>3</sub>, <sup>59</sup> HfLaO, <sup>170</sup> SiO<sub>2</sub>, <sup>154</sup> TiO<sub>2</sub>, <sup>154,157</sup> and HfO<sub>2</sub>) have been deposited by electron-beam evaporation. 157 Besides the mentioned vacuum-deposition techniques, highquality Al<sub>2</sub>O<sub>3</sub><sup>153,168</sup> or Al<sub>2</sub>O<sub>3</sub>:Nd gate dielectrics have also been grown anodizing a metallic gate.<sup>158</sup> Finally, organic layers, in particularly PVP, <sup>152,165,172</sup> chicken albumen, <sup>204</sup> or P(VDF-TrFE), have been spin coated. 132,136,146,149,167

As regards the deposition techniques of conductive materials, we have to distinguish between metals and transparent metal oxide conductors. Metals are typically deposited using e-beam evaporation, <sup>23,80–82,106,136,145–147,152,174,208,209</sup> thermal evaporation, <sup>149,152,157,165,167,178,179,202,204</sup> or sputtering. <sup>96,135,137,144,148,153–158,166,168,170,173,174,189</sup> Among these

techniques, the most common is evaporation, due to the non-conformal shape of the resulting layers that is beneficial for subsequent lift-off processes. Non metallic but transparent metal oxide conductors have been fabricated by sputtering (ITO,  $^{78,80,106,135,139,155,158,165,188,189,202,204,205}$   $In_2O_3,^{171}$  AZO,  $^{134}$  and  $IZO^{77,79,133,160,171}$ ), by e-beam evaporation (ITO  $^{177}$ ) or by PLD (ITO  $^{29}$ ). It is worth mentioning that also graphene monolayers grown by chemical vapor deposition (CVD) and transferred to a flexible PET substrate can be employed, as reported by Liu  $et\ al.^{96}$

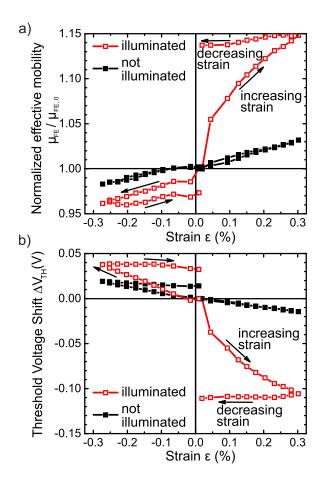

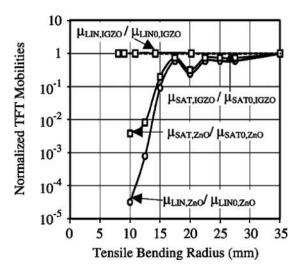

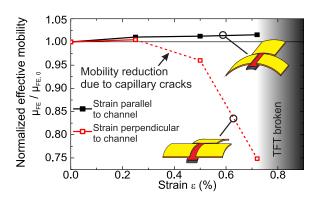

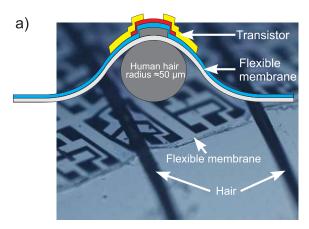

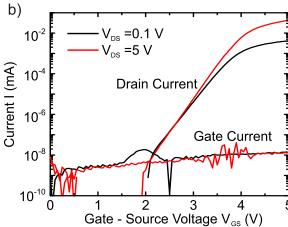

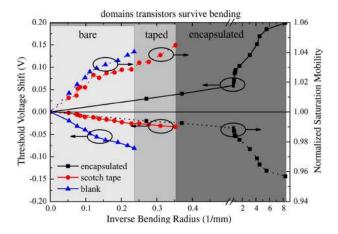

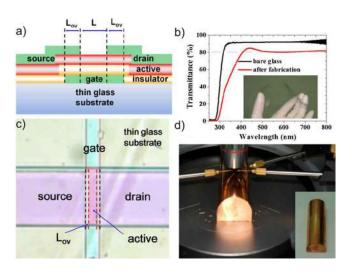

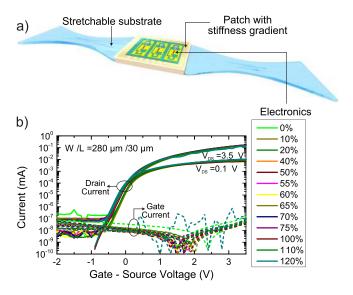

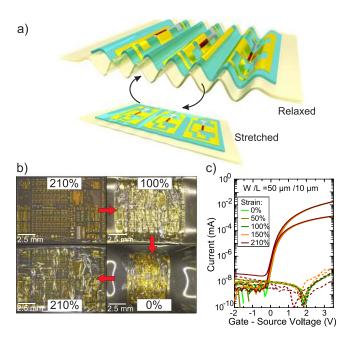

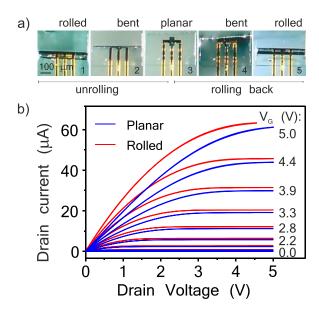

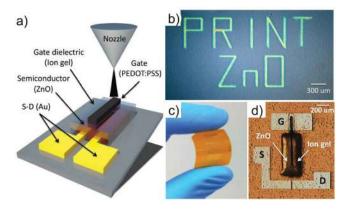

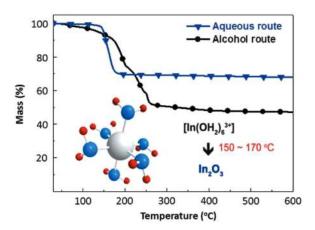

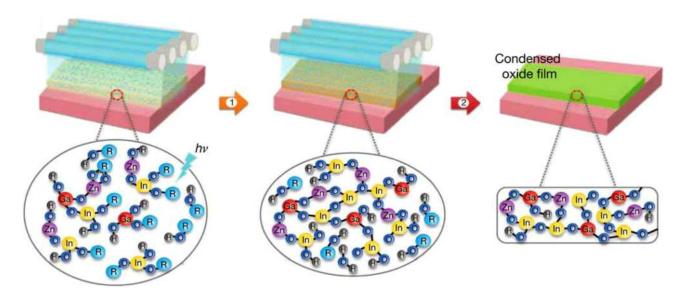

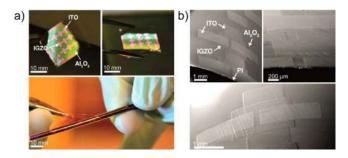

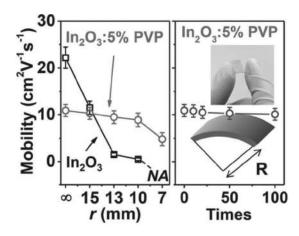

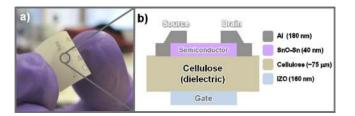

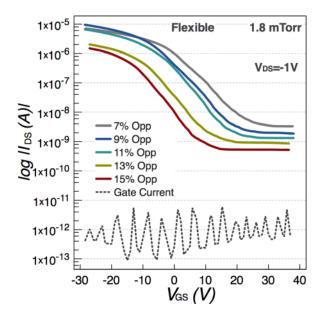

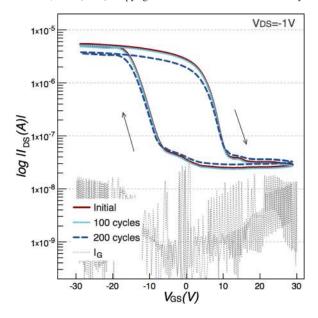

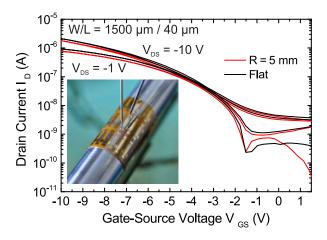

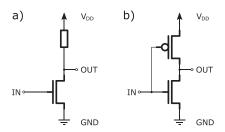

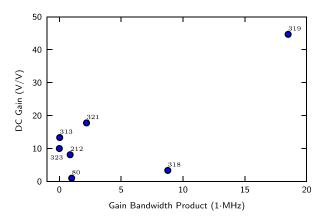

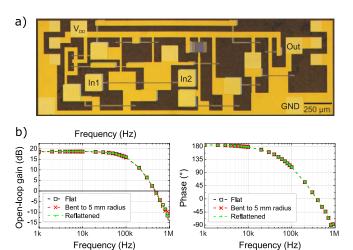

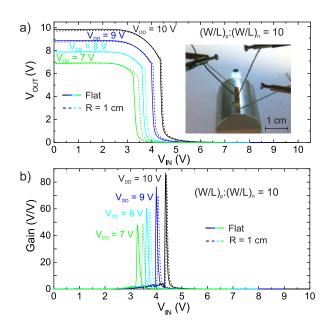

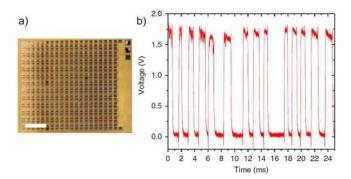

Some of the presented deposition procedures (e.g., from Li and Jackson<sup>179</sup> or Cherenack and Tröster<sup>182</sup>) are designed in a way that the semiconductor and the gate dielectric can be deposited with the same tool. <sup>179,182</sup> In this way, it is possible to avoid the surface contamination caused by breaking the vacuum and transferring the sample to another tool. However, there is no clear evidence in literature that breaking the vacuum necessarily leads to a degenerated device performance.