## United States Patent [19] Anthony [54] METHOD FOR MAKING ALIGNMENT-ENHANCING FEED-THROUGH CONDUCTORS FOR STACKABLE SILICON-ON-SAPPHIRE [75] Inventor: Thomas R. Anthony, Schenectady, Assignee: General Electric Company, Schenectady, N.Y. Appl. No.: 445,350 [22] Filed: Nov. 29, 1982 Related U.S. Application Data [62] Division of Ser. No. 244,854, Mar. 18, 1981, Pat. No. 4,394,712. Int. Cl.<sup>3</sup> ..... H01L 21/28 [51] [52] 29/589; 29/590; 29/591; 204/15 Field of Search ...... 29/576 J, 580, 589, 29/590, 591; 204/15

References Cited

U.S. PATENT DOCUMENTS

3,259,049 7/1966 Vithoven ...... 204/277 X

3,654,097 4/1972 Degnan ...... 204/15

1/1967 Krasnow ....... 204/15 X

[56]

| [11] | Patent Number:  | 4,499,655     |

|------|-----------------|---------------|

| [45] | Date of Patent: | Feb. 19, 1985 |

| 3,798,136 | 3/1974 | Olsen et al   | 204/26 X |

|-----------|--------|---------------|----------|

| 4,278,511 | 7/1981 | Dugan         | 204/15   |

|           |        | Schachter     |          |

| 4,312,897 | 1/1982 | Reimann       | 204/15 X |

| 4,368,106 | 1/1983 | Anthony       | 204/15   |

|           |        | Anthony       |          |

|           |        | Buckley et al |          |

Primary Examiner—G. Ozaki Attorney, Agent, or Firm—Paul E. Rochford; James C. Davis, Jr.; James Magee, Jr.

#### [57] ABSTRACT

Alignment-enhancing electrically conductive feed-through paths are provided for the high-speed low-loss transfer of electrical signals between integrated circuits of a plurality of silicon-on-sapphire bodies arrayed in a stack. The alignment-enhancing feed-throughs are made by a process of this invention involving the drilling of holes through the body, double-sided sputtering, electroplating, and the filling of the holes with solder by capillary action. The alignment-enhancing feed-throughs are activated by forming a stack of wafers and remelting the solder whereupon the wafers, and the feed-through paths, are pulled into alignment by surface tension forces.

15 Claims, 8 Drawing Figures

FIG.2

FIG. 4

F15-. 7

Fig. B -31 32 <u>30</u> // 33 32 12 <u>30</u> 33

### METHOD FOR MAKING ALIGNMENT-ENHANCING FEED-THROUGH CONDUCTORS FOR STACKABLE SILICON-ON-SAPPHIRE

The invention described herein was made in the performance of work under NASA Contract No. NAS5-25654 and is subject to the provisions of Sec. 305 of the National Aeronautics and Space Act of 1958, (72 Stat. 10 435; 42 U.S.C. 2457).

This application is a division of application Ser. No. 244,854, filed Mar. 18, 1981 now U.S. Pat. No. 4,394,712.

### CROSS-REFERENCE TO RELATED APPLICATIONS

This invention is related to the invention disclosed and claimed in copending U.S. patent application Ser. No. 204,957 entitled "Method of Forming Conductors 20 Through Silicon-on-Sapphire, and Product", filed on Nov. 7, 1980 in the names of inventors Anthony, Connery and Hoeschele, Jr., and to the invention disclosed and claimed in copending U.S. patent application Ser. No. 200,770 entitled "Formation of Electrical Conduc- 25 tors Through Silicon-on-Sapphire", filed on Oct. 27, 1980 in the name of inventor Anthony, now abandoned; both of said copending applications being assigned to the same assignee as the instant application.

#### FIELD OF THE INVENTION

This invention relates generally to the manufacture of semiconductor devices and more particularly to the formation of alignment-enhancing electrically conductive feed-through paths in semiconductor bodies in 35 order to reduce the number and length of conductive interconnections between logic and switching elements in a stacked multiwafer system.

### BACKGROUND OF THE INVENTION

Computer science has developed in an era of computer technology in which wire interconnects were inexpensive and logic and switching elements were expensive. Integrated circuit technology has recently reversed the cost situation leaving wire interconnects as 45 the more expensive component. Interconnections between the integrated circuits of a single chip or wafer, whether made of wires or strips of conducting material, are expensive because they occupy most of the space on the wafer and cause most of the delay in electronic 50 signals passing through the system. The same reasoning holds for interconnections between wafers. Computer architecture theory has just begun to take the cost reversal generated by integrated circuit technology into consideration. As a result, computer design has not yet 55 to the phenomenon of cross-talk. taken advantage of the full range of capabilities implicit in microelectronics.

Current advances in computer design involve the development of a massively parallel information processing system for ultrahigh speed processing of multi- 60 ple digital data streams. Such multiple data streams are encountered in situations where interactions of the physical data are significant as, for example, in image processing and studies of weather conditions, economics, hydrodynamics and stresses. The massively parallel 65 array processor with many processors operating simultaneously and in parallel requires many interconnections between processors. With multiple processors, the

number of interconnections, the space occupied by interconnections, the delay time caused by interconnections, the power consumed in interconnections, and the cost of interconnections has increased as the square of the number of processors in the system.

The massively parallel array processor system is built utilizing Complementary Metal Oxide Semiconductor/-Silicon-on-Sapphire Large Scale Integration (CMOS/-SOS LSI) circuitry. Processor arrays on many individual silicon-on-sapphire wafers must also be interconnected. In current technology, all such interconnections must run out to a pad on the edge of a wafer or chip. Such an interconnection scheme has several disadvantages.

First, the number of interconnection pads on the periphery of an LSI circuit is very limited. The relatively small number of interconnection pads severely restricts the information flow to and from an LSI circuit. For example, a typical memory chip has 16,384 bits arranged in a 128 by 128 array. An entire row of 128 bits can be assessed at one time, but a selector enables only a single bit to pass to an output pin. A typical memory system is made of 2,048 such chips arranged in 64 groups of 32. Only 32 chips can place their outputs on the 32 wires that join the bus to the central processor. Of the 262,144 bits that move less than a millimeter on each chip, only 2,048 move 3 millimeters to get off their chip and only 32 move a meter to the processor. In other words, because of an effective traffic tie-up on the interconnections, only about eight-thousandths of the available density of the memory chip can be used simul-

The second disadvantage of the interconnection scheme used by current technology is that a large fraction of the area of an LSI circuit is devoted to interconnections. This waste of a large area of a chip or a wafer is a direct consequence of the restriction of interconnections to substantially two-dimensional configurations.

Advantageous use of three dimensional configurations has been made in the construction of printed circuit boards. Unfortunately, however, compared to printed circuit boards, semiconductor substrates are brittle single crystals and a large density of small diameter holes having high depth-to-diameter aspect ratios through these brittle substrates would be required to effectively utilize three dimensions. Previous methods of providing conventional conductive paths in three-dimensional configurations by placing the paths in layers on one chip, such as the interconnects between addressing lines in the many x-y crossovers required for large area crossover switches of the type used in communication satellites, have generally resulted in a decrease in the quality of the processed information due primarily

# SUMMARY OF THE INVENTION

In accordance with the present invention, a large number of alignment-enhancing small diameter closelyspaced electrically conductive feed-throughs are introduced through bodies of semiconductor material typically used in information processing equipment. These electrically conductive feed-through paths reduce the number and length of conductive interconnections between logic and switching elements on a single wafer and between the wafers in a stacked multiwafer system thus providing, for example, increased speed and quality of information processing, decreased power require3

ments, and more compact packaging of microelectronic circuits.

In its most general aspects, the method of this invention for making alignment-enhancing feed-throughs comprises the steps of providing a plurality of holes 5 through a body of semiconductor material, depositing a first thin layer of a metal on the internal surfaces of each hole, applying a second thin layer of an electrically conductive metal to the metallized internal surfaces of with a low melting temperature metal, such as solder, by capillary action. The metal of the first layer is one such as gold or nichrome which can be effectively applied to the internal surfaces of the holes by means such als. Electroplating and copper have been found to be an effective method and material, respectively, for the second layer

The alignment-enhancing feed-throughs are activated, and a stacked array is produced, by forming a 20 stack of the wafers and remelting the solder whereupon the wafers, and the feed-through paths, are pulled into final alignment by surface tension forces.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention is more clearly understood from the following description taken in conjunction with the accompanying drawings wherein some details have been disproportionately enlarged for clarity and of which:

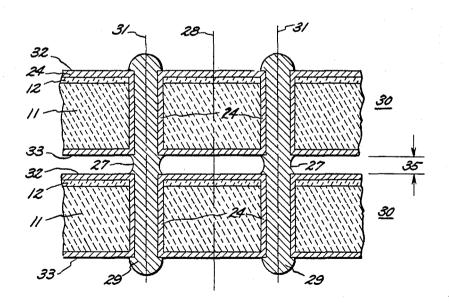

FIG. 1 is a schematic cross section of a typical siliconon-sapphire body.

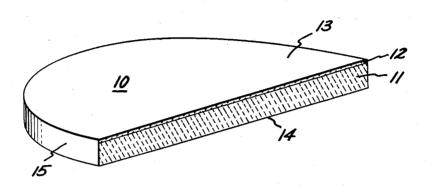

FIG. 2 is an enlarged schematic dimensional view in cross section of a section taken from the silicon-on-sapphire body of FIG. 1 following laser drilling of a square 35 array of holes through the body.

FIG. 3 is a schematic front view in cross section of the silicon-on-sapphire section of FIG. 2 after deposition of the first thin metallic layer.

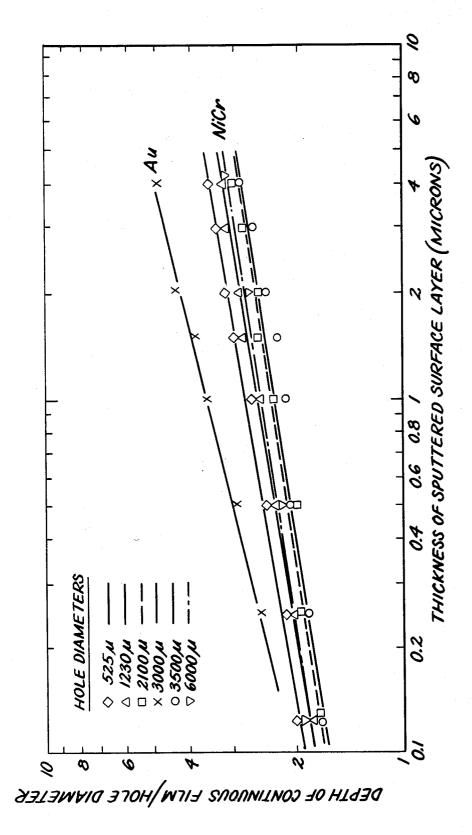

FIG. 4 is a graph of the ratio of the depth to which a 40 continuous film may be sputtered to the hole diameter as a function of the thickness of the surface layer.

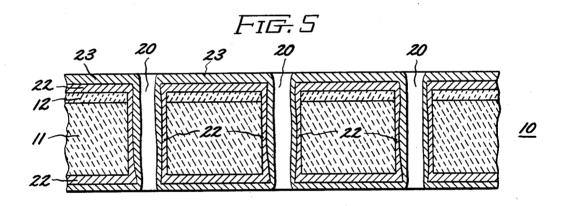

FIG. 5 is a schematic front view of FIG. 3 after deposition of the second thin metallic layer over the first metallic layer.

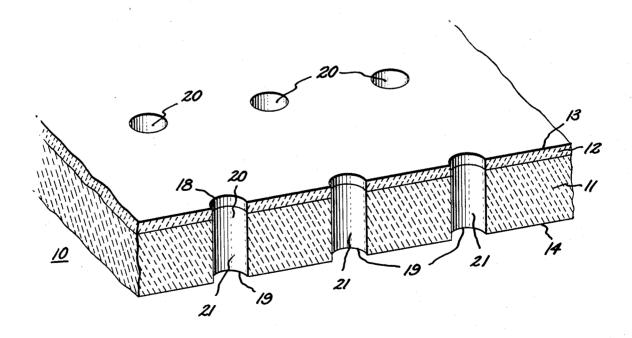

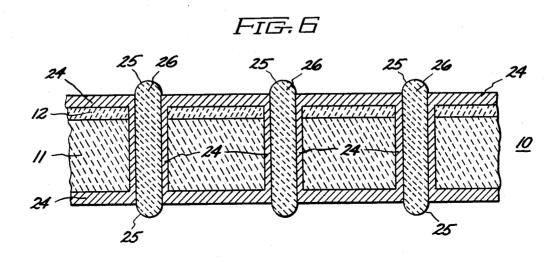

FIG. 6 is a schematic front view in cross section of several completed alignment-enhancing electrically conductive feed-through paths in a stackable silicon-onsapphire wafer.

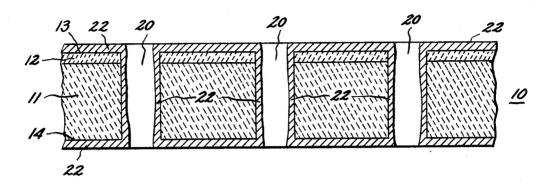

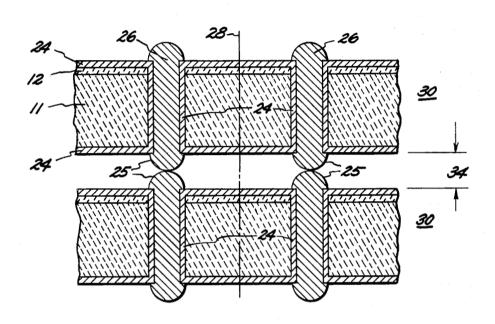

FIG. 7 is a schematic front view in cross section of a 50 stack of two silicon-on-sapphire wafers of FIG. 6 prior to the solder remelt operation.

FIG. 8 is a schematic front view in cross section of the wafers of FIG. 7 in the form of an aligned stacked array following the solder remelt operation.

### DETAILED DESCRIPTION OF THE **INVENTION**

Referring now to FIG. 1, there is shown a body 10 of semiconductor material; illustratively, the body 10 is a 60 typical silicon-on-sapphire (SOS) wafer. The body 10 is a composite of a substrate of single crystal sapphire 11 and a contiguous overlaying epitaxially-grown layer of single crystal silicon 12. The body 10 has front, or top, 13 and back, or bottom, 14 major opposed substantially 65 parallel surfaces and a peripheral edge area 15 interconnecting the front 13 and back 14 major surfaces. The two major surfaces are parallel to the (1102) plane of the

single crystal sapphire 11 to within  $\pm 2^{\circ}$  and to the (100) plane of the single crystal epitaxial silicon 12 to within  $\pm 2^{\circ}$ . The exposed silicon of the front major surface 13 of the wafer is polished to an optical finish smoother than about  $\pm 0.1$  micron and the exposed sapphire of the back major surface 14 of the wafer 10 is ground to a finish smoother than about  $\pm 0.5$  micron. One or more active integrated circuit semiconductor devices are ordinarily located in the silicon layer 12. The thickness each hole, and filling the remaining volume of each hole 10 of the epitaxial silicon layer 12 is typically less than about 4 microns while a typical thickness of the sapphire layer 11 is 325±25 microns.

A plurality of holes 20, as shown in FIG. 2, are provided through SOS wafer 10 preferably using the laser as sputtering and is adherent to semiconductor materi- 15 beam techniques disclosed and claimed in abovereferenced copending application Ser. No. 204,957. Holes provided in accordance with the referenced Ser. No. 204,957 application have apertures 18 and 19 in major surfaces 13 and 14, respectively, and an inner surface 21 interconnecting apertures 18 and 19. Typically, holes 20 have an average diameter of 2.5 mils and are spaced in arrays having center line-to-center line, i.e., axis-to-axis, spacings as small as about twice the

Next, a first metal layer 22, about 1 micron thick is deposited on the inner surfaces 21 of holes 20. Sputtering is the preferred technique and is conducted first with surface 13 and then with surface 14 facing the sputtering source, i.e., double-sided sputtering, to en-30 sure complete coverage of inner surface 21. As shown in FIG. 3, the sputtered material will also be deposited on top 13 and bottom 14 surfaces of the semiconductor body 10. If surface deposits are undesirable in the finished product, surfaces 13 and 14 may be masked, using techniques known to those skilled in the art of semiconductor device manufacture, before the first metal layer 22 is deposited to aid in subsequent removal.

The first layer must, however, form a continuous adherent film on the entirety of inner surfaces 21 and be accessible to electrical contact in order to perform the next step. Gold was found to penetrate further into the holes than nichrome, thereby forming a deeper continuous film, when sputtered into holes having the same diameter. However, nichrome was found to adhere to SOS material better than gold. It was also discovered that sputtering was optimized when conducted in a vacuum such that the mean free path of an atom in the vacuum was greater than or equal to ten times the hole diameter.

Using the optimum vacuum and normal sputtering conditions, it was found that double sided sputtering would effectively place a conducting layer 22 inside holes 20 having diameters greater than or equal to 2 mils through a 13 mil thick SOS wafer (aspect ratio of 6.5:1) using gold and inside holes 20 having diameters greater than or equal to about 3 mils (aspect ratio of 6.3:1) using nichrome. An improvement would be expected using the bias sputtering technique. In a separate related experiment, however, it was surprisingly determined, as shown in FIG. 4, that the depth of the continuous film in the holes was a weak function of the amount of metal sputtered as measured by the thickness of the sputtered layer on surfaces perpendicular to the holes. Thus, there appears to be a practical limit on the aspect ratio of holes that may be coated by sputtering irrespective of the sputtering technique employed.

The electrical resistance of each hole 20 after doublesided sputtering ranged between 10,000 and 30,000

ohms. In order to reduce this resistance a second layer 23, shown in FIG. 5, was electroplated on the sputtered metallized base layer inside holes 20. Copper is a preferred material and a suitable electroplating solution and equipment are described in copending above- 5 referenced application Ser. No. 200,770. The thickness of second layer 23 should be at least about 1 micron, but no more than about 10% of the hole diameter.

Initial attempts to electroplate copper on the inside diameter of the laser-drilled hole by conventional elec- 10 troplating means failed because the copper would preferentially electroplate around the entrance and exit apertures, 18 and 19 of holes 20, sealing the hole leaving acid solution and little electroplated copper in the hole. While manually holding a specimen, it was accidentally 15 discovered that moving the specimen to and fro in the electroplating solution perpendicular to the major surfaces of the wafer 10 at a speed greater than 4 cm/sec and a stroke length of about 8 cm prevented copper from building up at the entrance and exit of the hole. 20 Subsequent analysis showed that the movement of liquid into and out of holes 20 caused erosion of material on the entrance and exit edges of the hole and prevented the build-up of copper electro-deposits in those regions. This erosion kept the entrance and exit of each hole 25 open and allowed an even electroplated copper film to form on the interior of laser drilled holes 20. The resistance of a double-sided sputtered and electroplated hole was on the order of about  $10^{-5}$  ohms.

Occasionally, as will be explained in more detail be- 30 low, it may be desirable to form an elevated rim, termed a relief electroplate, of copper material around the apertures 18 and 19 of holes 20 rising above the plane of surfaces 13 and 14. The relief electroplate is accomplished by stopping the to and fro motion of the wafers 35 in the electroplating bath for a few minutes towards the end of the electroplating operation to allow the formation of the copper rim around the hole apertures by preferential electroplating in those regions.

At this stage in the process, the SOS wafers may be 40 processed, using conventional techniques known to those skilled in the art of semiconductor device manufacture, to provide signal paths between the active devices on the surfaces and the feed-through conductors.

Next, the SOS wafer 10 with the sputtered and elec- 45 troplated materials are floated on a solder bath whereupon solder is drawn into the holes by capillary action since solder wets copper. On withdrawal of the wafer from the solder bath, convex solder menisci 25 are left on both sides of the wafer as shown in FIG. 6. In FIG. 6, layers 22 and 23 have been replaced by a single layer 24 for clarity. The fabrication of the alignment-enhancing feed-through conductors 26 is now complete.

To form an array of CMOS/SOS wafers electrically 55 interconnected by the alignment-enhancing feed-throughs, SOS wafers 30 with solder-filled feedthroughs 26 are next manually stacked and aligned one on top of another. As shown in FIG. 7, for a pair of wafers from such a stack, the solder menisci 25 on ad- 60 joining wafers are thus mated and a gap 34 is formed between any given wafer and the next adjacent wafer. During a brief remelt, capillary forces cause the abutting solder menisci 25 to flow together, effect the final alignment, and form conductive solder bridges 27 be- 65 tween adjacent SOS wafers 30, as shown in FIG. 8. Capillary tension of one million menisci, the number expected for a typical stacked array for the massively

parallel processor, equals a net force of 40 grams which will pull any wafers out of alignment into final alignment during the remelt.

Final gaps 35 are established between wafers in the completed stack by spacers of an inert material or by the previously referred to relief electroplates. Initial gaps 34 and final gaps 35 may be the same. Gaps 35 between wafers should be less than the circumference of the feed-throughs, or else the molten solder bridge 27 between the wafers becomes unstable and may break apart. Thus, for a 3-mil diameter feed-through, the distance between wafers should be less than 9.4 mils (pi times 3). A greater separation distance between wafers can be obtained by giving the copper layer of the feedthroughs a relief electroplate as described above, however, the maximum separation distance between wafers in this case should not exceed two times the relief height plus the circumference of the feedthrough to avoid solder bridge instability.

In a completed stack of semiconductor bodies, which may number in the hundreds for the massively parallel processor, the major surfaces, 32 and 33 as viewed in FIG. 8, of the semiconductor bodies 30 are perpendicular to the axis of the stack 28. A plurality of feedthrough conducting paths 29, which may also number in the hundreds for the massively parallel processor, extend the height, or length, of the stack. These feedthroughs, may be used to transfer electrical signals from any given active device on any given semiconductor body to one or more other active devices on any other semiconductor body, or bodies, or on the same semiconductor body. Due to the alignment-enhancing characteristics of the feed-throughs of this invention, the feedthrough paths and their axes 31 are substantially mutually parallel to each other and to the axis of the stack 28. These feed-throughs have a substantially circular cross section when viewed in a plane oriented perpendicular to axes 31. When the plane is located between the top and bottom major surfaces 32 and 33 of body 30, the circular cross section is composed of three materials. The third, or core, material is the lead tin alloy. Circularly encompassing the core material is the second or electroplated material. A first outermost material circularly encompasses the second and core materials. In the regions between the bodies 30, i.e., between top surfaces 32 and bottom surfaces 33, the circular cross sections are substantially comprised of only the core material.

Although this invention has been described with at the entrance and exit apertures, 18 and 19 of holes 20 50 particular reference to silicon-on-sapphire material, the novel technology and objectives of this invention of preparing a body with alignment-enhancing feedthrough conductors is broadly applicable to other materials of the semiconductor arts including, for example, silicon (Si), germanium (Ge), gallium phosphide (GaP), gallium arsenide (GaAs), indium antimonide (InSb), cadmium telluride (CdTe), and zinc sulfide (ZnS). The invention may also be practiced with insulating materials such as alumina, quartz, glass, and beryllium oxide where such materials, with the alignment-enhancing feed-throughs therethrough, would be necessary or desirable in the stack, in other locations within the processor, or in other electronic applications.

Further, while the invention has been particularly shown and described with reference to several preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and detail may be made therein without departing from the

true spirit and scope of the invention as defined by the appended claims.

I claim as my invention:

1. A process for making alignment-enhancing electrically conductive feed-through conductors in a body 5

comprising the steps of:

(a) providing a stackable semiconductor body, said body having top and bottom major opposed surfaces substantially parallel to each other and an outer peripheral edge area interconnecting said 10 major surfaces:

(b) providing a plurality of holes through said body, each of said holes having apertures lying in said major opposed surfaces and an inner surface inter-

connecting said apertures;

(c) depositing a first thin layer of a first metal onto each of said inner surfaces;

(d) applying a second thin layer of a second metal over each of said first thin layers; and

- (e) filling the remaining hole volume with a third 20 metal forming thereby an alignment-enhancing electrically conductive feedthrough in a stackable semiconductor body.

- 2. The process of claim 1 further including the process steps of:

(1) forming a stack of the stackable bodies and

- (2) remelting said third metal, forming thereby a stacked self-aligned array of the bodies, said bodies having a plurality of electrically conductive paths communicating therebetween.

- 3. The process of claim 2 wherein said third metal is a lead-tin alloy.

- 4. The process of claim 2 wherein said remelting is accomplished by heating said stack to a temperature sufficient to cause melting of said third metal.

- 5. The process of claim 1 wherein said body is composed of a single material, said single material being one selected from the group consisting of silicon, germa-

nium, gallium arsenide, gallium phosphide, indium antimonide, cadmium telluride, and zinc sulfide.

- 6. The process of claim 1 wherein said body is a composite, said body having a single crystal sapphire substrate and a contiguous overlaying epitaxially-grown layer of single crystal silicon, said top major surface being the exposed surface of said silicon layer, said bottom major surface being the exposed surface of said sapphire substrate and said outer peripheral edge area encompassing both said sapphire substrate and said layer of silicon.

- 7. The process of claim 1 wherein said body is composed of an insulating material, said insulating material being one selected from the group consisting of alumina, quartz, glass and beryllium oxide.

- 8. The process of claim 1 wherein said holes are provided by a laser drilling process.

- 9. The process of claim 1 wherein said first metal is gold.

- 10. The process of claim 1 wherein said first metal is nichrome.

- 11. The process of claim 1 wherein said first thin layer is deposited by sputtering.

- 12. The process of claim 1 wherein said second thin layer is applied by an electrodeposition process.

- 13. The process of claim 12 wherein said electrodeposition process includes agitation of said body substantially perpendicular to said major surfaces during said 30 electrodeposition process.

- 14. The process of claim 1 wherein the metal of said second thin layer is copper.

- 15. The process of claim 14 further including the process step of arresting said agitation prior to comple-35 tion of said electrodeposition process for a time sufficient to cause a relief electroplate of predetermined height to form.

# 50

# 55