# Microspring Characterization and Flip-Chip Assembly Reliability

Bowen Cheng, Dirk De Bruyker, Chris Chua, Kunal Sahasrabuddhe, Ivan Shubin, John E. Cunningham, Ying Luo, Karl F. Böhringer, *Fellow, IEEE*, Ashok V. Krishnamoorthy, *Fellow, IEEE*, and Eugene M. Chow, *Senior Member, IEEE*

Abstract—Electronics packaging based on stress-engineered spring interconnects has the potential to enable integrated IC testing, fine pitch, and compliance not readily available with other technologies. We describe new spring contacts which simultaneously achieve low resistance (< 100 m $\Omega$ ) and high compliance (> 30  $\mu$ m) in dense 2-D arrays (180  $\sim$  180- $\mu$ m pitch). Mechanical characterization shows that individual springs operate at approximately 150- $\mu$ N force. Electrical measurements and simulations imply that the interface contact resistance contribution to a single contact resistance is  $< 40 \text{ m}\Omega$ . A daisy-chain test die consisting of 2844 contacts is assembled into flip-chip packages with 100% yield. Thermocycle and humidity testing suggest that packages with or without underfill can have stable resistance values and no glitches through over 1000 thermocycles or 6000 h of humidity. This paper suggests that integrated testing and packaging can be performed with the springs, enabling new capabilities for markets such as multichip modules.

*Index Terms*—Flip chip packaging, MEMS, package reliability, springs, testing.

## I. INTRODUCTION

OLDER bonding is the dominant method of interconnecting for electronics, but suffers from inherent problems such as brittleness and high-temperature assembly. Current commercial flip-chip interconnects, such as solder balls, gold bumps, and conductive adhesives, all have very limited compliance, making it difficult to compensate for the large thermal expansion mismatches typically existing in packages. Other challenges for flip-chip include scaling to fine pitch and small gaps—important for enabling ever smaller system-in-packages

Manuscript received October 8, 2010; revised January 25, 2011; accepted June 29, 2012. Date of publication December 28, 2012; date of current version January 31, 2013. This work was supported in part by the Defense Advanced Research Projects Agency (DARPA) under Agreement HR0011-08-09-0001. Recommended for publication by Associate Editor K.-N. Chiang upon evaluation of reviewers' comments.

- B. Cheng is with the Palo Alto Research Center, Palo Alto, CA 94304 USA, and also with the Electrical Engineering Department, University of Washington, Seattle, WA 98195 USA (e-mail: bcheng@parc.com).

- D. De Bruyker, C. Chua, K. Sahasrabuddhe, and E. M. Chow are with the Palo Alto Research Center, Palo Alto, CA 94304 USA (e-mail: dirk. debruyker@parc.com; christopher.chua@parc.com; kunalsahasrabuddhe@gmail.com; eugene.chow@parc.com).

- I. Shubin, J. E. Cunningham, Y. Luo, and A. V. Krishnamoorthy are with Oracle Labs, San Diego, CA 92121 USA (e-mail: ivan.shubin@oracle.com; john.cunningham@oracle.com; ying.luo@sun.com; ashok.krishnamoorthy@oracle.com).

- K. F. Böhringer is with the Electrical Engineering Department, University of Washington, Seattle, WA 98195 USA (e-mail: karlb@washington.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCPMT.2012.2213250

(SIPs). Currently, complex multidie packages are rare because of testing and the challenges of obtaining known good dies.

We are developing compliant thin film interconnects that have the potential to dramatically improve IC flip-chip packaging. They can absorb large thermal expansion mismatches between silicon chips and substrates, simplifying packaging design, as current solder-based approaches are not flexible. The high stresses of lead-free solder on organic boards can be avoided, facilitating integration of fragile low-k dielectrics. If the compliant interconnect enables bare die testing, then integrating at-speed testing of chips before bonding to a final substrate is possible, alleviating the need for an expensive known good die. Such capability can reduce the cost of multichip module (MCM) and SIP solutions by enabling both testing and packaging functions.

Other approaches for building a compliant interconnect include compliant layers under the solder [1], metalization over organic elastomers [2], [3], plated wirebonds [4], bent printed circuit board (PCB) metal [5], and machined bulk metal for land grid array (LGA). The use of compliant layers under the solder is established for memory packaging, but does not improve integrated testing for MCM (no rework) and is not low-profile. The wire-bond approach, because of its serial manufacturing process, is inherently more expensive than a batch process. The metalized elastomer requires more complicated fabrication than the stress-engineered approach presented here. The bent PCB metal has been recently commercialized and the LGA well established for sockets, but both are of millimeter scale and not readily scalable because of the use of thick films.

In contrast, the stress-engineered spring approach presented here has a wide mechanical and electrical design range and has been demonstrated down to high-density interconnect regimes. For flip-chip packaging, multiple packages have been demonstrated. Silicon dies with large springs (>500  $\mu$ m pitch) have been assembled directly on organic substrates [6]. Because they are photolithographically defined, stress-engineered springs can offer tighter pitches than other compliant packaging approaches such as polymer bumps [2] or plated wire bonds [4]. Dense linear arrays of stress-engineered springs at both 20- $\mu$ m [7] and 6- $\mu$ m pitch [8] have been assembled into flip-chip packages. Previous stress-engineered springs have been designed for probe cards for probing aluminum pads [9] and can achieve many grams of force (tens of mN). The stress-engineered spring process inherently includes redistribution,

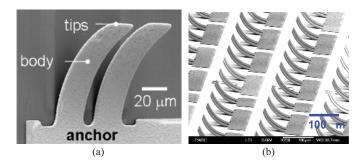

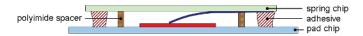

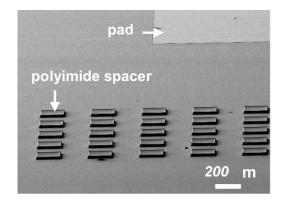

Fig. 1. SEM image of a (a) contact and (b) 2-D array contacts.

as the spring metal layers are also traces, which reduces the overall system cost. The fabrication process is a thin-film metallization process that is compatible with complimentary metal-oxide-semiconductor (CMOS) or backend wafer-scale packaging. The manufacturing cost of the process has been modeled and found to be similar to that of solder.

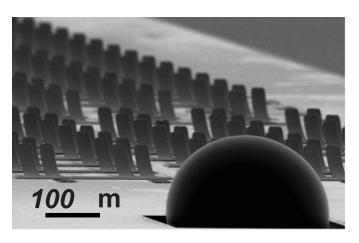

This paper describes a new stress-engineered contact design for dense 2-D array applications such as processors. An important future application of such contact design is in the construction of 2.5-D assemblies of chips where large vertical clearance and rematability are important for constructing tightly coupled multichip computing systems [10]. The springs achieve low resistance ( $< 100 \text{ m}\Omega$ ), high compliance (>30  $\mu$ m), and high yield for 2-D arrays (thousands of contacts,  $180 \times 180 \ \mu m$  pitch). In Section II, the spring fabrication and yield are described. Section III summarizes the mechanical and electrical characterization of a single spring. Simulations are used to estimate the interface contact resistance ( $<40 \text{ m}\Omega$ ). In Sections IV and V, various package assemblies and their reliability testing are described. Air-gap packages using spacer layers or self-aligning ball-and-pit [11], [12] mechanisms are described, as well as packages with springs embedded in adhesive.

# II. SPRING FABRICATION

The microsprings are fabricated with stress-engineered thin-film processing. The key step is the deposition of a  $1-\mu m$ thick alloy of molybdenum-chromium with a large stress gradient (GPa per  $\mu$ m). After being lithographically patterned into cantilever beams (100- $\mu$ m long, 30- $\mu$ m wide) and subsequently released, the spring stress relaxes, lifting the tips out of the plane, forming a 3-D-compliant spring interconnect. Extra metal such as gold can be electrodeposited after the release to provide conductivity and strength. Fig. 1 shows a close-up of a contact, consisting of two springs in parallel and 2-D array contacts. The fabrication process uses 4-in waferscale processing and requires only two masks. Routing and redistribution can be performed without extra masks by using traces that are not released. The process is a low-temperature one and has been integrated at the wafer scale onto post-CMOS devices [13]. See [14] for other fabrication details.

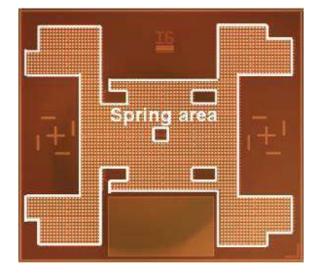

The spring process is uniform and of high yield. A key parameter is the lift-height, defined as the vertical distance of the tip above the substrate. Each test chip is  $14 \times 16$  mm and has 2844 contacts (Fig. 2). A commercially available

Fig. 2. Spring chip die with 2844 contacts and an area of  $14 \times 16$  mm.

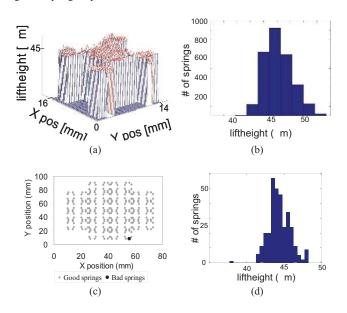

Fig. 3. Spring lift-height uniformity measurements. (a) and (b) Across a chip of 2844 contacts. (c) and (d) Across a wafer.

tool (Nikon VMR-3020) is used to automatically measure the lift-heights using pattern recognition. The repeatability of the measurement technique is  $\pm 3~\mu m$ . Measurements of each spring in the chip give an average height of  $\sim 45~\mu m$ , with a variation equal to or less than the measurement error [Fig. 3(a) and (b)]. Measurements across a 4-in wafer give similar results [Fig. 3(c) and (d)]. Out of 319 measured springs spaced evenly across the wafer, only one spring on the wafer edge (black dot) is outside of 42–48  $\mu m$  range (the measurement error is  $\pm 3~\mu m$ ). Release yields above 99.9% have been demonstrated (based on  $\sim 10^5$  springs per wafer), and 100% yield has been achieved for more than half of the 20 dies per wafer in our research prototype facility.

## III. SINGLE SPRING CHARACTERISTICS

Chips consisting of single spring test structures are used to measure the mechanical and electrical properties of a single

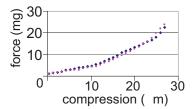

Fig. 4. Measured force of a single spring. Two measurements are shown.

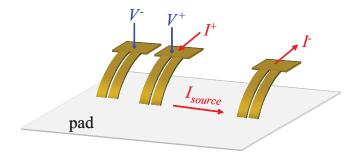

Fig. 5. Four-wire resistance measurement of a contact (middle contact).  $I_{\text{source}}$  is forced from  $I^+$  to  $I^-$ , electrical potential drop  $V_{\text{sense}}(V^+ - V^-)$  is monitored during compression. Electrical resistance of the middle contact is  $V_{\text{sense}}/I_{\text{source}}$ .

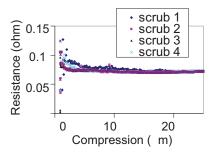

Fig. 6. Four-wire resistance monitored while the spring is compressed. The plateau value is  ${\sim}72~\text{m}\Omega.$

spring. The measured force versus compression of a spring is directly measured by a force scale (see [15] for setup description). Fig. 4 shows that the force curve is repeatable as the spring is repeatedly compressed to just under 30  $\mu$ m. After full compression, a negligible change in the lift-height is observed. This suggests that the spring is operating below the yield point threshold for plastic deformation. A typical compression in a package is 25  $\mu$ m, corresponding to a compressive force of 0.015 g (150  $\mu$ N). While this force is significantly less than in macroscopic pressure contacts, the pressure is similar (~15 MPa, see [16] and therefore, we believe, is adequate for gold-to-gold pressure contacts. Note that microscale gold pressure contacts have already been commercialized as RF microelectromechanical systems switches, showing that there are no fundamental barriers to high reliability [17].

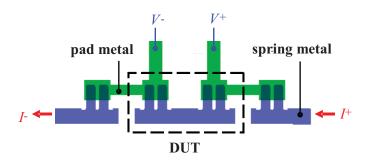

A resistance test structure is measured and modeled to study the resistance constituents. A single contact (two-spring) device in a four-wire configuration is measured as a function of compression (Fig. 5). Fig. 6 shows a typical measurement versus spring compression against a large gold pad. The resistance reaches a plateau of  $\sim 70~\text{m}\Omega$  when compressed

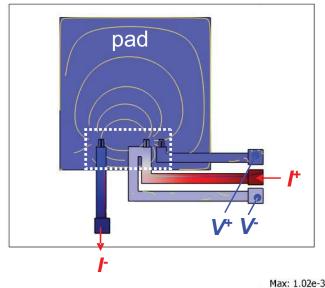

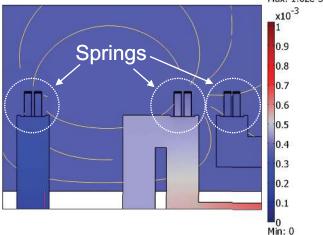

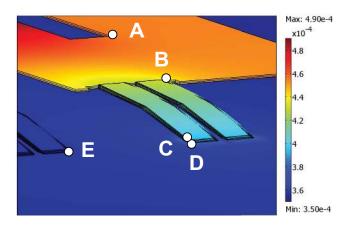

Fig. 7. Electrical potential with current density arrows of single-contact four-wire resistance test structure. Constant current  $I_{\text{source}}$  is forced from  $I^+$  to  $I^-$  and potential drop  $V_{\text{sense}}$  ( $V^+ - V^-$ ) is calculated.

by 10–20  $\mu$ m. Finite element modeling (FEM) was used to study the resistance components of the test structure. Using the commercial software COMSOL, a geometric model was constructed. The electrical potential distribution of the entire structure was calculated by setting Isource (1 mA) and calculating  $V_{\text{sense}}$  (Fig. 7). The simulated total resistance value equals  $V_{\text{source}}/I_{\text{source}}$ . Several potential drops contribute to  $V_{\rm sense}$ , including the lead traces, spring body, tip-pad interface, and pad spreading (Fig. 8). All of them are defined as effective resistance components that contribute to total measured resistance ( $V_{\text{source}}/I_{\text{source}}$ ). FEM was used to determine all of these components based on measured sheet resistance and geometric values, except for the tip-pad resistance. The tippad interface resistance physically consists of asperities and constriction resistance. While models for this resistance exist [18], they require assumptions concerning multiple variables, such as the effective contact area, asperity dimensions, and local conductivity. We, instead, modeled the tip-pad interface resistance as a simple resistor and swept the value of this resistor to fit the total measured resistance.

Fig. 8. Electrical potential distribution of the middle contact. Measured  $V_{\rm sense}$  equals  $V_{\rm A-E}$ , and is composed of effective lead trace  $V_{\rm A-B}$ , spring body  $V_{\rm B-C}$ , tip-pad interface  $V_{\rm C-D}$ , and pad spreading  $V_{\rm D-E}$ .

TABLE I

RESISTANCE COMPONENTS OF ONE CONTACT

| Resistance component                   | Value (mΩ) |

|----------------------------------------|------------|

| Lead trace $R_{A-B}$                   | 23         |

| Spring body R <sub>B-C</sub>           | 36         |

| Tip-pad R <sub>C-D</sub>               | 11–41      |

| Pad spreading resistance $R_{\rm D-E}$ | ~ 0        |

| Total                                  | 70–100     |

Total measured resistances of  $70\text{--}100~\text{m}\Omega$  were observed, which were used for estimating the range of the resistance components based on the above FEM analysis. Table I shows that 16%--41% of the resistance is due to the tip-pad interface. This is an estimate of the low resistance limit for a gold-gold pressure contact with this contact area and force (11–41 m $\Omega$ ). This is similar to other reported values [18]. The spring body contributes another third of the resistance. This value can be lowered by changing the spring dimensions. For example, if a smaller lift-height or compliance is required, then the spring can be shorter. The trace resistance contributes 23%–33%. This routing exists to enable the measurement, and would be much less for the typical case of a spring on via (with no routing). The spreading resistance was found to be almost negligible.

## IV. PACKAGE ASSEMBLY

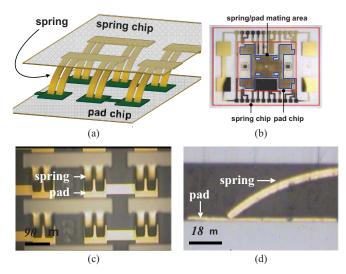

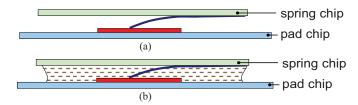

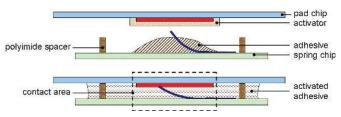

To study the reliability and packaging options, flip-chip packages were assembled by placing a chip with springs (see Fig. 9) onto the corresponding metal pads on another chip (pad chip) using a variety of approaches. Generally, two types of packages were built: springs in air, and springs embedded in adhesive (Fig. 10). Other important parameters include how the gap between the chips is controlled and the bonding method. The gap should ensure that the springs are compressed by more than 15  $\mu$ m to operate in the resistance plateau region (Fig. 6). For springs with initial lift-heights of 45  $\mu$ m, our target gap was 20  $\mu$ m, corresponding to a 25- $\mu$ m compression. The gap was defined by using a polyimide spacer wall on the pad chip, a precise ball-and-pit scheme [19], or precision assembly. The bonding methods

Fig. 9. (a) Schematic of a flip-chip package with aligned springs and pads. (b) Top view and (c) close-up of a glass-on-glass package with 2844 springs landing on 2844 pads in spring/pad mating area. (d) Cross section of a silicon-on-silicon flip-chip package. Note that the slight delamination of the pad in this picture is caused by the cross-sectioning procedure; such defects have never been observed in actual packages (as inspected visually for glass packages, and with infrared imaging for silicon packages).

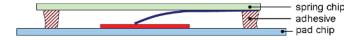

Fig. 10. Schematic of two package types. (a) Spring and contact are in air. (b) Springs embedded in adhesive.

used are adhesive on the edges/corners, at the corners only, all along the edges, or everywhere (Loctite 352 adhesive). Note that, for the last case, the adhesive can be applied onto the spring chip before assembly, or after assembly by wicking from the edges. An activator can be mixed with the adhesive for curing, or UV cure can be used for the adhesive on the edges. Note that the spring and pad substrates are either silicon or glass. Glass substrates aid inspection during development and have the same thermal expansion coefficient as silicon.

The relative merits of each assembly approach depend on the application requirements. Chips in air are easier to rework. In previous work, we have shown springs in air with no adhesive, as they are bonded through a clamping mechanism [19]. Such an approach can be appropriate for large high-end MCMs, where easy rework is particularly important. Springs in adhesive can have lower profiles (no clamp on top) and have extra protection from the environment. These cannot be readily reworked, but at-speed testing can be performed before bonding. Gap control based on a spacer layer is substrate-independent, while the ball-and-pit approach requires silicon substrates.

## V. PACKAGE TESTING

Thermocycle testing consisted of cycling between 0  $^{\circ}$ C and 100  $^{\circ}$ C with 10 min dwells and 10 min rise and fall

| Package | Springs  | Adhesive                      | Gap Stop     | Humidity<br>(hours) | Thermocycle (cycles) | Resistance                   | Pre-scrubs |

|---------|----------|-------------------------------|--------------|---------------------|----------------------|------------------------------|------------|

| A       | In Air   | Edges and corners             | Spacer layer |                     | 1017                 | +/-15%                       | NO         |

| C       | In Air   | Edges and corners             | NONE         | 6474                |                      | Mostly increasing, submerged | NO         |

| D       | In Air   | Perimeter                     | Balls/pits   | 2347                |                      | Decreasing                   | YES        |

| E       | Embedded | Pre-mixed activator           | Spacer layer |                     | 1082                 | Mostly decreasing            | NO         |

| G       | Embedded | Underfill pre-mixed activator | Spacer layer |                     | 1112                 | Stable or decreasing         | NO         |

| Н       | Embedded | Pre-mixed activator           | Spacer layer | 7746                |                      | Stable or decreasing         | NO         |

TABLE II

SUMMARY OF PACKAGE RELIABILITY TESTS

Fig. 11.  $I_{\text{source}}$  forced from  $I^+$  to  $I^-$  and electrical potential drop  $V_{\text{sense}}(V^+ - V^-)$  measured. Device under test (DUT) resistance equals  $V_{\text{sense}}/I_{\text{source}}$ .

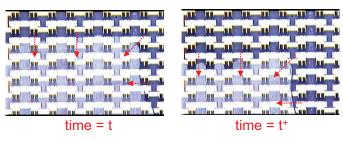

times in an oven (Sigma Systems, model M18). The packages inside the thermocycle oven were wired to an event detector so that any momentary resistance increase in any one of the 2844 contacts of longer than 200 ns was detected as a glitch. For humidity testing, the packages were stored in an oven (Espec, SH-241) at 85 °C, 85% RH. Periodically, the packages were removed from the thermocycle and humidity chambers and four-wire resistance measurements of the daisy chains were taken (Fig. 11). The measured resistance is composed of the spring resistance (body, tip-pad interface, spreading) and significant amounts of spring trace and pad trace. These measurements used an automated pogopin setup which had a system repeatability of approximately  $\pm 5\%$ , corresponding to  $\pm 10$ –20 m $\Omega$  for the two spring contact chains. Table II summarizes the reliability testing. None of the packages showed glitches during thermocyling. The majority of resistances were stable or decreased from initial values through over >1000 thermocycles and 2000–6500 h in humidity. No increases over 15% the nominal stable value for a chain were observed, unless noted by an obvious defect.

Within the air-gap packages, the resistance tends to decrease during testing if pre-scrubs are performed (see Package C). For pre-scrubbing, the die was compressed until the gap was less than 20  $\mu$ m, fully retracted, and then repeated five times before bonding. We believe this helps to clean the tips and pads as well as increase the effective contact area. Note that prescrubbing is commonly used for probe cards. Separate mate

TABLE III

PACKAGE A THERMOCYCLING MEASUREMENTS

| Number of Contacts | Four-W  | ire Resistano | e, ohms        | %      |

|--------------------|---------|---------------|----------------|--------|

| in a Daisy Chain   | Initial | 680<br>Cycles | 1017<br>Cycles | Change |

| 2                  | 0.155   | 0.148         | 0.166          | 6.7    |

| 2                  | 0.169   | 0.157         | 0.190          | 12.2   |

| 2                  | 0.214   | 0.176         | 0.182          | -15.0  |

| 2                  | 0.180   | 0.153         | 0.165          | -8.0   |

| 2                  | 0.168   | 0.162         | 0.186          | 10.6   |

| 2                  | 0.165   | 0.153         | 0.174          | 5.5    |

| 2                  | 0.143   | 0.124         | 0.121          | -14.8  |

| 2                  | 0.128   | 0.112         | 0.126          | -1.9   |

| 2                  | 0.106   | 0.103         | 0.120          | 13.5   |

| 2                  | 0.117   | 0.118         | 0.115          | -1.2   |

| 134                | 0.259   | 0.247         | 0.271          | 4.5    |

| 134                | 0.257   | 0.246         | 0.281          | 9.2    |

| 246                | 0.286   | 0.272         | 0.300          | 4.9    |

| 246                | 0.278   | 0.267         | 0.293          | 5.4    |

| 384                | 0.305   | 0.253         | 0.271          | -11.1  |

| 384                | 0.253   | 0.239         | 0.256          | 1.1    |

| 530                | 0.270   | 0.249         | 0.257          | -4.6   |

| 530                | 0.253   | 0.245         | 0.260          | 2.7    |

Total 2608

and remate tests show that scrubbing can reduce the resistances by 5%–20%. Air gap packages with the pre-scrubs more consistently show resistance decreases with time, possibly caused by an annealing of the interface contact or increase in the effective contact area during cycling. Slight reductions in resistance with time are typical for gold-to-gold contacts [20]. Thermocycle data for a package similar to Package C is reported in [19], and shows similar results.

For the springs embedded in adhesive, very stable or decreasing resistance values are observed for both thermocycle and humidity testing. The package that is underfilled after assembly (E) shows stable or decreasing resistance values. These packages do not have pre-scrubs. Performing prescrubs might reduce the initial resistance values and improve reliability.

TABLE IV

PACKAGE B HUMIDITY MEASUREMENTS

| Contacts Per | Four    | %          |            |        |

|--------------|---------|------------|------------|--------|

| Chain        | Initial | 1015 Hours | 6474 Hours | Change |

| 2            | 0.405   | 0.420      | 0.448      | 10.8   |

| 2            | 0.418   | 0.419      | 0.459      | 9.9    |

| 2*           | 0.097   | 0.100      | 0.129      | 33.4   |

| 2            | 0.386   | 0.391      | 0.418      | 8.3    |

| 2            | 0.416   | 0.410      | 0.407      | -2.2   |

| 2            | 0.407   | 0.407      | 0.406      | -0.2   |

| 2**          | 0.310   | 0.345      | 0.401      | 29.4   |

| 2            | 0.357   | 0.366      | 0.407      | 14.2   |

| 2            | 0.307   | 0.312      | 0.317      | 3.3    |

| 2            | 0.360   | 0.379      | 0.392      | 9.0    |

| 132          | 40.448  | 41.252     | 43.118     | 6.6    |

| 132          | 38.554  | 39.707     | 38.602     | 0.1    |

| 246          | 82.412  | 84.219     | 88.270     | 7.1    |

| 246          | 77.789  | 79.157     | 78.930     | 1.5    |

| 384          | 108.800 | 113.265    | 119.071    | 9.4    |

| 384          | 109.931 | 109.782    | 113.748    | 3.5    |

| 530          | 152.799 | 157.965    | 161.965    | 6.0    |

| 530          | 159.962 | 161.684    | 159.326    | -0.4   |

<sup>\*</sup>Chain resistance is low initially, due to suspected electrical short.

TABLE V

PACKAGE C HUMIDITY MEASUREMENTS

| <b>Contacts Per</b> | Four    | Four-Wire Resistance, ohms |            |             |  |  |

|---------------------|---------|----------------------------|------------|-------------|--|--|

| Chain               | Initial | 909 Hours                  | 2347 Hours |             |  |  |

| 2                   | 0.352   | 0.349                      | 0.352      | 0.1         |  |  |

| 2                   | 0.367   | 0.358                      | 0.360      | -1.9        |  |  |

| 2                   | 0.351   | 0.347                      | 0.347      | -1.1        |  |  |

| 2                   | 0.371   | 0.356                      | 0.355      | <b>-4.7</b> |  |  |

| 2                   | 0.388   | 0.368                      | 0.365      | -6.4        |  |  |

| 2                   | 0.390   | 0.366                      | 0.363      | -7.3        |  |  |

| 2*                  | 0.234   | 0.242                      | 0.263      | 10.8        |  |  |

| 2                   | 0.243   | 0.245                      | 0.245      | 0.7         |  |  |

| 2                   | 0.262   | 0.251                      | 0.247      | -6.0        |  |  |

| 2*                  | 0.258   | 0.271                      | 0.283      | 8.8         |  |  |

| 134                 | 46.012  | 44.551                     | 44.359     | -3.7        |  |  |

| 134                 | 46.597  | 44.587                     | 44.301     | -5.2        |  |  |

| 246                 | 90.377  | 89.284                     | 89.090     | -1.4        |  |  |

| 246                 | 93.151  | 90.352                     | 89.807     | -3.7        |  |  |

| 384                 | 128.603 | 127.055                    | 127.238    | -1.1        |  |  |

| 384                 | 132.793 | 127.651                    | 127.068    | -4.5        |  |  |

| 530                 | 177.211 | 177.477                    | 178.036    | 0.5         |  |  |

| 530                 | 185.669 | 180.171                    | 179.276    | -3.6        |  |  |

\*Chains increasing; suspected gap issue because both on corner of package.

$\label{eq:table_vi} \textbf{TABLE VI}$  Package D Thermocycle Measurements

| Contacts Per | Four    | %                      |         |        |

|--------------|---------|------------------------|---------|--------|

| Chain        | Initial | 435 Cycles 1082 Cycles |         | Change |

| 2            | 0.232   | 0.222                  | 0.217   | -6.5   |

| 2            | 0.232   | 0.233                  | 0.226   | -2.7   |

| 2            | 0.240   | 0.255                  | 0.247   | 2.8    |

| 2            | 0.230   | 0.247                  | 0.246   | 6.9    |

| 2            | 0.230   | 0.219                  | 0.216   | -6.1   |

| 2            | 0.236   | 0.222                  | 0.214   | -9.2   |

| 2            | 0.191   | 0.189                  | 0.201   | 5.3    |

| 2            | 0.206   | 0.190                  | 0.190   | -7.9   |

| 2            | 0.189   | 0.178                  | 0.177   | -6.3   |

| 2            | 0.194   | 0.198                  | 0.193   | -0.8   |

| 134          | 29.303  | 28.243                 | 28.135  | -4.0   |

| 134          | 29.579  | 28.474                 | 28.240  | -4.5   |

| 246          | 60.408  | 58.821                 | 58.705  | -2.8   |

| 246          | 60.539  | 58.866                 | 58.658  | -3.1   |

| 384          | 87.527  | 85.201                 | 84.465  | -3.5   |

| 384          | 87.801  | 86.363                 | 86.353  | -1.6   |

| 530          | 116.468 | 113.676                | 113.717 | -2.4   |

| 530          | 119.233 | 115.577                | 114.736 | -3.8   |

Total 2608

TABLE VII

PACKAGE E THERMOCYCLE MEASUREMENTS

| Contact Per | Four    | Four-Wire Resistance, ohms |             |             |  |  |

|-------------|---------|----------------------------|-------------|-------------|--|--|

| Chain       | Initial | 322 Cycles                 | 1112 Cycles |             |  |  |

| 2           | 0.238   | 0.230                      | 0.228       | -4.1        |  |  |

| 2           | 0.233   | 0.229                      | 0.228       | -2.2        |  |  |

| 2           | 0.220   | 0.218                      | 0.215       | -2.4        |  |  |

| 2           | 0.229   | 0.227                      | 0.225       | -2.1        |  |  |

| 2           | 0.238   | 0.228                      | 0.228       | -4.3        |  |  |

| 2           | 0.242   | 0.227                      | 0.225       | <b>-6.7</b> |  |  |

| 2*          | 0.181   | 0.173                      | 0.201       | 11.0        |  |  |

| 2           | 0.173   | 0.164                      | 0.162       | -6.5        |  |  |

| 2           | 0.165   | 0.159                      | 0.157       | -5.2        |  |  |

| 2           | 0.171   | 0.182                      | 0.172       | 0.8         |  |  |

| 134         | 28.836  | 28.066                     | 27.848      | -3.4        |  |  |

| 134         | 29.022  | 28.269                     | 28.051      | -3.3        |  |  |

| 246         | 59.129  | 57.584                     | 57.054      | -3.5        |  |  |

| 246         | 59.777  | 57.961                     | 57.408      | -4.0        |  |  |

| 384         | 82.418  | 82.069                     | 81.327      | -1.3        |  |  |

| 384         | 78.453  | 78.585                     | 77.799      | -0.8        |  |  |

| 530         | 117.680 | 113.601                    | 113.111     | -3.9        |  |  |

| 530         | 117.205 | 114.195                    | 115.975     | -1.0        |  |  |

| Total 2608  |         |                            |             |             |  |  |

<sup>\*</sup>Chain had a bubble contacting springs, caused by insufficient underfill supply.

Detailed reliability results for packages with springs in air and springs embedded in adhesive are given in Tables III–VIII. All four-wire measurements of contacts are reported for each

package (2608 total). In general, the initial uniformity of the measurements within each contact chain type (highlighted) is less than 5% within a package. Variations between packages

<sup>\*\*</sup>Chain increase cause unknown, though possibly water related as packages was accidentally submerged in water and then subsequently dried.

TABLE VIII

PACKAGE F THERMOCYCLE MEASUREMENTS. PACKAGE F HAS

UNSTABLE INITIAL RESISTANCE VALUES. THEREFORE % CHANGE

IS CALCULATED BETWEEN 160 h AND 7746 h

| Contacts Per | Four     | %          |                       |       |

|--------------|----------|------------|-----------------------|-------|

| Chain        | Initial  | 160 Cycles | 60 Cycles 7746 Cycles |       |

| 2            | 0.364    | 0.357      | 0.348                 | -2.7  |

| 2            | 0.356    | 0.361      | 0.359                 | -0.4  |

| 2            | 0.365    | 0.371      | 0.36                  | -2.9  |

| 2            | 0.375    | 0.37       | 0.359                 | -2.9  |

| 2            | 0.146    | 0.374      | 0.36                  | -3.7  |

| 2            | 0.344    | 0.275      | 0.285                 | 3.7   |

| 2            | 0.353    | 0.344      | 0.277                 | -19.4 |

| 2            | 0.258    | 0.262      | 0.248                 | -5.5  |

| 2            | 0.18     | 0.293      | 0.282                 | -3.7  |

| 134          | 44.753   | 44.406     | 43.434                | -2.2  |

| 134          | 44.495   | 44.229     | 43.211                | -2.3  |

| 246          | 90.561   | 93.858     | 89.506                | -4.6  |

| 246          | 90.511   | 98.071     | 90.528                | -7.7  |

| 384          | 127.219  | 128.525    | 125.921               | -2    |

| 384          | 128.287  | 129.145    | 126.373               | -2.1  |

| 530          | 177.553  | 175.475    | 172.228               | -1.9  |

| 530          | 7799.544 | 180.266    | 176.815               | -1.9  |

Total 2608

Fig. 12. Schematic of assembled Package A.

Fig. 13. SEM image of the polyimide spacer.

Fig. 14. Schematic of assembled Package B.

are attributed to variations between the spring trace and pad trace metal thickness, as pad chips and spring chips are from different fabrication process runs.

Certain chains with relatively high resistance are denoted with asterisks. Inspections show that most are caused by clear assembly or spring fabrication defects, such as particles near

Fig. 15. Schematic of assembled Package C.

Fig. 16. SEM image of balls/pits with springs [19].

Fig. 17. Adhesive near the contacts of Package D cured by activator and edges cured by UV light.

Fig. 18. Schematic of Package E.

the spring tips, lithography defects, or air bubbles in the case of adhesive. It is important to avoid these defects, as during assembly process development it is observed that these defects can also cause clear failures such as large resistance increases or opens.

## 1) Air-Gap Package (Thermocycle):

Package A: Package gap is defined by a lithographically defined polyimide spacer. The Loctite 352 adhesive holds the spring and pad chips together after UV curing. The adhesive is applied at four corners of the chip, see Figs. 12 and 13.

## 2) Air-Gap Package (Humidity):

Package B: Package gap control is performed by a precision flip-chip assembler. The Loctite 352 adhesive holds the spring and pad chips together after UV curing, see Fig. 14.

Package C: Package gap is defined by self-aligned balls and pits. Loctite 352 on edges holds the spring and pad chips together after UV curing (Figs. 15 and 16).

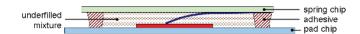

## 3) Embedded Package (Thermocycles):

Package D: Package gap is defined by polyimide spacer. Contact area is cured by Loctite 352 which is activated/cured

## underfill front direction

Fig. 19. Image of Package E during underfill. Capillary force pull the adhesive toward the bottom left of the image.

by the activator. Noncontact area is cured by the adhesive that is cured by UV light, see Fig. 17.

Package E: After assembly, Loctite 352 on the corners only holds the package. The package is underfilled by the self-curing and UV curable mixture. Non-contact area on the edge is cured by UV light, see Figs. 18 and 19.

4) Embedded Package (Humidity):

Package F: The assembly method is the same as package D.

#### VI. CONCLUSION

A microspring capable of low resistance ( $<100~\text{m}\Omega$ ), high compliance ( $>30~\mu\text{m}$ ), and dense 2-D array pitches ( $180~\times~180~\mu\text{m}$ ) has been demonstrated. The components of the resistance have been analyzed in detail, suggesting that the tip–pad interface is  $<40~\text{m}\Omega$  for the contact area ( $100~\mu\text{m}^2$ ) and force (0.01 grams) used in these contacts. High yield and uniform fabrication enables flip-chip packages with 100% assembly yield with thousands of contacts. A variety of packaging methods have been demonstrated, including springs in air, springs embedded, and use of different spacers (no spacer, polymer, ball–pit). In situ glitch testing shows no intermittent resistance increases during thermocycling. Stable or decreasing resistances were observed during thermocycle and humidity testing. Pre-scrubbing the tips was found to be a beneficial assembly step.

This paper suggests that a micropressure contact can be used for next-generation flip-chip packaging. Such an architecture can enable new ways to address the known-good-die problem, which prevents more complex MCMs from being fabricated, because the chips can be tested at speed and reworked if needed before final assembly. The fabrication process is scalable to even smaller pitch 2-D arrays because it is based on lithographically patterning of thin films. Similarly, if less than 30  $\mu$ m vertical compliance is required, shorter springs can be used, enabling lower resistance and increased parallelism. Note that while solder and gold bumps have already demonstrated  $<100 \text{ m}\Omega$  contacts, these have negligible compliance compared to the springs. The gaps (bond-line) between the chip surface and pad surface is approximately 18  $\mu$ m in this paper, but can be made much smaller as the springs are designed to be fully compressible. This enables packages with smaller vertical heights. The spring compliance can accommodate more thermal expansion mismatch than conventional approaches.

The springs have the potential to be a basic enabler for future microsystems.

#### ACKNOWLEDGMENT

The authors would like to thank V. Geluz-Aguilar and L. Wong, Palo Alto Research Center, Palo Alto, CA, for providing fabrication support.

#### REFERENCES

- [1] G. Guilian, B. Haba, V. Oganesian, K. Honer, D. Ovrutsky, C. Rosenstein, E. Axelrod, F. Hazanovich, and Y. Aksenton, "Compliant wafer level package for enhanced reliability," in *Proc. Int. Symp. High Density Packag. Microsyst. Integr.*, 2007, pp. 1–5.

- [2] M. S. Bakir, H. A. Reed, P. A. Kohl, K. P. Martin, and J. D. Meindl, "Sea of leads ultrahigh-density compliant wafer-level packaging technology," in *Proc. 52nd Electron. Comp. Technol. Conf.*, 2002, pp. 1087–1094.

- [3] H. Hedler, T. Meyer, W. Leiberg, and R. Irsigler, "Bump wafer level packaging: A new packaging platform (not only) for memory products," in *Proc. Int. Symp. Microelectron.*, 2003, pp. 681–686.

- [4] J. Novitsky and C. Miller, "MicroSpring contacts on silicon: Delivering Moore's law-type scaling to semiconductor package, test and assembly," in *Proc. Int. Conf. High-Density Interconnect Syst. Packag.*, Denver, CO, 2000, pp. 250–255.

- [5] P. Chen, K. Kalakkad, K. Matsubavashi, W. Maynard, and J. Williams, "Assessing design tradeoffs with a customizable area-array connector," in *Proc. SMTA Int. Conf.*, San Diego, CA, 2009, pp. 424–430.

- [6] E. M. Chow, D. K. Fork, C. L. Chua, K. Van Schuylenbergh, and T. Hantschel, "Wafer-level packaging with soldered stress-engineered micro-springs," *IEEE Trans. Adv. Packag.*, vol. 32, no. 2, pp. 372–378, May 2009.

- [7] E. M. Chow, C. Chua, T. Hantschel, K. Van Schuylenbergh, and D. K. Fork, "Pressure contact micro-springs in small pitch flip-chip packages," *IEEE Trans. Comp. Packag. Technol.*, vol. 29, no. 4, pp. 796–803, Dec. 2006.

- [8] C. L. Chua, D. K. Fork, and T. Hantschel, "Densely packed optoelectronic interconnect using micromachined springs," *IEEE Photon. Technol. Lett.*, vol. 14, no. 6, pp. 846–848, Jun. 2002.

- [9] D. L. Smith and A. S. Alimonda, "A new flip-chip technology for high-density packaging," in *Proc. 46th Electron. Comp. Technol. Conf.*, 1996, pp. 1069–1073.

- [10] A. V. Krishnamoorthy, H. Ron, Z. Xuezhe, H. Schwetman, L. Jon, P. Koka, L. GuoLiang, I. Shubin, and J. E. Cunningham, "Computer systems based on silicon photonic interconnects," *Proc. IEEE*, vol. 97, no. 7, pp. 1337–1361, Jul. 2009.

- [11] J. E. Cunningham, Z. Xuezhe, I. Shubin, H. Ron, J. Lexau, A. V. Krishnamoorthy, M. Asghari, F. Dazeng, J. Luff, L. Hong, and K. Cheng-Chih, "Optical proximity communication in packaged Si photonics," in *Proc. 5th IEEE Int. Conf. Group IV Photon.*, Sep. 2008, pp. 383–385.

- [12] I. Shubin, E. M. Chow, J. Cunningham, D. De Bruyker, C. Chua, B. Cheng, J. C. Knights, K. Sahasrabuddhe, Y. Luo, A. Chow, J. Simons, A. V. Krishnamoorthy, R. Hopkins, R. Drost, R. Ho, D. Douglas, and J. Mitchell, "Novel packaging with rematable spring interconnect chips for MCM," in *Proc. 59th Electron. Comp. Technol. Conf.*, 2009, pp. 1053–1058.

- [13] C. L. Chua, D. K. Fork, K. Van Schuylenbergh, and J.-P. Lu, "Out-of-plane high-Q inductors on low-resistance silicon," *J. Microelectromech. Syst.*, vol. 12, no. 6, pp. 989–995, Dec. 2003.

- [14] T. Hantschel, L. Wong, C. L. Chua, and D. K. Fork, "Fabrication of highly conductive stressed-metal springs and their use as sliding-contact interconnects," *Microelectron. Eng.*, vols. 67–68, no. 1, pp. 690–695, 2003

- [15] E. M. Chow, T. Hantschel, K. Klein, D. K. Fork, C. L. Chua, L. Wong, and K. Van Schuylenbergh, "Micro-spring force characterization and applications in integrated circuit packaging and scanning probe MEMS metrology," in *Proc. IEEE Int. Solid-State Sensors Actuat. Conf.*, Boston, MA, Jun. 2003, pp. 408–411.

- [16] E. M. Chow, C. Chua, T. Hantschel, K. Van Schuylenbergh, and D. K. Fork, "Pressure contact micro-springs in small pitch flip-chip packages," *IEEE Trans. Comp. Packag. Technol.*, vol. 29, no. 4, pp. 796–803, Dec. 2006.

- [17] J. Maciel, S. Majumder, R. Morrison, and J. Lampen, "Lifetime characteristics of ohmic MEMS switches," *Proc. SPIE, Int. Soc. Opt. Eng.*, vol. 5443, pp. 9–14, Dec. 2003.

- [18] S. C. Bromley and B. J. Nelson, "Performance of microcontacts tested with a novel MEMS device," in *Proc. 47th Electr. Contacts*, 2001, pp. 122–127.

- [19] I. Shubin, E. M. Chow, J. Cunningham, D. De Bruyker, C. Chua, B. Cheng, J. C. Knights, K. Sahasrabuddhe, Y. Luo, A. Chow, J. Simons, A. V. Krishnamoorthy, R. Hopkins, R. Drost, R. Ho, D. Douglas, and J. Mitchell, "Novel packaging with rematable spring interconnect chips for MCM," in *Proc. IEEE 59th Electron. Comp. Technol. Conf.*, Piscataway, NJ, May 2009, pp. 1053–1058.

- [20] O. Rezvanian, C. Brown, M. A. Zikry, A. I. Kingon, J. Krim, D. L. Irving, and D. W. Brenner, "The role of creep in the time-dependent resistance of ohmic gold contacts in radio frequency microelectromechanical system devices," *J. Appl. Phys.*, vol. 104, no. 2, pp. 024513-1–024513-3, 2008.

Kunal Sahasrabuddhe received the B.S. degree in engineering physics from the University of California, Berkeley, in 2008. He is currently pursuing the Ph.D. degree in applied physics with Stanford University, Stanford, CA. His dissertation topic is related to the development of devices based on photon-enhanced thermionic emission.

He was an Intern with Palo Alto Research Center, Palo Alto, CA, in 2009.

**Bowen Cheng** received the B.S. and M.S. degrees in power mechanical engineering from National TsingHua University, Hsinchu, Taiwan, in 2001 and 2003, respectively, and the Ph.D. degree in electrical engineering from the University of Washington-Seattle, Seattle, in 2010.

He joined the Palo Alto Research Center (PARC), Palo Alto, CA, as a Visiting Researcher in 2008, where he has been a Post-Doctoral Researcher since 2011. He is currently involved in research on design, development, and testing of deep-ultraviolet semi-

conductor light emitters. He was involved in research on high-density interconnects for high-power electronic packages, self-assembly, and micro-optical scanners for optical coherence tomography-related applications. His current research interests include optoelectronics and microelectromechanical systems and packaging.

**Ivan Shubin** received the M.S. degree in quantum electronics from the Moscow Institute of Physics and Technology, Moscow, Russia, in 1994, and the Ph.D. degree in electrical engineering from the School of Optics, CREOL, UCF, in 2001.

He was a Senior Engineer with Optium/Finisar, Orlando, FL, from 2001 to 2007, and a Project Scientist with the University of California, San Diego. Since 2007, he has been with Oracle Labs, San Diego, where he is currently a Principal Hardware Engineer researching advanced packaging solutions

and platforms for electronic, optoelectronic and microelectromechanical system applications, wafer scale packaging, 3-D integration, and novel silicon and III–V photonic components. He has authored or co-authored over 50 technical papers and conference presentations.

**Dirk De Bruyker** received the M.Sc. and Ph.D. degrees in electrical engineering from Katholieke Universiteit Leuven, Leuven, Belgium, in 1994 and 2002, respectively.

He has been involved in research on microelectromechanical systems (MEMSs) and microsystem design, CAD, and fabrication for ten years. He is currently a Senior Staff Scientist with Palo Alto Research Center (PARC), Palo Alto, CA. He invented a novel microfluidic mixing technique and co-invented the world's smallest pressure sensor. He

was a Principal Investigator with PARC on several U.S. government-funded projects. He has authored or co-authored over 30 peer-reviewed articles and he holds several patents. His current research interests include microspring technology for packaging, optical MEMSs (miniaturized optical switches and micromirrors), and biomedical microsystems (bioelectric field sensing and calorimetric enthalpy arrays for proteomics).

John E. Cunningham received the B.S. degree from the University of Tennessee at Knoxville, Knoxville, and the M.S. and Ph.D. degrees from the University of Illinois at Champaign-Urbana, Urbana, all in physics.

He is a Veteran Research Scientist with over 25 years of experience in universities, Bell Laboratories, Murray Hill, NY, Sun Laboratory, Sun Microsystems/Oracle, San Diego, CA, and start-up experience in optoelectronic and semiconductor devices and packaging used within optical networks.

Since joining Sun Microsystems/Oracle, he has led advanced packaging initiatives to develop interchip proximity communication and researched Si nanophotonics solutions for data communications within computers. Before joining Sun Microsystems, he was the Chief Scientist with AraLight, Inc., Jamesburg, NJ, where he developed products based on hybrid integration of vertical cavity surface emitting lasers and photodetectors with CMOS, a technology he co-developed with Bell Laboratories. While at Bell Laboratories, he also pioneered eight world records on various types of quantum mechanically engineered devices and materials. Before joining Bell Laboratories, has was a Research Faculty Member with the Physics Department, University of Illinois, where he initiated the first metals molecular beam epitaxy. He is currently a Distinguished Engineer with Sun Microsystems/Oracle, the Principal Lead of the Advanced Packaging Group, Inc., Oracle, San Diego, and the Co-Principal Investigator of the DARPA UNIC Project. He has co-authored over 360 journal papers including some with Nobel Prize Laureates, and he holds 40 U.S. patents.

**Chris Chua** received the Bachelors degree in physics and in electrical engineering from the Massachusetts Institute of Technology, Cambridge, in 1990, and the Ph.D. degree in optoelectronic devices with Cornell University, Ithaca, NY, in 1996.

He joined the Palo Alto Research Center (PARC), Palo Alto, CA, as a Research Associate, and was involved in research on vertical-cavity surfaceemitting lasers. He is currently a Senior Research Staff Member with PARC researching high-density

interconnects and semiconductor light emitters.

Ying Luo, photograph and biography are not available at the time of publication.

Karl F. Böhringer (S'94–M'97–SM'03–F'11) received the Dipl.-Inform. degree from the University of Karlsruhe, Germany, in 1990, and the M.S. and Ph.D. degrees in computer science from Cornell University, Ithaca, NY, in 1993 and 1997, respectivly.

He was a Visiting Scholar with Stanford University, Stanford, CA, from 1994 to 1995, and was a Post-Doctoral Researcher with the University of California, Berkeley, from 1996 to 1998. He has been with the University of Washington, Seattle,

since 1998, where he is currently a Professor of electrical engineering and bioengineering and holds the J. M. Fluke Distinguished Chair of Engineering. He is the Director of the University of Washington Microfabrication Facility. He held visiting faculty positions with the universities of Tohoku, Tokyo, Japan, and São Paulo, Brazil. He has created, among others, multibatch self-assembling systems, massively parallel microactuator arrays, and a walking microrobot. His current research interests include microelectromechanical systems, manipulation and assembly from macro- to nano-scales, microfluidic systems for the life sciences, and microrobotics.

Dr. Böhringer was a recipient of the Long-Term Invitational Fellowship for Research in Japan from the Japan Society for the Promotion of Science in 2004, the IEEE Robotics and Automation Society Academic Early Career Award in 2004, the National Science Foundation (NSF) CAREER Award in 1999, and the NSF Post-Doctoral Associateship in 1997. His work was listed among the Top 100 Science Stories of 2002 in *Discover Magazine*. He is an editor of the IEEE/ASME JOURNAL OF MICROELECTROMECHANICAL SYSTEMS and the IEEE TRANSACTIONS ON AUTOMATION SCIENCE AND ENGINEERING. He was, among others, on the technical program committees for the IEEE MEMS and Transducers conferences and he was a General Co-Chair of the IEEE MEMS in 2011. He is a member of the Society for Nanoscale Science, Computing and Engineering, the American Society for Engineering Education, and the German Society for Information Sciences.

Eugene M. Chow (SM'12) received the B.S. degree in engineering physics from the University of California, Berkeley, in 1995, and the M.S. degree in electrical engineering, the M.S. degree in management science and engineering, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1997, 2000, and 2001, respectively.

He researched microelectromechanical systems with Stanford University, focusing on through wafer electrical interconnects in silicon, atomic force piezoresistive cantilever arrays, and deep plasma

etching. He is currently a Principal Scientist and Manager of the Microsystems Group, Electronic Materials and Devices Laboratory, Palo Alto Research Center (formerly Xerox PARC), Palo Alto, CA. He is involved in device and commercialization research in topics such as microsprings for integrated circuit packaging, thin-film transistor and microelectromechanical systems integration, large area printed organic electronics, microassembly, biodevices, and novel printing concepts. He has authored or co-authored 45 technical papers and holds several patents, including 38 issued and over 30 pending.

Ashok V. Krishnamoorthy (M'93–SM'10–F'12) received the B.S. (Hons.) degree from the California Institute of Technology, Pasadena, in 1986, the M.S. degree from the University of Southern California, Los Angeles, in 1988, and the Ph.D. degree from the University of California at San Diego, La Jolla, in 1993.

He is currently with Oracle Labs, San Diego, CA, where he is an Oracle Architect and the Chief Technologist in Photonics. He serves as a Principal Investigator of the Oracle

Laboratory DARPA UNIC/POEM initiatives on silicon photonics-tothe-processor. He was a Distinguished Engineer and the Director of Sun Microsystems, and was involved in advanced optical interconnect and silicon photonics development. He also spent several years as CTO and the President of AraLight, Inc., formerly part of Lucent Technologies, Inc., developing high-density parallel optical products and technologies. Prior to that, he was an Entrepreneur in Residence with the Lucent New Ventures Group and a Technical Staff Member with the Advanced Photonics Research Department, Bell Laboratory, Holmdel, NJ. For over two decades, he has been involved in packaging and integration of photonic devices with silicon complimentary metal-oxide-semiconductor circuits (including electrooptic modulators on silicon, quantum-well devices, vertical-cavity surface-emitting lasers, and, most recently, Si and Ge photonics) and in creating transceivers, switching systems, and computing systems based on these components. He has authored or co-authored over 200 technical papers and eight book chapters, and presented over 85 invited and plenary talks at conferences. He holds 80 U.S. patents.

Dr. Krishnamoorthy was a recipient of the 2004 ICO International Prize in Optics, the 2003 IEEE Photonics Society Distinguished Lecturer Award, the Eta Kappa Nu's Outstanding Engineer Citation, the 2006 Chairman's Award from Sun Microsystems, and multiple team awards. He was a member or the Chair of over 35 international conferences. He has been a Guest Editor of several technical journals. He is a Distinguished Member of Tau Beta Pi, and is a fellow of the Optical Society of America.