Received March 2, 2021, accepted March 27, 2021, date of publication April 5, 2021, date of current version April 14, 2021. *Digital Object Identifier* 10.1109/ACCESS.2021.3071198

# Mitigation of Complex Non-Linear Dynamic Effects in Multiple Output Cascaded DC-DC Converters

SAJJAD AHMED<sup>[10]</sup>, (Graduate Student Member, IEEE), SYED ABDUL RAHMAN KASHIF<sup>[0]</sup>, NOOR UL AIN<sup>1</sup>, AKHTAR RASOOL<sup>[10]</sup>, MUHAMMAD SOHAIB SHAHID<sup>[10]</sup>, SANJEEVIKUMAR PADMANABAN<sup>[10]</sup>, (Senior Member, IEEE), EMRE OZSOY<sup>[10]</sup>, (Senior Member, IEEE), AND MUHAMMAD ASGHAR SAQIB<sup>1</sup> <sup>1</sup>Department of Electrical Engineering, University of Engineering and Technology, Lahore 54890, Pakistan

<sup>2</sup>Department of Electrical Engineering, Sharif College of Engineering and Technology, Lahore 55150, Pakistan

<sup>3</sup>CTIF Global Capsule, Department of Business Development and Technology, Aarhus University, 7400 Herning, Denmark

<sup>4</sup>Research and Development Design Center, Danfoss Drives A/S Ulsnaes 1, DK-6300 Graasten, Denmark

Corresponding author: Sajjad Ahmed (sajjad.ahmed@uet.edu.pk)

**ABSTRACT** In the modern world of technology, the cascaded DC-DC converters with multiple output configurations are contributing a dominant part in the DC distribution systems and DC micro-grids. An individual DC-DC converter of any configuration exhibits complex non-linear dynamic behavior resulting in instability. This paper presents a cascaded system with one source boost converter and three load converters including buck, Cuk, and Single-Ended Primary Inductance Converter (SEPIC) that are analyzed for the complex non-linear bifurcation phenomena. An outer voltage feedback loop along with an inner current feedback loop control strategy is used for all the sub-converters in the cascaded system. To explain the complex non-linear dynamic behavior, a discrete mapping model is developed for the proposed cascaded system and the Jacobian matrix's eigenvalues are evaluated. For the simplification of the analysis, every load converter is regarded as a fixed power load (FPL) under reasonable assumptions such as fixed frequency and input voltage. The eigenvalues of period-1 and period-2 reveal that the source boost converter undergoes period-2 orbit and chaos whereas all the load converters operate in a stable period-1 orbit. The proposed configuration eliminates the period-2 and chaotic behavior from all the load converters and is also validated using simulation in MATLAB/Simulink and experimental results.

**INDEX TERMS** Bifurcation, chaos, DC-DC power converters, non-linear dynamical systems.

#### I. INTRODUCTION

DC-DC converters are the inescapable components of modern DC distribution systems. The non-linear behavior of those individual converter circuits is thoroughly carried out in the studies of power electronics circuits presented in reference [1], [2]. The time-varying behavior of those converter circuits is because of the low and high-frequency oscillations that result in multiple period bifurcations and chaos phenomena [3]. In the modern era of technology, most of the consumer devices are comprised of DC-DC converter circuits that necessitate the design engineers to mainly focus on the elimination of sub-harmonics [4]. So, it is important to go through the studies of the non-linear dynamics of those converter systems. The main advantages of the DC distribution systems include simplicity in the connectivity with renewable

The associate editor coordinating the review of this manuscript and approving it for publication was Eklas Hossain.

sources, higher efficiency, and a wide range of choices for the design parameters. The reliability and stability of DC power converters are the main issues that come across when they are used in the distribution systems. The design and stability of a single converter can be easily carried out. However, the main stability issues arise in a DC distribution system when the interaction of sub-converters takes place [5].

The DC converters connected in a cascaded style is the basic form in a DC distribution system where various renewable energy sources deliver power to a shared DC bus and all the load converters take power from that bus [6]. Hence, it is the need of the hour to study the reliability and stability of cascaded DC-DC converter systems. The studies have proven that the non-linear dynamic effect is due to the cascaded configuration in the DC-DC converter systems [7]–[9]. These studies are only suitable for small-signal analysis about the stability of DC converter systems. Some models such as FPLs, impedance calculation criteria, and Thevenin network

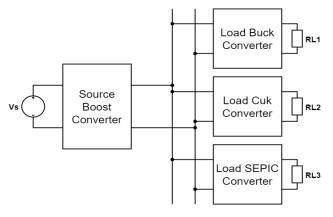

FIGURE 1. Block diagram of the proposed cascaded system.

have been developed for large-scale systems [10]–[12]. However, the study of the stability issues about the non-linear dynamic behavior of cascaded DC converter systems is less explored. This paper presents the non-linear dynamic behavior of a cascaded converter system having one source and three load converters and proposes remedial measures to avoid non-linear effects.

Over the past few decades, the complex non-linear behavior of individual converters such as a boost, buck, Cuk, buck-Boost, SEPIC, and flyback converter has been studied. Using the average and discrete mapping model, the eigenvalues at the equilibrium point are evaluated and examined for the stability behavior [13]-[18]. The main problem associated with the analysis using the averaged model is that the perioddoubling bifurcation cannot be estimated because the switching frequency of the converter under analysis is completely neglected [19]. Several complex non-linear dynamic studies such as Niemark-Sacker bifurcation, border collision bifurcation, discrete mapping model, slow and fast scale instabilities, and chaos are available in the literature, but they are only used in the studies of single DC-DC converter circuits with stand-alone operation [20]-[23]. Those bifurcation studies are not used in the investigation of the non-linear dynamic behavior of cascaded DC-DC converter systems whose behavior is dependent on the load converters. Therefore, this paper presents the investigation of the complex non-linear bifurcation phenomena for the cascaded DC-DC converter systems.

The block diagram of the proposed systems to improve the complex bifurcation phenomena of the cascaded multiple outputs DC-DC converter systems that are part of a large DC distribution system is shown in Fig. 1. The simulation of every individual sub-converter of the cascaded system is carried out and the complex bifurcation phenomena of the cascaded converter systems are studied in detail. Section 2 presents the implementation of the cascaded converter system along with the control scheme used for all subconverters. In section 3, the results of the simulation of the individual converter and for the complete cascaded system are presented. Section 3 also shows the results in the form of inductor current waveforms obtained from the real hardware FPLs in detail. The Jacobian matrix's eigenvalues are used to explain the unstable behavior of the cascaded system. Finally, in section 5, the results are summarized, and a conclusion is drawn which confirms that by decreasing the input source voltage, the system undergoes period-2 phenomena which finally turns into chaos if the input voltage is further decreased and hence the system stability weakens. When the system becomes unstable, some of the eigenvalues are out of the unit circle that severely affects the performance of the source boost converter in the cascaded system. This paper provides an efficient way to get rid of the complex non-linear dynamic behavior in the cascaded DC distribution systems and in DC micro-grids that have multiple output configurations.

circuit board. Section 4 describes the discrete mapping model of the proposed simplified cascaded converter system with

#### II. IMPLEMENTATION OF CASCADED CONVERTER SYSTEM

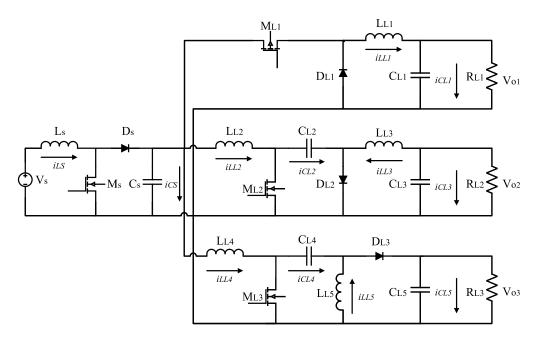

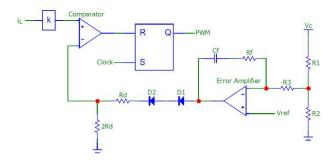

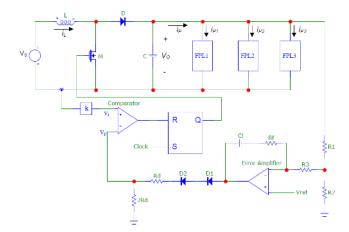

The schematic diagram of the cascaded system with multioutput converters is presented in Fig. 2. The source boost converter in the cascaded system at the first stage takes DC input and its output becomes the input to all the sub-converters on the load side. The load side converters include a buck converter, a Cuk converter, and a SEPIC converter. All the converters in the cascaded system are controlled individually with the same control technique which is shown in Fig. 3. The control technique used for all the sub-converters in the cascaded converter system comprises an outer voltage feedback loop and an inner current feedback loop. Furthermore, the voltage loop contains a resistive divider circuit, an error amplifier with a compensation network, and one protection circuit with offset-divided protection property. The resistive divider circuit steps down the output capacitor voltage of every sub-converter and feeds to the inverting input of the error amplifier. The protection circuit with offset divided property offsets the voltage by dropping the voltage across two diodes. The voltage is then divided by a ratio of 3:1 with Rd and 2Rd which is further fed to the inverting input of the comparator. This configuration of using diodes confirms that there is no switching pulse when the converter is operating under no-load condition. In the current feedback loop, the current is subjected to a gain which is then fed to the comparator's non-inverting input. The output of the comparator is connected to the R input of the R-S latch whereas the S input of the latch is fed with a clock source with period T. The control scheme operates as follows: When the current feedback level reaches the voltage feedback level, the output of the comparator circuit applies a reset signal to the R-S latch which turns OFF the MOSFET switch. When the switch is turned OFF, the current and the voltage feedback levels begin to fall, and hence, the output of the comparator is not asserted. Hence, it lifts the reset signal of the R-S latch and the output of the R-S latch is set by the clock source with period T which directly turns ON the MOSFET, and the voltage and current feedback increases again. This process continues indefinitely,

FIGURE 2. Circuit diagram of the proposed cascaded converter system.

**FIGURE 3.** Circuit diagram of feedback controller implemented for every sub-converter in the cascaded system.

and the reference voltage can be calculated as:

$$V_{ref} = \frac{R_2}{R_1 + R_2} \times V_C \tag{1}$$

#### III. STABILITY ANALYSIS USING SOFTWARE SIMULATIONS AND HARDWARE IMPLEMENTATION

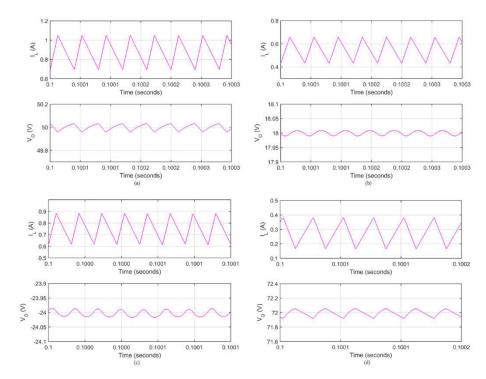

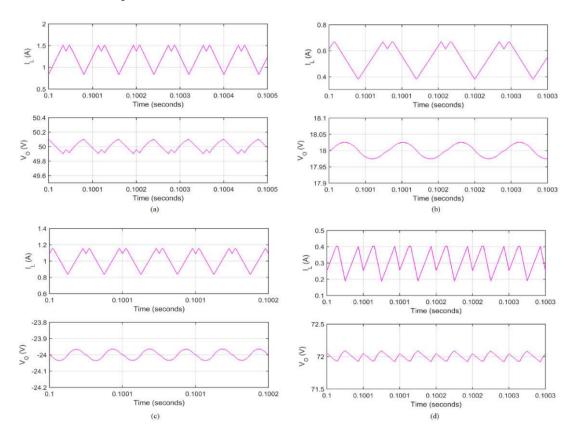

The parameters used for the simulation study are presented in Table 1. For simulation purposes, the source boost converter is designed for an input voltage of 35 V and an output voltage of 50 V which acts as the bus voltage for all the load converters. However, the converters can be designed for any other voltage range. The initial values of all the energy storing elements are set to zero and each converter has been simulated individually at rated power and designed input voltage. The inductor current and capacitor voltage waveform for every individual converter in the cascaded converter system at the rated input voltage is obtained by simulating the system in MATLAB/Simulink and is shown in Fig. 4.

From Fig. 4, it can be found that all the converters operate in stable period-1 orbit when they are subjected to the input voltage equal to the rated value. However, when the input

TABLE 1. Component values for the converters in the cascaded system.

| Parameter           | Boost | Buck  | Cuk    | SEPIC  |

|---------------------|-------|-------|--------|--------|

| V <sub>8</sub> (V)* | 35    | 50    | 50     | 50     |

| D                   | 0.3   | 0.36  | 0.3243 | 0.5902 |

| $L_1$ (mH)          | 1.225 | 2.074 | 2.1113 | 5.7637 |

| $C_1$ (uF)          | 28.8  | 12.34 | 27.39  | 11.38  |

| $L_2$ (mH)          | -     | -     | 1.013  | 8.2983 |

| $C_2(uF)$           | -     | -     | 13.03  | 11.38  |

| $R(\Omega)$         | 83.33 | 32.4  | 48     | 648    |

| $V_{O}(V)$          | 50    | 18    | 24     | 72     |

| $P_{O}(W)$          | 30    | 10    | 12     | 8      |

$^{*}$ The parameter V<sub>s</sub> for the load converters represents the bus voltage which is also the output of the source boost converter.

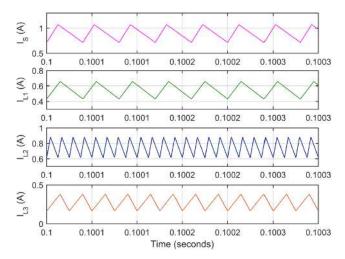

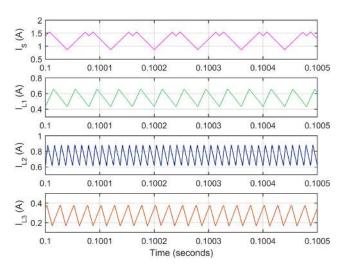

source voltage for every individual converter is decreased from the rated value, the converters undergo period-2 orbit which severely affects their stability. The period-2 behavior of every individual converter is shown in Fig. 5. After the verification of period-2 orbit from the simulation of every individual converter, the complete cascaded converter system is simulated at the source input voltage of 35 V, and the inductor currents are shown in Fig. 6. We have seen from Fig. 6 that all the sub-converters of the cascaded system are operating in a stable period-1 orbit. As the input voltage of the source boost converter is decreased to 25 V, the source boost converter undergoes period-2 orbit however all the load converters continue operating in period-1 orbit with stable behavior. This phenomenon is shown in Fig. 7. Since, for any DC-DC converter, almost all the practical applications require a specific operating point at equilibrium. Therefore, the designed system should behave accurately around that equilibrium point within a certain tolerance band. As seen from Fig. 7, it is clear that the proposed converter enters period-2 orbit at 25 V which confirms that it has a tolerance

# IEEE Access

**FIGURE 4.** Inductor current ripple and output voltage ripple waveforms of stable period-1 operation for a) boost converter at  $V_S = 35$  V b) buck converter at  $V_S = 50$  V c) Cuk converter at  $V_S = 50$  V d)SEPIC converter at  $V_S = 50$  V.

**FIGURE 5.** Inductor current ripple and output voltage ripple waveforms of period-2 operation for a) boost converter at  $V_S = 25 \text{ V b}$ ) buck converter at  $V_S = 36 \text{ V c}$ ) Cuk converter at  $V_S = 24 \text{ V d}$ ) SEPIC converter at  $V_S = 40 \text{ V}$ .

band for input voltage as 10 V and within this tolerance band, the converter operates linearly under stable period-1 orbit.

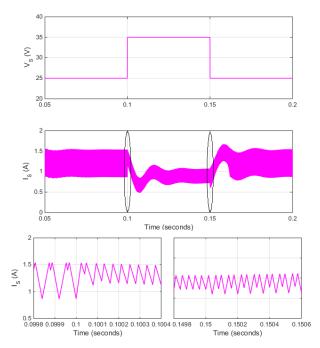

The inductor current waveform of the source boost converter for a step variation in the input voltage from 25 V to 35 V at

FIGURE 6. Inductor current waveforms of all the converters of the cascaded system at  $V_S=35$  V.

FIGURE 7. Inductor current waveforms of all the converters of the cascaded system at  $V_S = 25$  V.

t = 0.1 s and then again 35 V to 25 V at t = 0.15 s is plotted in Fig. 8. The inductor current waveform at t = 0.1 s and t = 0.15 s is zoomed-in and shown separately within the same figure. It can be seen from Fig. 8 that before t = 0.1 s, the input voltage is set at 25 V and hence, the inductor current of the source boost converter undergoes period-2 phenomenon. From t = 0.1 s to t = 0.15 s, the input voltage is kept constant at 35 V which confirms that the inductor current exhibits period-1 behavior. After t = 0.15 s, the input voltage is again stepped down to 25 V and the inductor current again exhibits period-2 behavior. However, it is confirmed that the inductor current waveforms for all the load converters are having period-1 behavior.

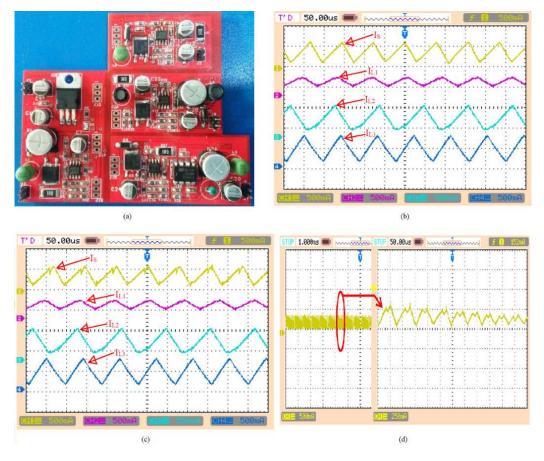

Since in the simulation studies, the influences and disturbances from the external environment do not occur, it is necessary to consider the effect of external disturbances and influences on the system behavior. So, for the verification of the simulation results, a hardware printed circuit board (PCB) is developed using the UC3842, fixed frequency current mode

FIGURE 8. Inductor current waveform of source boost converter for step change in the input voltage verifying non-linear incident effects.

pulse width modulation (PWM) control integrated circuit (IC) and is shown in Fig. 9(a). The internal diagram of the IC depicts a similar circuit as developed for the control scheme of every individual converter in the cascaded system. In the design of the hardware circuit, an N-channel MOSFET STD20NF20 having very small internal resistance, high current, and low gate charge is used which ensures fast switching. The inductor current waveform for the input voltage of 35 V and 25 V is obtained using a digital storage oscilloscope and is shown in Fig. 9(b) and Fig. 9(c) respectively. When the input voltage of the source boost converter is further decreased from 25 V, the source boost converter exhibits fast and slow scale instability behavior with all the load converters still operating in the stable period-1 state. This phenomenon is depicted in Fig. 9(d).

#### **IV. BIFURCATION AND CHAOS ANALYSIS**

The simulation studies presented in the previous section show that every load converter in the proposed cascaded system works in the stable period-1 orbit and is independent of the state and dynamic behavior of the source boost converter which may undergo period-2 orbit depending on the input voltage of the system. This section explains the instability phenomena regarding the simulation and experimental studies using the best suitable model. The discrete mapping model is developed that best describes the instability and dynamic behavior of the converters in the proposed cascaded system with multiple output configurations.

## A. SIMPLIFICATION OF THE SYSTEM AND DISCRETE MAPPING MODEL

If all the components used in the cascaded converter system are assumed to be ideal, then every load converter can be

**FIGURE 9.** Experimental hardware implementation and resulting waveforms a) Hardware circuit prototype board b) Inductor current waveforms at V<sub>S</sub> = 35 V c) Inductor current waveforms at V<sub>S</sub> = 25 V d) Inductor current waveform for source boost converter at V<sub>S</sub> < 25 V.

**FIGURE 10.** Schematic diagram of the simplified cascaded converter system by using FPLs.

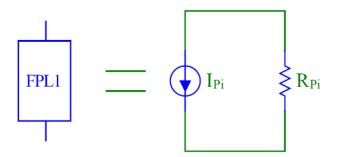

regarded as an FPL at a suitable switching frequency and input voltage range. This assumption is well supported by the simulation and experimental results of the previous section because all the load converters remain in stable period-1 orbit irrespective of the mode of operation and dynamic behavior of the source boost converter. The load buck, Cuk, and SEPIC converters are modeled as FPL1, FPL2, and FPL3 respectively which makes the overall cascaded converter system simplified as shown in Fig. 10.

The output power of an FPL<sub>i</sub> (where i = 1, 2, and 3 for the buck, Cuk, and SEPIC converter respectively) is given as:

$$P_i = \frac{V_{oi}^2}{R_{Li}} \tag{2}$$

Now, the input current of FPL<sub>i</sub> can be given as,

$$i_{Pi} = \frac{P_i}{v_o} \tag{3}$$

$$I_{Pi} = \frac{P_i}{V_o} \tag{4}$$

where (4) is the steady-state representation of (3).

The rate of change of input current with respect to  $v_{DC}$  using

(3) is given as:

$$\frac{\partial i_{Pi}}{\partial v_o} = -\frac{P_i}{V_o^2} \tag{5}$$

By integrating (5) and inserting into (4), we get:

$$i_{Pi} = -\frac{P_i}{V_o^2} v_o + \frac{2P_i}{V_o} \tag{6}$$

FIGURE 11. Simplified FPL model used for analysis.

TABLE 2. Circuit parameters for FPLS.

| Parameter                    | FPL1 | FPL2   | FPL3   |

|------------------------------|------|--------|--------|

| $I_{Pi}\left(A ight)$        | 0.4  | 0.48   | 0.32   |

| $R_{Pi}\left(k\Omega\right)$ | -250 | -208.3 | -312.5 |

Equation (6) shows that the current flowing through any FPL can be approximated by a negative resistance and a fixed current source. That is,

$$R_{Pi} = \frac{v_o^2}{P_i} \tag{7}$$

$$I_{Pi} = \frac{2P_i}{V_o} \tag{8}$$

The above two equations are transformed into a circuit diagram in the steady-state and are shown in Fig. 11. Table 2 shows the calculated parameters for all the FPLs using (7) and (8).

The state-space representation of the simplified system for the k<sup>th</sup> control cycle by assigning the state variables as  $X = [i_L v_O v_f]^T$  can be given as:

$$\dot{x} = \begin{cases} A_1 x + B_1, & kT \le t \le (k + d_k) T \\ A_2 x + B_2, & (k + d_k) T \le t \le (k + 1) T \end{cases}$$

(9)

where  $d_k$  is the duty ratio. The matrices  $A_1$  and  $A_2$  in the (9) can be written as:

$$A_{1} = \begin{bmatrix} 0 & 0 & 0 \\ 0 - \left(\frac{1}{R_{P1}} + \frac{1}{R_{P2}} + \frac{1}{R_{P3}}\right) \frac{1}{C} & 0 \\ 0 & \frac{R_{2}}{(R_{1} + R_{2})R_{3}C_{f}} & 0 \end{bmatrix}$$

$$A_{2} = \begin{bmatrix} 0 & -\frac{1}{L} & 0 \\ -\frac{1}{C} - \left(\frac{1}{R_{P1}} + \frac{1}{R_{P2}} + \frac{1}{R_{P3}}\right) \frac{1}{C} & 0 \\ 0 & \frac{R_{2}}{(R_{1} + R_{2})R_{3}C_{f}} & 0 \end{bmatrix}$$

and the vectors  $B_1$  and  $B_2$  are:

$$B_{1} = B_{2} = \begin{bmatrix} -\frac{\frac{V_{S}}{L}}{-\frac{I_{P1} + I_{P2} + I_{P3}}{C}} \\ -\frac{\frac{V_{ref}}{R_{3}C_{f}}} \end{bmatrix}$$

The discrete mapping model is the best match for the converters in power electronics. There are various reasons for this match, however, the main reason is that a digital control system can be designed very easily using the sampled data model. The discrete mapping model focuses on the cycleto-cycle behavior of the DC-DC converter system. Using the switching intervals described in equation (9) for ON and OFF time respectively, the sample data model for the simplified system presented in Fig. 10 can be given as:

$$x (kT + T) = e^{A_2(1-d_k)T} e^{A_1d_kT} x (kT) + e^{A_2(1-d_k)T} \int_0^{d_kT} e^{A_1t} B_1 dt + \int_0^{(1-d_k)T} e^{A_2t} B_2 dt$$

(10)

Using the control period number in subscript for easiness, we obtain the following:

$$f(X_k) = X_{k+1} = e^{A_2(1-d_k)T} e^{A_1 d_k T} x(kT) + e^{A_2(1-d_k)T} \int_0^{d_k T} e^{A_1 t} B_1 dt + \int_0^{(1-d_k)T} e^{A_2 t} B_2 dt$$

(11)

Now, referring to Fig. 10, the reference voltage of the outer voltage loop (inverting terminal voltage of the comparator) can be given as:

$$v_p = \frac{1}{2}(V_{ref} - v_f - R_f i_f - 2V_D)$$

(12)

where  $V_D$  represents the voltage drop across the diode. In matrix notation:

$$v_p = M_p X + \frac{1}{3} \left[ V_{ref} \left( 1 + \frac{R_f}{R_3} - 2V_D \right) \right]$$

(13)

where,

$$M_p = \left[ 0 - \frac{R_2 R_f}{3R_3 \left(R_1 + R_2\right)} - \frac{1}{3} \right]$$

(14)

The reference voltage for the inner current loop (noninverting terminal voltage of the comparator) can be written as:

$$v_i = ki_s \tag{15}$$

where  $i_s$  is the source current (also known as the inductor current in the case of a boost-converter). In matrix notation:

$$v_i = M_i X \tag{16}$$

where,

$$M_i = \begin{bmatrix} k & 0 & 0 \end{bmatrix}$$

Using (13) and (16), the switching condition can be stated as:

$$s(d_k, X_k) = v_i - v_p = (M_i - M_p) \left( e^{A_1 d_k T} X_k + \int_0^{d_k T} e^{A_1 t} B_1 dt \right) - \frac{1}{3} \left[ V_{ref} \left( 1 + \frac{R_f}{R_3} - 2V_D \right) \right]$$

(17)

The above switching condition equation can be used to determine the duty ratio  $d_k$  for the k<sup>th</sup> cycle. Once, the duty cycle is calculated using (17), it can be plugged into (11) and the solution can be obtained using the iterative approach. The Jacobian matrix for the proposed system whose discrete mapping model is given by the (11) can be stated as:

$$J(d_k, X_k) = \frac{\partial X_{k+1}}{\partial X_k} - \frac{\partial X_{k+1}}{\partial d_k} \left(\frac{\partial s}{\partial d_k}\right)^{-1} \frac{\partial s}{\partial X_k}$$

(18)

and the roots of the characteristic equation (18) gives the eigenvalues,

$$\det[\lambda I - J(d_k, X_k)] = 0 \tag{19}$$

By setting the equilibrium points for period-1 orbit as  $X_Q = [I_{SQ}V_{OQ}V_{fQ}]^T$  and for period-2 orbit as  $X_{Q2} = [I_{SQ2}V_{OQ2}V_{fQ2}]^T$  and  $X_{Q2}^* = [I_{SQ2}^*V_{OQ2}^*V_{fQ2}^*]^T$ , the resulting equations can be given as:

$$Period - 1 \begin{cases} f(X_Q) = X_Q \\ s(D_Q, X_Q) = 0 \end{cases}$$

(20)

$$Period - 2 \begin{cases} f(X_{Q2}) = X_{Q2} \\ f(X_{Q2}^*) = X_{Q2}^* \\ s(D_{Q2}, X_{Q2}) = 0 \\ s(D_{Q2}^*, X_{Q2}^*) = 0 \end{cases}$$

(21)

Hence, using (17), the duty ratio  $d_k$  is obtained and inserted into (11).

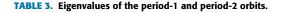

## B. EIGENVALUES CALCULATION FROM THE SYSTEM OF EQUATIONS AND BIFURCATION DIAGRAM

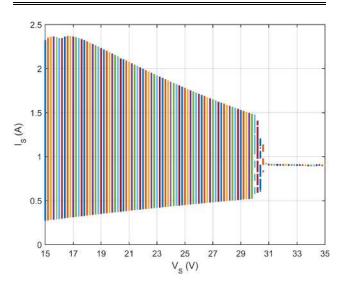

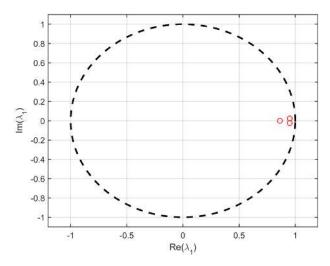

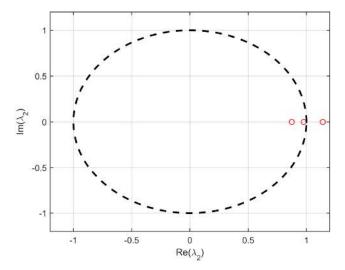

The system of equations for the discrete mapping model of the simplified cascaded system is iterated with the initial state vector as  $X_0 = [2500]^T$  for a range of input voltage values and the plot of the bifurcation diagram is shown in Fig. 12. The Jacobian matrix for the simplified cascaded system is obtained from the discrete mapping model and is presented in equation (18). By developing the Jacobian matrix, the system is again iterated, and the eigenvalues are obtained using the period-1 and period-2 conditions given by the equations (20) and (21). The eigenvalues of the simplified cascaded system of Fig. 10 for period-1 ( $\lambda_1$ ) and period-2 ( $\lambda_2$ ) orbits are shown in Table 3. The eigenvalues for period-1 at a source voltage of 35V are plotted in Fig. 13 and the eigenvalues for period-2 at a source voltage of 25V are plotted in Fig. 14.

It can be seen from the plots of the eigenvalues that one of the eigenvalues for period-2 is outside the unit circle which

| V <sub>s</sub> (V) | $\lambda_1$                  | $\lambda_2$            |

|--------------------|------------------------------|------------------------|

| 35                 | $0.8633, 0.9507\pm j 0.0231$ | 0.8738, 0.9770, 0.9891 |

| 25                 | 0.9512, 0.9705, 0.8759       | 1.3526, 0.9715, 0.8754 |

**FIGURE 12.** Bifurcation diagram of the proposed system iterated from state  $X_0$ .

FIGURE 13. Eigenvalues of period-1 orbit.

indicates the non-linear behavior of the source boost converter as the voltage is decreased. The results obtained from the simulation, mathematical model, and hardware circuit are the same. When a DC-DC converter is regulated accurately at a specific equilibrium point with its fast enough dynamic response for a given practical application, it can be thought to operate as an FPL when all the components are considered ideal. Therefore, it can be generalized from the above analysis which simplifies the cascaded DC-DC converter system with suitable assumptions that the discrete mapping model is a suitable model for the analysis of bifurcation phenomena

FIGURE 14. Eigenvalues of period-2 orbit.

in the cascaded multiple outputs DC-DC converter systems having any configuration.

The theoretical and experimental study presented in this paper provides adequate support for the modeling of modern renewable energy sources where input voltage varies with time. The proposed structure of the converters and investigations can be applied in DC distribution and DC microgrids with multiple input-output configurations to improve the stability and eliminate the complex non-linear dynamic behavior of load converters in the system.

#### **V. CONCLUSION**

This paper presents a configuration of the cascaded multiple output DC-DC converters to eliminate complex non-linear dynamic behavior and improve the stability when subjected to varying source voltage. The proposed cascaded DC-DC converter system consists of one source boost converter, one load Buck converter, one load Cuk converter, and a SEPIC converter. All the converters in the proposed system are engaged with a current-mode controller with a compensation network technique in which an outer voltage feedback loop and an inner inductor current feedback loop are used along with an offset divided voltage protection circuit and an RS-latch. The simulation and experimental results reveal that the source boost converter undergoes period-2 orbit and ultimately chaos when the input voltage of the source boost converter is decreased. However, it is verified that all the converters that are acting as a load in the proposed system continue to operate in the stable period-1 orbit and the input voltage of the source boost converter does not affect their stability. The discrete mapping model is developed by considering all the load converters as FPLs because of their stable behavior which also generalizes it for other types of converters. The Jacobian matrix is developed using the data of the discrete mapping model and the eigenvalues are obtained which are close to 1. So, by decreasing the input source voltage, the eigenvalues move out of the unit circle which results in period-2 behavior of the system that severely affects the stability of the whole cascaded converter system. The proposed structure makes load converters in the system insensitive towards input voltage variation which has been demonstrated analytically and using experimental results.

#### ACKNOWLEDGMENT

This research was executed under the Higher Education Commission of Pakistan, Project NRPU-9798 in Electric Machines Drives Laboratory, UET, Lahore.

#### REFERENCES

- C. M. F. S. Reza and D. D.-C. Lu, "Recent progress and future research direction of nonlinear dynamics and bifurcation analysis of grid-connected power converter circuits and systems," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 4, pp. 3193–3203, Dec. 2020.

- [2] A. Kargarian, J. Mohammadi, J. Guo, S. Chakrabarti, M. Barati, G. Hug, S. Kar, and R. Baldick, "Toward distributed/decentralized DC optimal power flow implementation in future electric power systems," *IEEE Trans. Smart Grid*, vol. 9, no. 4, pp. 2574–2594, Jul. 2018.

- [3] J. W.-T. Fan and H. S.-H. Chung, "Bifurcation phenomena and stabilization with compensation ramp in converter with power semiconductor filter," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9424–9434, Dec. 2017.

- [4] M. Schuck and R. C. N. Pilawa-Podgurski, "Ripple minimization through harmonic elimination in asymmetric interleaved multiphase DC–DC converters," *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 7202–7214, Dec. 2015.

- [5] A. Braitor, G. C. Konstantopoulos, and V. Kadirkamanathan, "Stability analysis and nonlinear current-limiting control design for DC micro-grids with CPLs," *IET Smart Grid*, vol. 3, no. 3, pp. 355–366, Jun. 2020.

- [6] W. Jiang, S. Xue, L. Zhang, W. Xu, K. Yu, W. Chen, and L. Zhang, "Flexible power distribution control in an asymmetrical-cascaded-multilevelconverter-based hybrid energy storage system," *IEEE Trans. Ind. Electron.*, vol. 65, no. 8, pp. 6150–6159, Aug. 2018.

- [7] R. Xu, Y. Zhang, L. Wang, G. Chen, S. Liu, and H. Wen, "Research on slow-scale bifurcation phenomenon of PFC cascade converter," *IET Power Electron.*, vol. 9, no. 15, pp. 2824–2832, Dec. 2016.

- [8] F. Xie, B. Zhang, D. Qiu, and Y. Jiang, "Coexistence of fast-scale and slow-scale instabilities in DC cascaded converters system with multi-load converters," in *Proc. IEEE 7th Int. Symp. Power Electron. Distrib. Gener. Syst. (PEDG)*, Vancouver, QC, Canada, Jun. 2016, pp. 27–30.

- [9] P. Deivasundari, G. Uma, and R. Poovizhi, "Analysis and experimental verification of Hopf bifurcation in a solar photovoltaic powered hysteresis current-controlled cascaded-boost converter," *IET Power Electron.*, vol. 6, no. 4, pp. 763–773, Apr. 2013.

- [10] X. Li, X. Zhang, W. Jiang, J. Wang, P. Wang, and X. Wu, "A novel assorted nonlinear stabilizer for DC–DC multilevel boost converter with constant power load in DC microgrid," *IEEE Trans. Power Electron.*, vol. 35, no. 10, pp. 11181–11192, Oct. 2020.

- [11] Q. Xu, Y. Yan, C. Zhang, T. Dragicevic, and F. Blaabjerg, "An offset-free composite model predictive control strategy for DC/DC buck converter feeding constant power loads," *IEEE Trans. Power Electron.*, vol. 35, no. 5, pp. 5331–5342, May 2020.

- [12] W. He and R. Ortega, "Design and implementation of adaptive energy shaping control for DC–DC converters with constant power loads," *IEEE Trans. Ind. Informat.*, vol. 16, no. 8, pp. 5053–5064, Aug. 2020.

- [13] S. Zhou, G. Zhou, Y. Wang, X. Liu, and S. Xu, "Bifurcation analysis and operation region estimation of current-mode-controlled SIDO boost converter," *IET Power Electron.*, vol. 10, no. 7, pp. 846–853, Jun. 2017.

- [14] W. Hu, B. Zhang, R. Yang, and D. Qiu, "Dynamic behaviours of constant on-time one-cycle controlled boost converter," *IET Power Electron.*, vol. 11, no. 1, pp. 160–167, Jan. 2018.

- [15] P. Deivasundari, G. Uma, C. Vincent, and K. Murali, "Non-linear intermittent instabilities and their control in an interleaved DC/DC converter," *IET Power Electron.*, vol. 7, no. 5, pp. 1235–1245, May 2014.

- [16] S. Kapat, "Sampling-induced border collision bifurcation in a voltagemode DPWM synchronous buck converter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 6, pp. 1048–1052, Jun. 2019.

- [17] R. Munuswamy, U. Govindarajan, and K. Anbukumar, "Performance comparison and stability analysis of ACM and ENLC controlled SEPIC PFC converter," *IET Power Electron.*, vol. 13, no. 5, pp. 991–1001, Apr. 2020.

- [18] A. K. Singha, S. Kapat, S. Banerjee, and J. Pal, "Nonlinear analysis of discretization effects in a digital current mode controlled boost converter," *IEEE J. Emerg. Sel. Topics Circuits Syst.*, vol. 5, no. 3, pp. 336–344, Sep. 2015.

- [19] S. Zhou, G. Zhou, S. Zeng, S. Xu, and H. Ma, "Unified discrete-mapping model and dynamical behavior analysis of current-mode controlled singleinductor dual-output DC–DC converter," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 1, pp. 366–380, Mar. 2019.

- [20] J. D. Morcillo, D. Burbano, and F. Angulo, "Adaptive ramp technique for controlling chaos and subharmonic oscillations in DC–DC power converters," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 5330–5343, Jul. 2016.

- [21] W. Hu, B. Zhang, and R. Yang, "Bifurcation mechanism and stabilization of V2C controlled buck converter," *IEEE Access*, vol. 7, pp. 77174–77182, 2019.

- [22] E. D. Tsirbas, F. V. Topalis, and E. N. Skoubris, "Non-linear bifurcation method to determine the boost converter switching frequency," *IET Power Electron.*, vol. 13, no. 11, pp. 2372–2379, Aug. 2020.

- [23] W. Ma, L. Wang, R. Zhang, J. Li, Z. Dong, Y. Zhang, M. Hu, and S. Liu, "Hopf bifurcation and its control in the one-cycle controlled Cuk converter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 8, pp. 1411–1415, Aug. 2019.

**SAJJAD AHMED** (Graduate Student Member, IEEE) received the bachelor's (Hons.) and master's degrees in electrical engineering from the University of Engineering and Technology, Lahore, Pakistan, in 2017 and 2019, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering. From June 2017 to September 2018, he served as a Hardware Design Engineer with MicroTech Industries Pvt. Ltd., Pakistan. From September 2018 to May 2019, he was a

Graduate Assistant with the Department of Electrical Engineering, University of Engineering and Technology, where he is currently a Teaching Assistant. His research interests include power electronics, control systems, electronic hardware design, and embedded systems development. He has been the reviewer for some popular journals, including IEEE Access and *IET Power Electronics*.

**SYED ABDUL RAHMAN KASHIF** received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the University of Engineering and Technology (UET), Lahore, Pakistan. From 2009 to 2010, he worked as a Researcher with the Power Electronics Laboratory, University of Paderborn, Germany. He is currently serving as an Associate Professor with the Department of Electrical Engineering, UET. His research interests include power electronics, the control of elec-

trical machines, smart grids, renewable energy systems, and the optimization of power systems.

**NOOR UL AIN** received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Engineering and Technology, Lahore, Pakistan, in 2013 and 2016, respectively. From 2014 to 2016, she was a Lab Engineer with the Department of Electrical Engineering, University of Engineering and Technology, where she is currently serving as a Lecturer. Her research interest includes power electronics and power systems.

**AKHTAR RASOOL** received the M.Sc. and B.Sc. degrees in electrical engineering, in 2009 and 2007, respectively, and the Ph.D. degree in mechatronics engineering with thesis title "Control of Converters as Source for Microgrid," in 2017.

Since April 2018, he has been serving as an Assistant Professor and the Director Quality Enhancement Cell with the Sharif College of Engineering and Technology, Lahore (Affiliated College of University of Engineering and Technology,

Lahore). Earlier, he has served as a Lab Engineer with the Government College University Faisalabad till January 2008, a Teaching Assistant with Sabanci University till July 2017, a Lecturer with Hajvery University till 2012, and an Assistant Professor with the University of Engineering and Technology, Taxila, till April 2018. Beside the academic roles, he has also served a vast range of industries through services and consultancy firms, PRESCON Engineering Pvt Ltd., Orient Energy Systems Pvt. Ltd., and AGITROL Solution Pvt Ltd. He is also actively involved in training for the Quality Enhancement, Objectives Based Education (OBE), and Objectives Based Assessment (OBA) techniques. His research interests include control of converters with applications ranging integration of renewable energy resources, microgrids, smart grid, electrical machines, automated electrical vehicles, electrical trains, automatic braking, steering, robotic actuators, energy management, process control, cascaded control applications, high voltage assets' life assessment, and biomedical applications with artificial intelligence.

He is serving as an Associate Editor for World Journal of Engineering (Emerald), an Editorial Advisory Member of International Journal of Electrical Engineering and Computing, and LC International Journal of STEM, beside reviewing for many prestigious journals from IEEE, IET, Elsevier, Emerald, and other publishers, including IEEE TRANSACTIONS ON ENERGY CONVERSION, IEEE TRANSACTIONS ON POWER SYSTEMS, and IET Power Electronics, and Energy Reports.

**MUHAMMAD SOHAIB SHAHID** received the bachelor's and master's degrees in power system from the University of Engineering and Technology, Lahore, Pakistan, in 2017 and 2019, respectively. He served as a Lab Engineer with the Department of Electrical Engineering, University of Lahore, Pakistan. He is currently a Junior Engineer with the Department of Metering and Testing, Water and Power Development Authority, Pakistan. His research interests include power elec-

tronics and power system planning and operation. He has an honor of performing his duties as a Graduate Assistant for power electronics and power transmission and distribution labs in his parent university.

**SANJEEVIKUMAR PADMANABAN** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

From 2012 to 2013, he was an Associate Professor with VIT University. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar,

funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. From 2016 to 2018, he served as an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa. From March 2018 to February 2021, he was a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. Since March 2021, he has been working as a Professor with the CTIF Global Capsule (CGC) Laboratory, Department of Business Development and Technology, Aarhus University, Herning, Denmark. He has authored over 300 scientific articles.

Dr. Padmanaban was a recipient of the Best Paper cum Most Excellence Research Paper Award from IET-SEISCON'13, IET-CEAT'16, IEEE-EECSI'19, IEEE-CENCON'19, and five best paper awards from ETAEERE'16 sponsored Lecture Notes in Electrical Engineering, Springer book. He is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He is an Editor/Associate Editor/Editorial Board for refereed journals, in particular the IEEE SYSTEMS JOURNAL, IEEE TRANSACTION ON INDUSTRY APPLICATIONS, IEEE ACCESS, *IET Power Electronics, IET Electronics Letters*, and Wiley-International Transactions on Electrical Energies journal (MDPI), and the Subject Editor for the *IET Renewable* Power Generation, IET Generation, Transmission and Distribution, and FACTS journal (Canada).

**EMRE OZSOY** (Senior Member, IEEE) received the B.S. degree in electrical engineering and the M.S. and Ph.D. degrees in control and automation engineering from Istanbul Technical University (ITU), Turkey, in 2003, 2008, and 2014, respectively. He has 13 years of industrial experience in electrical and automation engineering. He was a Postdoctoral Research Fellow with the University of Johannesburg, South Africa, in 2017. He currently works as a Research and Development Engi-

neer with Research and Development Center, Danfoss Drives, Gråsten, focusing on harmonic mitigation and filtering of drive systems.

**MUHAMMAD ASGHAR SAQIB** graduated in electrical power engineering from the Department of Electrical Engineering, University of Engineering and Technology, Lahore, Pakistan, in 1991. He received the master's and Ph.D. degrees in electrical power engineering from the University of Sydney, Australia, in 1996 and 1999, respectively. In 2005, he joined the Faculty of Electronics Engineering, GIK Institute, Topi, Pakistan, as an Assistant Professor, an Associate Professor, and

the Dean of the Faculty. He is currently working as a Professor with the Department of Electrical Engineering, University of Engineering and Technology, Lahore. His research interests include electrical system protection, drives, power electronics, electrical arcs, and power system operation and control.