# Mixed-Order Sturdy MASH $\Delta$ - $\Sigma$ Modulator

N. Maghari, S. Kwon, G. C. Temes, and U. Moon

Electrical Engineering and Computer Science Oregon State University, Corvallis, Oregon

Abstract—An enhanced version of Sturdy MASH (SMASH) [2] delta-sigma modulator is proposed. This structure takes advantage of the well-known stability of the MASH structure while greatly reducing its sensitivity to imperfect circuit blocks. Furthermore, no digital noise cancellation filters are needed. Hence there is no matching requirement for the analog and digital paths. With the proposed enhancement in noise shaping, the first and second stage quantization noise experience different (thus mixed) orders of noise shaping, and the accuracy of this modulator is comparable of that of the MASH structure. Simulations results and mathematical analysis demonstrate the effectiveness of this structure.

#### I. INTRODUCTION

Delta-Sigma modulators (DSMs) are mostly used in highaccuracy, low-to-medium bandwidth applications, benefiting from oversampled operation. Oversampling allows achieving high accuracy without necessarily using accurate circuit elements. This, however, comes at the cost of a higher sampling frequency. For wide-band applications, the sampling frequency may need to be over 200 MHz to satisfy the required SNR. This may require large bias power for the amplifiers in the modulator, and the speed of the amplifiers may exceed the transit frequency of the given technology. To decrease this high sampling frequency, while maintaining the accuracy, higher order modulators must be used.

Commonly used delta-sigma modulator structures are the single loop high order modulator and the multi-stage noise shaping (MASH) structure. The single loop high order DSM can provide high SNR with relaxed circuit specifications, but it is prone to instability. In high order modulators, the stable input range, which is defined by the input signal range that leads to proper operation of the modulator, is limited. The range depends on the number of levels used in DAC and quantizer. When the input signal exceeds the non-overload range, the filtered quantization error may push the output of the modulator into its overload range, which causes the input DAC to process larger signal. This chain reaction results in quantizer overload and hence the saturation of the modulator blocks [1].

On the other hand, the MASH structure may guarantee stable operation by employing several individual modulators but it requires high accuracy integrators to minimize the quantization error leakage resulting from the analog-digital filter mismatches.

Due to the high DC gain requirement for these amplifiers, and the high speed operation required for oversampled operation, these amplifiers become more power hungry as the bandwidth increases.

In this paper, a Mixed-Order Sturdy MASH (MOS-MASH) structure is proposed. This enhanced verion of the MASH structure enables mixed-order of noise shaping for the first and second stage quantization noise in the previously proposed Sturdy MASH structure (SMASH) [2]. Compared to the traditional MASH structures, this structure is less sensitive to circuit non-idealities, such as finite opamp gain and modulator coefficient errors. The paper is organized as follows. Sections II and III provide the properties of the MASH structure, respectively. Section IV presents the principle of operation of the MOS-MASH architecture and the advantages of the SMASH and MOS-MASH topologies. Section IV describes simulation results. Finally, conclusions are drawn in Section V.

## II. MASH STRUCTURE

The MASH structure performs high-order noise shaping by feeding the error of the preceding stage to the next stage, which is usually realized by another delta-sigma loop. Since the quantization error is dithered by the loop filter, it may often be regarded as independent from the input signal of the modulator. In this case, the operation of the second stage is independent of the first stage. Hence the stability of the modulator is determined by the stability of the individual stages, which are usually chosen to be first or second order modulators.

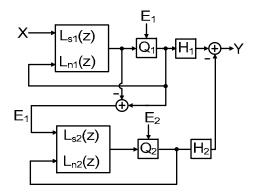

Fig.1 shows the MASH structure. In this figure  $L_{si}$  and  $L_{ni}$  denote the signal and noise loop filters of the *i*<sup>th</sup> stage, respectively. Digital filters  $H_i$  are used to cancel the first stage quantization error. The overall output of the MASH structure shown in Fig. 1 can be written as follows

$$Y = STF_{1}X + (H_{1}NTF_{1} - H_{2}NTF_{2})E_{1} + H_{2}NTF_{2}E_{2}$$

(1)

Here  $STF_i$ ,  $NTF_i$  and  $E_i$  denote the signal transfer function, noise transfer function and quantization error of the *i*<sup>th</sup> stage, respectively. Hence, choosing the digital filters as  $H_1$ = $STF_2$ and  $H_2$ = $NTF_1$  will eliminate the first stage quantization error, and the output will be

This work is supported by the Semiconductor Research Corporation under contract 2005-HJ-1308

Figure 1. Traditional MASH Structure

As a result, the first stage quantization noise is cancelled, and the second stage quantization noise is shaped by the product of the first and the second stage noise transfer functions. In practice, circuit non-idealities will cause  $E_1$  to appear at the output multiplied by  $STF_2NTF_{1a} - NTF_1STF_{2a}$ , where  $NTF_{1a}$  and  $STF_{2a}$  denote the actual analog transfer functions. Most of this leakage is caused by limited opamp DC gain and coefficient mismatches. The former can be reduced using high gain amplifiers, at the cost of more power dissipation, while coefficients mismatch is mostly technology related. Leakage of the first stage quantization error degrades the overall performance of the DSM [1].

#### III. STURDY MASH STRUCTURE

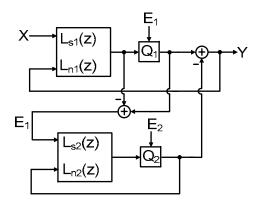

Fig. 2 illustrates the block diagram of the SMASH structure [2]. The first-stage quantization error is fed to the second stage, as in the traditional MASH structures, but the second stage output is directly subtracted from the output of the first stage quantizer, inside the first loop and in the digital domain. Thus, the overall output is given by

$$Y = STF_1 X + NTF_1 (1 - STF_2) E_1 + NTF_1 NTF_2 E_2$$

(3)

As can be seen from the above equation,  $E_2$  is shaped by the product of the first and second stage *NTFs*, as in the traditional MASH structure; however, the first stage quantization error is now shaped by the first stage *NTF* and additionally shaped by  $(1-STF_2)$ .

One way to reduce  $E_1$  is to set  $STF_2=1$  [3]. Ideally, this will completely eliminate the first stage quantization error. But in practice, at least half a clock period delay is required for all subtraction, integration, quantization and addition to take place. In addition to the fact that this zero-delay is a practical impossibility, to remedy this problem without using any additional amplifiers or digital filters, a new method should be developed.

The most effective way to reduce the first stage quantization noise is to use the  $(1-STF_2)$  factor for additional noise shaping [2]. This can be done by properly choosing the second stage *STF*.

Figure 2. General SMASH Structure

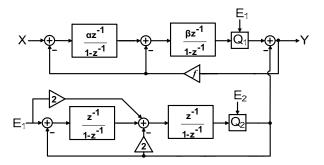

Figure 3. 2+2 SMASH Structure

For example, if the second stage *STF* is chosen to be a delay, i.e.,  $STF_2=z^{-1}$ , an extra first order noise shaping is achieved. Another example is a 2+2 SMASH with  $4^{th}$  order noise shaping for both  $E_1$  and  $E_2$ , which can be realized by choosing the *STF* and *NTF* of the second stage as

$$STF_2 = 2z^{-1} - z^{-2}$$

and  $NTF_2 = (1 - z^{-1})^{-2}$  (4)

A possible implementation is shown in Fig. 3. Depending on the second stage signal transfer function, extra noise shaping can be achieved for the first stage quantization error; however, since the shaping of  $E_2$  is determined by the product of the first and second stage noise transfer functions, it will remain the same. Further reduction for  $E_2$  may be made by employing an inter-stage gain between first and second stages [4], but the overall performance will be limited by the first stage quantization error, as discussed.

#### IV. MIXED-ORDER STURDY MASH STRUCTURE

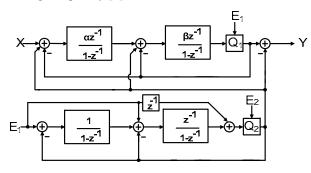

To further enhance this SMASH operation, Mixed-Order SMASH (MOS-MASH) is proposed next. It is shown in Fig. 4. The signal and noise transfer functions of the second stage can be written as follows

$$STF_2 = 3z^{-1} - 3z^{-2} + z^{-3}$$

and  $NTF_2 = (1 - z^{-1})^2$  (5)

Substituting these relations in equation (3) results in

$$Y = STF_1 X + (1 - z^{-1})^5 E_1 + (1 - z^{-1})^4 E_2$$

(6)

As it can be seen from eq. (6), a  $5^{th}$  order noise shaping is achieved for the first stage quantization error, despite the fact that the structure resembles a forth order loop composed of four integrators. Consequently, the noise power of  $E_1$  becomes negligible compared to that of  $E_2$ , which is shaped by a  $4^{th}$  order noise transfer function.

Tight timings for the quantizer and the digital adder used in the first stage loop might become impractical for high sampling rates, especially when DAC linearization techniques are used. Fig. 4 presents an alternative way to eliminate the need for the digital adder. As it can be seen from this figure, the digital adder is replaced by an extra DAC at the input of the  $l^{st}$  and  $2^{nd}$  integrators in the first stage loop and by another relaxed digital adder at the final output.

The contribution of the second stage output to the modulator input, shown in Fig. 4, should be highly accurate, since any error at the modulator input reduces the SNR. Hence, the second stage DAC needs to be highly linear.

This problem can be alleviated by employing two separate DACs at the modulator input to reduce the dynamic element matching complexity [5].

Figure 4. MOS-MASH Structure Using an Additional DAC

As equation (3) shows, both the SMASH and MOS-MASH structures are less sensitive to opamp gain and coefficients errors than the traditional MASH structure: the finite opamp gain and coefficient mismatches will only affect the zeros of the overall *NTF*, and the error will be suppressed by the noise shaping property of the modulator. This is because both *STF* and *NTF* are achieved by means of fully analog components, in contrast with the traditional MASH structure in which digital filters form part of the overall noise transfer function, hence matching between analog loop and digital filters is critical.

Employing fully analog loop filters combines the advantages of the single loop high order DSM with the stability of the MASH structure. Hence, even for high-order modulators, stability is guaranteed and high accuracy can be easily obtained using simple low-gain amplifiers. All these advantages make this structure a good candidate for lowpower, low-voltage applications.

#### V. SIMULATION RESULTS

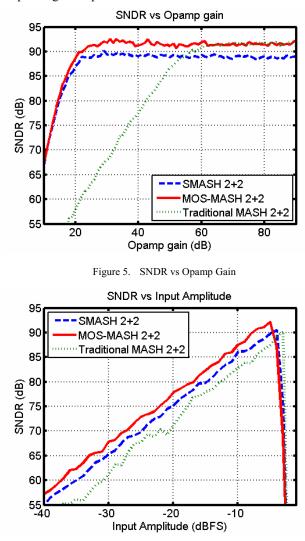

The proposed MOS-MASH structure shown in Fig. 4, along with the SMASH and traditional 2+2 MASH ones, was simulated using MATLAB/Simulink<sup>®</sup>. Fig. 5 illustrates the SNDR versus integrator opamp gain characteristics for all structures. The assumed OSR was 16 for all simulations. For all structures, 15-level quantizers were used in each stage, and a -6dB full-scale input signal was applied. It can be seen that the proposed structure requires less than 30 dB opamp gain, compared with traditional MASH which requires an opamp gain of 60 dB for proper noise shaping. Furthermore, it can be observed that the peak SNR of MOS-MASH structure is comparable to that of the 2+2 MASH structure, without high amplifier gain requirements.

Figure 6. SNDR vs input signal amplitude

Fig. 6 shows the SNDR versus input amplitude curves. For this simulation, an opamp DC gain of 50 dB was used. Due to the direct feedback from the second stage output to the first stage input, the SMASH as well as the proposed MOS-MASH structures saturate slightly earlier than the traditional one. This can be improved by using feed-forward techniques in the first stage, or by increasing the number of the first and/or second stage DAC levels.

Table I compares the peak SNRs of the traditional MASH, SMASH, and MOS-MASH structures with opamp gains of 20 dB and 60 dB. It can be seen that for the traditional MASH, a 35 dB drop in SNR occurs while under the same conditions, SMASH and MOS-MASH shows less than 3 dB drop in SNR as the gain drops from 60 dB to 20 dB.

Finally, Table II summarizes the hardware requirement for both traditional MASH and SMASH structures.

| TABLE I. FEAK SINK VS OPAMP DC GAIN COMPARISO | TABLE I. | PEAK SNR VS OPAMP DC GAIN COMPARISON |

|-----------------------------------------------|----------|--------------------------------------|

|-----------------------------------------------|----------|--------------------------------------|

| Table Head       | Opamp DC gain |         |  |

|------------------|---------------|---------|--|

|                  | 20dB          | 60dB    |  |

| Traditional MASH | 57 dB         | 91.5 dB |  |

| SMASH            | 88 dB         | 88.8 dB |  |

| MOS-MASH         | 89 dB         | 91.4 dB |  |

TABLE II. HARDWARE COMPARISON FOR VARIOUS MASHS

| Table Head           | Table Column Head |                      |  |

|----------------------|-------------------|----------------------|--|

|                      | SMASH             | Traditional MASH 2+2 |  |

| # of digital filters | 0                 | 2                    |  |

| Opamp DC gain        | > 25dB            | > 60dB               |  |

| Saturation level     | -4 dBFS           | -3 dBFS              |  |

| # of DACs            | 8                 | 5                    |  |

### VI. CONCLUSION

An enhanced version of Sturdy MASH (SMASH) [2] structure is proposed. Simulation results verify the effectiveness and robustness of this structure. Compared to the traditional MASH structure which suffers from the finite opamp gain and modulator coefficient variations, the proposed Mixed-Order Sturdy MASH (MOS-MASH) and SMASH structures provide reduced sensitivity to circuit non-idealities, while offering improved stability and enhanced noise shaping. Moreover, the MOS-MASH shows comparable performance to the MASH structure, even using low-gain amplifiers.

#### REFERENCES

- [1] R. Schreier and G. C. Temes, *Understanding Delta-Sigma Data Converters*, Piscataway, NJ: IEEE Press 2005.

- [2] N. Maghari, S. Kwon, G. C. Temes, and U. Moon, "Sturdy MASH Δ-Σ Modulator," *Electron. Lett.*, vol. 42, pp. 1269-1270, Oct. 2006.

- [3] P. Benabes, A. Gauthier, and R. Kielbasa,"New High-Order Universal  $\Sigma \Delta$  Modulators," *Electron. Lett.*, vol. 31, pp. 8-9, Jan. 1995.

- [4] I. Fujimori et al., "A 90-dB SNR 2.5-MHz Output-Rate ADC Using Cascaded Multibit Delta-Sigma Modulation at 8× Oversampling Ratio," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1820-1828, Dec. 2000.

[5] S. Kwon and F. Maloberti, "A 14mW Multi-bit Delta-Sigma Modulator with 82dB SNR and 86dB DR for ADSL2+," in *ISSCC Dig. Tech. Papers*, Feb. 2006, pp. 68-69.