# Mobility Enhancement Technology for Scaling of CMOS Devices: Overview and Status

YI SONG,  $^{1,2}$  HUAJIE ZHOU,  $^1$  QIUXIA XU,  $^1$  JUN LUO,  $^1$  HAIZHOU YIN,  $^1$  JIANG YAN,  $^1$  and HUICAI ZHONG  $^1$

1.—Key Laboratory of Microelectronics Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing, China. 2.—e-mail: songyi@ime.ac.cn

The aggressive downscaling of complementary metal-oxide-semiconductor (CMOS) technology to the sub-21-nm technology node is facing great challenges. Innovative technologies such as metal gate/high-k dielectric integration, source/drain engineering, mobility enhancement technology, new device architectures, and enhanced quasiballistic transport channels serve as possible solutions for nanoscaled CMOS. Among them, mobility enhancement technology is one of the most promising solutions for improving device performance. Technologies such as global and process-induced strain technology, hybrid-orientation channels, and new high-mobility channels are thoroughly discussed from the perspective of technological innovation and achievement. Uniaxial strain is superior to biaxial strain in extending metal-oxide-semiconductor field-effect transistor (MOSFET) scaling for various reasons. Typical uniaxial technologies, such as embedded or raised SiGe or SiC source/ drains, Ge pre-amorphization source/drain extension technology, the stress memorization technique (SMT), and tensile or comprehensive capping layers, stress liners, and contact etch-stop layers (CESLs) are discussed in detail. The initial integration of these technologies and the associated reliability issues are also addressed. The hybrid-orientation channel is challenging due to the complicated process flow and the generation of defects. Applying new highmobility channels is an attractive method for increasing carrier mobility; however, it is also challenging due to the introduction of new material systems. New processes with new substrates either based on hybrid orientation or composed of group III-V semiconductors must be simplified, and costs should be reduced. Different mobility enhancement technologies will have to be combined to boost device performance, but they must be compatible with each other. The high mobility offered by mobility enhancement technologies makes these technologies promising and an active area of device research down to the 21-nm technology node and beyond.

**Key words:** Nanoscale CMOS device, mobility enhancement technology, process-induced strain, high-mobility channel

#### INTRODUCTION

In the past half-century, the integrated circuit (IC) industry has been growing rapidly, benefiting from the dimensional downscaling of transistors

according to Moore's law as well as larger wafer sizes. This downscaling results in higher performance, lower power consumption, more complex functionality, faster device speeds, and lower cost per transistor. As the feature size of MOSFETs shrinks down to sub-21-nm nodes, CMOS technology faces tremendous challenges, including severe short-channel effects (SCEs), degraded drive

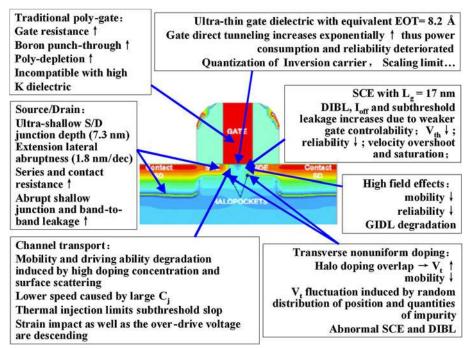

Fig. 1. Main challenges for CMOS technology at the 21-nm technology node. DIBL: drain induced barrier lowering.

Table I. High-performance logic technology requirements for extended planar bulk at the 21-nm technology node as predicted by ITRS 2009 edition

| MPU physical gate length (nm) | Mobility enhancem factor due to stra               |                                | nt Maximal gate<br>leakage current<br>density (kA/cm²) |

|-------------------------------|----------------------------------------------------|--------------------------------|--------------------------------------------------------|

| 17                            | 1.8 (nMOS)/2.3 (pMo                                | OS) 8.2                        | 1.3                                                    |

| Average $V_{\rm dd}$ (V)      | Maximal $I_{\rm on}/I_{\rm off}$ ( $\mu A/\mu m$ ) | Saturated threshold voltage (V | 7) Intrinsic delay (ps)                                |

| 0.81                          | 1680/0.1 (nMOS),<br>1377/0.1 (pMOS)                | 10.3021                        | 0.45 (nMOS)/0.55 (pMOS)                                |

MPU: Micro processor unit.

capability, boron penetration and polysilicon depletion, high-field effects, direct gate tunneling current, and high series resistance. Unprecedented difficulties must be overcome if Moore's law is to be followed. Figure 1 summarizes the main challenges in the scaling of traditional planar bulk MOSFETs, and Table I provides the main projected targets for high-performance logic technology at the 21-nm technology node, as predicted by the *International Technology Roadmap for Semiconductors* (ITRS). <sup>1</sup>

As channel gate lengths are scaled down to the sub-21-nm range, mobility degradation becomes more severe, though mobility still effectively describes FET performance in the quasiballistic conduction state for the overall consideration of different degradation mechanisms.<sup>2</sup> The degradation of carrier mobility and SCEs caused by ultrahigh and nonuniform channel doping, high surface

scattering, and vertical electric fields makes mobility enhancement engineering the most important technique in improving device performance. Three common mobility enhancement methods are (1) uniaxial strain through stress liners, embedded SiGe source/drain for pMOS and SiC source/drain for nMOS, stress memorization or biaxial global strain generated by epitaxial growth of a thin Si layer on top of a relaxed SiGe substrate; (2) the adoption of a hybrid-orientation substrate; and (3) the utilization of group III—V materials or pure germanium as the channel. Mobility enhancement technologies are still effective, even in the ballistic region, where ballistic efficiency and the injection velocity can be increased.

In the following sections of this paper, various mobility enhancement technologies will be thoroughly reviewed, and possible future trends will also be discussed.

## GLOBAL (BIAXIAL) AND PROCESS-INDUCED (UNIAXIAL) STRAIN

The introduction of stress into a silicon channel is desirable because of its low cost, compatibility with traditional CMOS processing, and high efficiency compared with new channel materials with high mobility, such as Ge and III–V materials. There are two major techniques to exert strain on a Si channel: imposing global biaxial strain on the entire wafer and locally applying uniaxial strain to certain areas.

## **Global Biaxial Strain**

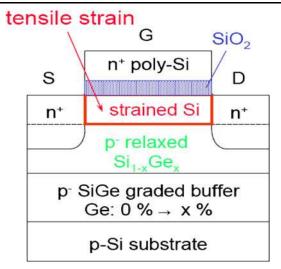

In Fig. 2, the biaxial tensile strain at an interface, induced by the crystal lattice mismatch between Si and SiGe, can be realized either by growing a thin Si layer on a relaxed SiGe substrate epitaxially<sup>5</sup> or growing strained silicon directly on an insulator by a bond and etch-back technique. Consequently, in the energy band of the strained Si, the sixfolddegenerate valleys are split into two sets of twofold and fourfold bands, giving rise to enhanced carrier transport. Furthermore, the repopulation of the energy bands and the reduction of intervalley phonon scattering boost carrier mobility significantly, especially for bulk nMOSs. Biaxial strain can also be introduced by SiGe-free strained siliconon-insulator (SOI) technology, which uses a wafer bonding technique. Devices fabricated using this method are free of high off-state leakage due to the elimination of dislocation cores at the strained Si/SiGe interface.<sup>8,9</sup> It was demonstrated that nMOSs exhibit a 112% electron mobility enhancement and nearly ideal subthreshold slopes of 66 mV/dec. 10

Biaxial global strain technology possesses inherent and obvious drawbacks, however, which make it difficult to implement in practice. First, when the Ge content (%) reaches a moderate value, the elec-

Fig. 2. nMOS with strained Si channel grown epitaxially on relaxed SiGe substrate (Reprinted from Ref. 11 with permission. Copyright 2001, IEEE publisher).

tron mobility enhancement will saturate. Moreover, this mobility enhancement will be significantly impaired at high electric fields due to surface roughness scattering. Additionally, to enhance the mobility for holes, high Ge contents (>30%) are usually required, which conflicts with the moderate Ge content requirement for electron mobility enhancement. Therefore, the compromise in mobility enhancement between electrons and holes remains a significant challenge. 11 Complex processes, defects, high costs, and self-heating effects arising from the low thermal conductivity of SiGe also limit its applicability.

As device dimensions shrink, strain is, however, offset by the augmented effective field and corresponding quantum confinement effects, which lead to reduced hole mobility. Moreover, at high processing temperatures, the strain will be released in the form of dislocations, and Ge may diffuse into the strained Si layer or even further to the interface of the strained Si/gate dielectric layer, which narrows the processing window of the thermal budget.

## **Uniaxial Process-Induced Strain**

With respect to aggressively downscaled MOS-FETs, uniaxial strain is superior to biaxial strain in the following aspects: (1) Uniaxial stress can offer high hole mobility enhancement in both low strain and high vertical electric fields due to additive strain and confined splitting, larger two-dimensional in-plane density of states, and smaller conductivity mass; 12 (2) Uniaxial stress-enhanced electron and hole mobilities mainly arise from reduced conductivity effective mass<sup>13</sup> versus reduced scattering for biaxial stress. Therefore, uniaxial stress provides larger drive current improvement for nanoscaled short-channel devices with minimal increases in manufacturing complexity. 14 (3) Uniaxial stress causes *n*-channel threshold voltage shifts that are approximately five times smaller<sup>15</sup> and, thus, do not require adjustment in substrate uniaxial doping. (4) Process-induced increases with decreasing channel length. <sup>16</sup> (5) A uniaxially strained device shows much better reliability.<sup>17</sup> (6) Smaller leakages arise from reduced bandgap narrowing, as compared with biaxial tensile stress, which causes much greater band-to-band tunneling (BTBT) leakage. (7) Significantly less strain (5×) is required for hole mobility enhancement when applying longitudinal uniaxial compression versus in-plane biaxial tension using the conventional SiGe substrate approach. Therefore, process-induced uniaxial stress is very promising for scaling down CMOS technology as per the goals of the proposed roadmap.

However, the drawbacks of uniaxial stress (e.g., the localized stress dependence on device size and defects from additional processes) may affect the overall performance and must be addressed carefully.

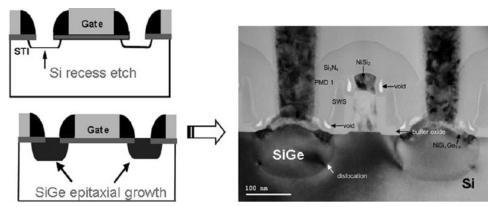

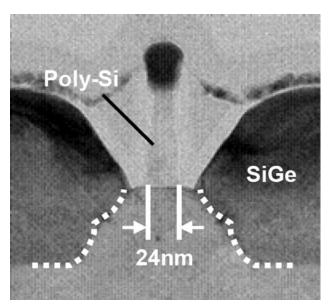

Fig. 3. Formation of embedded source/drain regions (left panel) and a cross-sectional transmission electron microscopy image of a pMOS transistor with an embedded SiGe stressor (right panel). (Reprinted from Ref. 16 with permission. Copyright 2006, IEEE publisher).

Uniaxial stress introduced from manufacturing processes, such as shallow-trench isolation (STI)<sup>19</sup> or silicidation, have already been implemented at the 90-nm technology node.<sup>20</sup> However, STI-originated stress causes both dislocations and electron mobility degradation as well as increased junction leakage as a result of bandgap narrowing.<sup>21</sup> Moreover, the gate direct tunneling current of holes in the inverted regime increase as STI-induced stress increases, as the growth of the gate oxide is slowed by the stress.<sup>22</sup> Therefore, uniaxial stress introduced by STI and silicide may need to be suppressed<sup>23</sup> to suppress junction leakage.<sup>24</sup>

Other promising ways to induce uniaxial strain, such as use of a stress nitride contact etch-stop layer (CESL)<sup>25,26</sup> in the recessed source/drain regions filled with SiGe for pMOSs<sup>27</sup> and SiC for nMOSs, and the stress memorization technology<sup>28,29</sup> for nMOSs, are discussed below.

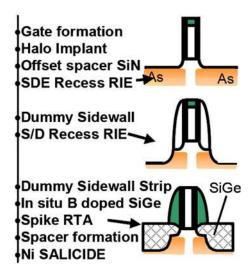

## Embedded or Raised SiGe and SiC Source/Drain

Figure 3 shows one way to fabricate an embedded or raised SiGe/SiC source/drain. First, the source/drain regions are etched to form recessed regions. Then, SiGe (pMOS) or SiC (nMOS) grows epitaxially in the recessed regions. A 35% improvement in the drive current of pMOSs with embedded SiGe source/drain was demonstrated.<sup>30</sup>

To drive Ge deeper into the source/drain regions and, thus, further increase the strain, a local Ge condensation technique without recessed etching was proposed. The key to this technique is selective epitaxial growth (SEG) of Si<sub>0.7</sub>Ge<sub>0.3</sub> in the source/drain regions, followed by dry oxidation at 950°C or higher to drive Ge into the source/drain regions. The embedded SiGe induces lateral compressive stress, which leads to the reduction in the effective mass of holes and consequently a significant saturation drive current enhancement of 38%. 33

Regarding the application of  $Si_{1-x}Ge_x$  stressors, trade-offs between performance and leakage as a function of  $Si_{1-x}Ge_x$  depth, Ge concentration, pro-

cess sequence, geometry, and layout must be considered carefully.  $^{32,34}$  Although deeper  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  layers, higher Ge concentration, and higher source/drain elevation result in larger strain, the leakage simultaneously increases because SiGe approaches the metallurgical junction. Implantation and annealing after SiGe regrowth is not desirable because of the high junction leakage induced by bandgap narrowing due to the Ge mole fraction as well as the compressive stress in SiGe. The improvement in the current is also sensitive to the orientation of the Si channel because the piezore-sistance is directional.

With a longitudinal compressive stress above 1 GPa in the channel, a low-field mobility enhancement of 140% is observed. This significant improvement is explained by band repopulation and transverse mass modulation. <sup>35</sup>

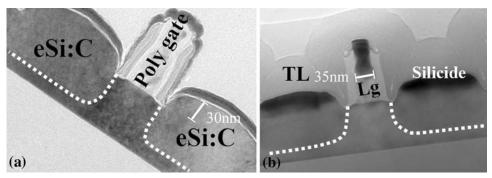

The incorporation of a Si:C stressor in source/ drain regions could exert lateral tensile stress in the channel, which is beneficial to nMOSs. A straightforward approach is to recess the source and drain regions by etching and then deposit Si:C using a selective epitaxial process.<sup>36</sup> High-performance nMOSs with epitaxially grown phosphorus-doped SiC source/drain stressors have been demonstrated.<sup>37</sup> SiC strain is fully preserved through epitaxial-last processes with only one laser annealing step, and low parasitic resistance is achieved by in situ phosphorus-doping  $(3 \times 10^{20} \text{ cm}^{-3} \text{ to } 4.8 \times 10^{20} \text{ cm}^{-3})$ 10<sup>20</sup> cm<sup>-3</sup>) and intimate stressor-to-channel proximity (10 nm to 20 nm). A mobility enhancement of 13% and a corresponding on-current enhancement of 9% in control devices with gate lengths of 60 nm have been achieved. Furthermore, the Si:C stressor and tensile stress liner (TL) are integrated at the 45-nm node. The ground rules and processes involved in the aforementioned techniques are shown in Fig. 4. nMOSs with Si:C stressors (1.9% substitutional C and  $3\times 10^{20}~{\rm cm}^{-3}$  P) showed a 25% enhancement in mobility and 9% enhancement in on-current over the best 45-nm node baseline using the stress memorization technique (SMT) and tensile liner stressors.<sup>38</sup>

Fig. 4. Cross-sectional transmission electron microscopy (TEM) images of typical eSi:C poly-gate nMOS device: (a) post epitaxial growth and (b) post device fabrication to first metal (M1) (Reprinted from Ref. 38 with permission. Copyright 2008, IEEE publisher).

The critical issue in enabling eSi:C stressors for high-performance nMOSs with short channels and thin gate oxides is the source/drain extension doping concentration, which strongly affects the extension structural and electrical connectivity. The drawbacks of in situ-doped SiC stressor technology are also evident. It is difficult to grow Si:C stressors with  $[C]_{sub} > 1$  at% due to the extremely low solid solubility of C in Si; it is also difficult to keep C atoms at substitutional sites during thermal processing, which causes stress loss. Recently, solid-phase epitaxy (SPE) has provided an excellent way to fabricate nMOSs with eSi:C stressors. For SPE growth of eSi:C stressors, C is first implanted into a Si substrate, and then an amorphous layer with C atoms is formed. Upon thermal treatment at low temperature, the amorphous layer will completely regrow with C atoms at the substitutional positions.<sup>39</sup> A tensile stress of 615 MPa was generated in a channel with a record high 1.65 at.% substitutional C concentration in the source and drain regions, resulting in a 35% improvement in electron mobility.

# Ge Pre-amorphization Source/Drain Extension Technology

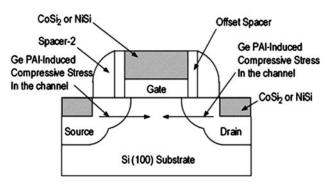

Germanium pre-amorphization implantation (PAI) for source/drain extension of pMOSs is a meaningful method for maintaining a high effective hole mobility at a high vertical electric field. An improvement of up to 32% in the effective mobility of holes is obtained at a vertical electric field of 0.6 MV/cm for a pMOS with a gate length of 90 nm, as shown in Fig. 5.40 The scalability of this technique has been demonstrated without any influence on electron mobility. source/drain extension implantation is performed by Ge PAI and low-energy implantation after offset spacer formation. The Ge PAI method not only suppresses boron ion channeling but also improves the activation efficiency of boron. This leads to a 38% and 109% improvement in junction depth and surface concentration, respectively. More importantly, the Ge PAI method also introduces a large uniaxial compressive stress in the channel, which significantly improves the hole mobility. As an ion implantation process, the

Fig. 5. Schematic of a strained-channel pMOS with uniaxial compressive stress of the channel induced by Ge PAI for source/drain extension (Reprinted from Ref. 40 with permission. Copyright 2008, IEEE publisher).

dose and energy of Ge implantation should also be optimized carefully to balance between strain effects and the leakage of ultrashallow junctions.

An improvement in the effective hole mobility of up to 43% has been achieved for a pMOS with a 35-nm gate length and optimized Ge PAI with a vertical effective field of 1.1 MV/cm. A significant comprehensive strain of up to -3.0% has been confirmed by zero-order Laue zone diffraction with large-angle convergent-beam electron diffraction patterns in a transmission electron microscope. The depth profiles of residual compressive strain and shear strain in the channel are also shown.<sup>41</sup> By using Ge PAI, a high-performance CMOS of 22-nmgate-length, and well behaved 32 dividers embedded with a 201-stage ring oscillator based on the 27-nm-gate-length CMOS technology, have been fabricated. The strained channel induced by Ge PAI for source/drain extension demonstrates that this technique is simple, low cost, and highly manufacturable.

#### Stress Memorization Technique (SMT)

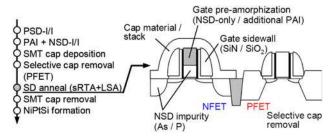

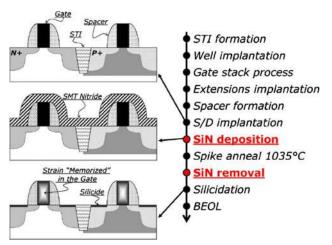

As a design rule, such as for the shrinking of gate pitch, the effects of stress liners and epitaxial SiGe growth in the source/drain regions are weakened because of reduced source/drain areas. Therefore, the SMT is emerging as a way to overcome the drawbacks of stress liners and epitaxial stressors. As shown in

Fig. 6. Typical process sequence and key process parameters of the selective SMT for nMOS. NSD: NFET source/drain, PSD: PFET source/drain (Reprinted from Ref. 43 with permission. Copyright 2008, IEEE publisher).

Fig. 6, the SMT for nMOS devices is introduced by selective deposition of a high-tensile nitride layer on an  $n^+$  poly-Si gate electrode as a stressor with polyamorphous implantation performed in advance. This high-tensile nitride capping layer is removed after poly-recrystallization and source/drain activation. A current drivability improvement greater than 15% has been obtained for nMOSs due to the memorized strain underneath the poly-gate electrode without any degradation of the pMOS.  $^{42}$

Grain growth leads to gate volume expansion, which induces large stresses in polysilicon. The memorized stress in the poly-gate results in high vertical compressive strain in the channel. Because P diffuses into the channel, deteriorating the short-channel effects, it is not suitable as an *n*-type impurity. Using additional laser-spike annealing (LSA) after spike rapid thermal annealing (RTA) for SMT annealing, a thicker SMT layer and sidewall spacer materials with high Young's moduli will induce larger stain; however, physical damage to the gate oxynitride is also induced. Therefore, compromises between larger strain and lower leakage are required. Optimized PAI conditions and tilted buffer implantation technique are required to suppress implantation damage to the upper part of the sidewalls and the defects at the sidewall edges.

When SMT applied to an initially low-stress film, its stress significantly increases after spike annealing. This distinct shift in stress effectively memorizes the stress in the poly-Si gate; additionally, it reduces the gate leakage of an nMOS because the grain size changes during the SMT process, affecting the interface between poly-Si and the gate oxide, which modulates the barrier height in poly-Si.

The layout dependency of the SMT is small due to uniform strain across the channel, which makes the SMT suitable to be integrated into aggressively scaled CMOS with tight scaling rules. The SMT does not degrade  $V_{\rm th}$  mismatch, and the  $T_{\rm pd}$ -power curve is shifted to the left, which denotes a lower standby power. <sup>44,45</sup>

A surprising discovery was that the performance improvement of nMOSs is not related to the intrinsic stress level of the nitride layer but merely relates to the SiN porosity. As the density and Young's modulus of SiN increase, the stress created in the poly-Si gate increases, which is more beneficial to an nMOS. Reducing either the gate length or width is significantly helpful for the stress level as well as the transconductance. Reducing the gate pitch, however, will impair drive current gain because of the lower SiN layer rigidity between two neighboring gates with reduced SMT efficiency.

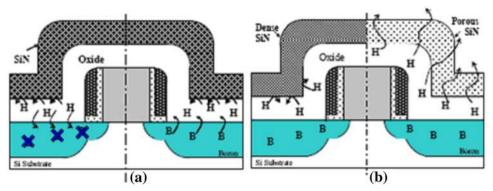

The incorporation of the SMT into CMOS fabrication should ideally improve the performance of an nMOS without degradation of pMOS. Selective removal of the capping tensile layer in a pMOS requires four additional process steps, including a specific lithography step, which significantly complicates the fabrication process. By optimizing the properties of the capping nitride, dopant activation, and poly-Si gate mechanical stress, a novel SMT for 45-nm CMOS with neither additional steps nor masks was proposed, 46 displaying a performance improvement of 7% for nMOS and no performance degradation for pMOS. The possible performance degradation of a pMOS (i.e., reduction in the inversion capacitance slope and increase in subthreshold slope) is attributed to hydrogen within the capping oxide, which cannot be flushed out due to the SiN capping layer, causing B deactivation and exodiffusion, as shown in Fig. 7a. A porous SiN layer with a high deposition temperature can prevent the performance degradation of pMOS due to the removal of H, as shown in Fig. 7b.

Recently, Ortolland claimed that the degradation of pMOS is not simply due to strain effects but is strongly influenced by the hydrogen content of the SMT stressor layer. Based on this assumption, a maskless SMT process without pMOS performance degradation (Fig. 8) has been proposed. The key to this technique is to utilize an ultraviolet (UV)-cured nitride stressor with a low concentration of hydrogen in conjunction with optimized channel orientation to avoid the degradation of pMOSs while maintaining the performance improvement of nMOSs. X-ray diffraction (XRD) results show that the performance gain in an nMOS results not only from the mechanical stress created in the poly-Si gate during SMT processing but also from the additional contribution of the source/drain regions.

## Stress Liners as a Contact Etch-Stop Layer

The introduction of a strain CESL (tensile and compressive liners for nMOSs and pMOSs, respectively) is an efficient way to enhance mobility. A CESL with intrinsic tensile stress tends to shrink; however, the shrinkage is counteracted by the stress induced in the source/drain, gate, and spacer regions, as the CESL is restrained within these regions. The stress in the source/drain, spacer, and gate regions is finally transferred to the channel. For the case of intrinsic tensile stress, the CESL expands the poly-gate and the channel regions, resulting in tensile stress in the channel. On the

Fig. 7. (a) Schematic representation of hydrogen effects on boron deactivation and exodiffusion; (b) schematic representation of nitride with/without hydrogen flush through (Reprinted from Ref. 46 with permission. Copyright 2006, IEEE publisher).

Fig. 8. Schematic illustration of the maskless SMT process without degradation of pMOS performance. BEOL: back end of the line (Reprinted from Ref. 47 with permission. Copyright 2009, IEEE publisher).

sidewall of the spacers, the vertical shrinkage of the CESL leads to compression of the poly-gate region, which, in turn, produces compressive vertical stress in the gate material and channel. It is worth noting that CESL technology is not compatible with source/ drain stressors such as  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  and  $\mathrm{Si}_{1-x}\mathrm{C}_x$  for reduced gate topography. An intrinsic tensile (compressive) stress in a CESL results in a tensile (compressive) parallel stress in the channel and a compressive (tensile) vertical stress. A thicker CESL leads to larger channel stress, but the stress starts to saturate for CESLs thicker than 40 nm to 50 nm. 48 A parallel tensile stress and a vertical compressive stress induced by a CESL with intrinsic tensile stress are favorable for electron mobility, whereas only the parallel stress induced by a CESL with intrinsic compressive stress is helpful for enhancement of hole mobility. It is crucial that the spacer width is scaled proportionally to the gate length in order to reduce the layout sensitivity of both the vertical and parallel stress and to preserve the highest possible stress level in the densest layouts.

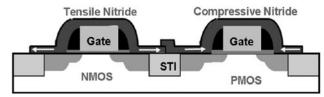

Fig. 9. Dual stress liner process architecture with tensile and compressive silicon nitride capping layers (Reprinted from Ref. 16 with permission. Copyright 2006, IEEE publisher).

A novel method for depositing a liner-stressor material composed of diamond-like carbon (DLC) with a very high intrinsic compressive stress up to 6 GPa is applied to FinFETs. <sup>49</sup> An enhancement above 30% in  $I_{\rm dsat}$  is observed for FinFETs with a 20-nm-thick DLC liner stressor over control devices, which is attributed to the coupling of compressive stress from the DLC liner to the channel. The physical origin of hole mobility enhancement has proven to be the small effective mass of the top valence band rather than any scattering modification; this mobility gain is maintained even at high electric field. <sup>50</sup>

Plasma-enhanced chemical vapor deposition could be used to produce a SiN CESL. The intrinsic stress in the SiN CESL could be modulated using different radiofrequency (RF) powers or thicknesses. A highly tensile-strained layer with 1.2 GPa of pressure and a highly compressive-strained layer with -1.8 GPa of pressure have been demonstrated to be responsible for the performance enhancement (10% for nMOS, 17% for pMOS).<sup>51</sup> Strain edge effects are dominant when the gate length is extremely small, whereas stress becomes less tensile for larger devices. The strain in the channel is also strongly dependent on geometrical parameters (W,  $L_{\rm gate}$ ).

Efforts to integrate strain in CMOS could resort to dual CESL technology, as illustrated in Fig. 9. The tensile and compressive SiN layer in nMOS and pMOS devices, respectively, are deposited sequentially and etched selectively. The resulting nMOS delivers an on-current of 1.05 mA/ $\mu$ m and an

off-current of 70 nA/ $\mu$ m at a 1-V drain bias. A pMOS exhibits a 66% increase in linear drain current and a 55% increase in saturation current. The improvement in the drain current for nMOS and pMOS devices depends on the channel doping concentration. Channel doping should be kept as low as possible to avoid deterioration of the improvement in drain current.

Complicated process steps are required in dual stress liner technology to enhance the drive currents for both nMOS and pMOS devices simultaneously. Therefore, a novel ultimate spacer process (USP) with a single stress liner has been developed, resulting in a 15% and 7% drive current improvement for nMOS and pMOS devices, respectively. Except for the single USP step inserted into the salicide module for both nMOS and pMOS devices, the whole process is commonly exempt from extra lithography steps. In combination with the oriented channel and poly stressors, current increases of 25% for nMOSs and 35% for pMOSs are achieved

## Combination of Different Strain Schemes

As the dimensional shrinkage of devices proceeds, different schemes must be combined together. Preliminary research has focused mainly on the combination of CESLs and source/drain stressors for CMOS integration, for example, SiGe stressors for pMOS and CESLs for nMOS.

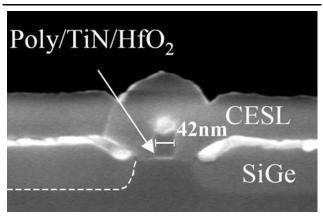

By integrating a HfO<sub>2</sub>/TiN/poly gate stack with a SiGe stressor and a compressive nitride CESL, as shown in Fig. 10,  $^{54}$  an improvement of up to 65% for  $I_{\rm dsat}$  has been demonstrated for pMOS devices. A 100-nm-thick CESL with 1.5 GPa of compressive stress is added after Ni silicidation in the typical epitaxy SiGe source/drain process. An on-current of 422  $\mu$ A/ $\mu$ m and off-current of 20 pA/ $\mu$ m are obtained at  $V_{\rm dd}$  = 1.1 V and 25% Ge concentration. Furthermore, a recessed Si<sub>0.8</sub>Ge<sub>0.2</sub> stressor and compressive CESL have been successfully integrated, resulting

Fig. 10. Cross-sectional scanning electron microscopy (SEM) image showing SiGe in source/drain area, combined with a TiN and  $HfO_2$  combination and CESL stress booster, showing a 42-nm-gate-length device (Reprinted from Ref. 54 with permission. Copyright 2005, IEEE publisher).

in an 85%  $I_{\rm dsat}$  improvement and a nearly 200% improvement in the hole mobility of a pMOS with a 70-nm gate length. <sup>55</sup>

The drive current improvements from recessed  $\mathrm{Si_{0.8}Ge_{0.2}}$  plus a compressive nitride layer are additive; furthermore, it has been shown that the mobility enhancement is a superlinear function of stress, leading to larger additive gains in drive current when combining several stress sources.

The most important step in CESL technology is the deposition of highly stressed nitride. During the deposition of a SiN film in an optimized plasma environment in combination with heavy-ion bombardment, an engineered compressive stress of 2.5 GPa could be used to form source/drain regions with SiGe stressors. A uniaxial compressive stress greater than 1 GPa and a drive current greater than 1 mA/ $\mu$ m have been achieved for pMOS devices. <sup>56</sup>

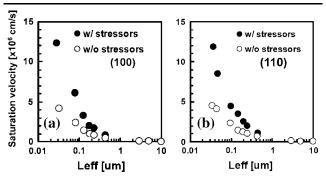

By adopting both compressive stress liners and embedded SiGe stressors, the achieved stress (as high as -2.4 GPa for pMOS devices) formed on (100) substrates is larger than that for pMOS devices formed on (110) substrates. These findings make CMOS integration with stressors on (100) substrates very promising. Figure 11 shows the saturation velocity of holes as a function of effective gate length with and without stressors, strongly suggesting that the stress is additive, and the saturation velocity of holes on (100) substrates is larger than that on (110) substrates for pMOSs. When the effective gate length becomes shorter, the saturation velocity of holes on (100) substrates is superior to that on (100) substrates.

A two-step method for creating recessed SiGe stressors was developed to boost the performance of pMOS devices. The process flow is detailed in Fig. 12. The hole mobility, short-channel effects, and source/drain resistance of pMOSs are notably improved by carefully optimizing the device structure, such as the recess depth of source/drain extension (SDE) and source/drain offset spacer width. <sup>58</sup> The combination of SiGe stressors formed by a two-step method with compressive stress liners would lead to a further enhancement of perfor-

Fig. 11. Saturation hole velocity dependence on effective gate length ( $L_{\rm eff}$ ) for devices with and without stressors on (a) (100) and (b) (110) substrates (Reprinted from Ref. 57 with permission. Copyright 2009, IEEE publisher).

Fig. 12. Schematic flow of the two-step process for recessed SiGe source/drain (Reprinted from Ref. 58 with permission. Copyright 2006, IEEE publisher).

Fig. 13. Cross-sectional TEM of a pMOS device with a two-step recessed SiGe source/drain structure and compressive stress liner (Reprinted from Ref. 58 with permission. Copyright 2006, IEEE publisher).

mance. <sup>59</sup> A record-high drive current of 714  $\mu$ A/ $\mu$ m at  $V_{\rm dd}$  = 1.0 V and  $I_{\rm off}$  = 100 nA/ $\mu$ m was reported by optimizing the source and drain overlap, defect control, and elevated SiGe stressor structure. <sup>59</sup> Figure 13 shows a cross-sectional TEM image of a pMOS with SiGe stressors formed by combining the two-step method with compressive stress liners.

Epitaxial SiGe stressors and tensile SiN CESL stressors are integrated to improve the performance of pMOS and nMOS devices simultaneously.<sup>60</sup> The saturated drive current of an nMOS and pMOS is increased by 10% and 25%, respectively. By care-

fully adjusting the stress in the capping layer for nMOS devices and adjusting the Ge concentration in SiGe stressors for pMOS devices, the strain level of each can be tuned independently. At large vertical electric fields, the hole mobility is increased by 50% because of the large longitudinal uniaxial compressive stress induced by SiGe stressors; at the same time, the tensile stress induced by the SiN capping layer does not degrade the hole mobility but enhances the electron mobility by 20%.

## **Reliability Issues**

Due to the reorientation of the band structure caused by the strain, both nMOS devices with uniaxial tensile strain and pMOS devices with compressive strain show improved drive current. However, because of the introduction of additional processes and new materials that give rise to tensile or compressive strain, reliability issues may also arise.

With uniaxial tensile strain induced by a SiN cap layer on polysilicon gate/SiON oxide, a 15% improvement in the drive capability of nMOS devices has been demonstrated without degrading the noise performance. The cap-layer-induced strain neither degrades the low-frequency drain noise nor increases the degradation rate in accelerated stress tests. Hot-carrier stress, bias-temperature instability, and time to breakdown are also robust in this type of strained device. No significant degradation of intrinsic negative-bias temperature instability (NBTI) behavior is observed because of post-oxide-growth process-induced strain on various gate stacks, such as poly-Si/SiON, TiN/HfO<sub>2</sub>/SiO<sub>2</sub>, and Ni fully-silicided (FUSI)/HfSiON/SiO<sub>2</sub>. 62

However, instead of the strain itself, it is the SiN CESL that influences device performance and reliability characteristics. Hydrogen passivation at the interface accounts for the deteriorated reliability characteristics. <sup>63</sup>

Compressive CESLs may worsen dynamic NTBI characteristics. This is attributed to the high hydrogen content within the SiN CESL layer as well as the high strain placed on the channel. A strong dependence on the alternating-current (AC) stress frequency is observed due to excess hydrogen content in strained devices. However, the NBTI instability of strained devices could be alleviated by operating at high frequency. 64

The excess hydrogen content within SiN CESLs can also lead to increased substrate current and potentially aggravate hot-electron effects. The deposition of a tetraethyl orthosilicate (TEOS) buffer layer prior to that of a SiN CESL could block the diffusion of hydrogen and thus improve the hot-electron reliability. <sup>65</sup>

The increased strain has not been found to fundamentally limit hot-carrier reliability in submicron MOS technologies and can actually improve intrinsic hot-carrier lifetime. <sup>66</sup> However, the strain leads

to bandgap narrowing and an increase in the phonon mean free path,  $^{67}$  both of which contribute to improved impact ionization. The improved impact ionization for short-channel pMOS devices with uniaxial strain is also ascribed to the strainenhanced mobility. In this case,  $V_{\rm dsat}$  becomes lower, which results in observable  $V_{\rm g}$ -dependent enhancement in  $I_{\rm sub}/I_{\rm d}$ .  $^{68}$

The enhanced mechanical stress may degrade flicker noise characteristics, especially for pMOS devices, due to the trap states and dipoles generated by the stress. The flicker noise could be reduced, and the device performance could be improved, by optimizing the nitrogen profile in the gate dielectric (i.e., reducing the surface nitrogen concentration and increasing the total number of nitrogen atoms in the dielectric to prevent boron penetration from the gate electrode). <sup>69</sup>

For pMOS devices with HfO<sub>2</sub>/TiN gate stacks, using a cap layer does not degrade the magnitude of 1/f noise. However, an increase in 1/f noise is found for pMOS devices with SiGe stressors, which results from additional traps created in high-k dielectrics during the epitaxial growth of SiGe stressors. The applied stress does not directly correlate with the noise magnitude. For HfSiON/SiO<sub>2</sub> and a fully silicided gate stack, the 1/f noise is not affected by SiGe stressors, indicating that the embedded (source/drain) processing does not degrade the quality of the gate stack and that the intrinsic strain does not affect 1/f noise. Ti

Briefly, strain engineering, when properly characterized and implemented, has only a marginal impact on oxide quality and does not compromise long-term reliability. Strain has no intrinsic effect on 1/f noise. For nMOS devices, CESL strain (uniaxial) is much better in terms of reliability, performance, and process simplicity, whereas pMOS devices with SiGe stressors have the drawback of Ge outdiffusion. Strained SOI requires special care due to its channel interface defects.

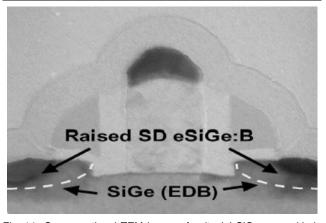

Fig. 14. Cross-sectional TEM image of epitaxial SiGe source/drain stressor formed by the EDB process (Reprinted from Ref. 17 with permission. Copyright 2008, IEEE publisher).

Although they suffer from junction leakage, nMOS devices with SiC stressors show high drive capability. Therefore, SiC stressors with low defect densities are important for nMOS devices. As shown in Fig. 14, pMOS devices with SiGe stressors combined with embedded diffusion barriers (EDBs) exhibit much better NBTI characteristics as a result of the improved junction quality. Therefore, SiGe stressors seem to be promising in terms of performance and reliability, but SiGe channel exhibits worse NBTI and complex process characteristics. <sup>17</sup>

#### HYBRID-ORIENTATION CHANNEL

Because of the low oxide-interface charge density and the highest electron mobility, a silicon substrate oriented along the (100) crystalline plane is desirable for nMOS devices. However, the highest hole mobility occurs in  $\mathrm{Si}(110)$  with a channel along the <110> direction; moreover, the peak mobility of  $\mathrm{Si}(110)$  is more than twice than that of  $\mathrm{Si}(100)$ . Therefore, to take full advantage of electron and hole mobility simultaneously, nMOS devices should be fabricated on  $\mathrm{Si}(100)$  and pMOS devices on  $\mathrm{Si}(110)$ .

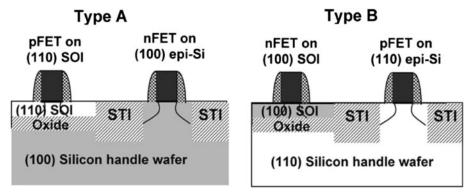

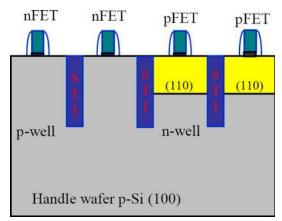

Hybrid-orientation technology (HOT), in which wafer bonding and selective silicon epitaxy are utilized to improve the mobilities in both nMOS and pMOS devices simultaneously, as shown in Fig. 15, has been proposed. 73,74 Symmetrical performance of nMOS and pMOS devices is achieved by using this novel technology, so that area can be significantly saved. HOT is fully compatible with existing very large-scale integration (VLSI) technology in that no new material is introduced, and the device structure remains planar. Moreover, HOT is also compatible with dual stress liners, which further improve carrier mobility by local strain engineering.

There are many difficulties in fabricating pMOS devices on Si(110), such as channelling effects of dopants along the (110) axis. Furthermore, a higher density of surface atoms and available bonds on Si(110) compared with Si(100) leads to a higher interface trap density. Different surface properties also result in orientation dependence of oxidation and epitaxial deposition. To maximize the hole mobility, all gates of pMOS devices must be aligned along a single direction, because hole mobility is strongly anisotropic in Si(110). Therefore, the ground rules of layout design must be modified. Fortunately, the impact of oxide-interface charge on threshold voltage and subthreshold slope decreases with gate oxide thickness. Because the nitrogen concentration in current gate oxides is increased and because of the expected introduction of high-k gate dielectric materials, the detrimental effects from surface orientation are diminishing.

#### **Hybrid-Orientation Substrate Preparation**

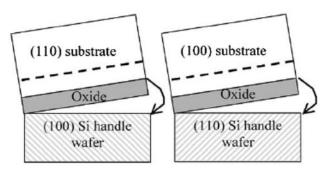

Hybrid-orientation substrates could be formed by layer transfer through a wafer bonding technique,

Fig. 15. Schematic cross-section of CMOS on hybrid-orientation substrates, including two types: type A with pFET on (110) SOI and nFET on (100) silicon epitaxial layer and type B with nFET on (100) SOI and pFET on (110) silicon epitaxial layer (Reprinted from Ref. 73 with permission. Copyright 2006, IEEE publisher).

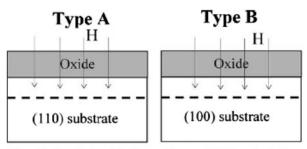

as shown in Fig. 16. A 150-nm-thick oxide is thermally grown on a starting Si(110) substrate for type A or Si(100) substrate for type B. Hydrogen is then implanted through the oxide at a tilt of  $7^{\circ}$  at room temperature to form a sheet near the interface. Then, the H-implanted wafer is hydrophilically bonded at room temperature to a handle wafer with a different surface orientation. Low-temperature (300°C to 500°C) annealing is performed in  $N_2$  to reinforce the bonding interface before mechanical stripping. The bonding interface is further reinforced by subsequent high-temperature (1100°C) annealing. Finally, the top SOI layer is chemically and mechanically polished and thinned down to the desired thickness.

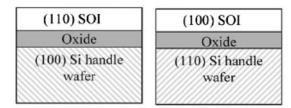

The crystal orientation of single-crystal silicon layers could be changed in selected areas from one orientation to another by an amorphization/templated recrystallization (ATR) process. Therefore, ATR could serve as an alternative approach to fabricating planar hybrid-orientation substrates with both Si(100) and Si(110) surfaces. 75

Figure 17 shows the ATR process schematically. The process starts with substrates composed of "direct-silicon-bonded" (DSB) overlayers of Si(110) on Si(100) handle wafers, giving rise to a Si-to-Si interface that is free of interfacial oxide. A DSB substrate could be formed by a "quasi-hydrophobic" bonding method in which ultrathin (1 nm to 2 nm) oxide present on the wafer surfaces during bonding is removed by high-temperature (1320°C to 1325°C) oxide dissolution annealing, leaving the desired direct Si-to-Si contact at the bonding interface. <sup>76</sup> ATR is performed on these selected regions of Si(110) bonded to a Si(100) handle wafer. The Si regions selected for ATR are first separated from those that are not selected for ATR by SiO<sub>2</sub> trenches. The selected regions are then amorphized by ion implantation through openings in a resist mask and recrystallized to form Si(100), whereas nonselected regions remain on Si(110).

Step 1: Buried oxide formation and H implantation.

Step 2: Flip-bond implanted wafer to a handle wafer with different orientation at room temperature.

Step 3: Wafer split anneal, bonding anneal, touchup polish and SOI thinning.

Fig. 16. Process flow of hybrid-orientation substrate fabrication using wafer bonding technology (Reprinted from Ref. 73 with permission. Copyright 2006, IEEE publisher).

Fig. 17. Schematic of the ATR approach for forming hybrid-orientation substrates in substrates without (a–c) or with (d–f) trench isolation regions (Reprinted from Ref. 75 with permission. Copyright 2005, American Institute of Physics).

Integration of nMOS devices on Si(100) and pMOS devices on Si(100) in the vertical direction is also applicable. The key to this integration strategy relies on low-temperature molecular bonding, in which independent optimization of channel materials and the crystalline orientation of top and bottom FETs is allowed. This method makes full use of a

hybrid-orientation substrate and high integration density. The best hole mobility for pMOS devices on Si(110) is obtained by rotating the top wafer by 90° during bonding. The optimization of NiSi silicide, SPE, and *in situ-*doped SiGe stressors is also carried out to achieve low parasitic resistance. Hybrid-orientation technology (HOT) exhibits excellent scalability due to its low thermal budget.

#### **Device Fabrication and Characterization**

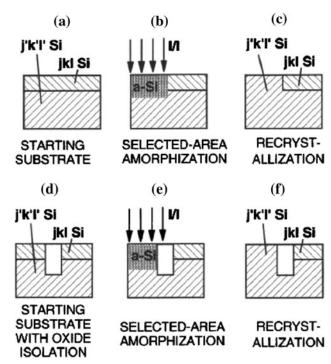

Figure 18 shows a typical integration process flow of CMOS fabrication using HOT on a hybrid-orientation substrate composed of bulk and SOI.73,78 Starting with a hybrid-orientation substrate, a thin oxide/SiN stack is deposited. One additional block lithography and reactive ion etching (RIE) step is used to etch through the entire stack, and the surface of the underlying handle wafer is exposed. Following spacer formation, epitaxial silicon is selectively grown in the openings by rapid thermal chemical vapor deposition. Owing to the nature of epitaxy, this epi-Si has the same crystal orientation as the handle wafer. Chemical mechanical polishing (CMP) is performed, and the dielectric layer on top of the SOI is removed, followed by standard CMOS fabrication.

A significant enhancement in the performance of pMOS devices ( $I_{\rm on}$  = 730  $\mu \rm A/\mu m$  at  $V_{\rm dd}$  = 1.0 V and  $I_{\rm off}$  = 90 nA/ $\mu m$ ) without degrading nMOS performance is achieved. Wafer bonding and the selective silicon epitaxy process introduce process integration and circuit design complexity, which result in a mixture of bulk and SOI devices. The HOT should be carefully optimized for the sake of reducing  $R_{\rm ext}$  and defect density, as pMOS devices fabricated by HOT suffer from significant external resistance ( $R_{\rm ext}$ ). <sup>74</sup>

Fig. 18. Integrated process flow for HOT CMOS fabrication on a hybrid-orientation substrate mixed of bulk and SOI, where nMOS is on the (100) surface and pMOS is on the (110) surface (Reprinted from Ref. 79 with permission. Copyright 2005, IEEE publisher).

Fig. 19. Schematic of a CMOS structure fabricated on a DSB bulk substrate with SPE (Reprinted from Ref. 79 with permission. Copyright 2005, IEEE publisher).

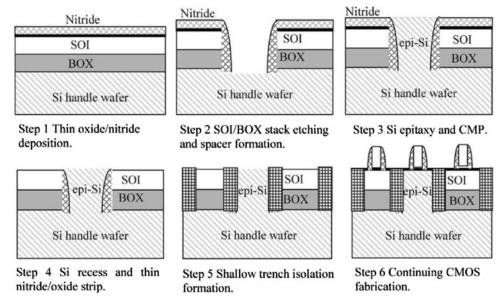

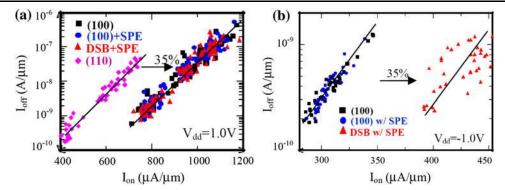

High-performance 65-nm-technology  $[L_{poly} =$ 45 nm, equivalent oxide thickness (EOT) = 1.2 nm] bulk CMOS devices have been demonstrated on mixed-orientation substrates using DSB wafers and a SPE process, as shown in Fig. 19. nMOS devices on SPE-converted Si(100) exhibit the same performance as the controls on Si(100) ( $I_{\rm on}=1000~\mu{\rm A}/\mu{\rm m}$  at  $V_{\rm dd}=1.0~{\rm V}$  and  $I_{\rm off}=40~{\rm nA}/\mu{\rm m}$ ), as shown in Fig. 20a. pMOS performance is improved by 35% because of the hole mobility enhancement observed on Si(110) compared with Si(100) surfaces, as shown in Fig. 20b. 79 DSB substrates and the SPE process are fully compatible with conventional CMOS processes, and no new material is introduced. Only one extra lithography step is included in this process; this includes amorphization and solid-phase epitaxy, which bring marginal additional cost.

## APPLYING NEW HIGH-MOBILITY CHANNELS

A 40% performance enhancement can be achieved in pMOS devices by strain engineering to reach the end of the ITRS roadmap; however, less than 5% enhancement is expected for nMOS devices, indicating that nMOS technology is at its limits.

Applying new channel materials, such as SiGe, 80-82 Ge, 83 and group III-V materials 84 (GaAs, InAs, InSb, and InGaAs), will improve the carrier mobility through effective mass modulation and subband structure engineering.85 The guidelines for modulating effective mass are summarized as follows:<sup>86</sup> (1) heavier  $m_z$  for reducing inversion-layer thick-(1) heavier  $m_z$  for reducing inversion-layer thickness and increasing  $C_{\text{inv}}^{\text{thickness}}$ ; (2) lighter  $m_x$  for increasing  $v_s$ ; (3) optimized  $D_{2D}$  in thin  $t_{ox}$  for tradeoffs between  $C_{\text{inv}}^{\text{DOS}}$  and  $v_s$ ; and (4)  $m_y > m_x$ , where  $m_x$ ,  $m_y$ , and  $m_z$  represent directional components of effective mass, respectively, and  $C_{\text{inv}}^{\text{DOS}}$  and  $C_{\text{inv}}^{\text{thickness}}$ represent inversion-layer capacitance due to finite density-of-states (DOS) and quantum-mechanical thickness of inversion layers, respectively;  $D_{2D}$ represents the DOS of the two-dimensional (2D) subband, and  $v_s$  is the carrier velocity near the source edge. In particular, a thinner  $t_{ox}$ , shorter  $L_{g}$ , and lighter  $m_x$  are better under a given  $D_{2D}$ . The selection of appropriate channel materials is based on these considerations.

Table II shows the mobility and effective mass of both electrons and holes, bandgap, DOS, and permittivity of Si, Ge, and main III–V semiconductors.

The electron mobilities of III–V materials are quite high, such that the enhancement factor of electron mobility against Si can amount to 3 to 50 in bulk Si. Such high mobilities could be attributed to the light effective mass of the electrons. However, there are also some fundamental deficiencies in material properties, such as a typically low DOS, small direct bandgap, and high permittivity, as shown in Table II. Many difficult theoretical and technological issues remain unsolved, which prohibits mass production of CMOS devices using these new materials. In the following sections, the current progress and difficulties concerning these issues are reviewed.

### SiGe Channel

Due to their high mobility, pMOS devices with compressively strained SiGe channels are promising. However, the small bandgap of Ge-rich materials inevitably leads to an increase in  $I_{\rm off}$ , which

Fig. 20. (a)  $I_{on}$  versus  $I_{off}$  from nFETs on (100), (100) with SPE, and DSB with SPE, and (110) control; (b)  $I_{on}$  versus  $I_{off}$  from pFETs on (100), (100) with SPE, and DSB with SPE,  $L_{poly} = 45$  nm, EOT = 1.2 nm (Reprinted from Ref. 79 with permission. Copyright 2005, IEEE publisher).

| Table II. Electron and hole mobilities, electron and hole effective mass, bandgap, DOS, and permittivity for |

|--------------------------------------------------------------------------------------------------------------|

| Si, Ge, and typical III-V compound semiconductors (Reprinted from Ref. 86 with permission, copyright 2008,   |

| IEEE publisher, and from Ref. 165 with permission, copyright 2010, American Institute of Physics)            |

|                                         |                      | Si                                                           | Ge                                      | GaAs                  | InP                   | InAs                | InSb                  |

|-----------------------------------------|----------------------|--------------------------------------------------------------|-----------------------------------------|-----------------------|-----------------------|---------------------|-----------------------|

| Electron mobility (cm <sup>2</sup> /Vs) |                      | 1600                                                         | 3900                                    | 9200                  | 5400                  | 42000               | 77000                 |

| Electron effective mass $(m_0)$         |                      | $m_{\rm t}$ : 0.19                                           | $m_{\rm t}$ : 0.082                     | 0.067                 | 0.082                 | 0.023               | 0.014                 |

| Electron DOS (/eV·cm $^2$ )             | Valley 1<br>Valley 2 | $m_{ m l} : 0.916 \ 6.97 	imes 10^{14} \ 1.59 	imes 10^{14}$ | $m_{ m l} : 1.467 \ 5.01 	imes 10^{14}$ | $2.76\times10^{13}$   | $3.34\times10^{13}$   | $9.61\times10^{12}$ | $5.85\times10^{12}$   |

| Hole mobility (cm <sup>2</sup> /Vs)     |                      | 430                                                          | 1900                                    | 400                   | 200                   | 500                 | 850                   |

| Hole                                    | Heavy                | $1.22\times10^{14}$                                          | $5.6 	imes 10^{13}$                     | $1.95\times10^{14}$   | $2.5\times10^{14}$    | $6.27\times10^{13}$ | $1.79 \times 10^{14}$ |

| $DOS (/eV \cdot cm^2)$                  | Light                | $1.05 \times 10^{14}$                                        | $8.94\times10^{12}$                     | $3.13 \times 10^{13}$ | $3.71 \times 10^{13}$ | $3.59\times10^{12}$ | $6.27 \times 10^{12}$ |

|                                         | Split-off            | $1.21 \times 10^{14}$                                        | $3.51\times10^{13}$                     | $7.1 	imes 10^{13}$   | $7.09 \times 10^{13}$ | $5.85\times10^{13}$ | $7.94 \times 10^{13}$ |

| Hole                                    |                      | $m_{ m HH}$ : 0.49                                           | $m_{ m HH}$ : 0.28                      | $m_{ m HH}$ : 0.45    | $m_{ m HH}$ : 0.45    | $m_{ m HH}$ : 0.57  | $m_{ m HH}$ : 0.44    |

| Effective mass $(m_0)$                  |                      | $m_{ m LH}\!\!:0.16$                                         | $m_{ m LH}$ : 0.044                     | $m_{ m LH}$ : 0.082   | $m_{ m LH}\!\!:0.12$  | $m_{ m LH}$ : 0.035 | $m_{ m LH}$ : 0.016   |

| Bandgap (eV)                            |                      | 1.12                                                         | 0.66                                    | 1.42                  | 1.34                  | 0.36                | 0.17                  |

| Permittivity                            |                      | 11.8                                                         | 16                                      | 12                    | 12.6                  | 14.8                | 17                    |

mainly consists of junction leakage and band-toband tunneling.<sup>87</sup>

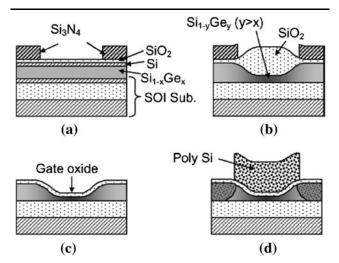

High-performance devices are only fabricated on selective SiGe-on-insulator (SGOI) or Ge-on-insulator (GOI) regions to maintain low  $I_{\rm off}$ . A method of epitaxial growth using a SiGe layer with an initially low Ge fraction and a local Ge-condensation technique <sup>87</sup> has been developed to form compressively strained SGOI channels, allowing fabrication of MOSFETs with very high Ge fractions in selected regions on SOI substrates. <sup>82</sup>

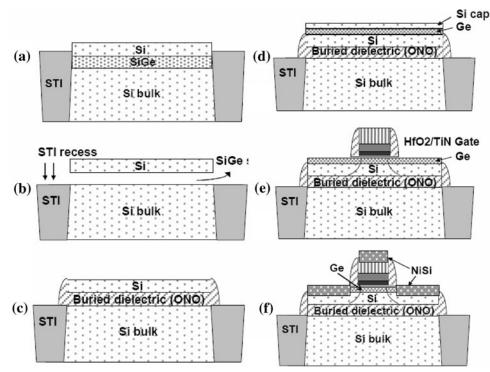

The fabrication process is shown in Fig. 21. First, a low-Ge-fraction SiGe layer is grown epitaxially on an SOI substrate by low-pressure chemical vapor deposition. This is followed by conventional local oxidation of silicon (LOCOS) isolation to form a recessed channel underneath. After stripping the LOCOS layer, a second oxidation is performed to grow the

Fig. 21. Fabrication procedure for strained SGOI MOSFETs by a local condensation technique (Reprinted from Ref. 82 with permission. Copyright 2005, IEEE publisher).

gate oxide at 900°C. Using this process, pMOS devices with Ge-rich (up to 96%) strained SiGe layers are fabricated locally in selected areas and exhibit significant enhancements in hole mobility up to 10 times that of control devices.

The combination of uniaxial compressive stress with SiGe (Ge) channel materials can potentially provide stress greater than 1 GPa. The lateral strain relaxation technique is proposed for this purpose. See Preserving the strain along the channel direction while relaxing it along the width direction is the key to this technique. Moreover, the elastic strain relaxation from pattern edges effectively suppresses dislocation nucleation. Therefore, dislocation-free SGOI channels with only longitudinal compressive stress along the channel can be realized.

The fabrication process is compatible with that of standard CMOS technology, except for the compressively strained SGOI substrates formed by the above-mentioned Ge-condensation technique. One minor flaw is the thicker gate oxide compared with that of control devices because of the Ge-induced enhancement of the oxidation rate. In Fig. 22, the fabricated pMOS on uniaxially strained SGOI (Ge content 20%) exhibits a high mobility enhancement of 100% and  $I_{\rm on}$  enhancement as high as 80% over control devices. This enhancement effect could be maintained at high vertical field as well as in the short-channel regime.

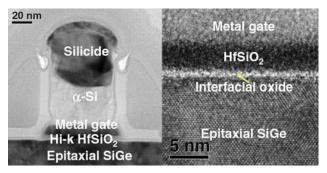

A Si cap layer is always deposited on the SiGe channel to reduce interface trap density and gate leakage. However, avoiding the Si capping layer is necessary to further scale down the gate oxide due to Ge-enhanced Si oxidation. Therefore, an optimized epitaxial SiGe on Si and high-k dielectric/metal gate process is proposed. <sup>89</sup> The formation of high-quality epitaxial SiGe films with optimized Ge concentration as well as excellent wafer uniformity and HfSiO<sub>2</sub> gate dielectrics of improved interface

Fig. 22. Cross-sectional TEM images of 30-nm- $L_{poly}$  strained SGOI pMOS (Reprinted from Ref. 88 with permission. Copyright 2006, IEEE publisher).

Fig. 23. TEM images of a gate stack with  $HfSiO_2$  high-k gate dielectrics and metal gates fabricated on high-quality epitaxial SiGe layers selectively grown on Si(100) substrates (Reprinted from Ref. 89 with permission. Copyright 2008, The Japan Society of Applied Physics).

quality and surface roughness are critical. These can be achieved by optimizing the temperature of the Si substrate and partial pressure of the chemical vapor deposition gases.

Figure 23 shows TEM images of a pMOS architecture with a  $HfSiO_2$  gate dielectric/metal gate deposited on an epi-SiGe channel.  $HfSiO_2$  remains amorphous with a visible  $SiO_2$  interfacial layer. The resulting gate stack of  $HfSiO_2$  on the SiGe channel exhibits minimal C-V hysteresis (<20 mV) and low gate leakage current (3 × 10² times lower than  $SiO_2/Si$  channel) at an EOT of 14 Å. High  $I_{on}$  is achieved through the effective suppression of off-state leakage.  $V_{th}$  roll-off, Subthreshold slope ( $S_s$ ), and gate-induced drain leakage (GIDL) decrease when Ge% increases due to the variation in the bandgap  $E_g$  and dielectric constant of the SiGe channel.

Threshold voltage  $(V_{\rm th})$  variation and strain maintenance are also important concerns for aggressively scaled strained MOSFETs. By adopting millisecond flash annealing, the severe issues of Ge diffusion and strain relaxation during source/drain activation may be solved. pMOS devices with high Ge% (50%) in their SiGe channels demonstrate  $2.8\times$  mobility gain with superior NBTI (<30 mV)

reliability. <sup>80</sup>  $V_{\rm th}$  can be flexibly controlled by Ge% in the SiGe channel and the Si cap effect. High Ge% (50%) as well as preserved strain in the SiGe layer is achieved even at high temperature, resulting in low (-0.2 V to -0.3 V) and tight  $V_{\rm th}$  distributions ( $\delta V_{\rm th} < 30$  mV) at low EOT (1 nm).

# Germanium (Ge) Channel

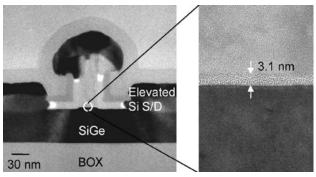

A Ge channel can be considered as the extreme case of a  $Si_xGe_{1-x}$  channel (i.e., when x is 0). However, band-to-band tunneling due to the small bandgap of Ge<sup>90</sup> must be carefully optimized as downscaling is pursued. Although large-diameter Ge wafers are available, one may resort to strained-Si/strained-Ge heterostructure MOSFETs on bulk substrates, which can be fabricated by a bond and etch-back technique. 91 High-mobility carriers in strained-Ge channels are confined in strained-Si/ strained-Ge heterostructures with discontinuous valence bands. To deposit Ge layers as smooth, atomically flat, relaxed interfaces, Si<sub>1-r</sub>Ge<sub>r</sub> dislocation blocking layers can be used to fabricate high-mobility Ge-channel pMOSs. 92,93 This process is quite interesting, because it facilitates Si/Ge integration.

With regards to Ge channels for nMOS devices, the small process window is a hindrance to application. Depositing a stable gate stack and improving dopant activation in the source/drain remain challenging. <sup>94,95</sup> Therefore, most work focuses on Ge-channel pMOS devices.

The problems with Ge MOSFETs are low interface quality, <sup>96</sup> high leakage, compromises between high channel mobility and low band-to-band tunneling leakage, and compatibility with the traditional CMOS process. The problems of broadening of the energy band as described by quantum mechanics and understanding the activation and diffusion mechanism of Ge in Si are also urgent. These critical issues could cause researchers to resort to gate dielectric/channel interface optimization, source/drain engineering, new gate stack, and device architecture integration. Among these strategies, the most effective strategy is to engineer the interface.

Slot-plane-antenna (SPA) radical oxidation of Ge could provide high-quality GeO<sub>2</sub>/Ge interfaces, as the atomic oxygen radical (O\*) is more active than molecular oxygen (O<sub>2</sub>). Consequently, it can effectively repair oxide defects. GeO<sub>2</sub> grown by such SPA radical oxidation is amorphous, and the GeO<sub>2</sub>/Ge interface is smooth with a low density of interfacial states. 97

Surface passivation is another effective way to achieve smooth interfaces. A 4-nm-thick defect-free silicon capping layer on an ultrathin strained Ge channel could improve the mobility and reduce the leakage current significantly. The improved interface between Ge and the gate dielectric accounts for the improvement in hole mobility in

Ge-channel pMOS devices with Si capping layers. At low effective field ( $E_{\rm eff}$ ), the reduction of Coulomb scattering due to the separation of mobile carriers from interface charges by inserting a Si layer, as well as the reduction in the density of Coulomb scattering centers, is believed to contribute to the mobility enhancement. However, at high  $E_{\rm eff}$ , the reduction in the surface roughness due to the change in the channel region from SiO<sub>2</sub>/Si interfaces to Si/Ge interfaces is responsible for the mobility enhancement. <sup>98</sup>

It is critical to control the thickness of the capping Si layer precisely, because excessively thick Si capping layers cause mobility degradation. This degradation is ascribed to generated dislocations, which result in spatial strain distribution in Si. <sup>98</sup> A small change in the thickness of the Si capping layer will strongly affect electrical parameters such as hole mobility and drive current. <sup>99</sup> The optimal Si thickness is about 0.8 nm, which produces the peak mobility. <sup>100</sup>

The mobility variation can be explained by the charged centers in the gate oxide and strong remote Coulomb scattering due to defects at the  $\mathrm{Si/SiO_2}$  interface. The fact that the increase in  $I_{\mathrm{on}}$  is inversely proportional to the EOT reveals the important scattering mechanisms due to defects located within the gate dielectric.

Although a Si capping layer could be employed on top of relaxed Ge, <sup>102</sup> it results in a buried channel. For Ge-channel devices, a high-k dielectric/metal gate is indispensable, because native Ge oxide is water soluble. Additionally, Ge-channel devices cannot withstand high-temperature annealing due to Ge diffusion.

A low-thermal-budget (≤400°C) process to fabricate Ge MOS devices, in which a high-k gate dielectric (ZrO<sub>2</sub>) of 6-A to 10-A EOT and platinum gate electrode are used, has been demonstrated. 108 A novel self-isolated process is employed to simplify the fabrication of a ring transistor. The key to this process is the formation of the gate stack and source/drain junction. The high-k dielectric is formed by ultrahigh vacuum (UHV) sputtering of 20-Å to 30-Å Zr films followed by in situ UV ozone oxidation at room temperature. The resulting Ge/ZrO<sub>2</sub> interface offers excellent C-V characteristics. The Pt gate electrode is formed by a lift-off process. BF<sub>2</sub> is implanted in a lightly Sb-doped Ge substrate, which is covered by low-pressure chemical vapor deposition (LPCVD) SiO<sub>2</sub>. Activation of dopants is performed at 400°C in a N<sub>2</sub> atmosphere. Dopants are sufficiently activated, and a low sheet resistance is attained. The resulting pMOS device shows low field mobility, twice that of Si MOSFETs.

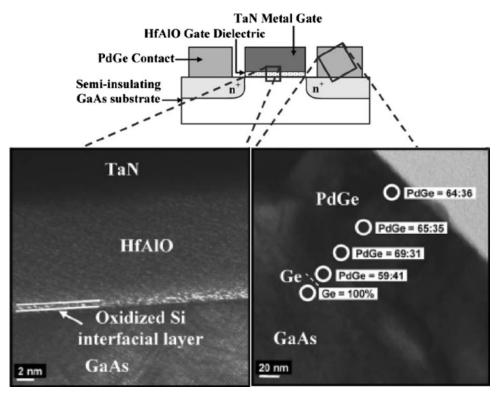

To further scale the EOT, molecular-beam epitaxy/deposition (MBE/MBD) techniques have been exploited for fabrication of Ge pMOS devices with  $TaN/HfO_2$  gate stacks. <sup>96,104</sup> An ultrathin Ge oxynitride layer is deposited as the interfacial layer between  $HfO_2$  and Si. The resulting EOT is 0.7 nm

thick after quantum-mechanical correction, and the gate leakage is extremely low, <sup>96</sup> which indicates that MBD offers advantages over conventional processes. The hole mobility is enhanced by a factor of 2, as compared with TaN/HfO<sub>2</sub>/Si control devices without interfacial Ge oxynitride layers.

Plasma-PH $_3$  and thin AlN between a high-k film and Ge substrate as surface passivation layers are efficient in suppressing the formation of GeO and preventing Ge outdiffusion, resulting in improved interfaces in nMOS devices with extremely low leakage. Enhancements in hole  $(1.6\times)$  and electron mobility  $(1.8\times)$  are obtained under optimized postannealing conditions.

It is necessary to avoid the formation of  $GeO_2$  at high-k/Ge interfaces to achieve thin EOT. Therefore, an approach to form a Sr germanide layer as an insulating interlayer for the high-k/Ge gate stack has been proposed to avoid the formation of a Ge oxide interlayer. The corresponding high-k/Ge pMOS with low gate leakage designed for ultrathin EOT (1 nm) and high hole mobility (481 cm²/Vs) has been fabricated. The standard high-k/gate-last process is applied with a slight modification to the Sr deposition process, and an MBE apparatus is used to provide an oxide-free Ge surface. A thermally stable amorphous  $SrGe_x$  interlayer exists at the high-k/Ge interface without diffusing into the high-k film after annealing at 400°C, which provides fair interfacial properties and EOT scalability.

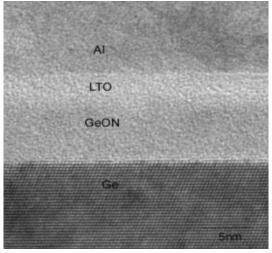

Another gate dielectric that could be used is Ge oxynitride (GeON) and a low-temperature oxide (LTO) stack, where GeON is formed by nitridation of a thermally grown Ge oxide. A smooth interface between Ge and Ge oxynitride is produced, and no interface between GeON and LTO is observed, as shown in Fig. 24. The drive current and transconductance of the fabricated pMOS devices are high compared with Si control devices. Excellent

Fig. 24. TEM image of Al/LTO/GeON/Ge stack. A smooth interface between Ge/GeON is achieved using this GeON process (Reprinted from Ref. 106 with permission. Copyright 2003, IEEE publisher).

Fig. 25. X-ray secondary emission microscopy (XSEM) image of thin-body GOI Schottky-barrier MOSFET with Pt germanide source/drain (Reprinted from Ref. 108 with permission. Copyright 2005, IEEE publisher).

subthreshold characteristics with 82 mV/dec are attributed to low interface trap density as well as low leakage junction.

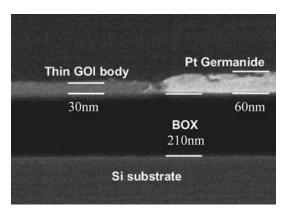

To solve the problems of high resistance and deep junctions due to low dopant solubility in Ge and fast dopant diffusion, Schottky barrier source/drain Ge transistors with intrinsic low thermal annealing temperature are considered an alternative solution. Excellent performance of pMOS devices with thin GOI channels using Pt germanide Schottky barrier source/drain with low barrier height has been demonstrated. The buried oxide and Si substrate are used as a gate dielectric and a bottom gate electrode, respectively, as shown in Fig. 25. The reaction of Pt with Ge leads to the formation of Pt germanide, which exhibits an extremely low Schottky barrier height, reducing the parasitic source/

drain resistance greatly. GOI substrates are prepared by using Ge-condensation technology, <sup>87</sup> followed by conventional Schottky Barrier MOSFET processing. A high hole mobility with an enhancement of 40% to 50% against the universal hole mobility of Si MOSFETs is obtained for the accumulated GOI channel.

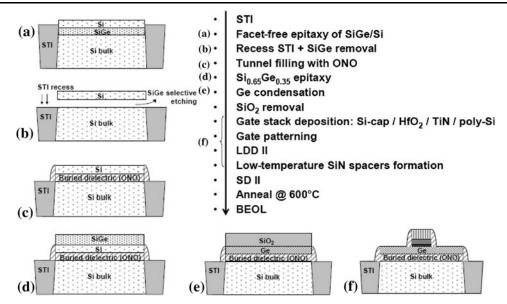

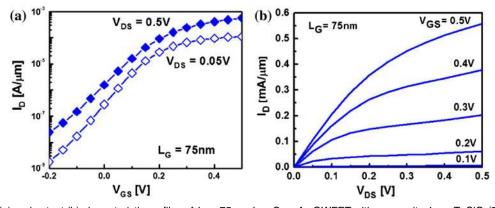

Fabricating Ge pMOS devices on ultrathin layers of insulator is advantageous in terms of increasing the bandgap and better  $V_{\rm th}$  control. A method of localized GeOI on Si substrates with Ge-condensation based on silicon-on-nothing (SON) technology has been developed. 109 The process is presented in Fig. 26. Nonuniform ultrathin Ge (8 nm) on buried dielectrics in source/drain areas makes it impossible to obtain Ge raised source/drain and germanidation, thus causing high access resistance, which is responsible for drive current degradation. A new process that uses direct Ge epitaxy, as shown in Fig. 27, has been proposed to overcome this issue. 110 Ultrathin pure Ge capped with thin Si epitaxial layers is directly integrated just under the gate of localized-SOI devices that benefit from high-mobility channels without the associated penalty of degraded parasitic resistance. Junctions in Si areas are activated by SPE with Ge amorphization of Si junctions. Boron atoms are implanted for the formation of extensions. Crystallization annealing is performed at 600°C to activate the dopants. Ge is only localized below the gate stack. NiSi silicidation is performed after the SPE process. The latter approach seems to be compatible with the low parasitic resistance requirement for performance improvement. Functional localized-GeOI pMOS transistors scaled down to 75-nm gate lengths with drive currents up to 600  $\mu$ A/ $\mu$ m at -1.1 V have been demonstrated.

Fig. 26. Process flow description: localized-GeOI technology is based on SON technology. LDD II: Lightly-doped-drain ion implementation, BEOL: back end of the line, ONO:  $SiO_2/Si_3N_4/SiO_2$ , SD II: source/drain ion implementation (Reprinted from Ref. 110 with permission. Copyright 2008, IEEE publisher).

Fig. 27. Process flow description of the localized ultrathin GeOI technology with pure Ge epitaxy (Reprinted from Ref. 110 with permission. Copyright 2008, IEEE publisher).

Fabrication of Ge nMOS devices is challenging for the reasons outlined above. The intrinsically low density of states in conventional (100) channel directions and the high conductivity effective masses of electrons that populate L valleys are believed to be the major causes of the low electron mobility and carrier concentration, resulting in the relatively low on-state current of Ge nMOS devices. 1 first conventional, self-aligned Ge nMOS device with fully activated phosphorus-doped Ge source/ drain junctions was demonstrated in Ref. 112. The fabrication process is a standard planar bulk prowith improved low-temperature junction annealing performed to minimize junction leakage. GeON and a LTO stack with a total equivalent oxide thickness of 8 nm and a W gate electrode are used as the gate stack. Device characteristics are less than satisfactory, with a subthreshold slope of 150 mV/dec and an on-off current ratio of only 10<sup>4</sup>.

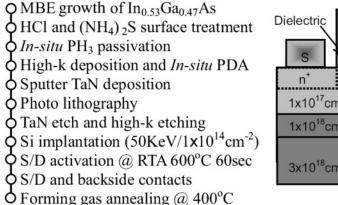

Breakthroughs in Ge nMOS fabrication have been recently reported. Fast traps due to the charge neutrality levels (i.e., interface donor and acceptor states close to the valence band)  $^{113-115}$  make contributions to the reduction of nMOS inversion mobility. The related density of interface states could be significantly reduced by improving  $\rm GeO_2$  quality by ozone oxidation.  $^{116}$  Low-temperature dopant activation is also required to suppress Ge suboxides. Slow traps in the bulk and borders of high-k dielectric due to the low conduction-band offset of  $\rm GeO_2$  and large source/drain series resistance due to the insufficient activation of n-type

dopants are considered the major causes of nMOS performance degradation. The highest electron mobility for Ge nMOS devices ( $1.5\times$  universal Si mobility) has been determined by Hall measurements, which excludes the effects of source/drain series resistance and trapping states.  $^{117}$

Another experiment also reports a high electron mobility greater than 1000 cm²/Vs by careful thermodynamic and kinetic control of the Ge/GeO<sub>2</sub> interface on Ge(111). High-pressure oxidation (HPO) and post-low-temperature oxygen annealing (LOA) processes have been developed to suppress GeO desorption and reduce the density of interfacial states, respectively. The physical nature is well explained through the kinetic and thermodynamic control of the GeO<sub>2</sub>/Ge system. This interface-conscious nMOS fabrication is implemented by gatelast processing at a relatively high phosphorus activation temperature (580°C). Further progress should focus on eliminating scattering by charged interface states and surface roughness.

In addition to interface engineering, source/drain junctions are also critical issues for Ge nMOS devices, because the implanted As and P have low solubilities and large diffusion constants. For fair interface quality, the activation temperature should be as low as possible, which makes it difficult to form a source/drain that simultaneously has low resistance and small junction leakage. Metalorganic vapor-phase epitaxy (MOVPE)-based gas-phase doping (GPD) has been explored to yield superior  $n^+/p$  junctions in Ge by reducing damage and crystal

defects. <sup>120</sup> Both the As diffusion constant and junction leakage are significantly reduced. Benefiting from the GPD and low interface states, the fabricated nMOS device exhibited electron mobility as high as 840 cm<sup>2</sup>/Vs.

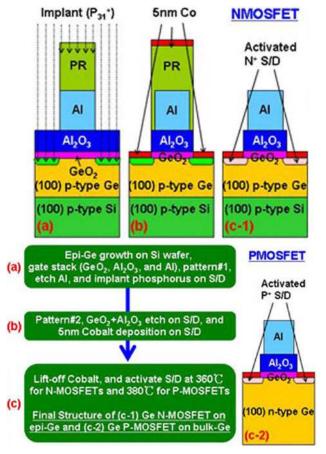

Obtaining highly active sources/drains through low-temperature annealing for the integration of high-performance Ge CMOS devices is challenging. Metal (Co)-induced dopant activation (Co MIDA) and Ge crystallization are used to achieve very low series resistance  $(2.23 \times 10^{-4} \,\Omega \, \text{cm})$  and shallow (92 nm) source/drain junctions with a high degree of dopant activation fabricated at low temperatures (below 380°C). 121 Figure 28 shows Ge nMOS and pMOS devices with a GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Al gate stack and a novel source/drain formed by Co MIDA; these were fabricated on epi-Ge (at 360°C) and bulk Ge (at 380°C), respectively. The fabricated Co MIDA  $n^+/P$ junction diode has an on/off ratio of 104, and the resulting Ge nMOS and pMOS devices provide a reasonable  $I_{\rm on}/I_{\rm off}$  ratio (10<sup>3</sup>) and a high  $I_{\rm on}$  per width (1.4  $\mu {\rm A}/\mu {\rm m}$  for nMOS and 1.17  $\mu {\rm A}/\mu {\rm m}$  for pMOS at  $L_g = 100 \mu m$ ).

Fig. 28. Ge nMOS and pMOS process flow at sub 380°C. (a, b) The same process steps are applied for both nMOS and pMOS, but (c) different activation temperatures for source/drain are used (360°C for nMOS and 380°C for pMOS in RTA) (Reprinted from Ref. 121 with permission. Copyright 2008, IEEE publisher).

Ultrashallow junctions with highly reduced contact resistance could also be achieved by the combination of high-concentration Sb  $\delta$ -doping techniques with the formation of atomically controlled metal/Ge.  $^{122}$  MBE Sb doping followed by homoepitaxial growth of Ge not only avoids ion implantation and thermal activation annealing, but also provides precisely controlled shallow doping depth. An atomically controlled interface between metal/Ge could alleviate Fermi-level pinning in metal/Ge contacts.  $^{123,124}$  Ohmic conductance of Fe<sub>3</sub>Si/Ge Schottky junctions is obtained with Sb concentrations as high as  $10^{20}~\rm cm^{-3}$  for Ge(111). Doped epi-Si passivation layers for n-Ge contacts could even eliminate Fermi-level pinning effects by incorporating an NiGe snow-plow to achieve contact resistivity as low as  $2\times 10^{-6}~\Omega$  cm.  $^{125}$

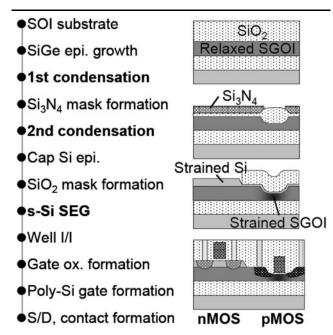

Uniaxial stress is believed to be indispensable for the performance enhancement of Ge nMOS to satisfy the high-performance specifications of the ITRS-defined 22-nm technology node. 97 For Ge CMOS integration, a combination of a SOI nMOS device with tensile strain and a GOI pMOS device with compressive strain on the same wafer is proposed, 83,126 combining multiple selective growth with the local Ge-condensation technique, as shown in Fig. 29. Strained-Si layers as n-channels are selectively grown on p-well regions of the relaxed SGOI substrates that are formed during the first condensation process. Strained-SGOI layers with Ge content of 66% are formed as p-channels on the *n*-well regions after the second condensation process, resulting in compressive strain of 1.3%. Conventional SiO<sub>2</sub>/poly-Si is used as the gate stack. The

Fig. 29. Schematics of fabrication procedures and device structures of dual Ge CMOS integration (Reprinted from Ref. 126 with permission. Copyright 2005, IEEE publisher).

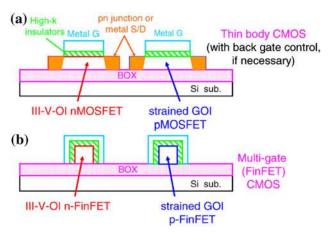

fabricated CMOS devices show over fourfold higher hole mobility enhancement in the GOI pMOS structure and a comparable current drive to that of the strained-Si nMOS structure.