This work has been published in Solid State Electronics, Vol. 52. Issue 4, pp. 514-518, 2008.

# **Mobility in Graphene Double Gate Field Effect Transistors**

M.C. Lemme<sup>\*</sup>, T.J. Echtermeyer, M. Baus, B.N. Szafranek, J. Bolten, M. Schmidt, T. Wahlbrink and H. Kurz

Advanced Microelectronic Center Aachen (AMICA), Otto-Blumenthal-Str. 25, 52074 Aachen, Germany

#### Abstract

In this work, double-gated field effect transistors manufactured from monolayer graphene are investigated. Conventional top-down CMOS-compatible processes are applied except for graphene deposition by manual exfoliation. Carrier mobilities in single- and double-gated graphene field effect transistors are compared. Even in double-gated graphene FETs, the carrier mobility exceeds the universal mobility of silicon over nearly the entire measured range. At comparable dimensions, reported mobilities for ultra thin body silicon-on-insulator MOSFETs can not compete with graphene FET values.

Keywords: graphene, field effect transistor, mobility, SOI

#### 1. Introduction

Scaling of transistor dimensions as described and dictated by Moore's law has generated astonishing innovation cycles in silicon technology over the last four decades [1][2]. As a result, CMOS technology today stands out as a fundamental technology that enables the global information society. Looking into the future, silicon technology is expected to remain the work horse for electronic applications for at least fifteen more years, but innovations no longer stem from pure geometrical scaling according to Moore's law. Instead, an era of material-based scaling has emerged, where novel materials must be introduced into the standard CMOS process to further reduce manufacturing cost. improve performance and/or reduce leakage power.

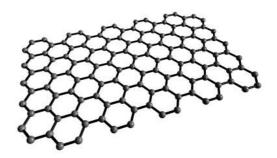

Fig. 1. Schematic of a graphene monolayer.

Carbon-based electronics are considered one of the most promising options to enhance silicon in the future [3]. A prominent example are carbon nanotubes (CNTs), which have received ample attention due to their intriguing electrical properties [4]. Nonetheless, two major drawbacks there are associated with CNTs. A lack of chirality control during production leads а mixture of metallic and to semiconducting nanotubes. In addition,

<sup>\*</sup>corresponding author. Tel.: +49 241 8867 207; fax: +49 241 8867 571 E-mail address: <u>lemme@amo.de</u> (M.C. Lemme)

there is no method currently available to accurately place hundreds of millions of nanotubes where they would be needed in order to form integrated circuits. Unless manufacturing processes are mastered and self-organization methods are employed, these could eventually prohibit their utilization as an addition to or replacement of silicon as a base material.

Another prominent example are carbon "substrates", thin carbon layers with similar properties to CNTs. Such twodimensional single and few layer carbon sheets, referred to as graphene sheets, have only verv recently been demonstrated to be thermodynamically stable [5]. A schematic of a graphene monolayer sheet is shown in Fig. 1: hexagonal rings formed by sp<sup>2</sup>-bonded carbon atoms are arranged in a dense honeycomb structure. In this twodimensional form, graphene is a semimetal with an extremely small overlap between the valence and the conduction band (zero-gap material). In its threedimensional graphite form, graphene sheets are weakly coupled between the layers with van der Waals forces.

Carrier mobility values between 3000 and 27000 cm<sup>2</sup>/Vs have been reported for graphene and make it an extremely promising material for future nanoelectronic applications [5][6]. It is further known that carrier transport in graphene takes place in the  $\pi$ -orbitals perpendicular to the surface [7]. Intrinsically this translates into charge carrier transport with a mean free path for carriers of L = 400 nm at room temperature [5]. This would make ballistic devices feasible even at relaxed feature sizes compared to State-of-the-Art CMOS technology.

Published experimental data has been so far mainly obtained from mono- or few layer graphene on oxidized silicon wafers or decomposed intrinsic silicon carbide [5][6]. In first experiments, the surface of the graphene has been left and pseudo-MOS uncovered characteristics have been obtained. This is in contrast to any device integration, where a gate insulator, an electrode and low-k dielectrics need to be deposited on top of the graphene. Only very recently, first field effect devices with top-gate structures have been reported [8][9][10].

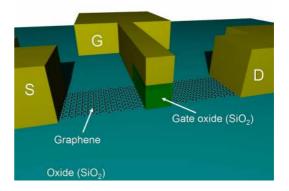

In this work, the electron and hole mobilities of graphene are extracted from field effect transistors (graphene FETs) with a double gate structure, where the pseudo-MOS back-gate is complemented by а second. lithographically defined sub-um topgate. A schematic of such a device is shown in Fig. 2. Carrier transport in double-gated transistors these is compared to "open" graphene FETs dielectric. without top-gate The values are compared to extracted literature data of silicon and ultra-thin body silicon on insulator (SOI) devices.

Fig. 2. Schematic of a graphene FET.

### 2. Experimental

High-quality silicon dioxide (SiO<sub>2</sub>) films of  $t_{ox} = 300 \text{ nm}$  have been thermally grown on boron doped silicon wafers (100) with a base doping concentration of  $N_A = 10^{15} \text{ cm}^{-3}$ . A manual exfoliation process similar to that described in [5] has been used to deposit graphene on the oxidized wafers. Next, mono- and few layer graphene flakes have been visually identified with an optical microscope. Lift-off processes have been used to structure evaporated titanium (Ti) / gold (Au) source (S) and drain (D) contacts. At this point, IV-measurements of the pseudo-MOS structures have been obtained.

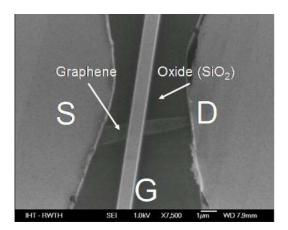

Fig. 3. Scanning electron microscope image of a graphene FET.

Next, electron beam lithography has been used to define top-gate electrodes. A gate stack of silicon dioxide gate dielectric (20 nm) and Ti (10 nm) / Au (100 nm) electrode has then been deposited by electron beam evaporation. Finally, the gate stack has been structured by a lift-off process. A scanning electron microscope image in Fig. 3 shows an example of a graphene field effect transistor. This particular graphene flake has a total length from source to drain of L = 5 µm and a width of W  $\approx$  650 nm under the top-gate. The e-beam defined top-gate transistor has a gate length of L = 650 nm.

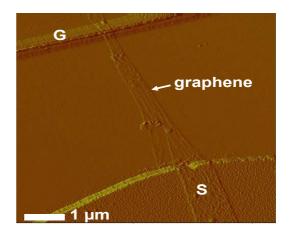

Graphene thickness has been measured by atomic force microscopy, shown in Fig. 4. Here, the thickness of the graphene flake ranges from  $t_g = 0.8$  nm to  $t_g = 2$  nm. This indicates that only a few layers of graphene are present.

Fig. 4. Atomic force microscope image of a graphene FET.

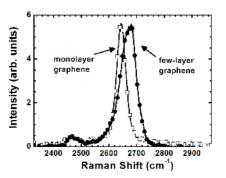

For а detailed analysis, Raman spectroscopy has been used to distinguish between fewand monolayer graphene [11][12]. For comparison, the Raman-spectra of the graphene flake (open rectangles) and a few layer graphene sample (solid circles) are depicted in Fig. 5. The graphene monolayer is clearly identified by the shape and the position of the Raman spectrum [11].

Fig. 5. Raman spectra of graphene flakes with different layer numbers.

#### 3. Discussion

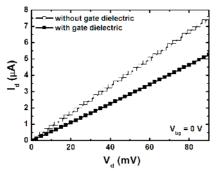

Electrical measurements have been performed on this monolayer graphene field-effect device prior and after topgate deposition. Fig. 6 shows the output characteristics at zero gate voltage with and without a gate dielectric on top. The drain current increases linearly with increasing drain bias. No saturation is observed in the entire voltage range of  $V_d = 0$  to 90 mV. After gate dielectric deposition the graphene FET shows a decreased drain current. Obviously, the presence of the gate dielectric on top of the graphene sheet has a large impact on the electrical characteristics of the graphene device.

Fig. 6. Graphene FET output characteristics with and without top-gate dielectric at zero transversal field.

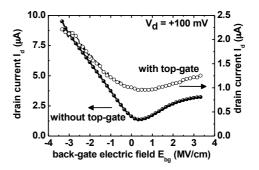

In Fig. 7, back-gate or pseudo-MOS transfer characteristics of a graphene FET before and after top-gate fabrication are shown. The source-drain voltage has been kept constant at  $V_{ds} = 100 \text{ mV}$  and the back-gate electric field has been swept from  $E_{bg} = -$ 3.5 MV/cm to  $E_{bg} = 3.5$  MV/cm. The drain current is modulated by almost one order of magnitude without a topgate (Fig. 7, black dots). Similar to CNTs, ambipolar behavior is observed. It is interesting to note that hole conduction is favored over electron conduction as negative back-gate fields higher result drain current in modulation compared to positive backgate fields. This is attributed to unintentional chemical doping by adsorbants during processing and handling of the sample [13], which is also believed to shift the current minimum towards positive  $E_{bg}$ .

Fig. 7. Back-gate transfer characteristics of a graphene FET with and without top-gate.

After the deposition of the SiO<sub>2</sub> topgate dielectric. the IV transfer characteristics maintain their basic signature, but the current level and the current modulation are decreased dramatically, represented by hollow circles in Fig. 7. This translates to a reduced carrier mobility in double gated graphene. This result seems to be in contrast with other groups which have reported no significant effect of top gate dielectrics on DC transport properties. Carrier mobilities have been calculated using a Drude model for carrier transport. First, the charge carrier density n<sub>s</sub> in the graphene FET in Fig. 7 has been calculated using

$$\mathbf{n}_{\rm s} = \varepsilon_{\rm ox} * \mathbf{V}_{\rm G} / (\mathbf{q} * \mathbf{t}_{\rm ox})$$

with the silicon dioxide permittivity  $\varepsilon_{ox}$ , gate voltage V<sub>G</sub>, electron charge q and silicon dioxide thickness t<sub>ox</sub>. The effective electric field in the graphene sheet has been calculated by using a value of  $\varepsilon_g = 2.4$  for the dielectric constant of graphene [14].

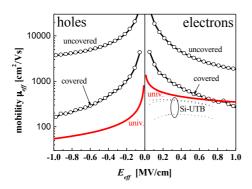

For the uncovered graphene, mobilities of  $\mu_h \ge 4790 \text{ cm}^2/\text{Vs}$  for holes and

$\begin{array}{ll} \mu_e \geq 4780 \ cm^2/Vs \quad for \quad electrons \quad at \\ effective \quad electric \quad fields \quad of \\ E_{eff} = 0.4 \ MV/cm \quad have \quad been \quad obtained \\ [8]. \end{array}$

Fig. 8 compares carrier mobilities in graphene with and without a top-gate electrode to the universal mobility of silicon [15] and to experimental literature data for ultra thin body SOI transistors [16] over a range of effective transversal electric field. A distinct mobility reduction after top-gate deposition is observed that is attributed to the participation of the top  $\pi$ -orbitales to van der Waals bonds to the silicon dioxide. The resultant reduction of orbital overlap then leads to a reduced conductivity [7].

Fig. 8. Mobility curves of graphene FETs with and without top-gate.

substantial Despite the mobility reduction after the top-gate deposition, graphene mobility exceeds the universal mobility of silicon almost over the entire measured range. This is particularly encouraging since this result has been achieved with an evaporated top-gate oxide with a high density. charge trap Finally, comparison with ultra-thin body SOI transistors further makes a good case for graphene. Here, literature reports electron mobilities below  $\mu_e = 70 \text{ cm}^2/\text{Vs}$  in  $t_{\text{Si}} = 2.5 \text{ nm}$  films and hole mobility below [16]  $\mu_h \sim 60 \text{ cm}^2/\text{Vs}$  in 3.7 nm films [17][18]

both in (100) silicon at room temperature.

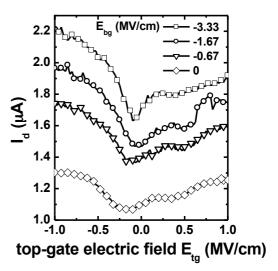

The top-gate transfer characteristics of a graphene FET are shown in Fig. 9 for four different back-gate fields E<sub>bg</sub>. The drain current I<sub>d</sub> is modulated by the topgate field Etg. The constant back-gate field  $E_{bg}$  results in an offset of the topgate transfer characteristics and does not change its ambipolar signature. The influence of the back-gate field is mainly attributed therefore to а modulation of the series resistance in the source and drain leads of the graphene FET.

Fig. 9. Top-gate transfer characteristics of a Graphene FET for different back-gate fields  $E_{bg}$ .

#### 4. Conclusion

Double-gated graphene field effect transistors are investigated in this work. In addition to previously investigated pseudo-MOS structures, a second gate is fabricated on top of graphene layers. IV-measurements show a reduction of drain currents caused by decreased carrier mobilities. Despite a poor quality top-gate oxide, however, graphene mobility values still exceed the universal mobility of silicon over

almost the entire range investigated. Furthermore, graphene exceeds by far reported mobilities in UTB SOI MOSFETs. Even though band gap engineering has been theoretically proposed to improve graphene FET operation [19][20][21], this experimental work confirms the potential of graphene as а nanoelectronics material

## 5. Acknowledgement

Financial support by the German Federal Ministry of Education and Research (BMBF) under contract number NKNF 03X5508 ("ALEGRA") is gratefully acknowledged.

## 6. References

- [1] G.E. Moore, "Cramming more components onto integrated circuits", Electronics, **38**(8), 1965.

- [2] R. H. Dennard, F. H. Gaensslen, L. Kuhn, H. N. Yu, "Design of micron MOS switching devices," Tech. Dig. IEDM, 1972.

- R. Chau, S. Datta, M. Doczy, B. [3] Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz. M. "Benchmarking Radosavljevic, Nanotechnology for High-Performance and Low-Power Logic Transistor Applications", Trans. Nanotechnology, IEEE 4(2), 2005.

- [4] Y.-M. Lin, J. Appenzeller, C. Zhihong, Z.-G. Chen, Н.-P. Avouris, "High-M. Cheng, performance dual-gate carbon nanotube FETs with 40-nm gate IEEE Electron Dev. length", Lett., 26(11), 2005.

- [5] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang,

S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, "Electric Field Effect in Atomically Thin Carbon Films", Science, **306**, pp. 666-669, October 2004.

- [6] C. Berger, Z. Song, X. Li, X. Wu, N. Brown, C. Naud, D. Mayou, T. Li, J. Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, "Electronic Confinement and Coherence in Patterned Epitaxial Graphene", Science, **312**, pp. 1191-1196, April 2006.

- [7] S. Banerjee, M. Sardar, N. Gayathri, A.K. Tyagi, B. Raj, "Enhanced Conductivity in Graphene Layers and at Their Egdes", Applied Physics Letters, 88, pp. 06211-1 06211-3, February 2006.

- [8] M.C. Lemme, T.J. Echtermeyer, M. Baus, H. Kurz, "A Graphene Field Effect Device", IEEE Electron Device Letters, 28(4), 2007.

- [9] B. Özyilmaz, P. Jarillo-Herrero, D. Efetov, D.A. Abanin, L.S. Levitov, P. Kim, "Local Gate Control of Electronic Transport in Graphene Nanostructures", preprint available at http://arxiv.org/abs/0705.3044

- [10] Williams JR, DiCarlo L, Marcus CM, "Quantum Hall Effect in a Gate-Controlled p-n Junction of Graphene", Science, 1144657, 2007.

- [11] A. C. Ferrari, J. C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscanec, D. Jiang, K. S. Novoselov, S. Roth, A. K. Geim, "Raman Spectrum of Graphene and Graphene Layers", Phys. Rev. Letters, 97: 187401, November 2006.

- [12] T.J. Echtermeyer, M.C. Lemme, J. Bolten, M. Baus, M. Ramsteiner, H. Kurz,

"Graphene Field-Effect Devices", submitted to: Springer, Special Topis Issue: European Physics Journal, 2007.

- [13] E.H. Hwang, S. Adam, S. Das Sarma, A.K. Geim, "Transport in chemically doped graphene in the presence of adsorbed molecules", pre-print available at http://www.arxiv.org/condmat/0610834

- [14] K.W.K. Shung, "Dielectric Function and Plasmon Structure of Stage-1 Intercalated Graphite", Phys. Rev. B, 34(2), pp. 979-993, 15 July 1986

- [15] S.-I. Takagi, A. Toriumi, M. Iwase, H. Tango, "On the Universality of Inversion Layer Mobility in Si MOSFET's: Part I-Effects of Substrate Impurity Concentration", IEEE Trans. Electron Dev., 41(12), 1994.

- [16] G. Tsutsui, T. Hiramoto, "Mobility and Threshold-Voltage Comparison Between (110)- and (100)-Oriented Ultrathin-Body Silicon MOSFETs", IEEE Trans. Electron Dev., 53(10), October, 2006.

- [17] Z. Ren, P. M. Solomon, T. Kanarsky, B. Doris, O.

Dokumaci, P. Oldiges, R. A. Roy, E. C. Jones, M. Ieong, R. J. Miller, W. Haensch, and H.-S. P. Wong, "Examination of hole mobility in ultra-thin body SOI MOSFETs," in IEDM Tech. Dig., 2002, pp. 51–54.

- [18] K. Uchida, S. Takagi, "Carrier scattering induced by thickness fluctuation of silicon-on-insulator film in ultrathin-body metal– oxide–semiconductor field-effect transistors", Appl. Phys. Lett., 82(17), pp. 2916-2918, 2003.

- [19] B. Obradovic, R. Kotlyar, F. Heinz, P. Matagne, T. Rakshit, M.D. Giles, M.A. Stettler, D.E. Nikonov, "Analysis of graphene nanoribbons as a channel material for field-effect transistor", Appl. Phys. Lett., 88(17), 142106, 2006.

- [20] T. Ohta, A. Bostwick, T. Seyller,

K. Horn, E. Rotenberg,

"Controlling the Electronic Structure of Bilayer Graphene",

Science, 313, 18 August 2006.

- [21] Y.W. Son, M.L. Cohen, S.G. Louie, "Energy Gaps in Graphene Nanoribbons", Phys. Rev. Letters, 97: 216803, November 2006.