# Department of Computer Science Technical Report

# Model Checking of Software for Microcontrollers

Bastian Schlich

ISSN 0935–3232 · Aachener Informatik Berichte · AIB-2008-14

RWTH Aachen · Department of Computer Science · June 2008

The publications of the Department of Computer Science of  $RWTH\ Aachen$ University are in general accessible through the World Wide Web. http://aib.informatik.rwth-aachen.de/

# Model Checking of Software for Microcontrollers

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

Diplom-Informatiker Bastian Schlich

$\frac{\mathrm{aus}}{\mathrm{Essen/Ruhr}}$

Berichter: Professor Dr.-Ing. Stefan Kowalewski Professor Dr. Jan Peleska

Tag der mündlichen Prüfung: 04.06.2008

Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar.

## **Abstract**

Software of microcontrollers is getting more and more complex. It is mandatory to extensively analyze their software as errors can lead to severe failures or cause high costs. Model checking is a formal method used to verify whether a system satisfies certain properties.

This thesis describes a new approach for model checking software for microcontrollers. In this approach, assembly code is used for model checking instead of an intermediate representation such as C code.

The development of [MC]SQUARE, which is a microcontroller assembly code model checker implementing this approach, is detailed. [MC]SQUARE has a modular architecture to cope with the hardware dependency of this approach. The single steps of the model checking process are divided into separate packages. The creation of the states is conducted by a specific simulator, which is the only hardware-dependent package. Within the simulator, the different microcontrollers are modeled accurately.

This work describes the modeling of the ATMEL ATmega16 microcontroller and details implemented abstraction techniques, which are used to tackle the state-explosion problem. These abstraction techniques include lazy interrupt evaluation, lazy stack evaluation, delayed nondeterminism, dead variable reduction, and path reduction. Delayed nondeterminism introduces symbolic states, which represent a set of states, into [MC]SQUARE while still explicit model checking techniques are used. Thus, we successfully combined explicit and symbolic model checking techniques.

A formal model of the simulator, which we developed to prove the correctness of abstraction techniques, is described. In this work, the formal model is used to show the correctness of delayed nondeterminism.

To show the applicability of the approach, two case studies are described. In these case studies, we used programs of different sizes. All these programs were created by students in lab courses, during diploma theses, or in exercises without the intention to use them for model checking.

# **Acknowledgments**

First and foremost, I would like to thank Professor Dr.-Ing. Stefan Kowalewski for giving me the opportunity to join his group to write my Dissertation thesis. He provided me great degrees of freedom to find my own topic and assisted me making important decisions. He was always willing to listen to my problems and gave me many useful advices.

I thank Professor Dr. Jan Peleska for his willingness to be part of my Promotionskomission. Moreover, I thank him for the invitations to Bremen during which we had many fruitful discussions.

I sincerely thank all members of Informatik 11 for the friendly working atmosphere, which contributed a lot to this thesis. Particularly, I have to thank my friends and colleagues Daniel Klünder, Falk Salewski, and Dirk Wilking for many fruitful discussions and for answering a pledora of questions both related and unrelated to my Dissertation thesis. Furthermore, I thank Dr. Carsten Weise for many useful hints and advices during the final phase of my thesis. I thank my students Lucas Brutschy, Eduard Feicho, Dominique Gückel, Volker Kamin, Jann Löll, Michael Rohrbach, Florian Scheuer, and John Schommer for helping me to implement [MC]SQUARE.

I gratefully thank Dr. Thomas Noll for his support during the last year. He helped me to get a more formal insight of delayed nondeterminism and gave me many useful advices for my thesis. He always took the time to answer my numerous questions.

I thank Dr. Ralf Huuck for inviting me to Australia. We had many interesting discussions and his pragmatism helped me to solve some of the problems that arise when writing a Dissertation thesis. Furthermore, I thank all colleagues of the Managing Complexity program at the National ICT Australia in Sydney. Especially, I thank Timothy Bourke, Jörg Brauer, Dr. Ansgar Fehnker, Dr. Gerwin Klein, Rafal Kolanski, and Harvey Tuch for many discussions and their valuable comments about my thesis.

I appreciate Dr. Michael Weber's contribution in the initial phase of my Dissertation thesis. He helped me discovering the peculiarities of assembly code.

Last but not least, I would like to thank my family. They always supported me and helped my to find my way. Without them, this thesis would not have been possible.

Bastian Schlich Aachen, June 2008

# **Contents**

| 1 | Intr | oduction 1                                      |

|---|------|-------------------------------------------------|

|   | 1.1  | Objectives                                      |

|   | 1.2  | Contributions                                   |

|   | 1.3  | Outline                                         |

|   | 1.4  | Bibliographic Notes                             |

|   | 1.5  | Notation                                        |

| 2 | Pre  | iminaries 7                                     |

|   | 2.1  | Computation Tree Logic                          |

|   | 2.2  | Model Checking                                  |

|   |      | 2.2.1 Explicit vs. Symbolic Model Checking      |

|   |      | 2.2.2 Global vs. Local Model Checking           |

|   |      | 2.2.3 Counterexamples & Witnesses               |

|   | 2.3  | Static Analysis                                 |

| 3 | Mod  | del Checking Software for Microcontrollers 13   |

|   | 3.1  | Model Checking C Code                           |

|   | 3.2  | Model Checking Assembly Code                    |

|   | 3.3  | Requirements for an Assembly Code Model Checker |

| 4 | [mc  | square 21                                       |

|   | 4.1  | Features                                        |

|   | 4.2  | Architecture                                    |

|   | 4.3  | Evaluation                                      |

| 5 | Stat | e Space Building in [mc]square 29               |

|   | 5.1  | Simulator Overview                              |

|   | 5.2  | Simulator State                                 |

|   | 5.3  | Microcontroller                                 |

|   |      | 5.3.1 Core                                      |

|   |      | 5.3.2 Memories                                  |

|   |      | 5.3.3 Stack                                     |

|   |      | 5.3.4 Interrupts                                |

|   |      | 5.3.5 I/O Ports                                 |

| 8 | Case | Studie  | es 1                                     | 15  |

|---|------|---------|------------------------------------------|-----|

|   | 7.4  | Relate  | d Work                                   | 113 |

|   | 7.3  |         |                                          | 112 |

|   | 7.2  |         | 1                                        | 109 |

|   | 7.0  | 7.1.4   | 1                                        | 107 |

|   |      | 7.1.3   | 9                                        | 106 |

|   |      | 7.1.2   | 9                                        | 103 |

|   |      |         | Local Model Checking                     | 99  |

|   | 7.1  |         | Checker                                  | 97  |

| 7 |      |         |                                          | 97  |

| 7 | N. 4 | I-I C'  | atticus in facultament                   | 07  |

|   | 6.5  | Relate  | d Work                                   | 93  |

|   |      | 6.4.2   | Path Reduction                           | 91  |

|   |      | 6.4.1   | Dead Variable Reduction                  | 90  |

|   | 6.4  | Abstra  | action Techniques                        | 90  |

|   |      | 6.3.5   | Global Interrupt Flag Analysis           | 88  |

|   |      | 6.3.4   | Stack Analysis                           | 86  |

|   |      | 6.3.3   | Reaching Definitions Analysis            | 84  |

|   |      | 6.3.2   | Live Variables Analysis                  | 81  |

|   |      | 6.3.1   | Control Flow Analysis                    | 79  |

|   | 6.3  |         | Analyses                                 | 79  |

|   | 6.2  |         | Analyzer Overview                        | 77  |

|   | 6.1  |         | nges in Static Analysis of Assembly Code | 75  |

| 6 | Stat | ic Anal | ysis in [mc]square                       | 75  |

|   |      | 5.8.2   | Delayed Nondeterminism                   | 73  |

|   |      | 5.8.1   | Model Checking Machine Code              | 71  |

|   | 5.8  |         | d Work                                   | 70  |

|   | F 0  | 5.7.4   | Establishing Correctness                 | 70  |

|   |      | 5.7.3   | Coping with Nondeterminism               | 67  |

|   |      | 5.7.2   | Modeling the ATMEL ATmega16              | 65  |

|   |      | 5.7.1   | Handlers and Guarded Assignments         | 63  |

|   | 5.7  |         | l Model of the Simulator                 | 62  |

|   |      | 5.6.3   | Delayed Nondeterminism                   | 58  |

|   |      | 5.6.2   | Immediate Instantiation                  | 56  |

|   |      | 5.6.1   | Determinizer Overview                    | 53  |

|   | 5.6  | Determ  | ninizer                                  | 53  |

|   | 5.5  | Instruc | ction Simulator                          | 50  |

|   | 5.4  | Progra  | vm                                       | 48  |

|   |      | 5.3.6   | Timers                                   | 44  |

|   |      |         |                                          |     |

|   | 8.1 | Effects | s of Abstracti | on T  | echn         | ique | s o | n I  | Diff | ere | $_{ m nt}$ | Pr | og | rai | ns |  |  |  | 115 |

|---|-----|---------|----------------|-------|--------------|------|-----|------|------|-----|------------|----|----|-----|----|--|--|--|-----|

|   |     | 8.1.1   | Execution .    |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 115 |

|   |     | 8.1.2   | Evaluation     |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 120 |

|   | 8.2 | An Au   | atomotive Mic  | croco | $_{ m ntro}$ | ller | Apj | plic | ati  | ion |            |    |    |     |    |  |  |  | 121 |

|   |     | 8.2.1   | Application    |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 122 |

|   |     | 8.2.2   | Execution .    |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 122 |

|   |     | 8.2.3   | Evaluation     |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 129 |

| _ | _   |         |                |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  |     |

| 9 | Con | clusion |                |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 131 |

|   | 9.1 | Discus  | ssion          |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 131 |

|   | 9.2 | Future  | e Work         |       |              |      |     |      |      |     |            |    |    |     |    |  |  |  | 133 |

## 1 Introduction

Embedded systems are widely used in our daily life. They are, for example, employed in airplanes, cars, mobile phones, and household appliances. Embedded systems consist of hardware and software. The importance of the software on these devices is increasing because more and more functionality is implemented within the software and no longer realized by the hardware. The software of embedded systems has to be tested extensively and validated because errors in the software may lead to severe or even fatal events, as in case of the Ariane 5 disaster [76], or high costs and loss of reputation, as in the case of the Toyota Prius bug [68].

Many embedded systems are based on microcontrollers, which are special purpose computers on a single chip. They are often specifically developed for single applications. The software for microcontrollers is mostly written in C or in assembly language.

Removing errors in microcontroller software is difficult in the field because deploying the updates is complicated and cost-intensive. In contrast to software run on general-purpose personal computers, it is often not possible for users to update microcontroller software themselves. For example, the software of a car can only be updated in a garage. In some cases, the software cannot be updated at all due to the type of memory used to store the program. This may render the affected microcontrollers useless.

Full or extensive testing of microcontroller software is often not possible because it is too time-consuming for the desired time to market or too expensive for the specific product. Also, testing alone is not sufficient for safety critical systems. There are standards such as IEC61508 [66] that strongly recommend the application of formal methods if a system requires a certain safety level. An example for safety levels are the safety integrity levels defined in the IEC61508 standard. The formal methods mentioned in this standard include verification techniques such as model checking [5, 15, 33, 78, 108] and automatic theorem proving.

Model checking is able to automatically verify systems. It uses an exhaustive search over all reachable system states to check whether the system (model) satisfies a given property (specification). If the system does not satisfy the property, the model checker provides a counterexample, which details the error. Model checking can be applied to systems that do not have a full specification.

Automatic theorem proving is a verification technique used to prove the correctness of a system. Depending on the complexity of the problem, an automatic theorem prover is able to prove that something is true, but it may be unable to disprove something, which is not true. In this case it is possible that the theorem prover does not terminate. Often, the theorem prover requires user interaction and hence, developers have to be educated to use theorem provers. In contrast, developers familiar with simulators can use model checkers more easily as their application is similar [33].

Model checking is used by companies such as AMD, Infineon, Intel, and Siemens for the analysis of hardware systems. After the Pentium FDIV bug [128], hardware vendors realized that errors in designs can cause major losses and hence started to use model checking and other formal methods to analyze their systems. Also, software companies such as Microsoft are beginning to use model checking for the verification of crucial parts of their software.

Industries such as the automotive industry are interested in using model checking for the analysis of software for microcontrollers. In the development of software for microcontrollers, however, model checkers are far from being well established. Besides the state-explosion problem, one of the limiting factors is that most of the available model checkers use custom input models. Consequently, developers have to remodel specifications and implementations to feed them into the model checker. They have to do this every time the system is changed. This is usually not considered to be worth the effort as it is time-consuming and error-prone.

Existing model checkers are not able to handle all constructs needed to check microcontroller programs out-of-the-box [101, 104]. Due to short market cycles in many microcontroller software projects, developers often do not have enough time and training to create models of their software for model checking. Furthermore, many model checkers are not intuitively usable and differ from development tools usually applied by developers. Therefore, model checking is not widely used in microcontroller software projects.

## 1.1 Objectives

Our objective is to develop an approach for verifying microcontroller software. We want to implement this approach in a model checker, which should be usable by developers of microcontroller software. The approach should work on source code out-of-the-box. That is, the user should be able to check the source code without preprocessing or manually annotating the code or creating a model in a custom language.

To achieve our goals, we first have to decide whether to model check C or assembly code. Furthermore, we need to find out whether we can implement our approach by extending an existing model checker or if it is beneficial to develop a new model checker. We have to apply techniques to mitigate the state-explosion problem, which

model checking can suffer from. For this purpose, we want to utilize static analysis and employ different abstraction techniques. Furthermore, we want to find out whether accurately modeling particular microcontrollers enables us to develop more specific abstraction techniques. Finally, we have to develop a formal model to prove the validity of such abstraction techniques.

Since developers of microcontroller software should apply the model checker themselves, we must hide its internal details from them and provide a GUI that is similar to their other tools.

#### 1.2 Contributions

The main contributions of this thesis supporting our objectives are as follows.

- We have developed an approach to model check microcontroller assembly programs and implemented this approach within our model checker [MC]SQUARE. [MC]SQUARE uses a special *simulator* for microcontroller assembly code to build the state space. Within this simulator, we have accurately modeled the microcontroller to support reasoning about microcontroller features such as registers, I/O registers, and the values of variables. To tackle the state-explosion problem, we have implemented various *abstraction techniques* in the simulator.

- We have developed a new abstraction technique called *delayed nondeterminism*, which reduces the size of the state space. It introduces *lazy states* into our model checker. A lazy state is a state that consists of explicit and symbolic parts and hence represents a set of states. As our model checking algorithms are explicit, the symbolic parts, which are induced by nondeterminism, are lazily resolved only when the model checker accesses them. Using this technique, we have combined explicit and symbolic techniques in [MC]SQUARE.

- We have adapted two abstraction techniques, namely dead variable reduction and path reduction, to be applicable in model checking of microcontroller assembly code. These two techniques use static analyses, which were initially not directly applicable to microcontroller assembly code. We have adapted these static analyses and improved their accuracy by using abstract interpretation.

- Within the simulator, we have realized two abstractions techniques that exploit the specifics of the microcontroller. One technique called *lazy stack evaluation* deals with the contents of the stack. The other technique called *lazy interrupt evaluation* addresses the invocation of interrupt handlers.

- We have developed a *formal model* of our microcontroller simulator, which can be used to prove the validity of abstraction techniques implemented in [MC]-SQUARE. This formal model can also be used as an intermediate representation for the implementation of simulators for other microcontrollers.

- Using our formal model, we have proven that the abstraction technique called delayed nondeterminism preserves a simulation relation between the concrete and the abstract state space.

- We have conducted two case studies showing that model checking can indeed be used to analyze microcontroller assembly programs of a certain, reasonable size.

#### 1.3 Outline

Chapter 2 describes preliminaries used throughout the thesis. The next chapter discusses the choice of whether to model check C or assembly code and provides requirements for a new model checker for microcontroller assembly code.

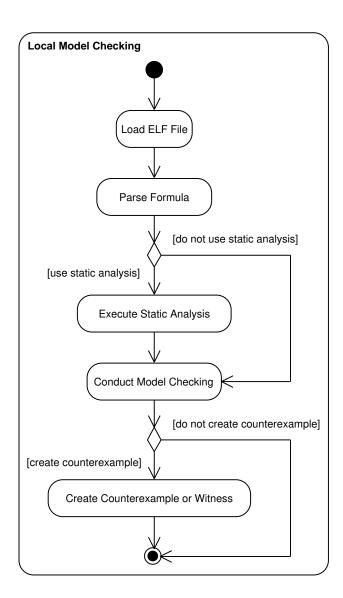

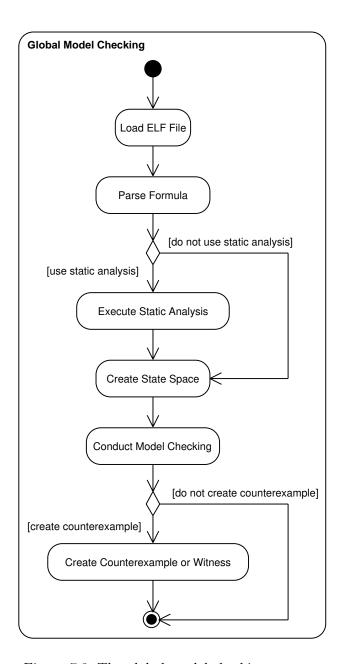

Chapter 4 gives an overview of our assembly code model checker [MC]SQUARE and depicts its architecture. The subsequent three chapters detail the four main packages of [MC]SQUARE. First, the *Simulator* package, which is used to create states, is described. Then, the *Static Analyzer* package, which conducts the static analyses used by some abstraction techniques, is presented. Finally, in Chapter 7, the *Model Checker* package, which performs the actual model checking, and the *State Space* package, which manages the states, are detailed.

Chapter 8 presents two case studies, which demonstrate the usage of [MC]SQUARE. The first case study presents the effects of the different abstraction techniques implemented in [MC]SQUARE. The second case study details the way the user applies [MC]SQUARE for model checking. Chapter 9 concludes the thesis and gives directions for future improvements. We cover related work within each chapter.

## 1.4 Bibliographic Notes

Some parts of this thesis are based on work that we described in earlier publications. The survey of the C code model checkers, which is described in Sect. 3.1, is summarized by us in two papers [101, 104]. We described a preliminary version of the architecture of [MC]SQUARE presented in Sect. 4.2 elsewhere [103]. The idea to use a simulator to build the state space for model checking is sketched in two publications [102, 103]. We outlined the handling of nondeterminism detailed in Sect. 5.6 in a paper [60]. The formal model presented in Sect. 5.7 is described by us in two publications [60, 88]. The static analyses detailed in Chap. 6 are summarized

in a paper [107]. We also applied the programs used in the case study shown in Sect. 8.1 elsewhere [60, 88, 101–104, 107]. The case study presented in Sect. 8.2 is published in a paper [106]. The individual chapters of this thesis detail related work.

#### 1.5 Notation

In this thesis, we use the following notations. Names of tools are typeset in a capitalized font like ExampleTool. Names of packages and classes are set in a slanted font, for example, *ExampleClass*. Source code is typeset in a sans-serif font, for instance, exampleMethod(). Ideas and important terms are emphasized such as *example idea*.

# 2 Preliminaries

This chapter presents some preliminaries, which are used throughout this thesis. The first section describes the computation tree logic. Section 2.2 presents the basic idea of model checking, gives a basic classification of different model checking algorithms, and explains the terms counterexample and witness. The last section gives an introduction into static analysis.

#### 2.1 Computation Tree Logic

Propositional logic only allows to reason about states. In reactive systems we are also interested in describing the sequence of states. Temporal logic [93] extends propositional logic to allow the reasoning about the sequence of states. Examples for a temporal logic are Linear Temporal Logic (LTL) [92, 93] and Computation Tree Logic (CTL) [13, 31, 42]. LTL formulas describe properties of the set of all paths. In contrast, CTL formulas describe properties of computation trees. That is, these formulas can describe properties of single paths within these trees. In the following we describe CTL in detail. This section is primarily based on the book by Clarke et al. [33].

CTL is a sublogic of CTL\* [31, 32, 43]. In CTL\*, there are path quantifiers and temporal operators. Path quantifiers include **A** and **E**. **A** means that from a certain state on all paths satisfy some property. **E** means that at least one path leaving the current states satisfies some property. The temporal operators describe the properties of a path through the tree:

- Next (X) means that the property has to hold in the next state.

- Finally (**F**) requires that the property holds in one state on the path.

- Globally (**G**) means that the property holds in all states on the path.

- Until (U) requires that the first property holds until the second property becomes true.

In CTL\* there is no restriction on how to combine temporal operators and path quantifiers. In CTL, a temporal operator always must be preceded by a path quantifier. In CTL there are two kinds of formulas: state formulas and path formulas. Given a set AP of atomic propositions, the syntax of CTL is defined as follows:

- If  $p \in AP$ , then p is a state formula.

- If  $f_1$  and  $f_2$  are state formulas, then  $\neg f_1$ ,  $f_1 \lor f_2$ , and  $f_1 \land f_2$  are state formulas.

- If  $f_1$  is a path formula, then  $\mathbf{E} f_1$  and  $\mathbf{A} f_1$  are state formulas.

- If  $f_1$  and  $f_2$  are state formulas, then  $\mathbf{X} f_1$ ,  $\mathbf{F} f_1$ ,  $\mathbf{G} f_1$ , and  $f_1 \mathbf{U} f_2$  are path formulas.

The semantic of CTL can be defined with respect to a Kripke structure. A Kripke structure is triple  $\langle S, R, L \rangle$ , where:

- S is the set of states,

- $R \subseteq S \times S$  is the total transition relation and

- $L: S \to 2^{AP}$  is a function that labels each state with a set of atomic propositions.

Details about the semantics of CTL formulas are given elsewhere [5, 15, 33, 57].

In this thesis, we need the terms subformulas, proper subformulas, length of a formula, and the subformula evaluation order. These terms are defined in the following. All these definitions are taken from Heljanko [57].

**Definition 1** (Subformulas). Let f be a CTL formula. The set of *subformulas* sub(f) of f is recursively defined as follows:

- 1. If f is an atomic proposition  $p \in AP$ , then  $sub(f) = \{f\}$ .

- 2. If f is of the form  $\neg f_1$ ,  $\mathbf{EX} f_1$ ,  $\mathbf{EF} f_1$ ,  $\mathbf{EG} f_1$ ,  $\mathbf{AX} f_1$ ,  $\mathbf{AF} f_1$ , or  $\mathbf{AG} f_1$ , then  $\mathrm{sub}(f) = \{f\} \cup \mathrm{sub}(f_1)$ .

- 3. If f is of the form  $f_1 \vee f_2$ ,  $f_1 \wedge f_2$ ,  $\mathbf{E}[f_1 \mathbf{U} f_2]$ , or  $\mathbf{A}[f_1 \mathbf{U} f_2]$ , then  $\mathrm{sub}(f) = \{f\} \cup \mathrm{sub}(f_1) \cup \mathrm{sub}(f_2)$ .

**Definition 2** (Proper Subformulas). Let f be a CTL formula. The set of *proper* subformulas psub(f) of f is defined by:

$$psub(f) = sub(f) \setminus \{f\}.$$

**Definition 3** (Length of a Formula). Let f be a CTL formula. The *length of a* formula f, length (f) is defined by:

$$length(f) = |sub(f)|,$$

where  $|\operatorname{sub}(F)|$  means the cardinality of the set  $\operatorname{sub}(f)$ .

**Definition 4** (Subformula Evaluation Order). Let f be a CTL formula. We define the partial order  $<_s$ , which is called *subformula evaluation order*, as follows. For all CTL formulas f' and  $f'' \in \text{sub}(f)$ ,  $(f', f'') \in <_s$  (also written as  $f' <_s f''$ ), iff  $f' \in \text{psub}(f'')$  (f' belongs to the set of proper subformulas of f'').

In this thesis, we often refer to a logic called ACTL [38, 41, 52]. ACTL is a sublogic of CTL in which only the **A** path quantifier is allowed and negations are only feasible in atomic propositions. This fragment is called the universal fragment of CTL. Another sublogic of CTL is ECTL [38, 41, 52]. In ECTL formulas only the **E** path quantifier is permitted and negations are only allowed in atomic propositions. This fragment of CTL is called existential fragment of CTL.

Furthermore, we often refer to invariants. An invariant is a formula of the form  $\mathbf{AG} f$ , where f is only using operators from propositional logic and not using path operators or temporal operators.

### 2.2 Model Checking

Model checking [5, 15, 33, 78, 108] is a formal method for the automatic verification of systems. It uses an exhaustive search over all reachable states of the system to check whether the system (model) satisfies a given property (specification). The method was independently proposed by Clarke and Emerson [31] and by Queille and Sifakis [95]. Given a model M and a formula f, it checks whether M is a model of f ( $M \models f$ ). That is, it checks if the system satisfies the given property.

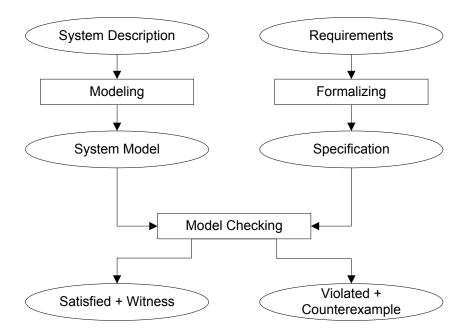

The method is depicted in Fig. 2.1. In a first step, which is called modeling, the system description is transformed into the system model. A system description is, for example, a program written in C, Java or Assembly language. A system model is, for example, a Kripke structure, a labeled transition system, or a finite automaton. The modeling can be done manually or automatically. A manual modeling is error-prone and time-consuming, but it can help to find errors in the system description or in the specification because it complies with an intensive review of the system. When dealing with large descriptions of real systems, an automatic approach is preferable.

The requirements have to be manually formalized because they are mostly given in natural language. The result of this formalization is the formal specification given as formulas in a temporal logic such as CTL\*, CTL, or LTL. The model and the specification are inputs given to the model checker.

The model checker uses an exhaustive search over all reachable states of the model to check whether the model satisfies the formula. In the end, it returns a result. The result may be that the model satisfies the formula together with a witness or that the model does not satisfy the formula together with a counterexample (see Sect. 2.2.3). Due to the state-explosion problem, it may happen that the model checker runs out of memory and does not return a result.

Figure 2.1: Model checking process (see Baier and Katoen [5] and Manna and Pnueli [78]).

There are different ways to conduct model checking. In the following, we describe and compare some of them. A thorough classification of different model checking techniques is given by Visser [123]. At the end of this section, we detail the differences between a counterexample and a witness.

#### 2.2.1 Explicit vs. Symbolic Model Checking

In explicit model checking the state and the transitions are represented explicitly. That is, each state is stored as it is. Explicit model checking algorithms have to visit single states and work on them. In symbolic model checking states are not represented explicitly but implicitly. Symbolic model checking algorithms work on sets of states instead of single states. The sets of visited states and transitions is often encoded in Binary Decision Diagrams or Ordered Binary Decision Diagrams. Depending on the structure of the transition system, these representations can be very compact. However, there are cases where these representations are not effective. Hu et al. [65] show that each of these two methods has domains where it outperforms its counterpart.

#### 2.2.2 Global vs. Local Model Checking

In global model checking, the complete state space is built before model checking because a global model checking algorithm evaluates the truth values of all subformulas for all states. In contrast, only the truth values of certain subformulas in certain states are evaluated in local model checking. A local model checking algorithm only needs to evaluate the subformulas and visit the states that are needed to evaluate the truth value of the formula in the initial states of the model. Therefore, it is possible generate the state space on-the-fly during model checking when using a local model checking algorithm.

#### 2.2.3 Counterexamples & Witnesses

As we use CTL model checking, we define counterexamples and witnesses in reference to model checking of CTL formulas. These definitions are based on the books by Baier and Katoen [5] and Clarke et al. [33].

**Definition 5** (Counterexample). A counterexample is a part of the state space indicating why a universally quantified path formula (e.g.,  $\mathbf{AG} f$ ) is refuted.

**Definition 6** (Witness). A witness is a part of the state space that indicates why an existential quantified path formula (e.g.,  $\mathbf{EF} f$ ) is satisfied.

If a universally quantified formula is false, the model checker finds a witness for the negation of this formula. For instance, if the formula  $\mathbf{AG}f$  is false, the model checker returns a witness for the formula  $\mathbf{EF}\neg f$ , which is a counterexample for the formula  $\mathbf{AG}f$ . Hence, the terms witness and counterexample can be used alternatively. Therefore, we only use the term counterexample in this thesis whenever we mean counterexample or witness.

## 2.3 Static Analysis

Static analysis, which is also called program analysis, offers techniques to statically determine at compile time an approximation of the values or behaviors observed during runtime. In static analysis, the program is not executed, but the analysis are conducted on the source code of the program. This has the advantage that static analysis can be applied to very large programs. The disadvantage is that sometimes the approximation of the values and behaviors calculated by the static analysis can be too coarse. That is, no definite conclusions can be drawn from the results of the static analysis. This section, which is mainly based on the book by Nielson et al. [87], introduces the basic principles of static analysis.

Here, we sketch two different types of static analyses:  $control\ flow\ analysis\ (CFA)$  and  $data\ flow\ analysis\ (DFA)$ . CFA is used to determine how control evolves from one

program location to another program location. That is, it is used to determine the control flow graph of a program. The nodes in this graph are program locations, and the edges connect two program locations if it is possible for the control to get from one location to the other. In the DFA, this graph is used to determine different data flow properties. Example for DFAs are: live variables analysis, reaching definitions analysis, and available expressions analysis.

DFA can be conducted intraprocedural or interprocedural. In an intraprocedural analysis, the analysis is conducted for each function alone. Interactions between functions are not accounted. In an interprocedural analysis, the analysis additionally considers interactions between different functions. That is, it considers the effect of function calls and interrupts. DFAs can be expressed as so-called *data flow equations*. One way to solve these equations is the *worklist algorithm* [87] (see Sect. 6.3.2).

In abstract interpretation [36] a program is interpreted using an abstract semantics instead of the concrete semantics of the program. Using a sufficiently abstract semantics enables analyses that are otherwise not computable. In abstract interpretation, the abstract semantics has to be a superset (over-approximation) of the concrete semantics. Due to the abstract semantics, the program can exhibit behavior that is not possible using the concrete semantics. Thus, false alarms are possible, but if no errors are found in the abstract semantics, it is guaranteed that no errors are present in the concrete semantics.

# 3 Model Checking Software for Microcontrollers

This chapter details why we use assembly code instead of C code for model checking software for microcontrollers. The first section gives an overview of existing C code model checkers and explains why none of them are currently able to model check microcontroller C code out-of-the-box. After that, we explain why we decided not to check C code. The next section presents the advantages and disadvantages of using assembly code for model checking and evaluates them. The last section gives a list of requirements that a model checker for microcontroller assembly code has to fulfill to be applicable. A comparison of existing assembly code model checkers is given in Sect. 5.8.

### 3.1 Model Checking C Code

In almost every microcontroller software project there is a development phase in which the software exists as C code. Hence, one solution to model check software for microcontrollers is to model check the corresponding C code.

We conducted a case study [101, 104] in which we tried to model check micro-controller C programs using existing C code model checkers. Table 3.1 gives a survey of all model checkers considered in the case study. The table presents for each model checker a short description of the techniques utilized. We composed the information shown in the table during the case study. Therefore, it is possible that some techniques may have changed and some newer model checkers are not mentioned at all. We provide more details about the case study in the corresponding papers [101, 104].

All model checkers shown in the table except for STEAM are used to verify hardware-independent ANSI C software such as protocols or high-level drivers. Most of them check sequential programs, but MAGIC, KISS, and ZING are also able to handle concurrent programs. STEAM is utilized to check parallel C++ programs. Some of the model checkers shown in the table support almost full ANSI C and C++ respectively, while others restrict the set of allowed constructs due to the techniques applied in the model checking process.

Table 3.1: List of C code model checkers.

| Model Checker         | Institute                | Model | Techniques used                                                                                                                                                       |

|-----------------------|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLAST [59]            | UC Berkeley              | С     | C intermediate language (CIL) [86], control flow automaton, predicate abstraction [35, 51], counterexample-guided abstraction refinement (CEGAR) [34], theorem prover |

| BOOP [127]            | IST Graz                 | С     | Boolean program [8], predicate<br>abstraction, CEGAR, theorem<br>prover, model checking with<br>MOPED [110]                                                           |

| CBMC [28]             | CMU                      | C/C++ | bounded model checking using SAT solver                                                                                                                               |

| FEAVER [64]           | Bell Labs                | С     | translation into Promela, model checking with SPIN [62]                                                                                                               |

| FOCUSCHECK [69]       | Iowa State<br>University | С     | CIL, translation into pushdown<br>system, constraint solver, model<br>checking of pushdown system                                                                     |

| F-Soft [67]           | NEC                      | С     | CIL, CFG, predicate abstraction,<br>SAT solver, model checking with<br>VERISOL (DIVER) [48]                                                                           |

| MAGIC [23, 24]        | CMU                      | С     | CIL, modular verification, control flow automaton, predicate abstraction, CEGAR, theorem prover                                                                       |

| MOPS [25]             | UC Davis, UC<br>Berkeley | С     | CFG, translation into pushdown automaton, model checking of pushdown automaton                                                                                        |

| SATABS [29, 30]       | CMU                      | C/C++ | Boolean program, predicate<br>abstraction, CEGAR, SAT solver,<br>model checking with SMV [79]                                                                         |

| SLAM [9, 10]          | Microsoft<br>Research    | С     | Boolean program, predicate abstraction, CEGAR, theorem prover, model checking with BEBOP [8]                                                                          |

| STEAM<br>[73, 80, 81] | University<br>Dortmund   | C++   | translation into machine code, state space generation with Internet C++ Virtual Machine                                                                               |

| KISS [94]             | Microsoft<br>Research    | -     | extension to SLAM to check<br>concurrent programs                                                                                                                     |

| ZING [1, 2]           | Microsoft<br>Research    | С     | translation into ZING model, model checking with ZING model checker                                                                                                   |

Model checkers that use theorem provers suffer from three restrictions due to the underlying general-purpose theorem provers. First, only a limited number of C constructs are supported. Second, pointer arithmetic is only supported in a restricted manner. Third, possible arithmetic overflows are neglected. Model checkers utilizing SAT solvers require the model to be finite. Consequentially, recursion and dynamic memory allocations are not handled.

Approaches that translate the C code into another model or language have to cope with two problems. First, the target language has to support all constructs present in the source language, which is sometimes not possible. Second, the translation process often leads to growth of the model to be checked and hence, the state spaces created during model checking tend to be bigger. Besides, the bigger state spaces lead to longer error traces, which are more complex and hence, more difficult to understand.

Beside ANSI C language features, microcontroller C programs also comprise extra language features such as compiler-specific constructs, hardware-dependent constructs, and embedded assembly language statements. All these features are not handled by the model checkers shown in Tab. 3.1. Furthermore, microcontroller C programs often access the memory directly as certain operations of the microcontroller are controlled by special registers, which are located at fixed memory addresses (e.g., I/O registers used to read input from the environment). In contrast, direct memory accesses are reported as errors by most C code model checkers because direct accesses to memory can lead to errors in an environment where dynamic linking and loading is supported.

Listing 3.1 shows an example for a microcontroller C program that controls an automotive window lift. The program is one of the programs used in case studies described in Chap. 8, which are used to determine the overall performance of [MC]-SQUARE and compare effects of different techniques applied. At first sight, it looks like an ANSI C program. It contains function calls, assignments, if clauses, and while loops. Most variables are read and written by the program, while a couple of the variables, such as TCCR1B, are only written. These variables are used to control the microcontroller. Some of the model checkers shown in Tab. 3.1 remove or ignore variables that are only written and thus disregard important parts of microcontroller C programs.

Listing 3.2 displays the program shown in List. 3.1 after being preprocessed. This listing evidences that the window lift program is not an ANSI C program, but it is a typical microcontroller C program. The program contains embedded assembly language statements, direct memory accesses, and accesses to certain microcontroller functions. None of the model checkers described above can handle these constructs out of the box. Some produce warnings, while others just ignore these features. In case of direct memory accesses, a couple of the C code model checkers throw error messages because direct memory accesses are considered as errors in ANSI C

Listing 3.1: Part of window lift program before preprocessing.

```

int main (void) {

// call initialization

init();

sei();

while(1) {

inputs = PINA & 0 \times 0F;

cli();

if (direction != 5) {

if (inputs & (1 << 1)) {// down

if (direction != 1 \&\& direction <math>!= 2) {

10

TCCR1B = 0 \times 00;

TIFR = 0 \times FF;

TCNT1 = 0 \times 00;

TIMSK = (1 << OCIE1A);

TCCR1B = 0 \times 05;

1.5

direction = 1;

}

```

programs running on general-purpose computers that support dynamic linking and loading. Using direct memory accesses in conjunction with dynamic linking and binding is error-prone because wrong parts of the memory can be accessed, which is an issue for code and stack safety, for example.

As these C code model checkers only support a subset of the needed constructs, it is not possible to use them out-of-the-box to model check microcontroller C programs. We tried to extend one of these C code model checkers to support all needed constructs, but we found out that the necessary changes were too costly [101, 104]. Therefore, we propose another solution.

# 3.2 Model Checking Assembly Code

Since we could not use existing C code model checkers to model check microcontroller C programs, we decided to use the assembly code for model checking. Assembly code is the artifact that is deployed to the microcontroller and not an intermediate representation such as C code. Therefore, model checking of assembly code has various advantages compared to model checking of C code [6, 73, 80, 82, 102, 105]:

• As the assembly code is the result at the end of the development, all errors introduced during the complete development process can be found. These

Listing 3.2: Part of window lift program after preprocessing.

#### errors include:

- compiler errors, that is, errors introduced by compiler behavior or optimizations,

- errors introduced during post-compilation steps (e.g., insertion of instrumentation code or optimizations),

- errors in microcontroller usage (e.g., write access to reserved registers),

- errors that are not visible in intermediate representations such as C code (e.g., reentrance problems), and

- hardware-dependent errors such as stack overflows and underflows.

- Programs consisting of components written in different programming languages can be verified. When model checking the source code, only single components can be verified, and for each programming language a specific model checker has to be utilized.

- Source code of the software is not required. Hence, programs that use libraries, which are not available in source code, can be analyzed.

- The model checker does not need to exploit the compiler and optimizer behavior.

- Hardware-dependent constructs can be handled.

- Assembly language statements that are embedded into the source code are considered appropriately by the model checker (i.e., not ignored as done by most C code model checkers).

- Assembly language has a clean and well documented semantics. Microcontroller vendors provide documentations describing the semantics of the different assembly language constructs.

- Assembly language statements are easier to handle than certain C constructs (e.g., pointer arithmetic or function calls via pointers).

Beside these various advantages, model checking assembly code has some disadvantages:

- A model checker for microcontroller assembly code is hardware dependent. That is, the model checker has to be adapted for each new microcontroller that should be supported.

- Since assembly code has more lines of code and involves more details than C code, the state spaces created during model checking of assembly code tend to be larger than the state spaces created during model checking of C code. This growth of the state spaces may also lead to longer counterexamples.

The advantages and disadvantages of model checking assembly code for micro-controllers lead to requirements that have to be fulfilled by a model checker to be applicable in industry. To the best of our knowledge, there was no model checker available that was able to model check microcontroller assembly code without manual preparation when we started the development of our model checker. Section 5.8 gives a detailed description of related work regarding assembly code model checking.

# 3.3 Requirements for an Assembly Code Model Checker

This section describes the requirements that our model checker for microcontroller assembly code has to satisfy. Table 3.2 presents the non-functional requirements (qualities)<sup>1</sup>, and Tab. 3.3 shows the functional requirements<sup>1</sup>.

The aim of our development is a model checker that serves two purposes. First, it is usable by developers working in industry, which are not familiar with the application of formal methods. Second, the model checker serves as a research tool that can be utilized to evaluate new algorithms and abstraction techniques. These

<sup>&</sup>lt;sup>1</sup>We use the terms functional requirement and quality as defined by Bass et al. [12].

two purposes are reflected by qualities Q1 and Q2. These two qualities implicate other qualities and requirements. Extendability (Q3–Q6) in different directions is an implication of both qualities. The model checker is extendable to support new microcontrollers to be applicable in industry. Moreover, it is possible to integrate existing simulators into the model checker. To use the model checker as a research tool in academia, it is extendable to use other model checking algorithms and abstraction techniques. Since there are different operating systems used in industry and academia, the tool is executable on the three major operating systems (Q7).

Table 3.2: List of non-functional requirements.

| Number | Requirement                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q1     | The model checker is usable by developers working in industry, which are not familiar with formal methods.                                                               |

| Q2     | The model checker is usable as a research tool in academia to evaluate new algorithms in different areas (e.g., model checking, static analysis, simulation of systems). |

| Q3     | The model checker is extendable to support new microcontrollers.                                                                                                         |

| Q4     | It is possible to use external simulators to build the state space.                                                                                                      |

| Q5     | The model checker is extendable to support new model checking algorithms.                                                                                                |

| Q6     | The model checker is extendable to support new abstraction techniques.                                                                                                   |

| Q7     | The model checker works on the following operating systems: Microsoft Windows, Mac OS, and Linux.                                                                        |

Q1 and Q2 are the driving qualities (see Bass et al. [12]) of our model checker's development. These two qualities implicate most of the functional requirements shown in Tab. 3.3. To support users of the model checker, arbitrary assembly programs (F1) for certain microcontrollers (F2 and F3) are supported without the need to manually prepare them. Debug information in Dwarf [40] or Stabs [46] format is used to map information from assembly code to C code (F4). Specifications are given in CTL (F5), and it is possible to use atomic propositions about registers, I/O registers, and variables (F6). For every program under verification, the specifications is stored in a list (F7). To minimize the size of the state space and to evaluate abstraction techniques, the model checker implements different abstraction techniques (F8). The tool provides a GUI (F9). Within this GUI, users are able to choose between various abstraction techniques, model checking algorithms, and state compression techniques (F10). Counterexamples are presented in source code (assembly and C), as a state space graph, and in the CFG of the assembly code (F11). Within all these representations, users are able to step through the counterexample and to survey in each state the values of registers, I/O registers, variables, and formulas (F12).

Table 3.3: List of functional requirements.

| Number | Requirement                                                             |

|--------|-------------------------------------------------------------------------|

| F1     | The model checker accepts arbitrary microcontroller assembly code files |

|        | given in ELF file format as input.                                      |

| F2     | The model checker first supports the ATMEL ATmega16                     |

|        | microcontroller. Other microcontrollers, such as the ATMEL              |

|        | ATmega128 and Infineon XC167, are added later.                          |

| F3     | The model checker supports all constructs found in assembly code for    |

|        | the supported microcontrollers.                                         |

| F4     | The model checker handles debug information given in Dwarf or Stabs     |

|        | format to map information between assembly and C code.                  |

| F5     | The model checker accepts specifications given in CTL.                  |

| F6     | The model checker allows to use propositions about registers, I/O       |

|        | registers, and variables within the specification.                      |

| F7     | For every program under verification, users are able to store a list of |

|        | specifications.                                                         |

| F8     | The model checker implements different abstraction techniques (e.g.,    |

|        | dead variable reduction and path reduction).                            |

| F9     | The model checker provides a GUI.                                       |

| F10    | User are able to choose between different abstraction techniques, model |

|        | checking algorithms, and state compression techniques.                  |

| F11    | Counterexamples (witnesses) are presented in the source code (assembly  |

|        | and C), as a state space graph, and in the CFG of the assembly code.    |

| F12    | Users are able to step through the counterexample and to analyze the    |

|        | values of registers, I/O registers, variables, and formulas.            |

The requirements presented in this section are the basis for the development of our model checker. The next chapter describes the model checker [MC]SQUARE, which is the result of this development.

# 4 [mc]square

[MC]SQUARE stands for Model Checking MicroControllers. It is a discrete CTL model checker for microcontroller assembly code. We have developed [MC]SQUARE at the embedded software laboratory during the last four years. It is written in Java as one requirement is that the model checker is usable on any of the three major operating systems. Currently, we are using Java SE 6.

This chapter gives an overview of [MC]SQUARE<sup>1</sup>. Section 4.1 presents the features of [MC]SQUARE. The subsequent section details the architecture of [MC]SQUARE. In the end, we evaluate the chosen architecture in Sect. 4.3.

We published a preliminary version of this architecture in a paper [103].

#### 4.1 Features

[MC]SQUARE is a discrete CTL model checker for microcontroller assembly code. Following, a list of the main features of [MC]SQUARE.

- Supported microcontrollers

- ATMEL ATmega16

- ATMEL ATmega128

- Infineon XC167

- Inputs

- Assembly program given as an ELF file

- Specification given as a CTL formula

- Stepwise simulation of the program

- Model checking by means of three different algorithms

- Global

- Local

- Invariant

<sup>&</sup>lt;sup>1</sup>We use revision 2233 of [MC]SQUARE in this thesis unless otherwise quoted.

- Abstraction techniques to tackle the state-explosion problem

- Dead variable reduction

- Delayed nondeterminism

- Lazy interrupt evaluation

- Lazy stack evaluation

- Path reduction

- Minimization of memory requirements via

- Compression algorithms such as run-length encoding and ZIP compression

- Storage of states on hard disk

- Incremental storage of states

- Presentation of Counterexamples (witnesses) in

- Assembly code

- Control flow graph of the assembly code

- C code

- State space graph

At present, [MC]SQUARE handles assembly code of the following microcontrollers: ATMEL ATmega16, ATMEL ATmega128 and Infineon XC167. It handles programs given in Executable and Linking Format (ELF) [116] and the specifications given as CTL formulas. The specification may contain propositions about registers, I/O registers, and variables (including C variables). Additionally, [MC]SQUARE checks for stack overflows, stack underflows, and non-intended use of microcontroller features such as write access to reserved registers. Furthermore, users can use [MC]SQUARE to stepwise simulate the assembly program.

We have implemented three explicit model checking algorithms in [MC]SQUARE: a global CTL model checking algorithm presented by Clarke et al. [33], a local CTL algorithm first introduced by Vergauwen and Lewi [121] and later adapted by Heljanko [57], and an algorithm used to verify invariants. Section 7.1 describes details of the applied model checking algorithms.

During state space creation, [MC]SQUARE uses various abstraction techniques to lower the size of the state space. These abstraction techniques include, for example, dead variable reduction, path reduction, and delayed nondeterminism. Chapters 5–7 give detailed descriptions of the implemented abstraction techniques.

The users can choose the abstraction techniques that are applied during model checking. Thereby, they are able to adjust the granularity of the abstraction used and hence, influence the size of the resulting state space. Furthermore, they can

select other options to lower memory consumption such as different compression levels and storage of states on hard disk.

[MC]SQUARE presents counterexamples, which are created during model checking, in the assembly code, in the control flow graph of the assembly code, in the C code, and as a state space graph. Hence, users can pick the representation that suites their needs best. In each of these representations, they can analyze the values of registers, I/O registers, and variables and the truth values of the formulas.

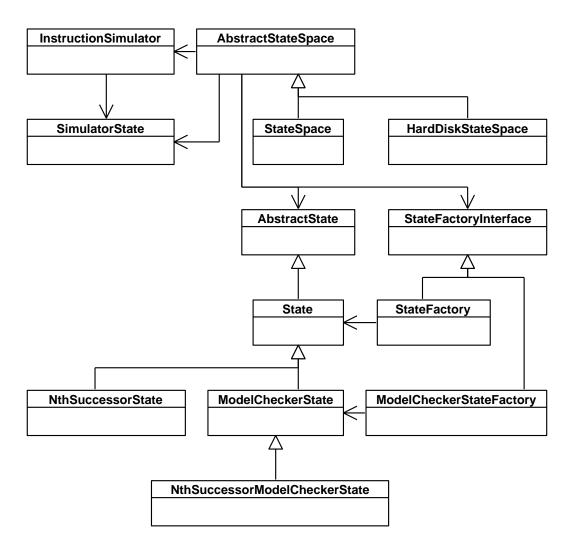

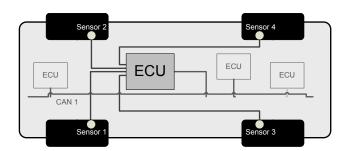

#### 4.2 Architecture

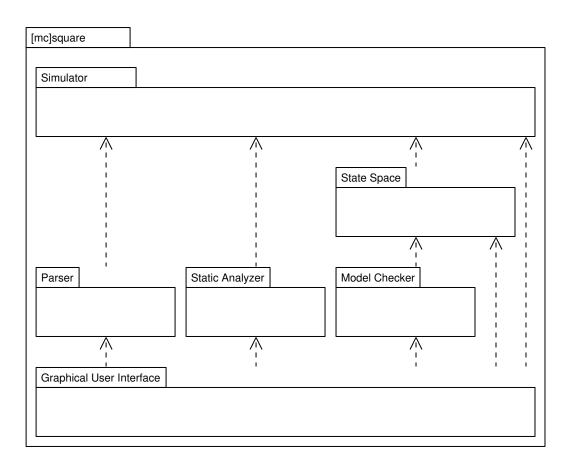

This section describes the current architecture of [MC]SQUARE, which was developed to reflect the requirements shown in Sect. 3.3. Figure 4.1 shows the layered architecture of [MC]SQUARE as a *UML package diagram* [12, 17, 61, 113, 119] consisting of the six basic packages: Parser, Static Analyzer, Model Checker, State Space, Simulator, and Graphical User Interface (GUI). For clarity, we left out support packages such as Util, Error, and Exception, which execute miscellaneous supporting functions such as array operations, compression algorithms, or hard disk operations. The relations between the packages shown in the figure are access relations. In the implementation, the packages shown in Fig. 4.1 are directly mapped to Java packages.

Every step of the model checking process is implemented in a separate package. Additionally, the *Simulator* and the *State Space* are separated into single packages. The communication between packages is conducted by means of well-defined interfaces. Therefore, single parts of the process can be exchanged independently. By separating the *Model Checker* and the *Simulator*, model checking is conducted independently from the underlying microcontroller.

In the following, a short description of each of the six packages is given. Chapters 5–7 detail the three important packages: Simulator, Static Analyzer, and Model Checker.

That is, it presents data to the user and gets input from the user. The user can, for example, load files, edit formulas, simulate programs, model check programs, and inspect counterexamples. The second purpose of the GUI is to control the different processes used in [MC]SQUARE. That is, it starts, for instance, static analysis, simulation, and model checking. The different processes are implemented as threads within the corresponding packages. The GUI uses the observer pattern [47] to collect the data that is presented to the user. Furthermore, we implemented the model-view-controller pattern to separate the data (model) from its representation (view).

Figure 4.1: The layered architecture of [MC]SQUARE.

**Parser** The Parser package provides capabilities to parse different file formats, such as ELF, and logics, such as CTL, and to transfer them into the corresponding internal representations used throughout [MC]SQUARE. It is, for example, used to process programs and formulas provided by the user.

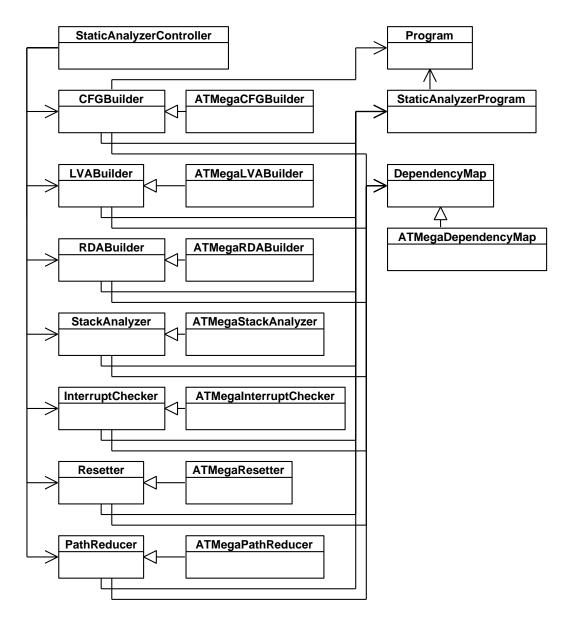

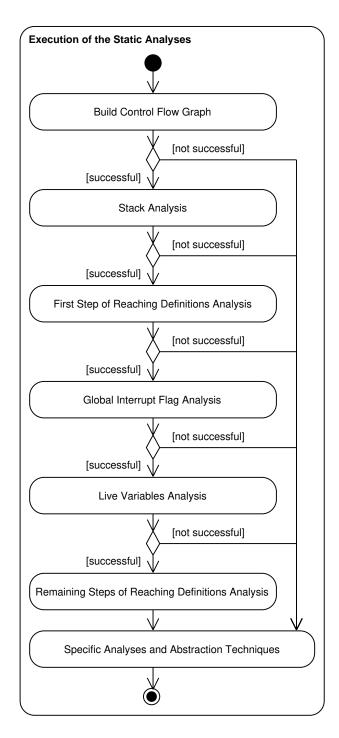

Static Analyzer The Static Analyzer conducts different static analyses and abstraction techniques and annotates the program. It is used before model checking. The Simulator uses the annotations to limit the size of the state space during creation. Furthermore, the Static Analyzer creates a control flow graph of the assembly code, which is, for instance, used to present the counterexample. Chapter 6 details the Static Analyzer.

State Space The State Space package is used to store the states. It uses the Simulator to create successor states on demand. The State Space contains different state space implementations. Some use the main memory, whereas others use the hard disk to store the states. The interface to access the State Space is independent from the method used to store the states. Hence, model checking is implemented independent from the method used to store the states. Chapter 7 describes details of the State Space.

Simulator The Simulator package serves different purposes. First, it is used by the State Space package to create successors of given states. When creating successor states, the Simulator natively handles nondeterminism and creates an over-approximation of the behavior exhibited by the corresponding microcontroller. This is important to preserve the validity of the formulas checked. Most of the abstraction techniques, which are used to limit the size of the state space, are implemented within the Simulator. The second purpose of the Simulator is to allow other packages to get information about the microcontroller and the program without the need to implement specifics of the different microcontrollers and programs. We implemented three different microcontrollers within the Simulator. Chapter 5 presents the internals of the Simulator.

Model Checker The Model Checker conducts the actual model checking. In this package, the different model checking algorithms are implemented. Currently, it includes a global and a local model checking algorithm and an algorithm to check invariants. Depending on the chosen algorithm, states are created before model checking or on-the-fly during model checking. The Model Checker does not manage the creation of states. It only requests states from the State Space, which creates states using the Simulator if required. Moreover, the Model Checker is responsible for the creation and processing of counterexamples. Chapter 7 details the Model Checker.

# 4.3 Evaluation

Extendability and maintainability are the requirements that notably influenced the architecture. These two requirements are achieved by the chosen division of packages. Each step of the model checking process, that is, parsing, static analysis, state space building, and model checking, is conducted within a single package. Communication between these packages is conducted by means of well-defined interfaces. Thereby, parts of these processes can be exchanged without the need to change the complete application. For example, model checking is conducted independently of the microcontroller used, and hence, adding new microcontrollers can be done without changing the model checking.

To show that [MC]SQUARE is extendable, we already extended it in several directions. The first version of [MC]SQUARE used a patched version of a simulator called AVRORA [117, 118] to build the state space. AVRORA is a cycle-accurate simulator for microcontroller assembly programs written for the ATMEL ATmega16, 32, and 128. We had to change AVRORA because it is cycle-accurate and does not natively support nondeterminism. Preserving cycle-accuracy would lead to real-time model checking [14, 71, 72], which suffers even more from the state-explosion problem.

Using the patched version of AVRORA, we found out that [MC]SQUARE spent 85% to 95% of the processing time building the state space. Therefore, we decided to concentrate on improving the creation of state spaces instead of the model checking. Changing AVRORA was rather involved because it was built for cycle-accurate simulation of microcontroller programs and not for the creation of state spaces for model checking. Many parts of AVRORA were automatically created and not written by hand and thus, these parts were not easy to understand and difficult to change.

Every time a new version of AVRORA was published, we had to apply the same changes. In the second version of [MC]SQUARE, we exchanged AVRORA by our own simulator, which adopted some parts of AVRORA, to avoid these changes and to ease the adaption of the state space creation. Our simulator natively handles nondeterminism and builds a safe over-approximation of the behavior shown by the microcontroller. The simulator is implemented within the *Simulator* package.

Later, we added an additional ATMEL ATmega microcontroller and the Infineon XC167 microcontroller to the Simulator package [100, 103]. In the Model Checker package, we added a local model checking algorithm and an algorithm used to check invariants [103]. The State Space package was extended to store states on hard disk [103, 106]. Furthermore, we added the capability to conduct different static analyses to [MC]SQUARE [107]. This was obtained by adding the Static Analyzer package and adapting the procedures using the static analyses. During these extensions, we adapted the architecture of [MC]SQUARE to better reflect the requirements of extendability and maintainability. This makes it easier to extend [MC]SQUARE in

the future.

However, extendability has its limits. At present, based on the classification given by Visser [123], all model checking algorithms implemented within [MC]SQUARE are explicit, graph-based, structural model checking algorithms. Changing to an automata-based algorithm or to symbolic model checking algorithms is more involved than just changing single parts of a procedure. Schommer [109] tried to extend [MC]SQUARE to support symbolic model checking. This try was very involved, but it was not successful in the end. We finally removed it from [MC]SQUARE. It failed because known abstractions, such as modulo and interval abstractions, did not work as expected, and no abstractions that solve this problem could be found within this work. It did not fail due to the architecture of [MC]SQUARE. Schommer [109] gives details in his thesis. Although we were not successful in adding symbolic model checking to [MC]SQUARE, we combined explicit and symbolic model checking techniques within [MC]SQUARE. Chapter 5 explains the details about the combination of explicit and symbolic techniques.

Our aim is to use [MC]SQUARE as a research platform and as a tool that can be applied in industry. Extendability is important because new model checking algorithms, new microcontrollers, and new abstraction techniques have to be added to [MC]SQUARE. As described above, [MC]SQUARE satisfies the requirement of extendability and maintainability. Additionally, the modular structure enables students to work on parts of [MC]SQUARE that they are specialized and interested in. For example, a student interested in static analysis does not have to bother with model checking. Beside extendability, usability is also important for our aim. The architecture supports usability by hiding all internals except for the CTL specifications from the user via the GUI.

# 5 State Space Building in [mc]square

It turned out that the main focus of this thesis is the domain-specific creation of state spaces for model checking microcontroller assembly code. This includes the application of domain-specific abstraction techniques. In [MC]SQUARE, the Simulator package builds the state space. It uses a similar process to build the state space as is used in typical simulators, which simulate the behavior of microcontroller programs. That is, it simulates the effect of instructions on the model of the microcontroller. Our Simulator differs in two important respects from other simulators. First, it natively supports nondeterminism and second, it creates an over-approximation of the real behavior of the microcontroller to preserve validity of the model checking results. We integrated abstraction techniques into the Simulator to limit the size of the state space already during creation.

Another purpose of the *Simulator* is to hide microcontroller peculiarities from the other packages of [MC]SQUARE. Thus, the other packages can access the microcontroller or the states of the microcontroller without considering the peculiarities of the respective microcontroller. Hence, the other packages of [MC]SQUARE are implemented hardware independently.

This chapter describes the modeling of the ATMEL ATmega16 microcontroller within the *Simulator*. The general structure and functionality of the *Simulator* is similar for all microcontrollers. Different microcontroller models only vary in hardware-dependent details such as memory, external devices, instructions, and interrupts.

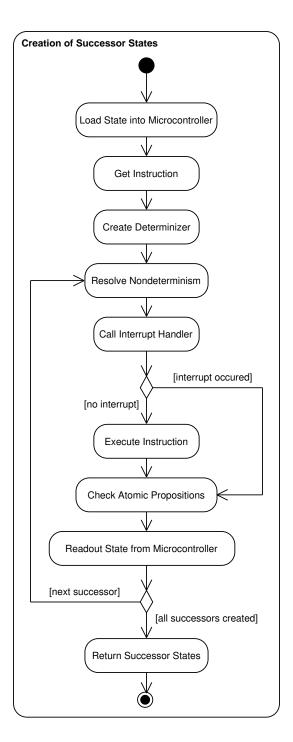

The first section gives an overview of the Simulator package. Section 5.2 describes the states that are used within the Simulator. The subsequent sections detail the four important parts of the Simulator package. First, the model of the microcontroller (Sect. 5.3) and the model of the program (Sect. 5.4) are described. These two are the representation of the real microcontroller and the real program within [MC]SQUARE. Then, the creation of successor states, which is done by the InstructionSimulator, is explained in detail in Sect. 5.5. Section 5.6 details the Determinizer, which handles nondeterminism within the Simulator. Section 5.7 describes the formal model of the Simulator. Then, this formal model is used to establish the correctness of the delayed nondeterminism abstraction technique. Section 5.8 presents related work regarding model checking of assembly code and delayed nondeterminism.

We published the general idea of using a simulator to build a state space in several papers [102, 103]. Furthermore, we outlined the ideas presented in Sect. 5.6

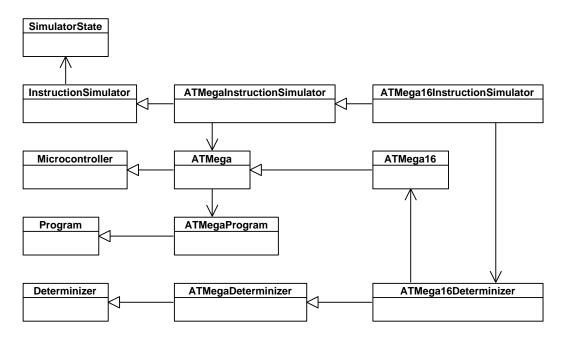

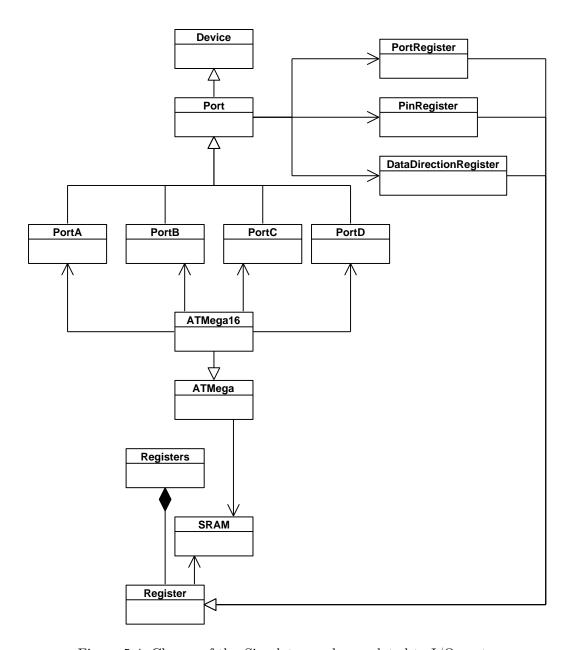

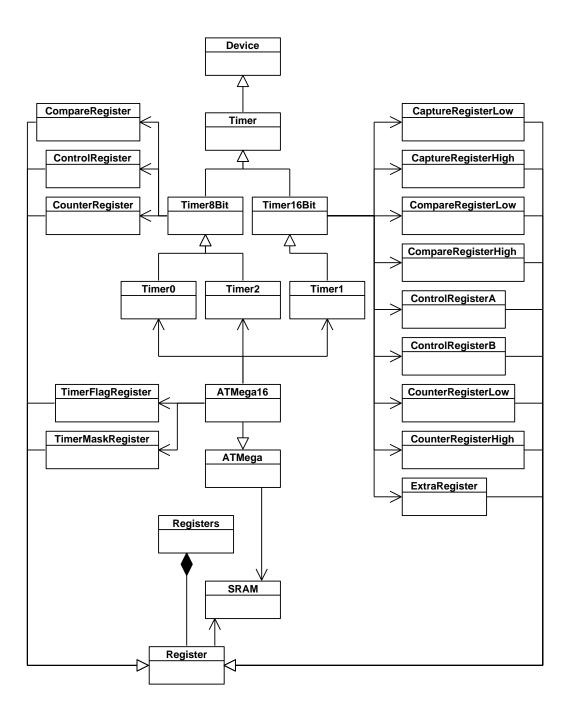

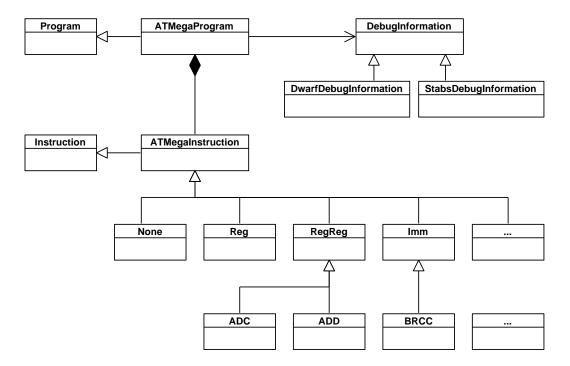

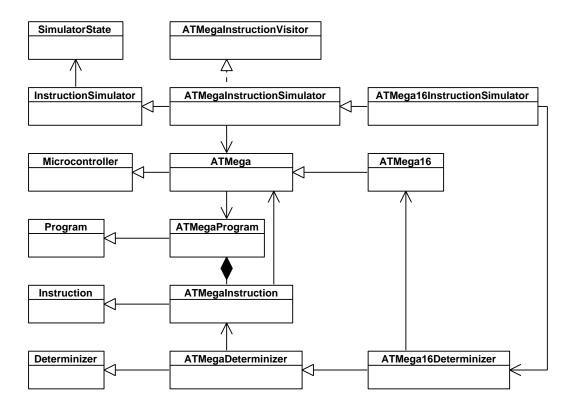

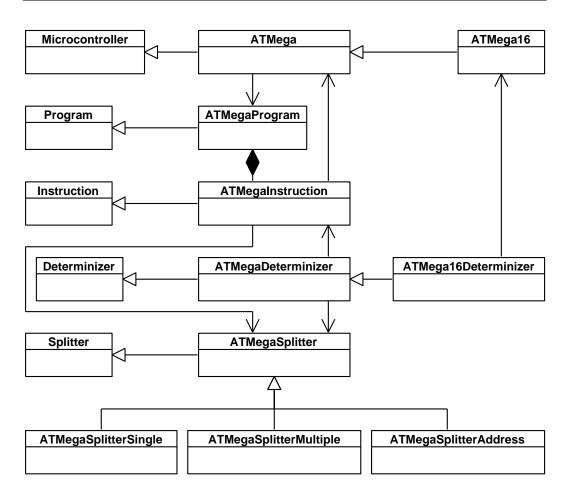

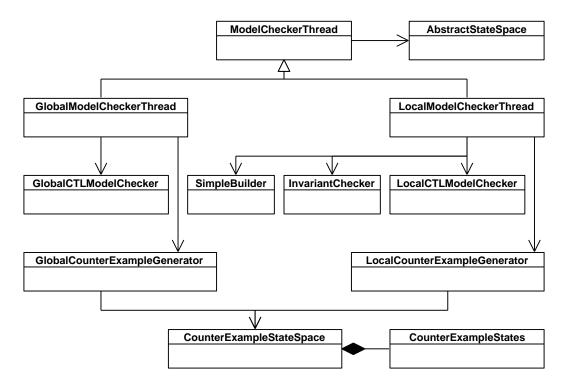

Figure 5.1: Classes of the Simulator package related to the ATMEL ATmega16 microcontroller.

in another paper [60] and published a summary of the formal model described in Sect. 5.7 elsewhere [60, 88].

# 5.1 Simulator Overview

The Simulator package generates states for model checking by simulating the effects of instruction executions on the model of the microcontroller. Additionally, the Simulator package provides facilities for the other packages to access the microcontroller model through well-defined interfaces. Thus, other packages do not have to deal with the peculiarities of the different microcontrollers.

Figure 5.1 gives an overview of the Simulator package. It is a UML class diagram [12, 17, 61, 113, 119] depicting the topmost classes of the Simulator package. Minor classes are omitted for clarity. On the left side of the figure, the superclasses are shown, and on the right side of the figure, the specialized subclasses are shown. We follow this guideline in all UML class diagrams shown in this chapter.

The *Microcontroller* class and its subclasses represent microcontrollers and their different features within [MC]SQUARE. In these classes, for instance, the memory, the registers, and the external devices are modeled. Section 5.3 provides details on the modeling of these different features. The program run on the microcontroller is

modeled within the *Program* class and its subclasses. Details are given in Sect. 5.4. The *InstructionSimulator* class and its subclasses control the generation of states. The semantics of the different instructions are modeled within these classes. They use the *Microcontroller* and *Determinizer* classes to execute the instructions and to simulate their effects on the microcontroller model. Classes outside the *Simulator* package use the *InstructionSimulator* class to create states and access the microcontroller. The *InstructionSimulator* uses states of type *SimulatorState* to pass the

The *Determinizer* class is used to handle and hence resolve the nondeterminism. The *Determinizer* and its subclasses are described in Sect. 5.6. The handling of nondeterminism is also detailed in conjunction with the formal model of our *Simulator* in Sect. 5.7.

created states to the other packages such as the State Space. Section 5.2 describes

the SimulatorState class, and Sect. 5.5 details the InstructionSimulator.

In this chapter, we are especially interested in all *ATMega16* classes as we focus on the modeling of the ATmega16, but we explain features modeled in the superclasses whenever they are not refined in the *ATMega16* classes. Some of the following sections refine the *Simulator UML* class diagram shown in Fig. 5.1.

# 5.2 Simulator State

The SimulatorState class, which represents the state of the simulator, is used by the InstructionSimulator to exchange states with other packages such as the State Space. It consists of three parts:

- the name of the state,

- the truth values of the atomic propositions used within the formula, and

- data representing the state of the microcontroller (microcontroller state).

The name of a state is determined by a hash function applied to the microcontroller state. If a hash collision occurs, it is resolved via a quadratic probing algorithm. As names map one-to-one to states, they are also used for states stored in the *State Space*.

The truth values of the atomic propositions are evaluated by the *InstructionSimulator*, which is located within the *Simulator* package, and stored in the *SimulatorState*. The *Model Checker* uses these pre-evaluated atomic propositions during model checking. Thus, it does not have to handle the peculiarities of the microcontroller.

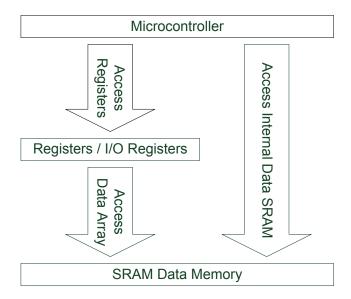

The microcontroller state comprises all details representing the state of the microcontroller. It contains the complete memory of the microcontroller including general-purpose registers, I/O registers, SRAM, flash memory, and EEPROM. Additionally, it stores fields that are not stored in the memory of the microcontroller

such as the program counter, sleep mode bits, and boot lock bits. Microcontroller states are stored as a byte array. As they are rather big, up to 2 kB in case of the ATmega16, and not all parts are necessarily used, they are compressed using techniques such as run-length encoding and ZIP compression. This considerably reduces the size of the microcontroller states.

A microcontroller state can contain nondeterministic values. Nondeterministic values are introduced by certain I/O registers or by specific abstraction techniques such as lazy stack evaluation (see Sect. 5.3.3) or delayed nondeterminism (see Sect. 5.6.3). Through nondeterministic values, the state does not only represent a single state but a set of states. The state representation thus contains both explicit and symbolic parts. The simulator only works on the explicit parts. Whenever the Simulator accesses a symbolic part, that is, a nondeterministic value, the nondeterminism of this value is resolved lazily. Therefore, we call such a state a lazy state. The resolution of nondeterminism is detailed in Sect. 5.6. Using this technique, we have combined explicit and symbolic techniques within [MC]SQUARE. To implement lazy states, the model of the microcontroller memory has to store nondeterministic values. Section 5.3.2 describes the modeling of the microcontroller memory and the way nondeterministic values are stored within it.

# 5.3 Microcontroller

We have modeled different microcontrollers within the *Simulator* package. This section presents the ATmega16 microcontroller model, which is the focus of this chapter. The technical information about the ATmega16, given in this section, is taken from the ATMEL documentation [3, 4].