Aalborg Universitet

# Modeling and analysis of complex dynamics for dSPACE controlled closed-loop DC-DC boost converter

Banerjee, Subrata; Ghosh, Arnab; Padmanaban, Sanjeevikumar

Published in: International Transactions on Electrical Energy Systems

DOI (link to publication from Publisher): 10.1002/etep.2813

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Banerjee, S., Ghosh, A., & Padmanaban, S. (2019). Modeling and analysis of complex dynamics for dSPACE controlled closed-loop DC-DC boost converter. *International Transactions on Electrical Energy Systems*, *29*(4), [e2813]. https://doi.org/10.1002/etep.2813

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Modeling and Analysis of Complex Dynamics for dSPACE Controlled Closed-loop DC-DC Boost Converter

Subrata Banerjee<sup>1</sup> | Arnab Ghosh<sup>2</sup> | Sanjeevikumar Padmanaban<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering, National Institute of Technology Durgapur, Durgapur, India <sup>2</sup>Department of Electrical Engineering, National Institute of Technology Rourkela, Rourkela, India <sup>3</sup>Department of Energy Technology, Aalborg University, Esbjerg, Denmark

Abstract—DC-DC switched mode power converter circuits are time varying and nonlinear in nature. This work analyzes the modeling and complex dynamics of voltage mode controlled of boost converter in continuous conduction mode (CCM) of operation by using continuous-time model. The switching converter is governed by naturally sampled constant frequency pulsed signals. Mathematical model of the boost converter numerically developed by using differential equations and tested in simulation software. The switching converter may exhibit fundamental, quasi-periodic & chaotic oscillations by systematic changing of converter's variables. The stability of the system investigated through the locus of the complex eigenvalues, and the characteristic multipliers locating the on-set of Hopf bifurcation. The 1-periodic orbit loses its stability via Hopf bifurcation, and the resulting attractor is a quasi-periodic orbit. A dSpace controlled boost converter prototype hardware fabricated to establish the experimental studies in this work. Both the numerical simulation and experimental results have been included to validate the set analysis. It is observed, shown that the route to chaos reached by the slow-scale instability in this proposed work.

*Index Terms*—State-space equations, discrete time iterative modeling, phase-plane trajectories, dSPACE, chaos.

## I. INTRODUCTION

The DC-DC switching converters are renowned for their domestic as well as industrial

applications from few hundred watts to several hundreds of kilowatt. Due the presence of, the switches, non-linear elements (like diode) and control strategies (e.g. pulse width modulation), the circuits behaves non-linear and time-varying dynamical systems. The converters may show complex phenomenon with the variation of circuit parameters and that may cause to unusual magnified noise, EMI problem and non-linear oscillation [1]. The exploration and analysis in complex dynamics of a system had made phenomenal progression in the late nineteen century. It is most striking that simple systems may behave 'random' like oscillation by changing their parameters and system dynamics may deny 'long-term predictability' even the initial conditions are known [2]. Such behavior well known as chaos, which may introduce the complexity in realworld systems. The mathematicians, engineers, and scientists from different disciplines have observed similar sort of complex phenomena in their systems. The study of non-linear dynamics of power converters are the popular ongoing research area from the last decades [1-10]. Investigation of complex dynamics in DC-DC switched mode Boost converter [11-17] carried out much attention for their versatile zone of applications. The designers have always tried to make the 'Chaos free' power supplies for sophisticated applications. Hence, the non-linear dynamics in switching converter is important for finding the zones of instability and useful for the design of practical power supplies.

The DC-DC switching converter is externally clock driven system, the frequency of the clock pulse is similar to the converter's switching frequency. Dynamics of the system is fully non-autonomous and non-linear in nature [18-20]. The non-linear dynamics of the converter system depends upon the different circuit parameters of the converter like as input voltage, inductance, capacitance, and the switching frequency etc. The periodicity and stability of the periodic orbit (limit cycle) has been changed due to the systematic variation of the converter parameters that causes sub-harmonic oscillations in the converter [20]. It is normal habit to mention the ranges of parameters where the switching converter will reliably operate in steady-state condition by avoiding any occurrence of sub-harmonic oscillations. The parameters of the converter chosen based on the desired specifications like required power and voltage rating, good transient and the steady-state response etc. DC-DC Boost converter has problem of non-minimum phase because of a right half plane (RHP) zero in converter's plant transfer function [21-22]. Therefore, the Type-controllers [23-26] are the most efficient to exhibit the good closed-loop response with parametric uncertainty, load and line variations. It is important to estimate and check the fast-

scale and slow-scale stability [8-0] from simulation and experimental results over a large parameter range because these will have an effect on sub-harmonic oscillation. Main reason for carrying out this work is to identify and explore the complex phenomena in power electronic converters. This investigation, aimed to the non-linear dynamics of power converters under certain operating conditions to make them suitable for practical applications.

Even though considerable amount of work already done by the prior researchers, the presented work has added additional contributions, which are indifferent from the recent works [27-30]. The most important aim of this paper is to study, analysis and explore the theoretical and practical chaos for Type-III controller controlled VMC boost converter circuit by using dSPACE based real time controller. The study of non-linear dynamics in Type-III controller based boost converter by using DSP based real time platform and first time reported in this work, the main novelty of paper. It is noticeable that the route to chaos reached by the slow-scale instability. This approach is conceptually simple to implement, and the designers can easily find out the probable operating zone. By identifying the zones of quasi-periodic and chaotic oscillation for accurate range of parametric values will assist to design a chaos free power supply.

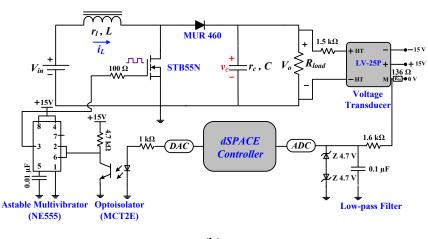

#### II. DC-DC BOOST CONVERTER

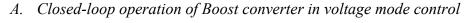

The schematic diagram of Voltage Mode Control (VMC) of Boost converter shown in Fig.1. The power circuit consists of a controlled switch *SW* (MOSFET), diode *D*, an inductor *L*, a capacitor *C*, and a load resistance  $R_L$ . The switching of the MOSFET controlled by the output of the comparator through a driver circuit. In this present work, the main objective is to study the non-linear dynamics of dSPACE controlled closed-loop converter.

Fig. 1. Schematic diagram of closed-loop operation of Boost converter in voltage mode control.

It can be viewed from the schematic diagram (Fig.1) that the converter's output voltage ( $V_o$ ) is sensed. Further, scaled load voltage is compared with reference voltage ( $V_{ref}$ ). The generated error signal is proceeding through analog to digital (ADC) converter to the digital controller (Type-III controller embedded in dSPACE platform) and a control signal is from the controller. Finally, the pulse wide modulating (PWM) signal created after making comparison between control signals with high frequency triangular waveform. PWM signal is passing through digital to analog (DAC) converter, opto-isolator and astable multi-vibrator circuits before driving the gate terminal of the MOSFET switch.

#### III. STATE -SPACE EQUATIONS OF DC-DC BOOST CONVERTER

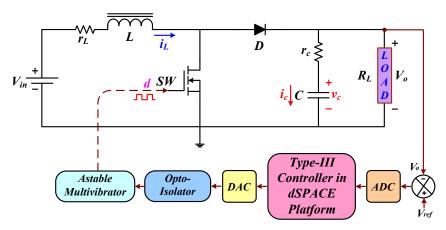

By the presence of non-linear elements (*like* MOSFET switch, diode) and controlling signal (*like* PWM) the converter circuits are time varying and non-linear dynamical systems [8]. The block diagram of the boost converter shown by the Fig.1. A free running clock is there to control the switching of the converter. The switch is turn-on at the beginning of each clock pulse & the clock frequency is similar to the switching frequency and operated under the continuous conduction mode (CCM). Therefore, exhibits two switching instants *i.e.* (a) switch on and (b) switch off condition. The differential equations of converter's states derived and elaborated below. The output capacitor voltage ( $v_c$ ) and the inductor current ( $i_L$ ) are considered as state variables of the converter dynamical system.

Fig. 2: (a) switch on and (b) switch off circuits of Boost converter.

## Mode 1: Switch (SW) is ON:

Applying Kirchhoff's current law (KCL)

$$i_c(t) = -\frac{V_o}{R_L} \tag{1}$$

$$or, \frac{dv_c(t)}{dt} = -\frac{1}{\left(R_L + r_c\right)C} v_c(t)$$

<sup>(2)</sup>

Applying Kirchhoff's voltage law (KVL)

$$V_{in} - L\frac{di_L(t)}{dt} - r_L \times i_L(t) = 0$$

(3)

$$or, \frac{di_L(t)}{dt} = -\frac{r_L}{L}i_L(t) + \frac{1}{L}V_{in}$$

(4)

Now, we can write both the state equations in matrix form

$$\frac{dX(t)}{dt} = A_1^o X(t) + B_1^o V_{in} \quad \text{for } nT_{sw} \le t < (n+d)T_{sw}$$

$$V_o(t) = C_1^o X(t)$$

(5)

where, X(t) is noted as state vector of this circuit *i.e.*  $X(t) = \begin{bmatrix} v_c(t) \\ i_L(t) \end{bmatrix}$  and  $A_1^o, B_1^o, C_1^o$  can be

written as

$$A_{\mathbf{l}}^{o} = \begin{bmatrix} -\frac{1}{\left(R_{L}+r_{c}\right)C} & 0\\ 0 & -\frac{r_{L}}{L} \end{bmatrix}, B_{\mathbf{l}}^{o} = \begin{bmatrix} 0\\ \frac{1}{L} \end{bmatrix}, C_{\mathbf{l}}^{o} = \begin{bmatrix} \frac{R_{L}}{R_{L}+r_{c}}\\ 0 \end{bmatrix}$$

# Mode 2: Switch (SW) is OFF

Applying Kirchhoff's current law (KCL)

$$i_L(t) = i_c(t) + \frac{V_o}{R_L} \tag{6}$$

$$or, \frac{dv_c(t)}{dt} = -\frac{1}{\left(R_L + r_c\right)C} v_c(t) + \frac{R_L}{\left(R_L + r_c\right)C} i_L(t)$$

$$\tag{7}$$

Applying Kirchhoff's voltage law (KVL)

$$V_{in} - L\frac{di_L(t)}{dt} - r_L \times i_L(t) - V_o = 0$$

(8)

$$or, \frac{di_L(t)}{dt} = -\frac{R_L}{\left(R_L + r_c\right)L} v_c(t) + \left\{-\frac{r_L}{L} - \frac{r_c R_L}{\left(R_L + r_c\right)L}\right\} i_L(t) + \frac{1}{L} V_{in}$$

$$\tag{9}$$

Now, we can write both the state equations in matrix form

$$\frac{dX(t)}{dt} = A_2^o X(t) + B_2^o V_{in} \text{ for } (n+d) T_{sw} \le t < (n+1) T_{sw}$$

$$V_o(t) = C_2^o X(t)$$

(10)

where  $A_l^o$ ,  $B_l^o$ ,  $C_l^o$  can be written as

$$A_{2}^{o} = \begin{bmatrix} -\frac{1}{(R_{L} + r_{c})C} & \frac{R_{L}}{(R_{L} + r_{c})C} \\ -\frac{R_{L}}{(R_{L} + r_{c})L} & -\frac{r_{L}}{L} - \frac{r_{c}R_{L}}{(R_{L} + r_{c})L} \end{bmatrix}, B_{2}^{o} = \begin{bmatrix} 0 \\ \frac{1}{L} \end{bmatrix}, C_{2}^{o} = \begin{bmatrix} \frac{R_{L}}{R_{L} + r_{c}} \\ \frac{r_{c}R_{L}}{R_{L} + r_{c}} \end{bmatrix}$$

The Eqn.5 and Eqn.10 combined in only one expression by neglecting parasitic elements.

$$\frac{dX(t)}{dt} = f(X,t) \equiv \begin{pmatrix} -1/(R_L C) & (1-d)/C \\ -(1-d)/L & 0 \end{pmatrix} X(t) + \begin{pmatrix} 0 \\ V_{in}/L \end{pmatrix} \hat{1}_{SW}(t)$$

(11)

where,

$$\hat{1}_{SW}(t) = \begin{cases} 1 & \text{if } t \in SW \\ 0 & \text{if } t \notin SW \end{cases}$$

(12)

#### A. Discrete Time Iterative Mapping for Non-linear Modelling of the Converter

In the first step of the discrete time iterative mapping, the state-equations of individual switching instants written down and finally the difference equation for the overall system derived. The converter is operating here in CCM and two switched circuits can be identified, one corresponding to the 'switch on' interval  $(t_n \ t < t'_n)$  and the other to the 'switch off' interval  $(t'_n \ t < t_{n+1})$ . The details derivations of the state equations described in the previous section. For the sake of simplicity, the parasitic elements such as  $r_L \ t < r_c$  are not considered here.

In this case, the sparseness of the matrix  $A_l^o$  can be derived from the solution of the switch on interval easily by taking integration to the right hand side of Eqn.5, *i.e.*,

$$X(t) = \underbrace{\underbrace{\underbrace{e}}_{e}^{e} c}_{e} \frac{(t-t_n)}{CR_L} \underbrace{\underbrace{v}}_{U}_{U} \quad \text{for } t_n < t < t'_n \quad \text{for } t_n < t'_n \quad \text{for } t_n$$

for \\ t\_n \in t'\_n \quad \text{for } t\_n < t'\_n \quad \text{for } t\_n < t'\_n \quad \text{for } t\_n for \\ t\_n \in t'\_n \quad \text{for } t\_n < t'\_n \quad \text{for } t\_n < t'\_n \quad \text{for } t\_n \quad \text{for } t\_n \in t'\_n \quad \text{for } t\_n \quad \text{for } t\_n \quad \text{for } t\_n \quad \text{for } t\_n

Now, putting  $t = t'_n$  to Eqn. 13 and the value of X obtained at the end of the switch-on interval.

$$v_c(t_n) = v_c(t_n)e^{-\frac{dT_{sw}}{CR_L}}$$

(14)

$$i_L(t_n) = i_L(t_n) + \frac{V_{in}dT_{sw}}{L}$$

(15)

where,  $d = t'_n / T_{SW}$  is known as duty cycle.

By applying Laplace Transformation on Eqn.10 in *s*-domain to get the solution for the switch off interval. Note that the Laplace transform of the input voltage is  $V_{in}/s$ .

$$X(s) = \oint I - A_2^{o} \bigvee_{H}^{o} \stackrel{1}{\underbrace{\in}} X(t_n) + B_2^{o} V_{in}(s) \bigvee_{H}^{\circ}$$

$$= \frac{\oint S}{\frac{1}{L}} - \frac{1}{C} - \bigvee_{H}^{\circ} \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} + \frac{1}{CR_L} \bigvee_{L}^{\circ} \frac{1}{C} + \frac{V_{in}}{sL} \bigvee_{H}^{\circ}$$

$$= \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} + \frac{V_{in}}{sL} \bigvee_{H}^{\circ}$$

$$= \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} + \frac{V_{in}}{SL} \bigvee_{H}^{\circ}$$

$$= \frac{1}{C} - \bigvee_{L}^{\circ} \frac{1}{C} + \frac{1}{CR_L} + \frac{1}{LC}$$

(16)

Here, X(s) represents the Laplace transform of X(t). Now, it may be written from the Eqn.16 that the mathematical expressions for the output capacitor voltage and the inductor current in *s*-domain as

$$V_{c}(s) = \frac{V_{in}}{s} + \frac{K_{1}s + K_{2}}{H(s)}$$

(17)

$$I_{L}(s) = \frac{V_{in}}{R_{L}s} + \frac{K_{3}s + K_{4}}{H(s)}$$

(18)

where,

$$K_1 = v_c \left( \dot{t_n} \right) - V_{in}, K_2 = \frac{1}{C} i_L \left( \dot{t_n} \right) - 2sV_{in}, K_3 = i_L \left( \dot{t_n} \right) - \frac{V_{in}}{R_L}, H(s) = s^2 + \frac{s}{CR_L} + \frac{1}{LC},$$

$$K_4 = \frac{1}{CR_L} i_L \left( \dot{t_n} \right) - \frac{1}{L} v_c \left( \dot{t_n} \right) + \overleftarrow{\mathbf{e}}_L^{\mathbf{R}_L} - 2s \overleftarrow{\mathbf{e}}_{R_L}^{\mathbf{O}}, s = \frac{1}{2CR_L}$$

Now, the inverse Laplace transformation is used for the partial fraction expressions of  $V_c(s)$ and  $I_L(s)$ , the time-domain equations of  $v_c$  and  $i_L$  for the interval  $t'_n < t < t_{n+1}$  can be expressed as

$$v_{c}(t) = V_{in} + K_{1}e^{-s(t-t_{n}')}\cos w(t-t_{n}') + \frac{K_{2}-K_{1}s}{w}e^{-s(t-t_{n}')}\sin w(t-t_{n}')$$

(19)

$$i_{L}(t) = \frac{V_{in}}{R_{L}} + K_{3}e^{-s(t-t_{n}')}\cos w(t-t_{n}') + \frac{K_{4}-K_{3}s}{w}e^{-s(t-t_{n}')}\sin w(t-t_{n}')$$

(20)

where,  $w = \sqrt{\frac{1}{LC} - s^2}$ .

Since  $K_1$ ,  $K_2$ ,  $K_3$ , and  $K_4$  are the term of  $X(t'_n)$  and that  $X(t'_n)$  is also the function of  $X(t_n)$ . The *d*, difference equation is involving with  $X(t_{n+1})$ ,  $X(t_n)$  and *d* found after putting  $t = t_{n+1}$  and  $t_{n+1} - t'_n = (1 - d)T_{sw}$  into Eqn.19 & Eqn.20. The general form of discrete-time iterative mapping of the converter expressed as below:

$$X(t_{n+1}) = f(X(t_n), d)$$

<sup>(21)</sup>

where, the term f(.) is written as

$$f(X,d) = \oint_{\mathcal{F}_{21}}^{\mathcal{F}_{11}} \frac{f_{12} \dot{\mathcal{U}}}{f_{22} \dot{\mathcal{U}}} + \oint_{\mathcal{F}_{22}}^{\mathcal{F}_{11}} \dot{\mathcal{U}}_{in}$$

(22)

where,

$$f_{11} = e^{-\frac{dT_{sw}}{CR_L}} \cdot s(1-d)T_{sw} \stackrel{e}{\Leftrightarrow} \cos(1-d)wT_{sw} - \frac{s}{w}\sin(1-d)wT_{sw} \stackrel{u}{\forall}$$

$$f_{12} = \frac{1}{wC}e^{-s(1-d)T_{sw}}\sin(1-d)wT_{sw}$$

$$f_{21} = -\frac{1}{wL}e^{-\frac{dT_{sw}}{CR_L}} \cdot s(1-d)T_{sw}}\sin(1-d)wT_{sw}$$

$$f_{22} = e^{-s(1-d)T_{sw}} \stackrel{e}{\Leftrightarrow} \cos(1-d)wT_{sw} + \frac{1}{w}\stackrel{e}{\otimes} \frac{1}{CR_L} - s\stackrel{o}{=} \frac{1}{sin}(1-d)wT_{sw} \stackrel{u}{\forall}$$

$$g_1 = e^{-s(1-d)T_{sw}} \stackrel{e}{\Leftrightarrow} \cos(1-d)wT_{sw} - \frac{1}{w}\stackrel{e}{\otimes} \frac{2dT_{sw}}{LC} - s\stackrel{o}{=} \frac{1}{sin}(1-d)wT_{sw} \stackrel{u}{\forall}$$

$$g_2 = \frac{1}{R_L} \frac{1}{1+e^{-s(1-d)T_{sw}}}\stackrel{e}{\otimes} \frac{2R_LdT_{sw}}{L} - 1\stackrel{o}{=} \frac{1}{sos}(1-d)wT_{sw} \stackrel{u}{\forall}$$

#### IV. TYPE-III CONTROLLER DYNAMICS

Generally, many different classical controllers like PI, PID, lead-lag etc., used to achieve preferred closed-loop response of the converter [21]. In case of CCM of operation of the boost converter a Right Half Plane (RHP), the zero is observed in control-to-output transfer function of converter plant. Hence, the converter shows the poor dynamic response for the occurrence of non-minimum phase problem [22]. This RHP zero restricts the closed-loop bandwidth of the switching converter and that may reason for slower response [23]. It is challenging for PID controller to show fast closed-loop response with parametric uncertainty, load and line changes [24]. Whereas, the Type controllers [21-26] reported to show better dynamic response for this class of switching converter.

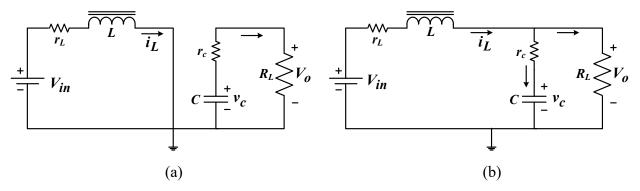

Fig. 3. (a) Basic structure, and (b) Bode diagram of Type-III controller.

"Type-III" controller is a lead-lead controller with a pole at origin. The origin pole is responsible for providing extremely high gain at low frequencies. The other pole-zero pairs may decrease the phase shift between the frequency of the two zeros and the frequency of two poles as lead controller [25]. That is why this controller delivers the phase boost of 0° to 180° with zero steady-state error. However, converter as a problem of non-minimum but this controller may provide better closed-loop dynamics. The basic structure of a Type-III controller is given in Fig.3(a). It can be noticed from frequency domain diagram (Fig.3(b)) that changing the locations of controller's pole-zero combinations maximum 180° phase boost can be achieved. The Type-

III controller plant transfer function can be written from the controller's basic structure of Fig.3(a).

$$T_{c_{T-III}}(s) = \frac{\left(1 + s/\omega_{z1_{T-III}}\right)\left(1 + s/\omega_{z2_{T-III}}\right)}{\left(s/\omega_{p0_{T-III}}\right)\left(1 + s/\omega_{p1_{T-III}}\right)\left(1 + s/\omega_{p2_{T-III}}\right)}$$

(23)

It is notable, one pole  $(f_{p0\_III})$  at origin and the other two poles are at  $f_{p1\_T-III} = 1/2\pi R_3 C_3$  and  $f_{p2\_T-III} = (C_1 + C_2)/2\pi R_3 C_3$  respectively. The zeros are presented at  $f_{z1\_T-III} = 1/2\pi R_2 C_1$  and  $f_{z2\_T-III} = 1/2\pi (R_1 + R_3)C_3$ . The two controller gains are (i)  $K_{1\_T-III} = R_2/R_1$  and (ii)  $K_{2\_T-III} = R_2(R_1 + R_3)/R_1R_3$ . Now, the two zeros are assumed at same point and likely the two poles are considered same point. Thus, the double pole and double zero are placed at  $\omega_{z1\_T-III} = \omega_{z2\_T-III} = \omega_{z1,2\_T-III}$  and  $\omega_{p1\_T-III} = \omega_{p2\_T-III} = \omega_{p1,2\_T-III}$ .

$$T_{c_{T-III}}(s) = \frac{\left(1 + s/\omega_{z1,2_{T-III}}\right)^{2}}{\left(s/\omega_{p0_{T-III}}\right)\left(1 + s/\omega_{p1,2_{T-III}}\right)^{2}}$$

(24)

The transfer-function for the designed classical Type-III controller of boost DC-DC converter

given by the function as

$$\frac{3.003 \times 10^6 (s + 605)^2}{s (s^2 + 1.31 \times 10^5 s + 4.26 \times 10^9)}.$$

## V. RESULTS AND DISCUSSION

The non-linear phenomena in DC-DC boost converter, investigated by the simulation and experimental test in this section. The non-linear dynamics examined by time domain waveforms and phase portraits. Due to the fact that these are popular laboratory techniques to study the theoretical and practical chaos.

#### A. Numerical Simulation Results

The VMC Boost converter numerical developed in MATLAB/SIMULINK platform. The simulations test carried out cycle-by-cycle by solving the differential equations of switching states. The circuit parameters of converter given in Table I. To study and analysis the non-linear phenomena of the converter, the basic circuit parameters *i.e.* bifurcation parameters (*like* load resistance, input voltage etc.) of the converter has been varied by keeping other parameters fixed and observed the converter's dynamics in phase plane. In this study, the load resistance ( $R_L$ ) considered as a primary bifurcation parameter.  $R_L$  varied from a certain range keeping the other

| TABLE I: LIST OF CIRCUIT PARAMETERS |        |  |

|-------------------------------------|--------|--|

| <b>Circuit Components</b>           | Values |  |

| Input Voltage V <sub>in</sub>       | 5 V    |  |

| Output Voltage Vo                   | 12 V   |  |

| Inductance L                        | 20 mH  |  |

| Output Capacitance C                | 220 µF |  |

| Load Resistance $R_L$               | 25 Ω   |  |

| Switching Frequency $f_{sw}$        | 25 kHz |  |

parameters fixed and observed the different periodicities of the limit cycles in phase plane.

(b)

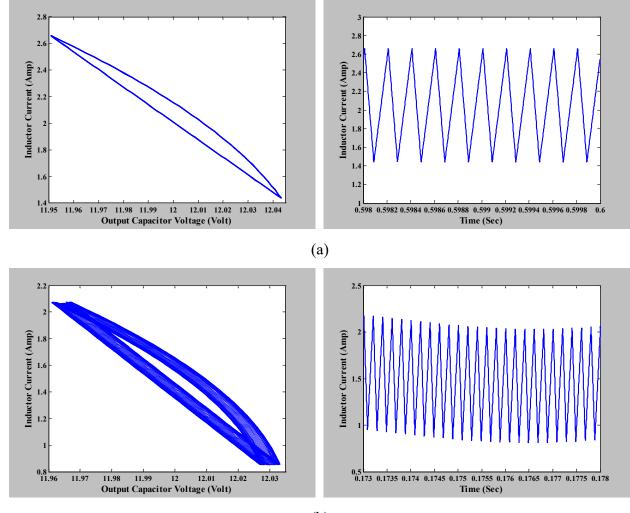

Fig. 4. Complex dynamics of DC-DC boost converter in voltage mode control: (a) Period-I orbit at  $R_L = 25.2 \Omega$  & respective time-domain waveform of inductor current,

(b) Quasi-period orbit at  $R_L = 35.5 \Omega$  & respective time-domain waveform of inductor current,

(c) Chaotic operation at  $R_L = 50.8 \Omega$  & respective time-domain waveform of inductor current,

(d) Period-I orbit in discontinuous conduction mode at  $R_L = 55 \Omega$ , & respective time-domain waveform of inductor current in Period-I operation,

(e) Chaotic operation in discontinuous mode at  $R_L = 70 \ \Omega$  & respective time-domain waveform of inductor current in Chaotic operation.

In condition, when load resistance ( $R_L$ ) equals to 25.2  $\Omega$  the converter works in stable (Period-I) operation. To see the converter dynamics clearly, the sampled values of state variables like inductor current ( $i_L$ ) and output capacitor voltage ( $v_c$ ) fetched at the starting of each switching cycle in steady-state. The phase portrait and time-domain waveform of inductor current of fundamental periodicity (Period-I) are illustrated in Fig. 4(a). The two state variables likes  $v_c$  and  $i_L$  have taken the axis of the phase portrait. It has been observed from the phase portrait that the periodicity of the limit cycle is one in phase plane and this kind of dynamics technically known as fundamental periodic operation i.e. Period-I operation.

In condition, where  $R_L$  is gradually increased to 35.5  $\Omega$ , the converter lose the stable operation, and leads to slow scale instability as given by Fig. 4(b. The quasi-periodic orbit observed in this situation, the trajectory moves on the surface of a torus. The motion is associated with a finite number of frequencies, related to one another by irrational ratios and the motion appears 'almost periodic' but is not exactly periodic. This kind of instability manifests itself as Hopf bifurcation, whereby a stable fixed-point change to a limit cycle as a certain parameter (e.g. load resistance) is changed. As the bifurcation parameter remains to change, the system admits another periodicity not in a rational ratio to that of the first limit cycle, and the resulting system dynamics is quasi-periodic by nature. This slow-scale instability causes low frequency oscillation in practical power supply. It is important to note that the chaotic dynamics observed at  $R_L$  equals to 50.8  $\Omega$  (Fig.4(c)). At  $R_L = 50.8 \Omega$ , the periodicities of the phase portrait (limit cycle) turned into infinite (practically periodicity is more than ten), so that the chaotic dynamics observed in phase portrait. The chaotic orbits of the converter are attained a bounded aperiodic oscillation within a definite zone in the phase-plane (i.e. phase portrait). In chaotic dynamics, the same state never repeats, in every loop of phase-plane the state traverses through a new trajectory and the resultant attractor known as strange attractor [10] and the periodicity of the chaotic limit cycle is infinite.

The converter dynamics observed here almost on the verge of discontinuous conduction mode (DCM) i.e. the lower threshold of the inductor current is almost zero.

In the condition,  $R_L$  is increased further to 55  $\Omega$ , the converter enters into DCM of operation. The phase portrait, respective time domain waveform shown by Fig. 4(d). Similarly, the chaotic operation in DCM observed at  $R_L$  equals to 70  $\Omega$  (Fig. 4(e)). These slow-scale instabilities and chaotic behavior may deteriorate the dynamic performance of the closed-loop converter. It can concluded that, the fundamental periodic operation of the converter dynamics is preferred as operating zone for designing practical power supplies.

#### B. Bifurcation Diagrams and Discussion

Bifurcation is a mathematical study and the system dynamics is observed by qualitative variation of system parameters. A small smooth change made to the values of bifurcation parameters (i.e. load resistance, inductance, output capacitance *etc.*) that may cause qualitative changes (bifurcation) of the system. The converter driven by external clock pulse so the system works like a non-autonomous system and the clock frequency dictates the switching frequency. Noted, the time-period of clock pulse must be lesser than the load time constant  $R_LC$  and the state variables sampled here at the clock frequency. Numerical simulation of current mode boost converter circuit carried out by using FORTRAN programming (Microsoft developer studio Fortran PowerStation 4.0) and bifurcation diagrams plotted by using Origin software (Fig.5).

#### 1. Characteristic Multipliers

In ordinary differential equations, a characteristic multiplier is an eigenvalue of a mono-dromy matrix and the logarithm of a characteristic multiplier as characteristic exponent. They appear in Floquet theory of periodic differential operators and in the Frobenius method. The characteristic multipliers of an iterative function f(.) are the roots,  $\lambda$ , of the characteristic equation:

$$\det\left(\lambda I - J_F\left(X_Q\right)\right) = 0 \tag{25}$$

where,  $J_F(X_Q)$  is the Jacobian matrix of f(.) calculated at the fixed point  $X_Q$  and I is the identity matrix. In case Boost converter, the function f(.) can be written in the following form:

$$X_{n+1} = f\left(X_n, \kappa\right) = \begin{bmatrix} f_1\left(v_{c,n}, i_{L,n}, \kappa\right) \\ f_2\left(v_{c,n}, i_{L,n}, \kappa\right) \end{bmatrix}$$

(26)

From Eqn.22, the expression written as:

$$f_1(.) = \alpha_{11}(d_n)v_{c,n} + \alpha_{12}(d_n)i_{L,n} + \beta_1(d_n)V_{in}$$

<sup>(27)</sup>

$$f_2(.) = \alpha_{21}(d_n)v_{c,n} + \alpha_{22}(d_n)i_{L,n} + \beta_2(d_n)V_{in}$$

(28)

where,  $d_n$  is a function of bifurcation parameter ( $\kappa$ ).

Now, the Jacobian matrix  $J_F(X_Q)$  is

$$J_F(X_Q) = \begin{bmatrix} \frac{\partial f_1(.)}{\partial v_{c,n}} & \frac{\partial f_1(.)}{\partial i_{L,n}} \\ \frac{\partial f_2(.)}{\partial v_{c,n}} & \frac{\partial f_2(.)}{\partial i_{L,n}} \end{bmatrix}_{X_n = X_Q}$$

(29)

where,

$$\begin{cases} \frac{\partial f_{1}(.)}{\partial v_{c,n}} = f_{11}(d_{n}) + v_{c,n}f_{11}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} + i_{L,n}f_{21}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} + V_{in}\beta_{1}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} \\ \frac{\partial f_{1}(.)}{\partial i_{L,n}} = v_{c,n}f_{11}^{'}(d_{n})\frac{dd_{n}}{di_{L,n}} + f_{12}(d_{n}) + i_{L,n}f_{12}^{'}(d_{n})\frac{dd_{n}}{di_{L,n}} + V_{in}\beta_{1}^{'}(d_{n})\frac{dd_{n}}{di_{L,n}} \\ \frac{\partial f_{2}(.)}{\partial v_{c,n}} = f_{21}(d_{n}) + v_{c,n}f_{21}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} + i_{L,n}f_{22}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} + V_{in}\beta_{2}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} \\ \frac{\partial f_{2}(.)}{\partial i_{L,n}} = v_{c,n}f_{21}^{'}(d_{n})\frac{dd_{n}}{di_{L,n}} + f_{22}(d_{n}) + i_{L,n}f_{22}^{'}(d_{n})\frac{dd_{n}}{di_{L,n}} + V_{in}\beta_{2}^{'}(d_{n})\frac{dd_{n}}{dv_{c,n}} \end{cases}$$

Now, the characteristic multipliers calculated at the fixed point for any bifurcation parameter (by keeping other parameter fixed) by the above-described equations.

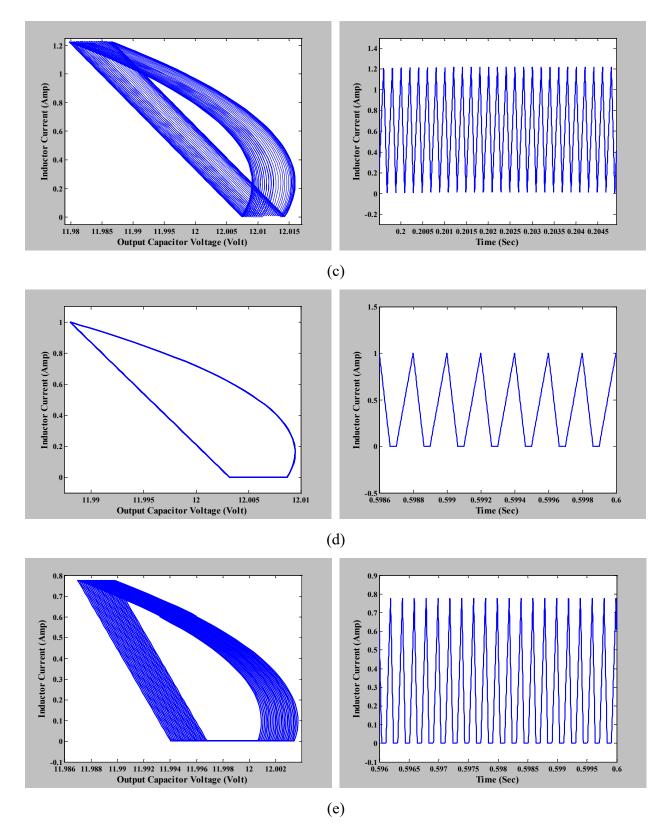

Fig. 5 Bifurcation diagrams of VMC Boost converter for (a) load resistance, (b) inductance, (c) output capacitance, and (d) Type-III controller gain.

#### I. Load Resistance as Bifurcation Parameter

Fig.5(a) shows the bifurcation diagram for taking load resistance as a bifurcation parameter in VMC of boost converter. In the diagram, change of load resistance considered in X-axis and inductor current sampled at clock frequency (stroboscopic sampling) taken in Y-axis. The load resistance is varied from 1  $\Omega$  to 50  $\Omega$  with a step of 0.1  $\Omega$  while other parameters are kept fixed.

**Stable Period-I operation:** The values of the characteristic multipliers are less than unity for  $R_L < 25.2 \Omega$ . So, stable fundamental periodicity or Period-I orbit is observed at 25.2  $\Omega$ .

**Stable Period-II operation:** The iterative function f(.) is unstable for  $R_L > 25.3 \Omega$ . But the function f(f(.)) may be considered stable. So, the period has been doubled. Here, the fixed point of f(f(.)) actually contains of two alternate fixed points of f(.), and exhibits up to  $R_L \approx 25.7 \Omega$ .

**Hopf bifurcation:** When  $R_L \approx 25.8 \Omega$  the iterative function f(f(.)) is become unstable and the stable iterative function is f(f(f(.))). This type of bifurcation characterized by a sudden expansion of a stable fixed point to a stable limit cycle [10]. Systems that exhibit this bifurcation normalized to second-order equation, where the system has a stable fixed point, which is associated with a pair of complex eigen values which having negative real parts. By varying the parameter, the real parts become positive and the complex eigen values move across the imaginary axis. Thus, the fixed point loses stability and the system has followed a stable limit cycle.

Routes to chaos via Hopf bifurcation: By gradually increasing the value of  $R_L$ , the system enters in chaotic region *i.e.* Period-infinity and chaotic behavior is observed in the entire

remaining zone. One can be noted that the system is undergone Period-I to Period-infinity through Hopf bifurcation.

### **II. Inductance as Bifurcation Parameter**

The bifurcation diagram with inductance as parameter is shown in Fig.5(b). The inductance (L) is varied from 1 mH to 200 mH with step of 0.1 mH by keeping other parameters fixed. The system dynamics started with Period-I, the behavior is observed from 1 mH to 19.74 mH and Period-II started at 19.75 mH from two distinguished zones. The Period-II, behavior last up to 29.24 mH bifurcates to Period-IV at 29.25 mH, than enters into chaos at 31.5 mH. This chaotic zone observed up to 49 mH and after that, the Period-III behavior sustains up to 58 mH. Then Period-III has bifurcated to Period-VI, and finally entered to chaotic zone at 71.25 mH and continues up to 200 mH.

## **III.** Output Capacitance as Bifurcation Parameter

The capacitance varied for 1  $\mu$ F to 500  $\mu$ F with a step of 0.1  $\mu$ F by keeping the other parameter fixed (Fig.5(c)). Initially Period-I dynamics observed and Period-I bifurcated to Period-II at output capacitance (*C*) equals to 28  $\mu$ F sustains up to the 152  $\mu$ F and bifurcates to Period-IV. Period-III observed at 188  $\mu$ F after the Period-IV and this Period-III bifurcated to Period-VI at 416  $\mu$ F and entered to chaos at 469  $\mu$ F.

## **IV. Type-III Controller Gain as Bifurcation Parameter**

In the control circuit of CMC boost converter, a Type-III controller implemented after the differential amplifier. The purpose of this controller is to control the height of the control voltage and maintain to comparable condition with inductor current. The main objective of this section is to study the non-linear dynamics by varying the Type-III controller gain by keeping other converter parameter fixed.

From the Fig. 5(d), observed that converter dynamics changed from fundamental periodicity to chaotic periodicities through Hopf bifurcation by gradually increasing the gain values of the Type-III controller. Here controller gain varied from  $0.1 \times 10^7$  to  $2.6 \times 10^7$  with a step of  $0.001 \times 10^7$  by keeping other converter parameters fixed. Initially, the converter dynamics is started with Period-I operation and this Period-I behavior is observed up to  $0.35 \times 10^7$ . After the slow-scale,

instabilities noticed and these Periodicities are bifurcated by gradually increasing the controller gain. Finally, the converter dynamics has shown chaotic dynamics at =  $0.6 \times 10^7$ .

| Sl. No. | Controller Gain     | Characteristics Multipliers (Eigen Values) | Remarks  |

|---------|---------------------|--------------------------------------------|----------|

| 1.      | $0.1 \times 10^{7}$ | -0.0137, -0.0159±j0.2318                   | Stable   |

| 2.      | 0.6×10 <sup>7</sup> | -0.0199, -0.0097±j0.2313                   | Stable   |

| 3.      | $1.1 \times 10^{7}$ | -0.0221, -0.0054±j0.2310                   | Stable   |

| 4.      | $1.6 \times 10^{7}$ | -0.0233, -0.0020±j0.2306                   | Stable   |

| 5.      | $2.1 \times 10^{7}$ | -0.0240, 0.0008±j0.2303                    | Unstable |

| 6.      | $2.6 \times 10^{7}$ | -0.0246, 0.0034±j0.2301                    | Unstable |

TABLE II: THE NATURE OF CHARACTERISTIC MULTIPLIERS

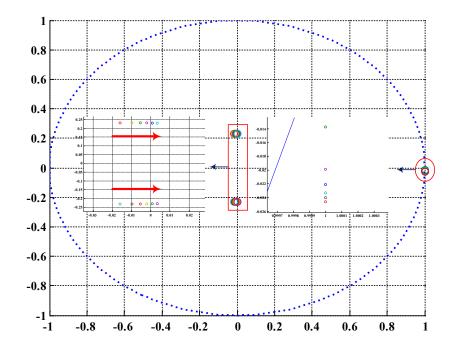

Fig. 6. Locus of the complex eigenvalue pair for different gains of Type-III controller.

Fig. 6, the stability of the system studied by deriving the eigenvalues of the system at the equilibrium point. The system has one negative real eigenvalue and a pair of complex poles. The real part of the complex pole may be either positive or negative real, depending upon the values of Type-III controller's gain. Table II shows the variation of the eigenvalues for various values of controller gain and the locus of the complex eigenvalues and shown in Fig. 6. From the nature

of the characteristics multipliers (i.e. eigen values) Hopf bifurcation confirmed. The movement of the locus from the left plane to the right plane shows that the system losses its stability when gain of controller is increased.

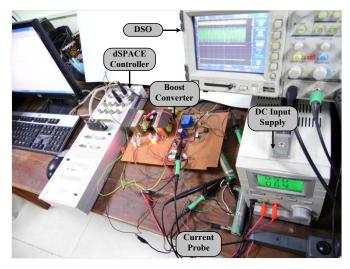

#### C. Experimental Implementation VMC Boost Converter

In order to study the practical non-linear phenomena, VMC boost converter designed and fabricated in the laboratory prototype scale. The circuit parameters of the converter given in Table I for investigation. Overall experimental setup and schematic circuit diagram are given in Fig.7(a) and Fig.7(b) respectively.

(a)

(b)

Fig. 7. (a) Experimental setup, (b) Schematic circuit diagram for closed-loop Boost converter in voltage mode control.

The experimental implementation of the closed-loop converter by using dSPACE controller in real-time platform fabricated. The dSPACE DS1104 is a controller board installed in the PCI slot of the PC. It contains two processors. The main processor is a MPC8240 PowerPC with a clock speed of 250 MHz and 32 kB internal cache memory. It acts as the master processor with TMS320F240 DSP as the slave containing 4 K Word of the dual port RAM. The LEM make Hall-effect voltage transducer (LV-25P) is used to sense the output voltage of the converter. Then the scaled and filtered signal fed to the ADC port of dSPACE controller. The output of voltage sensor is noisy and filtered by a low pass filter with a cut-off frequency of 5 kHz. This filter cut-off frequency is less than the switching frequency (25 kHz) of converter. The filtered output voltage is limited to a maximum of 4.7 V by placing two zener diodes in back to back fashion. The complete control system performed in dSPACE based real time interface platform. The reference input compared with conditioned digital voltage output coming from ADC port of dSPACE. After comparing two signals, an error signal generated and this error signal passed through the Type-III controller and control signal obtained. Now, this control signal is comparing with a high frequency (similar to switching frequency) triangular waveform for generating a PWM signal with in dSPACE environment. PWM output from dSPACE is passed through DAC, Opto-isolator (MCT2E) and Astable mutivibrator (NE555) circuit before inputting to the gate of MOSFET (STB55N) switch of the converter. The output of the opto-isolator is not sufficient to drive the gate of the MOSFET switch and fed to an inverting buffer circuit using 555-IC. The output of 555 inverting buffer connected to the gate of the MOSFET through 100  $\Omega$ resistance.

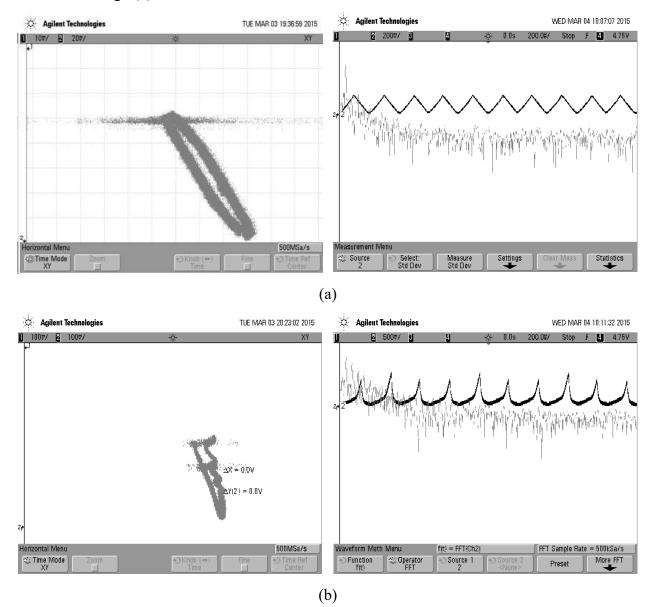

#### D. Experimental Results and Discussion

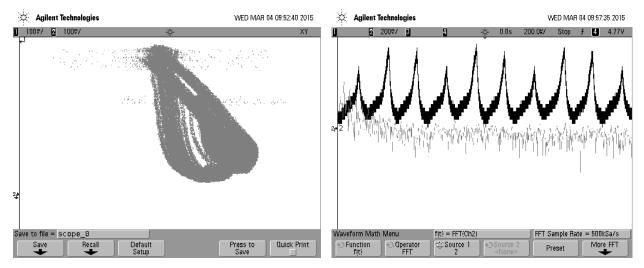

The phase portraits are useful method to identify the different periodic orbit to chaotic behavior. A DSO (Agilent Technologies DSO5014A) used in X-Y mode to capture the phase portraits at certain instants to study the different periodic and chaotic orbits. In this study, the output capacitor voltage is captured in Ch-1 (X-axis) and inductor current in Ch-2 (Y-axis) and measured by a FLUKE made current probe.

#### 1. Phase Portraits of Fundamental Orbit and Limit Cycle

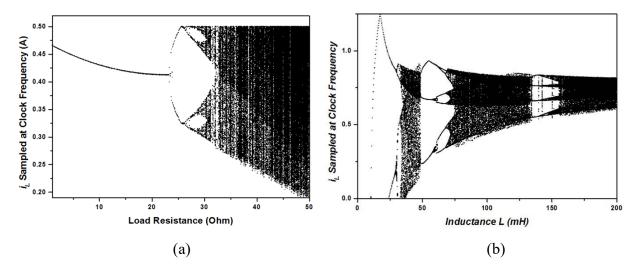

The experimental result of fundamental periodicity (Period-I) for the converter is observed in Fig.8(a) and the respective time domain wave form of inductor current is observed in Fig.8(a).

Noted, the fundamental periodic operation observed for load resistance ( $R_L$ ) equal to 21.7  $\Omega$ . From the time domain waveform, observed that the waveforms repeat after one clock cycle with time and the Period-I operation is known as fundamental periodic operation.  $R_L$  increased, the many other possible limit cycles observed due to the occurrence of slow-scale instabilities. At  $R_L$ = 32.3  $\Omega$ , the limit cycle of Period-III observed in phase portrait by keeping other parameters remain same (Fig.8(b)). The respective time domain waveform of this limit cycle has also been illustrated in Fig.8(b).

Fig. 8. (a) Phase portrait of Period-I operation at  $R_L = 21.7 \Omega$  and respective time-domain waveform & FFT analysis of inductor current (Ch-2), and (b) Phase portrait of limit cycle at  $R_L =$

32.3  $\Omega$ , and respective time-domain waveform & FFT analysis of inductor current (Ch-2).

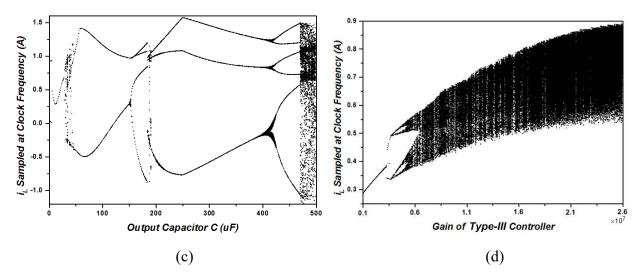

## 2. Phase Portrait of Chaotic Orbit

In chaotic mode operation, the system dynamics is attained a bounded aperiodic oscillation within a definite zone in phase-portrait. In chaotic dynamics, the same state never repeats, in every loop of phase-plane the state traverses through a new trajectory. Periodicities of limit cycle are infinite and in time domain the waveform of the state variables repeat after time-domain

Fig. 9. Phase portraits of chaotic operation at  $R_L = 43.6 \Omega$ , and respective waveform & FFT analysis of inductor current (Ch-2).

infinite clock cycle (practically above 10 clock cycles). Such situation occurs in an electronic circuit, the system undergoes apparently random oscillations. In this work for the value of load resistance of 43.6  $\Omega$  (keeping other variables remains constant) the above-mentioned phenomenon occurs. Fig. 9 illustrated the phase portrait of experimental chaotic orbits and the respective time domain waveform of VMC of the converter. Observed that the periodicities of the converter dynamics are high and the converter works almost on the verge of DCM operation.

Henceforth, the sequel of this study concluded that the choice of parameters and their values play a key role to determine the dynamics of the DC-DC boost converter, useful for designing the practical power supply.

#### VI. CONCLUSION

The analysis of discrete modeling and complex dynamics of Type-III controller based switched

mode boost converter with the voltage mode control studied in this work. The computational results observed by solving the differential equations of the switching converter and finally the nature of the converter's complex dynamics verified by experimental results. The slow-scale instability observed throughout the study by parametric variation of the converter. Also, shown that as the control parameters varied, the nominal periodic orbit undergoes a Hopf bifurcation, quasi-periodicity, and finally enters into chaotic regime. Zones of the practical chaos, quasi-periodic oscillation easily identified from the experimental results. It is to be noted that chaotic operations should not be accepted in the practical design of power supplies due to non-linear oscillation, EMI problem etc. For designing of the power supply one should avoid these types of complexities in their final products and the fundamental periodic behavior of system dynamics in VMC Type-III controller based DC-DC boost converter circuit observed by using dSPACE real time controller and firstly reported in this manuscript. Presented results suit the designers easily find out the probable operating zone and route to design a chaos free power supply.

#### References

- J. H. B. Deane, and D. C. Hamill, "Instability, subharmonics, and chaos in power electronic systems," IEEE Transactions on Power Electronics, vol. 5, no. 3, pp. 260-268, 1990.

- [2] J. H. Deane, "Chaos in a current-mode controlled boost dc-dc converter," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 39, no. 8, pp. 680-683, 1992.

- [3] D. C. Hamill, J. H. B. Deane, and D. J. Jefferies, "Modeling of chaotic DC-DC converters by iterated nonlinear mappings," IEEE Transactions on Power Electronics, vol. 7, no. 1, pp. 25-36, 1992.

- [4] W. C. Chan, and C. K. Tse, "Study of bifurcations in current-programmed DC-DC boost converters: from quasiperiodicity to period-doubling," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 44, no. 12, pp. 1129-1142, 1997.

- [5] S. Banerjee, and K. Chakrabarty, "Nonlinear modeling and bifurcations in the boost converter," IEEE Transactions on Power Electronics, vol. 13, no. 2, pp. 252-260, 1998.

- [6] A. El Aroudi, L. Benadero, E. Toribio, and G. Olivar, "Hopf bifurcation and chaos from torus breakdown in a PWM voltage-controlled DC-DC boost converter," IEEE Transactions

on Circuits and Systems I: Fundamental Theory and Applications, vol. 46, no. 11, pp. 1374-1382, 1999.

- [7] A. El Aroudi, and R. Leyva, "Quasi-periodic route to chaos in a PWM voltage-controlled DC-DC boost converter," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 48, no. 8, pp. 967-978, 2001.

- [8] S. Banerjee, and G. C. Verghese, "Nonlinear phenomena in power electronics: Bifurcations, chaos, control, and applications," Wiley-IEEE Press, 2001.

- [9] O. Dranga, C. K. Tse, H. H. Iu, and I. Nagy, "Bifurcation behavior of a power-factorcorrection boost converter," International Journal of Bifurcation and Chaos, vol. 13, no. 10, pp. 3107-3114, 2003.

- [10]C. K. Tsc, "Complex behavior of switching power converters," New York, CRC Press, 2003.

- [11] H. H. C. Iu, and C. K. Tse, "Study of low-frequency bifurcation phenomena of a parallelconnected boost converter system via simple averaged models," IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 50, no. 5, pp. 679-685, 2003.

- [12]A. Ghosh, "Nonlinear dynamics of power-factor-corrected AC-DC boost regulator: power converter, nonlinear phenomena, controlling the nonlinearity," LAP Lambert Academic Publishing, 2012.

- [13]A. Ghosh, S. Banerjee, P. K. Saha, and G. K. Panda, "Nonlinear modeling and bifurcations in switched power-factor-correction boost regulator," IEEE International Conference on Circuits, Power and Computing Technologies 2013 (ICCPCT-2013), pp. 517-522, 2013.

- [14]A. Ghosh, S. Banerjee, S. Basak, and C. Chakraborty, "A study of chaos and bifurcation of a current mode controlled flyback converter," IEEE 23<sup>rd</sup> International Symposium on Industrial Electronics 2014 (ISIE-2014), pp. 392-397, 2014.

- [15]W. Cheng, J. Song, H. Li, and Y. Guo, "Time-varying compensation for peak currentcontrolled PFC boost converter," IEEE Transactions on Power Electronics, vol. 30, no. 6, pp. 3431-3437, 2015.

- [16]M. Arjun, and V. Patil, "Steady state and averaged state space modelling of non-ideal boost converter", International Journal of Power Electronics, vol. 7, no. 1-2, pp. 109-133, 2015.

- [17]M. Zhioua, A. El Aroudi, S. Belghith, J. M. Bosque-Moncusí, R. Giral, K. Al Hosani, and M. Al-Numay, "Modeling, Dynamics, Bifurcation Behavior and Stability Analysis of a DC– DC Boost Converter in Photovoltaic Systems," International Journal of Bifurcation and Chaos, vol. 26, no. 10, pp. 1650166, 2016.

- [18]A. Ghosh, M. Prakash, S. Pradhan, and S. Banerjee, "A comparison among PID, Sliding Mode and internal model control for a buck converter, 40<sup>th</sup> IEEE Annual Conference of the Industrial Electronics Society 2014 (IECON 2014), pp. 1001-1006, 29<sup>th</sup> October – 1<sup>st</sup> November 2014, Dallas, TX, U.S.A.

- [19]A. Ghosh, and S. Banerjee, "Study on chaos and bifurcation in DC-DC flyback converter," International Journal of Industrial Electronics and Drives, vol. 3, no. 3, pp. 161-174, 2017.

- [20]A. Ghosh, and S. Banerjee, "Study of complex dynamics of DC-DC buck converter," International Journal of Power Electronics, vol. 8, no. 4, pp. 323-348, 2017.

- [21]A. Ghosh, and S. Banerjee, "Control of switched-mode Boost converter by using classical and optimized type controllers" in Journal of Control Engineering and Applied Informatics (CEAI), vol. 17, no. 4, pp. 114-125, 2015.

- [22]A. Ghosh, S. Banerjee, M. K. Sarkar, and P. Dutta, "Design and implementation of Type-II and Type-III controller for DC-DC switched-mode Boost converter by using K-Factor approach and optimization techniques", IET Power Electronics, vol. 9, no. 5, pp. 938-950, 2016.

- [23]S. Banerjee, A. Ghosh, and N. Rana, "An improved interleaved Boost converter with PSO based optimal Type-III controller", IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 1, pp. 323-337, 2017.

- [24]N. Rana, A. Ghosh, and S. Banerjee, "A comparative closed-loop performances of a DC-DC switched-mode Boost converter with classical and PSO based optimized Type-II/III controllers," International Journal of Power Electronics, 2017.

- [25]N. Rana, A. Ghosh, and S. Banerjee, "Development of an improved Tristate Buck–Boost converter with optimized Type-3 controller," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 400-415, 2018.

- [26]N. Rana, M. Kumar, A. Ghosh, and S. Banerjee, "A novel interleaved Tri-state Boost converter with lower ripple and improved dynamic response," IEEE Transactions on Industrial Electronics, vol. 65, no. 7, pp. 5456-5465, 2018.

- [27]R. Sakthivel, S. Santra, S.M. Anthoni, V. Kuppili "Synchronisation and anti-synchronisation of chaotic systems with application to DC–DC Boost converter," IET Generation, Transmission & Distribution, vol. 11, no. 4, pp. 959-67, 2017.

- [28]L. Cheng, W.H. Ki, F. Yang, P.K. Mok, and X. Jing, "Predicting subharmonic oscillation of voltage-mode switching converters using a circuit-oriented geometrical approach," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 3, pp. 717-730, 2017.

- [29]H. Zhang, W. Li, H. Ding, P. Luo, X. Wan, W. Hu, "Nonlinear modal analysis of transient behavior in cascade DC–DC Boost converters," International Journal of Bifurcation and Chaos, vol. 27, no. 9, pp. 1750140, 2017.

- [30]Y. Wang, R. Yang, B. Zhang, and W. Hu, "Smale horseshoes and symbolic dynamics in the Buck–Boost DC–DC converter," IEEE Transactions on Industrial Electronics, vol. 65, no. 1, pp. 800-809, 2018.