# MODELING AND SIMULATION FOR SIGNAL AND POWER INTEGRITY OF ELECTRONIC PACKAGES

A Dissertation Presented to The Academic Faculty

By

Jae Young Choi

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2012

Copyright © 2012 by Jae Young Choi

# MODELING AND SIMULATION FOR SIGNAL AND POWER INTEGRITY OF ELECTRONIC PACKAGES

## Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. David C. Keezer School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Andrew F. Peterson School of Electrical and Computer Engineering Georgia Institute of Technology Dr. James Stevenson Kenney School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hao-Min Zhou School of Mathematics Georgia Institute of Technology

Date Approved: October 25, 2012

#### **ACKNOWLEDGMENTS**

This dissertation would not have been possible without the support of the people who have helped and inspired me during the past five years of my Ph.D. life at Georgia Tech. First and foremost, I would like to thank my academic advisor, Dr. Madhavan Swaminathan, who gave me the invaluable opportunity to work on the cutting-edge research in his group. His continuous support, guidance, and encouragement enabled me to work on the research that has resulted in this dissertation. I respect and admire his technical insight, his reasonable management skill, and his endless passion for scientific research. I am also indebted to my committee members, Dr. David C. Keezer, Dr. Andrew F. Peterson, Dr. James Stevenson Kenney, and Dr. Hao-Min Zhou for their time and effort for providing me their valuable comments on my dissertation.

I would like to thank both current and past members of the Mixed Signal Design Group. I would like to thank Dr. Daehyun Chung, Dr. Sunghwan (Max) Min, and Dr. Andy Seo for their support as research mentors in my early Ph.D. life. I would also like to give my thanks to Dr. Junki Min for spending his time on technical discussions. I was fortunate to have kind, fun, and genius colleagues – Jianyong Xie, Dr. Myunghyun Ha, Dr. Suzanne Huh, Dr. Tapobrata Bandyopadhyay, Dr. Seunghyun Hwang, Dr. Narayanan T.V., Dr. Nithya Sankaran, Dr. Abhilash Goyal, Dr. Nevin Altunyurt, Dr. Ki Jin Han, Dr. Krishna Bharath, Aswani Kurra, Sukruth Pattanagiri, Vishal Laddha, and Bernard Yang. My special thanks go to Dr. Krishna Bharath for his help and advice on my early Ph.D. life that shaped and boosted my research progress. I would also like to credit Jianyong Xie, Sang Kyu Kim, Dr. Myunghyun Ha, Dr. Narayanan T.V., and Dr. Ki Jin Han for

sharing their profound knowledge on computational electromagnetics. I would like to express my sincere gratitude to colleagues with whom I spent my recent years, Kyu Hwan Han, Satyan Telikepalli, Biancun Xie, Stephen Dumas, David Zhang, Rishik Bazaz, Sung Joo Park, Ming Yi, Diapa Sonogo, Sang Kyu Kim, and Colin Pardue for their presence as active and passionate colleagues.

I owe my deepest heartfelt gratitude to my family. I am fortunate and proud to have been born to my parents. My father, Mr. Woun Jung Choi, has always been my life-time advisor. His keen insight, sound judgment, and cheerful mindset really helped me find ways through hardships, and his philosophic values will forever nurture my life. The devotion, passion, and love of my mother, Mrs. Sook Ja Hwang, have always been my greatest support and strength. Her warm-hearted and optimistic attitude and saying, "everything will be fine," have inspired me not only during the course of my studentship but also for my whole life. My sister, Jin Hee Choi, has been my noble mentor, precious counselor, and best friend. I want to credit her pioneering spirit that has led me to the path of a Ph.D. at Georgia Tech. Last, but by no means least, I am immensely lucky to have met my fiancée, Susie Kim, in the last year of my Ph.D. course. I am truly thankful for her being a part of my life!

格物致知-study of things and nature to reach for knowledge

# **TABLE OF CONTENTS**

| ACKN   | OWLEDGMENTS                                                    | iv  |

|--------|----------------------------------------------------------------|-----|

| LIST ( | OF TABLES                                                      | X   |

| LIST ( | OF FIGURES                                                     | xi  |

| SUMM   | IARY                                                           | xix |

| CHAP   | TER 1 INTRODUCTION                                             | 1   |

| 1.1    | BACKGROUND AND MOTIVATION                                      | 1   |

| 1.     | 1.1 Challenges in Electrical Design of Package Systems         | 1   |

| 1.     | 1.2 Challenges in Electrical Modeling of Package Systems       | 4   |

| 1.2    | CONTRIBUTIONS                                                  | 5   |

| 1.3    | ORGANIZATION OF THE DISSERTATION                               | 6   |

| CHAP   | TER 2 ORIGIN AND HISTORY OF THE PROBLEM                        | 7   |

| 2.1    | PDN Modeling Methods                                           | 7   |

| 2.     | 1.1 The Cavity Resonator Model Using Segmentation Method       | 8   |

| 2.     | 1.2 Modeling Methods Based on Discretization                   | 9   |

| 2.     | 1.3 Overview of Computational Electromagnetic Modeling Methods | 13  |

| 2.2    | EXTENSION TO MULTIPLE PLANE-PAIRS                              | 16  |

| 2.3    | INCORPORATION OF SIGNAL INTERCONNECTS INTO THE PDN             | 18  |

| 2.4    | SELECTION AND PLACEMENT OF DECOUPLING CAPACITORS               | 22  |

|        | TER 3 OPTIMIZATION OF DECOUPLING CAPACITOR SELECT              |     |

| 3.1    | Introduction                                                   | 26  |

| 3.2    | EXTENSION OF MFEM                                              | 26  |

| 3.     | 2.1 Formulation of Capacitive Elements in MFEM                 | 26  |

| 3.2 | 2.2 Inclusion of the Decoupling Capacitor Model to MFEM                      | 28 |

|-----|------------------------------------------------------------------------------|----|

| 3.3 | TEST CASES AND RESULTS                                                       | 29 |

| 3.4 | THE DECOUPLING OPTIMIZATION USING GENETIC ALGORITHM (GA)                     | 32 |

| 3.5 | GA CUSTOMIZED FOR THE DECOUPLING CAPACITOR PROBLEM                           | 35 |

| 3.6 | TEST CASES AND RESULTS                                                       | 37 |

| 3.0 | 6.1 Test Case 1                                                              | 37 |

| 3.0 | 6.2 Test Case 2                                                              | 41 |

| 3.7 | Summary                                                                      | 43 |

| _   | TER 4 POWER INTEGRITY MODELING USING THE MULTILA GULAR ELEMENT METHOD (MTEM) |    |

| 4.1 | INTRODUCTION                                                                 | 45 |

| 4.2 | FORMULATION FOR SINGLE PLANE-PAIR                                            | 45 |

| 4.2 | 2.1 Generalization of Planar Circuit Model                                   | 45 |

| 4.2 | 2.2 Application of Delaunay and Voronoi Mesh                                 | 47 |

| 4.2 | 2.3 Inclusion of Loss Terms                                                  | 51 |

| 4.3 | EXTENSION TO MULTIPLE PLANE-PAIRS                                            | 55 |

| 4.4 | MESH GENERATION                                                              | 59 |

| 4.5 | MODELING OF APERTURES                                                        | 59 |

| 4.6 | INCLUSION OF EXTERNAL CIRCUIT ELEMENTS                                       | 63 |

| 4.7 | TEST CASES AND RESULTS                                                       | 64 |

| 4.  | 7.1 Multiple Plane-Pairs with Apertures                                      | 64 |

| 4.  | 7.2 Decoupling Capacitors                                                    | 67 |

| 4.8 | COMPARISON OF COMPUTATIONAL COMPLEXITY                                       | 68 |

| 4.8 | 8.1 Multi-Dimensional and Multilaver Structure                               | 68 |

| 4.                                            | 8.2 Computational Efficiency under Same Accuracy    | 70                    |

|-----------------------------------------------|-----------------------------------------------------|-----------------------|

| 4.                                            | 8.3 Comparison of MTEM and MFEM                     | 71                    |

| 4.                                            | 8.4 Large Sized Problems                            | 74                    |

| 4.9                                           | SUMMARY                                             | 75                    |

| CHAP'                                         | TER 5 MODELING OF PORTS                             | 77                    |

| 5.1                                           | PORT REPRESENTATIONS                                | 77                    |

| 5.                                            | 1.1 Vertical Port                                   | 77                    |

| 5.                                            | 1.2 Meaning of Horizontal and Diagonal Port         | 79                    |

| 5.                                            | 1.3 Replacing Non-Vertical Port with Vertical Port  | 84                    |

| 5.                                            | 1.4 Results                                         | 85                    |

| 5.2                                           | SENSITIVITY OF SELF-IMPEDANCE                       | 89                    |

| 5.3                                           | SUMMARY                                             | 95                    |

| СНАР'                                         | TER 6 MODELING OF RETURN PATH DISCONTINUITIES       | 0.0                   |

|                                               | LEK O MODELING OF RETURN PATH DISCONTINUITIES       | 90                    |

| 6.1                                           | INTRODUCTION                                        |                       |

|                                               |                                                     | 96                    |

| 6.1                                           | INTRODUCTION                                        | 96<br>96              |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | INTRODUCTION                                        | 96<br>96              |

| 6.1<br>6.2<br>6.3<br>6.                       | INTRODUCTION                                        | 96<br>96<br>99        |

| 6.1<br>6.2<br>6.3<br>6.                       | INTRODUCTION                                        | 96<br>96<br>99<br>100 |

| 6.1<br>6.2<br>6.3<br>6.<br>6.                 | INTRODUCTION  RPD BY SPLIT PLANES  RPD BY APERTURES | 9696100102            |

| 6.1<br>6.2<br>6.3<br>6.<br>6.                 | INTRODUCTION                                        | 9696100102103         |

| 6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.           | INTRODUCTION  RPD BY SPLIT PLANES                   |                       |

| 6.1<br>6.2<br>6.3<br>6.<br>6.<br>6.<br>6.4    | INTRODUCTION                                        |                       |

| 6.5.1 RPD by Apertures                                            | 109  |

|-------------------------------------------------------------------|------|

| 6.5.2 RPD by Small Apertures                                      | 110  |

| 6.5.3 RPD due to Via                                              | 114  |

| 6.6 Summary                                                       | 118  |

| CHAPTER 7 PLANE-PAIR MODELING WITH ABOSORBING B CONDITION         |      |

| 7.1 Introduction                                                  | 119  |

| 7.2 Absorbing Boundary Condition for MTEM                         | 120  |

| 7.2.1 Open-Circuit Boundary Condition                             | 120  |

| 7.2.2 1 <sup>st</sup> Order Absorbing Boundary Condition for MTEM | 122  |

| 7.2.3 ABC for One-Dimensional Structure                           | 123  |

| 7.2.4 ABC for Two-Dimensional Structure                           | 127  |

| 7.2.5 Test Cases                                                  | 131  |

| 7.3 Summary                                                       | 139  |

| CHAPTER 8 CONCLUSIONS                                             | 140  |

| 8.1 Contributions                                                 | 142  |

| 8.2 Publications                                                  | 146  |

| 8.3 PATENT APPLICATION                                            | 147  |

| DEFEDENCES                                                        | 1.40 |

# LIST OF TABLES

| Table 1. Comparison of computational electromagnetic modeling methods                  | 15  |

|----------------------------------------------------------------------------------------|-----|

| Table 2. Target impedance trend [37]                                                   | 23  |

| Table 3. Comparison of system matrices created for the example in Figure 4.10          |     |

| $(K=10^3)$                                                                             | 70  |

| Table 4. Comparison of system matrices under the same accuracy                         | 71  |

| Table 5. Computational efforts in solving a 10-layer structure ( $K=10^3$ , $M=10^6$ ) | 74  |

| Table 6. Change of network parameters as mesh size changes.                            | 92  |

| Table 7. Comparison of memory consumption (K=10 <sup>3</sup> ).                        | 113 |

# LIST OF FIGURES

| Figure 1.1. SSN generation and influences in a package. (Reproduced from [5].)           |

|------------------------------------------------------------------------------------------|

| Figure 1.2. A part of the typical design process of electronic packages. (Modified       |

| from [7] and [8].)5                                                                      |

| Figure 2.1. Cell-centered discretization of the Laplace operator and the equivalent      |

| circuit of FDM11                                                                         |

| Figure 2.2. Equivalent circuit representation of a plane-pair using FEM (lower plane     |

| is not shown)                                                                            |

| Figure 2.3. (a) Cross-section of a three-layer structure. The equivalent (b) inductance  |

| and (c) capacitance model                                                                |

| Figure 2.4. Layout of (a) power and ground planes and (b) signal interconnects.          |

| (Courtesy of class notes for Purdue University ECE477, Spring 2009.)19                   |

| Figure 2.5. Current loops created at the return path discontinuities created by (a) slot |

| and (b) via transition                                                                   |

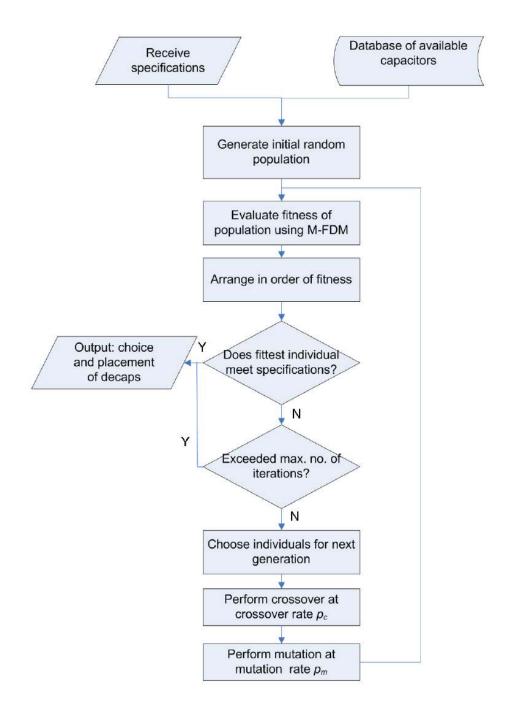

| Figure 2.6. A flow chart of the typical optimization procedures of decoupling            |

| capacitor selection and placement using the GA [42]25                                    |

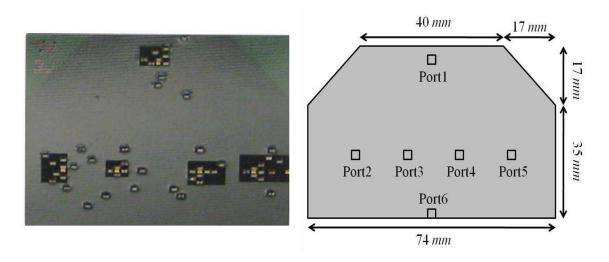

| Figure 3.1. Top view of the test vehicle with decoupling capacitors (left) and the       |

| dimensions and the port locations (right). (Test vehicle provided by Sony                |

| Corp., Tokyo, Japan)29                                                                   |

| Figure 3.2. Self-impedance responses at port 1 and 2 of the test vehicle without         |

| decoupling capacitors30                                                                  |

| Figure 3.3. Self-impedance responses at port 1 and 2 of the test vehicle with       |

|-------------------------------------------------------------------------------------|

| decoupling capacitors31                                                             |

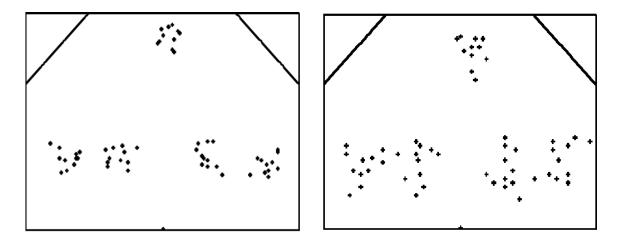

| Figure 3.4. Comparison of mesh generations of MFDM (left) and MFEM (right) for      |

| the test vehicle with decoupling capacitors31                                       |

| Figure 3.5. Pseudocode representation of the decoupling capacitor optimization      |

| problem using GA and MFEM35                                                         |

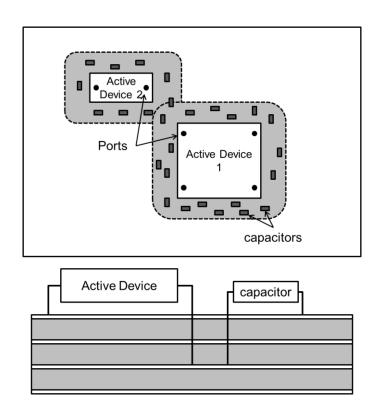

| Figure 3.6. Scenarios of decoupling capacitor placement. Capacitors are only placed |

| within the shaded region (top). Connectivity of the capacitors follows that         |

| of the nearest active device to reduce the spreading inductance (bottom)36          |

| Figure 3.7. A flow chart of the optimization process of selection and placement of  |

| decoupling capacitors using the customized GA and MFEM. The                         |

| components in the dotted-boxes represent the new features added or                  |

| replaced from the typical GA                                                        |

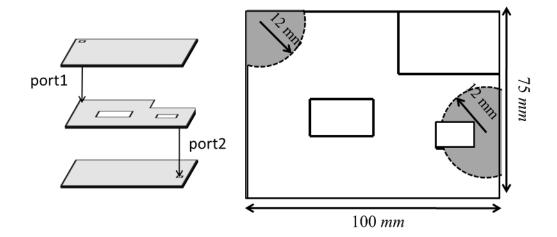

| Figure 3.8. Perspective view of an example structure (left). Top view shows the     |

| superposition of the feature outlines in each layer and the confined region         |

| (gray area) for capacitor placement (right)                                         |

| Figure 3.9. Self-impedance responses of port 1 and 2 of the test case 1 after the   |

| optimization using the customized GA40                                              |

| Figure 3.10. Comparison of the convergence between the customized GA and the        |

| typical GA using the fitness values                                                 |

| Figure 3.11. Comparison of final placement of capacitors using the customized GA    |

| (left) and the typical GA (right)41                                                 |

| Figure 3.12. Self-impedance responses at port 1 and 2 of the test case 2 after the     |

|----------------------------------------------------------------------------------------|

| optimization using the customized GA42                                                 |

| Figure 3.13. Comparison of final placement of capacitors using the customized GA       |

| (left) and the typical GA (right)                                                      |

| Figure 4.1. The equivalent circuit of a unit-cell in a plane-pair47                    |

| Figure 4.2. Triangle unit-cell and neighboring triangles of a plane-pair50             |

| Figure 4.3. Equivalent circuit of MTEM with loss terms.                                |

| Figure 4.4. Areas for the conductor loss calculation: Area enclosed by blue dashed     |

| line is for triangular mesh (MTEM), while red dotted line is for a                     |

| rectangular mesh54                                                                     |

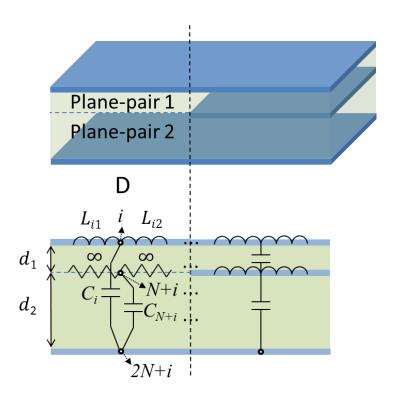

| Figure 4.5. Multiple plane-pairs (left) and the equivalent circuit of each plane-pair  |

| (right). i and j are node numbers that range between 1 and N, where N is               |

| the total number of the nodes on each plane-pair56                                     |

| Figure 4.6. Block diagrams of each plane-pair model using indefinite admittance        |

| matrices (top), and the combined model with a shift of the ground                      |

| reference (bottom)                                                                     |

| Figure 4.7. Plane-pair sections with and without apertures on the top and the bottom   |

| plane (top). One-dimensional equivalent circuits of each section (bottom)60            |

| Figure 4.8. Modeling of an aperture in the middle of multiple plane-pairs61            |

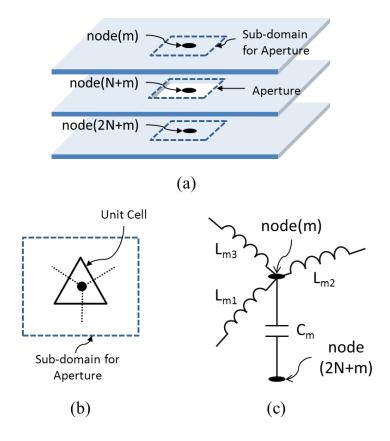

| Figure 4.9. (a) A three-layer structure with an aperture in the middle layer. (b) Top  |

| view of the sub-domain for the aperture. (c) Equivalent circuit for the                |

| node in the aperture63                                                                 |

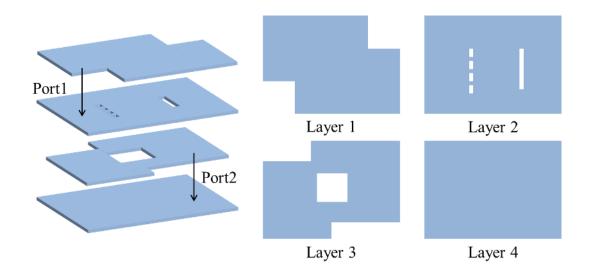

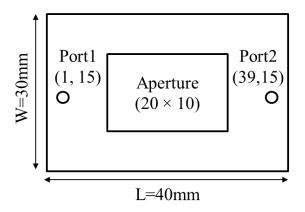

| Figure 4.10. Example of a multiple plane-pair structure with apertures on each layer65 |

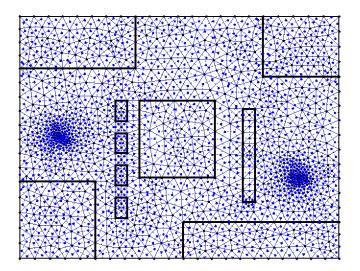

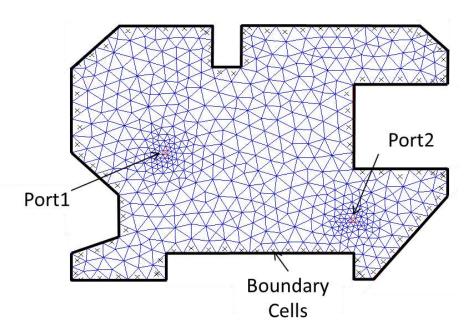

| Figure 4.11. Dual mesh created on the layer where all the geometries from each layer     |

|------------------------------------------------------------------------------------------|

| are concatenated together65                                                              |

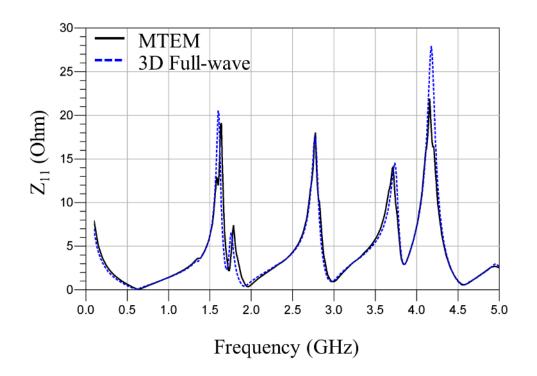

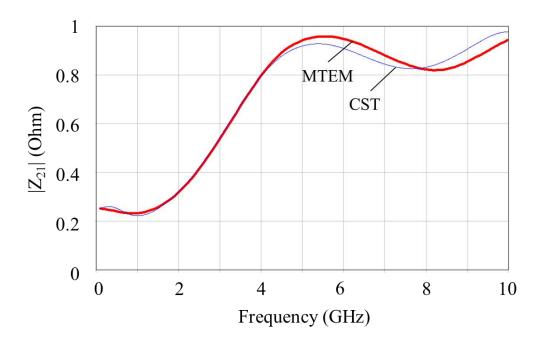

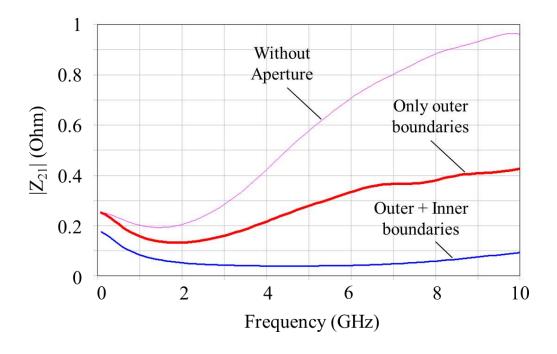

| Figure 4.12. Self-impedance at port 1                                                    |

| Figure 4.13. Transfer impedance between port 1 and 2                                     |

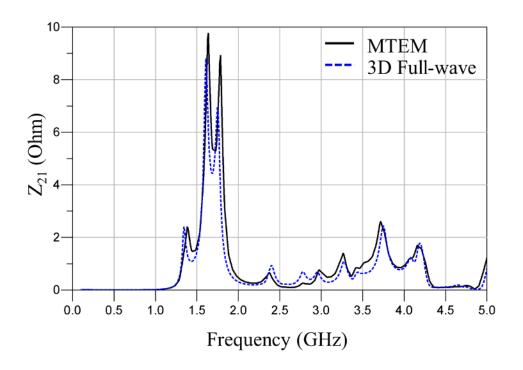

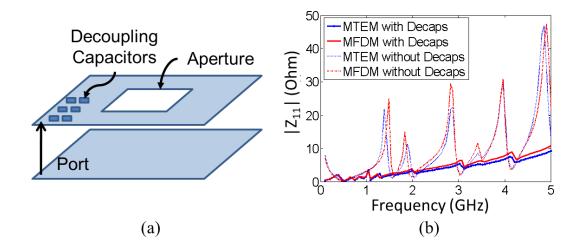

| Figure 4.14. (a) Two-layer structure with an aperture and six decoupling capacitors      |

| near the port. (b) Self-impedance responses with and without decoupling                  |

| capacitors68                                                                             |

| Figure 4.15. (a) Example of a structure with multi-dimensional geometries. (b)           |

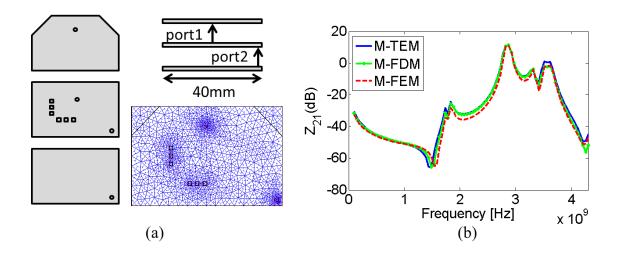

| Transfer-impedance responses                                                             |

| Figure 4.16. Created meshes by MFDM, MFEM, and MTEM for the example                      |

| structure shown in Figure 4.1569                                                         |

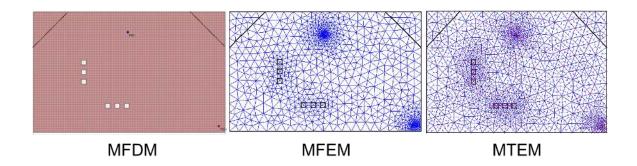

| Figure 4.17. Triangular mesh for MFEM and the dual graphs for MTEM72                     |

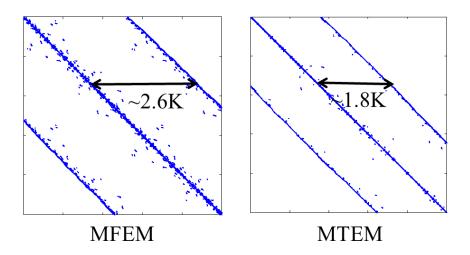

| Figure 4.18. Zoomed-in areas of the reordered matrices of MFEM and MTEM                  |

| $(K=10^3)$ 73                                                                            |

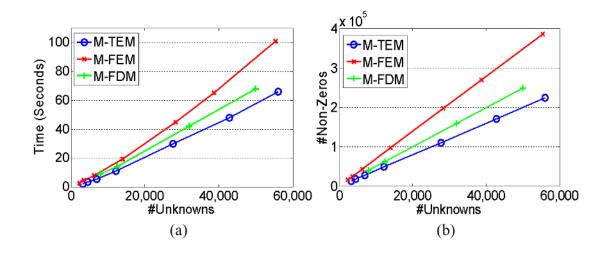

| Figure 4.19. (a) Growth of computation time and (b) growth of the number of non-         |

| zero entries as the number of unknowns increases                                         |

| Figure 4.20. Growth of the number of non-zero entries as the number of layers            |

| increases75                                                                              |

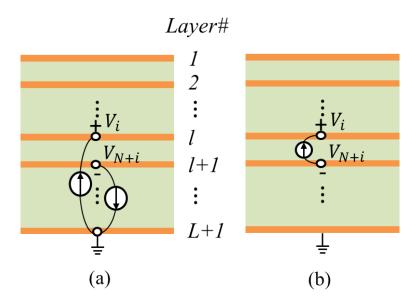

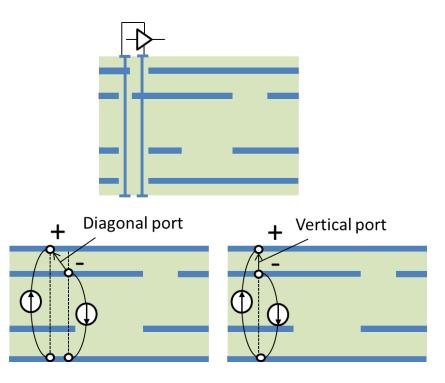

| Figure 5.1. Cross-section of a multilayer structure with a vertical port. (a) Excitation |

| of current sources at port terminals and (b) the equivalent source                       |

| excitation                                                                               |

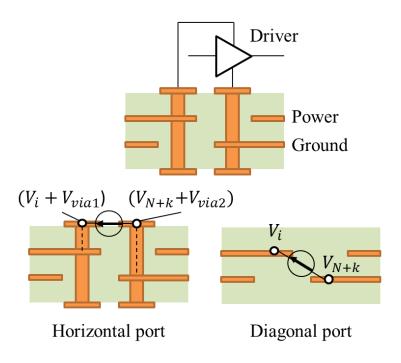

| Figure 5.2. Definition of a horizontal and a diagonal port                               |

| Figure 5.3. (a) Cross-section of a port, and (b) the equivalent port representation. (c) |    |

|------------------------------------------------------------------------------------------|----|

| Two current sources vertically connect port terminals and the voltage                    |    |

| reference layer.                                                                         | 31 |

| Figure 5.4. Noise source excitation of a diagonal port (red arrow) and generated E-      |    |

| field lines (black arrows)                                                               | 3  |

| Figure 5.5. Vertical port replaces (a) diagonal and (b) horizontal ports. Dotted lines   |    |

| indicate the path impedance excluded in the vertical port result                         | 35 |

| Figure 5.6. Cross-section of four-layer structure (top), and diagonal port (bottom left) |    |

| and vertical port (bottom right) model                                                   | 36 |

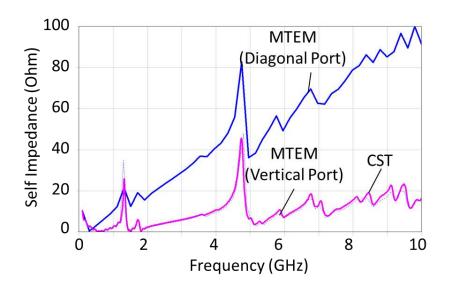

| Figure 5.7. Self-impedance results from MTEM and CST with different port                 |    |

| configurations                                                                           | 37 |

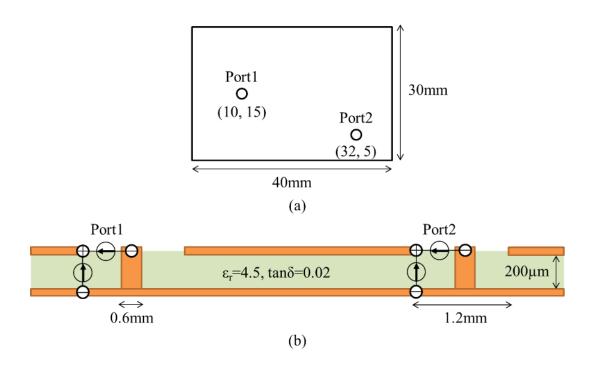

| Figure 5.8. (a) Top and (b) cross-sectional view of the structure simulated with a       |    |

| horizontal and a vertical port                                                           | 38 |

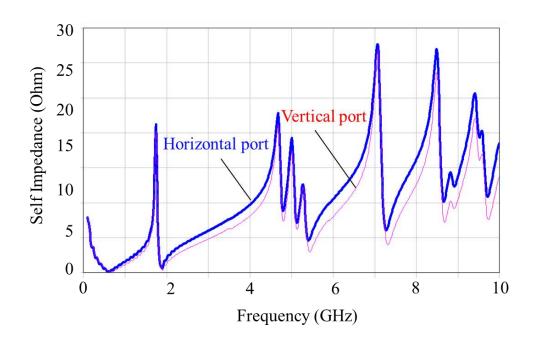

| Figure 5.9. Self-impedance results of horizontal and vertical port representations       | 38 |

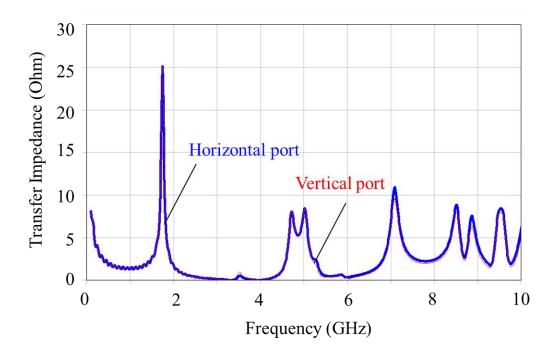

| Figure 5.10. Transfer-impedance results of horizontal and vertical port                  |    |

| representations8                                                                         | 39 |

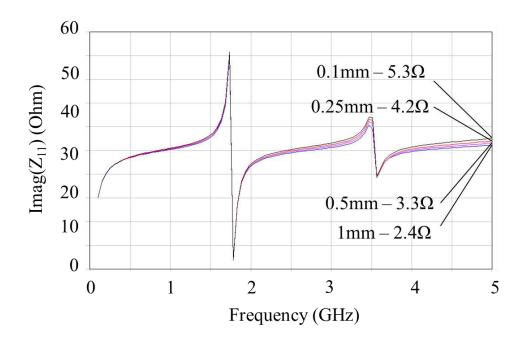

| Figure 5.11. Top view of a plane-pair for the sensitivity analysis of the self-          |    |

| impedance9                                                                               | 90 |

| Figure 5.12. Change of self-impedance along with the different mesh size around a        |    |

| port. Results are obtained from MFDM simulations9                                        | 90 |

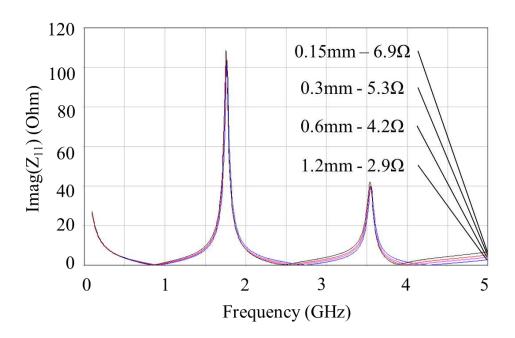

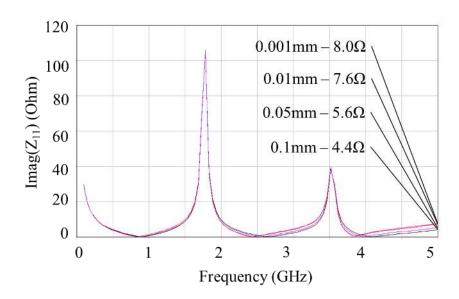

| Figure 5.13. Imaginary part of self-impedance                                            | 1  |

| Figure 5.14. Change of self-impedance along with the change of mesh size around a        |    |

| port. Results are obtained from CST transient solver9                                    | )3 |

| Figure 5.15. Change of self-impedance along with the change of mesh size around a          |

|--------------------------------------------------------------------------------------------|

| port. Results are obtained from the cavity resonator model94                               |

| Figure 5.16. Convergence of self-impedance as the port size decreases94                    |

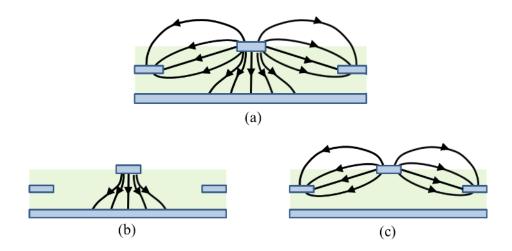

| Figure 6.1. Current distribution of a microstrip line crossing split planes97              |

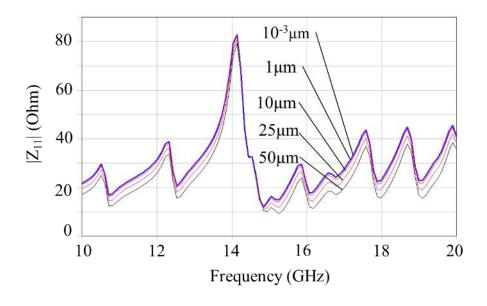

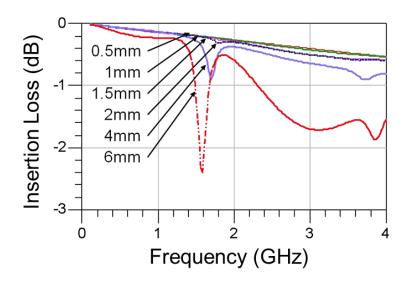

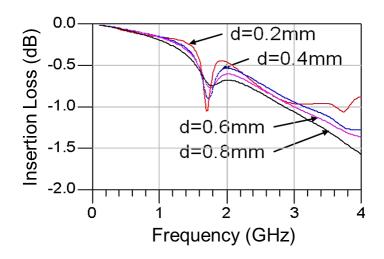

| Figure 6.2. Insertion loss curves as (a) the gap spacing and (b) the PDN thickness         |

| change98                                                                                   |

| Figure 6.3. Current distribution of a microstrip line crossing an aperture99               |

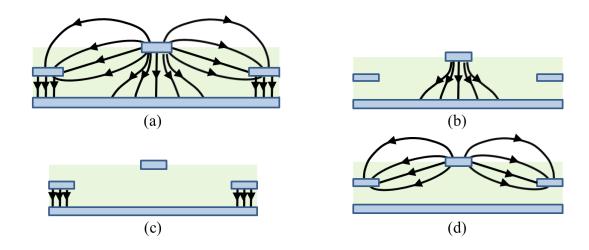

| Figure 6.4. (a) E-field distribution at the cross-section of a microstrip line crossing an |

| aperture. The propagation mode can be decomposed into (b) microstrip                       |

| line and (c) coplanar wave guide mode with an elevated center conductor. 100               |

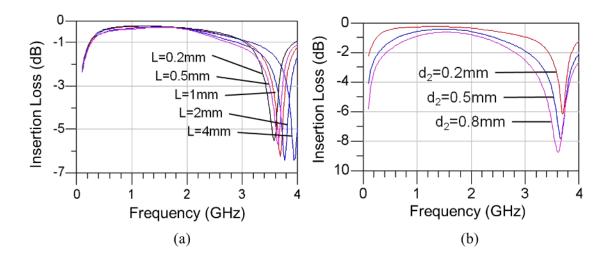

| Figure 6.5. Insertion loss changes as the aperture size changes                            |

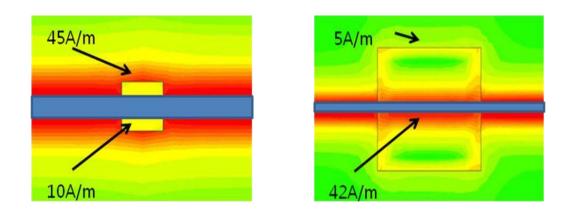

| Figure 6.6. Cross-sections of a microstrip line over an aperture. CPW-mode with an         |

| elevated center conductor (left) and a parallel-plate mode (right)102                      |

| Figure 6.7. Current densities around small and large apertures when a microstrip line      |

| transmits a 1-GHz signal                                                                   |

| Figure 6.8. Insertion loss changes as the dielectric thickness changes103                  |

| Figure 6.9. (a) E-field lines formed around the RPD created by an aperture. (b)-(d)        |

| Decomposed propagation modes                                                               |

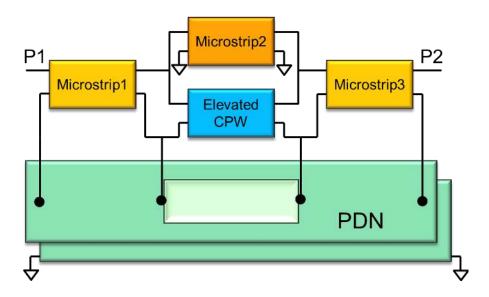

| Figure 6.10. Modal decomposition modeling of the microstrip line crossing an               |

| aperture                                                                                   |

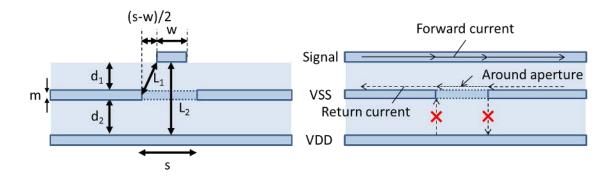

| Figure 6.11. Cross-sectional (left) and side view (right) of a microstrip line crossing a  |

| small aperture106                                                                          |

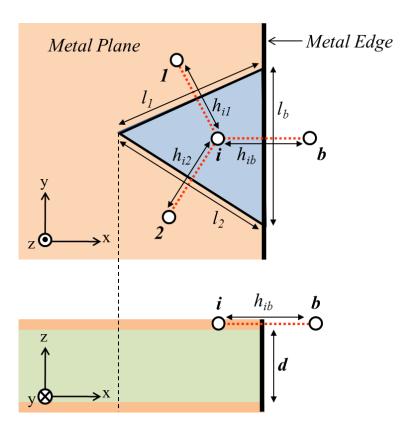

| Figure 6.12. Microstrip-via-microstrip transition                                          |

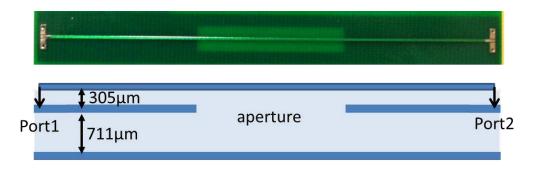

| Figure 6.13. Equivalent circuit model for the microstrip-via-microstrip transition108     |

|-------------------------------------------------------------------------------------------|

| Figure 6.14. Pi-model representation of a plate-through-hole via                          |

| Figure 6.15. A test vehicle of a microstrip line crossing an aperture                     |

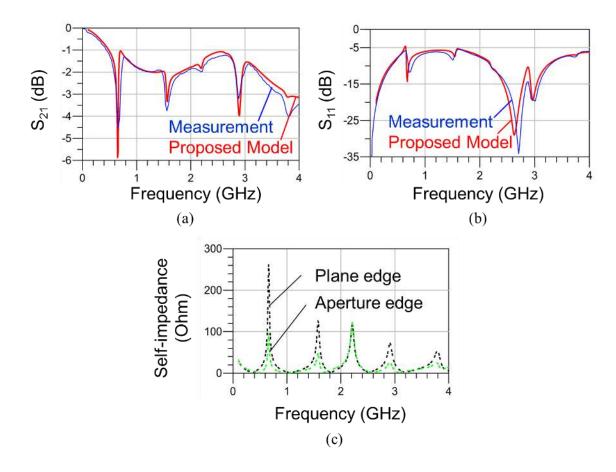

| Figure 6.16. (a) Insertion-loss and (b) return-loss responses of the microstrip line. (c) |

| Self-impedance responses at the edge and the middle of the plane110                       |

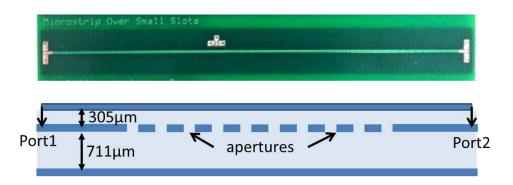

| Figure 6.17. Top view of the test vehicle (top) and cross-sectional view (bottom)111      |

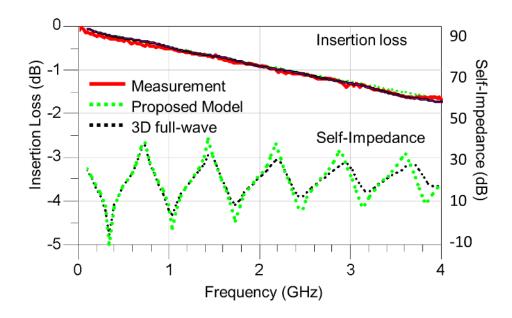

| Figure 6.18. Insertion loss and self-impedance curves of the test vehicle with a series   |

| of small apertures                                                                        |

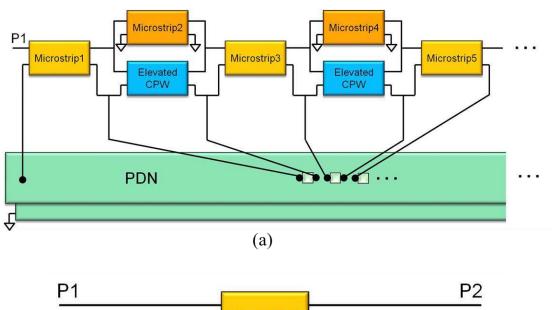

| Figure 6.19. Reduction of modeling complexity by ignoring small apertures. (a)            |

| Modeling small apertures. (b) Ignoring small apertures                                    |

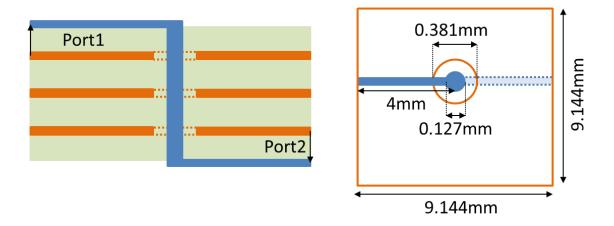

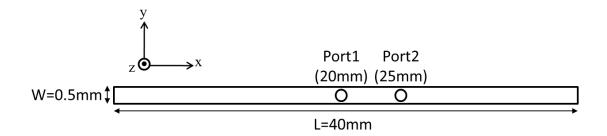

| Figure 6.20. Example of a microstrip-via-microstrip transition                            |

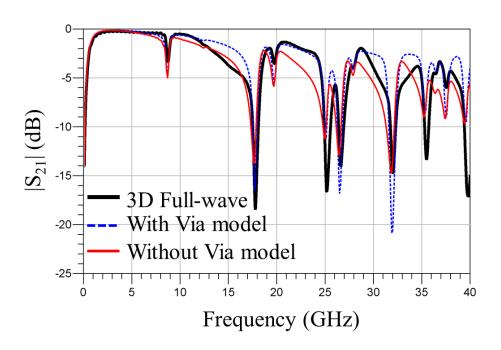

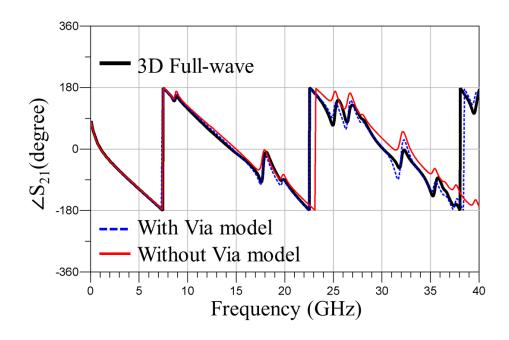

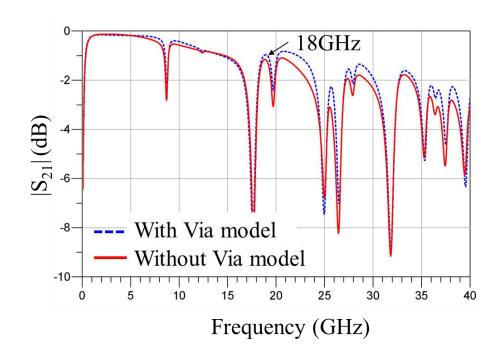

| Figure 6.21. Magnitude of the insertion loss of a microstrip-via-microstrip transition115 |

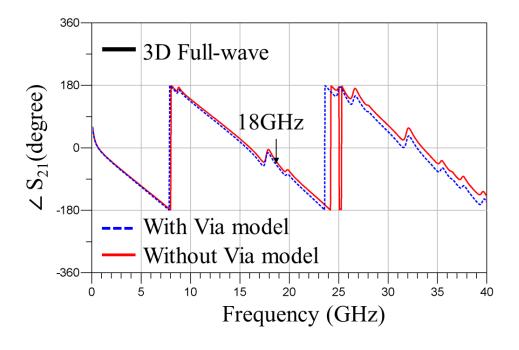

| Figure 6.22. Phase of the insertion loss of a microstrip-via-microstrip transition116     |

| Figure 6.23. Magnitude of the insertion loss of the structure with a short via117         |

| Figure 6.24. Phase of the insertion loss of the structure with a short via                |

| Figure 7.1. Top and cross-sectional view of a unit-triangle located at the boundary of    |

| a plane-pair                                                                              |

| Figure 7.2. Top view of a plane-pair with narrow left and right sides124                  |

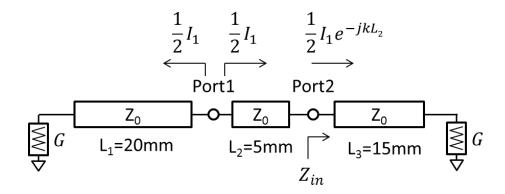

| Figure 7.3. Electrical model of the narrow plane-pair shown in Figure 7.2                 |

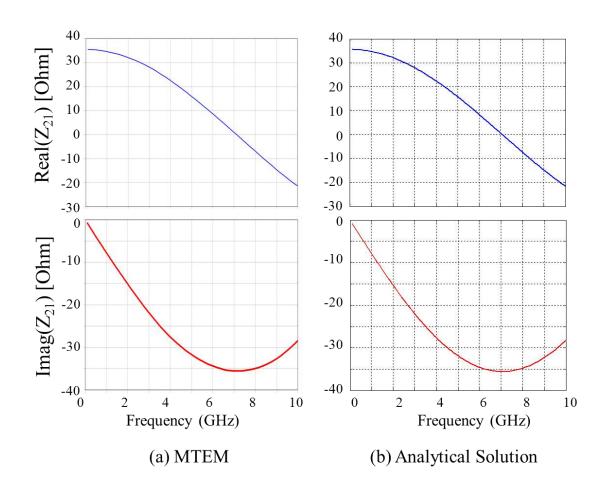

| Figure 7.4. Real and imaginary parts of the transfer impedance from (a) MTEM and          |

| (b) analytical solution126                                                                |

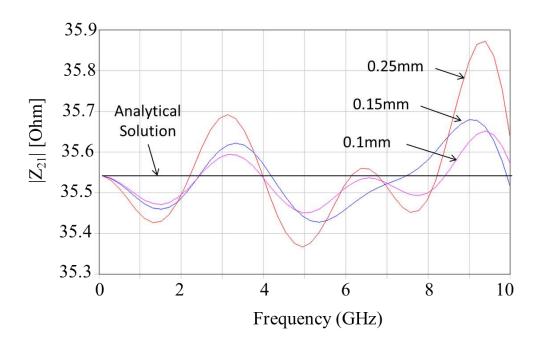

| Figure 7.5. Magnitude of the transfer impedance. Discrepancy reduces as mesh size         |

| dogranges 127                                                                             |

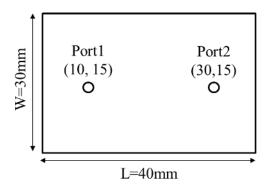

| Figure 7.6. Top view of a plane-pair with two ports.                                           | 128 |

|------------------------------------------------------------------------------------------------|-----|

| Figure 7.7. Transfer impedance and resonance modes.                                            | 128 |

| Figure 7.8. Electrical model of the plane-pair shown in Figure 7.6.                            | 129 |

| Figure 7.9. Magnitude of the transfer impedance of the plane-pair with ABC applied             |     |

| on left and right edges.                                                                       | 130 |

| Figure 7.10. Magnitude of the transfer impedance of the plane-pair with ABC applied            |     |

| on top and bottom edges.                                                                       | 131 |

| Figure 7.11. Transfer impedance of a plane-pair with ABC applied to the surrounding            |     |

| edges                                                                                          | 132 |

| Figure 7.12. Top view of test case 2 with an aperture in the middle of the top plane           | 133 |

| Figure 7.13. Transfer impedance of test case 2.                                                | 133 |

| Figure 7.14. Created mesh for an example structure. Crosses represent the boundary             |     |

| cells where 1st order ABC is applied.                                                          | 134 |

| Figure 7.15. Self-impedance results with and without the 1 <sup>st</sup> order ABC implemented |     |

| in MTEM.                                                                                       | 135 |

| Figure 7.16. Top (top) and cross-sectional view (bottom) of test case 4. Inner layers          |     |

| have slots.                                                                                    | 136 |

| Figure 7.17. Transfer impedance of test case 4 without ABC.                                    | 136 |

| Figure 7.18. Transfer impedance of test case 4 with ABC.                                       | 137 |

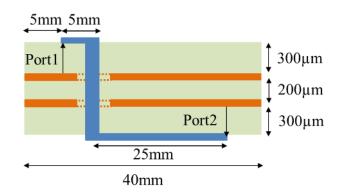

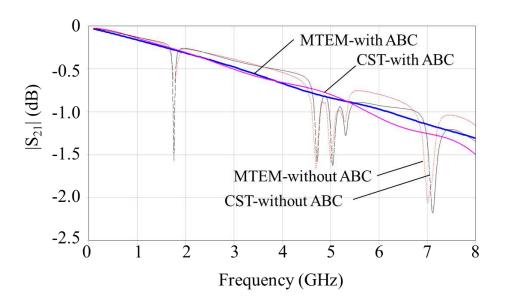

| Figure 7.19. Cross-sectional view of test case 5.                                              | 138 |

| Figure 7.20. Insertion loss of test case 5 simulated with both MTEM and CST with               |     |

| and without ABC at the plane boundary                                                          | 138 |

#### **SUMMARY**

The objective of this dissertation is to develop electrical modeling and cosimulation methodologies for signal and power integrity of package and board applications. The dissertation includes 1) the application of the finite element method to the optimization for decoupling capacitor selection and placement on a power delivery network (PDN), 2) the development of a PDN modeling method effective for multidimensional and multilayer geometries, 3) the analysis and modeling of return path discontinuities (RPDs), and 4) the implementation of the absorbing boundary condition for PDN modeling.

The optimization technique for selection and placement of decoupling capacitors uses a genetic algorithm (GA) and the multilayer finite element method (MFEM), a PDN modeling method using FEM. The GA is customized for the decoupling problem to enhance the convergence speed of the optimization. The mathematical modifications necessary for the incorporation of the capacitor model into MFEM is also presented.

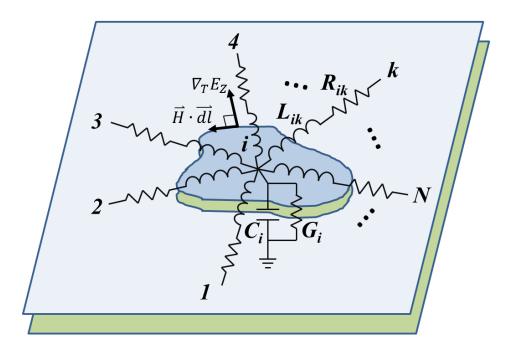

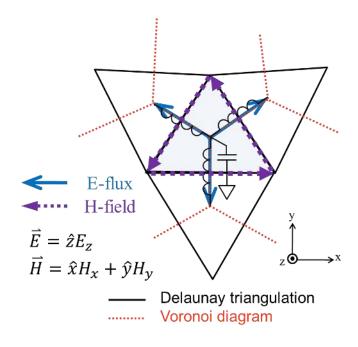

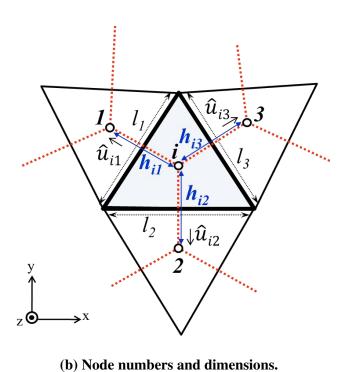

The main contribution of this dissertation is the development of a new modeling method, the multilayer triangular element method (MTEM), for power/ground planes of a PDN. MTEM creates a surface mesh on each plane-pair using dual graphs; a non-uniform triangular mesh (Delaunay triangulation) and its orthogonal counterpart (Voronoi diagram), to which electromagnetic and equivalent circuit concepts are applied. The non-uniform triangulation is especially efficient for discretizing multidimensional and irregular geometries which are common in package and board PDNs. Moreover, MTEM generates a sparse, banded, and symmetric system matrix, which enables efficient

computations. For a given plane-pair, MTEM extracts an equivalent circuit that is consistent with the physics-based planar-circuit model of a plane-pair. Thus, the values of the lumped elements can be simply calculated from the physical parameters, such as material properties and mesh geometries of each unit-cell. Consequently, the modeling of MTEM is flexible and easy to modify for further extensions, such as the incorporation of external circuits, e.g. decoupling capacitors and vertical interconnects.

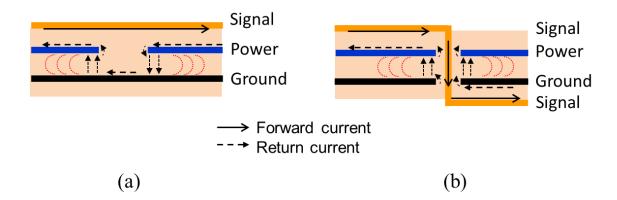

Power and ground planes provide paths for the return current of signal traces. Typically, planes have discontinuities such as via holes, plane cutouts, and split planes that disturb flow of signal return currents. At the discontinuity, return currents have to detour or switch to different layers, causing signal and power integrity problems. Therefore, a separate analysis of signal interconnects will neglect the significant coupling with a PDN, and the result will not be reliable. In this dissertation, the co-simulation of the signal and power integrity is presented focusing on the modeling of RPDs created by split planes, apertures, and vias.

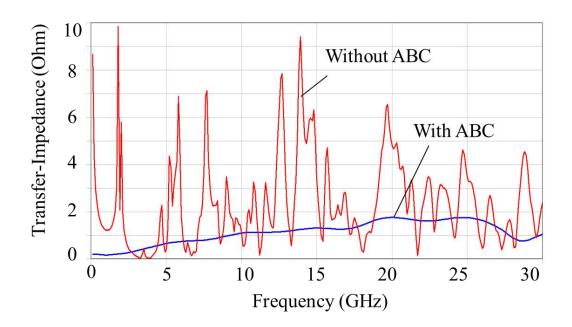

Plane resonance is one of the main sources of power integrity problems in package and board PDNs. A number of techniques have been developed and published in literature to reduce or prevent the resonance of a plane-pair. One of the techniques is to surround plane-pair edges with absorbing material that effectively damps the outgoing parallel-plate wave and minimizes the reflection. To model this behavior, the boundary condition of MTEM needs to be changed from its original form, the open-circuit boundary condition. In this dissertation, the application of the 1<sup>st</sup> order absorbing boundary condition to MTEM is presented.

#### CHAPTER 1

#### INTRODUCTION

# 1.1 Background and Motivation

The integration of electronic devices into a single system continues as new concepts of electronic packaging are being introduced. System-in-package (SiP) and system-on-package (SoP) typify the integration of multiple system functions into a single package providing all the needed system-level functions [1]. As a number of dissimilar components are integrated to a single platform requiring diverse power supply strategies, the design of a power delivery network (PDN) becomes more challenging.

# 1.1.1 Challenges in Electrical Design of Package Systems

The main function of an electronic package is the distribution of signal and power to the ICs. When multiple ICs draw electrical current from power supply, current flowing through a PDN causes voltage drops and fluctuations because of resistances and inductances residing in the power rail. To reduce the path impedance, power and ground nets are designed as conductor planes.

Typical PDNs comprise a stack-up of alternating layers of power and ground planes separated by dielectric substrates. This configuration can reduce the package inductance, and also isolate different levels of supply voltages. However, planes separated by a thin dielectric create a cavity that resonates at resonance frequencies. At anti-resonance frequencies, the cavity created by a plane-pair exhibits maximum impedance. When multiple drivers simultaneously draw power at the rate of the anti-

resonance frequency, the large impedance of the PDN results in large fluctuations in the supply voltage. This unwanted noise is known as simultaneous switching noise (SSN). The large voltage fluctuations impact on the performance of a microprocessor; the insufficient supply voltage slows down, and the excessive supply voltage breaks down the microprocessor [2]. Therefore, the PDN design emphasizes on ensuring that the voltage fluctuations do not exceed the allowed threshold of a system.

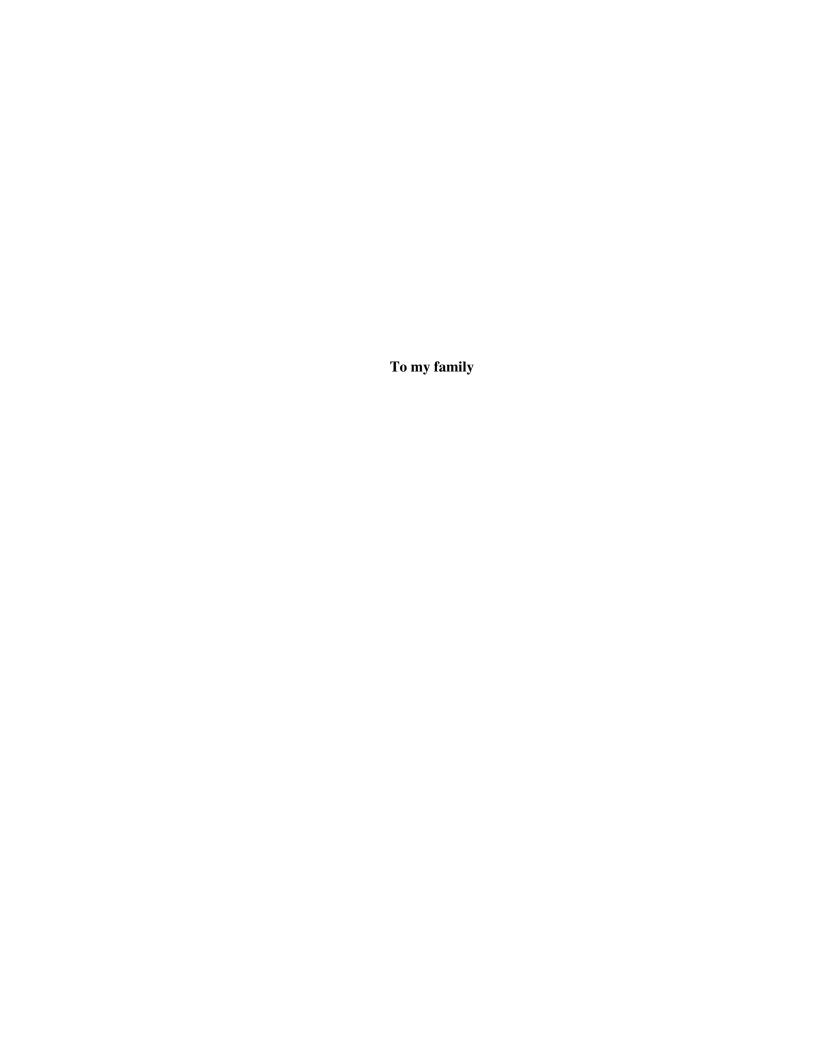

Since diverse components assembled in a package demand various supply voltages, power/ground planes are split for DC isolation. Planes also contain apertures and holes for embedded components and signal interconnects. These discontinuities in a PDN provide a path for the coupling of SSN throughout the system. The coupled SSN traverses the cavity created by a plane-pair as a radial wave, and is reflected from the plane edges. The reflected wave creates multiple resonances, which result in the fluctuation of supply voltage on the power/ground planes [3] [4]. The noise in power/ground planes can couple back to signal interconnects through the path created by PDN discontinuities and deteriorate the quality of signal. Since excessive voltage fluctuations cause both signal and power integrity (SI/PI) problems, the generation of SSN needs to be carefully analyzed in the design of a semiconductor system. The SI/PI problems in a package system are conceptually described in Figure 1.1.

Figure 1.1. SSN generation and influences in a package. (Reproduced from [5].)

To reduce the fluctuation of the supply voltage, the path impedance where the SSN current flows needs to be minimized. Hence, the purpose of the PDN design is to ensure that the impedance seen at the IC terminals meet the target impedance across the operating frequency range. To mitigate excessive fluctuations of the supply voltage, decoupling capacitors can be placed between the power and ground pads of nearby I/O circuits. However, since the decoupling capacitors become inductive at high frequencies, placing a number of capacitors without a well-organized strategy will fail to reduce the PDN impedance. Moreover, manually selecting an appropriate amount and right values of capacitors and placing them on optimal locations are complicated and time consuming processes. This tedious task becomes even more challenging as the level of the target

impedance of semiconductor systems is continuously falling, led by the decrease of supply voltage and increase of system current.

# 1.1.2 Challenges in Electrical Modeling of Package Systems

The impedance profile of a PDN can be obtained by simulations that capture the electromagnetic behaviors of the PDN. PDNs can be simply modeled as a single-node system assuming the voltage variations occur simultaneously across the planes [6]. However, the simple model fails to take into account the distributed behavior of the planes at high frequencies. PDN modeling also needs to accurately capture complex geometries, such as a stack-up of multiple planes, gaps and holes in planes, and decoupling capacitors.

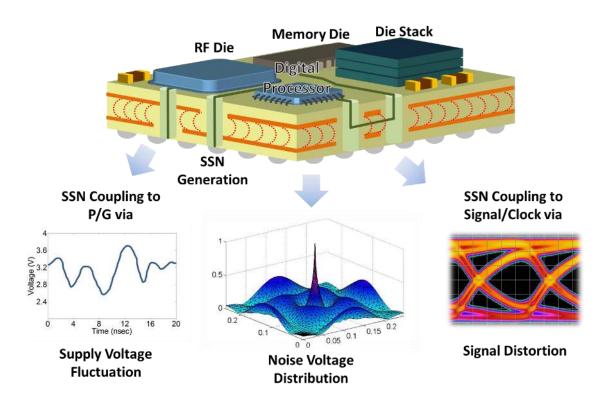

The computational efficiency of a PDN modeling and simulation is a critical factor that determines the efficiency of a design process. Figure 1.2 shows a flow chart of the typical design process for packages and PCBs. The process involves SI/PI simulations and analysis to ensure if the design at each step complies with the design rules and specifications. The original design is modified based on the simulation and analysis results, and this process persists until the simulation results satisfy the requirements. Hence, a time-consuming simulation can be a bottleneck that slows down the entire design process, and inevitably results in a long time-to-market cycle.

Figure 1.2. A part of the typical design process of electronic packages. (Modified from [7] and [8].)

# 1.2 Contributions

The major contributions of the dissertation are following:

Extension of the multilayer finite element method (MFEM) for the optimization of decoupling capacitor selection and placement using a customized genetic algorithm.

- 2) Development of a new PDN modeling method, the multilayer triangular element method (MTEM), especially effective for irregular and multidimensional structures, based on the physics-based equivalent circuit.

- 3) Modeling of the return path discontinuities created by apertures for a signal and power integrity co-simulation.

- 4) Application of the absorbing boundary condition to MTEM.

# 1.3 Organization of the Dissertation

The rest of this dissertation is organized as follows: In CHAPTER 2, the problems that will be addressed in this dissertation are defined, and the prior arts in literature are reviewed. In CHAPTER 3, the automation technique of finding optimal solutions of decoupling capacitor values and locations using the multilayer finite element method (MFEM) is presented. The development of a novel modeling method for a power/ground plane structure, the multilayer triangular element method (MTEM) is introduced in CHAPTER 4. In CHAPTER 5, port modeling is presented, and the modeling of returnpath discontinuities for the co-simulation of signal and power integrity is provided in CHAPTER 6. In CHAPTER 7, the absorbing boundary condition is presented focusing on its implementation in MTEM. Finally, summary and conclusions of this dissertation is presented in CHAPTER 8.

## **CHAPTER 2**

## ORIGIN AND HISTORY OF THE PROBLEM

# **2.1 PDN Modeling Methods**

Typical power delivery networks (PDNs) are composed of metal planes stacked on top of each other separated by low-loss insulators. Since each layer formed by metal planes with the low-loss dielectric can act as a cavity, the PDNs are highly resonant structures. To completely characterize such structures through time-domain analysis, a tremendous amount of time is required for a simulation. Hence, the frequency-domain analysis of package PDNs is more beneficial.

Electromagnetic field solvers that can emulate frequency responses of package PDNs can be classified as two folds: integral equation and differential equation solvers. Integral equation solvers include the method of moments (MoM) and the partial element equivalent circuit (PEEC) method. Since integral equation solvers require a discretization of only the sources of electromagnetic field, the size of the resultant linear system is small. However, the system matrix generated by integral equation solvers is dense, and the density increases according to the square of the problem size, resulting in high computational costs. On the other hand, differential equation solvers, such as the finite element method (FEM) and the finite difference method (FDM), generate a banded and sparse system, because elements are only locally connected. However, differential equation solvers that create volumetric meshes create sparse but impractically large systems for large-sized problems.

A package PDN consisting of planes separated by a dielectric is a planar structure. Since the thickness of a dielectric is electrically small, the field variation along the vertical direction of a power/ground plane-pair can be neglected. Therefore, a pair of power/ground planes can be modeled as a planar circuit [9], and several methods based on the planar circuit concept have been developed.

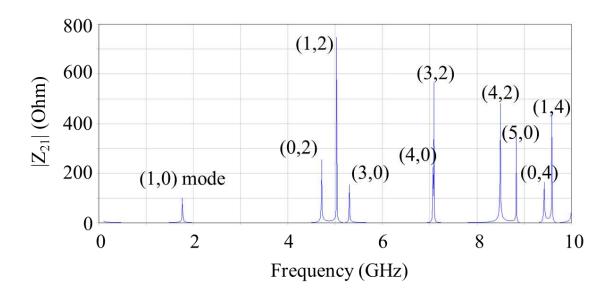

#### 2.1.1 The Cavity Resonator Model Using Segmentation Method

The cavity resonator model provides an analytic solution in the form of an impedance matrix. If a rectangular plane-pair with metal planes of dimensions  $a \times b$ , dielectric thickness d, permittivity and permeability of  $\varepsilon$  and  $\mu$ , respectively, and ports located at  $(x_i, y_i)$  and  $(x_j, y_j)$  can be calculated as

$$Z_{ij}(\omega) = j\omega\mu d \sum_{n=0}^{\infty} \sum_{m=0}^{\infty} \frac{\varepsilon_n^2 \varepsilon_m^2}{(k_{mn}^2 - k^2)ab} f(x_i, y_i, x_j, y_j), \tag{1}$$

where

$$f(x_{i}, y_{i}, x_{j}, y_{j})$$

$$= \left(\cos \frac{m\pi x_{i}}{a} \operatorname{sinc} \frac{m\pi t_{xi}}{2a}\right) \left(\cos \frac{m\pi y_{i}}{b} \operatorname{sinc} \frac{m\pi t_{yi}}{2b}\right)$$

$$\times \left(\cos \frac{m\pi x_{j}}{a} \operatorname{sinc} \frac{m\pi t_{xj}}{2a}\right) \left(\cos \frac{m\pi y_{j}}{b} \operatorname{sinc} \frac{m\pi t_{yj}}{2b}\right),$$

(2)

$t_{xi}$ ,  $t_{xj}$ ,  $t_{yi}$ , and  $t_{yj}$  are the size of the port, k is the complex wavenumber, and  $k_{mn}^2 = \left(\frac{m\pi}{a}\right)^2 + \left(\frac{n\pi}{b}\right)^2$  [10] [11].

Possible geometries that the cavity resonator model can handle are limited to simple structures, such as a square, a rectangle, or an equilateral triangle. To overcome this limit, the structure is segmented into sections that can be separately simulated by the

cavity model, and each segment is interconnected at corresponding virtual ports densely created (distance less than  $\lambda$ 10) at the segment boundaries [12] [13] [14]. However, if a given geometry is extremely irregular, the method creates too many virtual ports, consequently, the model becomes too complicated. Moreover, the double summation in Equation (1) up to a large number of modes can slow down the computation. Although acceleration techniques presented in [13] and [15] can improve the computational efficiency, the approximations associated with the techniques reduce modeling accuracy.

### 2.1.2 Modeling Methods Based on Discretization

Since the electromagnetic behavior of a plane-pair can be assumed to be two-dimensional (2D), the radial wave propagating in a plane-pair can be expressed with a 2D Helmholtz equation:

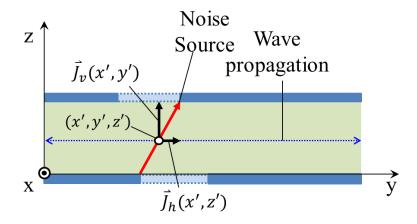

$$(\nabla_T^2 + k^2)u = j\omega\mu dJ_{z},\tag{3}$$

where  $\nabla_T^2$  represents the transverse Laplace operator parallel to the planar structures, k the wavenumber, u the voltage,  $\omega$  the angular frequency,  $\mu$  the permeability of the dielectric, d the distance between the planes, and  $J_z$  the current density at the excitation port [16]. Plane boundaries are assumed to be a magnetic wall, or an open circuit, which can be described by the Neumann boundary condition.

The governing equation, Equation (3), can be solved by applying the finite difference (FDM) or the finite element methods (FEM), which will be presented in the following sections.

#### 2.1.2.1 Transmission Matrix Method (TMM)

The transmission matrix method (TMM) [17] is a 2D modeling method that solves the equivalent circuit of a plane-pair analyzed as a planar circuit. A plane-pair is segmented into square unit-cells, which are converted to the transmission matrices. By solving the cascaded transmission matrices, TMM can solve the equivalent circuit with less computational effort than that required for a general SPICE solver. However, TMM is not applicable for multiple plane-pairs with a gap or an aperture, since the cascading property prevents the inclusion of coupling elements between neighboring cells [18].

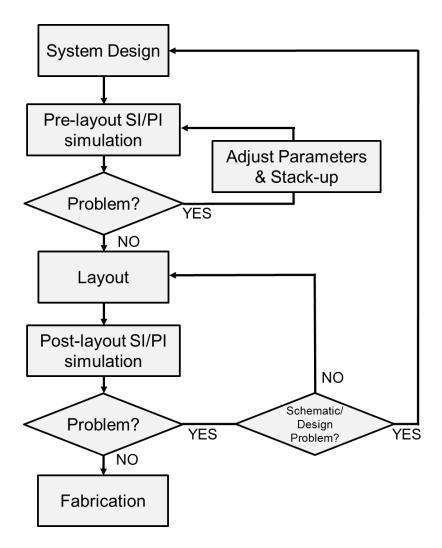

## 2.1.2.2 The Finite Difference Method (FDM)

By applying the central difference method, the transverse Laplace operator in Equation (3) is approximated as

$$\nabla_{\mathbf{T}}^{2} u_{i,j} = \frac{u_{i,j+1} + u_{i+1,j} + u_{i,j-1} + u_{i-1,j} - 4u_{i,j}}{h^{2}},\tag{4}$$

where h is the central distance between the neighboring cells, and  $u_{i,j}$  is the voltage at node (i,j). Substituting Equation (4) into Equation (3) leads to

$$\frac{u_{i,j+1} + u_{i+1,j} + u_{i,j-1} + u_{i-1,j} - 4u_{i,j}}{-j\omega L} + j\omega C u_{i,j} = I,$$

(5)

where  $C = \frac{\varepsilon h^2}{d}$ ,  $L = \mu d$ , and I is the current source injected into the cell. Since Equation (5) can be represented by the equivalent circuit as shown in Figure 2.1, a standard circuit solver based on the modified nodal analysis approach can be used for the computation. However, a direct solution of a matrix form,  $\overline{Y}\overline{U} = \overline{I}$ , using linear equations is computationally more beneficial, because the resultant system matrix,  $\overline{Y}$ , is sparse and

banded. If a nested dissection method is used, FDM can solve a system with N unknowns in  $O(N^{1.5})$  time and  $O(N \log_2 \sqrt{N})$  memory [19].

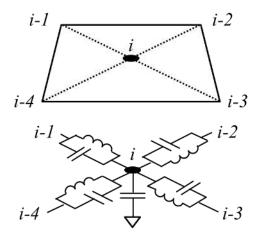

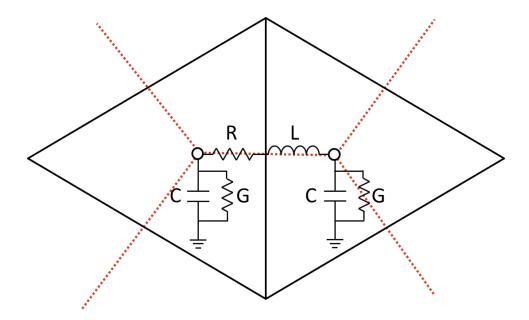

Figure 2.1. Cell-centered discretization of the Laplace operator and the equivalent circuit of FDM.

Including the computational efficiency, FDM has advantages of the ease of implementation, the capability of an equivalent circuit representation, and the application of wide range of shapes. However, this method discretizes surfaces with a square or a rectangular grid, which tend to create too many unit cells for a multidimensional structure that is common in the package PDN. Furthermore, if a structure is geometrically irregular, it is difficult to effectively discretize the structure with a square/rectangular mesh.

# 2.1.2.3 The Finite Element Method (FEM)

FEM is another approach that applies Equation (3) to each of the discretized segments and solve for the potential, u. For 2D problems, these segments are usually in the form of triangles or rectangles. In [20], FEM applied to a power/ground plane structure is presented using a non-uniform triangular mesh. The weak form of Equation (3) is expressed as

$$\sum \iint_{\Omega} (\nabla \phi_p \cdot \nabla \phi_q + \omega^2 \mu \varepsilon \phi_p \phi_q + j \omega \mu dJ_z \phi_p) dx dy = 0, \tag{6}$$

with linear pyramid basis functions, where  $\Omega$  is the problem domain, and  $\phi_p$  and  $\phi_q$  are the basis and test functions, respectively. After some derivations, the solution of Equation (6) can be obtained by solving linear equations,

$$\left(\overline{K} + \overline{M}\right)\overline{U} = \overline{F},\tag{7}$$

where the entries of  $\overline{\overline{K}}$  and  $\overline{\overline{M}}$  are

$$k_{p,q} = \frac{j}{\omega u d} \frac{b_p b_q + c_p c_q}{4\Delta},\tag{8}$$

$$m_{p,q} = \begin{cases} \frac{\Delta j\omega\varepsilon}{6}, p = q\\ \frac{\Delta j\omega\varepsilon}{12}, p \neq q. \end{cases}$$

(9)

From the mathematical properties of Equations (8) and (9), Equation (6) can be represented by an equivalent circuit using lumped elements as shown in Figure 2.2.

Figure 2.2. Equivalent circuit representation of a plane-pair using FEM (lower plane is not shown).

FEM can utilize a non-uniform triangular mesh scheme, which can effectively discretize multidimensional and extremely irregular geometries. In addition, FEM generates a sparse system, which promises an efficient computation. On the other hand, one of the disadvantages of FEM lies in the difficulty of implementation. Another disadvantage arises from the equivalent circuit representation for a power/ground planepair. The values of the lumped elements, Equations (8) and (9), are derived from not only physical properties of a simplex, but also mathematical formulations of FEM. Thus, the further extension of the model, such as the inclusion of external circuit models, is complicated and not physically intuitive.

## 2.1.3 Overview of Computational Electromagnetic Modeling Methods

Various electromagnetic modeling methods are available as commercial software as well as described in the literature. Each modeling method has its own strengths and weaknesses over another.

Table 1 summarizes and compares mesh and computational efficiency of various computational electromagnetic modeling methods. The selected methods include differential-equations, analytical solutions, and planar circuit methods. The comparison of the computational efficiency is based on the size and density of the system matrix.

Table 1. Comparison of computational electromagnetic modeling methods.

| Category                                               | Method                 | Discretization               | Mesh Efficiency                                                     | Computational<br>Efficiency                            |

|--------------------------------------------------------|------------------------|------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|

| 3D Full-<br>Wave                                       | FDM                    | Tetrahedron or<br>Hexahedron | Inefficient for planar structures                                   | Not good<br>(sparse but large<br>system)               |

|                                                        | FEM                    |                              |                                                                     |                                                        |

|                                                        | MoM                    |                              |                                                                     | Not good<br>(small but dense<br>system)                |

| Planar<br>Circuit<br>Model<br>(Analytical<br>Solution) | Cavity<br>Resonator    | -                            | -                                                                   | Good for solid rectangle/triangle                      |

|                                                        | Segmentation<br>Method | Virtual Ports                | Not good for irregular geometries (creating too many virtual ports) | Not good for irregular or multi-dimensional structures |

| Planar<br>Circuit<br>Model<br>(Numerical<br>Solution)  | TMM                    | Rectangle                    | Inefficient for irregular geometries                                | Good                                                   |

|                                                        | MFDM                   | Rectangle                    | Not good for multi-<br>dimensional<br>structures                    | Good                                                   |

|                                                        | MFEM                   | Triangle                     | Good                                                                | Good                                                   |

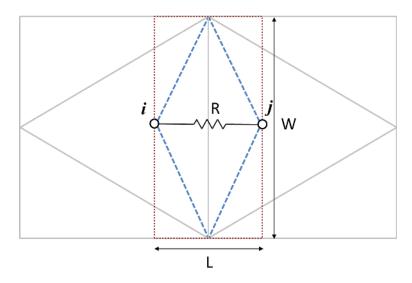

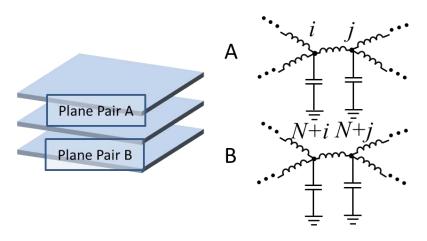

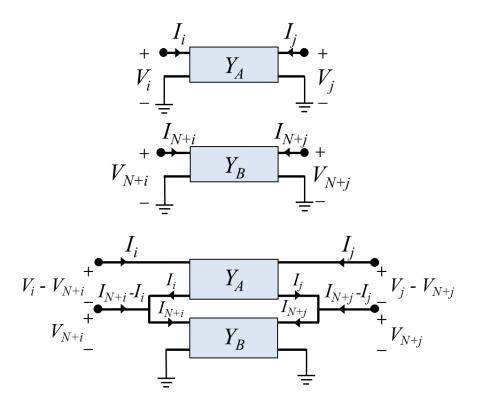

# 2.2 Extension to Multiple Plane-Pairs

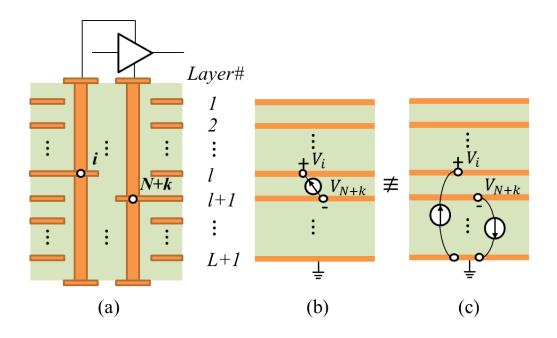

The differential equation methods, FDM and FEM, are expressed as an equivalent circuit using only passive lumped elements and independent current sources. To extend a single plain-pair to multiple plane-pairs, the equivalent circuit of each plane-pair can be stacked on top of each other. However, the simple interconnection of equivalent circuits will fail to take into account different references of each plane-pair, and the resultant model will be completely incorrect. Therefore, the reference of each plane-pair must be shifted to a global reference of multiple plane-pairs, and the shift of a reference can be realized using indefinite admittance matrices [21].

The multilayer finite difference method (MFDM) [22] and the multilayer finite element method (MFEM) [20] utilize the technique of the indefinite admittance matrix to extend a single plane-pair to multiple plane-pairs. This approach, shifting reference nodes, can be applied to any modeling scheme that can be expressed as an equivalent circuit composed of only passive elements and independent sources.

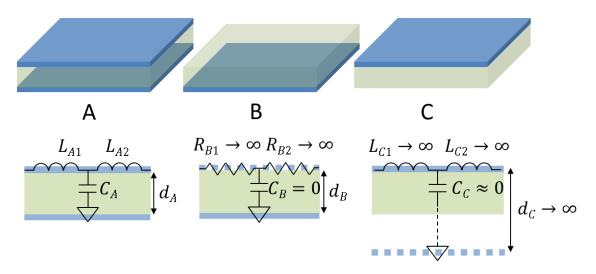

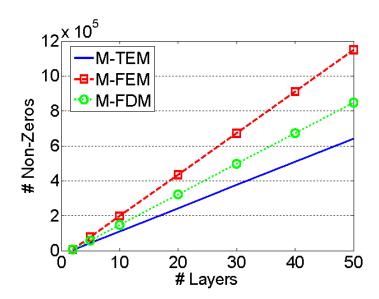

Consider the unit cell model shown in Figure 2.3 (a), which can be decomposed into two plane-pairs as shown in Figure 2.3 (b). The inductance and capacitance models are shown in Figure 2.3 (b) and (c).  $L_{12}$  and  $L_{34}$  are per unit cell inductances for each plane-pair that can be obtained from Equation (34). Assuming the plane 3 is the system reference, the indefinite admittance matrices for the top and bottom plane-pairs can be derived as follows:

$$\begin{bmatrix} I_1 \\ I_2 \\ I_3 \\ I_4 \end{bmatrix} = \begin{bmatrix} Y_1 & -Y_1 & -Y_1 & Y_1 \\ -Y_1 & Y_1 & Y_1 & -Y_1 \\ -Y_1 & Y_1 & Y_1 & -Y_1 \\ Y_1 & -Y_1 & -Y_1 & Y_1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \\ V_3 \\ V_4 \end{bmatrix}, \tag{10}$$

$$\begin{bmatrix} I_3 \\ I_4 \end{bmatrix} = \begin{bmatrix} Y_2 & -Y_2 \\ -Y_2 & Y_2 \end{bmatrix} \begin{bmatrix} V_3 \\ V_4 \end{bmatrix}, \tag{11}$$

where  $Y_1 = \frac{1}{j\omega L_{12}}$  and  $Y_2 = \frac{1}{j\omega L_{34}}$ . Similarly, an admittance matrix for capacitance between planes is obtained as follows:

$$\begin{bmatrix}

I_1 \\

I_2 \\

I_3 \\

I_4

\end{bmatrix} = \begin{bmatrix}

Y_{C1} & 0 & -Y_{C1} & 0 \\

0 & Y_{C1} & 0 & -Y_{C1} \\

-Y_{C1} & 0 & Y_{C1} + Y_{C2} & 0 \\

0 & -Y_{C1} & 0 & Y_{C1} + Y_{C2}

\end{bmatrix} \begin{bmatrix}

V_1 \\

V_2 \\

V_3 \\

V_4

\end{bmatrix}, (12)$$

where  $Y_{C1} = j\omega C_1$  and  $Y_{C2} = j\omega C_2$ . Loss terms are omitted in both models for simplification. Finally, superimposing all the indefinite admittance matrices, Equations (10), (11), and (12), completes the total admittance matrix for the given three-layered structure:

$$\begin{bmatrix} Y_{C1} + Y_1 & -Y_1 & -Y_{C1} - Y_1 & Y_1 \\ -Y_1 & Y_{C1} + Y_1 & Y_1 & -Y_{C1} - Y_1 \\ -Y_{C1} - Y_1 & Y_1 & Y_{C1} + Y_{C2} + Y_1 + Y_2 & -Y_1 - Y_2 \\ Y_1 & -Y_{C1} - Y_1 & -Y_1 - Y_2 & Y_{C1} + Y_{C2} + Y_1 + Y_2 \end{bmatrix}.$$

(13)

Figure 2.3. (a) Cross-section of a three-layer structure. The equivalent (b) inductance and (c) capacitance model.

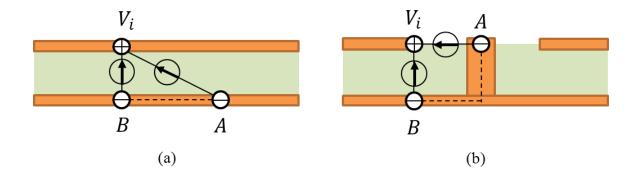

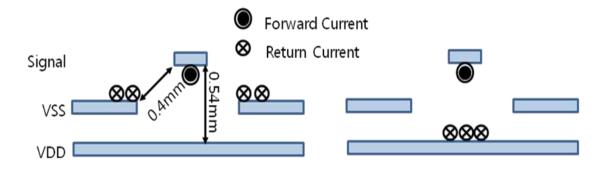

# 2.3 Incorporation of Signal Interconnects into the PDN

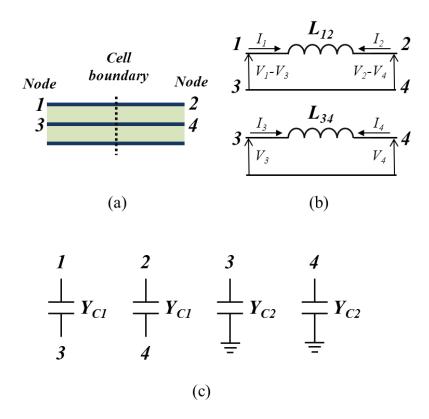

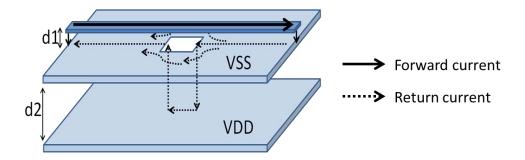

In a package and printed circuit board (PCB), the signal interconnects, such as copper traces and vias, link drivers and receiver circuits placed on the PDN. Metal planes in the PDN provide the paths for the return current of the signal interconnects. Power and ground planes typically contain many discontinuities such as plane cut-outs, split planes, and via anti-pads as shown in Figure 2.4 (a). On those metal planes with discontinuities, signal traces are placed as shown in Figure 2.4 (b). If a current-return path of a signal transmission line is discontinuous, the field distribution changes at the discontinuity and mode conversion occurs, which results in the distortion of the signal. Moreover, the mode

conversion can excite the cavity created by the power and ground planes and leads to a plane resonance, causing fluctuation of supply voltage. A discontinuity of this type along a signal interconnect is called as return path discontinuity (RPD).

Figure 2.4. Layout of (a) power and ground planes and (b) signal interconnects. (Courtesy of class notes for Purdue University ECE477, Spring 2009.)

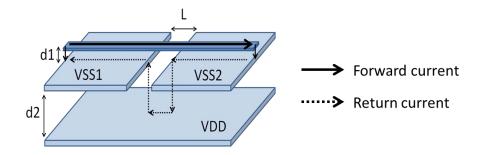

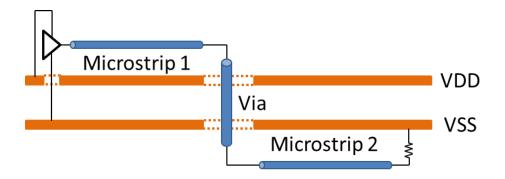

The electrical behavior at the RPDs can be explained using an example, a microstrip line placed above a slotted power plane as shown in Figure 2.5 (a). At the discontinuity, return current switches layer from power to ground plane and vice versa to complete the closed current loop. Current jumps from one layer to another as displacement current that is caused by the stray capacitance between the layers. Hence, the propagation mode of the microstrip line at the discontinuity changes from its original form to another, leading to the change of characteristic impedance and effective dielectric constant. In addition, the displacement current excites the plane-pair created by power

and ground planes, and may result in a plane resonance that causes the fluctuation of supply power. The plane resonance can also deteriorate the signal transmission, since the high impedance of the PDN at anti-resonant frequencies impedes the flow of return current. A similar effect is observed at the RPD created by a via anti-pad (clearance hole) as shown in Figure 2.5 (b). Therefore, in a package or PCB system, the electrical behaviors of the PDN and the signal interconnects are closely coupled, and their interactions must be included in simulations.

Figure 2.5. Current loops created at the return path discontinuities created by (a) slot and (b) via transition.

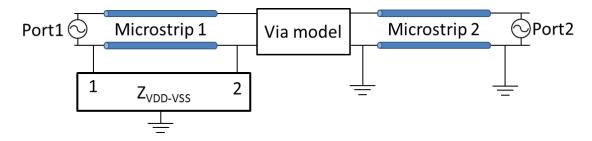

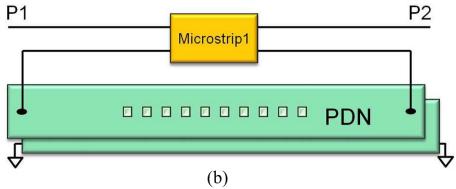

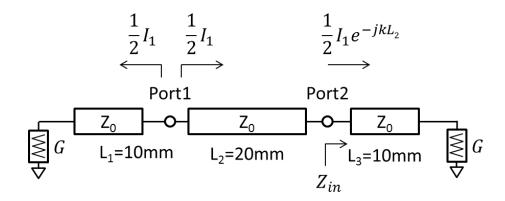

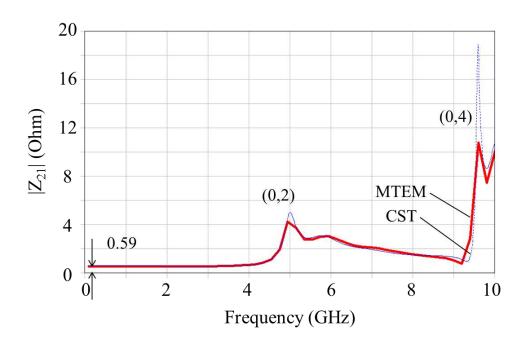

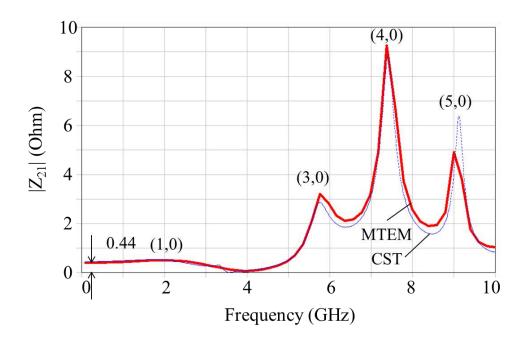

One of the methods to co-simulate the PDN and the signal interconnects is to model each domain separately and re-integrate using a modal decomposition technique, which was exploited in many articles or publications [4] [5] [23] [24] [25]. The PDN can be modeled using any analysis method that can provide the impedance profile of a given PDN, and the signal interconnects can be characterized by transmission line parameters, such as characteristic impedance, effective dielectric constant, and the electrical length.

The decoupled models are re-integrated by superimposing the admittance matrices of each model.

The co-simulation of a PDN and signal interconnects requires the accurate modeling of an RPD where mode conversions occur. Thus, to model an RPD, the thorough understanding and the analysis of the electromagnetic behaviors at the discontinuities need to precede.

A number of papers that describe and analyze RPDs have been published in recent decades. A microstrip line over a thin slot is analyzed in [26], and the impact of the plane gap RPD is shown in [27]. In [28], the difference between slot-induced and an aperture-induced RPDs is studied, and in [29], the coupling of ground bouncing through an aperture is investigated in time-domain modeling and simulations. The impact of a slot on the differential signaling and the coupling between the signal and the power plane are presented in [30]. Although the previous papers show analysis and modeling of RPDs, thorough analysis on the physics behind the different types and sizes of RPDs in the presence of the PDN is lacking in the literature.

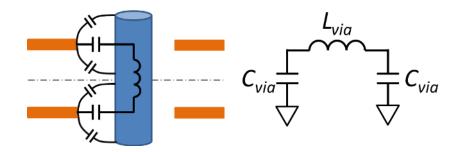

The RPD can also be created by a through-hole via which is widely used for vertical interconnections in package and board systems. The modeling of a via structure and the coupling between a via and a plane has been vigorously investigated and published [31] [32] [33] [34] [35] [36]. Any physical modeling method for a via can be incorporated into the modal decomposition technique for the modeling of the RPD of a via structure in consideration of the via-plate coupling.

## 2.4 Selection and Placement of Decoupling Capacitors

The main purpose of a PDN is to deliver electric current to the switching circuits from the voltage regulator module. Thus, maintaining low impedance for a PDN is necessary for a stable supply of desired voltage. The required impedance of a PDN is called the target impedance, which is calculated as [6]

$$Z_{tar} = \frac{Supply \, Voltage \times Allowed \, Ripple}{Current}.$$

(14)

A practical choice of the allowed ripple is usually 5% of the supply voltage ( $V_{dd}$ ), and the current (an average current drawn by the switching circuit) is assumed to be the half of the maximum current.

The conventional method to meet the target impedance is to place decoupling capacitors between power and ground nets of a PDN. However, since a decoupling capacitor behaves like an inductor at the frequencies above its self-resonance frequency, the accumulated behavior of decoupling capacitors eventually increases the PDN impedance at high frequencies. Moreover, the decoupling capacitor technique becomes ever challenging as the required target impedance continues to decrease as shown in Table 2. Therefore, selection and placement of hundreds and thousands of decoupling capacitors to meet the challenging target impedance across the wide-range of frequencies is a time consuming and cumbersome task.

Table 2. Target impedance trend [37].

| Year | Feature Size (nm) | Power (W) | V <sub>dd</sub> (V) | Current (A) | Target Impedance $(m\Omega)$ |

|------|-------------------|-----------|---------------------|-------------|------------------------------|

| 2009 | 52                | 143       | 0.95                | 151         | 0.63                         |

| 2011 | 36                | 161       | 0.72                | 224         | 0.32                         |

| 2013 | 28                | 149       | 0.67                | 222         | 0.30                         |

| 2015 | 23                | 143       | 0.63                | 227         | 0.28                         |

| 2018 | 16                | 136       | 0.57                | 239         | 0.24                         |

Searching for the locations and values of decoupling capacitors can be automated by applying an optimization algorithm. The process of finding optimal locations and values for decoupling capacitors that satisfy target impedance is a multi-dimensional combinatorial problem, since the solution is not unique. In addition, since candidate solutions are mutually independent, finding a solution through exhaustive search (generate and test) is infeasible. Therefore, finding optimal solutions for decoupling capacitor locations and values is a combinatorial optimization, which can be solved by metaheuristics such as simulated annealing [38], genetic algorithm [39], and swarm intelligence [40]. Among many metaheuristics, the genetic algorithm (GA) is an effective technique that finds a quality solution from a very large number of possible solutions [41]. Unlike other methods, GA can operate in parallel, and can search for an optimal solution using only small number of candidate solutions as explained in Holland's schema theorem [39].

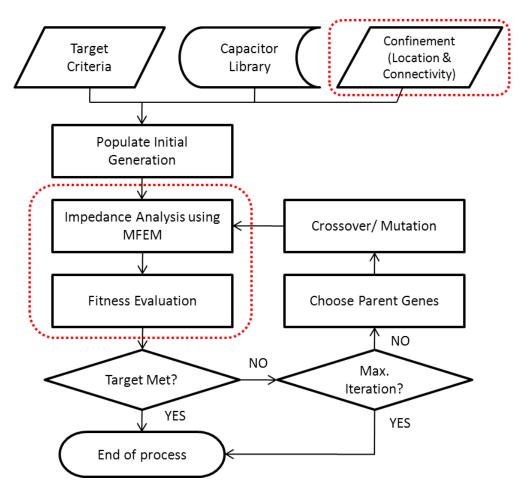

A flow chart of the typical GA process is shown in Figure 2.6 [42], and MFDM is used to obtain the PDN impedance profile. As explained in Section 2.1.2.1, the FDM is not optimal for complex and multidimensional geometries, which prevail in modern

packages. In [15] and [43], the authors employ a cavity resonator model in combination of the GA. The cavity resonator model in the paper does not handle multiple plane-pairs, and is limited to simple rectangular planes. In addition, optimization algorithms in [15], [42], and [43] use the general GA that is not customized for the decoupling capacitor problem. Thus, if the GA is combined with the decoupling capacitor placement techniques, which are presented in [5] [44] [45] [46] [47] and [48], further improvement of the convergence speed can be achieved.

Figure 2.6. A flow chart of the typical optimization procedures of decoupling capacitor selection and placement using the GA [42].

# **CHAPTER 3**

# OPTIMIZATION OF DECOUPLING CAPACITOR SELECTION AND PLACEMENT USING MFEM

#### 3.1 Introduction

This chapter presents the extension of the plane-pair modeling method, the multilayer finite element method (MFEM) [20], to include external circuit elements into the plane-pair model. The inclusion of the external circuit element enables MFEM to be applied to the automation of decoupling capacitor selection and placement. The automation employs a selected optimization engine, the genetic algorithm (GA), which is further customized for the decoupling problem to enhance the performance.

#### 3.2 Extension of MFEM

Since the equivalent circuit of MFEM is extracted from mathematical formulations, the circuit model does not directly interpret the physical properties of the PDN. Thus, the incorporation of external circuits into MFEM requires modifications of the external circuit model. This section describes the incorporation method of the decoupling capacitor model into MFEM.

## **3.2.1** Formulation of Capacitive Elements in MFEM

A standard finite-element approximation with a triangular mesh and linear pyramid basis functions is given in Equation (6), and its matrix form is Equation (7). The admittance matrix,  $\overline{\overline{M}}$ , represents capacitive components, and its entries are

$$m_{p,q} = \iint_{\Omega} \frac{j\omega\varepsilon}{d} \phi_p \phi_q \, dx \, dy. \tag{15}$$

For simplicity, the Cartesian coordinates are converted to simplex coordinates  $\{L1, L2, L3\}$  [49] to obtain

$$L_p = \frac{1}{2\Delta} (a_p + b_p x + c_p y), \tag{16}$$

$$a_p = x_{p+1} y_{p+2} - x_{p+2} y_{p+1}, (17)$$

$$b_p = y_{p+1} - y_{p-1}, (18)$$

$$c_p = x_{p-1} - x_{p+1}, (19)$$

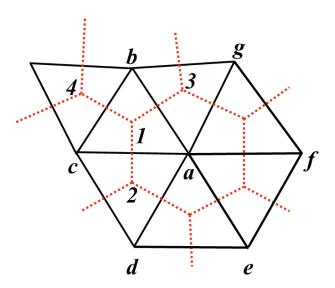

where  $\Delta$  is the area of the triangle with vertices at p-1, p, and p+1, and the subscripts are evaluated (modulo 3) + 1, which circulate at multiples of three. Notice that the integrals in Equation (15) are in the form of

$$I = \iint_{0} L_{1}^{a} L_{2}^{b} L_{3}^{c} dL_{1} dL_{2} = \frac{a! \, b! \, c!}{(a+b+c+2)!},\tag{20}$$

where a, b, and c are integer powers [49]. Therefore, the substitutions of a=2, b=0, and c=0 when i=j, and a=1, b=1, and c=0 when  $i\neq j$  in Equation (20), and the use of Equations (16) - (19) and the Jacobian,

$$dxdy = dL_1 dL_2 \frac{\partial(x, y)}{\partial(L_1, L_2)} = 2\Delta dL_1 L_2, \tag{21}$$

transform Equation (15) to simplex coordinates as follows:

$$m_{p,q} = \begin{cases} \frac{\Delta j\omega\varepsilon}{6}, p = q\\ \frac{\Delta j\omega\varepsilon}{12}, p \neq q. \end{cases}$$

(22)

### 3.2.2 Inclusion of the Decoupling Capacitor Model to MFEM

To comprehend the way to connect the decoupling capacitor model to the plane-pair model of MFEM, one must understand how vertical components of a plane-pair are represented in the system matrix. As shown in Equation (22), the value of the vertical component is decomposed into two different values for matrix representation: 1/6 and 1/12 of the original value. The reason for decomposition into the particular fractions stems from the nature of simplex coordinates (Equations (16)-(21)). Similarly, if a vertical circuit element is to be added to the system, its admittance must be decomposed into two different values as in Equation (22). Then, each value is added to the appropriate locations in the system matrix. For instance, the admittance of a decoupling capacitor can be represented as

$$Y_{decap} = \frac{1}{\left(\frac{1}{j\omega C_{decap}} + j\omega ESL + ESR\right)'}$$

(23)

where  $C_{decap}$  is capacitance, ESL is equivalent series inductance, and ESR is equivalent series resistance of the decoupling capacitor. Next, the admittance is decomposed into 1/6 and 1/12 of the original value:

$$m_{p,q}^{decap} = \begin{cases} \frac{1}{6} Y_{decap}, & p = q \\ \frac{1}{12} Y_{decap}, & p \neq q \end{cases}, \tag{24}$$

where p and q are the vertices of a selected unit triangle of a mesh. Finally, the 1/6 of the admittance is added to the diagonal locations, and the 1/12 to the off-diagonal locations of the system matrix.

## 3.3 Test Cases and Results

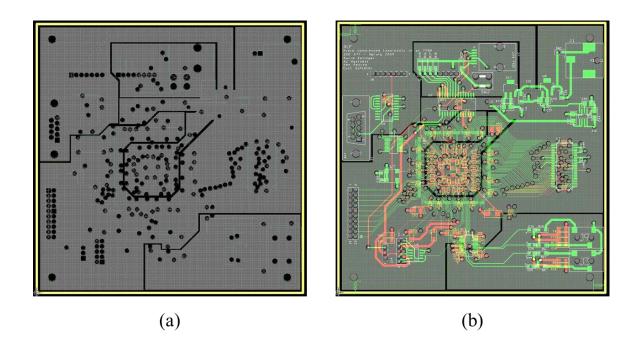

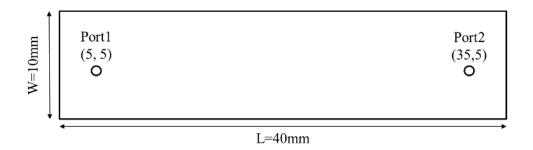

To verify the incorporation of the decoupling capacitor model into MFEM, a test vehicle, which has two metal plane layers with five ports, is created. The dielectric material is FR-4, with a relative permittivity of 4.5, a loss tangent of 0.025, and a thickness of 355 µm. The actual test vehicle and the top view of the structure with its dimensions are shown in Figure 3.1.

Figure 3.1. Top view of the test vehicle with decoupling capacitors (left) and the dimensions and the port locations (right). (Test vehicle provided by Sony Corp., Tokyo, Japan)

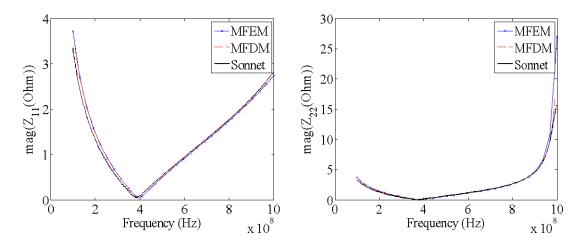

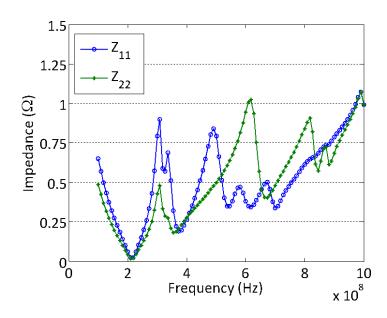

Before examining the results with decoupling capacitors, software simulations were performed for the bare planes without capacitors. Figure 3.2 shows the self-impedance results at port 1 and 2. With MFDM and Sonnet software [50] as references, the results from the three simulations show good correlations.

Figure 3.2. Self-impedance responses at port 1 and 2 of the test vehicle without decoupling capacitors.

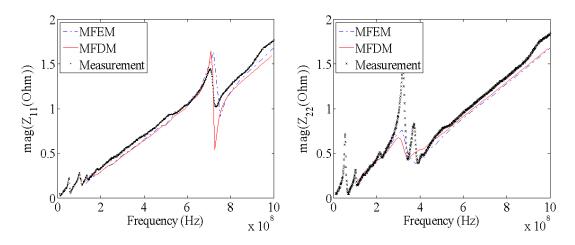

Next, decoupling capacitors were placed on the bare planes to reduce the self-impedances at the ports, and the target impedance was set at 1.5  $\Omega$  at all the ports over the frequency range of 100 MHz to 1 GHz. The GA optimizer randomly selected 55 capacitors from a given library that had twenty different capacitors with their ESL and ESR values, and placed them on the defined regions on the planes. The capacitance values ranged from 680 nF to 33 pF, and ESL and ESR ranged from 0.1 nH to 0.82 nH and from 0.04  $\Omega$  to 3  $\Omega$ , respectively. The inductance of the vias used for decoupling capacitor connection was 0.3 nH, which was calculated by a 3-D inductance extraction tool [51]. Hence, the effective series resonance frequencies of the used capacitors were calculated to be from 20 MHz to 1 GHz.

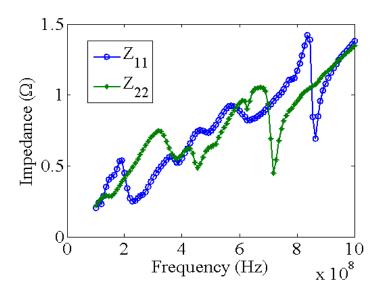

The measured self-impedance curves at ports 1 and 2 are depicted in Figure 3.3 along with results from MFDM and MFEM simulations. Figure 3.4 compares the generated meshes for MFDM and MFEM for the test vehicle with decoupling capacitors. To capture small dimensions of the decoupling capacitors, MFDM had to create

numerous square unit-cells all over the plane, while MFEM effectively discretized the multi-scale structures using non-uniform triangles. As a result, MFEM resulted in far fewer unknowns (around 3,300) than MFDM (around 8,000). The resonance and anti-resonance frequencies match, and the level of impedances are in good correlation over the frequency range of interest.

Figure 3.3. Self-impedance responses at port 1 and 2 of the test vehicle with decoupling capacitors.

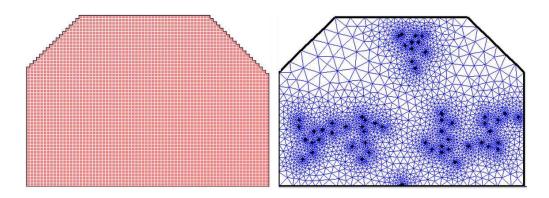

Figure 3.4. Comparison of mesh generations of MFDM (left) and MFEM (right) for the test vehicle with decoupling capacitors.

Some deviation in measurements, especially the anti-resonance peaks at port 2, resulted from the relatively large probe inductance compared to the PDN impedance. Thus, the transfer-impedance can provide a much more accurate result than the self-impedance, especially for a PDN with moderate impedance [5]. However, in this paper only one-port measurements were conducted due to limited probe accessibility. The impedance exceeded the target impedance (at  $1.5~\Omega$ ) at high frequencies because some decoupling capacitors located too close to the ports were removed for measurement probe access. Since the corresponding capacitors were also removed from MFEM, the model and the hardware are based on the same structure. Therefore, the provided measurement and simulation results validate the accuracy of the model incorporating decoupling capacitors into MFEM.

# 3.4 The Decoupling Optimization Using Genetic Algorithm (GA)

Manually selecting and placing hundreds to thousands of decoupling capacitors on a PDN to meet the target impedance require a considerable amount of time and effort. Such a complex task can be automated using an algorithm that eventually provides an optimized solution. A GA is suitable for the optimization of the decoupling capacitor selection and placement, since the GA is robust and effective in solving complex, combinational, and related problems [41].

A GA is based on the concepts of natural selection and evolution [39]; it exploits the ideas from evolutionary biology such as population, crossover, selection, mutation, and substitution. Thus, for the decoupling capacitor optimization, the data of the decoupling capacitor locations and their types (e.g., capacitance, ESL, ESR) are

analogous to genes on a chromosome. Each chromosome can contain the following information: capacitor indices, x- and y-locations, layer connectivity, cost, and physical size of the capacitor. These values are randomly generated at the beginning of the optimization for the determined number of chromosomes (population).

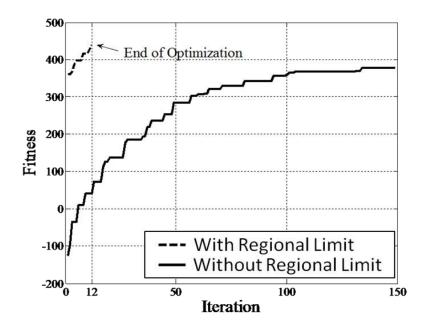

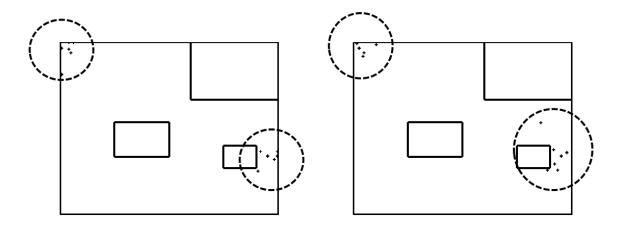

Once the chromosomes are initially generated, the core engine is run to produce impedance profiles including the decoupling capacitor data acquired from each chromosome. Once the impedance profiles are obtained, each result is subjected to a quality evaluation using a fitness function that quantifies the optimality of a solution to the target. Thus, it is critical that the fitness function be closely related to the solution and be computed quickly. The goal for the optimization is to minimize the difference between the acquired impedance and the target impedance at a port:

$$F(\bar{x}) = |Z(\bar{x})| - Z_{tar},\tag{25}$$

where  $Z(\bar{x})$  is the obtained impedance with variables  $\bar{x}$ , which may contain values, locations, and cost for each decoupling capacitor, and  $Z_{tar}$  is the target impedance (Equation (14)). Although the lower the PDN impedance the better, overachievement will cost unnecessary decoupling capacitors. Therefore, by accounting for the optimal achievement of the target impedance, the fitness function in Equation (25) can be defined for the number of ports and frequencies as follows:

$$fitness = \sum_{i=1}^{Nport} \left( \sum_{k=1}^{Nfreq} \left( \left( Z_{tar,i} - Z_{i,i}(\bar{x},k) \right) \sum \left( Z_{tar,i} > Z_{i,i}(\bar{x},k) \right) - \left( Z_{i,i}(\bar{x},k) - Z_{tar,i} \right) \sum \left( Z_{tar,i} < Z_{i,i}(\bar{x},k) \right) \right) \right), \quad (26)$$

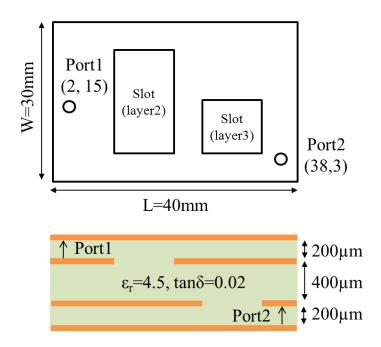

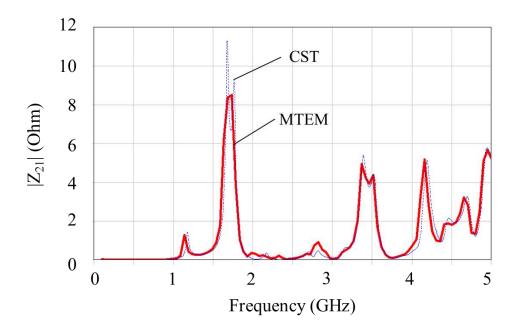

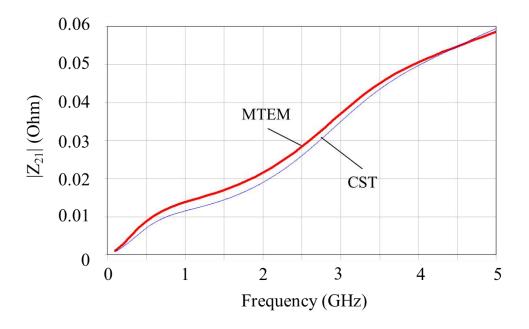

where  $Z_{tar,i}$  represents the target impedance at  $i^{th}$  port, and  $Z_{i,i}(k)$  is the self-impedance of  $i^{th}$  port at frequency k.