# MODELING AND SIMULATION OF SILICON INTERPOSERS FOR 3-D INTEGRATED SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Biancun Xie

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology Aug. 2015

**COPYRIGHT ©2015 BY BIANCUN XIE**

# MODELING AND SIMULATION OF SILICON INTERPOSER FOR 3-D INTEGRATED SYSTEMS

## Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Sung Kyu Lim School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Alenka Zajic School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Andrew F Peterson School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Suresh Sitaraman School of Mechanical Engineering Georgia Institute of Technology

Date Approved: Nov. 12<sup>th</sup> 2014

## **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all the people who inspired and helped me during my study in Georgia Tech. This dissertation would not been possible without their supports.

First and foremost being Prof. Madhavan Swaminathan, my academic advisor, who gives me the precious opportunity to work on the cutting-edge research in EPSILON group. I want to express my sincere appreciation to him. I still remember when I first joined EPSILON group four years ago, I did not have much electromagnetic background. It is his continuous support, guidance, and encouragement led to my accomplishments and this dissertation. His enthusiasm, patience in research will influence me throughout my life in the future. Also, I would like to extend my gratitude to my committee members, Prof. Andrew F. Peterson, Prof. Sung Kyu Lim, Prof. Alenka Zajic, Prof. Suresh Sitaraman, for their time and help, and their valuable feedback to the research work in this dissertation.

I would like to thank all the current and past members of the EPSILON group. Your friendship, opinions and help will always be appreciated. I am grateful to Dr. Ki Jin Han for his support and help in the early-stage of my research. I also would like to express my thanks to Dr. Jianyong Xie for spending his time on lots of technical discussions. I was fortunate to work with kind and genius colleagues who have graduated from EPSILON group – Dr. Narayanan T. V., Dr. Seunghyun Hwang, Dr. Tapobrata Bandyopadhyay, Dr. Myunghyun Ha, Dr. Suzanne Huh, Dr. Abhilash Goyal, Dr. Nithya Sankaran, Dr. Jae Yong Choi, Rishik Bazaz, Nithish Natu, Stephen Dumas. The discussions with all of you

are valuable to my Ph.D research. My thanks also go to my current colleagues: Kyu Hwan Han, Satyan Telikepalli, David Zhang, Ming Yi, Sung Joo Park, Colin Pardue, Antonio Astorino. It is fortunate for me to have so many colleagues working on various research topics and I learnt a lot from all of you.

I also would like to express my gratitude to professors with whom I took my graduate courses: Prof. G. T. Zhou who provides me lots of help during my graduate study in Georgia Tech-Shanghai dual master degree program. Prof. Biing Hwang Juang whom I had lots of discussions before I start my PhD study. Prof. Fekri Faramarz, Prof. Hongyuan Zha, Prof. Glenn S Smith, Prof. Andrew F Peterson, Prof. Hao-Min Zhou, Prof. Waymond R Scott. I learnt lots of fundamental knowledge of various subjects by taking your courses.

Finally, I owe my deepest gratitude to my family. Each time I encountered difficulty and setback, my parents are always there providing selfless love and support. All of my accomplishments throughout my life can not be achieved without the unconditional supports from my parents. This dissertation is dedicated to my parents. I wish their health and happiness.

# TABLE OF CONTENTS

|        |      |                                                            | Page |

|--------|------|------------------------------------------------------------|------|

| ACKN   | OW]  | LEDGEMENTS                                                 | iv   |

| LIST ( | OF T | ABLES                                                      | ix   |

| LIST ( | OF F | IGURES                                                     | X    |

| СНАР   | TER  | 1 INTRODUCTION                                             | 1    |

| 1.1    | Ba   | ckground                                                   | 1    |

| 1.2    | Mo   | tivation                                                   | 1    |

| 1.3    | Co   | ntributions                                                | 2    |

| 1.4    | Org  | ganization of the Dissertation                             | 4    |

| CHAP   | TER  | 2 ORIGIN AND HISTORY OF THE PROBLEM                        | 5    |

| 2.1    | Int  | roduction                                                  | 5    |

| 2.2    | Lu   | mped Element based TSV Modeling                            | 5    |

| 2.3    | Ele  | ctromagnetic Modeling of TSVs                              | 8    |

| 2.4    | MO   | OS Capacitance in TSVs                                     | 9    |

| 2.5    | Mo   | deling of RDL traces on silicon interposer                 | 11   |

| 2.6    | Teo  | chnical Focus of This Dissertation                         | 13   |

| CHAP   | TER  | 3 COUPLING ANALYSIS OF LARGE TSV ARRAYS USING              |      |

| SPECI  | ALI  | ZED BASIS FUNCTIONS                                        | 14   |

| 3.1    | Int  | roduction                                                  | 14   |

| 3.2    | TS   | V Modeling With Cylindrical Modal Basis Functions          | 16   |

| 3.     | 2.1  | Conductor Series Resistance and Inductance Extraction      | 16   |

| 3.     | 2.2  | Substrate Parallel Conductance and Capacitance Calculation | 18   |

| 3.     | 2.3  | Oxide Liner Excess Capacitance Extraction                  | 18   |

| 3.3    | Ch   | aracteristics of Coupled Waveform in TSV Array             | 20   |

| 3.4    | Eye  | e Diagram Analysis of TSV Arrays                           | 29   |

| 3.5    | Sui  | mmary                                                      | 32   |

## CHAPTER 4 MODELING OF NON-UNIFORM TSVS USING SPECIALIZED

| BASIS                                         | FUI  | NCTIONS                                                          | 34  |

|-----------------------------------------------|------|------------------------------------------------------------------|-----|

| 4.1                                           | Int  | roduction                                                        | 34  |

| 4.2                                           | Co   | nical TSV Modeling                                               | 35  |

| 4.                                            | 2.1  | Conical Conductor Series Resistance and Inductance Extraction    | 36  |

| 4.                                            | 2.2  | Substrate Conductance and Capacitance Extraction of Conical TSVs | 38  |

| 4.                                            | 2.3  | Oxide Liner Excess Capacitance Extraction of Conical TSV         | 39  |

| 4.3                                           | Sir  | nulation Results of Conical TSVs                                 | 41  |

| 4.4                                           | Mo   | odeling of Complex TSV Structures                                | 44  |

| 4.5                                           | Su   | mmary                                                            | 46  |

| CHAP                                          | TER  | 5 MODELING AND ANALYSIS OF SILICON AND GLASS                     |     |

| INTE                                          | RPOS | SER USING M-FDM AND MODAL DECOMPOSITION                          | 47  |

| 5.1                                           | Int  | roduction                                                        | 47  |

| 5.2                                           | Mo   | odeling of PDN Containing TSVs/Through-Glass-Vias                | 48  |

| 5.                                            | 2.1  | Modeling of Planes in Silicon Interposer                         | 48  |

| 5.2.2 Integration of TSVs/TGVs and P/G planes |      | Integration of TSVs/TGVs and P/G planes                          | 52  |

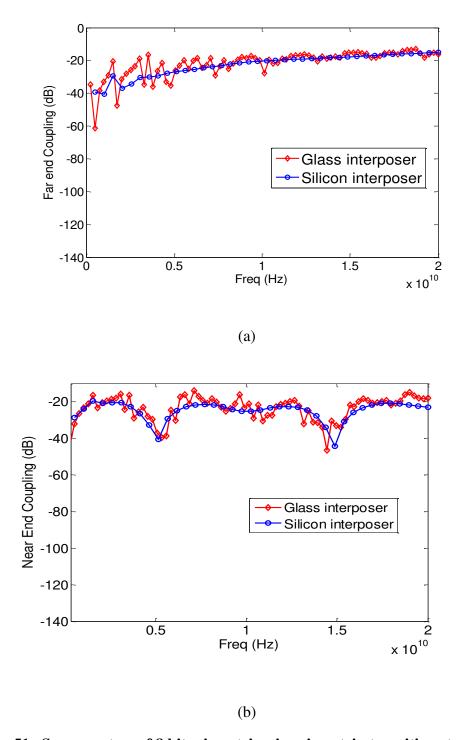

| 5.3                                           | Vi   | a Coupling Effects                                               | 55  |

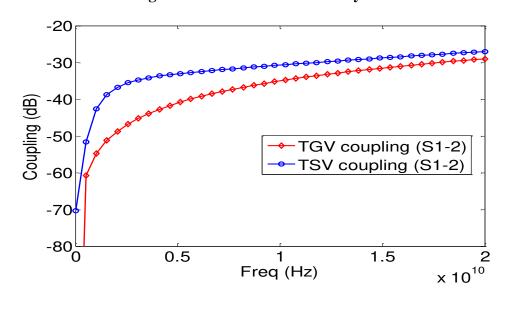

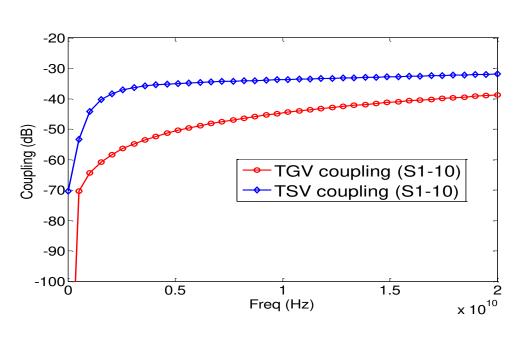

| 5.                                            | 3.1  | TSVs and TGVs Coupling Effects                                   | 55  |

| 5.                                            | 3.2  | TSVs/TGVs Coupling Effects with P/G Planes Included              | 57  |

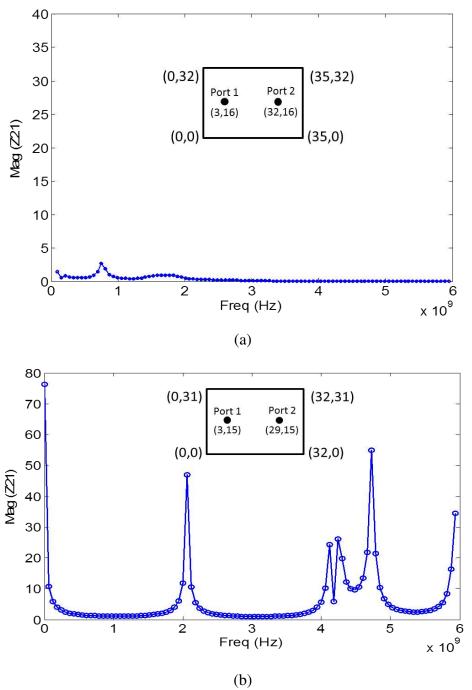

| 5.4                                           | SS   | N Comparison Between Silicon and Glass Interposer                | 60  |

| 5.5                                           | Su   | mmary                                                            | 63  |

| CHAP                                          | TER  | 6 FDFD MODELING OF SIGNAL PATHS WITH TSVS IN SILIC               | CON |

| INTE                                          | RPOS | SER                                                              | 65  |

| 6.1                                           | Int  | roduction                                                        | 65  |

| 6.2                                           | Mo   | odeling of signal paths in silicon interposer                    | 66  |

| 6.                                            | 2.1  | Modeling of Multiple RDL Traces on Lossy Silicon Interposer      | 66  |

| 6.                                            | 2.2  | Integration of TSVs and RDL traces                               | 68  |

| 6.3                                           | Di   | vide-and-Conquer Method                                          | 71  |

| 6.4                                           | Nu   | merical Examples                                                 | 75  |

| 6.5  | Summary                                                                    | 85  |

|------|----------------------------------------------------------------------------|-----|

| CHAP | TER 7 FDFD NON-CONFORMAL DOMAIN DECOMPOSITION FOR                          |     |

| MODE | LING OF INTERCONNECTIONS IN SILICON INTERPOSER                             | 87  |

| 7.1  | Introduction                                                               | 87  |

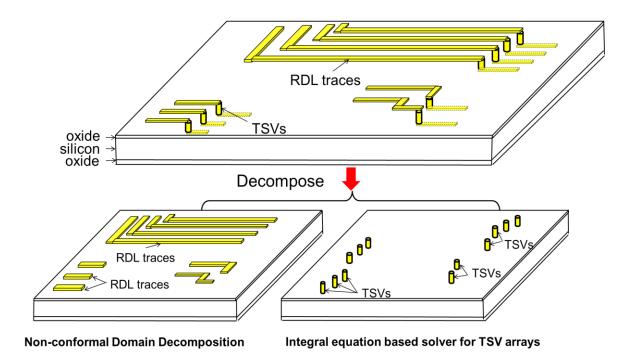

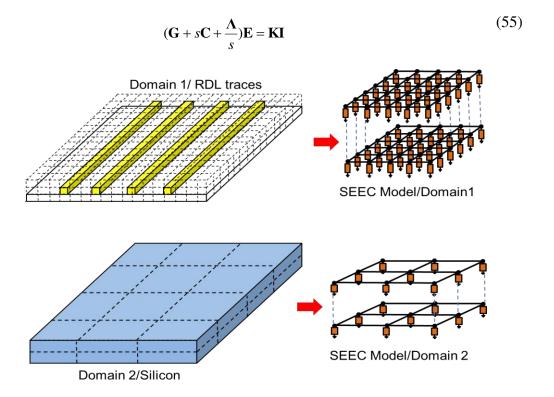

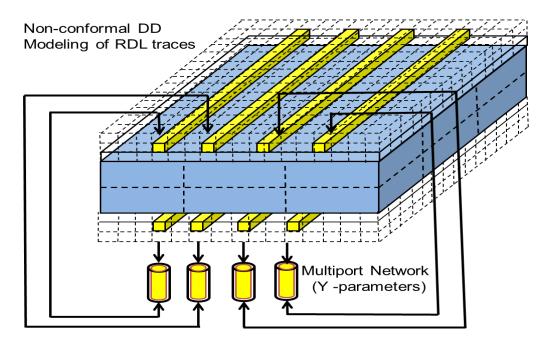

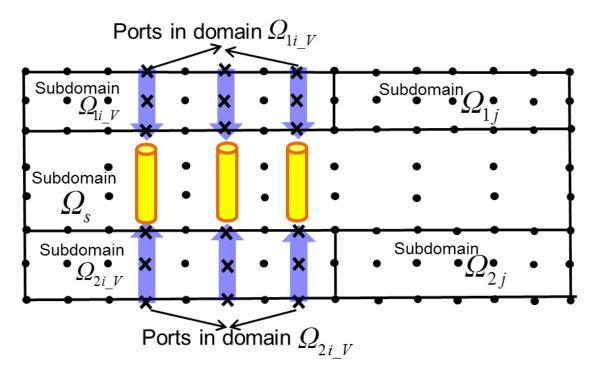

| 7.2  | Modeling of Interconnections in Silicon Interposer                         | 89  |

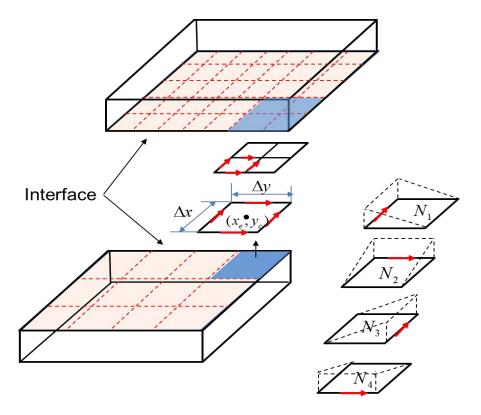

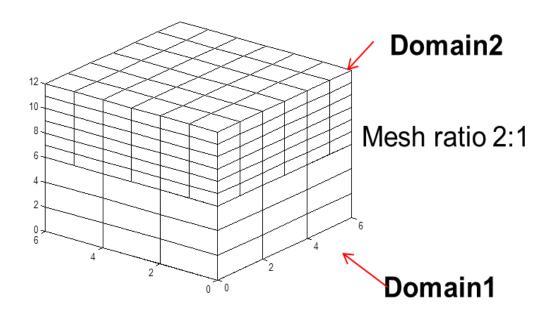

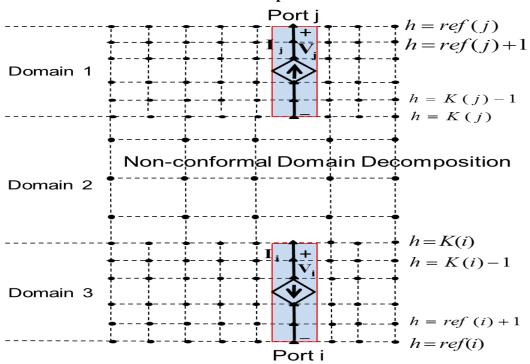

| 7.2  | .1 3-D FDFD Non-conformal Domain Decomposition                             | 89  |

| 7.2  | .2 Incorporating TSVs into Non-conformal Domain Decomposition              | 95  |

| 7.3  | System Matrix Solver                                                       | 98  |

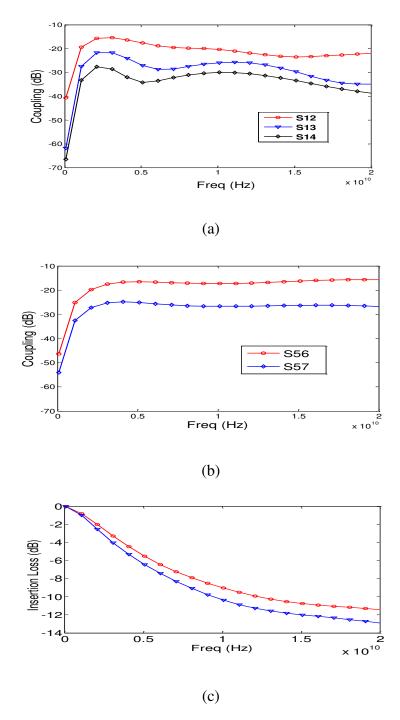

| 7.4  | Numerical Examples                                                         | 102 |

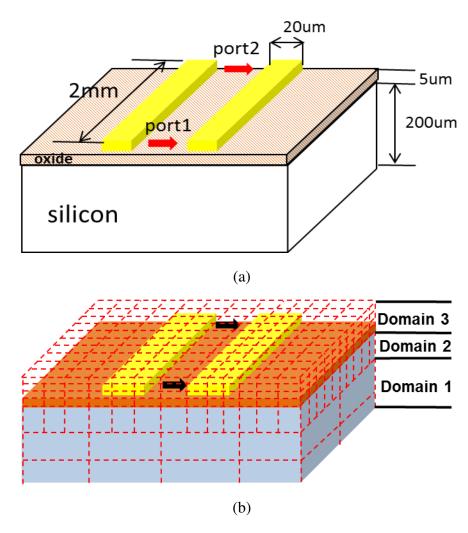

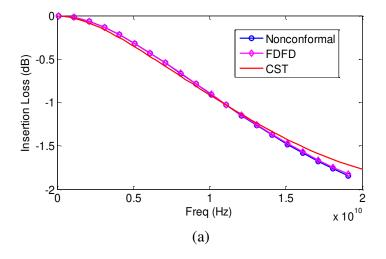

| 7.4  | .1 RDL traces on silicon interposer                                        | 102 |

| 7.4  | .2 RDL Traces Connected to TSVs in Silicon Interposer                      | 106 |

| 7.5  | Summary                                                                    | 113 |

| CHAP | TER 8 FUTURE WORK                                                          | 114 |

| 8.1  | TSV-to-Wire Coupling                                                       | 114 |

| 8.2  | Non-conformal Domain Decomposition with Model Order Reduction              | 115 |

| CHAP | TER 9 CONCLUSIONS                                                          | 116 |

| 9.1  | Contributions                                                              | 116 |

| 9.1  | .1 Modeling and analysis of simultaneous switch noise in silicon and glass |     |

| inte | erposer                                                                    | 116 |

| 9.1  | .2 FDFD modeling of signal paths with TSVs in silicon interposer           | 117 |

| 9.1  | .3 3-D FDFD non-conformal domain decomposition                             | 117 |

| 9.1  | .4 Coupling analysis of through-silicon via arrays                         | 118 |

| 9.1  | .5 Electromagnetic modeling of non-uniform TSVs                            | 118 |

| 9.2  | Publications                                                               | 118 |

# LIST OF TABLES

|                                                                                | Page |

|--------------------------------------------------------------------------------|------|

| Table 1: Comparison of peak amplitude of "victim TSVs" waveform with different |      |

| silicon substrate                                                              | 25   |

| Table 2. Eye height and jitter in case (a), (b) and (c)                        | 29   |

| Table 3. CPU time Comparison of the CST and proposed method                    | 32   |

| Table 4. Comparison of the proposed method, direct solver, QMR method, and CST | 80   |

| Table 5 Comparison of non-conformal DD and FDFD                                | 104  |

| Table 6. Comparison of the proposed method, direct solver and CST              | 109  |

# LIST OF FIGURES

| Pa                                                                                    | ige |

|---------------------------------------------------------------------------------------|-----|

| Figure 1. Silicon interposer with TSVs and RDL traces in 3-D systems.                 | . 2 |

| Figure 2. Typical TSV structure (a) Cross-section SEM image of TSVs (b) cross-section | n   |

| and top view of a single TSV                                                          | . 7 |

| Figure 3. A signal-ground TSV pair (a) Cross-section view (b) $\pi$ -type equivalent  |     |

| circuit model                                                                         | . 7 |

| Figure 4. Modeling procedure for 2×2 TSV arrays [16]                                  | . 9 |

| Figure 5. (a) Schematic cross section of a TSV biased in the depletion region (b)     |     |

| Capacitance-voltage plot for a planar MOS capacitor.                                  | 10  |

| Figure 6. RDL structure on dielectric layer with its structure parameters             | 12  |

| Figure 7. The equivalent circuit model of the RDL traces.                             | 12  |

| Figure 8. TSV pair with dimensions                                                    | 14  |

| Figure 9. Transient simulation setup for TSV pair.                                    | 15  |

| Figure 10. (a) Coupling for TSV pair, (b) Coupled noise obtained at TSV-2             | 15  |

| Figure 11. Modeling flow for coupled TSV analysis.                                    | 20  |

| Figure 12. 5×5TSV array structure.                                                    | 21  |

| Figure 13. Coupling between different TSV pairs.                                      | 21  |

| Figure 14. Insertion loss of TSV-1.                                                   | 22  |

| Figure 15. Configuration of TSVs in coupling analysis.                                | 22  |

| Figure 16. Positions of the ground TSVs in Case (c).                                  | 23  |

| Figure 17. Coupling waveform with substrate conductivity of 10S/m                     | 24  |

| Figure 18 Coupling waveforms with substrate conductivity of 0.01 S/m                  | 25  |

| Figure 19. Coupling waveform with substrate conductivity of 10 S/m and ground 27             |

|----------------------------------------------------------------------------------------------|

| Figure 20. Coupling S-parameter between TSV-1 and TSV-13 with and without ground             |

| TSVs                                                                                         |

| Figure 21. Three modes exist in Si-SiO2 system                                               |

| Figure 22. Quasi-TEM mode (a) Electric field distribution, (b) Magnetic field                |

| distribution                                                                                 |

| Figure 23. Skin effect mode (a) Electric field distribution (b) Magnetic field distribution. |

|                                                                                              |

| Figure 24. Slow wave mode (a) Electric field distribution, (b) Magnetic field distribution.  |

|                                                                                              |

| Figure 25. Configuration of "Signal TSV" and "Ground TSV" in the TSV array for eye           |

| diagram analysis                                                                             |

| Figure 26. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 10 S/m) 30           |

| Figure 27. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 0.01 S/m) 31         |

| Figure 28. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 10 S/m) 31           |

| Figure 29. Cross-sectional image of real TSV structure, (a) SEM cross-section view of        |

| laser drilled blind vias in silicon[31], (b) SEM cross-section of TSV after integration      |

| [32], (c) cross-section of 3D-WLP TSV [33]                                                   |

| Figure 30. Modeling flow for a conical TSV pair                                              |

| Figure 31. Definition of coordinate used to calculate numerical integral                     |

| Figure 32. Conical CMBFs at different cross-section of the conical structure at 0.1 GHz.     |

|                                                                                              |

| Figure 33 Parameters used to calculate oxide canacitance 40                                  |

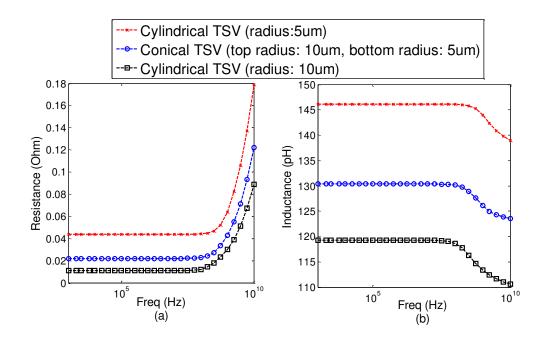

| Figure 34. (a) Geometry, ports setup of two conical TSVs (b) Equivalent circuit of two    |

|-------------------------------------------------------------------------------------------|

| conical TSVs                                                                              |

| Figure 35. Equivalent parasitic elements of conical TSVs with 10um top radius and 5um     |

| bottom radius, cylindrical TSVs with 5um radius, cylindrical TSVs with 10um radius, (a)   |

| Series resistance of the conductor, (b) Self-inductance of the conductor                  |

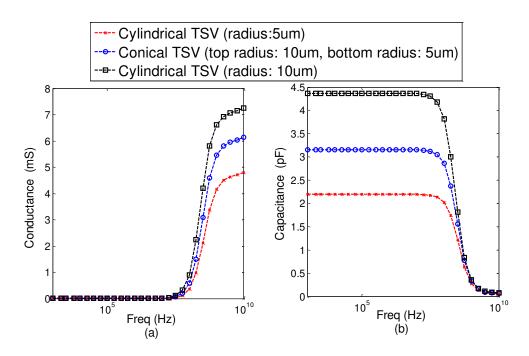

| Figure 36. Equivalent parasitic elements of conical TSVs with 10um top radius and 5um     |

| bottom radius, cylindrical TSVs with 5um radius, cylindrical TSVs with 10um radius, (a)   |

| Equivalence conductance $G_0 + 2G$ , (b) Equivalence capacitance $C_0 + 2C$               |

| Figure 37. Insertion loss for two conical TSVs. 43                                        |

| Figure 38. Complex TSV structures. 45                                                     |

| Figure 39. Insertion loss for three different complex TSV structures                      |

| Figure 40. Power/ground planes in silicon interposer with TSVs                            |

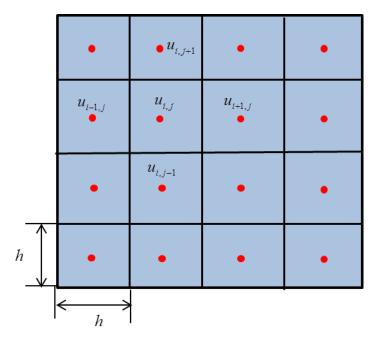

| Figure 41. Discretization of the Laplace operator                                         |

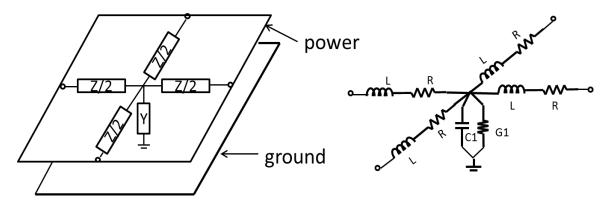

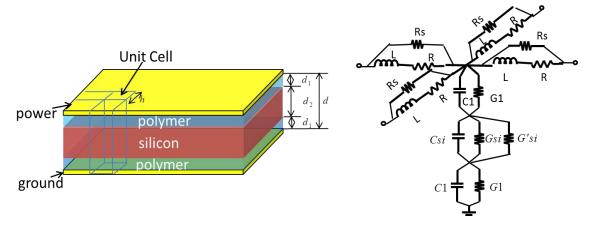

| Figure 42. Unit Cell model for power/ground planes                                        |

| Figure 43. Geometry of P/G planes with unit cell and unit cell model for a double sided   |

| silicon interposer with P/G planes                                                        |

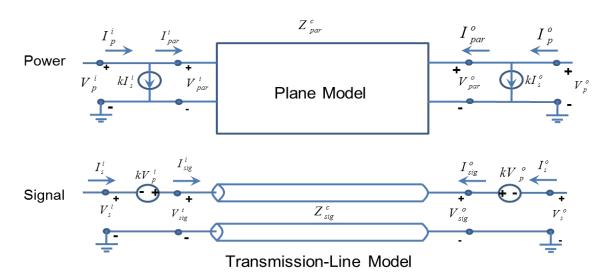

| Figure 44. Incorporating transmission line model into plane mode using modal              |

| decomposition. 52                                                                         |

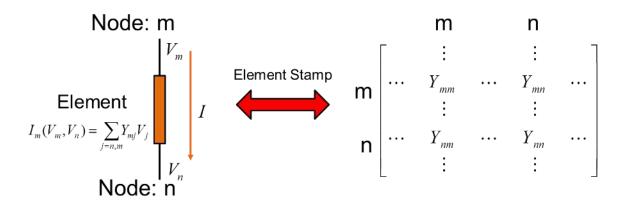

| Figure 45. Element stamping of modified nodal analysis [45]                               |

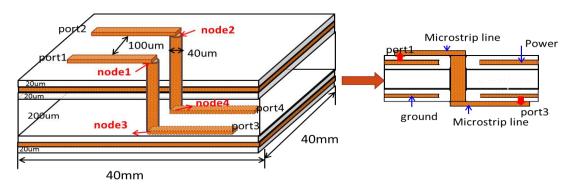

| Figure 46. Two bit microstrip-via-microstrip transition structure                         |

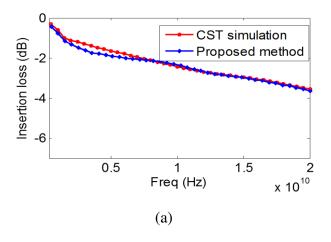

| Figure 47. S-parameters of the two bit microstrip-TSV transition structure, (a) insertion |

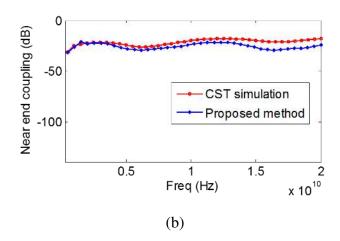

| loss, (b) near end coupling                                                               |

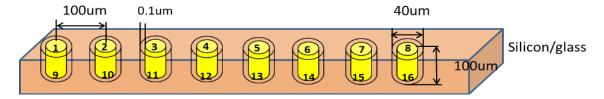

| Figure 48 8×1TSVs/TGVs array model 56                                                     |

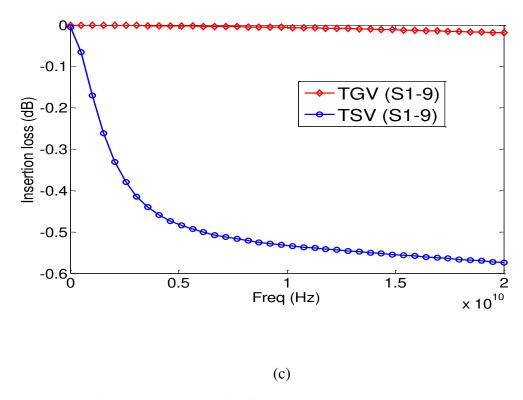

| Figure 49. S-parameters of TSVs/THVs array, (a) insertion loss, (b) near end coupling,     | ,  |

|--------------------------------------------------------------------------------------------|----|

| (c) far end coupling.                                                                      | 57 |

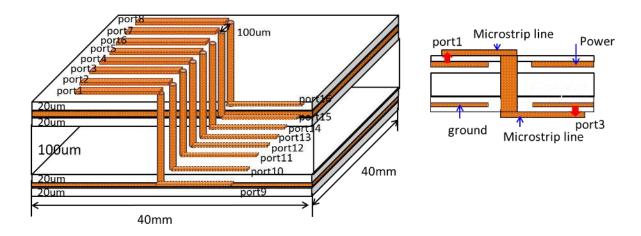

| Figure 50. 8 bit microstrip-via-microstrip transition structure.                           | 58 |

| Figure 51. S-parameters of 8 bit microstrip-via-microstrip transition structure, (a) near  |    |

| end coupling, (b) far end coupling.                                                        | 59 |

| Figure 52. (a) Silicon interposer transfer impedance, (b) glass interposer transfer        |    |

| mpedance                                                                                   | 60 |

| Figure 53. Insertion losses for 8 bit microstrip-via-microstrip transition structure, (a)  |    |

| Silicon interposer, (b) Glass interposer                                                   | 62 |

| Figure 54. Eye diagram for 8 bit microstrip-via-microstrip transition structure, (a) Silic | on |

| interposer, (b) Glass interposer.                                                          | 63 |

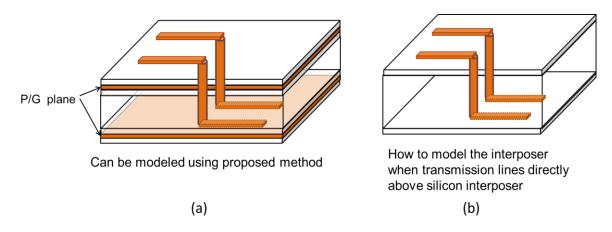

| Figure 55. (a) Interposer with P/G planes (b) Transmission lines directly above silicon    |    |

| nterposer                                                                                  | 64 |

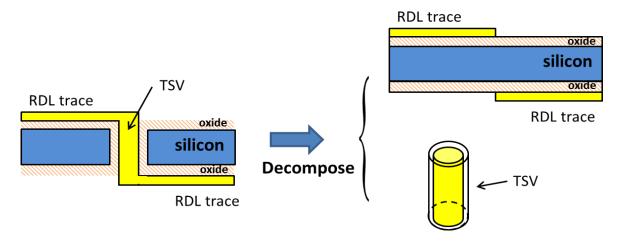

| Figure 56. Decomposition of the signal path problem into two problems                      | 66 |

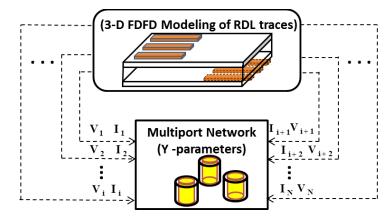

| Figure 57. Incorporating multiport network into 3-D FDFD                                   | 68 |

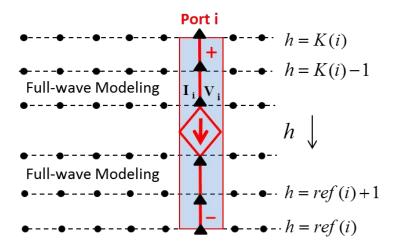

| Figure 58. Cross-sectional view of port $i$ which occupies multiple cells in FDFD Yee      |    |

| grid                                                                                       | 69 |

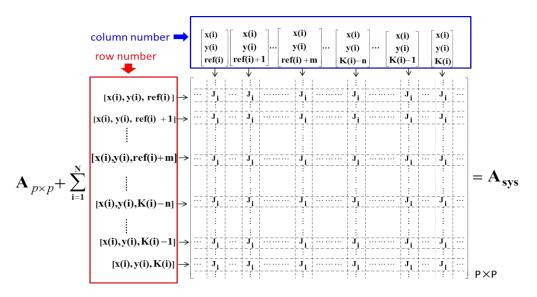

| Figure 59. Matrix operation for incorporating multiport network into 3-D FDFD              | 70 |

| Figure 60. RDL traces and TSVs in silicon interposer. Dot lines show how the               |    |

| subdomains are created                                                                     | 71 |

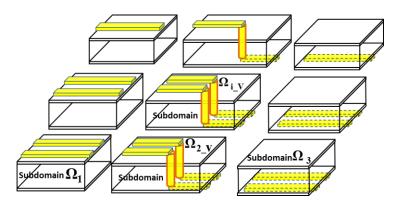

| Figure 61. <i>M</i> subdomains of the silicon interposer shown in Figure 39                | 71 |

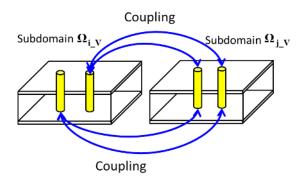

| Figure 62. Coupling between two subdomains due to the coupling between TSVs                | 72 |

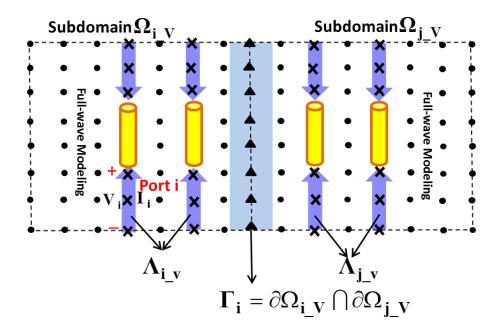

| Figure 63. Cross-sectional view of two subdomains with TSVs in the FDFD grid.           |

|-----------------------------------------------------------------------------------------|

| Triangle dots: interface unknowns between subdomains. X-shaped dots: the unknowns       |

| that introduce coupling due to TSvs                                                     |

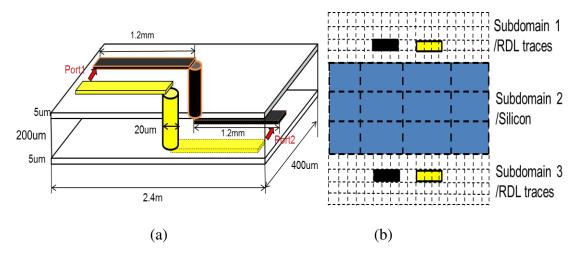

| Figure 64. RDL-TSV-RDL transition structure                                             |

| Figure 65. FDFD mesh grid for modeling RDL traces                                       |

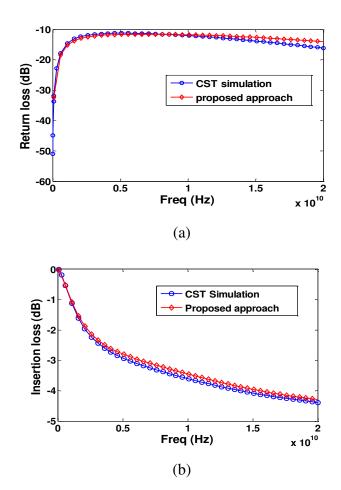

| Figure 66. S-parameters of one RDL-TSV-RDL transition structure with RDL length         |

| 2.4mm, (a) Return loss, (b) Insertion loss                                              |

| Figure 67. S-parameters of one RDL-TSV-RDL transition structure with RDL length         |

| 20mm, (a) Return loss, (b) Insertion loss                                               |

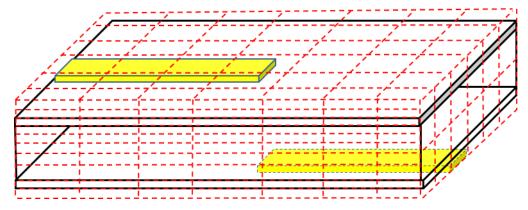

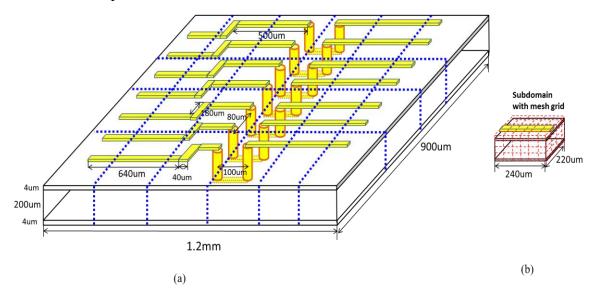

| Figure 68. (a) Five RDL-TSV-RDL transition structure, dotted lines shows how the        |

| subdomains are created. (b) Subdomain with mesh grids                                   |

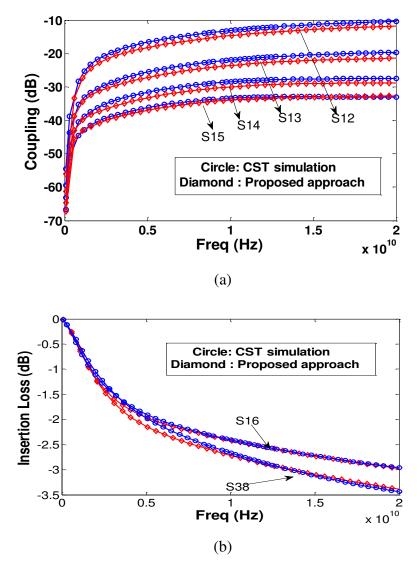

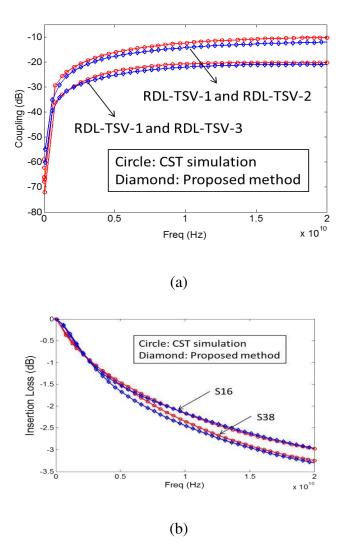

| Figure 69. S-parameters of five RDL-TSV-RDL transition structure, (a) Coupling S15,     |

| S14, S13, and S12, (b) Insertion loss S16 and S38                                       |

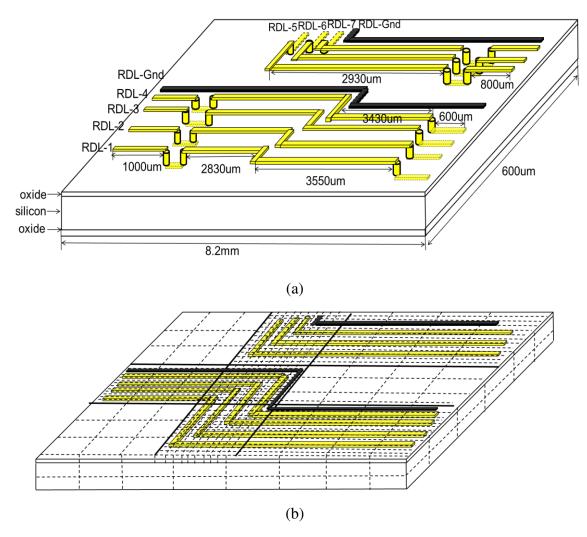

| Figure 70. (a) Irregular RDL traces routing with TSV array, dotted lines show how the   |

| subdomain are created. (b) Subdomain with mesh grids                                    |

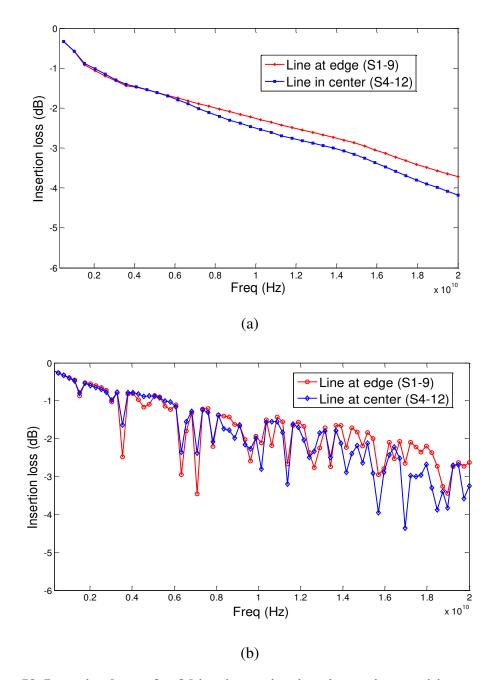

| Figure 71. S-parameters of seven irregular RDL-TSV-RDL transition structure. (a)        |

| Coupling S12, S13, and S14. (b) Insertion loss at the edge (S18) and in the center (S4- |

| 11)                                                                                     |

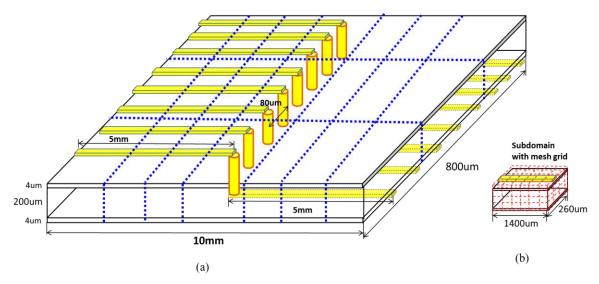

| Figure 72. (a) Multiple long RDL traces routing with 8×1 TSV array, dotted lines show   |

| how the subdomains are created. (b) Subdomain with mesh grids                           |

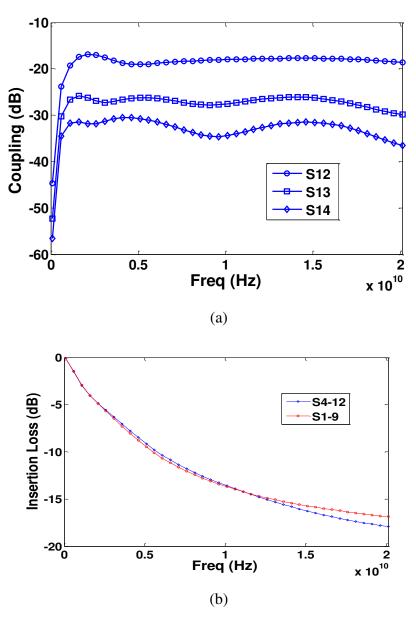

| Figure 73. S-parameters of eight RDL-TSV-RDL transition structure, (a) Coupling S12,    |

| S13, and S14, (b) Insertion loss at edge (S19) and in the center (S4-12)                |

| Figure 74. Decomposition of the interconnect problem into two problems                  |

| Figure 75. Two domains with non-matching grids at interfaces                               | 9  |

|--------------------------------------------------------------------------------------------|----|

| Figure 76. Vector basis functions for the <i>E</i> fields at the interfaces                | 2  |

| Figure 77. Two domains with non-matching grid at interface                                 | 13 |

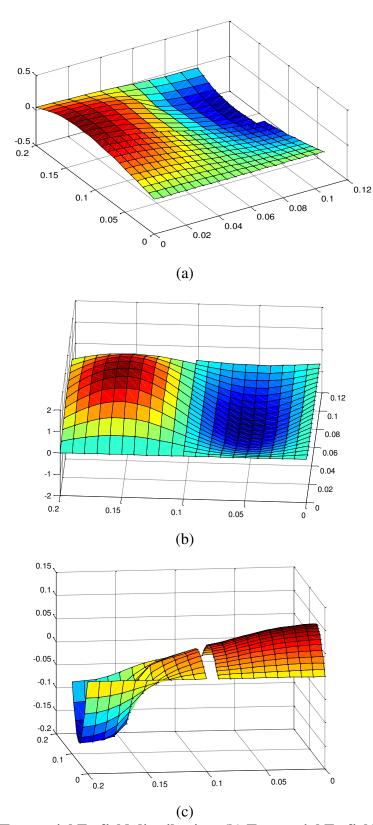

| Figure 78. (a) Tangential Ex field distribution, (b) Tangential Ey field distribution, (c) |    |

| Normal Ez field distribution                                                               | )4 |

| Figure 79. Incorporating multiport network into non-conformal domain decomposition.9       | 16 |

| Figure 80. Cross-sectional view of ports in different domains. Ports representing current  |    |

| sources occupy several FDFD grids                                                          | 16 |

| Figure 81. Matrix operation for incorporating multiport network into FDFD non-             |    |

| conformal domain decomposition9                                                            | 8  |

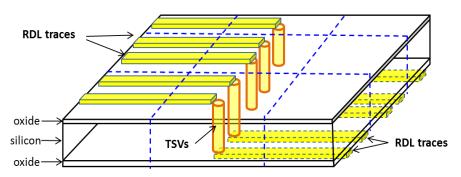

| Figure 82. RDL traces and TSVs in silicon interposer. 9                                    | 8  |

| Figure 83. Silicon interposer divided into subdomains in $x-$ , $y-$ , $z-$ direction 9    | 19 |

| Figure 84. Cross-sectional view of subdomains with TSVs in the DDM. X-shaped dots          |    |

| represents ports of TSVs stamped                                                           | 19 |

| Figure 85. RDL transmission line pair, (a) Geometry, (b) Non-conformal DD 10               | )3 |

| Figure 86. S-parameters of RDL transmission line pair, (a) Insertion loss, (b) Return      |    |

| Loss                                                                                       | )4 |

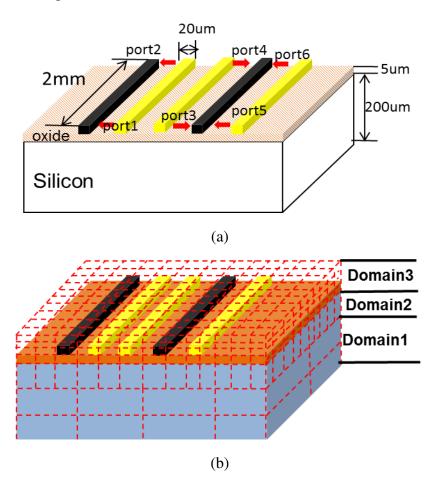

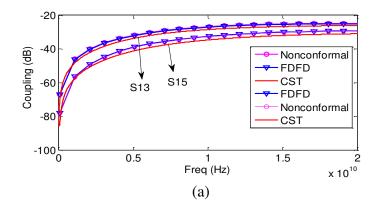

| Figure 87. Multiple RDL traces, (a) Geometry (b) Non-conformal DD                          | )5 |

| Figure 88. S-parameters of multiple RDL traces, (a) Geometry, (b) Non-conformal DD.        |    |

|                                                                                            | )6 |

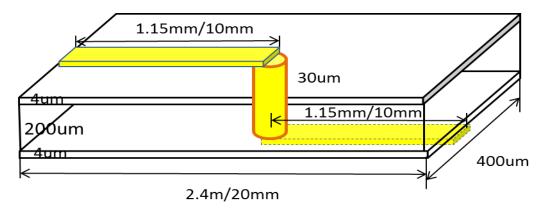

| Figure 89. RDL-TSV-RDL transition structure, (a) Geometry, (b) Cross-sectional view of     | of |

| non-conformal DDM                                                                          | )7 |

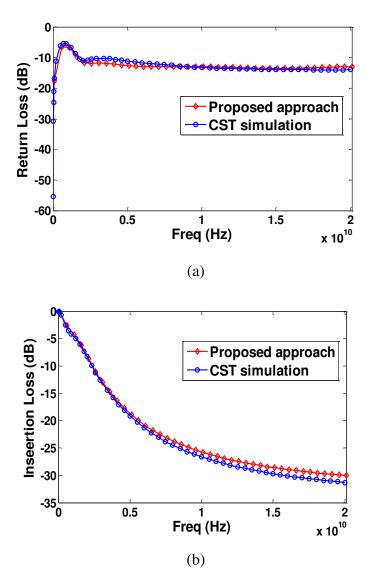

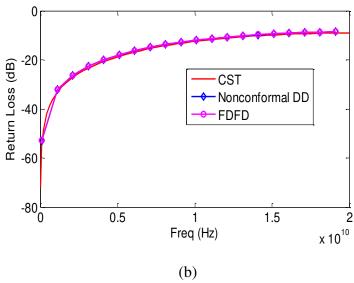

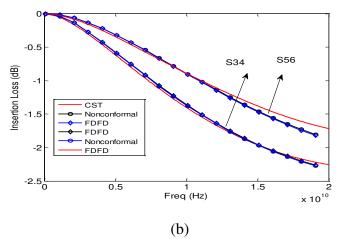

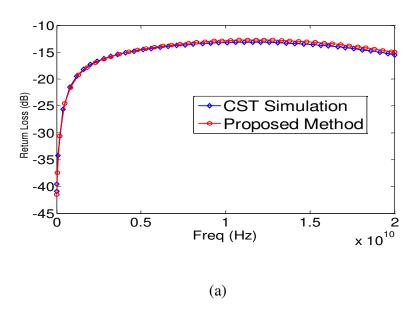

| Figure 90. S-parameters of RDL-TSV-RDL transition structure, (a) return loss, (b)     |       |

|---------------------------------------------------------------------------------------|-------|

| insertion loss.                                                                       | . 108 |

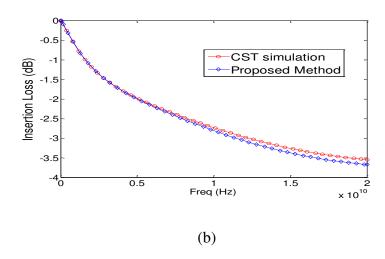

| Figure 91. Five RDL-TSV-RDL transition structure, (a) Geometry, (b) Cross-section     | al    |

| view of non-conformal DDM.                                                            | . 109 |

| Figure 92. S-parameters of five RDL-TSV-RDL transition structure. (a) Coupling S1     | 2,    |

| S13, (b) Insertion loss S16 and S38.                                                  | . 110 |

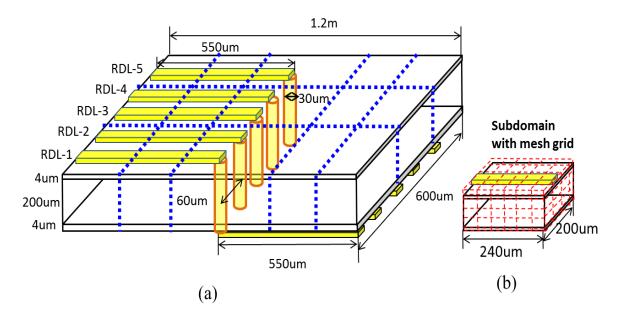

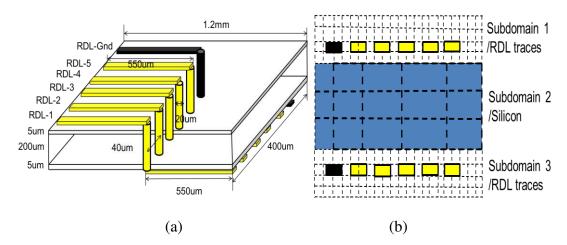

| Figure 93. RDL traces with different routing density and multiple TSV arrays, (a)     |       |

| Geometry, (b) Non-conformal domain decomposition                                      | . 111 |

| Figure 94. S-paramters of RDL traces with different routing densities and multiple TS | SV    |

| arrays, (a) Coupling between RDL-1, RDL-2, RDL-3 and RDL-4, (b) coupling between      | een   |

| RDL-5, RDL-6, and RDL-7, (c) insertion loss.                                          | . 112 |

| Figure 95. TSV-to-wire coupling.                                                      | . 114 |

| Figure 96. Domain decomposition with model order reduction.                           | . 115 |

## **CHAPTER 1**

#### INTRODUCTION

## 1.1 Background

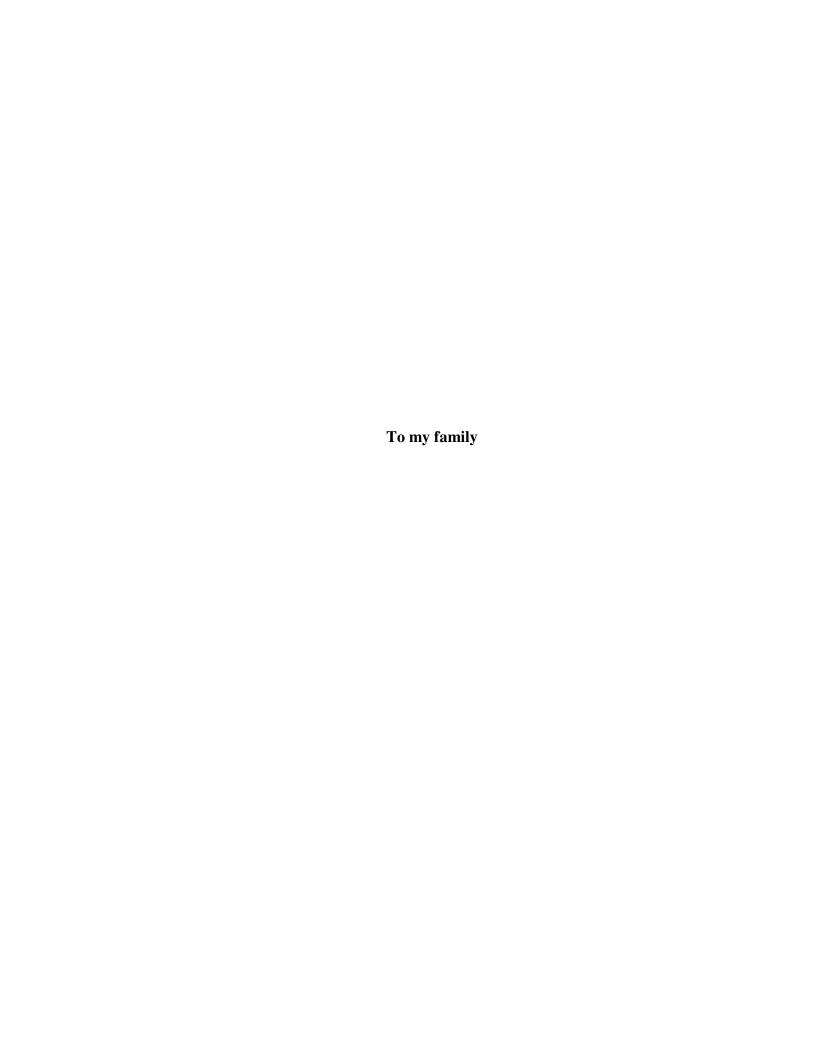

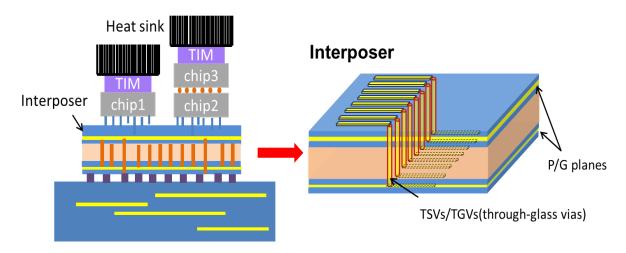

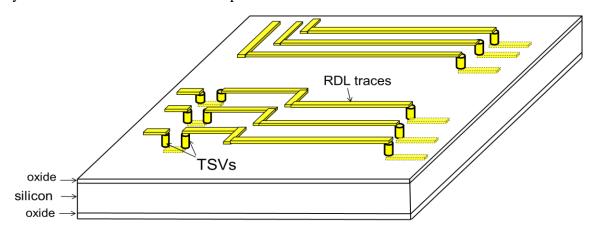

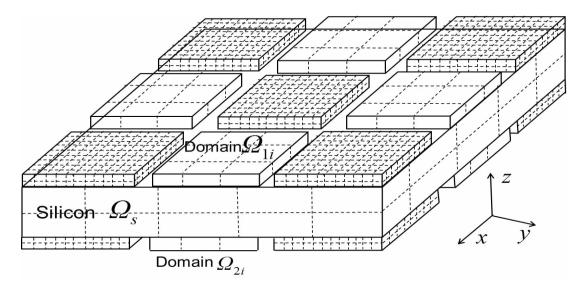

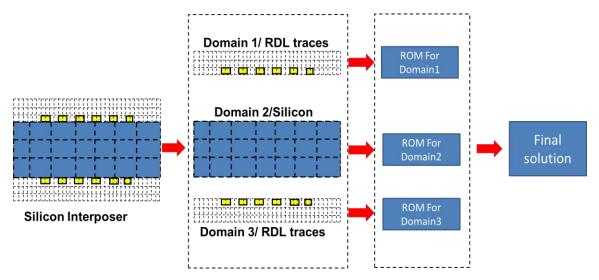

Three-dimensional (3-D) system integration is believed to be a promising technology and has gained tremendous momentum in the semiconductor industry recently. The concept of 3-D integrated circuits is shown in Figure 1. In 3-D ICs, multiple dies are stacked, and vertical interconnections between dies are realized by through-silicon vias (TSVs). These TSVs are the core technology that replace long interconnects in 2-D ICs with short vertical interconnects. The shortened wire can result in low wire delay, less parasitic effects and higher clock frequency [1-3] than 2-D ICs, thereby improving the overall system performance. In addition, it is possible with 3-D heterogeneous integration to stack different functional modules, including memory, MEMS, antenna, RF, analog/digital blocks into a package. Among all the components in the 3-D system as shown in Figure 1, the silicon interposer with TSVs and redistribution layer (RDL) traces is a key enabler and thus needs to be carefully designed to achieve optimal system performance [4]. As a result, the fast and reliable simulation of the interconnections in the silicon interposer is a necessity to speed up the design cycle time, while maintaining accuracy of the results.

#### 1.2 Motivation

The silicon interposer is expected to have high input/output counts, fine wiring lines and many TSVs. Modeling and design of the silicon interposer can be challenging due to the following reasons: (1) Silicon substrate is not an ideal medium for signal transmission since the interconnections and TSVs are exposed to additional losses due to leakage. (2) TSVs are multi-scale structures with oxide thickness less than one micron and aspect

ratio of 1:20 or higher. (3) Hundreds of interconnects routed with fine pitch on silicon substrates will cause enhanced coupling between signal lines, which can introduce distortion. (4) The insulating oxide layer around TSVs and below the RDL traces also influence the characteristics of interconnections, causing frequency-dependent parasitic effects. (5) The resistance and conductance of TSVs is temperature dependent because of the temperature-dependent conductivity [5]. Moreover, TSVs connected to multiple long RDL transmission lines will lead to frequent signal-via transitions in the silicon interposer, which results in combined signal and power integrity issues. As a result, modeling the interconnect response of high-density signal paths with TSVs in the silicon interposer is becoming a critical task.

Figure 1. Silicon interposer with TSVs and RDL traces in 3-D systems.

## 1.3 Contributions

This dissertation mainly focuses on developing an efficient modeling approach for silicon interposers in 3-D systems. The contributions of the research are listed as follows:

- 1. The investigation of the coupling effects in large TSV arrays. The importance of coupling between TSVs for low resistivity silicon substrates is quantified both in frequency and time domains. This has been compared with high resistivity silicon substrates. The comparison between the two indicates the importance of jitter and voltage analysis in TSV arrays for low resistivity silicon substrates due to enhanced coupling.

- 2. The development of an electromagnetic modeling approach for non-uniform TSVs. To model the complex TSV structures, an approach for modeling conical TSVs is proposed first. Later a hybrid modeling method which combines the conical TSV modeling method and cylindrical modeling method is proposed to model the non-uniform TSV structures.

- 3. The development of a hybrid modeling approach for power delivery networks (PDN) with through-silicon vias (TSVs). The proposed approach extends multi-layer finite difference method (M-FDM) to include TSVs by extracting their parasitic behavior using an integral equation based solver. Using the proposed modeling technique the power/signal integrity of the PDN with TSVs/through-glass vias (TGVs) in lossy silicon interposers and low loss glass interposers is investigated and compared.

- 4. The development of an efficient approach for modeling signal paths with TSVs in silicon interposers. The proposed method utilizes the 3-D finite-difference frequency-domain (FDFD) method to model the redistribution layer (RDL) transmission lines. A new formulation on incorporating multiport networks into the 3-D FDFD formulation is presented to include the parasitic effects of TSV arrays in the system matrix.

- 5. The development of a 3-D FDFD non-conformal domain decomposition method (DDM). The proposed method allows modeling individual domains independently using the FDFD method with non-matching meshing grids at interfaces. This non-conformal DDM is used to model interconnections in silicon interposers.

## 1.4 Organization of the Dissertation

This dissertation consists of nine chapters. In Chapter 1, the background and motivation, contributions, and the organization of this dissertation are introduced. In Chapter 2, the research problem to be addressed and prior arts that have been developed are investigated. In Chapter 3, the coupling effects in large TSV arrays are investigated, and the coupling effects in low resistivity and high resistivity silicon substrates are compared. In Chapter 4, a modeling approach for non-uniform TSVs is proposed. In Chapter 5, a modeling approach for the power delivery network with TSVs is proposed and the simultaneous switching noise (SSN) in silicon and glass interposers are analyzed. In Chapter 6, an efficient approach for modeling the signal paths with TSVs in silicon interposers is presented, this approach uses finite-difference frequency domain (FDFD) technique coupled with an integral equation based method where the latter is applied to TSVs. In Chapter 7, the 3-D FDFD non-conformal domain decomposition method is proposed and used to model the interconnections in silicon interposers. Chapter 8 presents the possible future work. Finally, the conclusion and summary of the research work in this dissertation are presented in Chapter 9.

## **CHAPTER 2**

#### ORIGIN AND HISTORY OF THE PROBLEM

## 2.1 Introduction

To design high-speed signal paths with TSVs in silicon interposers and perform signal/power integrity analysis for 3-D systems, the electrical model of TSVs must be obtained using design parameters such as material and geometric information. Then, this electrical model can be used to obtain overall system performance. Therefore, many approaches have been proposed for modeling and analysis of TSVs. In this chapter, the prior research for electrical modeling of TSVs is introduced.

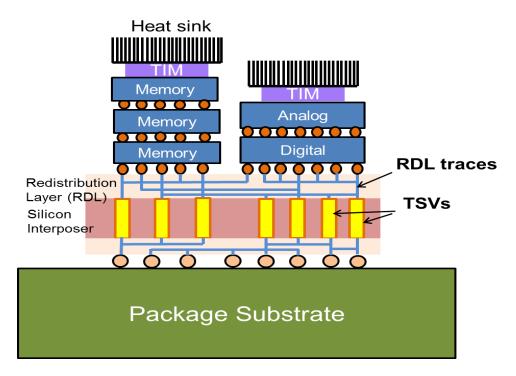

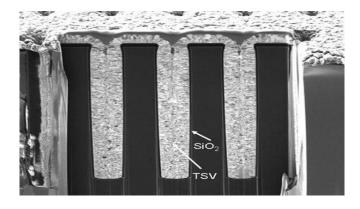

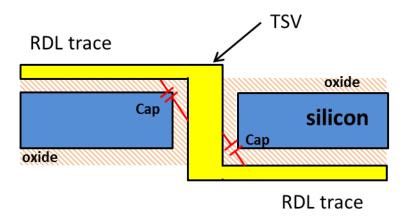

## 2.2 Lumped Element based TSV Modeling

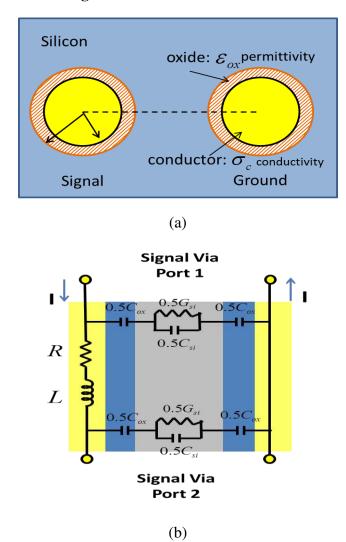

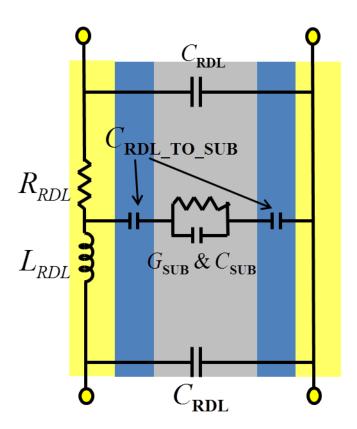

Figure 2 shows a typical structure of TSVs [6]. The conductor core of TSV usually is made of copper or tungsten. A thin oxide liner layer is deposited around the conductor. For the lumped element based TSV modeling, an equivalent circuit model can be constructed from physical intuition using an RLCG element [7]. The model contains series resistance and inductance of copper conductors, shunt oxide capacitance, and shunt silicon admittance. The value of each component is found by tuning the circuit element to fit its frequency response with measurement data using the parameter optimization method. Since this model is not tied to the geometrical and physical parameters of TSVs, several approaches are presented to obtain the closed-form formulae for the RLCG elements in the equivalent circuit model [7-11]. The  $\pi$ -type equivalent circuit is shown in Figure 3, where R and L denote the per-unit-length (p.u.l.) resistance and inductance of the TSV,  $C_{ox}$  denotes the p.u.l. capacitance due to the oxide liner, and  $C_{si}$  and  $G_{si}$  denote the p.u.l. capacitance of the silicon substrate. However, these

resistance-inductance models were not rigorously derived and did not consider the nonuniform current distribution in TSV conductor caused by adjacent TSVs, therefore it can not capture all the semiconductor effects. This equivalent circuit model was again investigated in [12], where rigorous closed-form formulae for the resistance and inductance of TSVs are derived from the magneto-quasi-static theory with a Fourier-Bessel expansion approach. This equivalent-circuit model can capture the important parasitic effects of TSVs, including skin effect, proximity effect and lossy silicon effects. It can generate accurate results comparable to 3-D full-wave solvers. The equivalent circuit model is extended in [13] to consider all the parasitic components of the TSV, where a scalable electrical model of TSVs including bump and RDL traces was proposed. Although lumped element modeling can provide reasonable good results for the insertion loss, it becomes difficult to extend this method to model large TSV arrays since the current distribution in one TSV conductor will be affected by all the other adjacent TSVs and becomes non-uniform in high-density TSV arrays, it is difficult to use analytical equations to accurately account for the complex current distribution in TSVs and capture all the coupling effects between TSVs. Hence a full wave analysis method is required that is scalable to multiple TSVs as in arrays. Because of the multi-scale dimensions of TSVs (oxide thickness and aspect ratio), this becomes a very challenging task and is a major bottleneck for commercially available EM solvers where large arrays of TSVs must be modeled.

(a)

Figure 2. Typical TSV structure (a) Cross-section SEM image of TSVs (b) cross-section and top view of a single TSV.

Figure 3. A signal-ground TSV pair (a) Cross-section view (b)  $\pi$  – type equivalent circuit model

## 2.3 Electromagnetic Modeling of TSVs

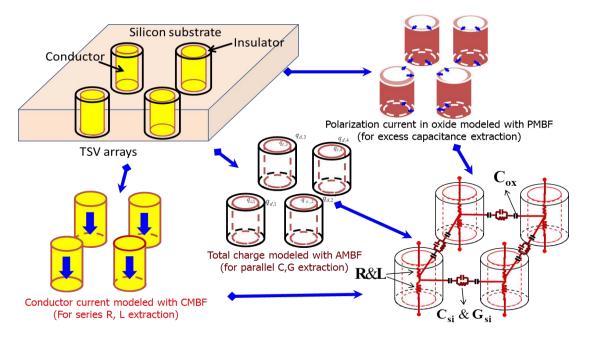

To address the problem of modeling large TSV arrays, a modeling method based on solving Maxwell's equations in integral form is proposed in [14-16]. In this approach, specialized basis functions which approximate the current and charge in the TSVs are derived. Using these basis functions, the electrical response of the structure can be extracted by solving Maxwell's equations. The modeling flow is shown in Figure 4. This proposed method can generate equivalent *RLCG* parameters of TSVs that represent the following parasitic elements.

- (1) Conductor series resistance and inductance: This represents the loss and inductive coupling in copper conductors, which are due to the volume current density distribution. The conductor series impedance can be extracted by solving the electric field integral equation (EFIE) with cylindrical conduction mode basis functions (CMBFs) [14].

- (2) Substrate parallel conductance and capacitance: This represents the loss and capacitive coupling between conductor and insulator surfaces, which is produced by the surface charge density distribution on the conductor and dielectric surfaces. The parallel admittance can be extracted by solving the scalar potential integral equation (SPIE) with cylindrical accumulation mode basis functions (AMBFs). The conductance terms can be computed by using the complex permittivity for silicon defined as in equation (1) [17]:

$$\varepsilon_{si} = \varepsilon_0 \varepsilon_{si,i} (1 - j \tan \delta - j \frac{\sigma_{si}}{\omega \varepsilon_0 \varepsilon_{si,i}})$$

(1)

where  $\varepsilon_{si}$  is the dielectric constant,  $\sigma_{si}$  is the conductivity of silicon and  $\tan \delta$  is the intrinsic loss tangent.

(3) Excess capacitance in oxide liner: This represents the effect of the insulator between conductor and silicon substrate, which originates from polarization current in the insulator. The new basis functions, called polarization mode basis functions (PMBFs),

[15] are proposed to capture the polarization current density distribution. The excess capacitance is extracted by solving EFIE with PMBFs.

Figure 4. Modeling procedure for  $2 \times 2$  TSV arrays [16].

All of these elements can capture the non-uniform effect of charge and current distribution in the TSVs, which depends on the proximity of the neighboring TSV interconnections. As illustrated in Figure 4, the extracted individual elements are combined to generate the complete equivalent circuit model of the entire TSV structure. A major challenge in modeling TSVs arises from the multi-scale dimensions of TSV structure due to the thin oxide thickness, aspect ratio and the need for modeling multiple TSVs. Using the specialized basis functions described above eliminates the need for meshing the structure and therefore is computationally less expensive and memory efficient.

## 2.4 MOS Capacitance in TSVs

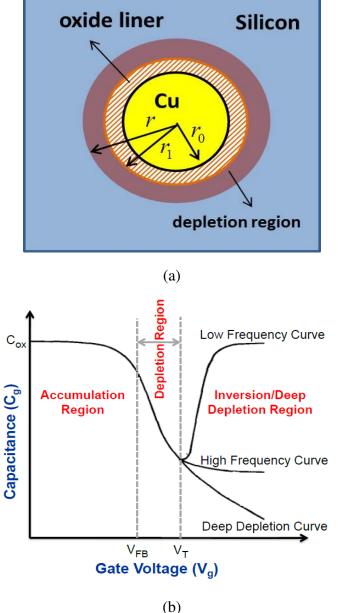

To obtain a rigorous model of TSVs, the voltage-dependent MOS capacitance of TSVs should be considered. The TSV shown in Figure 5(a) consists of a cylindrical conductor surrounded by an oxide liner embedded in a silicon substrate, which is a cylindrical

metal-oxide-semiconductor (MOS) structure. Such a TSV under bias condition exhibits a capacitance behavior similar to a planar MOS capacitor [18]. Figure 5(b) shows a typical capacitance ( $C_g$ ) plot with change in the gate voltage ( $V_g$ ) for a planar MOS capacitor. As shown in Figure 5(b), at high gate voltage the MOS capacitance has three possibilities: deep depletion, high frequency, and low frequency.

Figure 5. (a) Schematic cross section of a TSV biased in the depletion region (b) Capacitance-voltage plot for a planar MOS capacitor.

The first analytical model of the MOS capacitance effect is proposed in [19]. This analysis is performed by analytically solving Poisson's equation assuming full depletion approximation (FDA). The FDA simplifies the analysis by assuming that the depletion region (formed in the semiconductor) is fully depleted (i.e. there are no mobile charge carriers in the depletion region).

The full depletion approximation enables a simple analysis but it does not provide the most accurate result. A more accurate electrical model of a TSV is presented in [20]. This method performs exact analysis by solving Poisson's equation numerically in cylindrical coordinate using the Runge-Kutta method [21].

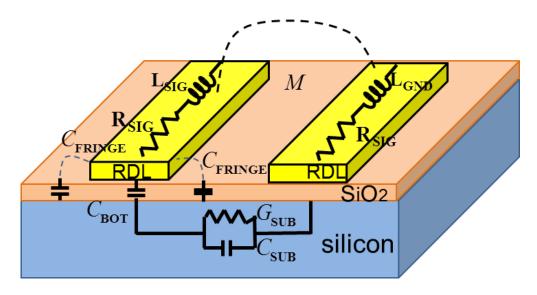

## 2.5 Modeling of RDL traces on silicon interposer

In the silicon interposer, signal paths often consist of TSVs and RDL transmission lines. When designing the signal paths with TSVs in a silicon interposer, the RDL is an essential component that should be considered with the TSV. Therefore, modeling and analysis of RDLs is also important for 3D system design. An analytical model for a RDL is proposed in [13]. In this approach, RDL traces are modeled using analytical equations. A RDL structure on a dielectric layer with structure parameters is shown in Figure 6 and the proposed equivalent circuit model is shown in Figure 7. An electrical model of the signal paths in the silicon interposer can be obtained by combing this analytical model of RDLs with the analytical model of TSVs discussed in the previous section. However, this model is mostly analytical and limited to a few interconnects. Efficient approaches for modeling a large number of RDLs and TSVs therefore need to be investigated.

Figure 6. RDL structure on dielectric layer with its structure parameters

Figure 7. The equivalent circuit model of the RDL traces.

## 2.6 Technical Focus of This Dissertation

The investigation of the prior arts for TSV modeling provides the understanding of the advantages and limitations of existing modeling techniques. With the evolution of 3-D integration, efficient modeling tools are needed to facilitate 3-D IC designs. The technical focus of this dissertation is summarized as follows:

- 1. The investigation of the coupling effects in large TSV arrays. The importance of coupling in large TSV arrays is quantified in both time domain and frequency domain.

- 2. The development of a modeling approach for non-uniform TSVs

- 3. The development of a hybrid modeling approach for a power delivery network with TSVs.

- 4. The development of an efficient approach for modeling signal paths with TSVs in silicon interposers.

- 5. The development of the 3-D FDFD non-conformal domain decomposition method and its application for modeling interconnections in silicon interposers.

## 2.7 Summary

This chapter introduces the origin and history of the research. It reviews previous modeling approaches for the interconnections in silicon interposer. Several lumped TSV/RDL modeling approaches are briefly introduced and later an electromagnetic modeling approach for TSVs arrays is investigated. The advantages and limitations of these previous modeling approaches are also provided. The limitations of existing modeling approaches for the interconnections in silicon interposer motivate the technique research in this dissertation.

## **CHAPTER 3**

# COUPLING ANALYSIS OF LARGE TSV ARRAYS USING

## SPECIALIZED BASIS FUNCTIONS

## 3.1 Introduction

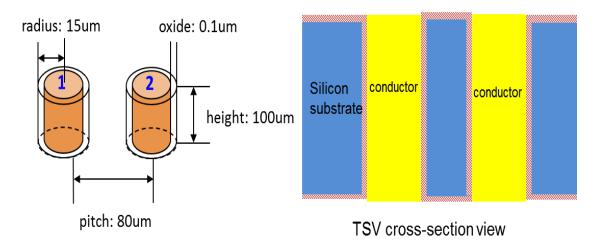

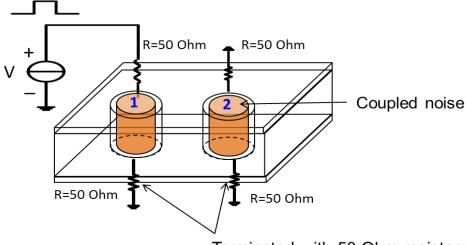

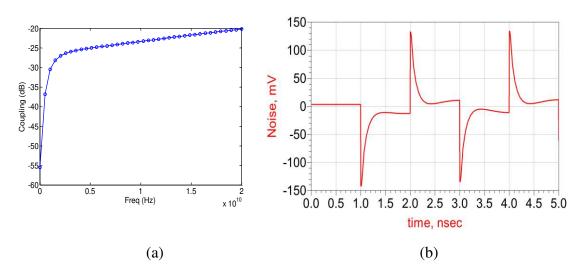

A TSV pair with dimensions is shown in Figure 8. Unlike vias in packages and PCBs, TSVs are embedded in a lossy silicon substrate and surrounded by a thin oxide liner. Therefore, the TSV-to-TSV coupling path will include the TSV conductor, oxide liner, and silicon substrate, which is more complicated and significant than traditional wire coupling [22]. The coupling of the TSV pair shown in Figure 8 is examined and Figure 10(a) shows the coupling S-parameter of this TSV pair. We use this TSV pair to perform transient simulation and obtain the coupled noise at the victim TSV. The configuration of the transient simulation is shown in Figure 9 and the simulation results show that the coupled noise can reach up to 150mV, which can not be neglected, as shown in Figure 10(b).

Figure 8. TSV pair with dimensions

Voltage amplitude: 1V

Terminated with 50 Ohm resistance

Figure 9. Transient simulation setup for TSV pair.

Figure 10. (a) Coupling for TSV pair, (b) Coupled noise obtained at TSV-2.

Because of the high integration density of interconnections in 3D stacked ICs, a large number of TSVs need to be used in the silicon interposer package. The coupling between TSVs in TSV arrays become more complicated since one victim TSV is surrounded by many aggressor TSVs, therefore, it is very difficult to estimate the coupling in large TSV arrays. This chapter focuses on analyzing TSV arrays and provides details on the coupling effects in large TSV arrays [23, 24].

## 3.2 TSV Modeling With Cylindrical Modal Basis Functions

This section describes the TSV modeling method used in TSV array coupling analysis. This method can generate equivalent *RLCG* parameters of TSVs by classifying TSV structures into the following three parts: (1) Conductor series resistance and inductance: this represents the resistive loss and inductive coupling of the copper conductor, which can be extracted by using the electric field integral equation (EFIE) [3] with cylindrical conduction mode basis functions (CMBFs) [4], (2) Substrate parallel conductance and capacitance: this represents the resistive loss and capacitive coupling in the substrate, which can be extracted by using the scalar potential integral equation (SPIE) with cylindrical accumulation mode basis functions (AMBFs) [5], (3) Oxide liner excess capacitance, this represents the capacitive coupling between the conductor and substrate, which can be extracted by using the EFIE with new basis functions called polarization mode basis functions (PMBFs).

Since the details of the modeling are discussed in previous work [2], we briefly describe the three parts of the extraction procedure using different basis functions.

#### 3.2.1 Conductor Series Resistance and Inductance Extraction

The EFIE equation used in the inductance and resistance extraction is given by [5]

$$\frac{\vec{J}(\vec{r},w)}{\sigma} + j\frac{\omega u}{4\pi} \int_{V'} G(\vec{r},\vec{r'}) \vec{J}(\vec{r'},\omega) dV' = -\nabla \Phi(\vec{r},\omega)$$

(2)

The current density of a conductor segment j can be approximated using the following equation

$$\vec{J}_{j}(\vec{r},\omega) \cong \sum_{n,q} I_{jnq} \vec{w}_{jnq}(\vec{r},\omega)$$

(3)

where  $\overrightarrow{w}_{jnq}(\overrightarrow{r},\omega)$  is the basis function in conductor segment j with order n and orientation q.

After inserting the approximation (3) into the current density term in (2) and applying the inner product (4) based on Galerkin's method,

$$\langle \vec{w}_{imd}(\vec{r},\omega), \vec{x} \rangle = \int_{V} \vec{w}_{imd}(\vec{r},\omega) \cdot \vec{x} dV$$

(4)

the following equivalent voltage equation (5) can be obtained.

$$\sum_{n,q} I_{jnq} R_{imd,jnq} + j\omega \sum_{n,q} I_{jnq} L_{imd,jnq} = \Delta V_{imd}^{j}$$

(5)

where  $R_{imd,jnq} = \frac{1}{\sigma} \int_{V_i} \vec{w}_{imd}(\vec{r}_i, \omega) \cdot \vec{w}_{jnq}(\vec{r}_j, \omega)$ ,

$$L_{imd,jnq} = \frac{\mu}{4\pi} \int_{V_j} \int_{V_i} \vec{w}_{imd} (\vec{r}_i, \omega) \cdot \vec{w}_{jnq} (\vec{r}_j, \omega) \frac{1}{|\vec{r}_i - \vec{r}_j|} dV_j dV_i$$

and

$$\Delta V_{imd}^{j} = -\frac{1}{\sigma} \int_{S_{i}} \Phi_{j}(\vec{r}_{i}) \vec{w}_{imd}^{*}(\vec{r}_{i}, \omega) \cdot d\vec{S}_{i}$$

In the above equations, i, m, d represent the index of the inductive cell, the order of CMBF and the orientation of CMBF, respectively.  $\overrightarrow{w}_{imd}(r_i, \omega)$  is the cylindrical CMBF with the (i, m, d)-th order.

#### 3.2.2 Substrate Parallel Conductance and Capacitance Calculation

The SPIE equation used for substrate parallel conductance and capacitance calculation is expressed as:

$$\frac{1}{4\pi\varepsilon_0} \int_{V'} G(\vec{r}, \vec{r'}) q(\vec{r'}, \omega) dV' = \Phi(\vec{r}, \omega)$$

(6)

By inserting the charge density distribution function  $q = \sum_{n=0}^{\infty} Q_{knq} v_{knq}$  and applying the inner product

$$\langle \vec{v}_{lmd}(\vec{r},\omega), \vec{x} \rangle = \int_{S} v_{lmd}(\vec{r},\omega) x dS$$

(7)

the following equation (8) can be deduced from the SPIE (6).

$$\sum_{lnq} P_{kmd,lnq,Q}^{C,D} Q_{lnq} = \Phi_{kmd}^{C,D}$$

(8)

where

$$P_{kmd,\ln q}^{C,D} = \frac{1}{4\pi\varepsilon_{si}} \int_{S_l} \int_{S_k} v_{kmd}(\vec{r_k}) v_{\ln q}(\vec{r_l}) \frac{1}{|\vec{r_i} - \vec{r_j}|}$$

.

Here, k, m, d represent the index of the conductor number, modal order and orientation, respectively.  $P_{kmd,\ln q}^{C,D}$  is the partial potential coefficient between the (k,m,d)-th and (l,n,q)-th order modes. The superscripts C and D represent the conductor surface and insulator surface of the TSV, respectively.

## 3.2.3 Oxide Liner Excess Capacitance Extraction

The EFIE equation used for the extraction of the excess capacitance in oxide liner is given by

$$\frac{\overrightarrow{J^{P}}(\overrightarrow{r},\omega)}{j\omega\varepsilon_{0}(\varepsilon_{ox}-\varepsilon_{si})}+j\omega\frac{u}{4\pi}\int_{V'}G(\overrightarrow{r},\overrightarrow{r'})\overrightarrow{J^{P}}(\overrightarrow{r'},\omega)dV'=-\nabla\Phi(\overrightarrow{r},\omega) \tag{9}$$

Using a similar process as for inductance and resistance extraction, the following equation (10) can be deduced from (9), expressed as

$$\sum_{l,n,q} I_{\ln q} \frac{1}{j\omega C_{kmd,\ln q}^{ex}} + \sum_{l,n,q} j\omega L_{kmd,\ln q} I_{\ln q} = \int_{V_k} \vec{u}_{kmd} \cdot (-\nabla \Phi) dV_k$$

(10)

where

$$C_{kmd,\ln q}^{ex} = \frac{\varepsilon_0(\varepsilon_{ox} - \varepsilon_{si})}{\int \vec{u}_{kmd} \cdot \vec{u}_{\ln q} dV_k}$$

and

$$L_{kmd, \ln q} = \frac{\mu}{4\pi} \int_{V_k} \int_{V_l} G(\vec{r_k}, \vec{r_l}) \vec{u}_{kmd} (\vec{r}_k) \cdot \vec{u}_{\ln q} (\vec{r}_l) \frac{1}{\left| \vec{r_l} - \vec{r_j} \right|} dV_l dV_k$$

Here, k, m, d also represent the index of conductor number, modal order and orientation respectively.

Equations (5), (8), and (10) can be combined into a large matrix equation, which relates the terminal currents and nodal voltages to the modal circuit elements consisting of the conductor *R-L* elements, the parallel conductance and capacitance in the substrate, and the excess capacitance in the oxide liner. Since this TSV modeling method uses a small number of global modal basis functions, it is more efficient than the full wave commercial EM solvers available and has been correlated with other results in [16]. Moreover, since this method is scalable, it can be easily extended to arrays of TSVs. In the following section, the TSV modeling method described is used to obtain the model for a large TSV array, which has then been used for coupling analysis in this chapter.

## 3.3 Characteristics of Coupled Waveform in TSV Array

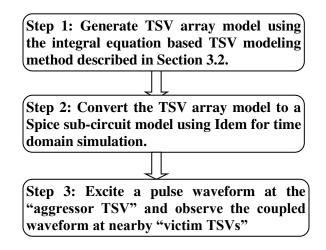

The flow of the proposed transient coupling analysis approach is shown in Figure 11. This method starts by obtaining a TSV array frequency domain model. Once the model is obtained, it is converted to a Spice sub-circuit model which can be used for time domain simulation in Hpsice. This is done using Idem [25] which enables the development of a macromodel by preserving passivity and causality. After generating the Spice sub-circuit model, the effects of waveform coupling in the TSV array can be obtained by performing time domain simulation. All transient simulations are performed using Hspice.

Figure 11. Modeling flow for coupled TSV analysis.

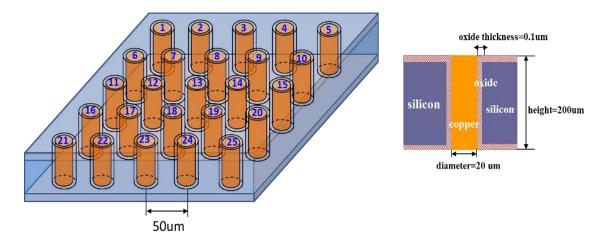

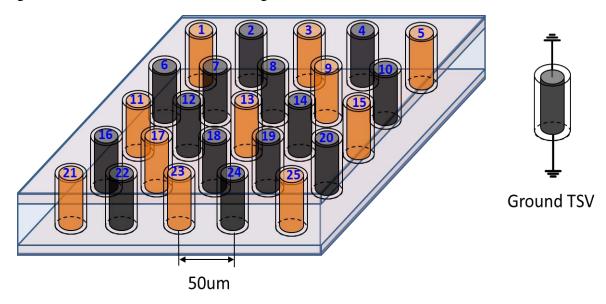

The structure for TSV coupling analysis is shown in Figure 12. To perform coupling analysis, a TSV array model is first generated using the integral equation based TSV modeling method described in Section 3.2 [16]. In this example, we generate a  $5 \times 5$  TSV array model of the structure shown in Figure 12. The dielectric constants of silicon and silicon dioxide used were 11.9 and 3.9, respectively. The copper conductivity used is  $\sigma = 5.8 \times 10^7 S/m$ . The TSV diameter, substrate thickness and oxide thickness are  $20 \,\mu\text{m}$ ,  $200 \,\mu\text{m}$  and  $0.1 \,\mu\text{m}$ , respectively. Before performing the transient analysis, the Sparameter model of the TSV arrays obtained using the modeling approach is examined.

Figure 12.  $5 \times 5$  TSV array structure.

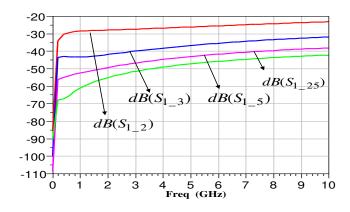

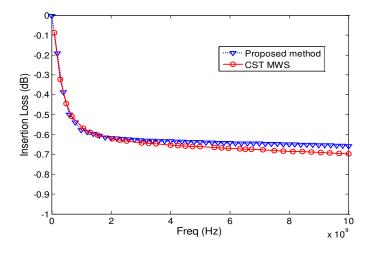

The coupling between TSV-1 and other TSVs (TSV-2, TSV-3, TSV-5, TSV-25) is shown in Figure 13. The frequency range is from 1000 Hz to 10 GHz. It can be seen that the isolation is high and the coupling has a sharp slope at low frequency. As frequency further increases, it shows a positive ramp, indicating that the coupling increases with frequency.

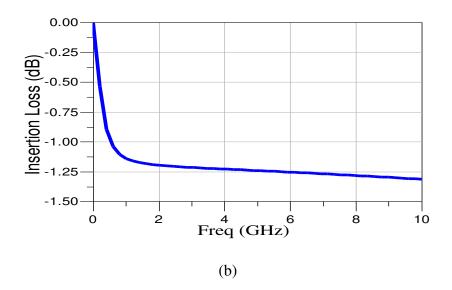

The insertion loss of TSV-1 is shown in Figure 14. It illustrates that there is significant signal loss and the insertion loss increases rapidly to 1.1 dB at 1 GHz. The sharp slope of the insertion loss at low frequency is due to the small oxide liner thickness resulting in a larger oxide capacitance, which provides a leakage path to the silicon substrate [26]. As frequency increases, the insertion loss shows a negative slope, indicating the signal loss increases with frequency.

Figure 13. Coupling between different TSV pairs.

Figure 14. Insertion loss of TSV-1.

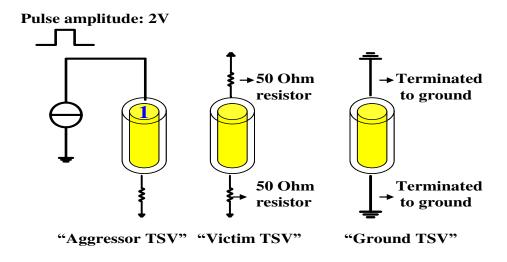

The structure for TSV coupling analysis is the same as shown in Figure 12. The configuration of TSVs in the coupling analysis is shown in Figure 15. In the TSV array, TSV-1 is defined as "aggressor TSV", which is excited with one pulse with 2 V magnitude and 10 ns width. The pulse rise and fall times are both 0.1 ns. All the other TSVs other than ground TSVs in the array are defined as "victim TSVs", which are terminated with 50 Ohm resistors on both sides, as shown in Figure 15.

Figure 15. Configuration of TSVs in coupling analysis.

Three different test cases are simulated and compared: (a) silicon substrate conductivity is 10 S/m and no ground TSV is used; (b) silicon substrate conductivity is changed to

0.01 S/m and no ground TSV is used; (c) silicon substrate conductivity is 10 S/m and ground TSVs are used, as shown in Figure 16.

Figure 16. Positions of the ground TSVs in Case (c).

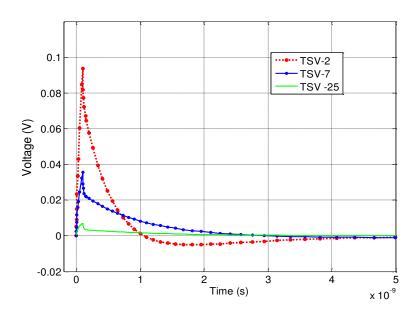

In Case (a), TSV-2, TSV-7 and TSV-25 are selected to observe the coupled waveform from aggressor TSV-1. The coupled waveform results are shown in Figure 17. As can be observed from Figure 17, with substrate conductivity of 10 S/m, the peak amplitudes of the coupled waveform at TSV-2, TSV-7 and TSV-25 are 95 mV, 35 mV and 7 mV, respectively. The coupling is more obvious at the adjacent TSVs (TSV-2 and TSV-7) of the aggressor TSV-1 due to shorter distance. Most importantly, it is observed that all these coupled waveforms have a very long tail, and the farther the TSV from the aggressor TSV-1, the longer is the tail. Hence, the time constant of the coupled waveform increases with the distance to the "aggressor TSV" which is due to the conductive and capacitive nature of silicon. The long tail of the coupled waveforms can have a detrimental effect on the signal integrity of the silicon interposer, since the effect of coupled noise is present on the coupled TSV for an extended period of time. Such an effect will never be seen in low loss dielectrics such as in organic/ceramic packages or printed circuit boards.

Case (b) is simulated to observe the coupling effects of TSVs in high resistivity substrate. As is well known, a high resistivity silicon substrate behaves like a low loss dielectric. The coupled waveforms at TSV-2, TSV-7 and TSV-25 are shown in Figure 18. As can be seen from Figure 18, the long tail of the coupled waveform disappears and the amplitude of the waveform is also smaller as compared to Case (a) when silicon conductivity was 10 S/m. The comparison of the peak amplitude of the coupled waveforms is shown in Table 1. From our preliminary simulation results, we can see that the high resistivity substrate is better for reducing the coupling between TSVs in the TSV array structure. This conclusion is validated in Section 3.4. However, a low resistivity silicon substrate is preferred from a manufacturing standpoint due to existing manufacturing infrastructure and lower cost. Hence, methods to reduce this coupling are required.

Figure 17. Coupling waveform with substrate conductivity of 10S/m

Figure 18. Coupling waveforms with substrate conductivity of 0.01 S/m.

Table 1: Comparison of peak amplitude of "victim TSVs" waveform with different silicon substrate

| Silicon substrate      | TSV-2 | TSV-7 | TSV-25 |

|------------------------|-------|-------|--------|

| Conductivity: 10 S/m   | 94 mV | 35 mV | 7 mV   |

| Conductivity: 0.01 S/m | 22 mV | 11 mV | 3 mV   |

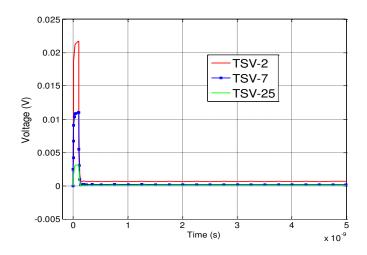

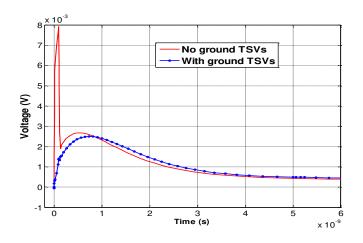

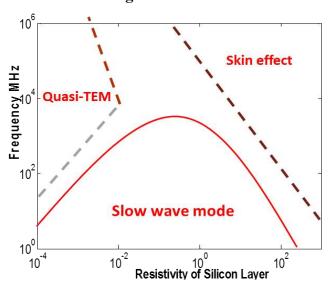

In Case (c), ground TSVs, as shown in Figure 16, are included and the silicon conductivity is set to be 10 S/m. It is simulated to observe the effects of ground TSVs on the coupled waveform. Figure 19 shows the comparison of the coupled waveform at TSV-13 with and without ground TSVs. It shows that when there is no ground TSV in the TSV array, the coupled waveform at TSV-13 has a spike, which can distort the signal when the signal is switching. However, with ground TSVs used, the spike disappears and the crosstalk becomes a smoother waveform, as shown in Figure 19. This is due to the ground TSVs providing shielding that can reduce the coupling between TSVs, as shown in Figure 20. However, even with shielding a long residual waveform in the time domain exist on TSV-13 which has considerable amplitude. This effect is unique to TSV arrays due to the presence of the silicon substrate, which is caused by the slow wave mode, resulting in a magnetic field that penetrates the silicon substrate through the shielding conductor. It has been concluded in the past that three modes exist for a microstrip line on Si-SiO2 double-layer system [27] as shown in Figure 21. Three modes are separated

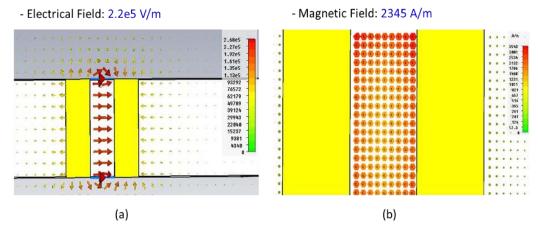

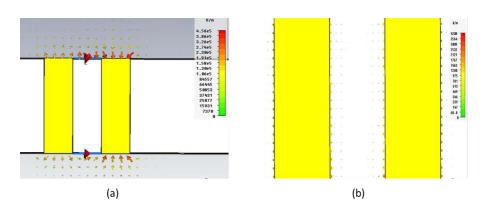

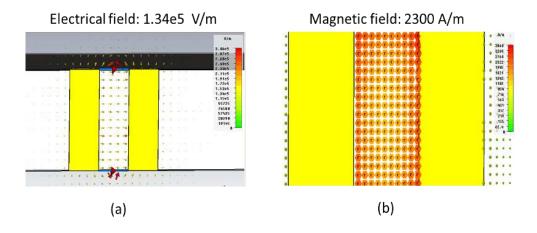

based on the frequency, thickness of SiO2 layer and Si substrate and silicon conductivity. 1) When the product of the frequency and resistivity of the Si-substrate is large enough to produce a small dielectric loss angle, the silicon substrate act as a dielectric, which is quasi-TEM mode. 2) When the product of the frequency and substrate conductivity is large enough to yield a small depth of penetration into silicon, the silicon substrate act as a conductor wall, which is skin effect mode. 3) When the frequency is not so high and the resistivity is moderate, the slow wave mode occurs. TSVs have a similar structure to Si-SiO2 system and these three modes also exist in TSV structure [28]. A TSV pair is simulated in CST Microwave Studio [29] to investigate the three modes in TSVs. The conductivity of the silicon substrate is first set at  $\sigma = 0.01S/m$  and the electric field and magnetic field distribution at 0.5 GHz in silicon substrate are obtained as shown in Figure 22. Both electric field and magnetic field penetrates the silicon substrate indicates the TSV pair in the quasi-TEM mode. The conductivity of the silicon substrate is then set at  $\sigma = 5.8e7S/m$ . There is almost no electric field and magnetic field in the silicon substrate as shown in Figure 23, which indicate that the TSV pair in the skin effect mode. Later, the conductivity of the silicon substrate is set at  $\sigma = 10S/m$ . The electric field and magnetic field at 0.5GHz in silicon substrate are obtained as shown in Figure 24. Intrinsic impedance is calculated using the simulated electric and magnetic field values. The low intrinsic impedance of  $\eta = \frac{|E|}{|H|} = 58.2\Omega$  indicates the electrical field partially penetrates

the silicon substrate and verifies that the slow wave mode exists in the TSV pair.

Figure 19. Coupling waveform with substrate conductivity of 10 S/m and ground  $\,$  TSVs.

Figure 20. Coupling S-parameter between TSV-1 and TSV-13 with and without ground TSVs.

Figure 21. Three modes exist in Si-SiO2 system

Figure 22. Quasi-TEM mode (a) Electric field distribution, (b) Magnetic field distribution.

Figure 23. Skin effect mode (a) Electric field distribution (b) Magnetic field distribution.

Figure 24. Slow wave mode (a) Electric field distribution, (b) Magnetic field distribution.

# 3.4 Eye Diagram Analysis of TSV Arrays

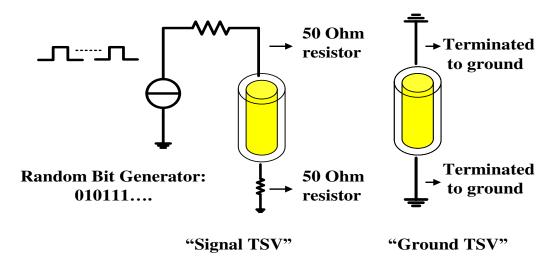

In this section, the eye diagram analysis of the TSV array structure is simulated. The TSV array structure used to obtain the eye diagrams is the same as in Figure 12. The same three test cases (a) (b) (c) as in Section 3.3 are used for simulation. In the eye diagram analysis, all the TSVs other than ground TSVs are defined as "signal TSVs". As shown in Figure 25, each signal TSV is connected with a 50 Ohm resistor and random bit generator. The random bit generators transmit different random bit sequences to the input of different signal TSVs. The bit rate of the random bit generator is set to be 5Gb/s.

Figure 25. Configuration of "Signal TSV" and "Ground TSV" in the TSV array for eye diagram analysis.

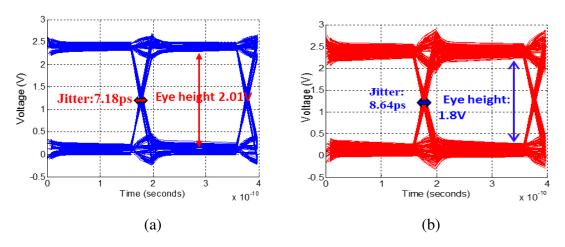

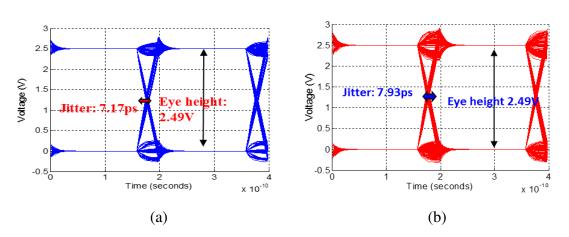

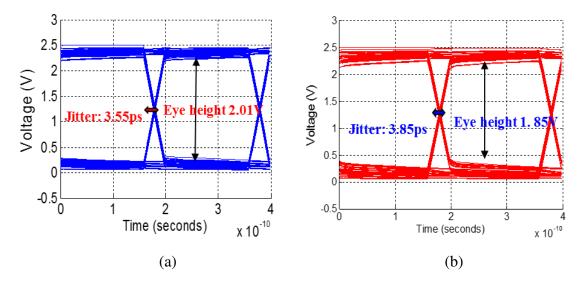

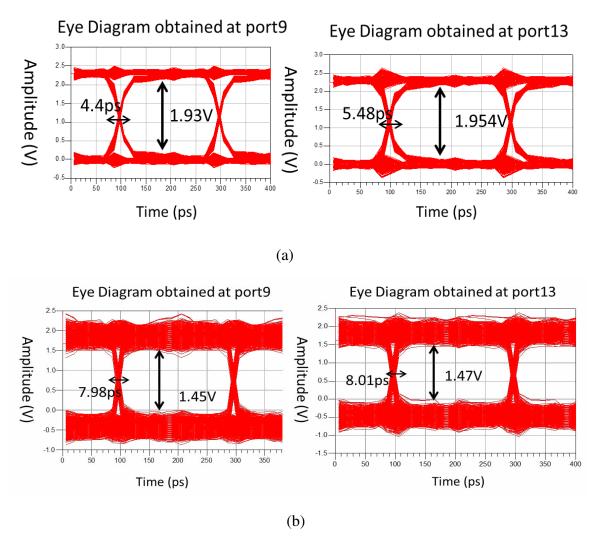

The simulated eye diagrams of TSV-1 and TSV-13 for case (a), (b) and (c) are shown in Figure 26, Figure 27, and Figure 28, respectively. The eye height and jitter of TSV-1 and TSV-13 for three cases are also simulated and summarized in Table 2.

Table 2. Eye height and jitter in case (a), (b) and (c)

| Ca       | ases   | Eye height (V) | Jitter (ps) |

|----------|--------|----------------|-------------|

| Case (a) | TSV-1  | 2.01           | 7.18        |

|          | TSV-13 | 1.8            | 8.64        |

| Case (b) | TSV-1  | 2.49           | 7.17        |

|          | TSV-13 | 2.49           | 7.93        |

| Case (c) | TSV-1  | 2.01           | 3.55        |

|          | TSV-13 | 1.85           | 3.85        |

Case a: Since the low resistivity substrate is used, the increased coupling and long tail of the coupled noise (Figure 17) will deteriorate the signal transmitted, which change the rise/fall times and amplitude of the signals, similar to pulse deterioration due to inter symbol interference (ISI). Therefore the coupling and long tail of the coupled noise causes variability in the eye height and increases jitter for TSV-1 and 13, as shown in Figure 26.

Figure 26. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 10 S/m).

Case b: As shown in Figure 27, for high resistivity substrates, since the coupled noise has narrow width with low peak amplitude, the coupled noise has less effect on rise/fall times and amplitude of the signals transmitted. Therefore there is no variability in the eye height between TSV-1 and 13.

#### Figure 27. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 0.01 S/m).

Case c: The ground TSVs are used in the TSV array. The number of signal channels is reduced to 11 as a result of surrounding the signal TSVs with ground connections. There is no spike exists in the coupled waveform when multiple ground TSVs are included as shown in Figure 23, therefore the coupled waveform in case (c) has little impact on the rise/fall times of the signals. As a result, the jitter is reduced by 4ps compared to case (a) and (b) as shown in Figure 26. With shielding using ground TSVs, though the jitter can be reduced, as shown in Figure 28, there is still a long tail of the coupled waveform which will affect the amplitudes of the signals. Therefore the variability still exists in the eye height between TSV-1 and 13.

Figure 28. Eye diagram of (a) TSV-1 (b) TSV-13 (substrate conductivity: 10 S/m).

As can be seen from the results comparison in Figure 26-Figure 28, without using ground TSVs, there is overshoot in the eye diagrams for case (a) and (b), which is caused by the spike in the coupled waveform.

## 3.5 Summary

The TSV modeling approach using global cylindrical modal basis functions is briefly described in this chapter. This modeling approach classifies the multi-scale TSV structure into three parts: (a) Resistance and inductance extraction. (b) Substrate capacitance and conductance extraction, (c) Oxide capacitance extraction. Since only a small number of global basis functions are used, it can model large TSV arrays. The CPU time comparison using this approach and the commercial full-wave solver CST Microwave Studio [29] are compared in [16] and shown in Table 3.

Table 3. CPU time Comparison of the CST and proposed method

|                | CST (sec.) | Proposed method (sec.) | Number of freq. point |

|----------------|------------|------------------------|-----------------------|

| Three TSVs     | 8608       | 773                    | 50                    |

| Four TSVs      | 10694      | 1227.24                | 50                    |

| 5×5 TSV arrays | N/A        | 16555.77               | 40                    |

TsVs in large TsV arrays and determine their effect on signal integrity. Coupling for low resistivity substrates induces variability in signal integrity across the silicon interposer which can be a major problem. Depending on the signal to ground ratio, the jitter can increase as well. Though this issue can be solved by using a silicon substrate with high resistivity, it is not a practical solution from a manufacturing stand-point due to the cost and infrastructure. Hence, alternate methods are required to address the variability issue to address signal integrity in silicon interposers with low resistivity.

## **CHAPTER 4**

# MODELING OF NON-UNIFORM THROUGH-SILICON VIA USING SPECIALIZED BASIS FUNCTIONS

## 4.1 Introduction

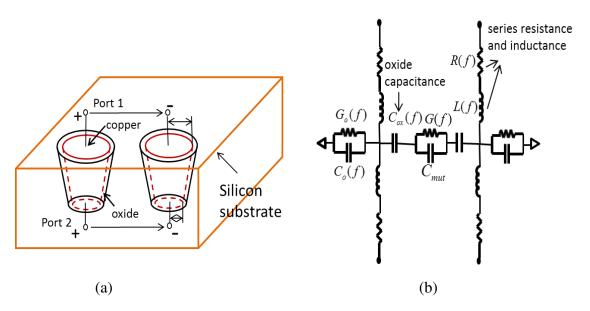

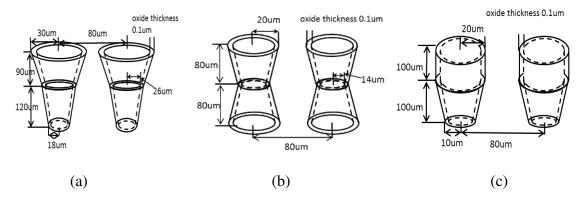

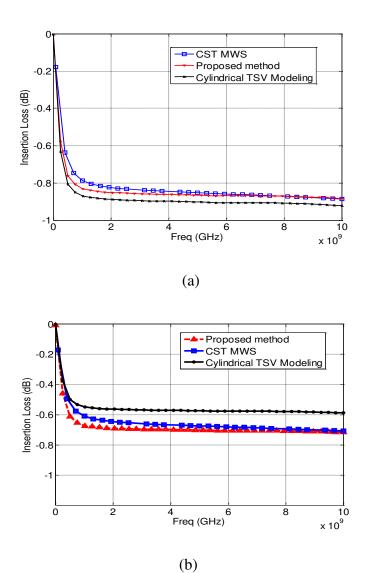

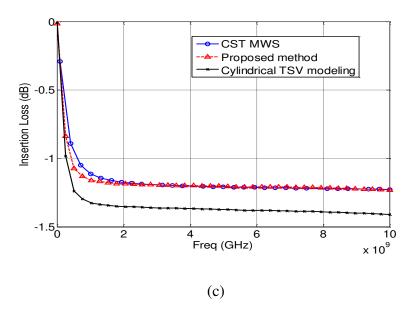

TSVs are treated as cylindrical structures in the modeling method described in CHAPTER 3. However, in reality, the fabricated TSVs sometimes end up with a non-uniform structure as shown in Figure 29. The tapered TSVs have different reflection noise, signal loss and parasitic effects compared to cylindrical TSVs. In this chapter, a hybrid approach for electromagnetic modeling of non-uniform through-silicon vias (TSVs) in three dimensional integrated circuits (3D ICs) is proposed. For non-uniform TSV structures, TSVs are divided vertically into conical and cylindrical sections. The modeling of the conical TSV is extended from [16] and uses conical modal basis functions to extract electrical parasitic elements of conical TSVs. By using the conical TSV modeling method combined with cylindrical TSV modeling method, complex TSV structures can be modeled efficiently [30]. The accuracy of this hybrid method is validated by comparison with 3-D full-wave simulations.

(a)

Figure 29. Cross-sectional image of real TSV structure, (a) SEM cross-section view of laser drilled blind vias in silicon[31], (b) SEM cross-section of TSV after integration [32], (c) cross-section of 3D-WLP TSV [33].

## **4.2 Conical TSV Modeling**

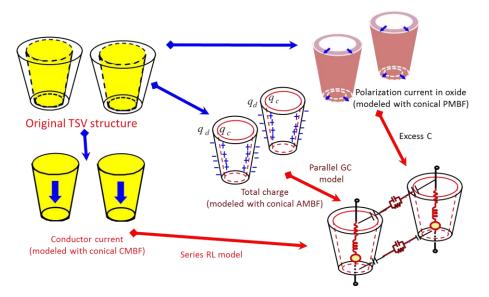

The structure of conical TSVs is similar to cylindrical TSVs except the conical contour. Therefore, the conical TSV modeling procedure can be divided into three parts similar as [16]: (1) Resistance and inductance extraction, which represents the loss and inductive coupling in conductors. (2) Substrate parallel conductance and capacitance extraction, which represents the loss and capacitive coupling between conductor and insulator surfaces. (3) Excess capacitance extraction, which represents the effect of the insulator between conductor and silicon substrate. The modeling flow for a conical TSV pair is shown in Figure 30.

Figure 30. Modeling flow for a conical TSV pair.

#### 4.2.1 Conical Conductor Series Resistance and Inductance Extraction

The electrical field integral equation (EFIE) [34] used to extract resistance and inductance of the conical conductor is the same as in [14], but V in equation (11) is extended to the conical volume of the conductor.

$$\frac{\vec{J}(\vec{r},\omega)}{\sigma} + \frac{j\omega\mu}{4\pi} \int_{V'} G(\vec{r},\vec{r}') \vec{J}(\vec{r}',\omega) dV' = -\nabla\Phi(\vec{r},\omega)$$

(11)

After inserting the approximation of the current density in equation (12) and applying Galerkin's method, equation (13) can be obtained.

$$\vec{J}_{j}(\vec{r},\omega) \cong \sum_{n,q} \vec{I}_{jnq} \vec{w}_{jnq}(\vec{r},\omega)$$

(12)

$$\sum_{n,q} I_{jnq} R_{imd,jnq} + j\omega \sum_{n,q} I_{jnq} L_{imd,jnq} = \Delta V_{imd}^{j}$$

(13)

where

$$R_{imd,jnq} = \frac{1}{\sigma} \int_{V_i} \vec{w}_{imd}^*(\vec{r}_i, \omega) \cdot \vec{w}_{jnq}(\vec{r}_j, \omega), L_{imd,jnq} = \frac{\mu}{4\pi} \int_{V_j V_i} \vec{w}_{imd}^*(\vec{r}_i, \omega) \cdot \vec{w}_{jnq}(\vec{r}_j, \omega) \frac{1}{|\vec{r}_i - \vec{r}_j|} dV_j dV_i$$

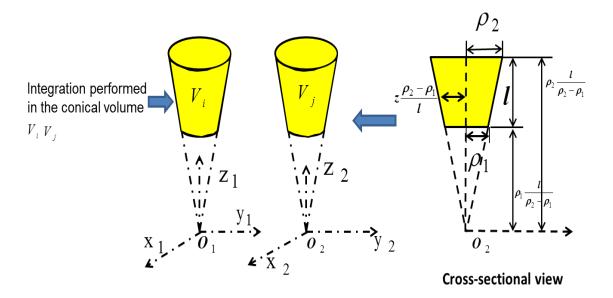

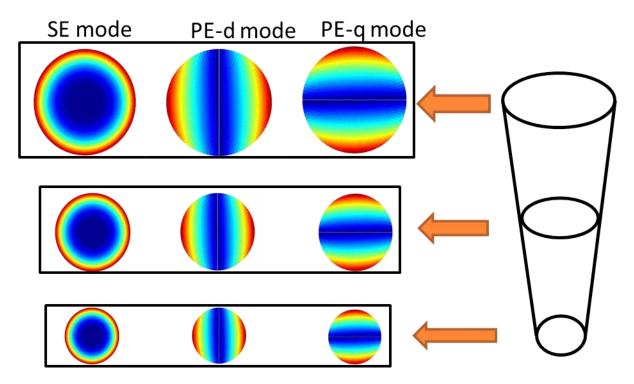

$\vec{w}_{jnq}(\vec{r}_i, w)$  is the normalized jnq th order conical conduction modal basis functions (CMBF), and j, n, q represent the index of the cell, modal order and orientation of conical CMBF, respectively.  $V_i, V_j$  in equation (13) are conical volumes. Partial resistance and partial inductance can be obtained by numerically integrating in the conical volume  $V_i, V_j$  shown in Figure 31. The conical CMBFs are obtained by modifying the normalization factor of cylindrical CMBFs [14]. The normalization factor of conical CMBFs is a function of the conical cross-sectional radius, described in equation (14). The skin effect (SE) and proximity effect (PE) mode of conical CMBFs at different cross-section of the conical structure are plotted in Figure 32. As can be seen from Figure 32,

the radius of the conical CMBFs is changing according to the radius of the conical structure.

To calculate the integral in equation (13), the coordinates are defined as shown in Figure 31. Therefore, after substituting the basis function  $\frac{1}{A_{in}}J_n(\alpha\rho)\cos(n\varphi_i-\varphi_d)$  [14], the original equation to calculate partial resistance and inductance can be expanded as equation 0 and equation (16), respectively.

$$A_{in} = \begin{cases} \frac{2\pi\rho}{\alpha} J_1(\alpha\rho) & n = 0\\ \frac{2^{2-n}\alpha^n \rho^{2+n}}{(2+n)n!} F_2(1 + \frac{n}{2}; \{2 + \frac{n}{2}, 1 + n\}; -\frac{1}{4}\alpha^2 \rho^2) & n > 0 \end{cases}$$

(14)

Figure 31. Definition of coordinate used to calculate numerical integral.

$$R_{imd,jnq} = \frac{1}{\sigma} \int_{0}^{2\pi} \cos(m\varphi_{i} - \varphi_{d}) \cos(n\varphi_{j} - \varphi_{q}) d\varphi \int_{\rho_{1}}^{\rho_{2}} \frac{1}{\rho_{2} - \rho_{1}} \frac{1}{A_{in}A_{jm}^{*}} dz \int_{0}^{z\frac{\rho_{2} - \rho_{1}}{l}} \frac{1}{\rho J_{m}(\alpha^{*}\rho)J_{n}(\alpha\rho)d\rho}$$

(15)

$$L_{imd,jnq} = \frac{\mu}{8\pi} \int_{\rho_{1}}^{\rho_{2}} \int_{\rho_{2}-\rho_{1}}^{\rho_{2}} \int_{\rho_{1}}^{\rho_{2}-\rho_{1}} \frac{1}{A_{im}^{*}A_{jn}} \frac{1}{\left|\vec{r}_{i}-\vec{r}_{j}\right|} dz \int_{0}^{z\frac{\rho_{2}-\rho_{1}}{l}} \int_{0}^{z\frac{\rho_{2}-\rho_{1}}{l}} \rho J_{m}(\alpha^{*}\rho_{i})J_{n}(\alpha\rho_{j})I_{\varphi}d\rho_{i}d\rho_{j}$$

(16)

Figure 32. Conical CMBFs at different cross-section of the conical structure at 0.1 GHz.

#### 4.2.2 Substrate Conductance and Capacitance Extraction of Conical TSVs

The Scalar Potential Integral Equation (SPIE) equation [35] combined with conical accumulation mode basis functions (AMBFs) can be used to extract substrate parallel conductance and capacitance. The conical AMBFs are obtained by modifying the normalization factor of cylindrical AMBFs [35]. The extraction procedure of conductance and capacitance is extended from [35] by changing the cylindrical TSV surfaces to conical TSV surfaces. The resultant equivalent circuit equation is expressed as:

$$\sum_{n,a} Q_{knq} P_{lmd,knq}^{C,D} = V_{lmd}^{k} \tag{17}$$

where

$$P_{lmd,knq}^{C,D} = \frac{1}{4\pi\varepsilon_0} \int_{S_l} \int_{S_k} v_{lmd}(\vec{r_l}) v_{knq}(\vec{r_k}) \frac{1}{|\vec{r_l} - \vec{r_k}|} dS_k dS_l$$

$v_{lmd}(\vec{r_l})$  is the normalized lmd th order conical AMBF. l,m,d represent the index of the cell, order and orientation of conical AMBF, respectively.  $S_l, S_k$  are the lateral conical surfaces. Partial potential coefficients  $P_{lmd,knq}^{C,D}$  can be obtained by calculating the integral over the conical surfaces  $S_l, S_k$ .

The normalization factor of a conical AMBF is obtained by equating the integration of the basis function over the lateral conical surface to unity, which is expressed as in equation (18).

$$A_{lm} = \begin{cases} \pi(\rho_1 + \rho_2)\sqrt{l^2 + (\rho_2 - \rho_1)^2} & m = 0\\ 2(\rho_1 + \rho_2)\sqrt{l^2 + (\rho_2 - \rho_1)^2} & m > 0 \end{cases}$$

(18)

In order to calculate the surface integral in equation (17), we first transform the Cartesian coordinates to circular conical coordinates. Then equation (17) can be expanded as shown in equation (19), which is used to calculate the potential coefficients.

$$P_{lmd,kmq} = \frac{1}{4\pi\varepsilon_0} \int_{\rho_1}^{\rho_2} \int_{\rho_1-\rho_1}^{\rho_2} \int_{\rho_1-\rho_1}^{\rho_2} dz dz' \int_{0}^{2\pi^2\pi} v_{lmd}(\vec{r_l}) v_{knq}(\vec{r_k}) \frac{1}{|\vec{r_l}-\vec{r_k}|} \left\| \frac{\partial \Phi}{\partial \varphi}(\varphi,z) \times \frac{\partial \Phi}{\partial t}(\varphi,z) \right\| \cdot \left\| \frac{\partial \Phi'}{\partial \varphi}(\varphi,z) \times \frac{\partial \Phi'}{\partial \varphi}(\varphi,z) \times \frac{\partial \Phi'}{\partial \varphi}(\varphi,z) \right\| d\varphi d\varphi$$

(19)

where

$$\left\| \frac{\partial \Phi}{\partial \varphi}(\varphi, z) \times \frac{\partial \Phi}{\partial \varphi}(\varphi, z) \right\| = z \left( \frac{\rho_2 - \rho_1}{l} \right) \sqrt{1 + \left( \frac{\rho_2 - \rho_1}{l} \right)^2} \quad \left\| \frac{\partial \Phi'}{\partial \varphi}(\varphi, z) \times \frac{\partial \Phi'}{\partial \varphi}(\varphi, z) \right\| = z \left( \frac{\rho_2' - \rho_1'}{l} \right) \sqrt{1 + \left( \frac{\rho_2' - \rho_1'}{l} \right)^2}$$

#### 4.2.3 Oxide Liner Excess Capacitance Extraction of Conical TSV

To calculate the oxide liner excess capacitance, the EFIE equation combined with conical polarization mode basis functions (PMBFs) can be used. The conical PMBFs are obtained by modifying the normalization factor of the cylindrical PMBFs [16] which are

deduced from solving the Laplace's equation in the insulator region. The oxide capacitance extraction procedure is extended from [16] by changing the integral volume to a conical annulus. The resultant oxide capacitance calculation formula is given as the following equation (20):

$$C_{kmd,\ln q}^{ex} = \frac{\varepsilon_0 (\varepsilon_{ox} - \varepsilon_{si})}{\int_{V_k} \vec{u}_{kmd} \cdot \vec{u}_{lnq} dV_k}$$

(20)

where  $\vec{u}_{kmd}$  is the conical PMBF. k, m, d represent the index of the cell, order and orientation of conical PMBF, respectively.  $V_k$  in equation (20) is the conical oxide region as shown in Figure 33.

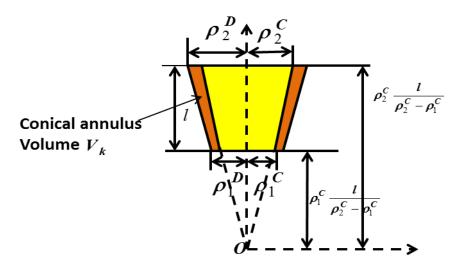

Figure 33. Parameters used to calculate oxide capacitance.

The normalization factor of the conical PMBFs is obtained by equating the integration of the basis function over the lateral surface to unity. Given the parameters of conical TSVs defined as shown in Figure 33, the normalization factor of conical PMBFs can be expressed as equation (21). Given the coordinate system defined as in Figure 32, the oxide capacitance calculation formula (20) can be expressed as equation (22).

$$A_{lm} = \begin{cases} 2\pi\sqrt{l^2 + (\rho_2^D - \rho_1^D)} & m = 0\\ 4\sqrt{l^2 + (\rho_2^D - \rho_1^D)} \{ \frac{(\rho_2^D - \rho_1^D)^m}{(\rho_2^C - \rho_1^C)^m} + \frac{(\rho_2^D - \rho_1^D)^{-m}}{(\rho_2^C - \rho_1^C)^{-m}} \} & m > 0 \end{cases}$$