# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

5,900

Open access books available

145,000

180M

Downloads

Our authors are among the

154

Countries delivered to

**TOP 1%**

most cited scientists

12.2%

Contributors from top 500 universities

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# **Modeling of Spiral Inductors**

Kenichi Okada and Kazuya Masu Tokyo Institute of Technology Japan

# 1. On-Chip Inductors

This section explains overview of the on-chip inductors. Demand for on-chip inductors has been increasing especially for CMOS RF circuits. An on-chip inductor is a key component because its performance directly affects the circuit performance and the chip cost. The on-chip inductors have been used, for example, as a matching network component, as baluns, and as an inductive load. The requirements for on-chip inductors are to have an appropriate inductance value, high self-resonance frequency, and high-quality factor Q, and to occupy a small layout area. In this section, several types of on-chip inductors are introduced.

#### 1.1 Classification of on-chip inductors

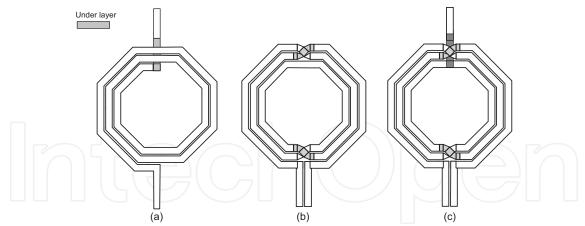

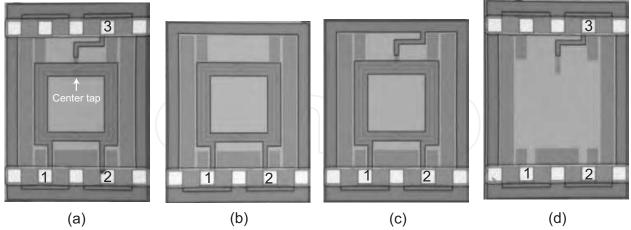

A spiral inductor is one of the most common structures among on-chip inductors, and there are some variants of spiral inductor. Figure 1 shows spiral inductors commonly used as an on-chip inductor. Figure 1(a) is a single-ended type of spiral inductor, which has a spiral trace with an underpass. The spiral trace is made on top metal layer, and the underpass is made on lower metal layer. Spiral inductors are usually characterized by the diameter, the line width, the number of turns, and the line-to-line space.

Symmetric inductors are often used for differential circuits, *e.g.*, voltage controlled oscillator, low noise amplifier, mixer, *etc*. Figures 1(b) and (c) show symmetric spiral inductors with/without a center tap. The center tap is used to obtain a connection to the center node of symmetric inductor. The symmetric inductor achieves chip area reduction rather than using two single-ended spiral inductors to realize a symmetric structure. The single-ended inductor usually has only one underpass while the symmetric one has some underpasses depending on the number of turns. The underpass has larger resistance caused by inter-layer vias, which degrades quality factor.

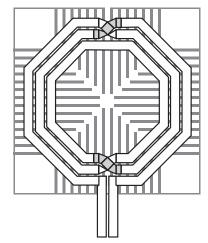

Patterned ground shield (PSG) is sometimes employed to reduce substrate loss as shown in Fig. 2. As a drawback, capacitance between the spiral metal and the shield is increased, and self-resonance frequency is also decreased.

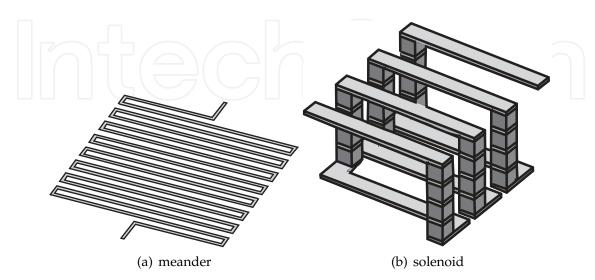

Figure 3 shows a meander inductor and a solenoid inductor, which are sometimes employed. The meander inductor does not have underpasses while area efficiency is not good due to negative line-to-line mutual inductance. The solenoid inductor can be implemented vertically by using multiple metal layers. Area efficiency is high even though quality factor is not good due to multiple via connections.

Fig. 1. On-chip spiral inductors. (a) single-ended (b) symmetric (c) symmetric with a center tap

Fig. 2. Spiral inductor with patterned ground shield (PSG).

Fig. 3. On-chip inductors.

# 2. Modeling of 2-Port and 3-Port Inductors

This section explains how to derive inductance and quality factor from measured S-parameters or Y-parameters for various excitation modes.

Definition of inductance and quality factor of on-chip inductors is not unique, and there are actually several definitions. The reason is that inductance and quality factor depend on excitation mode of input ports. In this section, an equivalent circuit model is shown, and derivation methods of the parameters in various excitation modes are explained. First, derivation for 2-port inductors is explained. Next, generic 3-port characterization is explained, and then, experimental results using measurements are shown.

# 2.1 Modeling of 2-port inductors

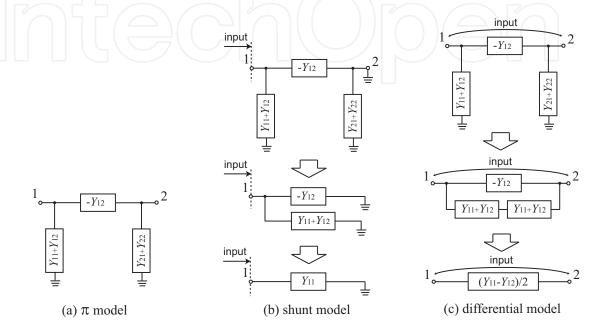

Here, a traditional  $\pi$ -type equivalent circuit is introduced for simple two-port inductors, and the derivation of inductance and quality factor is explained.

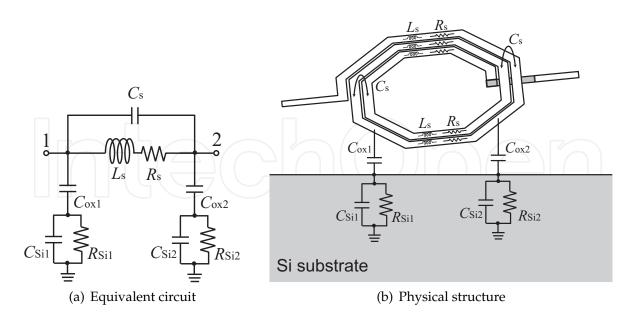

Figure 4(a) shows a common equivalent circuit model for 2-port inductors, utilized for CMOS LSIs, and Fig. 4(b) shows a physical structure of the inductor. Each parameter in Fig. 4(a) is related to the structure<sup>1</sup>. Actually, the  $\pi$ -type lumped equivalent circuit is usually utilized even if these RLC components are distributed.  $L_{\rm S}$  is inductance of the spiral wire, and  $R_{\rm S}$  means resistance of it.  $C_{\rm S}$  is line-to-line capacitance of the spiral wire.  $C_{\rm Ox}$  means capacitance between the wire and substrate.  $C_{\rm Si}$  and  $R_{\rm Si}$  mean capacitance and resistance in the Si substrate, respectively.

The equivalent circuit in Fig. 4(a) can express characteristics of on-chip inductors with frequency dependence, and each part of the equivalent circuit can be derived from Y-parameters according to the definition of Y-parameter as shown in Fig. 5(a). In this case,  $Y_{12}$  and  $Y_{21}$  are supposed to be equal to each other.

Fig. 4. An equivalent circuit model for a 2-port inductor.

<sup>&</sup>lt;sup>1</sup> Unfortunately, the parameters are not exactly agreed with values calculated from the physical structure.  $R_s$  sometimes becomes almost twice because of eddy current in Si substrate, which is not characterized by the equivalent circuit model shown in Fig. 4(a).

$L_{\rm s}$  can be derived from  $Y_{12}$ . However,  $L_{\rm s}$  is usually not utilized to evaluate an on-chip inductor because it is not an effective value used in a circuit. Actually, the inductance of on-chip inductor becomes zero at high frequency due to parasitic capacitances. To express this frequency dependence, inductance defined by  $Y_{11}$  is commonly employed. The reason is explained as followed. As explained, inductance and quality factor depend on each port impedance, and inductors are often used at a shunt part as shown in Fig. 6(a). In this case, input impedance of the inductor can be calculated by  $1/Y_{11}$  as shown in Fig. 5(b).

Fig. 5. Y-parameter calculation.

Fig. 6. Inductor usage.

$L_{\text{shunt}}$  and  $Q_{\text{shunt}}$  are defined by the following equations.

$$L_{\text{shunt}} = \frac{\text{Im}\left(\frac{1}{Y_{11}}\right)}{\omega} \tag{1}$$

$$L_{\text{shunt}} = \frac{\operatorname{Im}\left(\frac{1}{Y_{11}}\right)}{\omega}$$

$$Q_{\text{shunt}} = \frac{\operatorname{Im}\left(\frac{1}{Y_{11}}\right)}{\operatorname{Re}\left(\frac{1}{Y_{11}}\right)}$$

$$= -\frac{\operatorname{Im}\left(Y_{11}\right)}{\operatorname{Re}\left(Y_{11}\right)}$$

$$= 3$$

$$(3)$$

This definition (1)(3) is widely used because the definition does not depend on equivalent circuits and only  $Y_{11}$  is required to calculate them.

In case using the equivalent circuit in Fig. 4(a),  $Y_{11}$  can be derived by the following equation.

$$Y_{11} = \frac{1}{R_{\rm s} + j\omega L_{\rm s}} + j\omega C_{\rm s} + j\omega C_{\rm ox1} // \left(\frac{1}{R_{\rm Si1}} + j\omega C_{\rm Si1}\right),\tag{4}$$

and it can be approximated at lower frequency as follows.

$$1/Y_{11} \approx R_{\rm s} + j\omega L_{\rm s} \tag{5}$$

This means that  $L_{\rm shunt}$  and  $Q_{\rm shunt}$  are close to  $L_{\rm s}$  and  $\omega L_{\rm s}/R_{\rm s}$  at lower frequency, respectively, and they are decreased by the parasitic capacitances at higher frequency.

On the other hand, on-chip inductors are often used in differential circuits as shown in Fig. 6(b). In this case, the inductor has different characteristics from the shunt case shown in Fig. 6(a), and the input impedance in differential mode becomes  $\frac{4}{Y_{11}+Y_{22}-Y_{12}-Y_{21}}$  while the input impedance in single-ended mode is  $1/Y_{11}$ . The detailed calculation is explained in Sect. 2.2. Thus, effective inductance  $L_{\text{diff}}$  and effective quality factor  $Q_{\text{diff}}$  in differential mode can be calculated by using the differential input impedance  $\frac{4}{Y_{11}+Y_{22}-Y_{12}-Y_{21}}$  as follows.

$$L_{\text{diff}} = \frac{\text{Im}\left(\frac{4}{Y_{11} + Y_{22} - Y_{12} - Y_{21}}\right)}{\omega}$$

$$Q_{\text{diff}} = \frac{\text{Im}\left(\frac{4}{Y_{11} + Y_{22} - Y_{12} - Y_{21}}\right)}{\text{Re}\left(\frac{4}{Y_{11} + Y_{22} - Y_{12} - Y_{21}}\right)}$$

$$= -\frac{\text{Im}\left(Y_{11} + Y_{22} - Y_{12} - Y_{21}\right)}{\text{Re}\left(Y_{11} + Y_{22} - Y_{12} - Y_{21}\right)}$$

$$(8)$$

For symmetric inductors,  $Y_{22}$  and  $Y_{21}$  are approximately equal to  $Y_{11}$  and  $Y_{12}$ , respectively, so the following approximated equations can also be utilized as shown in Fig. 5(c).

$$L_{\text{diff}} \approx \frac{\text{Im}\left(\frac{2}{Y_{11} - Y_{12}}\right)}{\omega}$$

$$Q_{\text{diff}} \approx -\frac{\text{Im}\left(Y_{11} - Y_{12}\right)}{\text{Re}\left(Y_{11} - Y_{12}\right)}$$

$$(9)$$

$$Q_{\text{diff}} \approx -\frac{\text{Im}(Y_{11} - Y_{12})}{\text{Re}(Y_{11} - Y_{12})}$$

(10)

In a similar way to Eq.(4), the following equation can also be derived from Fig. 4. Examples of calculation of the above parameters will be explained in Sect. 2.5.

$$\frac{Y_{11} + Y_{22} - Y_{12} - Y_{21}}{4}$$

$$= \frac{1}{R_{s} + j\omega L_{s}} + j\omega C_{s}$$

$$+ \left\{ j\omega C_{ox1} // \left( \frac{1}{R_{Si1}} + j\omega C_{Si1} \right) \right\} // \left\{ j\omega C_{ox2} // \left( \frac{1}{R_{Si2}} + j\omega C_{Si2} \right) \right\}$$

(12)

### 2.2 Equivalent circuit model for 3-port inductors

A symmetric inductor with a center tap has 3 input ports as shown in Fig. 1(c). The characteristics of symmetric inductor depend on excitation modes and load impedance of center-tap, i.e., single-ended mode, differential mode, common mode, center-tapped and non-center-tapped. Unfortunately, 2-port measurement of the 3-port inductors is insufficient to characterize the 3-port ones in all operation modes. Common-mode impedance of center-tapped inductor has influence on circuit performance, especially about CMRR of differential amplifiers, pushing of differential oscillators, etc, so 3-port characterization is indispensable to simulate commonmode response in consideration of the center-tap impedance. The characteristics of symmetric inductor can be expressed in all operation modes by using the measured S parameters of the 3-port inductor. In this section, derivation method using 3-port S-parameters is explained to characterize it with the center-tap impedance.

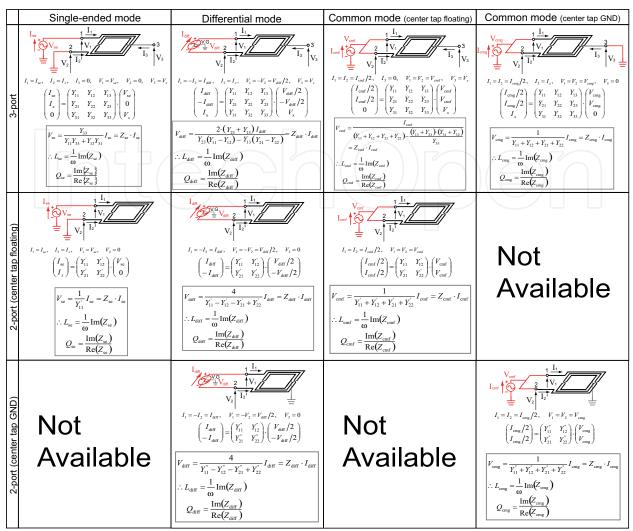

# 2.3 Derivation using Y-parameters

Inductance L and quality factor Q of 3-port and 2-port inductors can be calculated by using measured Y parameters. The detailed procedure is explained as follows. First, input impedance is calculated for each excitation mode, i.e., single-ended, differential, common. In case of common mode, the impedance depends on the center-tap impedance  $Y_3$ , so the input impedance is a function of the center-tap impedance  $Y_3$ . Next, inductance L and quality factor Q are calculated from the input impedance as explained in Sect. 2.1.

In case using 3-port measurements in differential mode, differential-mode impedance Z<sub>diff</sub> can be derived as follows.

$$\begin{pmatrix} I_{\text{diff}} \\ -I_{\text{diff}} \\ I_{3} \end{pmatrix} = \begin{pmatrix} Y_{11} & Y_{12} & Y_{13} \\ Y_{21} & Y_{22} & Y_{23} \\ Y_{31} & Y_{32} & Y_{33} \end{pmatrix} \cdot \begin{pmatrix} V_{\text{diff}}/2 \\ -V_{\text{diff}}/2 \\ V_{3} \end{pmatrix}$$

(13)

$$Z_{\text{diff}} = \frac{V_{\text{diff}}}{I_{\text{diff}}} = \frac{2(Y_{23} + Y_{13})}{Y_{23}(Y_{11} - Y_{12}) - Y_{13}(Y_{21} - Y_{22})}$$

(14)

Note that this differential impedance  $Z_{\text{diff}}$  does not depend on the center-tap impedance  $Y_3$ . Inductance  $L_{\text{diff}}$  and quality factor  $Q_{\text{diff}}$  are calculated with  $Z_{\text{diff}}$  by the following equations.

$$L_{\text{diff}} = \frac{\text{Im}\left[Z_{\text{diff}}\right]}{\omega} \tag{15}$$

$$L_{\text{diff}} = \frac{\text{Im} [Z_{\text{diff}}]}{\omega}$$

$$Q_{\text{diff}} = \frac{\text{Im} [Z_{\text{diff}}]}{\text{Re} [Z_{\text{diff}}]}$$

(15)

Fig. 7. Equations derived from Y parameter to evaluate L and Q of 2-port and 3-port inductors.

In case using 3-port measurements in common mode, common-mode impedance  $Z_{cm}$  can be derived as follows.

$$\begin{pmatrix}

I_{\rm cm}/2 \\

I_{\rm cm}/2 \\

I_3

\end{pmatrix} = \begin{pmatrix}

Y_{11} & Y_{12} & Y_{13} \\

Y_{21} & Y_{22} & Y_{23} \\

Y_{31} & Y_{32} & Y_{33}

\end{pmatrix} \cdot \begin{pmatrix}

V_{\rm cm} \\

V_{\rm cm} \\

V_3

\end{pmatrix}$$

(17)

$$Z_{\rm cm} = \frac{V_{\rm cm}}{I_{\rm cm}} = \frac{1}{(Y_{11} + Y_{12} + Y_{21} + Y_{22}) + \frac{(Y_{13} + Y_{23})(Y_{31} + Y_{32})}{Y_3 - Y_{33}}}$$

(18)

where the center-tap impedance  $Y_3$  is given by  $I_3/V_3$ . Note that the common-mode impedance  $Z_{cm}$  depends on the center-tap impedance  $Y_3$ . Inductance  $L_{cm}$  and quality factor  $Q_{cm}$  in common mode are calculated with  $Z_{cm}$  by the following equations.

$$L_{\rm cm} = \frac{\rm Im} [Z_{\rm cm}] \tag{19}$$

$$L_{cm} = \frac{\operatorname{Im} [Z_{cm}]}{\omega}$$

$$Q_{cm} = \frac{\operatorname{Im} [Z_{cm}]}{\operatorname{Re} [Z_{cm}]}$$

(20)

Figure 7 summarizes calculation of L and Q from 2-port and 3-port Y-parameters. The 2-port symmetric inductor has two types of structures, center-tapped and non-center-tapped ones. It is impossible to characterize the center-tapped inductor only from measurement of non-center-tapped one. On the other hand, all characteristics can be extracted from the Y parameters of 3-port inductor due to its flexibility of center-tap impedance. Therefore, we need 3-port inductor to characterize all operation modes of symmetric inductors.

The definition of quality factor in Eqs. (16) and (20) uses ratio of imaginary and real parts. The definition is very useful to evaluate inductors. On the other hand, it is not convenient to evaluate LC-resonators using inductors because the imaginary part in Eqs. (16) and (20) is decreased by parasitic capacitances, *e.g.*,  $C_{\rm s}$ ,  $C_{\rm oxn}$ ,  $C_{\rm Sin}$ . Quality factor of LC-resonator is higher than that defined by Eqs. (16) and (20). Thus, the following definition is utilized to evaluate quality factor of inductors used in LC-resonators.

$$Q = \frac{\omega}{2} \left| \frac{1}{Z} \frac{\partial Z}{\partial \omega} \right| \tag{21}$$

where *Z* is input impedance.

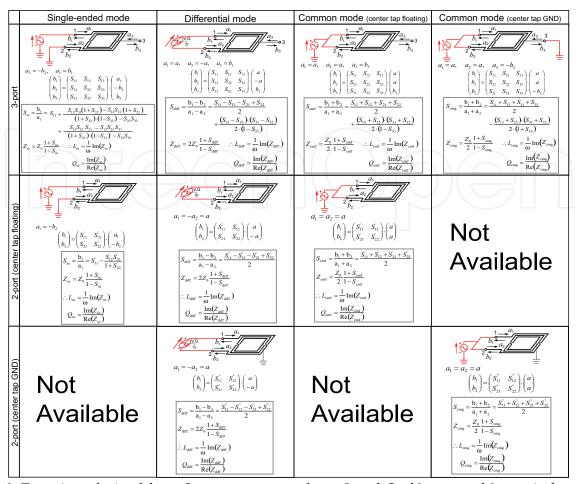

#### 2.4 Derivation using S-parameters

By the same way, inductance L and quality factor Q of 3-port and 2-port inductors can also be derived from S-parameters. As explained in Fig. 8, the input impedances for each excitation mode, e.g.,  $Z_{\rm diff}$ ,  $Z_{\rm cm}$ , can be derived from S-parameters as well as Y-parameters, and L and Q can also be calculated from the input impedance in a similar way.

# 2.5 Measurement and parameter extraction

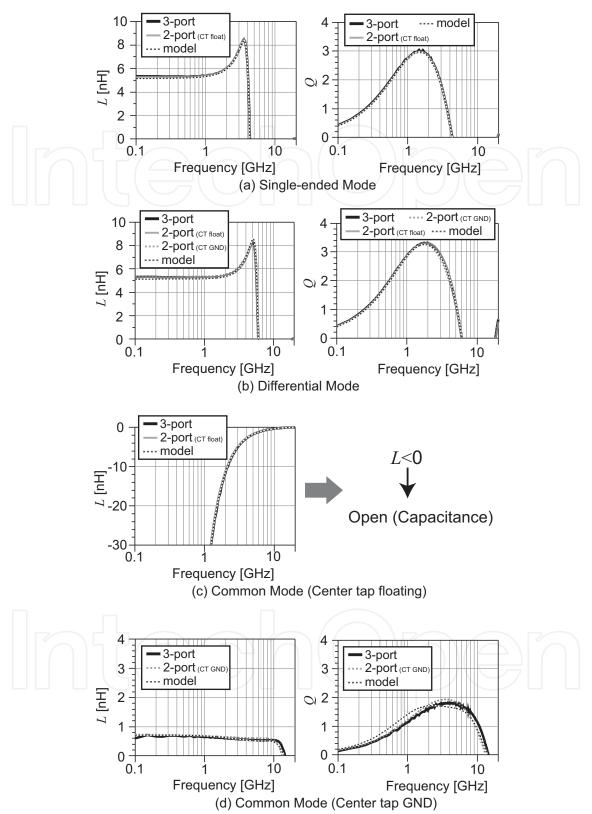

In this subsection, measurement and parameter extraction are demonstrated. Figure 9 shows photomicrograph of the measured symmetric inductors. The symmetrical spiral inductors are fabricated by using a 0.18  $\mu$ m CMOS process (5 aluminum layers). The configuration of the spiral inductor is 2.85 turns, line width of 20  $\mu$ m, line space of 1.2  $\mu$ m, and outer diameter of 400  $\mu$ m. The center tap of 3-port inductor is connected to port-3 pad. Two types of 2-port inductors are fabricated; non-center-tapped (center tap floating) and center-tapped (center tap GND) structures.

The characteristics of inductors are measured by 4-port network analyzer (Agilent E8364B & N4421B) with on-wafer probes. An open dummy structure is used for de-embedding of probe pads.

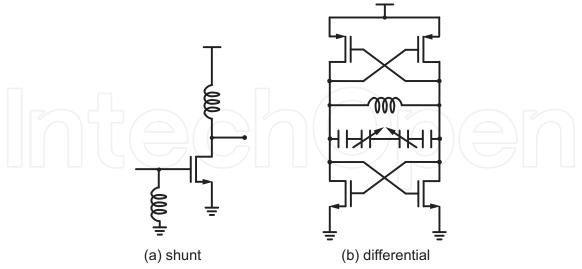

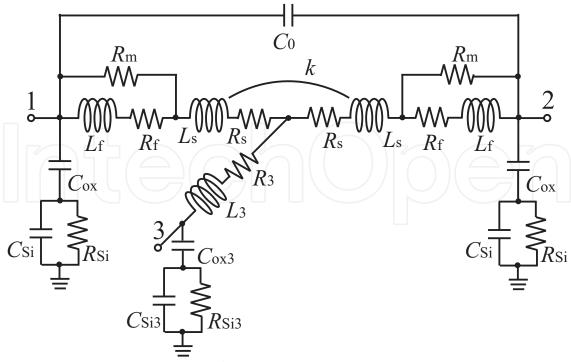

Several equivalent circuit models for symmetric inductor have been proposed Fujumoto et al. (2003); Kamgaing et al. (2002); Tatinian et al. (2001); Watson et al. (2004). This demonstration uses 3-port equivalent circuit model of symmetric inductor as shown in Fig. 10. This model uses compact model of the skin effect ( $R_{\rm m}$ ,  $L_{\rm f}$  and  $R_{\rm f}$ ) Kamgaing et al. (2002; 2004). Center tap is expressed by the series and shunt elements.

Figure 11 shows frequency dependences of the inductance L and the quality factor Q of measured 2-port and 3-port inductors and the equivalent circuit model for various excitation modes. L and Q of measured inductors can be calculated using Y parameters as shown in Fig. 7. Table 1 shows extracted model parameters of the 3-port equivalent circuit shown in Fig. 10. The parameters are extracted with numerical optimization.

In Figs. 11 (a) and (b), self-resonance frequency and Q excited in differential mode improve rather than those excited in single-ended mode due to reduction of parasitic effects in substrate Danesh & Long (2002), which is considerable especially for CMOS LSIs. In common

Fig. 8. Equations derived from *S* parameter to evaluate *L* and *Q* of 2-port and 3-port inductors.

Fig. 9. Photomicrograph of the measured symmetric inductors. (a) 3-port inductor. (b) 2-port inductor (center tap floating). (c) 2-port inductor (center tap GND). (d) Open pad. The center tap of 3-port inductor is connected to port-3 pad.

Fig. 10. An equivalent circuit model for a 3-port symmetric inductor.

| $L_{\rm s}$ [nH]                | $R_{\rm s}\left[\Omega\right]$   | $L_{\rm f}$ [nH]     | $R_{\mathrm{f}}\left[\Omega\right]$ | $R_{\rm m}\left[\Omega\right]$ |

|---------------------------------|----------------------------------|----------------------|-------------------------------------|--------------------------------|

| 1.34                            | 1.87                             | 0.91                 | 2.66                                | 14.6                           |

| $C_0$ [pF]                      | <i>L</i> <sub>3</sub> [nH]       | $R_3[\Omega]$        | C <sub>ox</sub> [pF]                | $C_{\text{ox3}}$ [pF]          |

| 0.08                            | 0.00                             | 0.25                 | 0.18                                | 0.19                           |

| $R_{\rm Si}\left[\Omega\right]$ | $R_{\rm Si3}\left[\Omega\right]$ | C <sub>Si</sub> [pF] | <i>C</i> <sub>Si3</sub> [pF]        | k                              |

| 24.7                            | 3.37                             | 0.01                 | 0.07                                | 0.44                           |

Table 1. Extracted Model Parameters of 3-port Symmetric Inductor

mode (center tap floating), L is negative value because inductor behaves as open Fujumoto et al. (2003) as shown in Fig. 11 (c). These characteristics extracted from 2-port and 3-port inductors agree with each other. In Fig. 11 (d), L and Q excited in common mode (center tap GND) are smaller because interconnections between input pads and center-tap are parallel electrically. The characteristics of the equivalent circuit model are well agreed with that of measured 3-port inductor in all operation modes. These results show measured parameter of 3-port inductor and its equivalent circuit model can express characteristics of symmetric inductor in all operation modes and connection of center tap.

Fig. 11. Frequency dependences of the inductance *L* and the quality factor *Q* in various excitation modes. (a) Single-ended mode. (b) Differential mode. (c) Common mode (center tap floating). (d) Common mode (center tap GND).

# 3. Modeling of Multi-Port Inductors

Multi-port inductors, like 3-, 4-, 5-port, 2-port symmetric one with a center-tap, *etc.*, are very useful to reduce circuit area?, ?. In this section, a generic method to characterize the multi-port inductors is presented??.

As a conventional method, one of the methods to characterize the multi-port inductor is to extract each parameter of an equivalent circuit by the numerical optimization. However, the equivalent circuit has to be consisted of many circuit components characterizing self and mutual effects, and it is not easy to extract these parameters considering all the mutual effects. In this section, a method utilizing a matrix-decomposition technique is presented, and the method can extract each self and mutual parameters mathematically, which contributes to improve the extraction accuracy. The method can also be used for charactering a differential inductor with a center-tap, which is a kind of 3-port inductor.

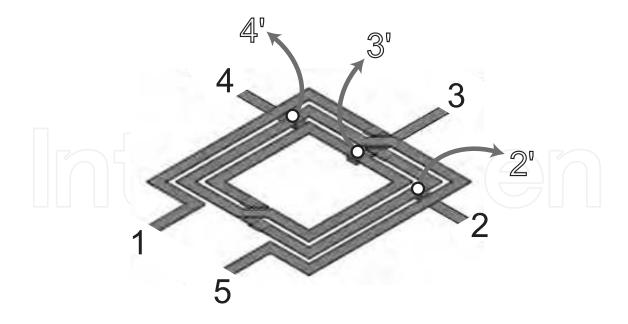

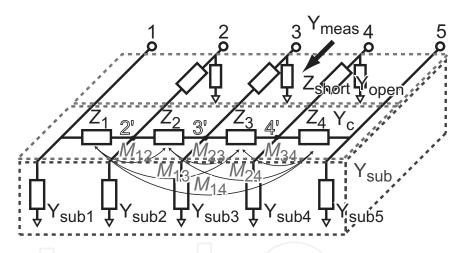

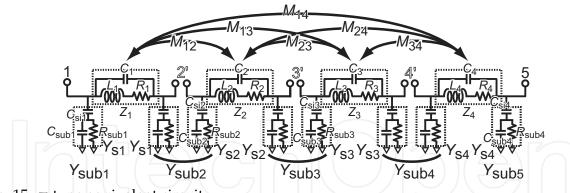

#### 3.1 Derivation of matrix $Y_c$

This section describes a method to decompose self and mutual inductances of multi-port inductors. A 5-port inductor shown in Fig. 12 is utilized as an example while the method can be also applied to generic multi-port inductors. Figure 13 shows an equivalent circuit of the 5-port inductor, which consists of core, shunt, and lead parts Long & Copeland (1997); Niknejad & Meyer (1998). The core part expresses self and mutual inductances with parasitic resistance and capacitance, which are characterized by  $Z_n$  in Fig. 13. The core part is also expressed by a matrix  $Y_c$ . The shunt part characterizes parasitics among Inter Layer Dielectric (ILD) and Si substrate. It is expressed by a matrix  $Y_{sub}$ . Ports 2, 3, and 4 have lead parts as shown in Fig. 12, which are modeled by  $Z_{short}$  and  $Y_{open}$  as shown in Fig. 13. On the other hand, a lead part of ports 1 and 5 is assumed to be a part of inductor as shown in Fig. 12.  $Y_{sub}$  consists of admittances  $Y_{subn}$  in Fig. 13. The lead part characterizes lead lines, and it is also expressed by matrix  $Y_{open}$  and  $Z_{short}$ . These matrices can be combined by the following equations.

$$Z_{\text{meas'}} = (Y_{\text{meas}} - Y_{\text{open}})^{-1}$$

$$- (Z_{\text{short}}^{-1} - Y_{\text{open}})^{-1}, \qquad (22)$$

$$Y_{\text{c}} = Y_{\text{meas'}} - Y_{\text{sub'}} \qquad (23)$$

where admittance matrix  $Y_{meas}$  is converted from measured S-parameter. To decompose each part of multi-port inductor in Fig. 13, first the matrix  $Y_{sub}$  is calculated. The matrix  $Y_{sub}$  can be expressed by admittances  $Y_{subn}$  as follows.

$$\mathbf{Y_{sub}} = \begin{pmatrix} Y_{\text{sub1}} & 0 & 0 & 0 & 0 \\ 0 & Y_{\text{sub2}} & 0 & 0 & 0 \\ 0 & 0 & Y_{\text{sub3}} & 0 & 0 \\ 0 & 0 & 0 & Y_{\text{sub4}} & 0 \\ 0 & 0 & 0 & 0 & Y_{\text{sub5}} \end{pmatrix}$$

(24)

For the sum of the matrices  $Y_c$  and  $Y_{sub}$ , the following equation can be defined by vectors v and i as defined in Fig. 14.

$$\begin{pmatrix}

i_1 \\

i_2 \\

i_3 \\

i_4 \\

i_5

\end{pmatrix} = \mathbf{Y_{meas'}} \begin{pmatrix}

v_1 \\

v_2 \\

v_3 \\

v_4 \\

v_5

\end{pmatrix} = (\mathbf{Y_c} + \mathbf{Y_{sub}}) \begin{pmatrix}

v_1 \\

v_2 \\

v_3 \\

v_4 \\

v_5

\end{pmatrix} \tag{25}$$

Fig. 12. Structure of the 5-port inductor.

Fig. 13. Equivalent circuit of the 5-port inductor.

$Y_{\text{meas'}}$  consists of  $Y_{\text{c}}$  and  $Y_{\text{sub}n}$ . The circuit part expressed by  $Y_{\text{c}}$  does not have a current path to ground as shown in Fig. 13. When  $v_1 = v_2 = v_3 = v_4 = v_5 = v'$ , no current flows into  $Z_n$  shown in Fig. 14, because  $Y_{\text{c}}$  connects to only ports and not ground. This is described by the following equation.

$$Y_{\mathbf{c}} \begin{pmatrix} v' \\ v' \\ v' \\ v' \end{pmatrix} = 0 \tag{26}$$

Fig. 14. Equivalent circuit of core.

The following equation is derived from Eqs.(25)(26)

$$\begin{pmatrix}

i_{1} \\

i_{2} \\

i_{3} \\

i_{4} \\

i_{5}

\end{pmatrix} = Y_{\text{meas}'} \begin{pmatrix}

v' \\

v' \\

v' \\

v' \\

v' \end{pmatrix} = Y_{\text{sub}} \begin{pmatrix}

v' \\

v' \\

v' \\

v' \\

v' \end{pmatrix} = \begin{pmatrix}

Y_{\text{sub1}} \\

Y_{\text{sub2}} \\

Y_{\text{sub3}} \\

Y_{\text{sub4}} \\

Y_{\text{sub5}}

\end{pmatrix} v'$$

(27)

Therefore, each  $Y_{\text{sub}n}$  in  $Y_{\text{sub}}$  can be calculated by the following equation.

$$Y_{\text{sub}n} = \sum_{i=1}^{5} Y_{\text{meas}'ni}$$

(28)

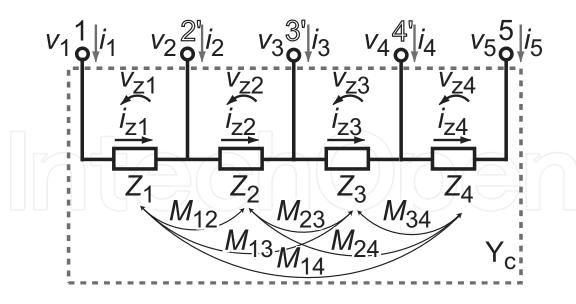

# 3.2 Conversion of matrix $Y_c$ to $Z_{core}$

Figure 14 shows the core part of the entire equivalent circuit in Fig. 13, which is expressed by the matrix  $Y_c$ . In this case, we need each parameter of  $Z_n$  and  $M_{nm}$ , so the matrix  $Y_c$  is converted into a matrix  $Z_{core}$ . When  $Y_c$  is a  $n \times n$  matrix,  $Z_{core}$  is a  $(n-1) \times (n-1)$  matrix. The matrix  $Z_{core}$  is defined by the following equations.

$$\mathbf{i} = \begin{pmatrix} i_1 \\ i_2 \\ i_3 \\ i_4 \\ i_5 \end{pmatrix} = \mathbf{Y_c} \begin{pmatrix} v_1 \\ v_2 \\ v_3 \\ v_4 \\ v_5 \end{pmatrix} = \mathbf{Y_c} \mathbf{v}$$

$$(29)$$

$$v_{\mathbf{z}} = \begin{pmatrix} v_{z1} \\ v_{z2} \\ v_{z3} \\ v_{z4} \end{pmatrix} = \mathbf{Z}_{\mathbf{core}} \begin{pmatrix} i_{z1} \\ i_{z2} \\ i_{z3} \\ i_{z4} \end{pmatrix} = \mathbf{Z}_{\mathbf{core}} i_{\mathbf{z}}$$

(30)

$$\mathbf{Z_{core}} = \begin{pmatrix} Z_1 & j\omega M_{12} & j\omega M_{13} & j\omega M_{14} \\ j\omega M_{21} & Z_2 & j\omega M_{23} & j\omega M_{24} \\ j\omega M_{31} & j\omega M_{32} & Z_3 & j\omega M_{34} \\ j\omega M_{41} & j\omega M_{42} & j\omega M_{43} & Z_4 \end{pmatrix}$$

(31)

where vectors v, i,  $v_z$ , and  $i_z$  are defined as shown in Fig. 14. Each element of the matrix  $Z_{core}$  expresses self and mutual components directly. The matrix  $Y_c$  has the same numerical information as  $Z_{core}$ , which is explained later. The self and mutual inductances in  $Z_{core}$  can be derived from  $Y_c$ .

In this case, rank of the matrix  $Z_{core}$  is 4 for the 5-port inductor, and the matrix  $Y_c$  consists of the same components as shown in Fig. 14. Thus, rank of  $Y_c$  is also 4 although  $Y_c$  is a 5  $\times$  5 matrix. The matrix  $Y_c$  is not a regular matrix, and it does not have an inverse matrix. Here, converting matrices *A* and *B* are utilized, which are also not a regular matrix.

The converting matrices A and B are derived by the following procedure. Vectors iandvareconvertedintovectors $i_z$ and $v_z$ bythe followingequations. $v_z = Av(32)$

$$i_{\mathbf{z}} = Bi \tag{33}$$

$$\begin{pmatrix} v_{z1} \\ v_{z2} \\ v_{z3} \\ v_{z4} \end{pmatrix} = \begin{pmatrix} v_1 - v_2 \\ v_2 - v_3 \\ v_3 - v_4 \\ v_4 - v_5 \end{pmatrix} = Av$$

$$A = \begin{pmatrix} 1 & -1 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 & 0 \\ 0 & 0 & 0 & 1 & -1 \end{pmatrix}$$

(34)

$$A = \begin{pmatrix} 1 & -1 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 & 0 \\ 0 & 0 & 0 & 1 & -1 \end{pmatrix}$$

(35)

$$\begin{pmatrix}

i_{z1} \\

i_{z2} \\

i_{z3} \\

i_{z4}

\end{pmatrix} = \begin{pmatrix}

i_1 \\

i_1 + i_2 \\

i_1 + i_2 + i_3 \\

i_1 + i_2 + i_3 + i_4

\end{pmatrix} = \mathbf{B}i$$

(36)

Here, the follwing equation can be derived from Fig. 14

$$\sum_{n=1}^{5} i_n = i_1 + i_2 + i_3 + i_4 + i_5 = 0 \tag{37}$$

According to Eq.(37),  $i_1 + i_2 + i_3 + i_4$  is also expressed by  $-i_5$  as an example. Thus, matrix *B* has several solutions as follows.

$$B = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 \end{pmatrix}, \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & -1 \end{pmatrix}, \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & -1 & -1 \\ 0 & 0 & 0 & 0 & -1 \end{pmatrix}, \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & -1 & -1 & -1 \\ 0 & 0 & 0 & -1 & -1 \\ 0 & 0 & 0 & -1 & -1 \\ 0 & 0 & 0 & 0 & -1 \end{pmatrix}, \dots$$

$$\begin{pmatrix} 0 & -1 & -1 & -1 & -1 \\ 0 & 0 & -1 & -1 & -1 \\ 0 & 0 & 0 & 0 & -1 \end{pmatrix}, \dots$$

$$(38)$$

Fig. 15.  $\pi$ -type equivalent circuit.

Eqs. (29)(32)(33) are substituted into Eq. (30), and the following equations are obtained.

$$A \begin{pmatrix} v_{1} \\ v_{2} \\ v_{3} \\ v_{4} \\ v_{5} \end{pmatrix} = \begin{pmatrix} v_{z1} \\ v_{z2} \\ v_{z3} \\ v_{z4} \end{pmatrix} = \mathbf{Z_{core}} \begin{pmatrix} i_{z1} \\ i_{z2} \\ i_{z3} \\ i_{z4} \end{pmatrix} = \mathbf{Z_{core}} B \begin{pmatrix} i_{1} \\ i_{2} \\ i_{3} \\ i_{4} \\ i_{5} \end{pmatrix}$$

(39)

$$A = \mathbf{Z_{core}}BY_{c} \tag{40}$$

Matrices A and B are not regular matrix. Matrix  $Z_{core}$  is  $4\times4$  matrix.  $Y_c$  is shrunk to  $Z_{core}$  by pseudo-inverse matrix  $A^+$ . For example,  $A^+$  can be defined as follows.

$$A^{+} = B^{T} \tag{41}$$

$$AA^{+} = \begin{pmatrix} 1 & -1 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 & 0 \\ 0 & 0 & 0 & 1 & -1 \end{pmatrix} \begin{pmatrix} 1 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & -1 & 0 \\ 0 & 0 & -1 & -1 \end{pmatrix} = I$$

(42)

Finally, the following equations are derived.  $Z_{core}$  is expressed by Eq. (44). The self and mutual inductances are calculated from S-parameter.

$$I = Z_{\text{core}} B Y_{c} A^{+} \tag{43}$$

$$\mathbf{Z_{core}} = (\mathbf{BY_c}\mathbf{A}^+)^{-1} \tag{44}$$

Next, each parameter of equivalent circuit is extracted. Figure 15 shows a  $\pi$ -ladder equivalent circuit, which is transformed from the circuit model shown in Fig. 13.  $Z_n$  and  $M_{nm}$  can directly be obtained from  $\mathbf{Z_{core}}$  shown in Eq. (44).  $Y_{\mathrm{sub}m}$  is divided to  $Y_{\mathrm{s}n}$  as shown in Fig. 15

$$Y_{\text{sub}m} = \begin{cases} Y_{\text{s1}} & (m=1) \\ Y_{\text{sm}-1} + Y_{\text{sm}} & (2 \le m \le n-1) \\ Y_{\text{sn}-1} & (m=n) \end{cases}$$

(45)

$L_n$ ,  $C_n$ , and  $R_n$  in Fig. 15 are fitted to  $Z_n$  by a numerical optimization.  $C_{\sin n}$ ,  $C_{\sin n}$ , and  $R_{\sin n}$  in Fig. 15 are also fitted to  $Y_{\sin n}$ .

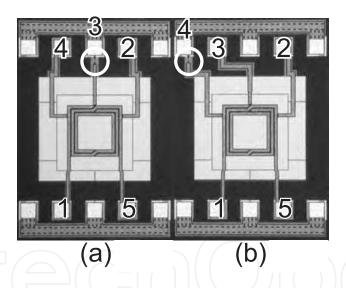

#### 3.3 Parameter extraction of multi-port inductor

In this subsection, parameter extraction using measurement results is presented. Figure 16 shows microphotograph of the 5-port inductors, which are fabricated by using a 180 nm Si CMOS process with 6 aluminum layers. The configuration of the 5-port inductor is symmetric, 3 turns, width of 15  $\mu$ m, line space of 1.2  $\mu$ m, and outer diameter of 250  $\mu$ m. 5-port S-parameter is obtained from two TEGs (Test Element Group) shown in Fig. 16 because common vector network analyzers have only four ports at most. Port 3 of inductor (a) is terminated by 50 $\Omega$  resistor as indicated in Fig. 16. Port 4 of inductor (b) is also terminated by 50 $\Omega$  resistor.  $Y_{\text{meas}}$  is obtained from measured S-parameters by the following equation.

$$Y_{\text{meas}} = \begin{pmatrix} a_{11} & a_{12} & b_{31} & a_{14} & a_{15} \\ a_{21} & a_{22} & b_{32} & a_{24} & a_{25} \\ b_{31} & b_{32} & b_{33} & b_{32} & b_{35} \\ a_{41} & a_{42} & b_{23} & a_{44} & a_{45} \\ a_{51} & a_{52} & b_{53} & a_{54} & a_{55} \end{pmatrix}, \tag{46}$$

where  $a_{ij}$  and  $b_{ij}$  are measured S-parameter elements of inductors (a) and (b), respectively. In this case,  $Y_{\text{meas}_{34}}$  and  $Y_{\text{meas}_{43}}$  cannot be obtained, so these components are substituted by  $Y_{\text{meas}_{32}}$  and  $Y_{\text{meas}_{23}}$ , respectively. The matrix  $Z_{\text{core}}$  is calculated from  $Y_{\text{meas}}$ ,  $Y_{\text{open}}$ , and  $Z_{\text{short}}$  as explained in Sect. 3.1 and 3.2.

Fig. 16. Microphotograph of the 5-port inductor.

Measured results and equivalent circuit model are compared as follows. First,  $L_n'$  are extracted from measured results by the following equations. To evaluate inductance and quality factor between port n and (n+1)',  $Y_{nn}$  is utilzed. For example,  $Y_{11}$  is derived from  $Z_1$  and  $Y_{s_1}$ .

$$Y_{11} = \frac{1}{Z_1} + Y_{s_1} \tag{47}$$

$$L_{1}' = \frac{\operatorname{Im}\left(\frac{1}{Y_{11}}\right)}{\omega} \tag{48}$$

$$Q_{L_{1'}} = \frac{\operatorname{Im}\left(\frac{1}{Y_{11}}\right)}{\operatorname{Re}\left(\frac{1}{Y_{11}}\right)},\tag{49}$$

where  $Z_1$  is derived from  $\mathbf{Z_{core}}$  in Eq. (44), and  $Y_{s_1}$  is derived from  $\mathbf{Y_{sub}}$  in Eq. (28). On the other hand,  $L_{n'\_model}$  and  $Q_{L_{n'\_model}}$  are obtained from fitted parameters by a numerical optimization in Sect. 3.2, which are calculated as follows.

$$Y_{11\text{model}} = \frac{1}{Z_{1\text{model}}} + Y_{\text{s_1model}}$$

$$= \frac{1}{(R_1 + j\omega L_1) // j\omega C_1}$$

$$+ j\omega C_{\text{si1}} // \left(\frac{1}{R_{\text{sub1}}} + j\omega C_{\text{sub1}}\right)$$

(50)

$$L_1'$$

\_model =

$$\frac{\operatorname{Im}\left(\frac{1}{Y_{11 \text{model}}}\right)}{\omega}$$

(51)

$$Q_{L_{1'}\text{_model}} = \frac{\operatorname{Im}\left(\frac{1}{Y_{11\text{model}}}\right)}{\operatorname{Re}\left(\frac{1}{Y_{11\text{model}}}\right)}$$

(52)

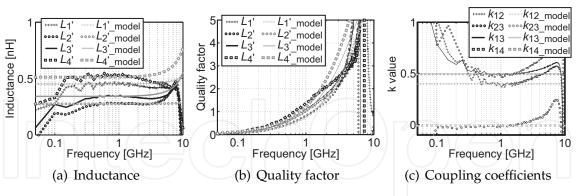

Fig. 17. Parameters of the 5-port inductor

Figures 17(a)(b)(c) show measured and modeled inductances, quality factors, and coupling coefficients of the 5-port inductor, respectively. The coupling coefficients of the 5-port inductor are calculated by Eq. (53).

$$k_{nm} = \frac{M_{nm}}{\sqrt{L_n L_m}} \tag{53}$$

$k_{nm}$  is coupling coefficient between  $L_n$  and  $L_m$ . Coupling coefficients  $k_{nm}$  have various values from -0.00 to 0.50 because line to line coupling intensity is different depending on topology of

each segment. In this experiment, coupling coefficient  $k_{23}$  is larger than the others because  $L_2$  and  $L_3$  are arranged parallelly. Coupling coefficient  $k_{14}$  is almost zero because  $L_1$  and  $L_4$  are arranged orthogonally.  $k_{nm\_model}$  is obtained from average coupling coefficient, because ideal coupling coefficient is independent of frequency.

# 3.4 Parameter extraction of 3-port symmetric inductor

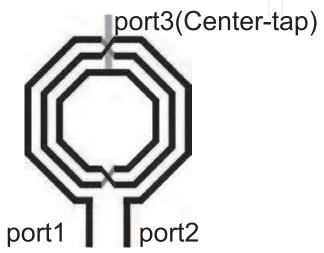

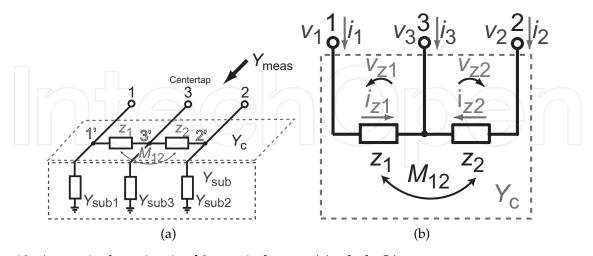

The 5-port modeling has been presented in Sect. 3.1-3.3, and in this subsection calculation and parameter extraction of a 3-port inductor, *i.e.*, a 2-port inductor with a center tap, shown in Fig. 18 are presented as a simple example. Note that the center tap is chosen as port 3 in Fig. 18.

Fig. 18. A symmetric inductor with a center-tap.

Fig. 19. An equivalent circuit of 3-port inductors (a) whole (b) core part.

Fig. 19(a) shows an equivalent circuit of 3-port inductors, and Fig. 19(b) shows core part of the equivalent circuit. In this case,  $Z_{core}$  can be defined by the following equation.

$$\mathbf{Z_{core}} = \begin{pmatrix} Z_1 & -j\omega M_{12} \\ -j\omega M_{21} & Z_2 \end{pmatrix}$$

(54)

Each element of the matrix  $Z_{core}$  expresses self and mutual components directly.

$$\mathbf{Y_{meas}} = \begin{pmatrix} Y_{11} & Y_{12} & Y_{13} \\ Y_{21} & Y_{22} & Y_{23} \\ Y_{31} & Y_{32} & Y_{33} \end{pmatrix}$$

(55)

According to Eq.(28),  $Y_{\text{sub}n}$  can be calculated by the following equations.

$$Y_{\text{sub1}} = Y_{11} + Y_{12} + Y_{13} \tag{56}$$

$$Y_{\text{sub2}} = Y_{21} + Y_{22} + Y_{23} \tag{57}$$

$$Y_{\text{sub3}} = Y_{31} + Y_{32} + Y_{33} \tag{58}$$

The self and mutual inductances in  $Z_{core}$  can be derived from  $Y_c$  as follows.

$$Y_{c} = Y_{\text{meas}} - Y_{\text{sub}}, \tag{59}$$

$$\mathbf{Z_{core}} = \begin{pmatrix} Z_1 & -j\omega M_{12} \\ -j\omega M_{21} & Z_2 \end{pmatrix}$$

(60)

$$= (BY_{c}A^{+})^{-1} = \begin{pmatrix} -Y_{12} - Y_{13} & Y_{12} \\ Y_{21} & -Y_{21} - Y_{23} \end{pmatrix}^{-1}$$

$$= \frac{-1}{Y_{12}Y_{23} + Y_{13}Y_{21} + Y_{13}Y_{23}} \begin{pmatrix} Y_{21} + Y_{23} & Y_{12} \\ Y_{21} & Y_{12} + Y_{13} \end{pmatrix},$$

(62)

$$= \frac{-1}{Y_{12}Y_{23} + Y_{13}Y_{21} + Y_{13}Y_{23}} \begin{pmatrix} Y_{21} + Y_{23} & Y_{12} \\ Y_{21} & Y_{12} + Y_{13} \end{pmatrix}, \tag{62}$$

where

$$A = \begin{pmatrix} 1 & 0 & -1 \\ 0 & 1 & -1 \end{pmatrix} \tag{63}$$

$$B = \begin{pmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \end{pmatrix} \tag{64}$$

$$A^{+} = B^{T} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 0 & 0 \end{pmatrix}. \tag{65}$$

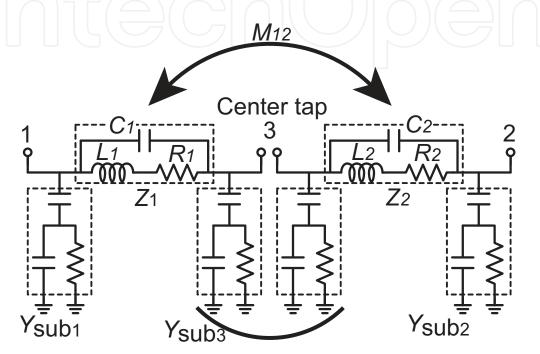

Here, a  $\pi$ -type equivalent circuit shown in Fig. 20 is utilized for the parameter extraction. Each parameter in Fig. 20, *i.e.*,  $Z_1$ ,  $Z_2$ ,  $M_{12}$ ,  $Y_{\text{sub1}}$ ,  $Y_{\text{sub2}}$ ,  $Y_{\text{sub3}}$ , can be calculated by Eqs.(56)(57)(58) (60)(62).

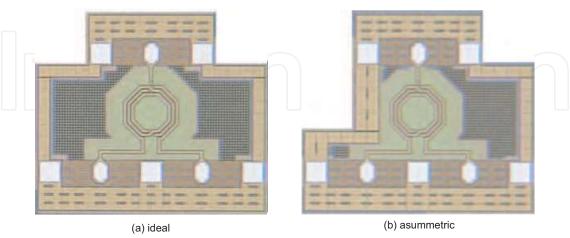

To demonstrate this method, left-right asymmetry is evaluated for symmetric and asymmetric inductors as shown in Fig. 21. As I described, symmetric inductors are often used for differential topology of RF circuits, e.g., voltage controlled oscillator, low noise amplifier, mixer. Asymmetry of inductors often cause serious degradation in performances, e.g., IP2 of LNA. The symmetric inductor shown in Fig. 21(a) is ideally symmetric. The asymmetric inductor shown in Fig. 21(b) has the same spiral structure as Fig. 21(a), but it has an asymmetric shape of ground loop.

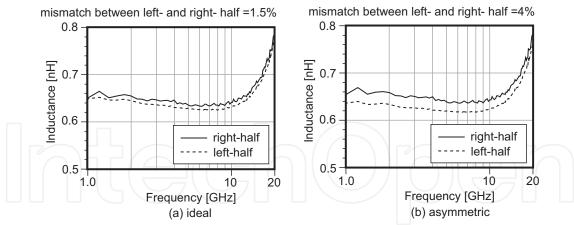

Left- and right-half inductances are compared, which are calculated by the following equation.

$$L_n = \frac{\operatorname{Im}\left[Z_n\right]}{\omega} \qquad (n = 1, 2) \tag{66}$$

Fig. 22 shows the results. The ideally symmetric inductor has only 1.5% of mismatch in inductance. On the other hand, the asymmetric inductor has 4.0% of mismatch as shown in Fig. 22(b). This can be utilized to characterize symmetric inductors in consideration of asymmetry.

Fig. 20.  $\pi$ -type equivalent circuit of the 3-port inductor.

Fig. 21. Microphotograph of the center-tapped inductors.

Fig. 22. Inductances of the center-tapped inductors.

# 4. References

- Danesh, M. & Long, J. R. (2002). Differentially driven symmetric microstrip inductors, *IEEE Trans. Microwave Theory Tech.* **50**(1): 332–341.

- Fujumoto, R., Yoshino, C. & Itakura, T. (2003). A simple modeling technique for symmetric inductors, *IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences* **E86-C**(6): 1093–1097.

- Kamgaing, T., Myers, T., Petras, M. & Miller, M. (2002). Modeling of frequency dependent losses in two-port and three-port inductors on silicon, *IEEE MTT-S Int. Microwave Symp. Digest*, Seattle, Washington, pp. 153–156.

- Kamgaing, T., Petras, M. & Miller, M. (2004). Broadband compact models for transformers integrated on conductive silicon substrates, *Proc. IEEE Radio Frequency Integrated Circuits (RFIC) Symp.*, pp. 457–460.

- Long, J. R. & Copeland, M. A. (1997). The modeling, characterization, and design of monolithic inductors for silicon RF IC's, *IEEE Journal of Solid-State Circuits* **32**(3): 357–369.

- Niknejad, A. M. & Meyer, R. G. (1998). Analysis, design and optimization of spiral inductors and transformers for Si RF IC's, *IEEE Journal of Solid-State Circuits* **33**(10): 1470–1481.

- Tatinian, W., Pannier, P. & Gillon, R. (2001). A new 'T' circuit topology for the broadband modeling of symmetric inductors fabricated in CMOS technology, *Proc. IEEE Radio Frequency Integrated Circuits (RFIC) Symp.*, Phoenix, Arizona, pp. 279–282.

- Watson, A. C., Melendy, D., Francis, P., Hwang, K. & Weisshaar, A. (2004). A comprehensive compact-modeling methodology for spiral inductors in silicon-based RFICs, *IEEE Trans. Microwave Theory Tech.* **52**(3): 849–857.

#### **Advanced Microwave Circuits and Systems**

Edited by Vitaliy Zhurbenko

ISBN 978-953-307-087-2

Hard cover, 490 pages

Publisher InTech

Published online 01, April, 2010

Published in print edition April, 2010

This book is based on recent research work conducted by the authors dealing with the design and development of active and passive microwave components, integrated circuits and systems. It is divided into seven parts. In the first part comprising the first two chapters, alternative concepts and equations for multiport network analysis and characterization are provided. A thru-only de-embedding technique for accurate onwafer characterization is introduced. The second part of the book corresponds to the analysis and design of ultra-wideband low- noise amplifiers (LNA).

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Kenichi Okada and Kazuya Masu (2010). Modeling of Spiral Inductors, Advanced Microwave Circuits and Systems, Vitaliy Zhurbenko (Ed.), ISBN: 978-953-307-087-2, InTech, Available from: http://www.intechopen.com/books/advanced-microwave-circuits-and-systems/modeling-of-spiral-inductors

# INTECH open science | open minds

# InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.