## Research Article

# Modeling of Temperature-Dependent Noise in Silicon Nanowire FETs including Self-Heating Effects

## P. Anandan, N. Malathi, and N. Mohankumar

SKP Engineering College, Tiruvannamalai, Tamil Nadu 606 611, India

Correspondence should be addressed to P. Anandan; anandanvp2000@gmail.com

Received 7 January 2014; Accepted 23 April 2014; Published 21 May 2014

Academic Editor: Agostino Bruzzone

Copyright © 2014 P. Anandan et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Silicon nanowires are leading the CMOS era towards the downsizing limit and its nature will be effectively suppress the short channel effects. Accurate modeling of thermal noise in nanowires is crucial for RF applications of nano-CMOS emerging technologies. In this work, a perfect temperature-dependent model for silicon nanowires including the self-heating effects has been derived and its effects on device parameters have been observed. The power spectral density as a function of thermal resistance shows significant improvement as the channel length decreases. The effects of thermal noise including self-heating of the device are explored. Moreover, significant reduction in noise with respect to channel thermal resistance, gate length, and biasing is analyzed.

## **1. Introduction**

As the device size scaling continues, many critical issues such as increased leakage current, short-channel effect, high-field effects, variability, reliability, noise, and parasitic impacts may pose more obstruction for highly scaled devices. Therefore, device structure and material innovation have attracted more attention as the primary enabler for performance enhancement in CMOS technology.

The gate-all-around (GAA) silicon nanowire transistor (SNWT) is considered as one of the promising candidates for ultimate scaling, due to its excellent electrostatic control capability, improved transport property, and feasible device design [1–4]. This kind of device has the unique structural nature, with quasi-one-dimensional and strongly confined nanowire channel, three-dimensional surrounding gate-stack of multiple crystallographic interface orientations, and sharp transition from the large source/drain region to the narrow part (of source/drain extension). Thus, some of the above mentioned critical issues may be even more complicated that would give rise to new challenges in device engineering of SNWTs.

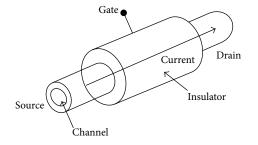

Channel thermal noise is the most dominant noise source of short-channel MOSFETs at high frequencies. As the MOSFET is scaled down, short-channel effects increase and it causes serious problems in device operation. Gate-all-around silicon nanowire MOSFET is one of the strong candidates, which has high performance even in short-channel devices [5–7]. As well as the short-channel effects, channel thermal noise is also increased as the MOSFET is scaled down. Thus, it is necessary to predict channel thermal noise in silicon nanowire MOSFET [8]. To compare the channel thermal noise in nanowire MOSFET with temperature-dependent model, analytical power spectral density (PSD) equation is used. The cross-sectional view of a silicon nanowire MOSFET is shown in Figure 1.

## 2. DC Characterization of Silicon Nanowires

Before analyzing the channel thermal noise, the DC characteristics of SNWFET are analyzed. From Figure 1, the drive current, threshold voltage, subthreshold swing, and DIBL are calculated by TCAD simulations. Here, different channel lengths are chosen and correspondingly the threshold voltage is noted. Here, the threshold voltage varies from 0.24 to 0.27 V; the subthreshold swing and DIBL are 71 mV/decade and 18.4 mV/volt, respectively. The drain current values are varied from 0.31 mA to 0.51 mA. It is predicted that channel thermal noise is much higher in devices with higher drain currents and increases with scaling.

FIGURE 1: Structure of SNWFET.

#### 3. Channel Thermal Noise Modeling

In this work, channel thermal noise of the silicon nanowire MOSFET (SNWFET) is derived from the analytic thermal noise model, by including short-channel effects [9, 10]. Power spectral density of the noise current is defined by

$$S_{\rm id} = 4KT\frac{1}{R}.$$

(1)

Here, K is Boltzmann constant, T is temperature (K), and R is resistance (ohm).

Using (1), we can find the power spectral density of channel thermal noise in SNWFET [11]:

$$S_{\rm id} = 4K_B T \frac{\mu \left(-Q_{\rm inv}\right)}{L^2}.$$

(2)

Here,  $\mu$  is mobility of charge carriers, *L* is channel length (nm), and  $Q_{inv}$  is inversion charge.

Considering the short-channel effects, the power spectral density of channel thermal noise is validated for short-channel transistors as follows:

$$S_{\rm id} = 4K_B T \cdot I_{\rm ds} \cdot \left(\frac{1}{V_{\rm ds}} + \frac{1}{E_c L_c}\right). \tag{3}$$

Here,  $E_c$  is critical electric field,  $L_c$  is channel length (nm), and  $V_{ds}$  is drain source voltage (V).

### 4. Temperature-Dependent Model

Special design approaches are derived for SNWT circuits by using the thermal model; the effect can be analyzed for the devices with the following relationship between temperature dependence and power dissipation [12] given by

$$T - T_0 = R_{\rm th} V_{\rm ds} I_{\rm ds}.$$

(4)

Here, *T* is actual temperature,  $T_0$  is the ambient (substrate) temperature, and  $R_{\text{th}}$  is a thermal resistance

$$S_{\rm id} = 4K_B \left(T - T_0\right) \cdot I_{\rm ds} \cdot \left(\frac{1}{V_{\rm ds}} + \frac{1}{E_c L_c}\right),\tag{5}$$

$$S_{\rm id} = 4K_B R_{\rm th} I_{\rm ds}^2 \left\{ 1 + \left(\frac{V_{\rm ds}}{E_c L_c}\right) \right\}; \tag{6}$$

$$R_{\rm th} = \frac{d}{A\lambda_{\rm th}},\tag{7}$$

$$S_{\rm id} = \frac{4K_B dI_{\rm ds}^2}{A\lambda_{\rm th}} \left\{ 1 + \left(\frac{V_{\rm ds}}{E_c L_c}\right) \right\}.$$

(8)

Equation (8) represents the power spectral density of channel thermal noise with temperature-dependent model. Here, A is the area and d is the thickness of silicon nanowire, respectively.  $\lambda_{\text{th}}$  is the thermal conductivity.

#### 5. Self-Heating Effects (SHE)

Once the temperature dependence of the device parameters is extracted, the same approach can be used for describing the self-heating effects of the device:

$$G_{\rm SEH} = \frac{\partial I_{\rm ds}}{\partial T} \cdot \frac{\partial T}{\partial V_{\rm ds}},\tag{9}$$

$$\frac{\partial T}{\partial V_{\rm ds}} = R_{\rm th} I_{\rm ds},\tag{10}$$

$$R_{\rm th} = \frac{G_{\rm SHE}}{I_{\rm ds} \cdot \left(\partial I_{\rm ds} / \partial T\right)},\tag{11}$$

$$C_{\rm th} = \frac{1}{2\pi f_{\rm th} R_{\rm th}}.$$

(12)

From (12),  $C_{\rm th}$  is the thermal capacitance,  $f_{\rm th}$  is the thermal frequency, and  $G_{\rm SHE}$  is the transconductance including self-heating effects (SHE) at the particular point. We use the AC drain output conductance ( $g_{\rm ds}$ ) data at one bias point to characterize both  $R_{\rm th}$  and  $C_{\rm th}$ . The SHE can be subtracted from the DC data and a SHE-free device model can be extracted as [13, 14]

$$\Delta T\left(f\right) = \frac{I_{\rm ds}V_{\rm ds}R_{\rm th}}{\sqrt{1 + \left(2\pi f R_{\rm th}C_{\rm th}\right)^2}}.$$

(13)

Temperature variation depending on the frequency  $(\Delta T(f))$  is calculated.

Substituting self-heating effect in power spectral density equation of channel thermal noise,

$$S_{\rm id} = 4K_B \Delta T\left(f\right) I_{\rm ds} \left\{\frac{1}{V_{\rm ds}} + \frac{1}{E_c L_c}\right\}$$

(14)

$$S_{\rm id} = 4K_B \cdot \frac{I_{\rm ds}^2 d}{\sqrt{(A\lambda_{\rm th})^2 + (2\pi f dC_{\rm th})^2}} \left\{ 1 + \frac{V_{\rm ds}}{E_c L_c} \right\}.$$

(15)

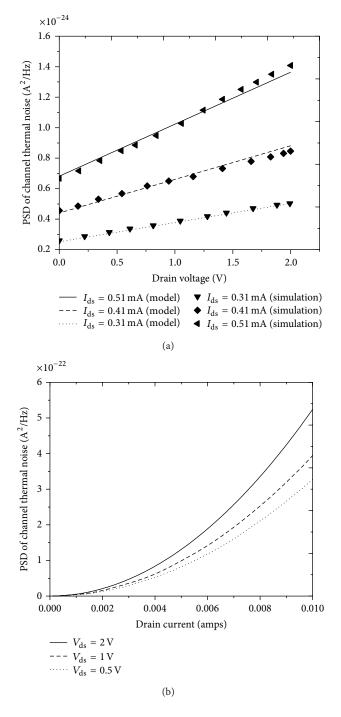

FIGURE 2: (a) Power spectral density of channel thermal noise versus drain source voltage of the SNWMOSFET. (b) Power spectral density of channel thermal noise versus drain current of the SNWMOSFET.

Equation (15) is derived for power spectral density of channel thermal noise.

In SNWTs, the self-heating problem may be even worse due to their ultrasmall and strongly confined nanowire channels. Therefore, a simple and accurate analytical channel thermal noise model for SNWTs is developed and optimized for future applications.

#### 6. Numerical Noise Model Calibration

In recent years, some effort has been devoted to the numerical simulation of noise phenomena in physics based device simulators. In most cases, the noise simulation is founded on Shockley's impedance field method [15] and its variations and generalizations. Bonani et al. [16] reported a numerically efficient Green function approach to the Langevin equation based simulation of the impedance field method (IFM) which is the basis for the implementation in the multidimensional, mixed-mode device simulator Synopsys TCAD described here. It is a variation of the direct impedance field method (DIFM). The so-called adjoint impedance field method (AIFM) (e.g., [17]) is limited to one-carrier devices and had been earlier implemented into Dessis-ISE [18].

6.1. Numerical Diffusion Noise. Diffusion noise is due to fluctuations of the velocities of the carriers, caused by collisions with phonons, impurities, temperatures, and so forth. The following expression for the electron diffusion noise source can be derived (e.g., [17]):

$$K_{\rm diff} = 4qnK_BT\mu,\tag{16}$$

where *n* is the electron density,  $\mu$  is the electron mobility, and *T* is one of lattice temperature, e temperature, *h* temperature, or *e h* temperature; the used temperature in the expression can be chosen with default lattice temperature. For example, *e* temperature uses the electron temperature for the electron noise source, while the lattice temperature is used for the hole noise source; the specification *e h* temperature uses for the carrier noise source the corresponding carrier temperature.

#### 7. Results and Discussion

Figure 2(a) shows the power spectral density of channel thermal noise versus drain voltage of the SNWMOSFET for different drain currents. It is evident that the channel thermal noise increases with increasing drain current because as the electrons approach the drain, its velocity increases simultaneously increasing the temperature of the carriers under the influence of high drain field thereby increasing the PSD of the carriers. This proportionality of PSD channel thermal noise with drain current is checked and verified with noise simulation data in Figure 2(a).

The effect of drain current with PSD of channel thermal noise is modeled in Figure 2(b). It is evident that the channel thermal noise increases with increasing drain current as shown in (3).

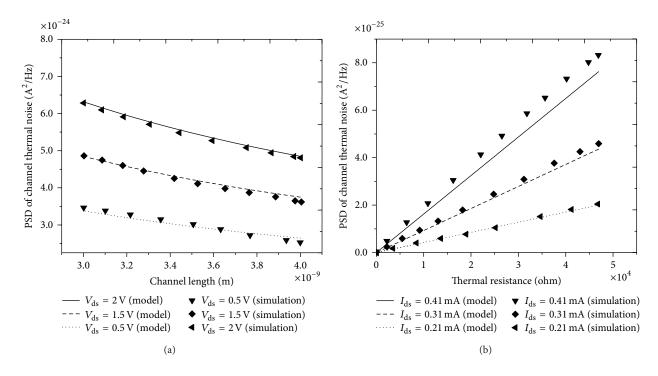

Figure 3(a) shows the power spectral density of channel thermal noise versus channel length of the SNWMOSFET. It is observed that as the channel length is increased, thermal noise decreases due to the fact that aggressive scaling causes increased channel thermal noise and is verified by simulation results.

FIGURE 3: (a) Power spectral density of channel thermal noise versus channel length of the SNWMOSFET. (b) Power spectral density of channel thermal noise versus thermal resistance of the SNWMOSFET.

FIGURE 4: Power spectral density of channel thermal noise versus thermal resistance of the SNWMOSFET.

Figure 3(b) shows the variation of PSD channel thermal noise for different thermal resistance values. Due to uniform scaling, the resistances at the source and drain tend to increase with temperature which in turn increases the thermal noise. For channel length below 65 nm, the thermal resistance effects could not be ignored.

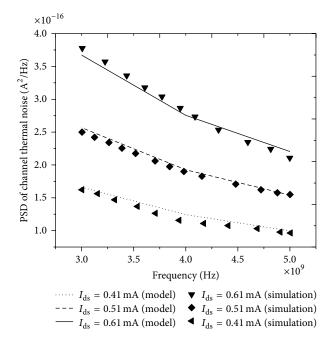

Figure 4 shows the power spectral density of channel thermal noise versus frequency of the SNWMOSFET for various drain current values. From the figure, it is clear that PSD of the channel thermal noise decreases at high frequency showing significant improvement in noise figure. This is because as the frequency increases, the parasitics increase, thereby increasing the reactance effects at high frequencies. The results are verified with simulations and are found to be matching each other.

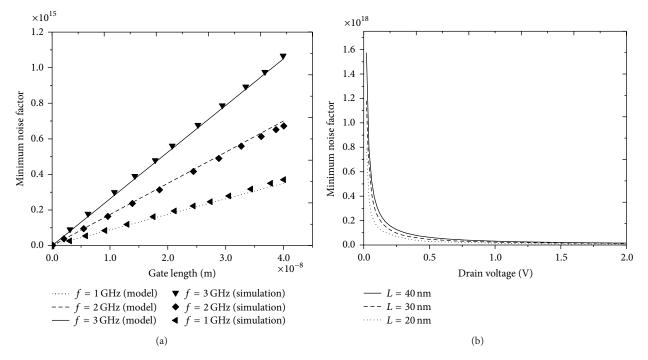

Figure 5(a) shows the variation of minimum noise factor with respect to gate length for different frequencies. As the MOSFET is scaled down from 0.1 to 0.03  $\mu$ m for increased  $F_t$ , the minimum noise factor increases since  $N_f$  is proportional to KTB and as temperature increases with the increase of  $F_t$ , the noise factor  $N_f$  also increases. The results are also verified using simulations.

Figure 5(b) shows the variation of noise factor with the drain voltage as the factor of gate length.  $N_f$  decays exponentially with increased drain voltages as the gate length is decreased.

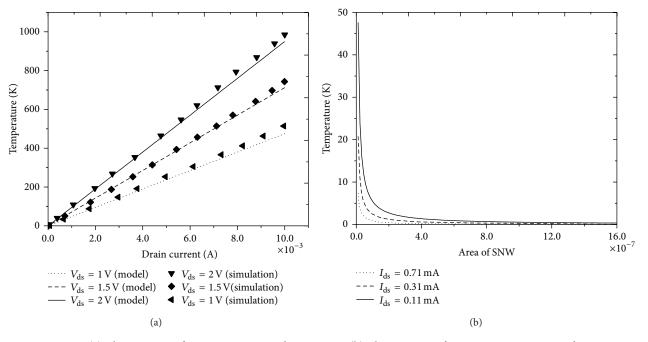

Figure 6(a) shows the effect of temperature on the drive current for increased drain voltages. The drain current increases as the drain voltage approaches  $V_{dd}$  also increasing the temperature of the device (hot carrier effects). This is verified by using simulation results.

Figure 6(b) shows the variation of temperature over the area of the silicon nanowire for increased drain current. The temperature decays exponentially with the area of the silicon nanowire for increased drain current. As the area

FIGURE 5: (a) Characteristic of minimum noise factor versus gate length. (b) Characteristic of minimum noise factor versus drain voltage.

FIGURE 6: (a) Characteristic of temperature versus drain current. (b) Characteristic of temperature versus area of SNW.

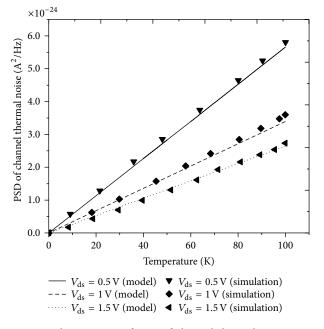

of the nanowire is increased the hot electron at the drain ends will have enough space for scattering within the channel increasing thermal conductivity and thereby decreasing the temperature. the temperature since  $P_n = KTB$ , where  $P_n$  is the signal to noise power, *T* is temperature, *K* is Boltzmann's constant, and *B* is the bandwidth. This is verified by simulation results.

Figure 7 shows the PSD of channel thermal noise as the function of temperature. It is evident that for increased drain voltages the drain current increases simultaneously increasing the channel thermal noise which in turn increases

## 8. Conclusion

This paper analyses the modeling of thermal noise in silicon nanowire MOSFET including the self-heating effects.

FIGURE 7: Characteristic of PSD of channel thermal noise versus temperature.

The variations of thermal noise with respect to various device oriented parameters are observed for improved performances of the device. The channel thermal noise is predicted using noise factor in silicon nanowire MOSFET at high frequencies. Improvement in noise figure owing to reduce area in case of effectively scaled Nanowires.

An analytical formulation of the thermal noise in shortchannel MOSFETs, working in the saturation region, is presented. Hence, the noise characteristic is analyzed by noise factor and the performance of the noise characterized by TCAD shows significant improvement in case of suitably scaled nanowires. The effects of thermal noise with respect to device geometry are discussed in detail.

## **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

#### References

- S. D. Suk, S.-Y. Lee, S.-M. Kim et al., "High performance 5 nm radius Twin Silicon Nanowire MOSFET (TSNWFET) : fabrication on bulk si wafer, characteristics, and reliability," in *Proceedings of the International Electron Devices Meeting (IEDM* '05), pp. 717–720, Washington, DC, USA, 2005.

- [2] N. Singh, F. Y. Lim, W. W. Fang et al., "Ultra-narrow silicon nanowire gate-all-around CMOS devices: impact of diameter, channel-orientation and low temperature on device performance," in *Proceedings of the International Electron Devices Meeting (IEDM '06)*, pp. 547–550, 2006.

- [3] Y. Tian, R. Huang, Y. Wang et al., "New self-aligned silicon nanowire transistors on bulk substrate fabricated by epi-free

compatible CMOS technology: process integration, experimental characterization of carrier transport and low frequency noise," in *Proceedings of the IEEE International Electron Devices Meeting (IEDM '07)*, pp. 895–898, Washington, DC, USA, December 2007.

- [4] Y. Jiang, T. Y. Liow, N. Singh et al., "Performance breakthrough in 8 nm gate length gate-all-around nanowire transistors using metallic nanowire contacts," in *Proceedings of the Symposium on VLSI Technology Digest of Technical Papers (VLSIT '08)*, pp. 34– 35, June 2008.

- [5] D. S. Kim, Y. C. Jung, M. Y. Park et al., "Electrical characteristics of the back-gated bottom-up silicon nanowire field effect transistor," *Nanotechnology, IEEE Transactions on*, vol. 7, no. 6, pp. 683–687, 2008.

- [6] J. W. Jeon, B.-G. Park, J.-D. Lee, and H.-C. Shin, "Analytical noise parameter model of short-channel RF MOSFETs," *Journal* of Semiconductor Technology and Science, vol. 7, no. 2, pp. 88–93, 2007.

- [7] S. Asgaran, M. J. Deen, and C. Chen, "Analytical modeling of MOSFETs channel noise and noise parameters," *IEEE Transactions on Electron Devices*, vol. 51, no. 12, pp. 2109–2114, 2004.

- [8] G. Tan, C.-H. Chen, B. Hung, P. Lei, and C.-S. Yeh, "Channel thermal noise and its scaling impact on deep sub-100 nm MOSFETs," in *Proceedings of the 21st International Conference* on Noise and Fluctuations (ICNF '11), pp. 356–359, Toronto, Canada, June 2011.

- [9] F. D. Agostino and D. Quercia, "Short-channel effects in MOSFETs," in *Introduction to VLSI design (EECS 467)*, 2000.

- [10] J. W. Jeon, B.-G. Park, J.-D. Lee, and H.-C. Shin, "An analytical channel thermal noise model for deep-submicron MOSFETs with short channel effects," *Solid-State Electronics*, vol. 51, no. 7, pp. 1034–1038, 2007.

- [11] J. Lee, J. Jeon, J. Kim, B. Park, J. D. Lee, and H. Shin, "Prediction of channel thermal noise in twin silicon nanowire MOSFET (TSNWFET)," in *Proceedings of the 9th International Conference* on Solid-State and Integrated-Circuit Technology (ICSICT '08), pp. 61–63, Beijing, China, October 2008.

- [12] T. Ytterdal, Y. Cheng, and T. Fjeldly, *Device Modeling for Analog & RF CMOS Circuit Design*, John Wiley & Sons, New York, NY, USA, 2003.

- [13] W. Jin, S. K. H. Fung, W. Liu, P. C. H. Chan, and C. Hu, "Self-heating characterization for SOI MOSFET based on AC output conductance," in *Proceedings of the International Electron Devices Meeting (IEDM '99)*, pp. 175–178, Washington, DC, USA, December 2007.

- [14] R. Huang, R. S. Wang, J. Zhuge et al., "Self-heating effect and characteristic variability of gate-all-around silicon nanowire transistors for highly-scaled CMOS technology (invited)," in *Proceedings of the IEEE International SOI Conference (SOI '10)*, pp. 1–4, San Diego, Calif, USA, October 2010.

- [15] W. Shockley, J. A. Copeland, and R. P. James, "The impedance field method of noise calculation in active semiconductor devices," in *Quantum Theory of Atoms, Molecules and the Solid State*, P. O. Loewdin, Ed., pp. 537–563, Academic Press, New York, NY, USA, 1966.

- [16] F. Bonani, G. Ghione, M. R. Pinto, and R. K. Smith, "An efficient approach to noise analysis through multidimensional physicsbased models," *IEEE Transactions on Electron Devices*, vol. 45, no. 1, pp. 261–269, 1998.

- [17] J. P. Nougier, "Fluctuations and noise of hot carriers in semiconductor materials and devices," *IEEE Transactions on Electron Devices*, vol. 41, no. 11, pp. 2034–2049, 1994.

- [18] A. Kunzmann, "Simulation of noise in semiconductor devices," Tech. Rep. 98/7, Integrated Systems Laboratory, Swiss Federal Institute of Technology, Zurich, Switzerland, 1998.