# University of Nebraska - Lincoln

# DigitalCommons@University of Nebraska - Lincoln

Faculty Publications from the Department of **Electrical and Computer Engineering**

**Electrical & Computer Engineering, Department**

2012

# Modeling, Simulation, and Validation of a Power SiC BJT

Tanya Kirilova Gachovska University of Nebraska, tgachovska@yahoo.com

Jerry L. Hudgins University of Nebraska-Lincoln, jhudgins2@unl.edu

**Angus Bryant** Converteam U.K. Ltd, A.T.Bryant@warwick.ac.uk

Enrico Santi University of South Carolina - Columbia, esanti00@cec.sc.edu

Alan Mantooth University of Arkansas, mantooth@uark.edu

See next page for additional authors

Follow this and additional works at: https://digitalcommons.unl.edu/electricalengineeringfacpub

Part of the Electrical and Computer Engineering Commons

Gachovska, Tanya Kirilova; Hudgins, Jerry L.; Bryant, Angus; Santi, Enrico; Mantooth, Alan; and Agarwal, Anant K., "Modeling, Simulation, and Validation of a Power SiC BJT" (2012). Faculty Publications from the Department of Electrical and Computer Engineering. 166.

https://digitalcommons.unl.edu/electricalengineeringfacpub/166

This Article is brought to you for free and open access by the Electrical & Computer Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Faculty Publications from the Department of Electrical and Computer Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

| <b>Authors</b><br>Tanya Kirilova Gachovska, Jerry L. Hudgins, Angus Bryant, Enrico Santi, Alan Mantooth, and Anant K.<br>Agarwal |

|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

# Modeling, Simulation, and Validation of a Power SiC BJT

Tanya Gachovska, *Student Member, IEEE*, Jerry L. Hudgins, *Fellow, IEEE*, Angus Bryant, *Member, IEEE*, Enrico Santi, *Senior Member, IEEE*, H. Alan Mantooth, *Fellow, IEEE*, and Anant K. Agarwal, *Fellow, IEEE*

Abstract—This paper presents a physics-based model of a silicon carbide bipolar junction transistor and verification of its validity through experimental testing. The Fourier series solution is used to solve the ambipolar diffusion equation in the transistor collector region. The model is realized using MATLAB and Simulink. The experimental results of static operation and also the simulated and experimental results of switching waveforms are given.

*Index Terms*—Silicon carbide (SiC) bipolar junction transistor (BJT), power semiconductor modeling.

| ,                                   |                                                |  |  |

|-------------------------------------|------------------------------------------------|--|--|

| 1                                   | Nomenclature                                   |  |  |

| A                                   | Device area (cm <sup>2</sup> ).                |  |  |

| $C_{J1}$ and $C_{J2}$               | Capacitance of the depletion layers            |  |  |

|                                     | (F).                                           |  |  |

| D                                   | Ambipolar diffusivity (cm $^2$ s $^{-1}$ ).    |  |  |

| $D_p$ and $D_p$                     | Electron and hole diffusivities                |  |  |

| 1                                   | $(cm^2s^{-1}).$                                |  |  |

| $\varepsilon$                       | Dielectric permittivity of SiC (F/cm).         |  |  |

| $h_n$                               | $N^+$ emitter recombination parameter          |  |  |

|                                     | $(cm^4 s^{-1}).$                               |  |  |

| $h_p$                               | $P^+$ emitter recombination parameter          |  |  |

|                                     | $(cm^4 s^{-1}).$                               |  |  |

| $I_B$                               | Base current (A).                              |  |  |

| $I_C$                               | Collector current (A).                         |  |  |

| $I_{\rm disp1}$ and $I_{\rm disp2}$ | Displacement currents at junctions $J_1$       |  |  |

|                                     | and $J_2$ (A).                                 |  |  |

| $I_{L0}$                            | Initial inductor current (A).                  |  |  |

| $I_{n0}$ , $I_{n1}$ , and $I_{n2}$  | Electron currents at junctions $J_0$ , $J_1$ , |  |  |

|                                     | and $J_2$ (A).                                 |  |  |

Manuscript received July 14, 2011; revised October 16, 2011, November 29, 2011, and February 7, 2012; accepted March 5, 2012. Date of current version May 31, 2012. This work was supported by the U.S. Office of Naval Research under Grant N00014-07-1-0611. Recommended for publication by Associate Editor A. Lindemann.

T. Gachovska and J. L. Hudgins are with the Department of Electrical Engineering, University of Nebraska-Lincoln, Lincoln, NE 472-2211 USA (e-mail: tgachovska@yahoo.com; hudgins@engr.unl.edu).

A. Bryant is with the Converteam U.K. Ltd, Rugby, CV21 1BU, U.K. (e-mail: A.T.Bryant@warwick.ac.uk).

E. Santi is with the Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208 USA (e-mail: esanti00@cec.sc.edu).

H. A. Mantooth is with the Department of Electrical Engineering, University of Arkansas, Fayetteville, AR 72701 USA (e-mail: mantooth@uark.edu).

A. K. Agarwal is with the SiC Power Device R&D, Cree Inc., Durham, NC 27703 USA (e-mail: Anant\_Agarwal@cree.com).

Digital Object Identifier 10.1109/TPEL.2012.2190622

| $I_{p0}$ , $I_{p1}$ , and $I_{p2}$ | Hole currents at junctions $J_0$ , $J_1$ , and |

|------------------------------------|------------------------------------------------|

|                                    | $I_{2}(A)$                                     |

$K_{FV}$  Feedback constant.  $L_L$  Load inductance (H).  $L_S$  Stray inductance (H).

M Number of terms of the Fourier series.  $\mu_n$  and  $\mu_p$  Electron and hole mobilities of SiC (cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).

$n_{B\,0}$  and  $n_{B\,1}$  Electron concentrations at the two boundaries of the base region (cm<sup>-3</sup>).  $N_E$  Emitter doping level (cm<sup>-3</sup>). Collector doping level (cm<sup>-3</sup>).

Intrinsic carrier concentration of SiC (cm<sup>-3</sup>).

$N^{-}$  region doping concentration (cm<sup>-3</sup>).

$P_B$  Doping concentration of the base (cm<sup>-3</sup>).

p(x, t) Excess carrier concentration in the drift region (cm<sup>-3</sup>).

$p_{x1}$  and  $p_{x2}$  Excess carrier concentrations at the two boundaries of the drift region

(cm<sup>-3</sup>). Load resistance ( $\Omega$ ).

$R_L$ Load resistance  $(\Omega)$ . $R_S$ Resistance of the wires  $(\Omega)$ . $Q_B$ Total electron charge in the

Total electron charge in the base (C). High-level carrier lifetime within the

drift region (s).

$au_{

m BHL}$  High-level lifetime in the  $P^+$ -base re-

gion (s).

$au_p$  Minority lifetime in  $N^+$  emitter (s). q Unit electron charge (1.6×10<sup>-19</sup>C).  $V_{BE}$  Base–emitter voltage (V).

$V_{CE}$  Collector-emitter voltage (V).  $V_{\rm CSR}$  Voltage across the carrier storage re-

$\begin{array}{c} {\rm gion} \ ({\rm V}). \\ V_{d\,1} \ {\rm and} \ V_{d\,2} \end{array} \qquad {\rm Voltages} \ {\rm across} \ {\rm the} \ N^-N^+ \ {\rm and} \ N^-P^+ \end{array}$

depletion layers (V). External dc voltage (V).

$V_{J0}$ ,  $V_{J1}$ , and  $V_{J2}$  Voltages across junctions  $J_0$ ,  $J_1$ , and

$J_2$  (V).

Saturation velocity of SiC (cm/s). Thermal voltage—kT/q (T is the temperature (K) and k is the Boltzmann

constant eV/K) (V). Base width (cm).

$W_B$  Base width (cm

$v_{\mathrm{sat}}$

$W_{d1}$  and  $W_{d2}$  Widths of the  $N^-N^+$  and  $N^-P^+$  de-

pletion layers (cm).

$W_{N^-}$  Drift region width (cm).

$x_1$  and  $x_2$  Boundary positions of the carrier stor-

age region (cm).

#### I. INTRODUCTION

N RECENT years, silicon carbide (SiC) has been recognized as a potential candidate material to realize high-performance switches in the high-power, high-frequency, and high-temperature area due to its superior material properties such as wider bandgap, higher saturation velocity, higher electric field strength, and higher thermal conductivity compared to Si and GaAs.

The SiC Schottky diode was the first commercially available power switch [1]. The SiC power MOSFET has drawn a lot of attention due to the advantages of a unipolar device and ease of gate control. However, the poor reliability of MOSchannel mobility and the dielectric oxide, especially in high electric fields, has greatly hampered the development of the SiC MOSFET [2]. Bipolar devices such as the power bipolar junction transistor (BJT), gate turn-off thyristor (GTO), and insulated gate bipolar transistor (IGBT) provide further utilization of SiC material in high-power and high-temperature applications.

BJTs based on 4H-SiC have the advantages of no gate oxide and low on-state voltage in the lightly doped drift region due to double-sided high-level injection. The first 6H-SiC BJT with a blocking voltage of 50 V and a common-emitter current gain of 4–8 was fabricated in 1978 [3]. The first 4H-SiC BJT was reported to have a capability of open-base blocking voltage rated at 800 V and a common-emitter current gain (the ratio of the collector current to the base current) of 9 [4]. Recently, the 4H-SiC NPN BJT with a 6-kV open-base blocking voltage  $(V_{\rm CEO})$  and 28 m $\Omega$  cm<sup>2</sup> specific on-resistance has been reported with a corresponding common-emitter current gain of 3 [5].

In power electronics, SiC BJTs could be used as switches having two states: ON and OFF. These states are important in determining the efficiency and applicability of the BJT, while the transient processes between the two states have an important role in determining the energy losses, reliability, and performance of the circuit.

The objective of this study is modeling, simulation, and validation of the transient processes in a 4H-SiC BJT (1200 V-5 A SiC BJT, Cree, Durham, NC).

## II. MODELING

Although SiC power BJTs have been fabricated and measured for several years, there are no physics-based models appropriate for circuit designers. The few models in the public domain have dealt with characterization of the current gain [6]. In this section, the development and implementation of a level-3 physics-based model [7] of a SiC BJT based on a Fourier series solution of the ADE equation using MATLAB and Simulink is presented.

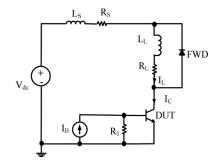

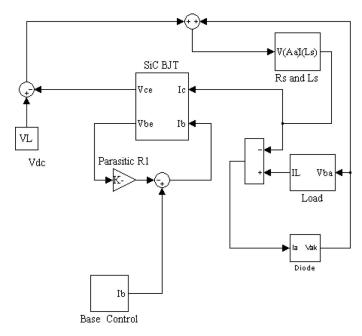

The SiC BJT is simulated under inductive load switching condition. The circuit schematic is shown in Fig. 1. A freewheeling high-voltage SiC diode is employed in the simulation model. Table I provides the BJT parameters, as provided by the manu-

Fig. 1. Schematic of a switching test circuit used for experiments and simulation.

TABLE I BJT PARAMETERS

| Parameters          | Units                                           | Definition                           | Value                                                            |

|---------------------|-------------------------------------------------|--------------------------------------|------------------------------------------------------------------|

| A                   | cm <sup>2</sup>                                 | Active area of the device            | 0.01                                                             |

| $W_{N^-}, W_B$      | μт                                              | Thickness of $N^-$ and $P^+$         | 40, 0.9                                                          |

| $N_{N^-}, P_B, N_C$ | cm <sup>-3</sup>                                | Doping of $N^-$ , $P^+$ , and $N^+$  | 1.1x10 <sup>15</sup> , 2x10 <sup>17</sup> , 1.2x10 <sup>19</sup> |

| $\tau_p, \ \tau_n$  | μs                                              | Minority lifetime in $N^*$ and $P^*$ | 0.02, 0.155                                                      |

| $\mu_n, \mu_p$      | cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | Electrons and hole mobility 900, 90  |                                                                  |

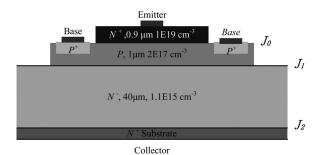

Fig. 2. Cross-sectional view of 4-kV 4H-SiC power BJT showing layer thicknesses (not to scale) and doping concentrations.

facturer, used in the simulation and Fig. 2 presents the structure of the SiC BJT. The carrier lifetimes were estimated based on experimental switching waveforms.

The circuit parameters listed in Table II are used for simulation of the SiC BJT under clamped inductive switching load.

The Fourier-series-based electrical model for power devices has been thoroughly introduced in [8]–[10]. The basic idea is to solve the ADE through a Fourier-series expansion.

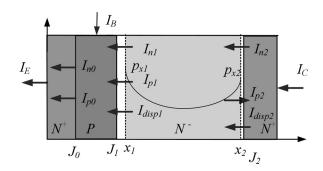

The basic 1-D structure of the SiC BJT is illustrated in Fig. 3. The BJT is divided into four regions: the  $N^+$  emitter, P-base,  $N^-$  drift region, and  $N^+$  collector region. The external and internal electron and hole currents are indicated for each region.

## A. N<sup>+</sup> Emitter Region

The  $N^+$  emitter layer can be simply characterized as a hole sink. The hole current at junction  $J_0$  is obtained by the equation

$$I_{p0} = qAh_n n_{B0} P_B. (1)$$

TABLE II

CIRCUIT PARAMETERS FOR EXPERIMENTS AND SIMULATIONS

| Parameters | Units | Value |

|------------|-------|-------|

| $V_{dc}$   | V     | 450   |

| $R_I$      | Ω     | 109   |

| $R_S/L_S$  | Ω/nH  | 1/330 |

| $R_L/L_L$  | Ω/mH  | 16/33 |

Fig. 3. 1-D cross section used for modeling the SiC BJT showing the hole and electron currents in each region.

The  $N^+$  emitter recombination parameter  $h_n$  depends on emitter properties such as doping level  $N_E$ , hole diffusivity  $D_p$ , and hole minority lifetime  $\tau_p$

$$h_n = \frac{N_E}{n_i^2} \sqrt{\frac{D_p}{\tau_p}}. (2)$$

The electron current component at junction  $J_0$  is determined by

$$I_{n0} = I_C - I_{n0}. (3)$$

The voltage drop across the junction  $J_0$  is

$$V_{j0} = V_T \ln \left( \frac{n_{B0}(n_{B0} + P_B)}{n_i^2} \right). \tag{4}$$

## B. P-Base Region

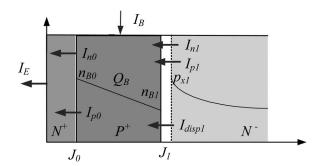

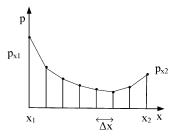

The P-base region is used to find the boundary current at junction  $J_1$ . The lumped charge method is used to model the charge behavior in the base region due to its moderate doping level and comparatively narrow base width. The injected carrier distribution in the base region during conduction is shown in Fig. 4.

Using the continuity equation for the base region, the injected minority carrier charge is described by the relation

$$\frac{dQ_B}{dt} + \frac{Q_B}{\tau_{\text{BHL}}} = I_{n0} - I_{n1} = I_B + I_{p1} + I_{\text{disp1}} - I_{p0} \quad (5)$$

where  $\tau_{\rm BHL}$  is the high-level lifetime in the *P*-base region.

Fig. 4. Charge distribution and boundary current components in the *P*-base.

The total electron charge in the base is expressed as

$$Q_B = \frac{n_{B0} + n_{B1}}{2} qAW_B \tag{6}$$

where  $n_{B\,0}$  is the electron concentration at the base region boundary on the emitter side and  $W_B$  is the base width. The electron concentration at the base region boundary on the collector side,  $n_{B\,1}$ , is related to the excess carrier concentration  $p_{x\,1}$  by the doping concentration of the base  $P_B$  by the equation

$$n_{B1} = \frac{p_{x1}^2}{P_B}. (7)$$

Since the diffusion length in the base region is much greater than the base width, the gradient of the electron concentration is approximately linear, giving the electron current at the base–collector junction,  $J_1$ , as

$$I_{n1} = qD_n A \frac{n_{B0} - n_{B1}}{W_B}. (8)$$

The base–emitter voltage  $V_{BE}$  is calculated by the equation

$$V_{BE} = V_T \ln \left( \frac{n_{B0} P_B}{n_c^2} + 1 \right). \tag{9}$$

# C. N<sup>-</sup> Drift Region (Collector)

The voltage drop in this region is calculated during the ON state. The injected excess carrier concentration is determined by the ADE. As for all power switches, high-level injection and quasi-neutral conditions exist. Under high-level injection conditions, the ADE describes the carrier dynamics in the majority of this region

$$D\frac{\partial^2 p(x,t)}{\partial x^2} = \frac{p(x,t)}{\tau} + \frac{\partial p(x,t)}{\partial t}$$

(10)

where D is the ambipolar diffusion coefficient,  $\tau$  is the high-level carrier lifetime within the drift region, and p(x, t) is the excess carrier concentration. The Fourier-series solution of the excess carrier distribution has been proposed in [11] as the solution of the second-order partial differential diffusion equation. It is converted into an infinite set of first-order linear differential equations [solutions in ([11])]

$$p(x,t) = p_0(t) + \sum_{k=1}^{\infty} p_k(t) \cos\left[\frac{k\pi(x-x_1)}{x_2 - x_1}\right]$$

(11)

where

$$p_0(t) = \frac{1}{x_2 - x_1} \int_{x_1}^{x_2} p(x, t) dx$$

$$p_k(t) = \frac{2}{x_2 - x_1} \int_{x_1}^{x_2} p(x, t) \cos\left(\frac{k\pi(x - x_1)}{x_2 - x_1}\right) dx. \quad (12)$$

The solution to the ADE is given by the following first-order differential equations as each of them refers to a harmonic  $p_k(t)$  of the total minority carrier density p(x,t):

for  $k = 1, 2, 3 \dots$

$$\frac{2D}{x_2 - x_1} \left[ \frac{\partial p(x,t)}{\partial x} \Big|_{x_2} (-1)^k - \frac{\partial p(x,t)}{\partial x} \Big|_{x_1} \right] \\

= \frac{dp_k(t)}{dt} + \left[ \frac{1}{\tau} + \frac{Dk^2 \pi^2}{(x_2 - x_1)^2} \right] p_k(t) \\

+ \frac{2}{x_2 - x_1} \left( \sum_{\substack{n=1\\n \neq k}}^{\infty} \frac{n^2}{n^2 - k^2} \left[ \frac{dx_1}{dt} - (-1)^{n+k} \frac{dx_2}{dt} \right] p_n(t) \\

+ \frac{p_k}{4} \left( \frac{dx_1}{dt} - \frac{dx_2}{dt} \right) \right)$$

for

$$k = 0$$

$$\frac{D}{x_2 - x_1} \left[ \left. \frac{\partial p(x, t)}{\partial x} \right|_{x_2} - \left. \frac{\partial p(x, t)}{\partial x} \right|_{x_1} \right] = \frac{dp_0(t)}{dt} + \frac{p_0(t)}{\tau} + \frac{1}{x_2 - x_1} \sum_{i=1}^{\infty} \left[ \frac{dx_1}{dt} - (-1)^n \frac{dx_2}{dt} \right] p_n(t) \tag{13}$$

$$p_{x_1} = \sum_{k=1}^{n} p_k$$

and  $p_{x_2} = \sum_{k=1}^{n} (-1)^k p_k$ .

The solution to the ADE is determined by using the boundary conditions at the edges of the charge storage region (CSR). The representation requires the width of the undepleted region and the hole and electron currents at the boundaries of the drift region, which give the gradients of the carrier concentrations at  $x_1$  and  $x_2$ , respectively. The required boundary conditions are given in

$$\frac{\partial p}{\partial x}\Big|_{x_1} = \frac{1}{2q} \left( \frac{J_n}{D_n} + \frac{J_p}{D_p} \right) \Big|_{x_1} \text{ and } \frac{\partial p}{\partial x}\Big|_{x_2}$$

$$= \frac{1}{2q} \left( \frac{J_n}{D_n} + \frac{J_p}{D_p} \right) \Big|_{x_2}.$$

(14)

The displacement currents  $I_{\text{disp1}}$  and  $I_{\text{disp2}}$  are due to the changing depletion widths at junctions  $J_1$  and  $J_2$

$$I_{\text{disp1}} = C_{J1} \frac{dV_{d1}}{dt} = \varepsilon A \frac{1}{W_{d1}} \frac{dV_{d1}}{dt}$$

$$I_{\text{disp2}} = C_{J2} \frac{dV_{d2}}{dt} = \varepsilon A \frac{1}{W_{J2}} \frac{dV_{d2}}{dt}.$$

(15)

Fig. 5. Carrier distribution in the lightly doped region.

The voltages across the  $N^-N^+$  and  $N^-P^+$  depletion layers,  $V_{d1}$  and  $V_{d2}$ , are calculated by the following equations:

$$V_{d1} = \begin{cases} 0 & \text{if } p_{x1} > 0 \\ -K_{FV} p_{x1} & \text{otherwise} \end{cases}$$

$$V_{d2} = \begin{cases} 0 & \text{if } p_{x1} > 0 \\ -K_{FV} p_{x2} & \text{otherwise.} \end{cases}$$

(16)

The feedback constant  $K_{FV}$  is set to  $10^{-12}$ , which gives good convergence and minimal error [12]. The associated depletion widths  $W_{d1}$  and  $W_{d2}$  are calculated using a step doping concentration change on each side of the junction

$$W_{d1} = \sqrt{\frac{2\varepsilon V_{d1}}{qN_{N^{-}} + (|I_{c}|/Av_{\text{sat}})}}$$

$$W_{d2} = \sqrt{\frac{2\varepsilon V_{d2}}{qN_{N^{-}} + (|I_{c}|/Av_{\text{sat}})}}.$$

(17)

The boundary positions  $x_1$  and  $x_2$  are calculated by

$$x_1 = W_{d1}$$

$$x_2 = W_{N^-} - W_{d2}.$$

(18)

The voltages at junctions  $J_1$  and  $J_2$  are

$$V_{j1} = 2V_T \ln \left(\frac{p_1}{n_i}\right)$$

$$V_{j2} = V_T \ln \left(\frac{p_{x2}}{N_C}\right). \tag{19}$$

The voltage drop in the carrier storage region  $V_{\rm CSR}$  is calculated based on the injected carrier concentration. The 1-D charge distribution in the lightly doped (carrier storage, CSR) region during the ON state is illustrated in Fig. 5.

The CSR is divided into equal width segments with the number of segments (M) being the same as the number of terms in the truncated Fourier series. The carrier distribution at every point is generated through the inverse Fourier transformation, while the carrier distribution between two points is a linear interpolation. Based on [11], the voltage drop in the region  $V_{\rm CSR}$

at any time is calculated by

$$V_{\text{CSR}} \approx \frac{I_C}{qA(\mu_n + \mu_p)} \frac{x_2 - x_1}{M - 1} \sum_{K=0}^{M - 1} \times \left[ \frac{1}{p_{T(k)} - p_{T(k-1)}} \ln \left( \frac{p_{T(k)}}{p_{T(k-1)}} \right) \right] + V_T \left( \frac{\mu_n - \mu_p}{\mu_n + \mu_p} \right) \ln \left( \frac{p_{x2}}{p_{x1}} \right)$$

(20)

where the carrier distribution  $p_{T(k)}$  is calculated as

$$p_{T(k)} = p\left(x_1 + \frac{k(x_2 - x_1)}{M - 1}\right) + \frac{\mu_n N_B}{\mu_n + \mu_p}.$$

(21)

#### D. N<sup>+</sup> Collector Region

The  $N^+$  collector region is similar to the  $N^+$  emitter region as it is also a hole sink. The hole current at junction  $J_2$  is obtained by the equation

$$I_{p2} = qAh_n p_{x2}^2. (22)$$

The electron current at junction  $J_2$  is

$$I_{n2} = I_c + I_{p2} - I_{\text{disp2}}.$$

(23)

#### E. Voltage Drop

The voltage drop  $V_{CE}$  across the high-power SiC BJT is comprised of six components including voltages across junctions  $J_0$ ,  $J_1$  and pseudojunction  $J_2$ , the voltage across the two depletion regions  $V_{d1}$  and  $V_{d2}$ , and the voltage across the carrier storage region  $V_{\rm CSR}$

$$V_{CE} = V_{i0} + V_{i1} + V_{i2} + V_{d1} + V_{d2} + V_{CSR}.$$

(24)

#### III. REALIZATION IN SIMULINK

The model of the high-power SiC BJT is implemented using MATLAB incorporated with Simulink. It is straightforward to couple Simulink to the numerical algorithm to solve differential equations [13]. The MATLAB program is used to input the basic parameters used by the Simulink program. The input parameters for the Simulink model are the device geometry parameters, the doping concentrations in each region (assumed to be uniform), charge carrier diffusion coefficients, and minority carrier lifetimes of different regions. SiC material parameters, such as hole and electron mobilities, dielectric permittivity, carrier saturation velocity, and the intrinsic carrier concentration (at 300 K), are also needed.

The implementation of the behavior of the BJT in Simulink requires use of a stiff solver due to the widely different time constants present in the model. Suitable solvers for simulation of power semiconductor devices are ode15s and ode23tb [14]. The configuration parameters chosen for the SiC BJT model are solver 23s (stiff/Mod. Rosenbrock); the maximum and minimum step sizes are, respectively,  $10^{-6}$  and  $10^{-120}$  s. The initial step size is set to "auto." The relative and absolute tolerances are set to be  $10^{-3}$  and  $10^{-5}$ , respectively. The simulation advanced options are set to use inline parameters, which means that the

Fig. 6. Switching test circuit used for experiments of a SiC BJT (see Fig. 1) implemented on Simulink.

parameters are fixed during a simulation run. The zero-crossing control is set to be "disable all."

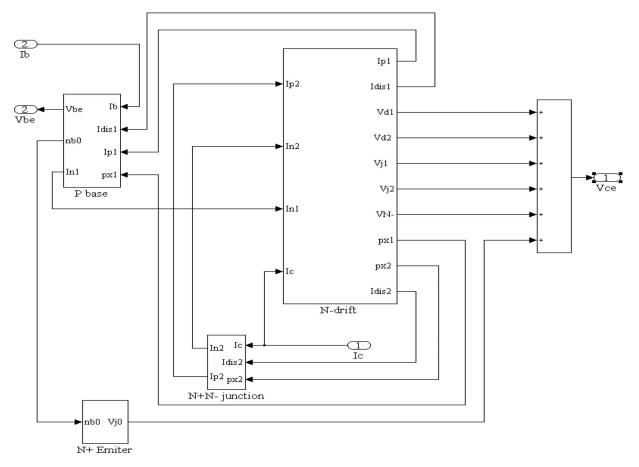

The electrical test circuit (see Fig. 1) of the SiC BJT under clamped inductive switching is realized in the MAT-LAB/Simulink environment. The diagram is presented in Fig. 6.

The high-power SiC BJT Simulink model is presented in Fig. 7. It has two inputs, collector and base currents, and two outputs, base–emitter and collector–emitter voltages. The BJT subsystem further contains embedded subsystems of the  $N^-$  drift region, the P-base, the  $N^+N^-$  pseudojunction,  $N^+$  emitter, and a sum for the total voltage drop.

The  $N^+$  emitter subsystem is used to calculate the voltage drop at junction  $J_0$  using (4).

The P-base subsystem is used to calculate the current  $I_{n1}$ , voltage  $V_{BE}$ , and minority carrier concentration  $n_{B0}$  at junction  $J_0$  by using (5)–(9).

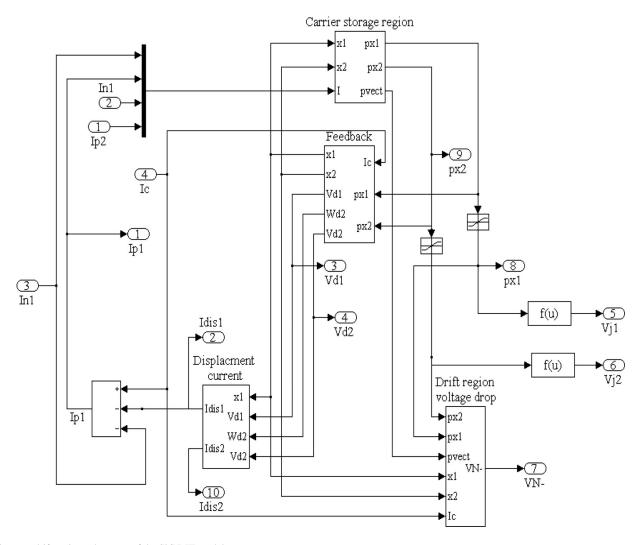

The N <sup>-</sup> drift region subsystem presented in Fig. 8 is the most important and complicated subsystem in the power BJT model. It consists of four subsystems: carrier storage region (CSR), feedback, drift region voltage drop, and displacement current.

The CSR subsystem provides the solution to the ADE, (10), by using the Fourier solution; (13); and the boundary conditions of (14). The feedback subsystem uses the output data from the CSR subsystem, the charge carrier densities  $p_{x1}$  and  $p_{x2}$ , as inputs. These carrier densities are used to determine  $V_{d1}$  and  $V_{d2}$  using (16). The boundary positions  $x_1$  and  $x_2$  are calculated using (17) and (18). They are input signals to the CSR subsystem, and also to the displacement current subsystem.

The value for the carrier densities  $p_{x1}$  and  $p_{x2}$  are limited to the minimum of  $n_i$  and used to calculate the junction voltage  $V_{j1}$  and  $V_{j2}$  using (19).

Fig. 7. SiC BJT subsystem implemented on Simulink.

The displacement current subsystem calculates the displacement currents at junctions  $J_1$  and  $J_2$  implementing (15). The drift region voltage drop subsystem uses the parameters of the other subsystems and calculates the voltage drop in the storage region using (20) and (21).

The  $N^+N^-$  junction subsystem calculates  $I_{n2}$  and  $I_{p2}$ ; (22) and (23).

The total voltage  $V_{CE}$  is given as a sum the junction, the drift region, and the depletion layer voltages from (24).

#### IV. MEASUREMENT AND SIMULATION RESULT OF SIC BJT

To evaluate the behavior of the power semiconductor switches, two basic tests are usually employed: a static test and a dynamic test [15]. Generally, the static measurement is used to validate dc current and voltage characteristics while the dynamic test is used for measuring transient switching behavior.

The static measurement includes the *I–V* and *C–V* characteristics of semiconductor devices under dc conditions, breakdown voltage, and on-state voltage drop. The BJT dies used for the measurements are rated at 1200 V-5A. The *I–V* curves are measured with a curve tracer, Tektronix TEK 371A.

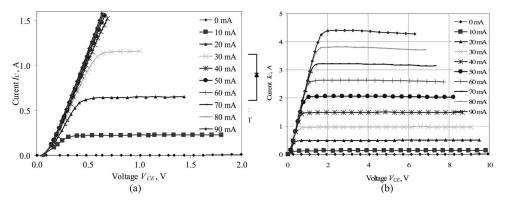

The measured common emitter I-V curves at room temperature for two different ranges of collector emitter voltage  $V_{CE}$  0–2 V and 0–10 V are plotted in Fig. 9. The base current is increased from 0 to 90 mA in steps of 10 mA. Typically increasing

the collector–emitter voltage when the transistors are operating in the active region results in a slight positive slope due to the Early effect. Instead, for the high-power SiC BJTs, it was observed that the collector current remained constant for low-base current values ( $I_B < 50\,\mathrm{mA}$ ). For base currents higher than 50 mA, an increasing  $V_{CE}$  leads to a decrease in collector current. This is thought to be due to self-heating, which reduces the carrier mobility, and from increased effects due to surface states in these small-area devices [15]. The dc characteristics are only included as supplemental information for the reader. The core of the work was to extend previously developed Si IGBT models to SiC BJT for future converter designs. Therefore, modeling the switching operations is of prime importance.

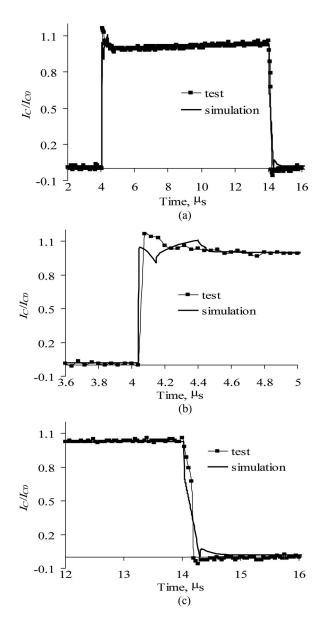

The experimental and simulation results of the inductive switching tests on the SiC BJT at 450 V are presented in Fig. 10. It can be noticed that there is a small discrepancy between the experimental and simulation results during turn-on and turn-off. This discrepancy between the measured and simulated collector currents is probably caused by the differences in the freewheeling diode used in the model as compared to the experiments. The switching experiment was done using a high-voltage Schottky diode C3D20060, while during the simulation a power SiC  $PN^-N^+$  diode model was used. The details of the diode model are given in [11] and [16]. The intent of using the pin diode structure was to verify the robustness of the device models

Fig. 8.  $N^-$  drift region subsystem of the SiC BJT model.

Fig. 9. Common-emitter I-V curve of SiC BJT at room temperature: (a)  $V_{CE}=0$ –2 V; (b)  $V_{CE}=0$ –10 V.

through convergence of the simulation to the correct results when using more than one power device. The focus in this study was on the BJT behavior, so only the diode recovery was important for a correct description of the BJT behavior. Hence, the

recovery time of the modeled SiC  $PN^-N^+$  diode was adjusted to match the reverse recovery behavior of the Schottky diode.

From the results of the switching tests, it can be noted that there was approximately a 40-ns rise-time during collector

Fig. 10. Switching characteristics of the ratio of the collector current  $I_C$  / $I_{C\ 0}$  of SiC BJT at 450 V and  $I_{C\ 0}=2.7$  A: (a) pulse; (b) turn-on; and (c) turn-off.

current turn-on and approximately a 200-ns fall-time during turn-off. Similar results are given in [17].

## V. CONCLUSION

At the current density switched, 400 A/cm<sup>2</sup>, the BJT exhibits about a 2-V forward collector—emitter drop. This is about 0.5 V larger than in a Si IGBT rated for the same breakdown. However, at higher breakdown ratings, the SiC BJT should exceed the Si IGBT performance in internal power loss and exhibit superior thermal behavior, both in junction temperature and thermal conductivity.

It should also be noted that the SiC BJT does not exhibit a quasi-saturation region as is typical in Si power bipolar tran-

sistors. It is yet to be determined if SiC BJTs exhibit second breakdown effects as their Si counterparts do. The devices tested seem robust and not prone to turn-off failure during inductive switching.

Further refinements in the Fourier modeling are underway and will be extended to other SiC bipolar structures such as a GTO.

#### ACKNOWLEDGMENT

The authors would like to thank Cree, Inc., which provided the SiC BJT samples used for characterization in this study.

#### REFERENCES

- [1] W. J. Schaffer, G. H. Negley, K. G. Irvine, and J. W. Palmour, "Conductivity anisotropy in epitaxial 6H and 4H SiC," in *Proc. MRS*. vol. 339: @Materials Research Society, 1994, pp. 595–600. DOI: http://dx.doi.org/10.1557/PROC-339-595.

- [2] S. H. Ryu, A. K. Agarwal, R. Singh, and J. W. Palmour, "1800 V NPN bipolar junction transistors in 4H-SiC," *IEEE Electron. Device Lett.*, vol. 22, no. 3, pp. 119–120, Mar. 2001.

- [3] W. V. Muench and P. Hoeck, "Silicon carbide bipolar transistor," Solid-State Electron., vol. 21, pp. 479–480, 1978.

- [4] Y. Luo, L. Fursin, and J. H. Zhao, "Demonstration of 4 H-SiCpower bipolar junction transistors," *IEE Electron. Lett.*, vol. 36, no. 17, pp. 1496–1497, Aug. 2000.

- [5] S. Balachandran, C. Li, P. A. Losee, I. B. Bhat, and T. P. Chow, "6 kV 4 H-SiC BJTs with specific on-resistance below the unipolar limit using a selectively grown base contact process," in *Proc. 19th Int. Symp. Power Semiconductor Devices and IC's*, 2007, pp. 293–296.

- [6] E. Santi, J. L. Hudgins, and H. A. Mantooth, "Variable model levels for power semiconductor devices," in *Proc. 2007 Summer Comput. Simulation Conf.*, Jul. 2007, pp. 276–283.

- [7] H. Z. Fardi, "Modeling dc gain performance of 4 H-SiC BJTs," COMPEL, vol. 26, no. 5, pp. 1236–1246, 2007.

- [8] P. R. Palmer, E. Santi, J. L. Hudgins, X. Kang, J. C. Joyce, and P. Y. Eng, "Circuit simulator models for the diode and IGBT with full temperature dependent features," *IEEE Trans. Power Electron.*, vol. 18, no. 5, pp. 1220–1229, Sep. 2003.

- [9] X. Kang, "Characterization and modeling of trench gate IGBT," Ph.D. dissertation, Dept. Elect. Eng., Univ. South Carolina, Dec. 2002.

- [10] A. T. Bryant, Liqing Lu, E. Santi, P. R. Palmer, and J. L. Hudgins, "Physical modeling of fast p-i-n diodes with carrier lifetime zoning: Part I. Device model," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 189–197, Jan. 2008.

- [11] A. T. Bryant, P. R. Palmer, E. Santi, and J. L. Hudgins, "Simulation and optimization of diode and insulated gate bipolar transistor interaction in a chopper cell using MATLAB and simulink," *IEEE Trans. Ind. Appl.*, vol. 43, no. 4, pp. 874–883, Jul./Aug. 2007.

- [12] A. Brant, "Simulation and optimization of diode and IGBT interaction in a chopper cell," Ph.D. dissertation, Univ. Cambridge, Jan. 2005.

- [13] The MathWorks, Inc. (1994–2012). [Online]. Available: http://www.mathworks.com

- [14] L. F. Shampine and M. W. Reichelt, "The MATLAB ODE suite," SIAM J. Sci. Comput., vol. 18, no. 1, pp. 1–22, Jan. 1997.

- [15] P. B. Klein, J. A. Freitas, Jr., S. C. Binari, and A. E. Wickenden, "Observation of deep traps responsible for current collapse in GaN metal semiconductor field effect transistors," *Appl. Phys. Lett.*, vol. 75, pp. 4016–4018, 1999

- [16] A. T. Bryant, M. R. Jennings, N.-A. Parker-Allotey, P. A. Mawby, A. Perez-Tomas, P. Brosselard, P. Godignon, X. Jorda, J. Millan, P. R. Palmer, E. Santi, and J. L. Hudgin, "Physical modelling of large area 4 H-SiC PiN diodes," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2009, pp. 986–993.

- [17] T. K. Gachovska, B. Du, J. L. Hudgins, A. Grekov, A. Bryant, E. Santi, H. A. Mantooth, and A. Agarwal, "Modeling and simulation of a SiC BJT," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2009, pp. 979–985.

**Tanya Gachovska** (S'08) received the M.Eng. degree in automation of production and the Ph.D. degree in pulsed electric field from the University of Ruse, Ruse, Bulgaria, in 1995 and 2003, respectively.

From 1999 to 2003, she was an Assistant Professor in the University of Ruse. She conducted research for two years and taught for a semester at McGill University, Montreal, Canada. For 18 months, she was a Postdoctoral Researcher involved in PEF at the University of Nebraska Lincoln, Lincoln, NE, and in 2008 she started her second PED on modeling of

mower semiconductor devices. During her studies, she has taught different courses in labs and continued collaboration for PEF research with University of Ruse, McGill, and UNL. She is Student Teacher, and Research Assistant in UNL. She is the author or coauthor of more than 30 technical papers and conference presentations, and holds a world patent.

**Jerry L. Hudgins** (S'79–M'85–SM'91–F'04) received the Ph.D. degree in electrical engineering in 1985 from Texas Tech University, Lubbock, TX.

He is currently the Chair of the Department of Electrical Engineering, the Director of the Nebraska Wind Applications Center, and the Associate Director of the Nebraska Energy Sciences Research Center, University of Nebraska-Lincoln, NE. Previously, he was on the faculty at the University of South Carolina until 2004. He has published more than 120 technical papers and book chapters concerning power semicon-

ductors and engineering education, and was with numerous industries.

Dr. Hudgins served as the President of the IEEE Power Electronics Society for 1997 and 1998, and as the President of the IEEE Industry Applications Society for 2003. He is the 2012 IEEE Division-II Director-Elect.

Angus Bryant (S'02–M'06) received the M.Eng. degree in electrical and information sciences and the Ph.D. degree in power electronics both from Queens' College, Cambridge University, Cambridge, U.K., in 2001 and 2005, respectively.

He was a Research Fellow at the School of Engineering, University of Warwick, Coventry, U.K., where he was involved in power device modeling. He became an Assistant Professor at the University of Warwick in 2007. Since 2010, he has been with Converteam U.K. Ltd, Rugby, U.K., where he is involved

with design of low- and medium-voltage drives. His main interests include semiconductor device modeling, simulation and characterization of power electronic systems, power module reliability and thermal modeling, and optimization and testing of power electronic systems under realistic loading conditions. He is a member of the Institution of Engineering Technology.

Enrico Santi (SM'01) received the Dr. Ing. degree in electrical engineering from the University of Padua, Padua, Italy, in 1988, and the M.S. and Ph.D. degrees from Caltech, CA, in 1989 and 1994, respectively.

He was a Senior Design Engineer at TESLAco from 1993 to 1998, where he was responsible for the development of various switching power supplies for commercial applications. Since 1998, he has been with the University of South Carolina, Columbia, where he is currently an Associate Professor in the Department of Electrical Engineering. He has pub-

lished more than 100 papers in power electronics and modeling and simulation in international journals and conference proceedings and holds two patents. His research interests include switched-mode power converters, advanced modeling and simulation of power systems, modeling and simulation of semiconductor power devices, and control of power electronics systems.

**H.** Alan Mantooth (S'83–M'90–SM'97–F'09) received the B.S. (*summa cum laude*) and M.S. degrees in electrical engineering from the University of Arkansas (UA), Fayetteville, in 1985 and 1987, respectively, and the Ph.D. degree from the Georgia Institute of Technology, Atlanta, in 1990.

He joined Analogy in 1990 where he focused on semiconductor device modeling and the research and development of HDL-based modeling tools and techniques. Besides modeling, his interests include analog- and mixed-signal IC design and power elec-

tronics. In 1996, he was a Distinguished Technical Staff Member at Analogy (now owned by Synopsys). In 1998, he joined the faculty of the Department of Electrical Engineering, UA, as an Associate Professor and became a Full Professor in 2002. In 2003, he cofounded Lynguent, an EDA company focused on modeling and simulation tools. He helped establish the National Center for Reliable Electric Power Transmission at the UA in 2005, for which he serves as a Director. In 2006, he was selected as the inaugural holder of the 21st Century Endowed Chair in mixed-signal IC design and CAD. He has published more than 100 refereed articles on modeling and IC design. He holds patents on software architecture and algorithms for modeling tools and has others pending. He is a coauthor of the book *Modeling with an Analog Hardware Description Language* (Kluwer) and has served on several technical program committees for IEEE conferences.

Dr. Mantooth has received numerous teaching, service, and research awards since returning to the UA. He was also selected to the Georgia Tech Council of Outstanding Young Engineering Alumni in 2002, and the Arkansas Academy of Electrical Engineers in 2006. He was the Technical Program Chair for the IEEE International Workshop on Behavioral Modeling and Simulation (BMAS) in 2000 and the General Chair in 2001. He served as a Guest Editor for the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN and the *IET Computers and Digital Techniques*, and as an IEEE Circuits and Systems Society Distinguished Lecturer. He is currently serving the profession as IEEE CAS representative on the IEEE Council on Electronic Design Automation and a member of the Power Electronics Society Advisory Committee as Chair of the Society's Standards Committee. He is a member of Tau Beta Pi and Eta Kappa Nu, and Registered Professional Engineer in AR.

Anant K. Agarwal (SM'06–F'12) received the B.E. degree in electrical engineering from MNR Engineering College, University of Allahabad, Allahabad, India, in 1978, the M.S. degree in electrical engineering from University of Tennessee Space Institute, Tullahoma, in 1981, and the Ph.D. degree in electrical engineering from Lehigh University, Bethlehem, PA, in 1984.

From 1984 to 1985, he was with Bell Laboratories, Murray Hill, NJ, where he developed highspeed GaAs digital circuits for optical communication cir-

cuits. From 1985 to 1990, he was an Assistant Professor with the MNR Engineering College. From 1990 to 1999, he was with Northrop Grumman Science and Technology Center (formerly, Westinghouse STC), Pittsburg, PA, where his research interests included SiC power and microwave device design and processing, design and process of SiC GTOs, UMOSFETs, DMOSFETs, and SITs for a variety of externally and internally sponsored programs, and development of SiGe HBTs for X-band power amplifiers. Since 1999, he has been with Cree, Inc., Durham, NC, where his research interests include SiC high-power high-temperature devices. He is the author or coauthor of more than 200 technical papers and conference presentations, and holds 21 U.S. patents.

Dr. Agarwal is a Senior Member of the IEEE Electron Device Society.