**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# Modelling and Analysis of Novel Topology for Multilevel Inverter With Reduce Number of Switches

Rohit Kumar<sup>1</sup>, Shimi S.L<sup>2</sup>, Shivendra Kaura<sup>3</sup>

<sup>1</sup> ME Scholar, Electrical Department, NITTTR, Chandigarh

<sup>2</sup> Assistant Professor, Electrical Department, NITTTR, Chandigarh

<sup>3</sup>Shivendra Kaura, Assistant Professor, Electrical Department, GLBITM, Gr. Noida \*Corresponding author E-mail.<sup>1</sup>nitttrrohit2016@gmail.com

#### Abstract

The demand of quality power is increasing continuously. The problem of global warming and rate of decrease of non-renewable energy sources are increasing day by day. Hence renewable energy sources such as fuel cell, solar, Magneto hydro Dynamic (MHD), geothermal are the best alternatives to solve the problem of environmental issue and increasing demand of energy. The output of these resources is dc, therefore to connect these resources to the grid, multilevel inverter is the key device. But the output of multilevel inverter has power quality issues such as harmonic generation and notching due to conversion of dc to ac and high number of switch. Hence, this paper deals with harmonic elimination using Genetic Algorithm based Selective Harmonic Elimination (GA-SHE) techniques for asymmetric and symmetric topology of MLI. In the present study, comparative study among the 5-level, 7-level, 9-level, 11-level and 15-level multilevel inverters with reduced number of switches topologies has been discussed. A novel topology of 15-level inverter which consists least number of switches has been designed for a desired voltage level. Also, the comparison of Total harmonic distortion developed in the output voltage generated by different topology at different levels with the proposed 15-level inverter topology are discussed.

Keywords: Multilevel Inverter(MLI), Selective Harmonic Elimination(SHE),

## 1. Introduction

The power quality and the rate of decrease in non-renewable energy sources are the major issues of present time [1]. Therefore, fuel cell, solar energy, Magneto hydro Dynamic (MHD), geothermal are the best alternatives to solve the problem of environmental issue. The flexibility of connecting renewable energy sources with grid is due to multilevel inverter [1]. Now in recent days MLI has drawn large interest in high power industry [2]. The multilevel VSI allows to achieve high voltages with the less harmonics without using series connected synchronized switching devices or transformers [3][4]. Generally multilevel which is used for industrial application are classified as: Diode clamped, Flying capacitor, Cascaded H-bridge. Flying capacitor and diode-clamped inverter suffered from the problem of capacitor voltage balancing and this problem is resolved in cascaded H-bridge inverter [4][5][6][7]. Cascaded H-bridge MLI has a combination of switches with dc sources to create a one cell and then a lot of number of cells are connected in series for increasing voltage level [8]. The cascaded H- bridge multilevel inverter can be classified as symmetric or asymmetric. The asymmetric topologies use the unequal dc voltage sources on the other hand symmetric topologies have equal voltage sources [9]. Number of switches and dc voltage sources required in asymmetric topology is less as compared with symmetric topologies [8]. But main limitation with cascaded Hbridge MLI is the requirement of separate dc voltage sources for every H- bridge [8]. Hence, cascaded H- bridge is bulkier in size and costly. In last few decade, different types of multilevel inverter topologies have been researched. These topologies provide the output voltage with lot of number of switches which leads to higher switching losses and notching. In this paper such type of topologies which had been researched in recent year are discussed. A novel topology which is presented in this paper is simplest and gives high power quality output voltage. This novel topology has less number of switches in comparison with conventional Hbridge and other topologies which are discussed in this paper. This novel topology follows IEEE519 standard according to which the total harmonic distortion of the output voltage is less than 5% [1]. The general optimization technique Genetic algorithm (GA) is used to determine the firing angle of switches of proposed topology.

# 2. Existing Topologies

## 2.1 Seven Level Nine Switch MLI Topology

This topology is proposed in [8]. This topology is developed with five switches and 3 dc voltage sources along with one H-bridge having 4 switches which is used for reversal of polarity to generate 3 positives(+ve) and 3 negative(-ve) and one zero-voltage level [10]. This topology is known as sub-multilevel inverter topology. This topology consists of both, bidirectional and unidirectional switches. Bidirectional switch can be designed by connecting two IGBTs back to back with antiparallel diode [6][8]. Various voltage levels can be obtained by adding voltage source and switches. A sub-multilevel inverter cell: No. of switches driver = N<sub>drive,sub</sub> No. of switch =N<sub>switch,sub</sub>

No. of IGBT= $N_{IGBT,sub}$ Output level=  $N_{Level}$

Copyright © 2018 Authors. This is an open access article distributed under the <u>Creative Commons Attribution License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Output levels are calculated as[8]:

Nswitch, sub =

$$\begin{cases} 2, & \text{for } n = 1\\ (n+2), & \text{for } n \ge 2 \end{cases}$$

(1)

$$N_{IGBT,sub} = 2n$$

(2)

$$N_{\text{Level}} = 2mn + 1 \tag{3}$$

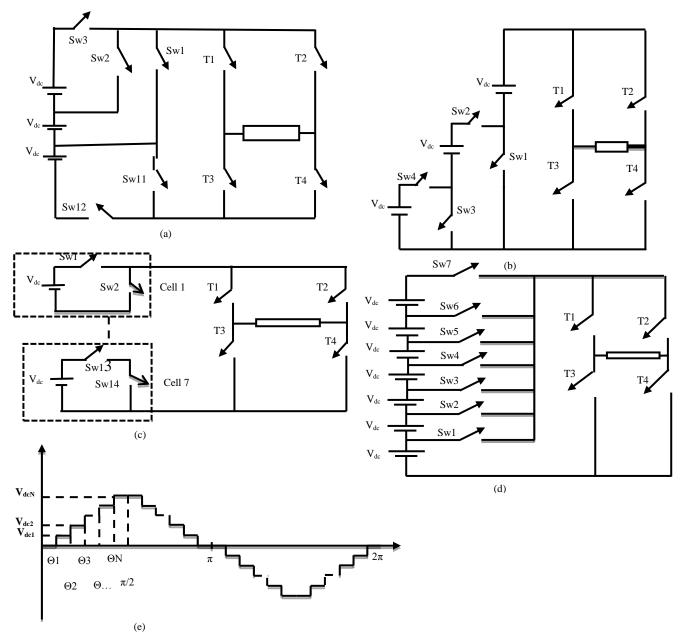

This topology as shown in Fig.1(a). The switching opertaions for getting desired output voltage level in this topology are shown in Table.1

#### 2.2 Seven Level Eight Switch MLI Topology

This topology is proposed in [11]. This topology is developed with four switches and 3 dc voltage sources along with one H-bridge having 4 switches which is used for reversal of polarity to generate 3 +ve and 3 -ve and one zero -voltage levels [10]. Different voltage levels can be achieved by adding voltage sources and switches [12]. This topology is known as Prior H-bridge cell based MLI. This topology as shown in Fig.1(b). The different switching opertaion for getting seven level output voltage using this topology are shown in Table.2

#### 2.3 Fifteen Level Eighteen Switch MLI Topology

This topology is proposed in [13]. This topology is developed with fourteen switches and seven dc voltage sources having one Hbridge which is having 4 switches which are used for reversal of polarity to generate 7 +ve and 7 -ve and one zero voltage level [8]. This topology as shown in Fig.1(c). Required switching opertaion for getting fiften level output voltage using this topology is shown in Table.3

## 3. Proposed Topology

Fig.6 represents proposed topology. It is obtained by seven dc voltage sources which may be unequal or equal in value. For equal voltage step, equal voltage sources are used and for unequal voltage step, unequal voltage sources are used [8]. This topology is obtained by unidirectional and bidirectional switches both. This topology consists of bidirectional switches which are required to oppose +ve and -ve voltage when load is inductive in nature.

The desired levels of output voltage from this topology is obtained by this equation,

$$N_{level} = 2n + 1 \tag{4}$$

Where, n denotes the number of dc voltage source. The number of switches which is required in this topology except bridge switch can be obtained from the following equation.

$$N_{switch} = n \tag{5}$$

This topology is designed for the 15-level output voltage. The 15-level output is developed with seven switches and seven dc voltage sources having 1-H-bridge which is having 4 switches which are used for reversal of polarity to generate seven +ve and seven -ve and 1 zero-voltage level. This topology as shown in Fig.1(d). The switching operation for getting fifteen level output voltage using this topology is shown in Table.4

# 4. Genatic Algorithm - Selective Harmonic Elimnation

Fig.1(es) shows a stepped voltage waveform generated by a (2N+1) –level inverter, where N is considered as number of volt-

age sources. The proposed topology is having 7 sources. In this paper 15-level inverter is simulated and analyzed using Fourier series for the harmonic reduction [14].

Proposed multilevel inverter topology is represented as: N

$$V_n = \frac{4V_{dc}}{n\pi} \sum_{m=1}^{\infty} \cos(n\theta_m) \tag{6}$$

Where, N is equal to 7 for 15-level inverter.

Where n= 1,3,5,7,9,11..... **V**<sub>deN</sub> is the maximum dc voltage of the multilevel inverter. The firing angles  $\Theta_1$ ,  $\Theta_2$ ,  $\Theta_3$ ,  $\Theta_4$ ,  $\Theta_5$ ,  $\Theta_6$ ,  $\Theta_7$  must fulfill the following limits [10].

$$0 < \theta_1 \le \theta_2 \le \theta_3 \le \theta_4 \le \theta_5 \le \theta_6 \le \theta_7 < \frac{\pi}{2}$$

The main objective of selective harmonic elimination techniqueis to find the firing angles  $\Theta_1$ ,  $\Theta_2$ ,  $\Theta_3$ ,  $\Theta_4$ ,  $\Theta_5$ ,  $\Theta_6$ ,  $\Theta_7$ . So that fundamental component of output is adjusted to desired amplitude and non-triple odd harmonic components can be eliminated. There are no triple order harmonics in 3-phase system. Mathematically, for a 3-phase system with symmetrical topology following set of different order harmonics equations are formulated [14].

$$\sum_{m=1}^{N} \cos(\theta_m) - NM = 0 \tag{8}$$

$$\sum_{m=1}^{N} \cos(5\theta_m) = 0 \tag{9}$$

$$\sum_{m=1}^{N} \cos(7\theta_m) = 0 \tag{10}$$

$$\sum_{m=1}^{N} \cos(11\theta_m) = 0 \tag{11}$$

$$\sum_{m=1}^{N} \cos(13\theta_m) = 0 \tag{12}$$

Where M is known as modulation index which is formulated as:

$$M = \frac{v_1}{4N^{\frac{V_{de}}{\pi}}} \qquad (0 < M \le 1) \tag{14}$$

To determine the firing angles, the eq. (8) to eq. (12) are solved by using GA.

#### 4.1 Genetic Algorithm

In the field of Artificial intelligence (AI), Genetic Algorithm is an evolutionary algorithm which can provide an optimized solution of a problem in which objective function may be continuous, discontinuous, Non-linear or stochastic in nature.

First, it selects individual heuristically from the initial population, who act as parents to generate offspring for next generation. A new population is generated after each iteration through crossover and mutation [14]. The process is continuously run till the point they are fulfilled end condition. In this paper, the problem of Selective Harmonic Elimination (SHE) has been solved using Genetic Algorithm. All the lower order harmonic such as  $5^{\text{th}}$ ,7<sup>th</sup>,11<sup>th</sup>,13<sup>th</sup> are eliminated using GA.

Fig.1: (a) Sub-multilevel Inverter, (b) Prior H-bridge cell MLI, (c) Fifteen Level Eighteen Switch Topology, d) Proposed Topology, (e) (2N+1)-Level Output Voltage Waveform

## 5. Simulink Model

The simulation and the analogues harmonics analysis for the existing topology and proposed topology are designed in MATLAB/SIMULINK [15].

#### 5.1 Proposed Topology Simulink Model

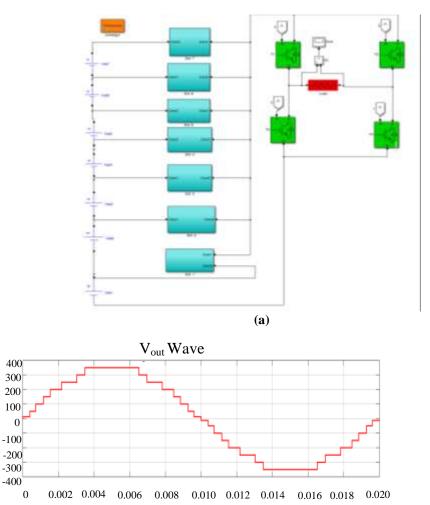

A novel topology is presented in this paper. Detailed configuration and switching sequence of this topology are explained in section III and Table.6 respectively. A single – phase MATLAB/SIMULINK model of this topology is presented in Fig.2(a). This model consists of seven equal voltage source. This MATLAB/SIMULINK model is design with 11 number of switch. In which four switch used for H-Bridge formation. It is an important point that switches S1- S6 are bidirectional switch [9]. The firing angles  $\Theta_1$ ,  $\Theta_2$ ,  $\Theta_3$ ,  $\Theta_4$ ,  $\Theta_5$ ,  $\Theta_6$ ,  $\Theta_7$ for discussed Simulink model are obtained using GA-SHE [1]. The optimal firing angles in radians determined by solving the MATLAB script file at 0.9 modulation index are:  $\Theta_1$ = 0.126,  $\Theta_2$ =0.228,  $\Theta_3$ =0.364,  $\Theta_4$ =0.484,  $\Theta_5$ =0.683,  $\Theta_6$ =0.952,  $\Theta_7$ =1.095. These optimal firing angles are used to generate the pulses for trigging of switches. This SIMULINK model is developed for symmetrical topology. Various modulation techniques can be used in MLI. Fundamental frequency modulation technique is used in this paper [9].

## 6. Simulation Result

This section shows the simulation result of the different topologies discussed in section V [17]. The result of proposed topology is obtained from SIMULINK the model which is shown in Fig.2(a). Output voltage and Total Harmonic distortion result is compared with the result of another topology.

| Table 1: Output voltage for different states of switch | hs |

|--------------------------------------------------------|----|

|--------------------------------------------------------|----|

| State | Sw <sub>1</sub> | Sw11 | Sw <sub>2</sub> | Sw <sub>12</sub> | Sw <sub>3</sub> | T <sub>1</sub> , T <sub>4</sub> | $T_{2}, T_{3}$ | VL                 |

|-------|-----------------|------|-----------------|------------------|-----------------|---------------------------------|----------------|--------------------|

| 1     | 1               | 1    | 0               | 0                | 0               | 1                               | 0              | 0                  |

| 2     | 0               | 1    | 0               | 0                | 0               | 1                               | 0              | 1*V <sub>dc</sub>  |

| 3     | 0               | 0    | 1               | 1                | 0               | 1                               | 0              | 2*V <sub>dc</sub>  |

| 4     | 0               | 0    | 0               | 1                | 1               | 1                               | 0              | 3*V <sub>dc</sub>  |

| 5     | 0               | 1    | 1               | 0                | 0               | 0                               | 1              | -1*V <sub>dc</sub> |

| 6     | 0               | 0    | 1               | 1                | 0               | 0                               | 1              | -2*V <sub>dc</sub> |

| 7     | 0               | 0    | 0               | 1                | 1               | 0                               | 1              | -3*V <sub>dc</sub> |

#### Table 2: Switches State in PHCMLI

| <b>X</b> 7 / | Switch State |    |    |    |     |     |     |     |  |  |

|--------------|--------------|----|----|----|-----|-----|-----|-----|--|--|

| Vout         | T1           | T4 | T2 | T3 | Sw1 | Sw2 | Sw3 | Sw4 |  |  |

| 0            | 0            | 0  | 1  | 1  | 0   | 0   | 0   | 0   |  |  |

| 1*Vdc        | 0            | 0  | 1  | 1  | 1   | 0   | 0   | 0   |  |  |

| 2*Vdc        | 0            | 0  | 1  | 1  | 0   | 1   | 1   | 0   |  |  |

| 3*Vdc        | 0            | 0  | 1  | 1  | 0   | 1   | 1   | 0   |  |  |

| 2*Vdc        | 0            | 0  | 1  | 1  | 0   | 1   | 1   | 0   |  |  |

| 1*Vdc        | 0            | 0  | 1  | 1  | 1   | 0   | 0   | 0   |  |  |

| 0            | 1            | 1  | 0  | 0  | 0   | 0   | 0   | 0   |  |  |

| -1*Vdc       | 1            | 1  | 0  | 0  | 0   | 0   | 0   | 0   |  |  |

| -2*Vdc       | 1            | 1  | 0  | 0  | 1   | 1   | 1   | 0   |  |  |

| -3*Vdc       | 1            | 1  | 0  | 0  | 1   | 1   | 0   | 1   |  |  |

| -2*Vdc       | 1            | 1  | 0  | 0  | 1   | 1   | 1   | 0   |  |  |

| -1*Vdc       | 1            | 1  | 0  | 0  | 0   | 0   | 0   | 0   |  |  |

| 0            | 0            | 0  | 0  | 0  | 0   | 0   | 0   | 0   |  |  |

#### Table. 3: Switches State in [13]

| Switch           | 0 | 1*V <sub>dc</sub> | 2*V <sub>dc</sub> | 3*V <sub>dc</sub> | 4*V <sub>dc</sub> | 5*V <sub>dc</sub> | 6*V <sub>dc</sub> | 7*V <sub>dc</sub> |

|------------------|---|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| $SW_1$           | 0 | 1                 | 1                 | 1                 | 1                 | 1                 | 1                 | 1                 |

| $SW_2$           | 1 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 |

| SW <sub>3</sub>  | 0 | 0                 | 1                 | 1                 | 1                 | 1                 | 1                 | 1                 |

| $SW_4$           | 1 | 1                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 |

| SW <sub>5</sub>  | 0 | 0                 | 0                 | 1                 | 1                 | 1                 | 1                 | 1                 |

| SW <sub>6</sub>  | 1 | 1                 | 1                 | 0                 | 0                 | 0                 | 0                 | 0                 |

| SW <sub>7</sub>  | 0 | 0                 | 0                 | 0                 | 1                 | 1                 | 1                 | 1                 |

| SW <sub>8</sub>  | 1 | 1                 | 1                 | 1                 | 0                 | 0                 | 0                 | 0                 |

| SW9              | 0 | 0                 | 0                 | 0                 | 0                 | 1                 | 1                 | 1                 |

| SW10             | 1 | 1                 | 1                 | 1                 | 1                 | 0                 | 0                 | 0                 |

| SW11             | 0 | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 | 1                 |

| SW <sub>12</sub> | 1 | 1                 | 1                 | 1                 | 1                 | 1                 | 0                 | 0                 |

| SW13             | 0 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 |

| SW14             | 1 | 1                 | 1                 | 1                 | 1                 | 1                 | 1                 | 0                 |

#### Table. 4: Switches State in Proposed MLI

| Tuble in Switches State in Hoposed MEL |   |                   |            |                   |            |            |                   |                   |  |  |

|----------------------------------------|---|-------------------|------------|-------------------|------------|------------|-------------------|-------------------|--|--|

| Switch                                 | 0 | 1*V <sub>dc</sub> | $2*V_{dc}$ | 3*V <sub>dc</sub> | $4*V_{dc}$ | $5*V_{dc}$ | 6*V <sub>dc</sub> | 7*V <sub>dc</sub> |  |  |

| $SW_1$                                 | 0 | 1                 | 0          | 0                 | 0          | 0          | 0                 | 0                 |  |  |

| $SW_2$                                 | 0 | 0                 | 1          | 0                 | 0          | 0          | 0                 | 0                 |  |  |

| SW <sub>3</sub>                        | 0 | 0                 | 0          | 1                 | 0          | 0          | 0                 | 0                 |  |  |

| $SW_4$                                 | 0 | 0                 | 0          | 0                 | 1          | 0          | 0                 | 0                 |  |  |

| SW <sub>5</sub>                        | 0 | 0                 | 0          | 0                 | 0          | 1          | 0                 | 0                 |  |  |

| SW <sub>6</sub>                        | 0 | 0                 | 0          | 0                 | 0          | 0          | 1                 | 0                 |  |  |

| $SW_7$                                 | 0 | 0                 | 0          | 0                 | 0          | 0          | 0                 | 1                 |  |  |

## 6.1 Proposed Topology Simulink Result

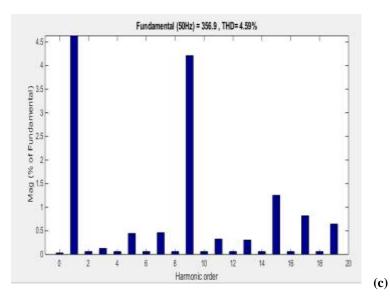

The results of proposed topology is obtained by GA-SHE algorithm in SIMULINK model. In the proposed topology the optimal firing angles are determined by MATLAB script file at 0.9 modulation index,  $\Theta 1 = 0.126$ ,  $\Theta 2 = 0.228$ ,  $\Theta 3 = 0.364$ ,  $\Theta 4 = 0.484$ ,  $\Theta 5 = 0.683$ ,  $\Theta 6 = 0.952$ ,  $\Theta 7 = 1.095$ . Fig.2(b) shows the waveform of single phase output voltage of the proposed topology. MATLAB Fast Fourier Transform(FFT) tool box is used for calculate the harmonic spectrum of proposed topology. Total har

monic distortion(THD) in proposed topology is shown in Fig.2(c). 4.59% Total harmonic distortion(THD) is found in proposed topology is found 4.59% which is very less as compared to other discussed topology.

Fig.2:. (a) Simulink Model of Proposed Topology (b) Single Phase Voltage of Proposed Topology (c) Phase Voltage THD in Proposed Topology

## 7. Comparision Between Different Topology

Table.5 gives the comparison between proposed topology and existing topologies on the behalf of THD, Number of switch, Methodology and switching frequency.

| Table 5: | Comparison | of Power | Quality | Improve |  |

|----------|------------|----------|---------|---------|--|

|----------|------------|----------|---------|---------|--|

| Ref. No  | Level | No. of | THD % | Lower           | Order Harm      | onics %         | Methodology     | Switching Fre- |

|----------|-------|--------|-------|-----------------|-----------------|-----------------|-----------------|----------------|

|          |       | Switch |       | 3 <sup>rd</sup> | 5 <sup>th</sup> | 7 <sup>th</sup> |                 | quency         |

| [21]     | 5     | 8      | 9.79  | -               | -               | -               | Soft Switching  | Low            |

| [16]     | 5     | 15     | 9.32  | 0.02            | 3.97            | 2.29            | Fundamental SHE | Low            |

| [8]      | 7     | 9      | 7.84  | -               | 0.15            | 0.27            | SHE             | High           |

| [8]      | 7     | 9      | 8.84  | -               | 5.20            | 0.77            | NLC             | High           |

| [22]     | 7     | 12     | 17.97 | -               | -               | -               | Soft Switching  | Low            |

| [11]     | 7     | 8      | <5    | -               | -               | -               | PWM             | High           |

| [25]     | 7     | 12     | 6.21  | -               | -               | -               | GA-MTHD         | High           |

| [20]     | 11    | 11     | 9.07  | -               | -               | -               | PWM             | High           |

| [23]     | 9     | 16     | 15.2  | 0.452           | 0.767           | 1.289           | TPWM            | High           |

| [23]     | 9     | 16     | 12.94 | 0.295           | 0.400           | 1.381           | SPWM            | High           |

| [12]     | 15    | 12     | 7.25  | -               | -               | -               | Fundamental SHE | Low            |

| [9]      | 15    | 12     | 7.6   | -               | -               | -               | Fundamental SHE | Low            |

| [20]     | 15    | 14     | 6.80  |                 |                 |                 | PWM             | High           |

| [24]     | 15    | 18     | 6.31  | -               | -               | -               | SPWM            | High           |

| Proposed | 15    | 11     | 4.59  | 0.13            | 0.45            | 0.46            | GA-SHE          | Low            |

## 8. Conclusion

This study proposes the MATLAB/SIMULINK design of a single phase fifteen level inverter with a novel topology. The proposed topology consists of less number of switch. For a 15-level MLI, proposed topology has only 11- switch compare to other topology discussed in [8], [11], [12], [9], [13], [19], [20] which used 13,16,12,12,16,16,14 switches.  $T_{on}$  (switch ON time) is less in this topology. Due to this, switching losses are reduced. Also the switching frequency is less thus the notching problem is overcome by this topology. SHE technique has been used for the removal of the lower order harmonics. This paper highlights that the THD in given topology is 4.85% ( $\leq$ 5%) according to the IEEE519 standard with the help of GA-SHE technique [18]. Hence GA-SHE technique gives better results. With the help of this inverter high quality power can be obtained.

Base on the observations, the proposed topology provides a lot of number of advantage such as: reduced THD, minimum computational complexity, simple design and less cost.

## Acknowledgement

The authors acknowledge and thank to the Department of Electrical Engineering of National Institute of Technical Teacher Training & Research(NITTTR), Chandigarh providing Lab facility for doing research work.

### Reference

- Shimi Sudha Letha, Tilak Thakur, Jagdish Kumar, "Harmonic elimination of a photo-voltaic based cascaded H-bridge multilevel inverter using PSO (Particle swarm optimization) for induction motor drive" Elsevier, Energy 107(2016),335-346

- [2] Ebrahim Babaei. "A Cascade Multilevel Converter Topology with Reduced Number of Switches", IEEE Trans. On Power electronics, Vol.23, No.6, November 2008

- [3] P Palanivel, SS Dash. Analysis of THD and output voltage performance for CMLI using carrier PWM. IET Power Electronics Vol. 4, Issue. 8, pp. 951-958

- [4] Balamurugan, C.R., S.P. Natrajan, and R.Basra, "Performance evaluation of unipolar PWM strategies for three phase five level diode clamped inverter",2012 International Conference on Emerging Trends in ScienceEngineeringAndTechnology (INCOSET),2012

- [5] Farouk Haddji Benali, Fouad AzzOuz, Ghalem Bachir, "The Operating improvement of the Supply Source and the Optimization of PWM Control", International Journal of Power Electronics and Drives systems (IJPEDS),2015

- [6] Shahrin Md Ayob. "NonSinusoidal PWM Method for Cascaded Multilevel Inverter" TELKOMNIKA. 2012; 10(4): 670-679.

[7] R Naveen Kumar. "Energy Management system for Hybrid RES with Hybrid Cascaded Multilevel inverter" International Journal of Electrical and Computer Engineering (IJECE). 2014; 4(1): 24~30.

- [8] Kamldeep, Jagdish Kumar, "Switch Reduction and Performance Analysis using Different Modulation Technique in Multilevel Inverter", ICPEICES-2016

- [9] M.Farhadi Kangarlu,E.Babaei, S.Laali, "Symmetric multilevel inverter with reduced components based on non-insulated dc voltage sources", IET Power Electronics 2012, Vol. 5, Issue.5, pp 571-581

- [10] BalamuruganM.,Gnana Prakash M.,and umashankar S., "A new seven level symmetric inverter with reduced number of switches and DC sources", 2014 International conference on Advances in Electrical Engineering(ICAEE),2014

- [11] Won-Kyun choi, "H-Bridge based multilevel inverter using PWm switching function", INTELEC 2009, 31<sup>st</sup>InternationalTelecomunicationsEnergyConference,10/2009

- [12] Javad Ebrahimi,Ebrahim Babaei, Govergpetian, "A New Topology of cascaded Multilavel Converters With Reduced Number of Components for High-Voltage Applications", IEEE TRANSACTION-SONPOWER ELECTRONICS, Vol.26.No.11,November 2011

- [13] Babaei, E.Hossemi.S.H, "New cascaded multilevel inverter toptolgy with minimum number of switches", Elsevier J.Energy Convers. Manage ,2009,50(H),PP 2761-2767

- [14] N.Farokhnia,S.H.Fathi,R.Salehi,G.B.Gharehpetian,M.Ehasani,"Imp roved selective harmonic elimination pulse –width modulation strategy in multilevel inverters", IET Power Electronics,2012 Vol.5,iss.9,pp.1904-1911

- [15] Albert Alexander, Manigandan Thathan, "Modeling and analysis of modular multilevel converter for solar photovoltaic applications to improve power quality", IET Renew, Power Gener, 2015 Vol.9

- [16] Sandeep Gupta,Mrs.shimi S.L, Dr.(Mrs.)Lini Mathew, Swati singh, "FPGA Implementation of 3-Ø Solar Powered 5-level Inverter", IJAESTR,Volume -2,Issue 04 December 2014

- [17] Faizal Arya Samman, Arie Azhari, "DC/AC Power Converter for Home Scale Electricity Systems Powered by Renewable Energy", IEEE, ICSGTEIS 2016

- [18] Bill Diong, Hossein Sepahvand, keith A, "Harmonic Distortion Optimization of Cascaded H-Bridge Inverters Considering Device Voltage Drops and Noninteger DC Voltage Ratios" IEEE Transactions on industrial electronics, Vol.60 No,8 August 2013

- [19] Babaei, E.Hosseni, S.H Gharehpetian, G.B. Tarafdar Haque,M.Sabahi, "reduction of dc voltage sources and switches in asymmetrical multilevel converter using a noval topology", Elsevier J.Elect, Power syst, Res, 2007, 77. (8), pp 1073-1085

- [20] Hinago, Y.Koizuami, "A single phase multilevel inverter using switched series/parallel dc voltage sources", IEEE Trans. Ind. Electron, 2010, 58(8), pp 2643-2650

- [21] T.Jagadeeswari, K.Srokrishnasatya, G.Rajkumar, U.S.S.Santhosh Kumar, "Impementiona of Cascaded H-bridge Five Level Inverter With Load", IRJET, 2016 Volume:03 Issue:09/sep-2016

- [22] G.Bhavanaryana ,Chavvakula Swamy,Ganta Mounika, Yedlapallinetaji,Sundru Sri durga, "Analysis and hardware implementation of five level cascaded H-bridge Inverter", IJERA,Vol.5 Issue10 (Part 2),October 2015,pp.43-53

- [23] Shuvankar Podder, Md. Multan Biswas, Md. Ziaur Rahman Khan, "A Modified PWm Technique to Improve Total Harmonic Distortion of Multilevel Invereter", International Conference on Electrical and Computer Engineering, IEEE, 20-22 December, 2016, Dhaka, Bangladesh

- [24] S.Harish, Dr.G.Raja Rao, S.N.S.Ravi Kiran, "Three Phase Multi Level Inverter for High Power Applictions", ", International Conference on Electrical, Electronics and Optimization Techniques(ICEEOT)-2016,IEEE

- [25] N.Farokhnia,S.H.Fathi,N.Yousefpoor,M.K.Bakhshizadeh, "Minimization of total harmonic distortion in a cascaded multilevel invereter by regulating voltage of DC", IET Power Electronics,2012 Vol.5,Iss.1,PP106-114