## Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Spring 2015

## Models predicting the performance of IC component or PCB channel during electromagnetic interference

Chunchun Sui

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons

**Department: Electrical and Computer Engineering**

#### **Recommended Citation**

Sui, Chunchun, "Models predicting the performance of IC component or PCB channel during electromagnetic interference" (2015). Doctoral Dissertations. 2395. https://scholarsmine.mst.edu/doctoral\_dissertations/2395

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# MODELS PREDICTING THE PERFORMANCE OF IC COMPONENT OR PCB CHANNEL DURING ELECTROMAGNETIC INTERFERENCE

by

#### **CHUNCHUN SUI**

#### A DISSERTATION

Presented to the Faculty of the Graduate School of the

#### MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

**COMPUTER ENGINEERING**

2015

Approved by

Dr. Daryl Beetner, Advisor Dr. David J. Pommerenke Dr. Jun Fan Dr. Yiyu Shi Dr. Dan Lin

© 2015 Chunchun Sui All Rights Reserved

#### PUBLICATION DISSERTATION OPTION

This dissertation has been prepared in the style utilized by the Journal of IEEE (Institute of Electrical and Electronics Engineers) Transactions on Electromagnetic Capability, listed as follows:

Paper 1, C. Sui, S. Bai, T. Zhu, C. Cheng, D. Beetner, "New Methods to Characterize Deterministic Jitter and Crosstalk Induced Jitter from Measurements", accepted by IEEE Trans. on EMC., 2015.

Paper 2, C. Sui, L. Ren, X. Gao, X. Li, J. Drewniak, D. Beetner, "Predicting Statistical Characteristics of Jitter Due to Simultaneous Switching Noise", submitted to IEEE Trans. on EMC., 2015.

Paper 3, C. Sui, X. Gao, D. J. Pommerenke, D. Beetner, "Modeling Delay Variations of DLL Due to Power and Ground Voltage Fluctuations", to be submitted to IEEE Trans. on EMC., 2015.

#### **ABSTRACT**

This dissertation is composed of three papers, which cover the prediction of the characteristics of jitter due to crosstalk and due to simultaneous switching noise, and covers susceptibility of delay locked loop (DLL) to electromagnetic interference.

In the first paper, an improved tail-fit de-convolution method is proposed for characterizing the impact of deterministic jitter in the presence of random jitter. A Wiener filter de-convolution method is also presented for extracting the characteristics of crosstalk induced jitter from measurements of total jitter made when the crosstalk sources were and were not present. The proposed techniques are shown to work well both in simulations and in measurements of a high-speed link.

In the second paper, methods are developed to predict the statistical distribution of timing jitter due to dynamic currents drawn by an integrated circuit (IC) and the resulting power supply noise on the PCB. Distribution of dynamic currents is found through vectorless methods. Results demonstrate the approach can rapidly determine the average and standard deviation of the power supply noise voltage and the peak jitter within 5~15% error, which is more than sufficient for predicting the performance impact on integrated circuits.

In the third paper, a model is developed to predict the susceptibility of a DLL to electromagnetic noise on the power supply. With the proposed analytical noise transfer function, peak to peak jitter and cycle to cycle jitter at the DLL output can be estimated, which can be use to predict when soft failures will occur and to better understand how to fix these failures. Simulation and measurement results demonstrate the accuracy of the DLL delay model.

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to Dr. Daryl Beetner, my advisor, for his guidance and instruction on my research work, financial support to my study and direction for this dissertation during my pursuit of the PhD's degree. I learned not only academic knowledge from Dr. Beetner, but also the rigorous attitude, good manners, and courage to face difficulties.

I would like to thank Dr. Jun Fan, Dr. David J. Pommerenke, Dr. Victor

Khilkevich and Dr. James Drewniak, for their teaching in my courses, discussions related to my research and helpful suggestions on my dissertation.

I would like to thank Dr. Minsu Choi, Dr. Yiyu Shi, Dr. Dan Lin, my previous advisor and committee members, for the discussion and helpful suggestions on my research.

I would also like to express my thanks to all the other faculty members and students in and out of the EMC lab for their team work and help in my coursework and research.

Finally, I would like to thank my family for their endless love and endless support in my life.

## TABLE OF CONTENTS

|                                                                                                    | Page |

|----------------------------------------------------------------------------------------------------|------|

| PUBLICATION DISSERTATION OPTION                                                                    | iii  |

| ABSTRACT                                                                                           | iv   |

| ACKNOWLEDGMENTS                                                                                    | v    |

| LIST OF ILLUSTRATIONS                                                                              | ix   |

| LIST OF TABLES.                                                                                    | xii  |

| SECTION                                                                                            |      |

| 1. INTRODUCTION                                                                                    | 1    |

| PAPER                                                                                              |      |

| I. New Methods to Characterize Deterministic Jitter and Crosstalk Induced Jitter from Measurements | 4    |

| Abstract                                                                                           | 4    |

| I. INTRODUCTION                                                                                    | 5    |

| II. CROSSTALK INDUCED JITTER MODEL                                                                 | 8    |

| A. Crosstalk Induced Jitter Model with Single Crosstalk Source                                     | 9    |

| B. Crosstalk Induced Jitter Model with Multiple Crosstalk Source                                   | 10   |

| III. DE-CONVOLUTION METHODS                                                                        | 12   |

| A. Tail-fit De-convolution Method.                                                                 | 13   |

| B. Inverse Filtering De-convolution Method.                                                        | 15   |

| C. De-convolution Using a Wiener Filter                                                            | 18   |

| IV. CROSSTALK INDUCED JITTER MODEL VALIDATION IN MEASUREMENTS                                      | 20   |

| A Characterization of the Crosstalk                                                                | 21   |

|         | B. Crosstalk Induced Jitter Histogram                                              | 21 |

|---------|------------------------------------------------------------------------------------|----|

| V. CO   | NCLUSION AND FUTURE WORK                                                           | 25 |

| REFE    | RENCES                                                                             | 26 |

|         | Statistical Characteristics of Jitter Due to Simultaneous Switching                | 30 |

| Abstra  | ct                                                                                 | 30 |

| I. INTI | RODUCTION                                                                          | 31 |

|         | EDICTION OF THE STATISTICAL CHARACTERISTICS OF CHING AND CHARGE CONSUMED PER CLOCK | 33 |

|         | A. Mean and Standard Deviation of Switching                                        | 34 |

|         | B. Mean and Standard Deviation of Charge Consumed per Clock.                       | 35 |

| III. VE | CTORLESS ESTIMATION OF POWER SUPPLY NOISE                                          | 36 |

|         | A. Power Delivery Network Impedance Model                                          | 36 |

|         | B. Switching Current Waveform.                                                     | 38 |

|         | C. Validation of Power Delivery Network Model                                      | 40 |

| IV.     | ESTIMATION OF PEAK JITTER                                                          | 43 |

|         | A. Delay Model.                                                                    | 43 |

|         | B. Prediction of Peak Jitter                                                       | 45 |

|         | C. Model Validation                                                                | 46 |

| V. STA  | ATISTICAL CHARACTERISTICS OF PEAK JITTER                                           | 49 |

| VI. DIS | SCUSSION AND CONCLUSIONS                                                           | 51 |

| REFE    | RENCES                                                                             | 53 |

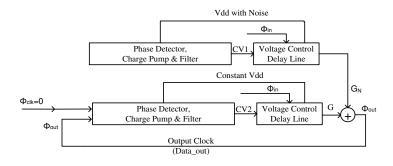

| _       | Delay Variations of DLL Due to Power and Ground Voltage                            | 56 |

| Ahstra  | of .                                                                               | 56 |

| I. INTRODUCTION                                      | 57 |

|------------------------------------------------------|----|

| II. DELAY LOCKED LOOP DESIGN                         | 61 |

| A. Phase Detector                                    | 64 |

| B. Charge Pump.                                      | 66 |

| C. Loop Filter.                                      | 66 |

| D. Voltage Control Delay Line                        | 67 |

| III. DELAY MODEL FOR DLLS CIRCUITS                   | 68 |

| A. Inverter Delay Model                              | 68 |

| B. Voltage Control Delay Line Delay Model            | 70 |

| C. Voltage Control Delay Line Long-term Jitter Model | 77 |

| D. DLL Close Loop Noise Transfer Function            | 77 |

| IV. CONCLUSION AND FUTURE WORK                       | 79 |

| REFERENCES                                           | 79 |

| SECTION                                              |    |

| 2. CONCLUSION                                        | 82 |

| VITA                                                 | 84 |

## LIST OF ILLUSTRATIONS

| Figure Pa                                                                                                                                                                                                | age |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| PAPER I                                                                                                                                                                                                  |     |

| 1. Common types of jitter                                                                                                                                                                                | 5   |

| 2. Coupled circuit schematic for crosstalk noise analysis                                                                                                                                                | 8   |

| 3. Aggressor, victim, and crosstalk induced noise waveforms                                                                                                                                              | 9   |

| 4. Relationship between crosstalk induced jitter and magnitude of crosstalk induced noise                                                                                                                | .10 |

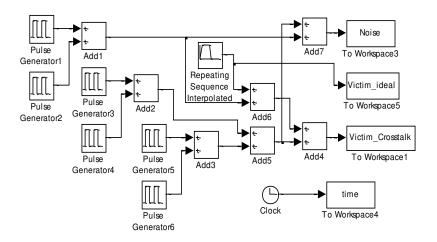

| 5. Simulink schematic to simulate crosstalk induced jitter from multiple aggressors                                                                                                                      | .11 |

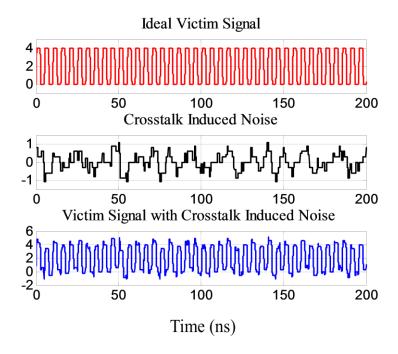

| 6. Impact of crosstalk noise from multiple aggressors on victim signal                                                                                                                                   | 11  |

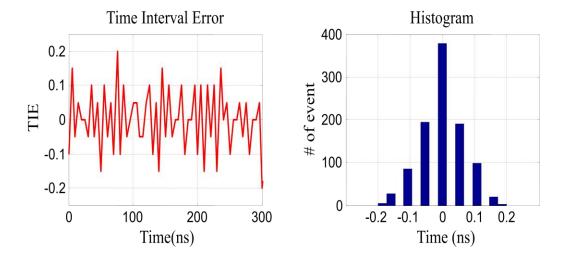

| 7. Time interval error and histogram of jitter with crosstalk                                                                                                                                            | .12 |

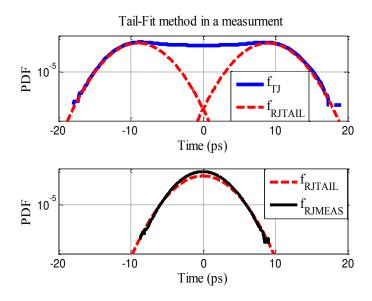

| 8. Probability density functions for measured total jitter (blue), measured random jitter (black), and estimate random jitter (red)                                                                      | .15 |

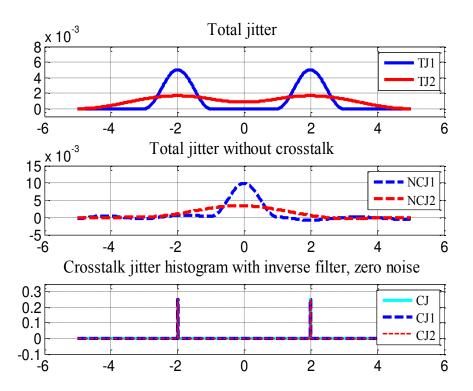

| 9. Probability density functions for total jitter found with different amounts of non-crosstalk induced jitter (top), total jitter without crosstalk, actual and estimated crosstalk induced jitter.     | .17 |

| 10. Estimates of crosstalk induced jitter made in the presence of noise. Top: estimated using (8). Bottom: estimated using (15)                                                                          | .18 |

| 11. Block diagram for the generation of a total jitter pdf measurement                                                                                                                                   | .18 |

| 12. Test PCB board.                                                                                                                                                                                      | .20 |

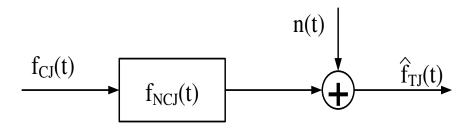

| 13. Waveforms on aggressor and victim and the relationship between the magnitude of the aggressor clock and the magnitude of the crosstalk on victim                                                     | .21 |

| 14. Crosstalk induced jitter measurement setup.                                                                                                                                                          | .22 |

| 15. Measured histogram for total jitter and estimated probability density function for crosstalk induced jitter using a Wiener filter (15) – middle – and using direct deconvolution as in (8) – bottom. | .23 |

| 16. Comparison of peak-to-peak crosstalk induced jitter in the model and in measurement.                                                                        | 24 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| PAPER II                                                                                                                                                        |    |

| 1. A generic logic gate with n-inputs and one output                                                                                                            | 34 |

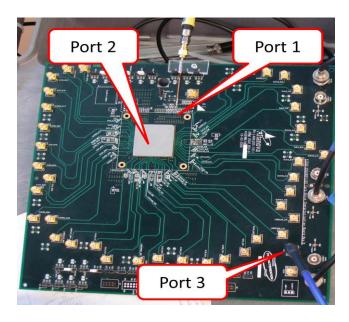

| 2. Test PCB picture                                                                                                                                             | 37 |

| 3. Model of the die-package-PCB power delivery network                                                                                                          | 38 |

| 4. Simulated power supply noise with different noise current waveforms which have the same average charge per clock                                             | 39 |

| 5. (a) Logic circuits in FPGA; (b) PDN noise measurement setup                                                                                                  | 40 |

| 6. Measured power supply noise on rising edges of the clock                                                                                                     | 40 |

| 7. Comparison of maximum voltage drop found in measurement and by multiplying simulated estimates of power with proportionality constant found from simulation. | 41 |

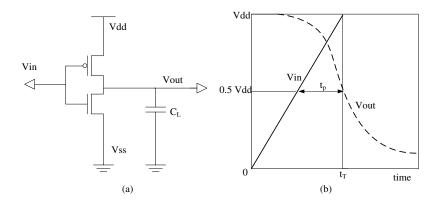

| 8. Inverter delay model, (a) Inverter schematic, (b) Time domain waveform                                                                                       | 43 |

| 9. Jitter diagram due to PDN noise                                                                                                                              | 45 |

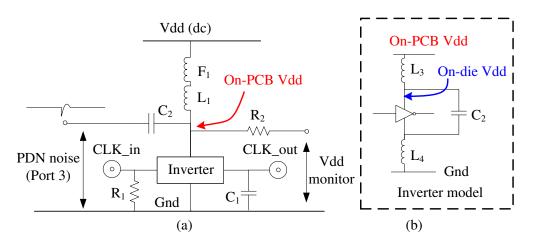

| 10. (a) Circuit diagram showing connection of inverter to FPGA PDN; (b) Model of inverter package and die power delivery network.                               | 47 |

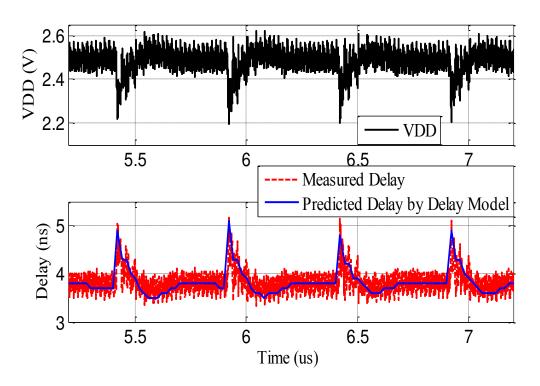

| 11. Comparison of measured and estimated inverter delay.                                                                                                        | 48 |

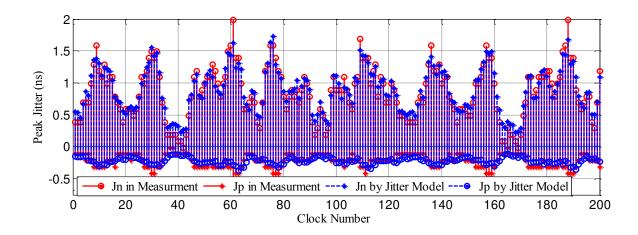

| 12. Comparison of the measured peak jitter and predicted peak jitter.                                                                                           | 49 |

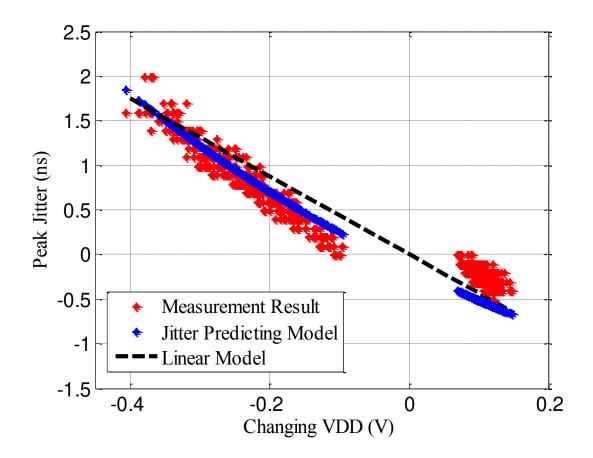

| 13. Relationship between power supply noise and peak jitter                                                                                                     | 50 |

| PAPER III                                                                                                                                                       |    |

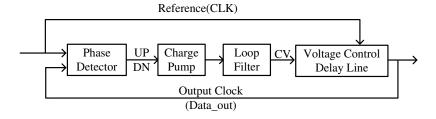

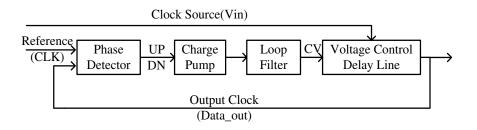

| 1. Type I DLLs structure                                                                                                                                        | 61 |

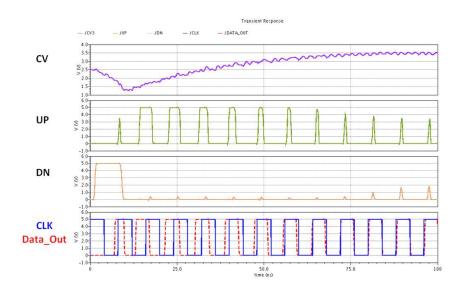

| 2. Function simulation results of Type I DLLs                                                                                                                   | 62 |

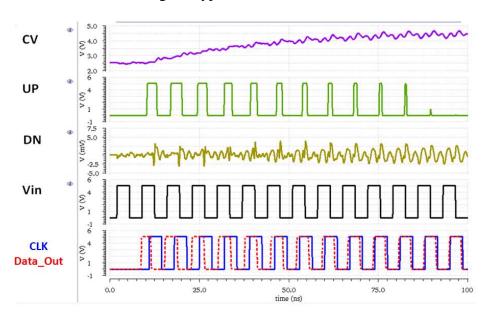

| 3. Type II DLLs structure.                                                                                                                                      | 63 |

| 4. Function simulation results of Type II DLLs.                                                                                                                 | 63 |

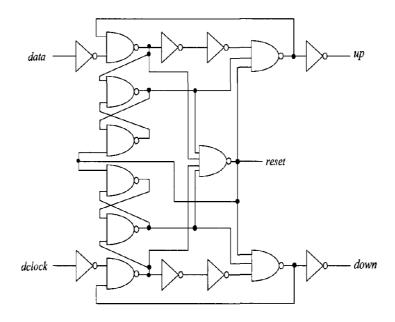

| 5. Circuit schematic of PFD.                                                                                                              | .64 |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

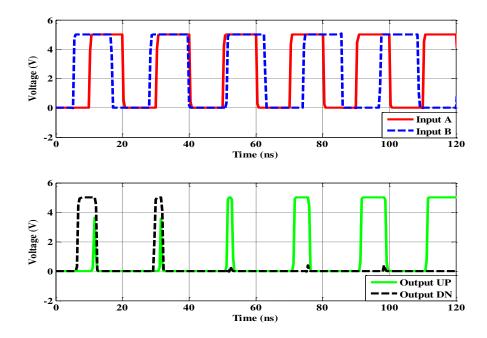

| 6. Functional simulation of PFD.                                                                                                          | .65 |

| 7. Circuit schematic of charge pump.                                                                                                      | 66  |

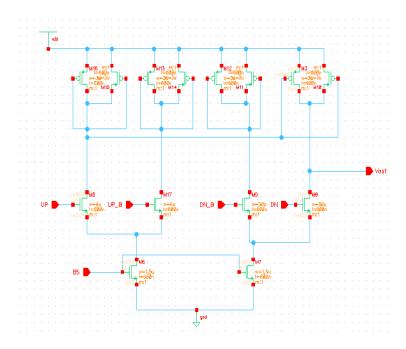

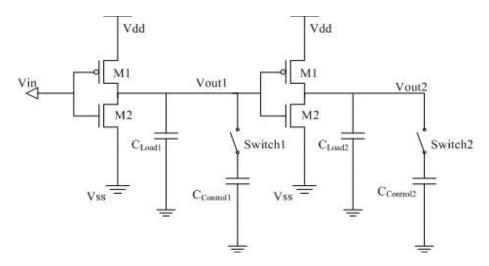

| 8. (a) Resistance delay cell in VCDL. (b) Capacitance delay cell in VCDL                                                                  | 67  |

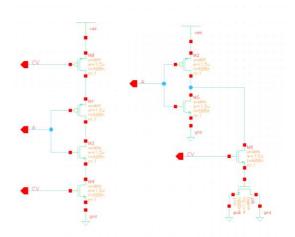

| 9. (a) Inverter schematic. (b) Inverter time domain waveform.                                                                             | .69 |

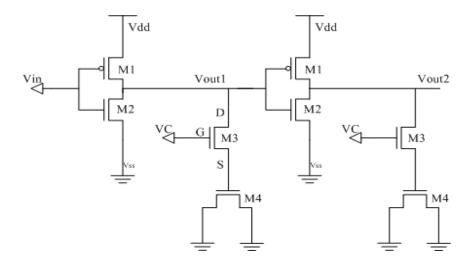

| 10. VCDL delay cell schematic (Two stage)                                                                                                 | 70  |

| 11. VCDL delay cell equivalent circuits schematic (Two stage)                                                                             | .71 |

| 12. VCDL delay cell Low-to-High transition simulation results (First stage)                                                               | 72  |

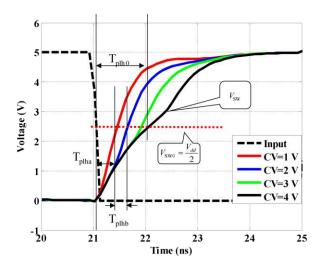

| 13. VCDL load capacitor extraction simulation results                                                                                     | .75 |

| 14. VCDL delay model verification results. A positive EFT noise is injected into Vdd pin and a sine wave is injected into control voltage |     |

| 15. DLL schematic with noise injection.                                                                                                   | 77  |

## LIST OF TABLES

| Table                                                 | Page |

|-------------------------------------------------------|------|

| PAPER II                                              |      |

| 1. STATISTICAL CHARACTERISTICS OF POWER SUPPLY NOISE  | 42   |

| 2. STATISTICAL CHARACTERISTICS OF PEAK-TO-PEAK JITTER | 51   |

#### 1. INTRODUCTION

For high speed circuits, a small amount of crosstalk can eat up the jitter budget and create timing issues. Precise crosstalk jitter characterization of signals at critical internal nodes provides valuable information for hardware fault diagnosis and next generation design. Understanding how crosstalk jitter contributions to overall jitter is challenging, because many types of jitter are combined together. One goal of this dissertation is to evaluate the crosstalk jitter contribution in a high speed I/O link. In this dissertation, crosstalk jitter and random jitter are modeled in simulation. A new tail-fit method is proposed to estimate the probability distribution for random jitter. This new tail fit method is applicable for the decomposition of the crosstalk jitter and random jitter. After prediction characteristics of the random jitter, de-convolution algorithm need to be implemented to separate the random jitter contribution and crosstalk jitter contribution in the total jitter histogram. The result of de-convolution is significantly impacted by noise. The noise is from the total jitter histogram measurement and also from the random jitter prediction. A de-convolution method is needs to be developed that works well in the presence of this noise.

Advanced high-speed I/O interconnects raise considerable signal integrity issues, e.g. switching power supply. An increase of switching power supply noise induces an increase in jitter which may cause severe degradation of the timing margin. Prediction of switching noise induced jitter can help to improve the system's timing margin and achieve lower error rate designs. One goal of this dissertation is to predict the statistical characteristics of jitter from an estimate of the statistical characteristics of switching noise. Current and future works on this topic include predicting the statistical distribution

of power ground noise due to simultaneous switching in FPGAs, predicting the statistical characteristics of jitter based on the predicted power ground noise, and validating the prediction method in simulation and measurement.

Generation and distribution of clock signals inside the IC is critical to the function of an IC. If the clock jitter is sufficiently large, it will cause timing and functional issue in the IC. Delay-locked loops (DLLs) are widely used in multiphase clock generators, clock de-skewing circuits and clock recovery circuits. In the previous researchers' work, there is no analytical equation described the DLL delay variation due to power/ground voltage fluctuations, like those occur during an Electrical Fast Transient (EFT), Electromagnetic Pulse (EMP), or High Power Microwave (HPM) event. One goal of this dissertation is to develop an analytical delay/jitter model of the DLL, which can describe the output phase variation due to power/ground voltage fluctuations.

This dissertation consists of three papers which focus on models predicting the performance of IC component or PCB channel during electromagnetic interference. Paper 1 proposes a method was proposed to estimate the pdf of random jitter from measurements of total jitter. This result can then be used to estimate the contribution of deterministic jitter (which includes crosstalk induced jitter). A method was also proposed for estimating crosstalk induced jitter from measurements of total jitter. Paper 2 proposes a methodology was proposed using vectorless methods to estimate the statistical characteristics of peak power supply noise and peak jitter due to power supply noise. Paper 3 proposes an analytical delay model of VCDL was proposed to predict propagation delay variations when the power supply is disturbed by an electromagnetic event.

The primary contributions of this dissertation include:

Improve the characterization of the crosstalk jitter contribution in the channel.

(paper 1).

Vectorless prediction of jitter distribution before circuits design. (paper 2).

Rapid evaluation of circuits performance based on the characteristics of jitter.

(paper 2).

Better understanding the delay variation of the DLL circuits. (paper 3).

Simple predictive model for DLL/PLL jitter. (paper 3).

#### **PAPER**

## I. New Methods to Characterize Deterministic Jitter and Crosstalk Induced Jitter from Measurements

Chunchun Sui, *Student Member, IEEE*, Siqi Bai, Ting Zhu, Christopher Cheng, Daryl G. Beetner, *Senior Member, IEEE*

Abstract—A small amount of jitter can quickly eat up timing budgets and create timing issues. Precise characterization of deterministic and crosstalk induced jitter can help isolate and solve issues within high-speed links. Characterizing deterministic and crosstalk induced jitter is challenging, however, because many types of jitter work together to create the overall jitter profile. Methods are presented in this paper to characterize the deterministic and crosstalk induced jitter from measurements of total jitter. An improved tail-fit de-convolution method is proposed for characterizing the impact of deterministic jitter in the presence of random jitter. The contribution of random jitter to total jitter is found first, and then that contribution is accounted for to find deterministic jitter. A Wiener filter de-convolution method is also presented for extracting the characteristics of crosstalk induced jitter from measurements of total jitter made when the crosstalk sources were and were not present. The Wiener filter allows for accurate deconvolution of the measured histograms for total jitter even in the presence of measurement noise. The proposed techniques are shown to work well both in simulations and in measurements of a high-speed link.

*Index Terms*— Crosstalk induced jitter, Jitter decomposition, De-convolution, Wiener filter

#### I. INTRODUCTION

Understanding the causes of jitter is critical to mitigating signal integrity issues in many high-speed digital circuits. Jitter can degrade the timing margin and cause functional issues in the circuit. Jitter is caused by a variety of mechanisms, such as channel loss and reflection, random noise, crosstalk, and other noise. Understanding the contribution of each of these sources of jitter is challenging, since multiple mechanisms work together to generate the total jitter. Precise characterization of the jitter can be a critical tool, however, for improving the circuit design. This paper focuses on the modeling and characterization of deterministic and crosstalk-induced jitter.

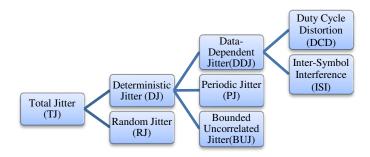

The sources of jitter are illustrated in Fig. 1 [1]. Total jitter includes deterministic jitter and random jitter. Random jitter is caused by random noise in the system and generally follows a Gaussian probability density function (pdf). The amplitude of random jitter is unbounded. Deterministic jitter is caused by imperfections in devices or by crosstalk or other circuit issues. It often has a non-Gaussian pdf. There are three types of deterministic jitter: data-dependent jitter, periodic jitter and bounded uncorrelated jitter.

Fig. 1. Common types of jitter

Data-dependent jitter is caused by duty cycle distortion and inter-symbol interference. Duty-cycle distortion results when driver characteristics, such as switching

threshold, bias, or supply voltage, cause the duration of a logical '1' to be different than the duration of a logical '0'. Duty-cycle distortion jitter can be modeled by the dual-Dirac delta function [2]. Inter-symbol interference is usually caused by bandwidth limitations of transmission lines, and depends on both data pattern and on the channel or medium system response function.

Periodic jitter, sometimes also called sinusoidal jitter, repeats at a predictable period and is typically caused by deterministic interference, such as from switching power supply noise or a strong local RF carrier, or by unstable PLL clock-recovery.

Bounded uncorrelated jitter is commonly caused by crosstalk from nearby data line. Bounded uncorrelated jitter is also called crosstalk induced jitter, which is the term that will be used in this paper. Unlike periodic jitter, crosstalk induced jitter is non-periodic. Crosstalk induced jitter is bounded by the finite coupling strength. It is uncorrelated, because there is no correlation to the channel's own data. Rather, it is correlated with the data on the adjacent traces. Crosstalk induced jitter is difficult to distinguish from random jitter, leading to increased estimates of both random jitter and total jitter [3], since the pdf for total jitter is a convolution of the pdf of each jitter component.

Several recent studies have focused on understanding, modeling, and measuring crosstalk induced jitter. A simple crosstalk induced jitter model was developed in [4] to calculate the time difference between the distortion-free and the distorted edge crossings of the victim signal. While this model was validated through H-spice simulation and measurement, the validation did not consider the effect of random and other types of jitter. Circuits to minimize the contribution of crosstalk induced jitter were proposed in [5] and [6]. The authors propose a model for the crosstalk induced jitter and then suggest

an equalizer circuit which compensates for the crosstalk, based on the coupling between the two circuits and the data on each. The authors of [7] present techniques to measure the amount of crosstalk induced jitter independent of other jitter sources. These techniques are based on an assumption that the crosstalk induced jitter dominates the total jitter in the system.

In the real word, crosstalk induced jitter is always associated with random and other types of jitter. Currently, there is no reliable method to decompose the total jitter into the different jitter components. Jitter decomposition methods are needed to verify the crosstalk induced jitter model. De-convolution can be used to decompose total jitter, but is very sensitive to noise [8]-[11], as will be illustrated in the following paper.

Methods are presented in the following paper to characterize deterministic and crosstalk induced jitter. The work is presented in five sections. A crosstalk induced jitter model is discussed in Section II which can be used to characterize the crosstalk induced jitter when the level of crosstalk is known. This model is validated through simulations and later through measurements. Methods for characterizing deterministic and crosstalk induced jitter are presented in Section III. A method is introduced in Section III.A for accurately characterizing random jitter in a measurement of total jitter. This characterization can then be used to determine the overall impact of deterministic jitter in the measurement. A method is presented in Section III.B for characterizing crosstalk induced jitter in measurements of total jitter made with and without the crosstalk sources present.

De-convolution of the pdf for crosstalk induced jitter is enabled using a Wiener filter. The models and methods are validated through measurements on a high-speed link

in Section IV. Results validate the crosstalk induced jitter model and demonstrate the effectiveness of the de-convolution method.

#### II. CROSSTALK INDUCED JITTER MODEL

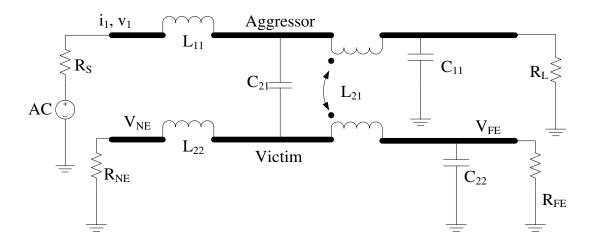

A simple crosstalk model is illustrated in Fig. 2. When the circuits are electrically long, coupling along transmission lines must be taken into account [12]. Analytic equations for crosstalk are given in [13] for 6 different transmission line terminations.

The maximum amplitude of crosstalk induced noise is given by [13], [4]

$$V_{p} = \frac{v_{1} \cdot l \cdot \sqrt{L_{11} \cdot C_{11}}}{2 \cdot t_{r}} \cdot \left(\frac{L_{21}}{L_{11}} - \frac{C_{21}}{C_{11}}\right)$$

(1)

where  $v_1$  is the voltage at the aggressor source,  $t_1$  is the length of the trace,  $t_r$  is the rise time of the aggressor signal, C11 and L11 are the per unit length self-capacitance and self-inductance of the victim, respectively, and C21 and L21 are the per unit length mutual capacitance- and mutual-inductance between the aggressor and victim. The maximum noise is important since it determines the peak-to-peak jitter.

Fig. 2. Coupled circuit schematic for crosstalk noise analysis

#### A. Crosstalk Induced Jitter Model with Single Crosstalk Source

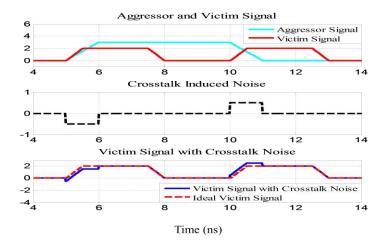

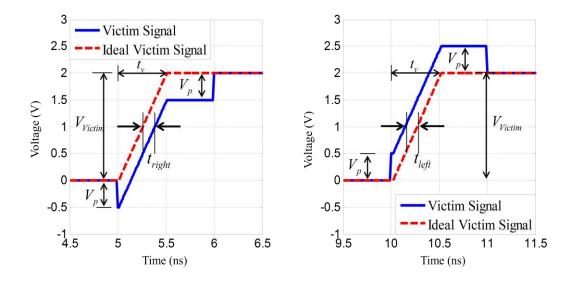

The jitter resulting from crosstalk can be determined from (1) and information about the victim signal. Figure 3 and Figure 4 shows an example of an aggressor and victim signal, and the resulting crosstalk induced jitter. Crosstalk causes the rising and falling edge of the victim signal to shift up or down in voltage, causing a corresponding shift in the time the edge occurs. The peak-to-peak crosstalk induced jitter is given by [4]:

$$t_{Xtalk} = t_{right} + t_{left} = \left| V_p \right| \cdot \frac{2t_v}{V_{victim}} \tag{2}$$

where  $t_{right}$  is the rightward shift in the edge of the victim signal,  $t_{left}$  is the leftward shift in the victim signal edge,  $V_{victim}$  is the full-range swing of the victim signal, and  $t_v$  is the rise time of the victim signal.

Fig. 3. Aggressor, victim, and crosstalk induced noise waveforms

Simulations were performed in Simulink to validate this model [14]. The time interval error and the crosstalk induced jitter histogram were calculated for a simple crosstalk problem with a single culprit, as in Fig. 2, and an aggressor and victim signal similar to Fig. 3, where the victim signal was twice the frequency of the aggressor. The

error between the simulation and the estimate from (2) was 4%, illustrating the accuracy of the model. This model can be used to estimate the peak-to-peak crosstalk induced jitter.

Fig. 4. Relationship between crosstalk induced jitter and magnitude of crosstalk induced noise

#### B. Crosstalk Induced Jitter Model with Multiple Crosstalk Sources

When multiple sources (traces) are present, the maximum crosstalk induced jitter can be approximated by assuming the crosstalk induced noise from each source is independent. For N aggressors, the peak-to-peak crosstalk induced jitter is given by [4]:

$$t_{Xtalk} = \left( \left| V_{p1} \right| + \left| V_{p2} \right| + \dots + \left| V_{pN} \right| \right) \cdot \frac{2t_{v}}{V_{victim}}$$

(3)

where  $V_{pN}$  is the amplitude of crosstalk noise caused by the  $N_{th}$  aggressor.

Additional simulations were performed in Simulink to validate this model. The simulation schematic shown in Fig. 5 was built to model crosstalk within a 4-trace system. The 3 aggressors and victim are all at unique frequencies (i.e. not at harmonics of

one another), so are not in phase. The induced noise was up to 0.5 V, with positive and negative pulses similar to Fig. 3. The simulated waveform is shown in Fig. 6.

Fig. 5. Simulink schematic to simulate crosstalk induced jitter from multiple aggressors

Fig. 6. Impact of crosstalk noise from multiple aggressors on victim signal

The time interval error and a histogram of crosstalk induced jitter were calculated from the simulated victim waveform, as shown in Fig. 7. An averaging function was used

to prevent "double counting" of edges (e.g. where a small amount of noise caused two transitions across Vdd/2 at an edge). Peak-to-peak crosstalk induced jitter was 0.4 ns in simulation compared to 0.35 ns predicted by the crosstalk induced jitter model. The use of averaging is expected to add some error to the simulation result.

Fig. 7. Time interval error and histogram of jitter with crosstalk

#### III. DE-CONVOLUTION METHODS

The pdfs for deterministic jitter, crosstalk induced jitter, or random jitter cannot be measured independently. They are naturally mixed together in the measurement of total jitter. The individual components of jitter can be estimated, however, through tail-fit or de-convolution methods.

The pdf for total jitter is determined by the convolution of the pdfs for each jitter component [1]. For example, the pdf for total jitter is given by a convolution of the pdf of deterministic jitter and random jitter:

$$f_{TJ}(\Delta t) = f_{DJ}(\Delta t) * f_{RJ}(\Delta t) = \int_{-\infty}^{\infty} f_{DJ}(\tau) * f_{RJ}(\Delta t - \tau) d\tau$$

(4)

where  $f_{TJ}$  is the pdf for total jitter, and  $f_{DJ}$  and  $f_{RJ}$  are the pdfs for deterministic and random jitter, respectively. The pdf for deterministic jitter is similarly given by a convolution of the probability density for crosstalk induced jitter, periodic jitter, and data-dependent jitter.

#### A. Tail-fit De-convolution Method

Tail-fit methods can be used to separate total jitter into its random and deterministic components [14]-[20]. The pdf for random jitter is estimated from measurements of total jitter. Assuming the random jitter has a Gaussian distribution; measurements of a point at the "peak" of the distribution and at one point along the tail of the total jitter can be used to estimate the mean and standard deviation of random jitter. The difficulty with the standard tail-fit approaches is that the peak if often difficult to define and points along the tail are noisy. The method only works well for histograms with an "ideal" shape which is constructed from a large number of measurements. Resulting estimates of random noise are often insufficient for use with processes with very low bit error rates.

A new tail-fit method was designed to provide a better estimate of random jitter [14]. As with previous techniques, it was assumed that the tail of the total jitter histogram results from random jitter which has a Gaussian distribution. Instead of picking only two points to estimate the characteristics of random jitter, the entire tail is fit to the tail of a Gaussian distribution plot. Once the tail is found, one can determine where the curve diverges from the Gaussian distribution. This point of divergence determines the bounds for the deterministic jitter (i.e. it is the point where deterministic jitter dominates

the overall histogram for jitter). These bounds approximate the peak-to-peak deterministic jitter.

The shape of a Guassian distribution is determined by its mean  $\mu$  and standard deviation  $\sigma$ . The parameters which best fit the tail can be found by sweeping the values of  $\mu$  and  $\sigma$  from their minimum to maximum values while comparing the resulting curves to the measured histogram. The quality of fit can be quantified by the parameter Fit\_threshold, defined as:

$$Fit _th = \frac{\sum_{i=0}^{i=n} \left( \left| \frac{A(i) - B(i)}{A(i)} \right| + \left| \frac{A(i) - B(i)}{B(i)} \right| \right)}{n}$$

(5)

where A and B represent points on the calculated Gaussian distribution curve and measured histogram tail, respectively, and n is the number of points evaluated along the tail. The tail fit quality is better for smaller values of Fit\_threshold.

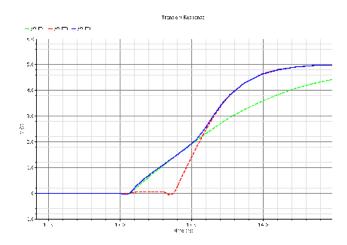

The proposed tail-fit method was validated through measurements. A J-BERT high-performance serial BERT was used to generate a jitter source. The total jitter was composed mostly of periodic and random jitter. Fig. 8 shows the measured total jitter (in blue), the measured random jitter (in black), and the predicted random jitter (in red) found using the proposed tail fit method. The random jitter was measured directly from the random "source" within the J-BERT instrument. The proposed method did a good job of estimating the pdf for random jitter. The peak-to-peak deterministic jitter, which is dominated by peak-to-peak period jitter in this case, is the time-difference between the peaks of the two Gaussian distributions in Fig. 8. Here, the periodic jitter should span from -9.2 to 9.5 ps, which closely matches the predicted span.

The tail-fit de-convolution method works well if the system contains very limited crosstalk induced jitter, so the impact of crosstalk induced jitter on the tail is small. If the crosstalk induced jitter is large, the tail of the total jitter pdf contains both crosstalk induced jitter and also random jitter. In this case, this technique cannot independently find deterministic jitter.

Fig. 8. Probability density functions for measured total jitter (blue), measured random jitter (black), and estimate random jitter (red)

### B. Inverse Filtering De-convolution Method

The pdf for deterministic jitter can be found through de-convolution of the pdfs of measured total jitter and random jitter. Working in the frequency domain, the characteristic function for deterministic jitter (i.e. Fourier transform of the pdf) is given by:

$$F_{DJ}(s) = \frac{F_{TJ}(s)}{F_{RJ}(s)}$$

(6)

where  $F_{DJ}(s)$ ,  $F_{TJ}(s)$ , and  $F_{RJ}(s)$  are the characteristic functions for the estimated deterministic jitter, measured total jitter, and estimated random jitter, respectively [21]. The pdf for jitter can be determined by inverse Fourier transform. For example,

$$f_{DJ}(\Delta t) = \mathfrak{I}^{-1}\left\{F_{DJ}(s)\right\} \tag{7}$$

where  $f_{\scriptscriptstyle DJ}(\Delta t)$  is the probability density and  $\mathfrak{T}^{\scriptscriptstyle -1}\{\!\mid\!\!\!]$  is the inverse Fourier transform.

While the de-convolution approach in (7) may work reasonably well for random jitter, which has a well defined pdf, it does not work as well for crosstalk induced jitter. One possibility for using de-convolution to determine crosstalk induced jitter is through measurements of total jitter with and without the crosstalk sources present, as shown in:

$$f_{CJ}(\Delta t) = \mathfrak{I}^{-1} \left\{ \frac{F_{TJ}(s)}{F_{NCJ}(s)} \right\}$$

(8)

where  $f_{CJ}$  is the predicted pdf for crosstalk induced jitter,  $F_{TJ}$  is the characteristic function for total jitter measured with crosstalk induced jitter, and  $F_{NCJ}$  is the characteristic function for total jitter without crosstalk induced jitter.  $F_{TJ}$  is found when all the crosstalk noise sources are turned on, and  $F_{NCJ}$  is found when the crosstalk noise sources are turned off.

This de-convolution method works well when the measurement noise is very small. Fig. 9 shows an example where (8) was used to estimate crosstalk induced jitter in a system with minimal noise. The top plot in Fig. 9 shows two histograms of total jitter that contain the same amount of crosstalk induced jitter, but different amounts of jitter from other sources. The second plot shows the total jitter found when the crosstalk sources are turned off. The bottom plot shows the estimated and actual crosstalk induced

jitter found using (8). The estimated and actual pdfs for crosstalk induced jitter match very well, but noise was nearly zero in this case.

Any practical measurement will contain non-negligible amounts of noise. This noise can corrupt the estimate of crosstalk induced jitter, because the inverse filter used for de-convolution is not stable [22]-[28]. This instability means that a small error in the measured total jitter can lead to large errors in the estimated crosstalk induced jitter. This effect is illustrated in Fig. 10. In the top plot, the pdf for crosstalk induced jitter was estimated using (8) when total jitter when the signal-to-noise ratio was 100. Even though the noise was only 1% of the measured pdf, the crosstalk induced jitter is unrecognizable. This problem can be solved in part by using a regularization technique, such as can be obtained using a Wiener filter.

Fig. 9. Probability density functions for total jitter found with different amounts of non-crosstalk induced jitter (top), total jitter without crosstalk, actual and estimated crosstalk induced jitter

### C. De-convolution Using a Wiener Filter

A Wiener filter is used to estimate the input to a linear system from a measurement of the output. The Wiener filter minimizes the mean square error in the estimate given information about the signal and noise power.

Fig. 10. Estimates of crosstalk induced jitter made in the presence of noise. Top: estimated using (8). Bottom: estimated using (15)

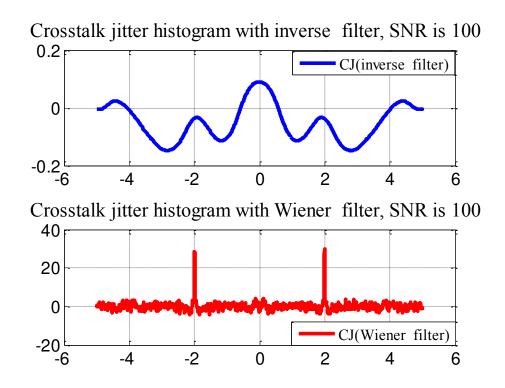

Fig. 11. Block diagram for the generation of a total jitter pdf measurement

The block diagram in Fig. 11 approximates the creation of the total jitter histogram in the presence of crosstalk and other source of jitter, as well as measurement noise, n(t). The measured histogram for the crosstalk induced jitter is given by:

$$\hat{f}_{TJ}(t) = f_{CJ}(t) * f_{NCJ}(t) + n(t)$$

(9)

where  $\hat{f}_{TJ}(t)$  is the measured estimate of the pdf of total jitter. This relationship can be represented in the frequency domain as:

$$\hat{F}_{TI}(\omega) = F_{CI}(\omega) \cdot F_{NCI}(\omega) + N(\omega) \tag{10}$$

The Wiener filter is used to eliminate the effect of measurement noise. For the system in Fig. 10, the Wiener filter is given by [18]:

$$W = \frac{F_{NCJ}^{*}(\omega) \cdot P_{TJ}}{\left|F_{NCJ}(\omega)\right|^{2} \cdot P_{TJ} + P_{N}}$$

(11)

where  $P_{TJ}$  is power spectra of the total jitter histogram and  $P_N$  is power spectra of measurement noise.  $F_{NCJ}^*(\omega)$  stands for the conjugate transpose of  $F_{NCJ}(\omega)$ . These power spectra are given by:

$$P_{TJ} = F_{TJ}^*(\omega) \cdot F_{TJ}(\omega) \tag{12}$$

$$P_{N} = N^{*}(\omega) \cdot N(\omega) \tag{13}$$

Re-arranging (13), the optimal Wiener filter is given by:

$$W = \frac{F_{NCJ}^{*}(\omega)}{\left|F_{NCJ}(\omega)\right|^{2} + \frac{1}{SNR}}$$

(14)

where *SNR* is the signal-to-noise ratio of the measured histogram for total jitter histogram, is equal to  $P_{TJ}$  /  $P_N$ .

Given that  $F_{NCJ}(\omega)$  must also be measured in the presence of noise, a reasonable estimate for the pdf of crosstalk induced jitter can be made using an estimate of the Wiener filter as:

$$\hat{F}_{CJ}(\omega) = W \cdot \hat{F}_{TJ}(\omega)$$

$$= \frac{\hat{F}_{NCJ}^{*}(\omega) \cdot \hat{F}_{TJ}(\omega)}{\left|\hat{F}_{NCJ}(\omega)\right|^{2} + \frac{1}{SNR}}$$

(15)

The SNR is a regularization parameter which can be estimated from knowledge of the measurement accuracy and from the measurement of total jitter. The utility of this approach is illustrated in Fig. 10, where the bottom plot shows the estimate of crosstalk induced jitter for the case in Fig. 9 with addd noise. The formulation in (15) was able to reconstruct the pdf of crosstalk induced jitter when (8) was not.

## IV. CROSSTALK INDUCED JITTER MODEL VALIDATION IN MEASUREMENTS

Measurements of jitter were made on a test PCB to demonstrate the accuracy of the jitter prediction models. The PCB is shown in the Fig. 12. This PCB consists of 1 oz copper layers (approximately 1.3 mil thick) and an FR402 dielectric that is 59 mils thick. The manufacturer's data sheet lists the FR402 dielectric constant as 4.25 at 1 GHz and a loss tangent of 0.015 at 1 GHz. Measurements were made separately on the top pair of traces (pair 1) and the bottom pair (pair 2). One trace acted as an aggressor and one as the victim.

Fig. 12. Test PCB board

#### A. Characterization of the Crosstalk

The level of crosstalk was needed to analytically form an estimate of the crosstalk induced jitter. The level of crosstalk was determined experimentally. A 70 MHz clock was applied to one trace, while the magnitude of crosstalk was measured on the second trace. The far ends of each trace were terminated with 50 ohms. The magnitude of the aggressor clock was varied from 0 V to 5 V while measuring the signal on the victim using an oscilloscope. The measured crosstalk as a function of the aggressor clock voltage is shown in Fig. 13. This relationship was used in the next experiments to define the magnitude of the crosstalk noise leading to jitter. If this crosstalk noise can be measured in a real system, it can be used directly with (2) or (3) to estimate peak-to-peak crosstalk induced jitter.

Fig. 13. Waveforms on aggressor and victim and the relationship between the magnitude of the aggressor clock and the magnitude of the crosstalk on victim

#### B. Crosstalk Induced Jitter Histogram

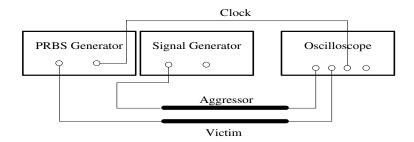

Histograms of the total jitter were measured with and without crosstalk to form a basis for estimating the crosstalk induced jitter. The measurement setup is shown in Fig.

14. The PRBS generator was connected to the victim trace and set to generate a 2 V, 400 MHz PRBS7 signal. Eye diagrams of the victim output signal were measured in the presence of crosstalk noise. The clock signal of the PRBS generator was used as the trigger signal to create the eye diagrams in the oscilloscope. A 70 MHz clock signal was applied to the aggressor trace while varying the magnitude of the clock signal. The magnitude of the resulting crosstalk was estimated from Fig. 13. While these signals are slow relative to signal speeds in modern systems, they are adequate for demonstrating the theory presented here.

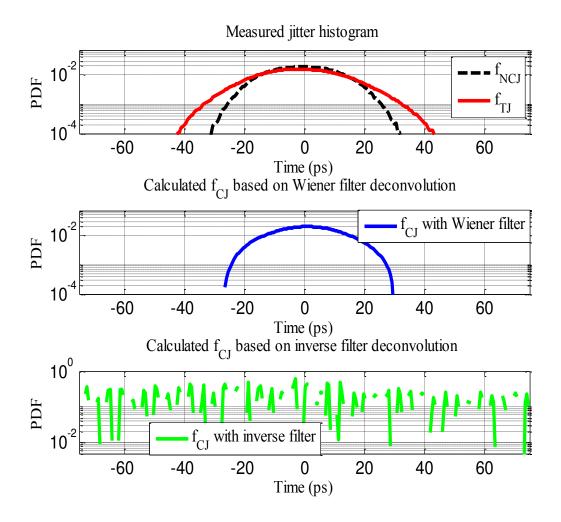

Figure 15 shows the measured histogram of the total jitter in the victim output when there was no crosstalk in red (i.e. when the magnitude of the aggressor signal was zero and the jitter was strictly due to random jitter and data-dependent jitter) and when a 5 V clock signal was applied to the aggressor in black (resulting in crosstalk induced jitter as well). The estimated pdf for the crosstalk induced jitter, found using a Wiener filter (15), is shown in blue. The value of the signal to noise ratio was determined experimentally. The accuracy of the crosstalk induced jitter estimate will be demonstrated in the next section. Without a Wiener filter, a reasonable estimate cannot be made, as demonstrated in the bottom plot in Fig. 15. The result found using (8) is clearly unrealistic.

Fig. 14. Crosstalk induced jitter measurement setup

Fig. 15. Measured histogram for total jitter and estimated probability density function for crosstalk induced jitter using a Wiener filter (15) – middle – and using direct deconvolution as in (8) – bottom

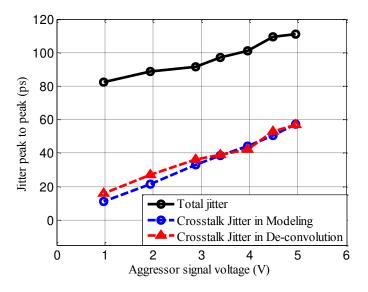

Use of the crosstalk induced jitter model and of the method for estimating the pdf of crosstalk induced jitter was validated by estimating the peak-to-peak crosstalk induced jitter in both cases. The peak-to-peak jitter can be found from (2) or (3) when the value of crosstalk is known, or can be found from the maximum and minimum values of crosstalk in the crosstalk induced jitter pdf found using (15) (e.g. in in Fig. 14, the peak-to-peak jitter is roughly 29 ps -(-28 ps) = 57 ps). To validate these approaches, the peak-to-peak jitter was found using (2) and using (15) while varying the magnitude of the aggressor

voltage. The magnitude of the crosstalk used in (2) was found from Fig. 13. The resulting estimates of peak-to-peak crosstalk induced jitter are shown in Fig. 16. When the aggressor signal was 5 V, the crosstalk induced jitter accounted for roughly 50% of the total jitter. When the aggressor signal was 1 V, it accounted for roughly 20% of the total jitter. The estimated peak-to-peak jitter found using both (2) and (15) were nearly the same at all aggressor signal levels, suggesting both are valid methods of estimating the impact of crosstalk induced jitter.

At low aggressor voltages, there is a small mismatch in the estimated crosstalk induced jitter (roughly 10%). This mismatch is likely caused by mis-estimation of the jitter by the Wiener filter. The Wiener filter is applied to noisy measurements. While the Wiener filter is an optimal estimator in the presence of uncorrelated noise, it cannot completely eliminate the impact of that noise. Some errors must remain. The error can be reduced by increasing the SNR and by using a larger number of sample points in the measurement (in this case, a larger number of bins in the measured histograms).

Fig. 16. Comparison of peak-to-peak crosstalk induced jitter in the model and in measurement

#### V. CONCLUSION AND FUTURE WORK

Crosstalk induced jitter can add significantly to the total jitter in high speed links, but determining the contribution of this jitter can be challenging. Methods were presented for determining the impact of crosstalk induced jitter analytically and from measurements. A method was proposed to estimate the pdf of random jitter from measurements of total jitter. This result can then be used to estimate the contribution of deterministic jitter (which includes crosstalk induced jitter). A method was also proposed for estimating crosstalk induced jitter from measurements of total jitter. The use of a Wiener filter allows the estimate to be made accurately even in the presence of measurement noise. The crosstalk induced jitter model and methods of estimating the contribution of crosstalk to jitter were validated both in simulation and in measurements with good results.

While a Wiener filter was shown to accurately estimate the pdf of crosstalk induced jitter, the technique may not work in all scenarios. One issue is that it may not be reasonable to make a measurement of jitter without crosstalk noise sources present. Such measurements are possible for special experimental measurements and test boards, but may not be reasonable for a fully working system. Another issue is that determining the level of SNR for use in (15) may not always be straightforward. Fortunately, even very rough estimates of SNR are typically sufficient for reasonable estimates of crosstalk induced jitter. For example in Fig. 16, nearly the same estimates of peak-to-peak crosstalk induced jitter are made using SNR estimates from 10-10000.

#### REFERENCES

- [1] M. P. Li, Jitter, Noise and Signal Integrity at High-Speed, Prentice Hall Pearson Education, Chapter 1, pp.14-16, 2007.

- [2] M. Marcu, S. Durbha, and S. Gupta, "Duty-cycle distortion and specifications for jitter test-signal generation." In Proc. IEEE Int. Symp. Electromagn. Compat, 2008.

- [3] P. Zivny, M. Agoston, K. Engenhardt, and J. Carlson, "Method of BERanalysis of high-speed serial data transmission in presence of jitter and noise." presented at the DesignCon 2007, Santa Clara, CA, Jan. 2007.

- [4] A. Kuo, R. Rosales, T. Farahmand, S. Tabatabaei, and A. Ivanov, "Crosstalk bounded uncorrelated jitter (BUJ) for high-speed interconnects." IEEE Trans. Instrumentation and Measurement, 54(5), 1800-1810, 2005.

- [5] J. Buckwalter, and A. Hajimiri, "Cancellation of crosstalk-induced jitter." Solid-State Circuits, IEEE Journal of 41.3: 621-632, 2006.

- [6] J. Buckwalter, and A. Hajimiri, "Crosstalk-induced jitter equalization." In Custom Integrated Circuits Conference IEEE, pp. 409-412, 2005.

- [7] M. Miller, and M. Schnecker, "Quantifying Crosstalk-induced jitter in multi-lane serial data system." DesignCon, 2009.

- [8] Q. Dou, J. A. Abraham, "Jitter decomposition in high-speed communication systems." In Test Symposium, 2008 13th European (pp. 157-162). IEEE. May, 2008.

- [9] S. Erb, W. Pribyl, "Comparison of jitter decomposition methods for BER analysis of high-speed serial links." In Design and Diagnostics of Electronic Circuits and Systems, 2010 IEEE 13th International Symposium on (pp. 370-375). IEEE. April, 2010.

- [10] C. d'Alessandro, V. Darsinos, B. Yegnanarayana, "Effectiveness of a periodic and aperiodic decomposition method for analysis of voice sources." Speech and Audio Processing, IEEE Transactions on, 6(1), 12-23. Chicago, 1998.

- [11] S. H. Hall, and H. L. Heck, Advanced Signal Integrity for High-Speed Digital Designs. John Wiley & Sons, 2011.

- [12] D. B. Jarvis, "The effects of interconnections on high-speed logic circuits." IEEE Trans. Electronic Computers, PP. 476-487, 1963.

- [13] J. A. DeFalco, "Reflection and crosstalk in logic circuit interconnections." Spectrum, IEEE, 7(7), 44-50, 1970.

- [14] C. Sui, T. Zhu, C. Cheng, and D. Beetner, "A NewTail-Fit Method Design for Jitter Decomposition" Proc. IEEE Int. Symp. Electromagn. Compat,2014.

- [15] N. Ou, T. Farahmand, A. Kuo, S. Tabatabaei, and A. Ivanov, "Jitter models for the design and test of Gbps-speed serial interconnects". Design and Test of Computers, IEEE, 21(4), 302-313, 2004.

- [16] B. Ham, "Fibre Channel-Methodologies for Jitter and Signal Quality Specification-MJSQ." INCITS, Washington, DC 11, 2004.

- [17] J. Patrin, and M. Li, "Comparison and correlation of signal integrity measurement techniques." DesignCon, 2002.

- [18] D. B. Jarvis, "The effects of interconnections on high-speed logic circuits," IEEE Trans. Electron. Comput., vol. EC-12, no. 10, pp. 476–487, Oct. 1963.

- [19] M. P. Li, J. Wilstrup, R. Jessen, and D. Petrich, "A new method for jitter decomposition through its distribution tail fitting." International Test Conference, 1999.

- [20] M. Shimanouchi, M. P. Li, and D. Chow, "New modeling methods for bounded gaussian jitter (BGJ)/noise (BGN) and their applications in jitter/noise estimation/testing." International Test Conference, 2009.

- [21] J. Tohka, and A. Reilhac, "A Monte Carlo study of deconvolution algorithms for partial volume correction in quantitative PET." In Nuclear Science Symposium Conference Record, IEEE, Vol. 6, pp. 3339-3345, 2006.

- [22] N. S. Nahman, and M. E. Guillaume, "Deconvolution of time domain waveforms in the presence of noise." NASA STI/Recon Technical Report N, 82, 27682, 1981.

- [23] R. Pintelon, P. Guillaume, Y. Rolain, J. Schoukens, and H. Van Hamme, "Parametric identification of transfer functions in the frequency domain-a survey." IEEE Transactions on Automatic Control, 39(11), 2245-2260,1994.

- [24] M. Van Noort, L. R. Van Der Voort, and M. G. Löfdahl, "Solar image restoration by use of multi-frame blind de-convolution with multiple objects and phase diversity." Solar Physics, 228(1-2), 191-215, 2005.

- [25] R. Keys, "Cubic convolution interpolation for digital image processing. Acoustics." Speech and Signal Processing, IEEE Transactions on, 29(6), 1153-1160, 1981.

- [26] J. I. Jackson, C. H. Meyer, D. G. Nishimura, and A. Macovski, "Selection of a convolution function for Fourier inversion using gridding computerised tomography application." Medical Imaging, IEEE Transactions on, 10(3), 473-478, 1991.

- [27] C. S. S. Burrus, and T. W. Parks, DFT/FFT and Convolution Algorithms: theory and Implementation. John Wiley & Sons, Inc, 1991.

- [28] D. Kundur, and D. Hatzinakos, "A novel blind deconvolution scheme for image restoration using recursive filtering." Signal Processing, IEEE Transactions on, 46(2), 375-390, 1998.

- [29] V. Madisetti, Digital Signal Processing Fundamentals. CRC press. Section 3, 25-3, 2010.

# II. Predicting Statistical Characteristics of Jitter Due to Simultaneous Switching Noise

Chunchun Sui, Student Member, IEEE, Liehui Ren, Student Member, IEEE, Xu Gao, Student Member, IEEE, Tun Li, Student Member, IEEE, James L. Drewniak, Fellow, IEEE, and Daryl G. Beetner, Senior Member, IEEE

**Abstract**—Switching of logic gates is often responsible for significant power supply noise. Predicting the jitter resulting from power supply noise can be critical to analyzing the proper operation of high-speed devices. The statistical characteristics of jitter, such as the mean and standard deviation of jitter, can be used to place a meaningful bound on the worst-case timing margin and to estimate the bit error rate. While the statistical characteristics of the noise can be found through simulations of many input logic vectors, such simulations require significant computational effort and require methods for choosing suitable data vectors. Vectorless methods allow rapid analysis of switching without using predefined input data and can be used to understand which portions of the logic circuit contribute most to noise. In this paper, methods using vectorless techniques are presented to predict the mean and standard deviation of power supply noise on the printed circuit board (PCB), and the mean and standard deviation of the resulting peak-to-peak jitter in a driver on the same PCB. Predictions and measurements while using a relatively slow clock demonstrate the approach can determine the average and standard deviation of the peak power supply noise on the PCB and of the peak-to-peak jitter within less than 21%, which is sufficient for predicting how a specific logic design might impact jitter, and for proposing means to minimize that impact.

*Index Terms*—Integrated circuit noise, statistical analysis, power distribution, jitter, field programmable logic array. analytical models, noise measurement

#### I. INTRODUCTION

As the speed of integrated circuits (ICs) grows and timing margins shrink, signal integrity issues become increasingly important to IC design [1]. Power supply noise can have a major impact on signal integrity, as an increase in noise can result in an increase of jitter [2]. Switching of logic gates at clock edges is responsible for significant power supply noise. An ability to predict bounds on the noise and the resulting jitter could allow the engineer to account for the jitter and could be used to develop improved designs with less jitter and lower bit error rate. Predicting the jitter caused by the noise from a particular logic design, however, is challenging. It requires a method to estimate the reasonable worst-case switching current consumed by the logic, a method of predicting the noise voltage resulting from the dynamic current consumed by the logic, and a method for predicting the jitter from the resulting noise. While vector-based methods are available for predicting the power supply noise caused by switching in the logic [3], vector-based methods require substantial computational effort, since many vectors must typically be simulated [4]. Finding appropriate vectors is challenging, particularly early in the design process. The goal of this paper is to develop a method using vectorless techniques to predict the statistical characteristics of timing jitter due to simultaneous switching noise. The statistical characteristics can be used to place bounds on the expected jitter and improve the logic design.

Prediction of simultaneous switching noise has been a topic of several recent studies. Power supply noise can be found through simulations [3] or from closed-form expressions [5]. Power supply noise from logic implemented in a field programmable gate array (FPGA) was predicted in [3]. Prediction was enabled with a high-frequency model of

the power delivery network (PDN) of the die, package, and printed circuit board (PCB). The PCB was modeled using a cavity structure. Switching current was determined through simulations in Quartus II of the power consumed by the logic when responding to specific input data. This paper demonstrated that power supply noise can be modeled precisely when given sufficient information about the PDN and the IC switching currents. Similar results were found in [6]. Input data vectors, however, are not always available and simulating many random vectors is computationally expensive.

Vectorless methods are computationally efficient and do not require known input data vectors [7]-[9], [15]. Vectorless methods are typically used to predict the power consumed by a logic design. As such, most vectorless methods only find the average switching rate and the average current. In [9], methods were presented for determining the variance of switching and of current from clock-to-clock. Calculating both the mean and variance allows precise statistical bounds to be place on peak current or power consumption. These techniques will be used here to statistically characterize the power supply noise.

The relationship between power supply noise and jitter is well known. A method to correlate simultaneous switching noise with signal jitter was presented in [10]. This work studied how the PDN impedance affects signal jitter and voltage margin. A similar study in [11] showed that output jitter peaks when the simultaneous switching noise is at the resonance frequency or at half the resonance frequency. Jitter in the clock and the I/O of an FPGA was studied in [12] and [13]. These papers investigated the relationship between jitter and the number of switching registers, the frequency of the switching circuit compared to the clock, the relative location of the switching circuit and the clock, and the

on-die decoupling capacitance. Since these papers are based on measured results, the methods cannot be used in the pre-design stage. A method for predicting clock jitter was introduced in [14] based on the amount of charge consumed per clock cycle by the logic design. This paper demonstrated that the charge consumed per clock could do a reasonably good job of predicting jitter, independent of the implemented logic pattern.

Methods are presented in the following paper to predict the statistical characteristics of jitter due to simultaneous switching noise in FPGAs when the clock speed is relatively low and the noise is on the PCB. Results demonstrate the accuracy of the approach and lay the foundations for future studies with faster clock speeds and with logic and I/O sharing the same power supply on-die. The work is presented in six sections. A vectorless method for predicting the statistical characteristics of the switching current is presented in Section II. These results are used in Section III to predict the statistical characteristics of power supply noise on a PCB. Methods to predict the statistical characteristics of peak jitter due to switching noise are presented in Section IV. Prediction of jitter characteristics is validated in Section V through simulations and measurements. Conclusions are summarized in Section VI.

# II. PREDICTION OF THE STATISTICAL CHARACTERISTICS OF SWITCHING AND CHARGE CONSUMED PER CLOCK

The statistical characteristics of switching in a logic circuit can be approximated directly from the logic when the statistical characteristics of the input data are known. The theory behind vectorless estimation is explained in detail in [9] and [15]. The results are summarized below.

## A. Mean and Standard Deviation of Switching

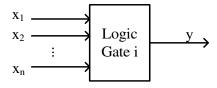

Consider the logic circuit in Fig. 1. The average number of switching events per clock at output y can be calculated as [15]:

$$\mu_{y} = \sum_{j=1}^{n} \mu_{y \leftarrow x_{j}} = \sum_{j=1}^{n} P\left(\frac{\partial y}{\partial x_{j}}\right) \mu_{x_{j}}$$

$$\tag{1}$$

where  $\mu_y$  is the average number of transitions per clock on y,  $\mu_{y \leftarrow x_j}$  is the average number of transitions on y caused by input  $x_i$ ,  $P\left(\frac{\partial y}{\partial x_j}\right)$  is the probability of a transition at y due to a transition at  $x_j$ ,  $\mu_{x_j}$  is the average number of transitions on input i, and n is the total number of inputs.

The average number of switching events per clock over many logic gates is given by a sum of the average number of switching events occurring at each gate:

$$\mu_{total} = \sum_{i=1}^{N} \mu_i \tag{2}$$

where  $\mu_{total}$  is the average number of switching events over all gates and  $\mu_i$  is the average number of switching events at the output of logical gate i.

Fig. 1. A generic logic gate with n-inputs and one output

The standard deviation in the number of switching events at output y among clock cycles is given by [9]

$$\sigma_{y}^{2} = \sum_{i=1}^{n} \left\{ P^{2} \left( \frac{\partial y}{\partial x_{i}} \right) \sigma_{x_{i}}^{2} + P \left( \frac{\partial y}{\partial x_{i}} \right) \left[ 1 - P \left( \frac{\partial y}{\partial x_{i}} \right) \right] \left( \mu_{x_{i}}^{2} + \sigma_{x_{i}}^{2} \right) \right\}$$

$$+ \sum_{i=1}^{n} \sum_{j=1 (i \neq j)}^{n} COV(x_{i}, x_{j}) P \left( \frac{\partial y}{\partial x_{i}} \right) P \left( \frac{\partial y}{\partial x_{j}} \right)$$

$$(3)$$

where  $\sigma_y$  and  $\sigma_{x_i}$  are the standard deviation in the number of switching events among clocks at the output y and input  $x_i$ , respectively.  $COV(x_i, x_j)$  is the covariance in the number of switching events per clock at gates  $x_i$  and  $x_i$ , and is given by

$$COV(x_i, x_j) = \sum_{i} \sum_{j} COV(A_i, B_j) \cdot P\left(\frac{\partial I}{\partial A_i}\right) \cdot P\left(\frac{\partial J}{\partial B_j}\right)$$

(4)

where  $A_i$  and  $B_j$  represent switching at the inputs to the logic gates with outputs  $x_i$  and  $x_j$ , respectively. The variance in the total number of switching events per clock over many logic gates can be found as [9]

$$\sigma_{total} = \sqrt{\sum_{i=1}^{n} \sigma_{i}^{2} + \sum_{i=1}^{n} \sum_{\substack{j=1\\ i \neq j}}^{n} COV(y_{i}, y_{j})}$$

(5)

where  $\sigma_i^2$  is the variance in the number of switching events at the output of gate i, and  $COV(y_i, y_j)$  is the covariance among switching at output nodes  $y_i$  and  $y_j$ .

## B. Mean and Standard Deviation of Charge Consumed per Clock

The statistical characteristics of the charge consumed per clock cycle can be determined from the charge consumed per switching event. The average charge per clock consumed across the logic circuit is given by

$$\mu_{\text{Charge}} = \sum_{i=1}^{N} \mu_i Q_i \tag{6}$$

where  $\mu_{\text{Charge}}$  is the average total charge consumed per clock, and  $Q_i$  is the charge consumed by each transition of output i. The standard deviation in the charge-per-clock is similarly given by [9]

$$\sigma_{\text{Charge}} \approx \sqrt{\sum_{i} Q_{i}^{2} \sigma_{i}^{2} + \sum_{i} \sum_{j} Q_{i} Q_{j} COV(y_{i}, y_{j})}$$

(7)

where  $\sigma_{\text{Charge}}$  is the standard deviation in the charge consumed per clock.

### III. VECTORLESS ESTIMATION OF POWER SUPPLY NOISE

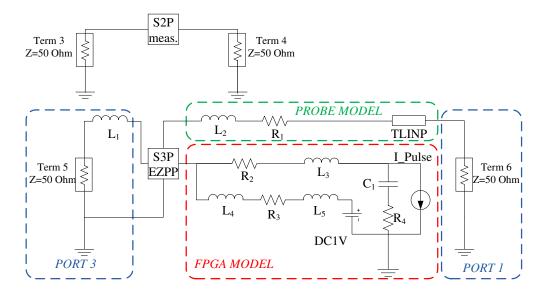

Previous work [3] has shown that the power supply noise can be accurately predicted when the input current waveform is known, but it not clear that knowledge strictly of the statistical characteristics of charge consumption is sufficient. Statistical estimates of charge consumption only give equivalent information about the average current drawn over each clock cycle, not the current waveform. Before estimating the statistical characteristics of power supply noise, a study was performed to demonstrate that knowledge of the charge consumed per clock was sufficient to estimate power supply noise. Sufficiency was demonstrated by simulating power supply noise for a variety of input current waveforms which each consume the same total charge.

## A. Power Delivery Network Impedance Model

To determine the impact of the switching current waveform on power supply noise requires an accurate model of the power delivery network impedance. The relationship between the switching current, I(f), and power supply noise voltage, V(f), is given by [3],[20]:

$$V(f) = Z(f) \cdot I(f) \tag{8}$$

where Z(f) is the transfer impedance of the power delivery network in the frequency domain, between the noise source (i.e. where I(f) is located) to the noise location (i.e. where V(f) is measured).

The FPGA and PCB studied here are shown in Fig. 2. The FPGA power supply is connected to the PCB at Port 2. All switching currents are generated at this port. Ports 1 and 3 are at other locations on the PCB, between the power and return planes.

Fig. 2. Test PCB picture

A model of the impedance of the complete PDN, including the FPGA and PCB, was developed in [3]. A simplified model is shown in Fig. 3. The impedance of the PCB power and return plane are modeled using a cavity model, calculated using EZPP [21]. EZPP provides an S-parameter block of the power plane impedance. Measurements of the transfer impedance between ports in [3] showed that the simulated and measured impedances matched within a few dB from 100 kHz to 2 GHz. When current waveforms resulting from switching were predicted in [3] using Quartus, this model was shown to provide an accurate estimate of the PCB power supply noise.

Fig. 3. Model of the die-package-PCB power delivery network

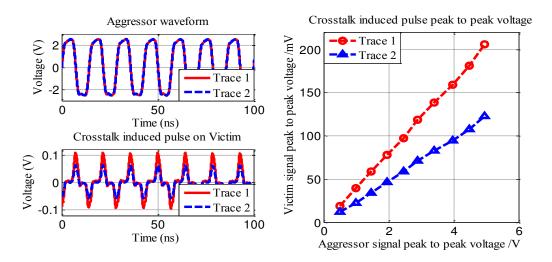

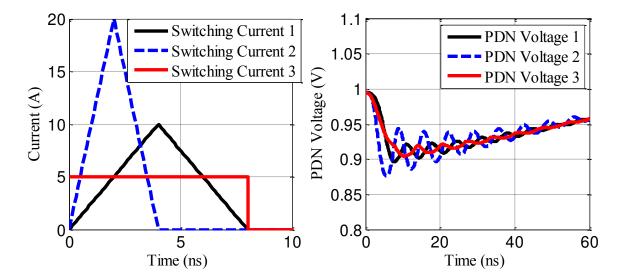

# B. Switching Current Waveform

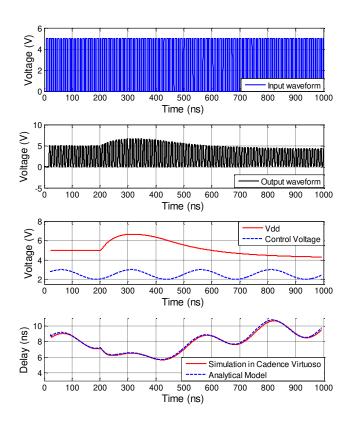

To demonstrate whether charge consumed per clock alone could be used to predict power supply noise, or if a switching current waveform was required, simulations of the power supply noise were made using multiple current waveforms consuming the same charge. Figure 4a shows three switching current waveforms in the FPGA, made assuming that switching occurs over a window of less than 8 ns (that smallest allowed clock period for the designs studied later). Figure 4b shows the power supply voltage at port 3 on the PCB during each noise waveform. The results demonstrate that each waveform, consuming the same charge per clock, generates roughly the same peak PDN noise (within about 10%). The peak noise voltage is consistent with charge until the pulse width is more than about 20 ns [22]. In the real design, all switching would end much earlier since the clock period can be as small as 8 ns.

Fig. 4. Simulated power supply noise with different noise current waveforms which have the same average charge per clock

Simulations in Quartus provide information about power rather than current or charge consumption. The charge consumed per clock is roughly proportional to the average power over the clock when the magnitude of the power supply voltage is relatively small. That is,

$$P_{AVG,i} \approx V_{DD} \cdot I_{AVG,i} = V_{DD} \cdot \frac{Q_i}{T}$$

(9)

where  $P_{AVG,i}$  and  $I_{AVG,i}$  are the average power and current consumed over clock cycle i,  $Q_i$  is the consumed charge, and T is the clock period. The voltage drop in Fig. 4b is directly proportional to the total charge consumed, so

$$V_{DROP} \approx K \cdot P_{AVG} \,. \tag{10}$$

$$K \approx \frac{V_{DROP}}{V_{DD} \cdot Q_i} \cdot T \tag{11}$$

From Fig. 4, the value of K was found to be 1.22 mV/mW. This value of K will be used in the next section to estimate the voltage drop on the PCB resulting from a power per clock estimate from Quartus II. A comparison between the measured and predicted voltage

drops will be made to validate the model of the switching current and the power delivery network. Once validated, the value of K will be used with vectorless predictions of charge to characterize the statistical nature of the PCB noise.

## C. Validation of Power Delivery Network Model

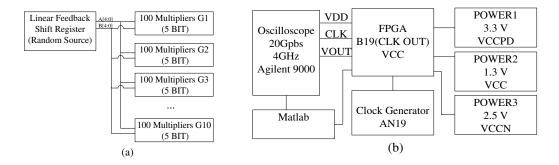

To validate the prediction of noise characteristics, 1000 5-bit multipliers were implemented in the Altera FPGA pictured in Fig. 2. The multipliers were driven by a 7-bit pseudorandom bit-sequence (PRBS7) generated by a linear feedback shift register. Fig. 5a shows the connection of the multipliers and the linear feedback registers. The resulting power supply noise at port 3 on the PCB was measured using the setup shown in Fig. 5b.

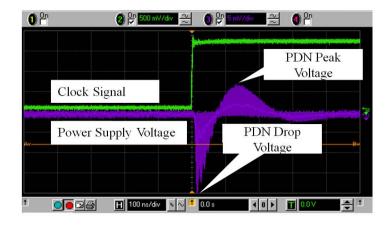

Fig. 5. (a) Logic circuits in FPGA; (b) PDN noise measurement setup

Fig. 6. Measured power supply noise on rising edges of the clock. The plot shows the measurement over many clocks, effectively showing the envelope of the noise

The average power consumed for each clock cycle was also predicted through simulations with Quartus II Power Play. The switching power for each clock cycle was determined by the power consumed within 500 ns of each rising edge of the clock. The voltage drop on the PDN was estimated by multiplying the simulated switching power by K, as in (10).

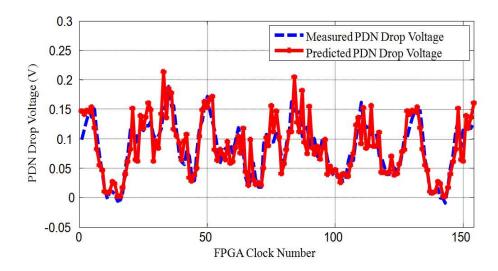

An example of the measured noise is shown in Fig. 6. The power supply voltage first drops, when the gates switch, then rises due to ringing. The noise was intentionally made large by removing most decoupling capacitors from the PCB. A comparison of the measured and predicted values of the maximum voltage drop is shown in Fig. 7 as a function of the clock number. The drop changes as the inputs (and the resulting noise) will vary from clock to clock. The measured and estimated drops match within an RMS error of 26 mV (26%), validating the simulation model and the method of estimating noise.

Fig. 7. Comparison of maximum voltage drop found in measurement and by multiplying simulated estimates of power with proportionality constant found from simulation

Since the maximum voltage drop is proportional to the consumed charge, the mean and standard deviation of the noise will be proportional to the mean and standard deviation of the consumed charge. That is,

$$\mu_{noise} \approx \frac{K \cdot V_{DD}}{T} \cdot \mu_{\text{Charge}}$$

(12)

$$\sigma_{noise} \approx \frac{K \cdot V_{DD}}{T} \cdot \sigma_{\text{Charge}}$$

(13)

A comparison of the statistical characteristics for the measured power supply noise, the noise predicted from the simulated power, and the noise predicted using (12) and (13) is shown in Table. 1. Comparisons between measured mean and standard deviation of the maximum voltage drop per clock and results predicted from simulated power are close, as expected. Results predicted using vectorless methods were within 2% of the experimental values for the mean and 8% for the standard deviation. Errors in the standard deviation may have been larger because of random noise in the measurement.

TABLE I

STATISTICAL CHARACTERISTICS OF POWER SUPPLY NOISE

| Maximum Noise<br>Voltage Drop on PCB<br>PDN | Mean (ns) | Standard Deviation (ns) | Calculation time |

|---------------------------------------------|-----------|-------------------------|------------------|

| Quartus simulation                          | 86.9      | 47.9                    | 12.7 hours       |

| Measurement                                 | 86.8      | 43.1                    | 1~3 hours        |

| Vectorless prediction                       | 93.6      | 44.0                    | 5 minutes        |

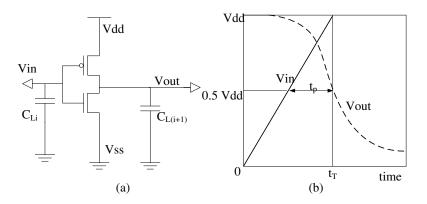

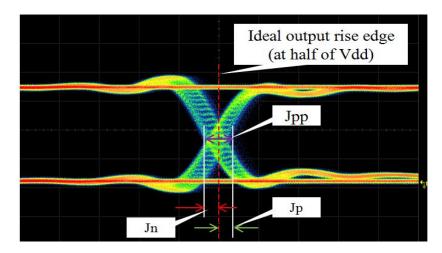

## IV. ESTIMATION OF PEAK JITTER