### UNIVERSIDAD DE LA REPÚBLICA

Facultad de Ingeniería Instituto de Ingeniería Eléctrica

> Tesis para optar por el Título de Magister en Ingeniería Eléctrica

## Modular Architecture For Ultra Low Power Switched-Capacitor DC-DC Converters

Author: Ing.Pablo Castro Lisboa pcastro@fing.edu.uy

Academic Director: Prof.Fernando Silveira

**Thesis Advisors:** Prof.Fernando Silveira Prof.Adj.Gabriel Eirea

Montevideo, Uruguay

22 de febrero de 2012

## UNIVERSIDAD DE LA REPÚBLICA ORIENTAL DEL URUGUAY FACULTAD DE INGENIERÍA INSTITUTO DE INGENIERÍA ELÉCTRICA

Los abajo firmantes certificamos que hemos leído el presente trabajo titulado "Modular Architecture For Ultra Low Power Switched Capacitor DC-DC Converters" hecho por Pablo Castro y encontramos que el mismo satisface los requerimientos curriculares que la Facultad de Ingeniería exige para la tesis del título de Magister en Ingeniería Eléctrica.

Fecha: 9 de Diciembre de 2011

Director académico y Co-tutor de tesis:

Prof.Fernando Silveira:

Co-Tutor de Tesis:

Prof.Adj.Gabriel Eirea: \_\_\_\_\_

Tribunal Examinador:

Prof.José Luis Huertas:\_\_\_\_\_

Prof.Cesar Briozzo:

Prof.Agr.Conrado Rossi:\_\_\_\_\_

A mis padres.... Que me dieron lo más importante.

### **Reconocimientos**

A mis tutores Fernando Silveira y Gabriel Eirea por haberme dado la oportunidad de llevar adelante este trabajo, y por su permanente disponibilidad para guiarme lo cual valoro mucho.

A la ANII (Agencia Nacional de Investigación e Innovación) por la beca otorgada.

Al cluster de Facultad de Ingeniería de la UDELAR por haberme permitido hacer la exploración del espacio de diseño.

## Contents

| 1. | Intr | oduction                                          | 1 |

|----|------|---------------------------------------------------|---|

|    | 1.1. | Motivation                                        | 1 |

|    | 1.2. |                                                   | 4 |

|    |      | •                                                 | 6 |

|    |      | •                                                 | 7 |

|    |      |                                                   | 8 |

| 2. | Prop | oosed Architecture 1                              | 1 |

|    | 2.1. | Capacitors Implementation                         | 3 |

|    | 2.2. |                                                   | 4 |

|    | 2.3. |                                                   | 8 |

|    | 2.4. |                                                   | 2 |

|    | 2.5. |                                                   | 7 |

|    | 2.6. |                                                   | 9 |

|    | 2.7. |                                                   | 0 |

| 3. | Nun  | nerical Model 3                                   | 3 |

|    | 3.1. | General Considerations for the Model              | 3 |

|    |      |                                                   | 4 |

|    |      |                                                   | 4 |

|    |      |                                                   | 4 |

|    | 3.2. |                                                   | 7 |

|    | 3.3. |                                                   | 8 |

|    | 3.4. |                                                   | 0 |

|    |      |                                                   | 0 |

|    |      |                                                   | 0 |

|    |      | 3.4.3. Conduction Losses                          | 1 |

|    |      | 3.4.4. Digital and Analog Control Circuits Losses | 1 |

|    | 3.5. | How the Model Works                               | 1 |

|    |      |                                                   | 2 |

|    |      |                                                   | 2 |

|    |      |                                                   | 3 |

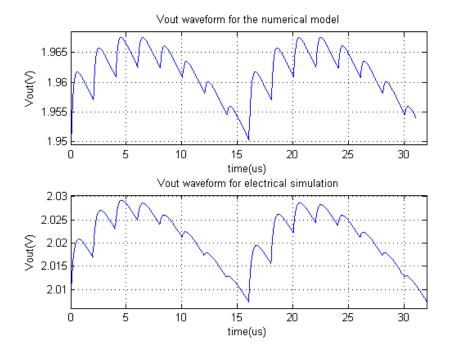

|    | 3.6. Comparison with Electrical Simulations                                                             | 44                    |

|----|---------------------------------------------------------------------------------------------------------|-----------------------|

|    | 3.7. Design Space Exploration for Optimum $N$ Selection $\ldots \ldots \ldots$                          | 45                    |

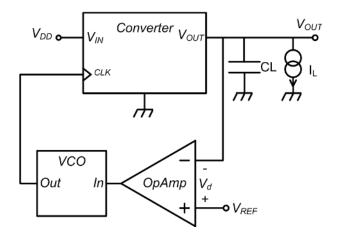

| 4. | Proposed Control Scheme         4.1. Feedback Loop Analysis         4.2. V <sub>REF</sub> Optimum Value | <b>47</b><br>48<br>50 |

|    | 4.3. About the Feedback Loop                                                                            | 50                    |

| 5. | Results and Comparison with Other Works         5.1. Results         5.2. Comparison with Other Works   | <b>53</b><br>53       |

|    | 5.2. Comparison with Other Works                                                                        | 55                    |

| 6. | Conclusions and Future Work         6.1. Future Work                                                    | <b>63</b><br>64       |

| A. | Numerical Model Data Construction                                                                       | 67                    |

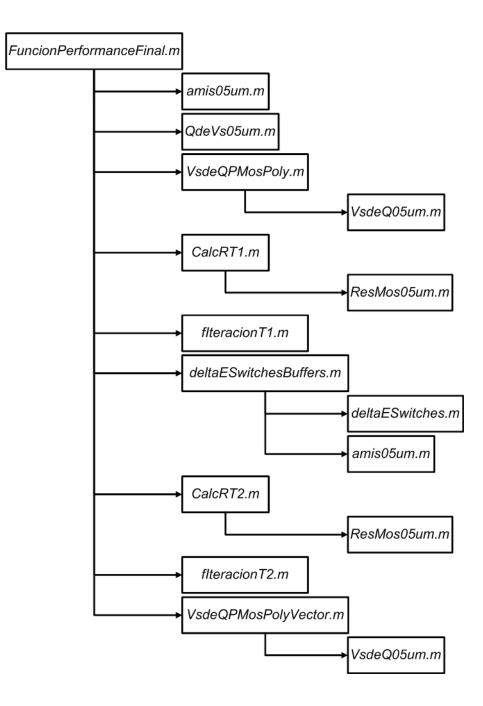

|    | A.1. File Tree                                                                                          | 67                    |

|    | A.1.1. FunctionPerformanceFinal.m.                                                                      | 67                    |

|    | A.1.2. amis05um.m                                                                                       | 67                    |

|    | A.1.3. QdeVs05um.m                                                                                      | 69                    |

|    | A.1.4. VsdeQPMosPoly.m                                                                                  | 69                    |

|    | A.1.5. VsdeQ05um.m                                                                                      | 70                    |

|    | A.1.6. CalcRT1.m                                                                                        | 70                    |

|    | A.1.7. ResMos05um.m                                                                                     | 70                    |

|    | A.1.8. flteracionT1.m                                                                                   | 70                    |

|    | A.1.9. deltaESwitchesBuffers.m                                                                          | 71                    |

|    | A.1.10. deltaESwitches.m                                                                                | 71                    |

|    | A.1.11. CalcRT2.m                                                                                       | 71                    |

|    | A.1.12. flteracionT2.m                                                                                  | 71                    |

|    | A.1.13. VsdeQPMosPolyVector.m                                                                           | 72                    |

| B. | Energy Transference Between Capacitors                                                                  | 73                    |

## List of Tables

|              | Comparison of the two implementations of the rotation                                            | 29<br>30             |

|--------------|--------------------------------------------------------------------------------------------------|----------------------|

| 3.1.         | Comparison between electrical and numerical simulations                                          | 45                   |

| 5.2.<br>5.3. | Designed converter parameters. Technology used $On - Semi 0.5 \mu m$ Comparison with other works | 54<br>60<br>60<br>61 |

## List of Figures

| 1.1. | DC/DC converter implemented with an emitter follower              | . 2  |

|------|-------------------------------------------------------------------|------|

| 1.2. | Capacitor to capacitor charge transfer.                           | . 3  |

| 1.3. | Two phases divider-by-two Switched Capacitor Converter basic exa  | m-   |

|      | ple                                                               | . 5  |

| 1.4. | Bottom and top parasitic capacitances in a poly-poly capacitor.   | . 7  |

| 1.5. | PMOS capacitor implementation and parasitic capacitances.         | . 7  |

| 1.6. | Switched Capacitor Converter equivalent circuit.                  | . 9  |

| 2.1. | Example of converter with $n = 5$ and conversion ratio of $3/5$   | . 12 |

| 2.2. | Basic Capacitor Cell                                              | . 14 |

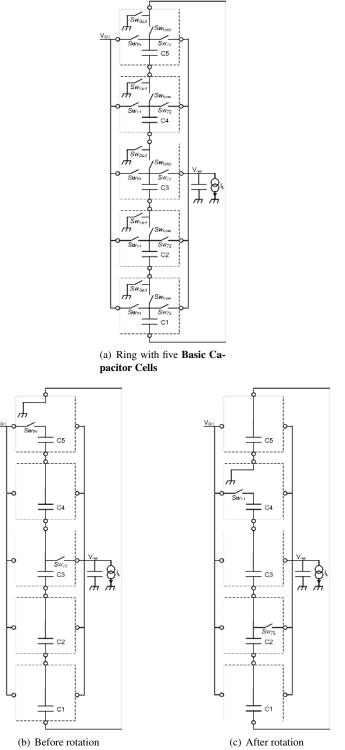

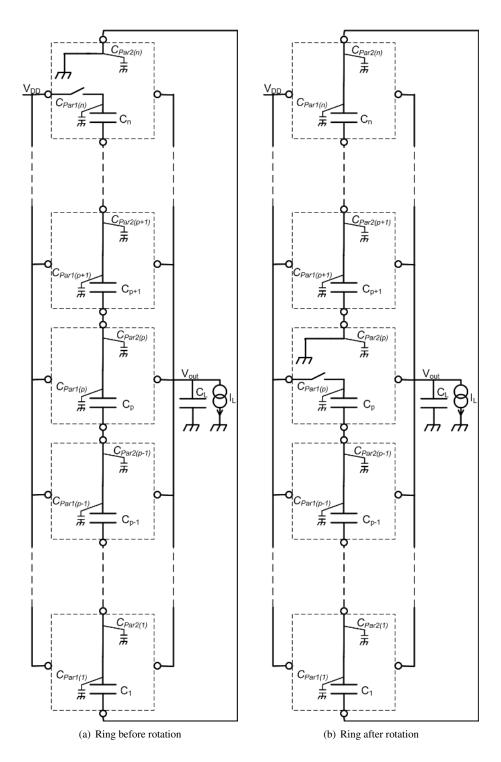

| 2.3. | Example of rotation in a five <b>Basic Capacitor Cells</b> ring   | . 15 |

| 2.4. | POLY1-POLY2 - PMOS composed capacitor.                            | . 16 |

| 2.5. | Power Transmission                                                | . 16 |

| 2.6. | Parasitic capacitance of a <b>Basic Capacitor Cell</b>            | . 19 |

| 2.7. | Ring configuration changes in a rotation                          | . 20 |

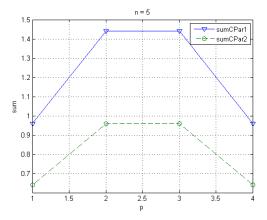

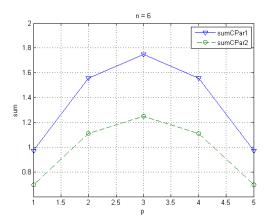

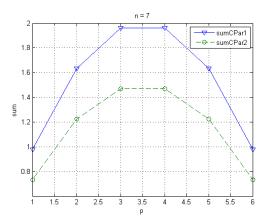

| 2.8. | SumCPar1 and SumCPar2 for different number of Basic Capacito      | r    |

|      | Cells converter.                                                  | . 23 |

| 2.9. | State of the parasitic capacitances before and after the rotation | . 25 |

| 2.10 | Rotation process.                                                 | . 26 |

|      | . Output and top plate voltages.                                  |      |

|      | Block diagram of control logic.                                   |      |

| 3.1. | N Basic Capacitor Cells Converter                                 | . 35 |

| 3.2. | N Basic Capacitor Cells ring circuits for numerical model         |      |

| 3.3. | Model Pseudo Code                                                 | . 43 |

| 3.4. | $V_{OUT}$ waveforms for numerical and electrical simulations      | . 45 |

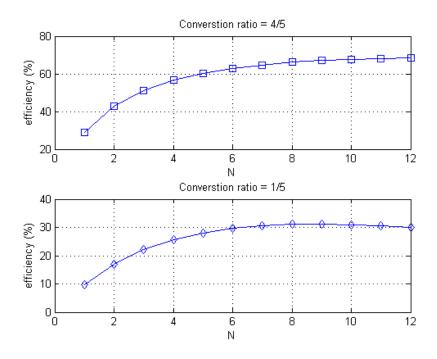

| 3.5. | Efficiency as a function of $N_{@I_L=100\mu A}$                   | . 46 |

| 4.1. | Proposed feedback loop.                                           | . 50 |

| 4.2. | Optimum $V_{REF}$ selection.                                      | . 51 |

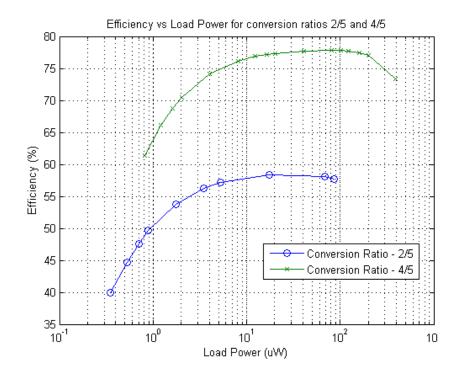

| 5.1. | Efficiency vs load power.                                         | . 54 |

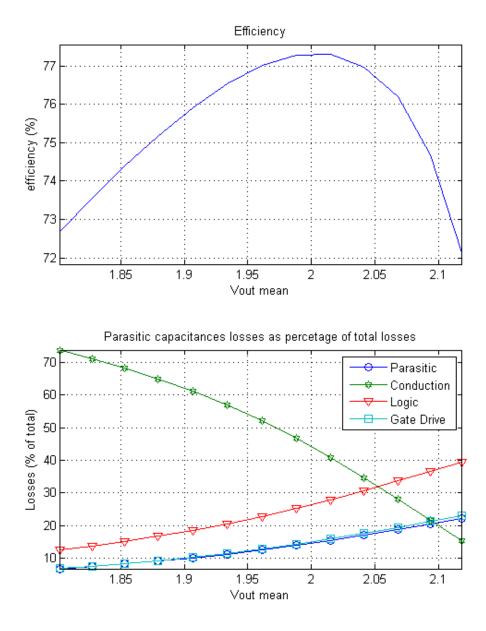

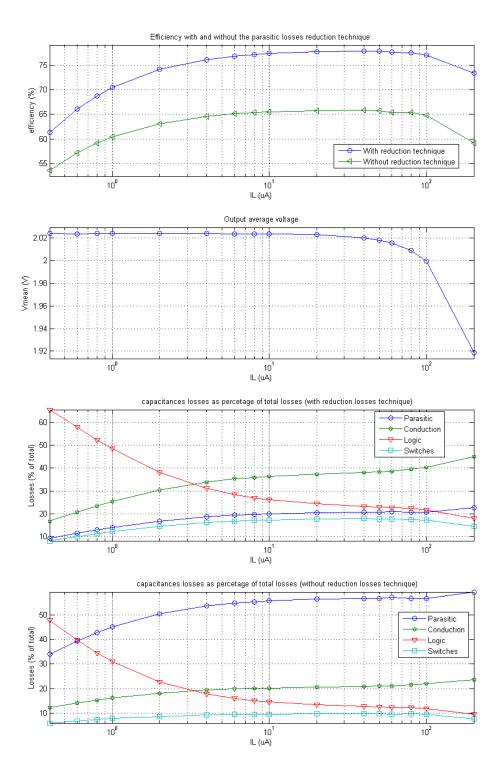

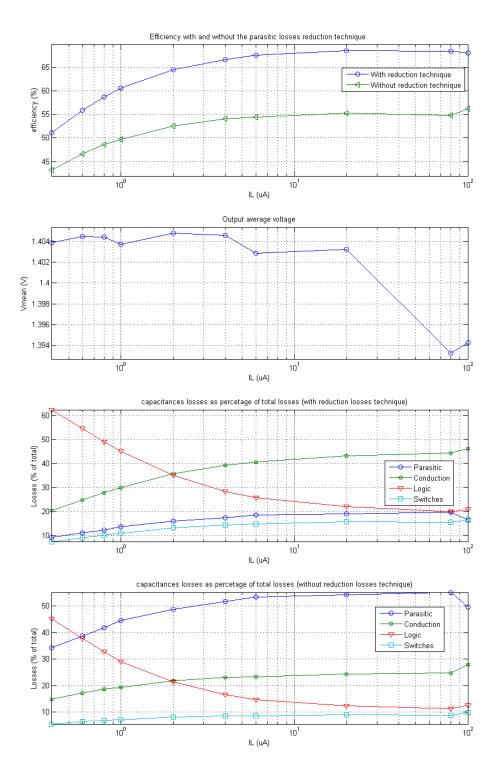

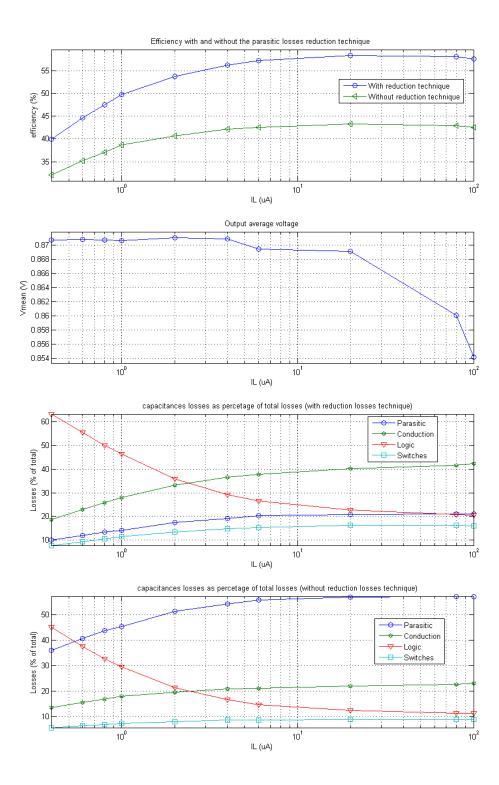

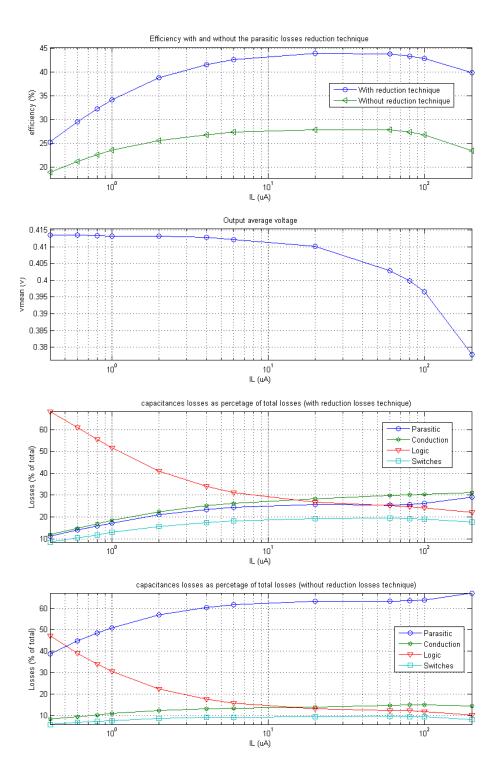

| 52   | 4/5 conversion ratio performance                                  | 56   |

| 5.4. | 3/5 conversion ratio performance.2/5 conversion ratio performance.1/5 conversion ratio performance. | <br>58 |

|------|-----------------------------------------------------------------------------------------------------|--------|

|      | Files Tree                                                                                          |        |

| B.1. | Capacitor to capacitor charge transfer.                                                             | <br>73 |

### Resumen

Este trabajo presenta una arquitectura novedosa para la implementación de convertidores DC-DC de condensadores conmutados de Ultra Bajo Consumo para aplicaciones como dispositivos implantables, redes de sensores inalámbricos, dispositivos portátiles, entre otros. El objetivo es suministrar energía a circuitos digitales tales como microcontroladores usando la técnica the escalado dinámico de voltaje que permite manejar el compromiso entre la performance y el consumo del circuito. Otra importante aplicación de este tipo de convertidores es para las nuevas tecnologías donde los transistores no soportan el voltaje entregado por los distintos tipos de pilas.

Cuantos más niveles de conversión tenga el convertidor mejor se puede aplicar la técnica de escalado dinámico de voltaje. Esto es porque diferentes niveles de performance de un circuito digital necesitan diferentes voltajes de alimentación para minimizar la potencia disipada alcanzando la performance necesaria. Existen algunos trabajos en el área, todos ellos tienen la particularidad de utilizar arquitecturas rígidas basadas en configuraciones particulares para cada nivel de conversión. Esto hace que este tipo de convertidores no sea apropiado para aumentar fácilmente la cantidad de niveles de conversión. La arquitectura propuesta en este trabajo tiene la particularidad de ser modular y permite fácilmente agregar más niveles de conversión si fuera necesario, a la vez que simplifica el diseño

Cada módulo esta compuesto por un condensador y una configuración de cuatro switches. El número de módulos usado en el convertidor define el número de niveles de conversión. Los módulos son conectados en forma de anillo el cual puede ser abierto en cualquiera de los nodos con el fin de conectar la fuente de alimentación. Luego la carga es conectada a uno de los nodos intermedios del anillo según el nivel de conversión deseado.

Dada la modularidad del convertidor un modelo numérico general fue desarrollado. Este modelo permite tener una predicción de la performance del convertidor para un número arbitrario de niveles de conversión. Dado que el modelo utiliza datos extraídos de simulaciones eléctricas y algunos parámetros de la tecnología, fácilmente puede ser usado para cualquier tecnología. El modelo es apropiado para realizar exploraciones del espacio de diseño y evitar los prolongados tiempos de las simulaciones eléctricas.

Un convertidor de cuatro niveles de conversion fue desarrollado y simulado a nivel eléctrico en la tecnología On Semi  $0.5\mu m$  con un voltaje de alimentación de 2.8V. El pico de eficiencia alcanzado es de 78 %. Esta performance es similar a la alcanzada por los trabajos existentes en la literatura. Para este convertidor la lógica fue implementado, pero no el lazo de control que fija la tensión de salida.

Una novedosa técnica para disminuir las pérdidas en las capacidades parásitas fue propuesta y simulada. Dicha técnica realiza una redistribución de la carga entre las capacidades parásitas que necesitan perder energía y aquellas que necesitan ganarla. Dado que las pérdidas en las capacidades parásitas son dominantes en esta arquitectura, una mejora significativa fue lograda en la eficiencia a partir de la aplicación de esta técnica.

### Abstract

This work presents a novel architecture for a step down **Switched Capacitor Converter** for **Ultra Low Power** applications such as implantable devices, Wireless Sensor Nodes, portable devices, etc. The objective is to supply energy to digital circuits such as micro-controllers using the **Dynamic Voltage Scaling** technique that allows to optimize the trade-off between performance and consumption. Other important applications of this type of converters are the newest technologies where the transistors are not able to tolerate the voltage provided by the different types of batteries.

The more conversion ratios the converter has the better to apply the **Dynamic Voltage Scaling** technique it is. This is because different performance levels in digital circuits need different supply voltages to minimize the power consumption while achieving the needed performance. In the literature there are some works in the area, all of them with the particularity of having a rigid architecture based on particular configurations for each conversion level. This makes this type of converters not suitable for adding easily more conversion ratios. The architecture proposed in this work has the particularity of being modular and being able to easily add new conversion ratios if necessary.

Each module (named **Basic Capacitor Cell**) is composed by a capacitor and a fourswitch configuration. The number of modules used in the converter defines the number of conversion ratios. The **Basic Capacitor Cells** are connected in a ring configuration that can be opened in each node to connect the supply voltage. Then the load is connected to one of the intermediate nodes.

Given the modularity of the converter a general numerical model was developed. This model allows to predict the performance of the converter for an arbitrary number of conversion ratios. As the model uses some data extracted from electrical simulation and some parameters of the technology, it can easily be used for any technology. The model is suitable to make design space exploration and avoid long electrical simulations times.

A four-conversion-ratios converter was developed and electrically simulated in the technology On Semi  $0.5\mu m$  with an input voltage of 2.8V. The peak efficiency achieved is 78 %. This performance is similar to the one achieved by existing works in the literature. The logic was implemented but not the control loop.

A novel technique to improve the losses in parasitic capacitances was proposed and simulated. This technique makes a redistribution of the charge between the parasitic capacitances that need to lose energy and those that need to gain energy. Since parasitic capacitances losses are dominant in this architecture a significant efficiency improvement was achieved using this technique.

Index Terms - Ultra Low Power , Switched Capacitor Converter , Dynamic Voltage Scaling , Power Management, DC-DC Converter .

## CHAPTER 1

### Introduction

### **1.1.** Motivation

The increasing emergence of battery-powered devices (notebooks, cell-phones, Wireless Sensor Networks, implantable devices, etc) has increased the efforts to optimize the consumption of these devices and thus increase battery life. This issue in implantable devices is critical because changing the battery involves surgery. The power consumption optimization effort is made at all levels: architecture, low level design, high level design, etc.

Since power consumption in digital circuits is proportional to the square of supply voltage (Equation  $1.1^1$ ) [1], decreasing it is a key factor for the purpose of maximizing battery life. Decreasing the supply voltage has a negative impact in the maximum frequency tolerated by digital circuits. So it is necessary to manage this trade-off decreasing the supply voltage when the performance of the digital circuit becomes lower to save energy and increasing it when the circuit needs a higher performance. This technique is named **Dynamic Voltage Scaling** [2].

$$P_{Digital} = f.C_L.V_{DD}^2 \tag{1.1}$$

On the other hand, the advance of technology has decreased the maximum voltage tolerated by **Integrated Circuits**, even below the voltage provided by different types of batteries (Ni-Cd, Li-ion, etc). So it is clear that having the capability of delivering to digital circuits a supply voltage lower than the provided by batteries is essential. This must be made with efficiency to avoid that the energy saved by decreasing the supply voltage is wasted by the **DC-DC Converter**.

In particular it is important to take into account the micro-controllers that in this type of devices have a repetitive behavior. They work staying long times in sleep mode

<sup>&</sup>lt;sup>1</sup>In this equation f is the switching frequency,  $C_L$  is an equivalent capacitor, and  $V_{DD}$  is the supply voltage.

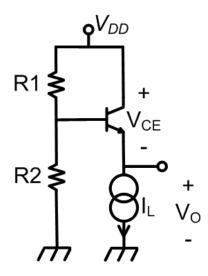

Figure 1.1: DC/DC converter implemented with an emitter follower.

with a consumption of some  $\mu A$  and then they wake up to make some calculations and transmit information, with a typical consumption of some hundred of  $\mu A$ . For example the PIC16(L)F1826/27 is a **Ultra Low Power** Micro-controller from Microchip that has a consumption of  $75\mu A/MHz_{@V_{DD}=1,8V}$  in active mode. In the sleep mode it has a consumption of 30nA but in most cases a time reference is needed so a timer is kept on all the time. The timer consumes  $0,6\mu A_{@32kHz}$  so this is a more real sleep mode consumption. The MSP430 is a family of Micro-controllers from Texas Instruments that has a consumption of  $220\mu A/MHz_{@V_{DD}=2,2V}$  and  $0,5\mu A$  in stand-by mode. So it is very important to have converters with good efficiency at these orders of currents.

A basic DC/DC converter can be an emitter follower as the one shown in Figure 1.1. The problem with this type of converter is that if we need to decrease the voltage to supply a digital circuit to improve the consumption, all the energy saved at the load is dissipated by the transistor, so there is no energy saved after all. Therefore for greater efficiency components capable of storing energy and then delivering it are used.

A very important family of such converters is the inductor-based converters such as buck and boost. The problem with them is that inductors are not suitable for integration mainly because they have a poor quality factor (Q), so they are not a good option for fully integrated DC/DC converters. In [3] a buck converter was presented with a poor achieved efficiency and a special technology was used in the capacitor fabrication and the inductor isolation. Also the design was made for much higher currents (in the order of mA). [4] presents a buck converter and said that the most complicated design issue is the inductor and uses a special technology that builds the inductor out of the chip but places it into the package. The power delivered by the converter is up to 0,5W so it is much higher than the previously mentioned. Then in [5] two techniques where used to avoid the low Q of the inductors and a good efficiency was achieved, but for much higher power too. In [6] a good efficiency was achieved but again for much higher power. As a conclusion, in the literature there are some works but most of them men-

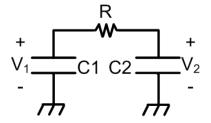

Figure 1.2: Capacitor to capacitor charge transfer.

tion difficulties or the need to use special technologies to build this type of converters on chip. On the other hand, the converters that achieve a good efficiency are designed for much higher power than the needed in **Ultra Low Power** applications. So this type of converters is not suitable for our aim.

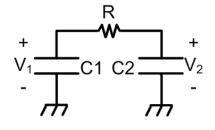

To avoid both problems (low efficiency for low currents and lack of easy integration capability), switched capacitor converters are used. This type of converters are based in the fact that energy transfer between capacitors can be made with an efficiency as close to 100 % as needed <sup>2</sup>. If we consider the capacitors shown in Figure 1.2 where the objective is to transfer energy from C1 to C2 through the resistance R, and we have the initial conditions:  $V1_i = V_i$  and  $V2_i = V_i - \Delta V$ , it is possible to demonstrate that the energy delivered to C2 is given by equation 1.2. It is also possible to demonstrate that the dissipated energy in the resistor is given by equation 1.3. The efficiency is the energy delivered to C2 over the energy consumed from the source (C1 in our case). So efficiency is given by equation 1.4<sup>3</sup>. As  $E_{Lost}$  decreases faster than  $\Delta E2$  when  $\Delta V \rightarrow 0$ , the asymptotic efficiency is 100% ( $\eta \rightarrow 1$ ) if  $\Delta V \approx 0$ .

$$\Delta E2 = \frac{C1.C2}{C1+C2} \cdot \left( V_i \cdot \Delta V - \frac{\Delta V^2}{2} \cdot \left( \frac{C1+2.C2}{C1+C2} \right) \right)$$

(1.2)

$$E_{Lost} = \frac{C1.C2.\Delta V^2}{2.(C1+C2)}$$

(1.3)

$$\eta = \frac{\Delta E2}{\Delta E2 + E_{Lost}} \tag{1.4}$$

For the reason mentioned above we can conclude that **Switched Capacitor Con**verters are the best option for our aim. So these are the converters studied in this thesis.

For low-level currents (below 1mA), comercial converter's efficiency is in general poor because they are designed for higher currents. So it is difficult to get a comercial **DC-DC Converter** to decrease the supply voltage efficiently for **Ultra Low Power** circuits (in the order of  $\mu A$  as mentioned above).

<sup>&</sup>lt;sup>2</sup>In this analysis we are just considering conduction losses. As will be see in the next section there are more losses that put a lower asymptotic limit in the efficiency.

<sup>&</sup>lt;sup>3</sup>Equations 1.2, 1.3 and 1.4 are derived in the appendix **B**.

However, academic research has been developing the area for some years. [7] is a very important work that achieves very good efficiency levels for **Ultra Low Power** applications. [8] is the most recent work that achieves similar results in terms of efficiency using different architecture and control logic. [9] has a good efficiency in relation with the conversion ratio (62% of efficiency with a 1/5 conversion ratio) but has just one conversion ratio. [10] has the peak of efficiency of 66,7% when the conversion ratio is approximately 0,6, but the controller consumes  $147,5\mu W^4$  despite using subthreshold logic. The specifications said that the minimum power to the load is  $400\mu W$  that is two or three orders higher than the consumption of a micro-controller in sleep mode. Then, [11] has an single output voltage (444mV) and a peak efficiency of 56% with a load current of 285nA. Furthermore, if we supply a digital circuit with 444mV we are working in the subthreshold region for the technology used. [12] achieves an efficiency from 37% to 56% but for currents from  $1\mu A$  to  $4\mu A$  and has just one output voltage level.

All these works use particular architectures that are hardly able to include another conversion ratio. This work presents a novel architecture for **Switched Capacitor Converters** that has the advantage of being modular and able to include more conversion ratios if necessary. This feature makes the architecture very appropriate for **Dynamic Voltage Scaling**. This is achieved presenting similar features in terms of efficiency in comparison with previous works. A novel technique to reduce dominant losses (parasitic capacitances losses) is presented, that has the particularity of reducing such losses as the number of conversion ratios is increased.

Summarizing the target application characteristics, the list of requirements for this work is:

- Input voltage 2,8V

- Current load  $1\mu A$   $100\mu A$

- Multiple conversion ratios with the same architecture

- High efficiency (> 60%)

# **1.2.** General Considerations for Switched Capacitor Converters

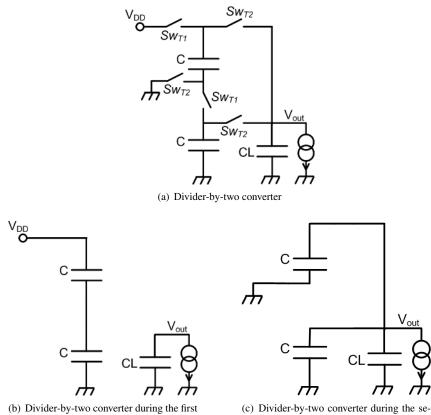

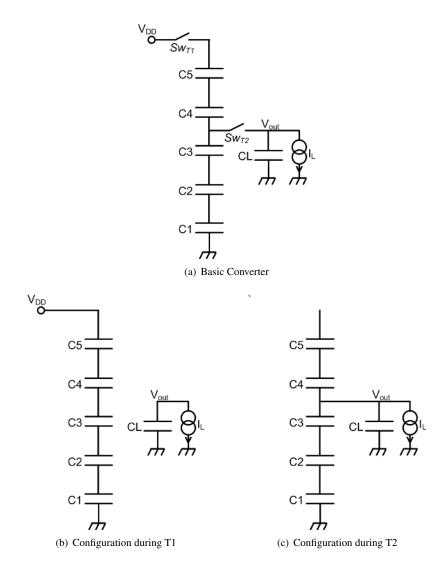

In a **Switched Capacitor Converter** there are several capacitor configurations and the times of duration of each configuration are called phases. An example of a basic **Switched Capacitor Converter** is shown in Figure 1.3. In Sub-Figure 1.3(a) the converter is shown with all the switches opened, then in Sub-Figure 1.3(b) the converter is shown in the configuration of phase one, and last in Sub-Figure 1.3(c) in the phase two.

During phase one the two capacitors of the converter are connected in series to the voltage source and each one is charged at  $\frac{V_{DD}}{2}$ . The output voltage is kept by the capacitor  $C_L$ . Then in the second phase the two capacitors are connected in parallel to

<sup>&</sup>lt;sup>4</sup>Remember that the power consumption of the micro-controllers previously mentioned is approximately this value.

phase configuration

(c) Divider-by-two converter during the se-cond phase configuration

Figure 1.3: Two phases divider-by-two Switched Capacitor Converter basic example

capacitor  $C_L$  and deliver to it the energy lost in the first phase and the needed by the load.

This cycle is repeated at a frequency  $f_{sw}$ . If the frequency and capacitors are such that the voltage in capacitors are essentially constant, the lost energy is negligible and the efficiency of the converter is close to 100%.

This and other configurations can be seen in [7].

#### 1.2.1. Losses In Switched Capacitor Converters

In the previous analysis a 100% asymptotic efficiency was mentioned. This was without considering some effects that cause an energy loss and a lower limit in the efficiency. This section analyzes the main types of losses.

#### Conduction Losses

As stated above, transfering charge from one capacitor to another (or from the supply voltage to a capacitor) with a lower voltage has a loss in the resistance of the switch involved in the process. As can be seen in equations (1.2), (1.3) and (1.4) the smaller is the voltage difference ( $\Delta V$ ) the more negligible are these losses. This type of energy loss is named  $E_{cond}$ .

#### Gate-drive Losses

To drive the gate of the switches that implement the different phases of the converter there is a cost of energy. So to minimize this losses it is necessary to implement the switches as small as possible. This type of energy loss is named  $E_{qates}$ .

#### **Parasitic Capacitance Losses**

When a floating capacitor is implemented in an **Integrated Circuit** some parasitic capacitances between the plates of the capacitor and the substrate appear. When the capacitor changes the voltage of the plates with respect to the substrate, energy is wasted to charge and discharge these parasitic capacitances, because this energy is not delivered to the load.

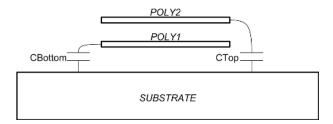

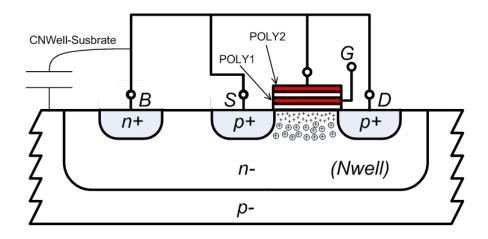

An example of floating capacitor implementation is with a poly1-poly2 capacitor. Figure 1.4 shows the capacitor and the parasitic capacitances involved.

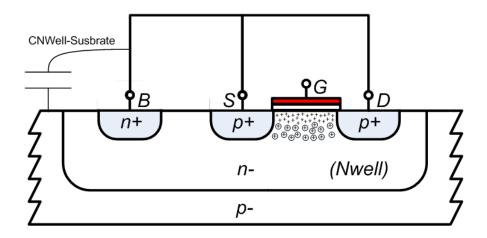

Another way to implement a floating capacitor is using a PMOS capacitor (in a N-Well technology)<sup>5</sup>. This implementation has the advantage that the capacity per unit area is higher than the first option (POLY1-POLY2), but has the disadvantage that it has a non-linear behavior. The implementation is shown in Figure 1.5 where it can be seen that Drain, Source, and Bulk are one plate of the capacitor and the Gate is the other. The NWell-Substrate diode parasitic capacitance appears in this case.

<sup>&</sup>lt;sup>5</sup>If we are using a N-Well technology it is necessary to use a PMOS transistor because the capacitor must be floating. As the NWell can float with respect to ground we must use a PMOS capacitor.

Figure 1.4: Bottom and top parasitic capacitances in a poly-poly capacitor.

Figure 1.5: PMOS capacitor implementation and parasitic capacitances.

The energy lost due to the charging and discharging of these parasitic capacitances is named  $E_{par}$ .

#### Logic Losses

To manage the switches of the converter a sequential logic is needed. The energy supplied to the logic circuits is not delivered to the load so it is important to minimize these losses to have a good efficiency mainly when the power delivered to the load is low. This type of energy lost is named  $E_{logic}$ . We will include in this term also the energy consumed by the analog circuits of the control block.

#### 1.2.2. Efficiency

As the objective of a **Switched Capacitor Converter** is to deliver energy to a device using a different voltage than the input one, the efficiency is defined in terms of energy. So the efficiency is the ratio between energy delivered by the converter to the load and the energy taken by the converter from the supply voltage:

$$\eta = \frac{E_{out}}{E_{in}} = \frac{E_{load}}{E_{load} + E_{loss}} \tag{1.5}$$

where

$$E_{loss} = E_{cond} + E_{gates} + E_{par} + E_{logic} \tag{1.6}$$

and  $E_{load}$  is the energy delivered to the load.

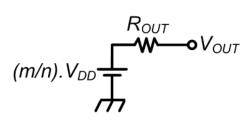

#### 1.2.3. Output Resistance

Figure 1.6 shows an equivalent circuit for a general **Switched Capacitor Conver**ter. It is not possible to have a general theory to derive the output resistance  $R_{OUT}$ . However it is possible to develop a general theory to calculate this resistance in the two limit modes that a **Switched Capacitor Converter** can work. These modes are the Slow Switching Limit (SSL from now on) and Fast Switching Limit (FSL from now on) that are discussed in the Chapter 2 of [13].

It is considered that a given **Switched Capacitor Converter** is working in SSL when the switching frequency is slow enough to consider that currents are impulsive, or equivalently each phase of the converter has a time duration much bigger than the time constants ( $\tau$ ) of the different topologies of the circuits. In this limit an equivalent output resistance ( $R_{SSL}$ ) can be calculated, this calculation can be made with a general theory that can be applied in all **Switched Capacitor Converters**. This equivalent resistance has the particularity of being inversely proportional to the switching frequency as can be seen in equation (1.7). The constant  $K_{SSL}$  is a function of the capacitor values, number of phases of the converter and the topology. In particular it is important to highlight that  $K_{SSL}$  is a sum where each term is inversely proportional to a capacitor of the converter.

$$R_{SSL} = \frac{K_{SSL}}{f_{Sw}} \tag{1.7}$$

On the other hand, it is considered that a given **Switched Capacitor Converter** is working in FSL when the switching frequency is fast enough to consider that currents are constant, or equivalently each phase of the converter has a time duration much lower than the time constants ( $\tau$ ) of the different topologies of the circuits. Again in this limit an equivalent output resistance ( $R_{FSL}$ ) can be calculated with a general theory that can be applied in all **Switched Capacitor Converters**. This equivalent resistance has the particularity of being independent of the switching frequency. The value of this resistance depends of the switches resistance, the number of phases of the converter and the topology.

As mentioned above it is not possible to develop a general theory to calculate the output resistance in the range of frequencies where none of the two modes are valid. However an accepted approximation can be used as shows the equation (1.8).

$$R_{OUT} \simeq \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{1.8}$$

A deeper analysis of the output resistance calculations can be seen in the chapter two of [13].

Figure 1.6: Switched Capacitor Converter equivalent circuit.

## CHAPTER 2

### **Proposed Architecture**

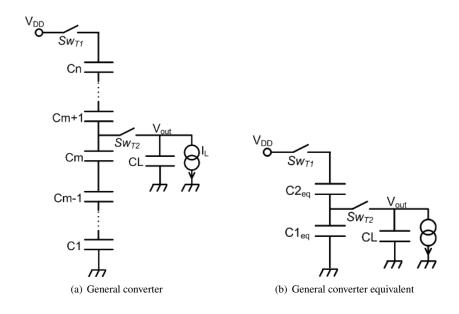

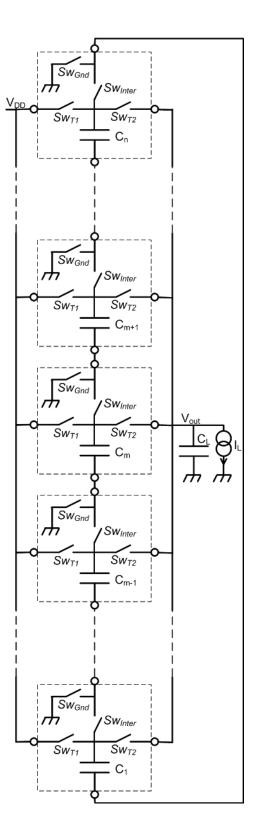

The general idea of the architecture proposed in this thesis is to have n equal capacitors connected in series and another capacitor connected in parallel with the load  $(C_L \text{ from now on})$ . One end of the series is always connected to ground. The other end is connected to the source during one phase. The load and  $C_L$  are connected to an alternative node during the other phase. Therefore, the converter has two phases and n-1 conversion ratios (as many as intermediate nodes in the series). Figure 2.1 shows a particular case with n = 5 and a conversion ratio of  $\frac{3}{5}$ .

In the first phase (T1 from now on) shown in the Sub-Figure 2.1(b) the source  $(V_{DD})$  is connected to the capacitor series, so the converter takes energy from the source and all the capacitors in the series have a voltage  $\frac{V_{DD}}{n}$ . In this phase  $C_L$  gives charge to the load and keeps the output voltage  $V_{OUT}$ .

In the second phase (T2 from now on) shown in Sub-Figure 2.1(c) one of the intermediate nodes of the series is connected to the load and the source is disconnected. So the converter gives charge to the load and returns to  $C_L$  the charge taken by the load during T1<sup>1</sup>. The conversion ratio is defined by the node where the load is connected during this phase.

Sub-Figure 2.1(a) shows the series of capacitors C1..C5, the capacitor connected to the load  $C_L$ , the load represented by a current source, and the switches SwT1 and SwT2 used in phases T1 and T2 respectively. Then in Sub-Figures 2.1(b) and 2.1(c) are shown respectively the configuration in the two phases. If for example we want to have a conversion ratio of  $\frac{4}{5}$  we must connect the output to the node between C4 and C5.

The problem here is that during T2 the capacitor composed by the series C1..C3 is discharged (gives charge to the load and  $C_L$ ) while the capacitor composed by the series of C4 and C5 keeps the same charge. This difference of charge remains unchan-

<sup>&</sup>lt;sup>1</sup>Expressions T1 and T2 are used to represent both the phase and the duration of each.

Figure 2.1: Example of converter with n = 5 and conversion ratio of 3/5

ged when in the next phase T1, the total series is connected to the supply voltage and the sum of voltages in the five capacitor is  $V_{DD}$ . Therefore the voltage in the series C1..C3 will decrease every cycle and the output voltage too. The voltage in the series of capacitors C4 and C5 has the opposite effect and will increase every cycle. So it is necessary a way to replace this charge in the node where the load is connected.

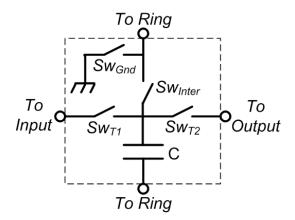

To solve this problem, capacitors are rotated of position in the ring. So instead of thinking about a series of capacitors it is better to imagine a ring which can be opened in every node. All the capacitors of the ring are associated to a switches configuration that implement a **Basic Capacitor Cell**. Figure 2.2 shows that cell.

It can be seen that the top plate of the capacitor can be connected to the input and to the output through the switches SwT1 and SwT2. It also shows that the ring can be opened with the switch SwInter and can be connected to ground through the switch SwGnd.

Figure 2.3 shows an example with n = 5 where the ring is composed by five **Basic Capacitor Cells**, Figure 2.3(a) shows the ring with all the switches opened. Then in 2.3(b) and 2.3(c) the configuration of the ring before and after a rotation are shown. In the first one the ring is opened in the **Basic Capacitor Cell** of capacitor C5 and the output is connected through the **Basic Capacitor Cell** of capacitor C3. After the rotation the ring is opened in the **Basic Capacitor Cell** of capacitor C4 and the output is connected through the **Basic Capacitor Cell** of capacitor C4 and the output is connected through the **Basic Capacitor Cell** of capacitor C2. In this way all capacitors will be connected to the supply voltage in a moment and will recover the charge.

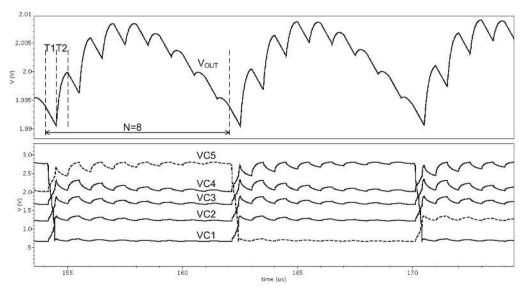

The rotation of the ring causes a significant loss in parasitic capacitances, so there is a trade-off between avoiding the rotation of the ring to minimize the mentioned losses, and the need to rotate the ring to replace the charge to the nodes where the load is connected. This effect is illustrated in Sub-Figure 2.11(a) showing the output voltage ( $V_{OUT}$ ). In the first phase T1 (bounded with two dotted lines) the ring is being rotated and the load is taking charge from  $C_L$ , so the output voltage is decreasing. In the next phase T2 (bounded with two dotted lines too) the output voltage is increased by the charge given by converter to  $C_L$  and the load. This process is repeated eight times before the next rotation. As can be seen in the first three periods T1 + T2 the output voltage is increased, but because the discharging process above mentioned in the next five periods the same will decrease. In this example the conversion ratio is  $\frac{4}{5}$ and the supply voltage ( $V_{DD}$ ) is 2.8V. The rest of the waveforms will be explained next.

A discussion on which is the best way to implement the rotation will be introduced in Section 2.3 after the parasitic capacitances losses are analyzed.

### 2.1. Capacitors Implementation

Since the capacitors of the ring have essentially the same bias voltage it is possible to use non-linear capacitors and keep the ratio between them (all equal in our case). So it is possible to use in parallel with the POLY1-POLY2 capacitors a PMOS capacitor. This increases the capacitance per unit area because it is possible to build a POLY1-POLY2 capacitor above a PMOS capacitor. The load capacitor ( $C_L$ ) needs no matching so it is possible to use a combined device too.

Figure 2.2: Basic Capacitor Cell

This has an advantage because the bottom parasitic capacitance (POLY1-NWell) can be connected in parallel with the main capacitor and the top parasitic capacitance (POLY2-NWell) is short-circuited (see Figure 1.4). As a disadvantage the NWell-Substrate parasitic capacitance appears. Figure 2.4 shows the composed capacitor and the parasitic capacitance.

### 2.2. Charge Transfer Analysis

Figure 2.5 shows a general series of n equal capacitors of value C and the load capacitor  $C_L$ . If we have a conversion ratio of  $\frac{m}{n}$  the equivalent circuit is a series of two capacitors:  $C1_{eq} = \frac{C}{m}$  and  $C2_{eq} = \frac{C}{n-m}$ . They can be seen in Figure 2.5(b).

To understand the energy transmission in a cycle we will consider three phases: T1 that gives us the initial conditions, T2 that transfers charge to the load and  $C_L$ , and T1 again because it is the phase when the supply voltage replaces the energy delivered by the converter to the load.

After the first phase T1, when the source  $V_{DD}$  is connected,  $C1_{eq}$  and  $C2_{eq}$  have a charge  $Q1_i$  and  $Q2_i$  respectively. To make a general analysis  $Q1_i$  and  $Q2_i$  are not necessarily equal. So we have the equation:

$$V_{DD} = \frac{Q1_i}{C1_{eq}} + \frac{Q2_i}{C2_{eq}}$$

(2.1)

During the phase T2 the load and  $C_L$  take a charge  $\Delta Q$  from  $C1_{eq}$ .<sup>2</sup>. Thus, the difference between the charge of  $C2_{eq}$  and  $C1_{eq}$  is  $\Delta Q$  more than at the beginning. So we have the equation:

<sup>&</sup>lt;sup>2</sup>The charge  $\Delta Q$  is the demanded by the load during T2 and the necessary to replace the charge taken by the load from  $C_L$  during one T1. So it is the total charge taken by the load in a cycle T1 + T2.

(b) Before rotation

Figure 2.3: Example of rotation in a five **Basic Capacitor Cells** ring

Figure 2.4: POLY1-POLY2 - PMOS composed capacitor.

Figure 2.5: Power Transmission

$$Q2_f - Q1_f = Q2_i - Q1_i + \Delta Q \tag{2.2}$$

As  $Q1_f$  and  $Q2_f$  are the charge in  $C1_{eq}$  and  $C2_{eq}$  respectively in the second considered phase T1 they meet the following equation:

$$V_{DD} = \frac{Q1_f}{C1_{eq}} + \frac{Q2_f}{C2_{eq}}$$

(2.3)

Now from (2.2) and (2.3)

$$V_{DD} = \frac{Q2_f - Q2_i + Q1_i - \Delta Q}{C1_{eq}} + \frac{Q2_f}{C2_{eq}}$$

(2.4)

Thus

$$V_{DD} - \frac{Q1_i}{C1_{eq}} = Q2_f \cdot \left(\frac{1}{C1_{eq}} + \frac{1}{C2_{eq}}\right) - \frac{Q2_i}{C1_{eq}} - \frac{\Delta Q}{C1_{eq}}$$

(2.5)

And from (2.1) we have that

$$\frac{Q2_i}{C2_{eq}} = Q2_f \cdot \left(\frac{1}{C1_{eq}} + \frac{1}{C2_{eq}}\right) - \frac{Q2_i}{C1_{eq}} - \frac{\Delta Q}{C1_{eq}}$$

(2.6)

Then

$$Q2_{i} \cdot \left(\frac{1}{C1_{eq}} + \frac{1}{C2_{eq}}\right) = Q2_{f} \cdot \left(\frac{1}{C1_{eq}} + \frac{1}{C2_{eq}}\right) - \frac{\Delta Q}{C1_{eq}}$$

(2.7)

Or

$$Q2_f = Q2_i + \Delta Q. \left(\frac{C2_{eq}}{C1_{eq} + C2_{eq}}\right)$$

(2.8)

Since the variation in the charge of  $C2_{eq}$  is given by the source, the charge taken from the source during the second considered phase T1 to replace the charge taken by the load and  $C_L$  during phase T2 is:

$$\Delta Q_{V_{DD}} = \Delta Q. \left(\frac{C2_{eq}}{C1_{eq} + C2_{eq}}\right)$$

(2.9)

For all devices we have that:

$$\Delta E = \int V.I.dt \tag{2.10}$$

In the case of the source the voltage is constant so the delivered energy is:

$$\Delta E_{V_{DD}} = \int V_{DD}.I.dt = V_{DD}.\int I.dt = V_{DD}.\Delta Q_{V_{DD}}$$

(2.11)

From (2.9) and (2.11)

$$\Delta E_{V_{DD}} = V_{DD}.\Delta Q. \left(\frac{C2_{eq}}{C1_{eq} + C2_{eq}}\right)$$

(2.12)

To calculate the energy taken by the load in the cycle we do not have a constant voltage, but if we think in capacitors as big as necessary to have essentially a constant voltage in all of them we can say that the equation (2.10) in the case of the load is

$$\Delta E_{Load} = V_{OUT} \Delta Q \tag{2.13}$$

As can be seen from figure 2.5 the no load output voltage is  $V_{OUT}^{NL} = V_{DD}$ .  $\left(\frac{C2_{eq}}{C1_{eq}+C2_{eq}}\right)$ . As capacitors are considerer as big as necessary we have that  $V_{OUT} = V_{OUT}^{NL}$ . So using equation 2.13:

$$\Delta E_{Load} = V_{DD} \cdot \left(\frac{C2_{eq}}{C1_{eq} + C2_{eq}}\right) \cdot \Delta Q \tag{2.14}$$

And the efficiency is:

$$\eta = \frac{\Delta E_{Load}}{\Delta E_{V_{DD}}} = 1 \tag{2.15}$$

As we have considered a general case it is possible to conclude that the architecture proposed has an asymptotic ideal efficiency of 100% for all the conversion ratios.

### **2.3.** Parasitic Capacitances Losses

As will be seen next these losses are the main source of loss so it is very important to have a good understanding of the subject. Parasitic capacitances losses happen when the ring is rotated. So to understand which is the best way to rotate the ring it is very important to know the dependence of these losses with the rotation process.

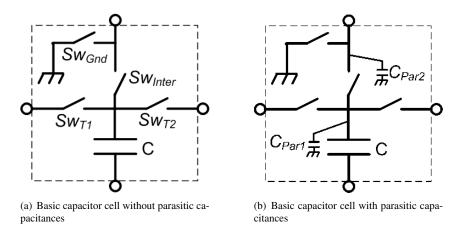

Figure 2.6 shows the **Basic Capacitor Cell** with and without the parasitic capacitances which appear in 2.6(b) as  $C_{Par1}$  and  $C_{Par2}^{3}$ .

$C_{Par1}$  is composed of the parasitic capacitances of the switches SwT1, SwT2, SwInter, and the parasitic capacitance of the NWell-Substrate diode of the PMOS capacitor<sup>4</sup>.  $C_{Par2}$  is composed of the parasitic capacitances of the switches SwGnd and SwInter. So  $C_{Par1}$  and  $C_{Par2}$  are described by equations (2.16) and (2.17) respectively.

$$C_{Par1} = C_{ParSwT1} + C_{ParSwT2} + C_{ParSwInter} + C_{NWell-Sust}$$

(2.16)

and

$$C_{Par2} = C_{ParSwGnd} + C_{ParSwInter} \tag{2.17}$$

As variation of energy in a capacitor is given by equation (2.18), to calculate the energy consumed in a rotation we need to know the voltage in every node of the ring before and after the rotation. To see this we must look at Figure 2.7. In 2.7(a) and

$<sup>^{3}</sup>$ Note that there are more parasitic capacitances but the ones shown in the figure 2.6(b) are the only ones that consume energy in the rotation. The other parasitic capacitances of the switches are connected to fix voltage nodes.

<sup>&</sup>lt;sup>4</sup>Remember that capacitor C is composed by a poly-poly capacitor in parallel with a PMOS capacitor (See Figure 2.4).

Figure 2.6: Parasitic capacitance of a Basic Capacitor Cell

2.7(b) we can see the ring configuration before and after a rotation respectively. We will analyze the general case when the ring is open in the **Basic Capacitor Cell** of the capacitor Cn and after the rotation we open the ring in the **Basic Capacitor Cell** of a generic Cp capacitor of the ring.

$$\Delta E_C = \frac{C}{2} \cdot \left( V_f^2 - V_i^2 \right)$$

(2.18)

In Figure 2.7(a) we can see that the bottom plate of capacitor  $C_1$  is connected to ground through the switch SwGnd of the capacitor  $C_n$ . The input  $(V_{DD})$  is connected during T1 through the switch SwT1 of the capacitor  $C_n$ . So it is simple to see that the voltage in the top plate of the capacitor  $C_1$  is  $V_{DD}$ .  $\frac{1}{n}$ , in  $C_2$  is  $V_{DD}$ .  $\frac{2}{n}$ , etc. So for  $C_{Par1}$  we have that:

$$V_{C_{Par1}i}(k) = V_{DD}.\left(\frac{k}{n}\right); \quad \forall k = 1:n$$

(2.19)

In the case of  $C_{Par2}$  it is the same with the exception of  $C_n$  because this node is connected to ground. So for  $C_{Par2}$  we have that:

$$V_{C_{Par2}i}(k) = \begin{cases} V_{DD}.\left(\frac{k}{n}\right) & \forall k = 1: n-1\\ 0 & k = n \end{cases}$$

(2.20)

In Sub-Figure 2.7(b) we can see that the bottom plate of  $C_{p+1}$  is connected to ground through the switch SwGnd of the capacitor  $C_p$ . The input  $(V_{DD})$  is connected during T1 through the switch SwT1 of the capacitor  $C_p$ . We can see that the voltage in the top plate of  $C_{p+1}$  is  $V_{DD}$ .  $\frac{1}{n}$  and so on to  $C_n$  that has a voltage in the top plate of  $V_{DD}$ .  $\frac{n-p}{n}$ . Equally we can see that top plate of  $C_p$  is  $V_{DD}$  and so on to  $C_1$  who has a voltage in the top plate of  $V_{DD}$ .  $\frac{n-p+1}{n}$ . Summarizing the final voltage of every parasitic capacitor  $C_{Par1}$  is:

$$V_{C_{Par1}f}(k) = \begin{cases} V_{DD} \cdot \left(\frac{k+n-p}{n}\right) & \forall k = 1:p \\ V_{DD} \cdot \left(\frac{k-p}{n}\right) & \forall k = p+1:n \end{cases} 0 (2.21)$$

Figure 2.7: Ring configuration changes in a rotation

In the case of  $C_{Par2}$  it is the same with the exception of  $C_p$  because this node is connected to ground. So for  $C_{Par2}$  we have that:

$$V_{C_{Par2}f}(k) = \begin{cases} V_{DD} \cdot \left(\frac{k+n-p}{n}\right) & \forall k = 1: p-1 \\ V_{DD} \cdot \left(\frac{k-p}{n}\right) & \forall k = p: n \end{cases} 0 (2.22)$$

Thus from equations (2.18), (2.19) and (2.21) we have that:

$$\Delta E_{C_{Par1}}(k) = \frac{C_{Par1}}{2} \cdot V_{DD}^{2} \cdot \left\{ \begin{bmatrix} \left(\frac{k+n-p}{n}\right)^{2} - \left(\frac{k}{n}\right)^{2} \end{bmatrix} & \forall k = 1:p \\ \left[ \left(\frac{k-p}{n}\right)^{2} - \left(\frac{k}{n}\right)^{2} \end{bmatrix} & \forall k = p+1:n \\ \end{bmatrix} 0

(2.23)$$

From equation (2.23) we can see that the energy variation in parasitic capacitors from  $C_1$  to  $C_p$  is positive and negative in the rest. This is because in the first case parasitic capacitors are receiving energy form the source and in the second one they are throwing the energy to ground. So to calculate the energy consumed from the source we have:

$$\Delta E_{C_{Par1}Total} = \sum_{k=1}^{p} \Delta E_{C_{Par1}}(k) = \frac{C_{Par1}}{2} \cdot V_{DD}^{2} \cdot \sum_{k=1}^{p} \left[ \left( \frac{k+n-p}{n} \right)^{2} - \left( \frac{k}{n} \right)^{2} \right]$$

(2.24)

And from equations (2.18), (2.20) and (2.22) we have that:

$$\Delta E_{C_{Par2}}(k) = \frac{C_{Par2}}{2} \cdot V_{DD}^{2} \cdot \left\{ \begin{bmatrix} \left(\frac{k+n-p}{n}\right)^{2} - \left(\frac{k}{n}\right)^{2} \end{bmatrix} & \forall k = 1: p-1 \\ \left[ \left(\frac{k-p}{n}\right)^{2} - \left(\frac{k}{n}\right)^{2} \end{bmatrix} & \forall k = p: n-1 \\ \left[ \left(\frac{k-p}{n}\right)^{2} - 0 \end{bmatrix} & k = n \end{bmatrix} 0 < m < n$$

(2.25)

From equation (2.25) we can see that the energy variation in parasitic capacitors from  $C_p$  to  $C_{n-1}$  is negative and positive in the rest. This is because in the first case parasitic capacitors are throwing to ground the energy and in the second one they are receiving energy form the source. In steady-state the energy received form the source is equal to the one thrown to ground. So to calculate the energy consumed from the source we can do it using the negative terms of equation (2.25) and multiplying them by -1. So we have that:

$$\Delta E_{C_{Par2}Total} = \sum_{k=p}^{n-1} \Delta E_{C_{Par2}}(k) = \frac{C_{Par2}}{2} \cdot V_{DD}^2 \cdot \sum_{k=p}^{n-1} \left[ \left(\frac{k}{n}\right)^2 - \left(\frac{k-p}{n}\right)^2 \right]$$

(2.26)

From equations (2.24) and (2.26) we can see that the consumption of a rotation of the ring has a dependency with p. This is equivalent to say that it has a dependency with the number of places that the capacitors are shifted in each rotation. To know which is

the best way to rotate the ring it is enough to know the dependence with p of the sums that appear in both equations. These sums will be called sumCPar1 and sumCPar2respectively. Figure 2.8 shows the value of the sums as function of p for converters of five, six, and seven **Basic Capacitor Cells**, where is clear that the best choice is to shift one place each capacitor in each rotation so the election is  $p = n - 1^5$ . So for the choice taken equations (2.24) and (2.26) become:

$$\Delta E_{C_{Par1}Total} = \frac{C_{Par1}}{2} \cdot V_{DD}^2 \cdot \sum_{k=1}^{n-1} \left[ \left(\frac{k+1}{n}\right)^2 - \left(\frac{k}{n}\right)^2 \right]$$

or

$$\Delta E_{C_{Par1}Total} = \frac{C_{Par1}}{2} . V_{DD}^2 . \left(1 - \frac{1}{n^2}\right)$$

(2.27)

and

$$\Delta E_{C_{Par2}Total} = \frac{C_{Par2}}{2} \cdot V_{DD}^2 \cdot \sum_{k=n-1}^{n-1} \left[ \left(\frac{k}{n}\right)^2 - \left(\frac{k - (n-1)}{n}\right)^2 \right]$$

or

$$\Delta E_{C_{Par2}Total} = \frac{C_{Par2}}{2} \cdot V_{DD}^2 \cdot \left(\frac{n-1}{n}\right)^2$$

(2.28)

Thus

$$\Delta E_{C_{ParTotal}} = \frac{C_{Par1}}{2} . V_{DD}^2 . \left(1 - \frac{1}{n^2}\right) + \frac{C_{Par2}}{2} . V_{DD}^2 . \left(\frac{n-1}{n}\right)^2$$

(2.29)

### 2.4. Rotation Technique to Reduce Parasitic Capacitances Losses

Since parasitic capacitances losses are the main reason for losses in the converter and therefore the fall in efficiency, a detailed analysis of this issue for the chosen case of rotation (p = n - 1) is made in this section. Then the implemented technique to decrease these losses is presented.

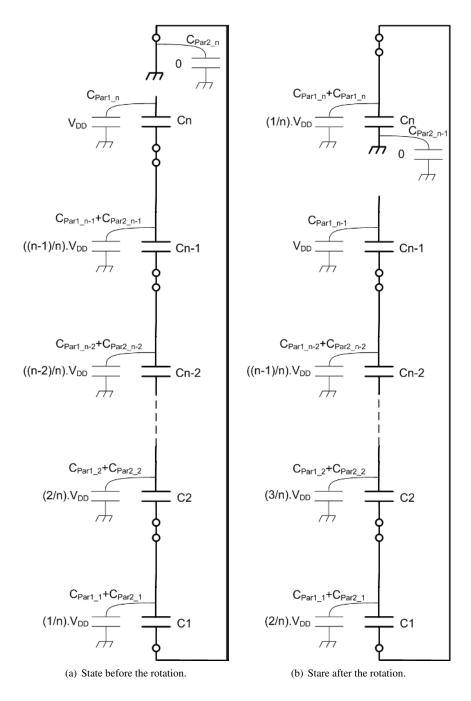

Figure 2.9 shows the state of the parasitic capacitances before and after the rotation. In Sub-Figure 2.9(a) the state of all the parasitic capacitances before the rotation is shown.  $C_{Par1.n}$  voltage is  $V_{DD}$  and  $C_{Par2.n}$  voltage is zero<sup>6</sup>. Parasitic capacitances

<sup>&</sup>lt;sup>5</sup>From Figure 2.8 it is clear that it is exactly the same to choose p = 1 or p = n - 1 so the election p = n - 1 is arbitrary. Furthermore this choice has no impact on other aspects as logic or switching consumption, etc.

<sup>&</sup>lt;sup>6</sup>Remember that parasitic capacitances  $C_{Par1}$  and  $C_{Par2}$  of a **Basic Capacitor Cell** are short-circuited if the interconnection switch is closed. See Figure 2.6.

(a) SumCPar1 and SumCPar2 for a five **Basic Capacitor Cells** converter as function of p.

(b) SumCPar1 and SumCPar2 for a six **Basic Capacitor Cells** converter as function of p.

(c) SumCPar1 and SumCPar2 for a seven **Basic Capacitor Cells** converter as function of p.

Figure 2.8: SumCPar1 and SumCPar2 for different number of Basic Capacitor Cells converter.

$C_{Par1.n-1}$  and  $C_{Par2.n-1}$  are short-circuited and have a voltage of  $\frac{n-1}{n} V_{DD}$ . The rest of parasitic capacitances are in a similar situation but with the other fractions of the supply voltage  $(\frac{n-2}{n} V_{DD}, \frac{n-3}{n} V_{DD}, \text{etc})$ .

In Sub-Figure 2.9(b) the state of all the parasitic capacitances after the rotation process is shown. It can be seen that capacitors  $C_{Par1.n}$  and  $C_{Par2.n-1}$  have lost energy while the rest of the parasitic capacitances have gained energy. In steady state the mentioned energy lost by  $C_{Par1.n}$  and  $C_{Par2.n-1}$  is equal to the energy gained by the rest of the parasitic capacitances<sup>7</sup>.

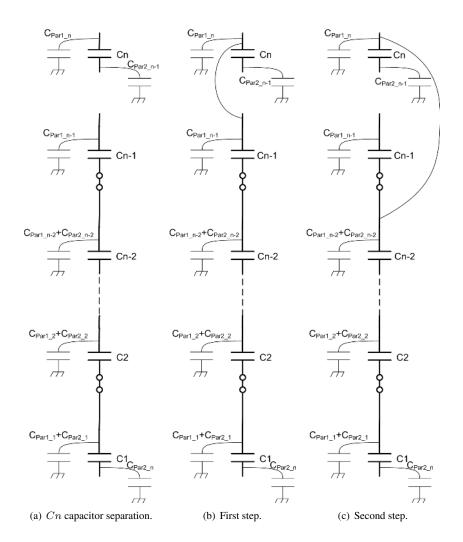

Equations (2.27) and (2.28) where derived assuming that the parasitic capacitances that lose energy during the rotation throw that energy to ground. Instead it is possible to make a redistribution of that charge to the parasitic capacitances that need to gain energy. Or, what is the same, the parasitic capacitances that need to lose energy can do it delivering energy to the parasitic capacitances that need to gain energy. For this the order in which the rotation sequence is performed is critical. Figure 2.10 shows the process.

#### **Preparation For the Rotation Process**

As capacitors of the ring (C1, C2,...,Cn) are much larger than parasitic capacitances they can be considered as constant voltage source. Before the first step of the rotation it is needed that all the capacitors of the ring be floating and separate from the ring the capacitor whose parasitic capacitances will lose energy (Cn in Figure 2.10). So all switches SWGnd must be kept opened during the rotation process and both SwInter that connect Cn to the ring must be kept opened. This situation is shown in Sub-Figure 2.10(a).

#### First Step in the Rotation Process

As energy lost in the energy transfer between two capacitors is proportional to the square of the difference in the initial voltage (Equation 1.3) the less is the difference the less is the energy lost. So the first step is to connect the parasitic capacitance  $C_{Par1.n}$  to the parasitic capacitance  $C_{Par1.n-1}$  that have less difference of voltage. That difference is  $\frac{V_{DD}}{n}$ . The mentioned situation is shown in Sub-Figure 2.10(b). As mentioned the capacitors of the ring can be considered as constant voltage sources, so if we consider only the variations in the parasitic capacitances the equivalent circuit is equal to the one shown in Figure 1.2, where C1 (the capacitor that delivers energy) is the parallel of  $C_{Par1.n}$  and  $C_{Par2.n-1}$  and C2 (the capacitor that takes energy) is the parallel of the rest of the parasitic capacitances.

If we define  $C_{Par} = C_{Par1} + C_{Par2}$  then we have that:  $C1 = C_{Par}$  and  $C2 = (n-1).C_{Par}$ . The energy lost in the first step is (using equation 1.3):

$$E_{Lost1} = \frac{C1.C2.\Delta V^2}{2.(C1+C2)} = \frac{C_{Par.}(n-1).C_{Par}.\Delta V^2}{2.(C_{Par}+(n-1).C_{Par})} = \frac{C_{Par.}(n-1).V_{DD}^2}{2.n^3}$$

(2.30)

<sup>&</sup>lt;sup>7</sup>This is because in steady-state the converter as a whole can't win energy.

Figure 2.9: State of the parasitic capacitances before and after the rotation.

Figure 2.10: Rotation process.

#### **Rest of Steps in the Rotation Process**

The second step is to connect parasitic capacitance  $C_{Par1.n}$  to the parasitic capacitance  $C_{Par1.n-2}$  (see Sub-Figure 2.10(c)). The difference of voltage is again  $\frac{V_{DD}}{n}$  and the equivalent circuit is the same as the first step. So the loss of energy is again the shown in equation (2.30).

This process is repeated until  $C_{Par1.n}$  is connected to the bottom plate of the capacitor C1 so the number of steps is n. Then the energy lost in the whole process is  $n.E_{Lost1}$ :

$$E_{LostRotation} = \frac{C_{Par}}{2} \cdot V_{DD}^2 \cdot \frac{(n-1)}{n^2}$$

or

$$\Delta E^*_{C_{ParTotal}} = \frac{C_{Par1}}{2} \cdot V^2_{DD} \cdot \frac{(n-1)}{n^2} + \frac{C_{Par2}}{2} \cdot V^2_{DD} \cdot \frac{(n-1)}{n^2}$$

(2.31)

with

$$\Delta E^*_{C_{Par1}Total} = \frac{C_{Par1}}{2} \cdot V^2_{DD} \cdot \frac{(n-1)}{n^2}$$

(2.32)

and

$$\Delta E^*_{C_{Par2}Total} = \frac{C_{Par2}}{2} .. V^2_{DD} .\frac{(n-1)}{n^2}$$

(2.33)

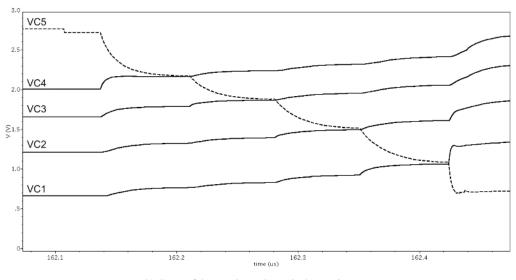

Figure 2.11 shows an example of 5 **Basic Capacitor Cells** ring rotation. In Sub-Figure 2.11(a) the output voltage waveform and the top plate of the five capacitors of the ring are shown. Then in Sub-Figure 2.11(b) a zoom of the process of rotation (see the time axis) shows how the voltage of the capacitor C5 go down pulling up the rest of the capacitors.

## 2.5. Energy Saved with Improved Rotation Technique

The energy saved with the technique can be computed comparing equations (2.29) and (2.31). In particular we can compare the contributions of  $C_{Par1}$  and  $C_{Par2}$  separately for each way of rotation. So we will see the expressions :

$$\frac{\Delta E^*_{C_{Par1}Total}}{\Delta E_{C_{Par1}Total}} = \frac{n-1}{n^2} \cdot \frac{n^2}{n^2 - 1} = \frac{1}{n+1}$$

(2.34)

and

$$\frac{\Delta E^*_{C_{Par2}Total}}{\Delta E_{C_{Par2}Total}} = \frac{n-1}{n^2} \cdot \left(\frac{n}{n-1}\right)^2 = \frac{1}{n-1}$$

(2.35)

The comparison is made in the table 2.1 as function of the number of capacitors of the ring (n). If we want to analyze the case of a five **Basic Capacitor Cells** converter,

(a) Output voltage and top plate voltages of the ring capacitors.

(b) Zoom of the top plate voltages in the rotation process.

Figure 2.11: Output and top plate voltages.

we must see the second row and it can be seen that the contribution of  $C_{Par1}$  decrease to 16,7% in comparison with the original mechanism of rotation. In the case of the  $C_{Par2}$  the contribution decrease to 25%. As  $C_{Par1}$  (having the NWell-Substrate diode parasitic capacitance) is much bigger than  $C_{Par2}$  the main contribution to the parasitic capacitances losses comes from  $C_{Par1}$ . Thus the total power consumption in the parasitic capacitances will be reduced to close to 17%.

| n | $\frac{1}{n+1}$ | $\frac{1}{n-1}$ |  |  |

|---|-----------------|-----------------|--|--|

| 4 | 0.200           | 0.333           |  |  |

| 5 | 0.167           | 0.250           |  |  |

| 6 | 0.143           | 0.200           |  |  |

| 7 | 0.125           | 0.167           |  |  |

Table 2.1: Comparison of the two implementations of the rotation

## 2.6. The Control Logic

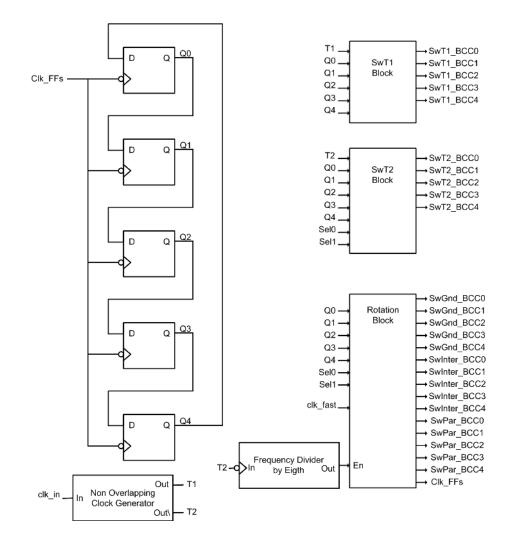

Figure 2.12 shows an schematic diagram of the logic used in the particular case of the designed converter. There is a "One Hot"<sup>8</sup> block that works as a pointer to the **Basic Capacitor Cell** in which the ring must be opened.

The block "Non Overlapping Clock Generator" generates from the main clock signal two non overlapped signals (T1 and T2) used to drive the gates of the switches SwT1 and SwT2.

The block "SwT1 Block" uses the signal T1 and the outputs of the different Flip Flops (Q0...Q4) to generate the five signals to drive the the gates of the switches SwT1. Basically it passes the signal T1 only to the **Basic Capacitor Cell** that is pointed by the "One Hot".

The block "SwT2 Block" uses the signal T2, the outputs of the different Flip Flops (Q0...Q4), and the signals Sel0 and Sel1 to generate the five signals to drive the gates of the switches SwT2. It works similar to the block "SwT1 Block" but passes the signal T2 only to the **Basic Capacitor Cell** that connects the ring to the output node. The signals Sel0 and Sel1 are used to select the conversion ratio as is shown in the table 2.2.

At last, the block "Rotation Block" implements the rotation of the ring. This happen when the block "Frequency Divider by Eight" enables the rotation. The signals  $SwPar_{BCC0}...SwPar_{BCC0}$  are used to drive the switches that implement the parasitic capacitances losses reduction technique. These switches are connected as a "star" to the top plates of the different capacitors of the ring. The block uses a secondary signal clock with a fourteen times faster frequency than the main clock one. The block implements the rotation as described in the section 2.4 in the following order:

1. Open the switch SwGnd that was closed and the switch SwInter that will remain open after end of the rotation.

<sup>&</sup>lt;sup>8</sup>A "One Hot block" is a ring of Flip Flops D that one of them has a one logic stored. Each clock edge the one logic is stored in the next Flip Flop of the ring.

| Sel1 | Sel0 | Conv.Ratio |

|------|------|------------|

| 0    | 0    | 1/5        |

| 0    | 1    | 2/5        |

| 1    | 0    | 3/5        |

| 1    | 1    | 4/5        |

Table 2.2: Conversion ratio selection.

- 2. Implement the technique of reduction of parasitic capacitances losses.

- 3. Close the switch SwInter that was opened before the start of the rotation process.

- 4. Close the switch SwGnd that will remain closed after the end of the rotation.

- 5. Generates a signal used to shift the "One Hot"

## 2.7. Chapter Summary

Basic ideas were first presented and then the first problem to solve, that is the inability to return the charge to the point where the load is connected. This problem was solved implementing a mechanism of rotation that basically consist in changing the position of all the capacitors of the converter systematically.

For implementing the converter and the rotation a switches configuration was defined for each capacitor of the ring. The basic set "capacitor-switches configuration" was named **Basic Capacitor Cell**.

Then the implementation of the capacitors was presented. After this a charge transfer analysis was made.

The calculation of the parasitic capacitances consumption was made and, as this consumption is the most significant power loss, a technique to reduce it was proposed. The consumption of the parasitic capacitances was calculated again for the case when this technique is applied. Both results were compared having as a result that the proposed technique has a significant decrease in the parasitic capacitances losses.

At last, a brief analysis of the logic implementation was presented.

Figure 2.12: Block diagram of control logic.

## CHAPTER 3

## Numerical Model

Electrical simulations of medium-complexity circuits have long simulation times and are not suitable for design space exploration. In these cases it is helpful to have a numerical model that allows us to explore the design space automatically and at reasonable times. This chapter shows the numerical model developed for the converter with the purpose of exploring the design space.

A very important feature of the developed model is that it allows the designer to perform a design space exploration of any technology with little work. All the designer needs are some curves extracted from electrical simulation and some parameters of the technology.

First, the chapter shows the general considerations for the model, then the development of the model for the two phases. Finally, it shows how losses were modeled. In the appendix A the matlab files tree and the way to introduce the information required for other technologies are presented.

### **3.1.** General Considerations for the Model

Since voltage-oriented models in circuits with non-linear capacitances can have cumulative errors as is described in [14], it is better to have a charge-oriented model, so this was the model used. Given that PMOS capacitors and switch resistances are nonlinear the model developed is non-linear.

As mentioned, we used a charge-oriented model so the state variables are the charge of the capacitors. There are n + 1 capacitors of which n make up the ring and the remaining one is  $C_L$ .

Figure 3.1 shows the converter for which the model was developed. Throughout this section a  $\frac{m}{n}$  conversion ratio is considered with 0 < m < n.

Equations used in the Matlab code are highlighted with double box.

#### 3.1.1. Non-linear Capacitors

The non-linearity of the model comes from the fact that every capacitor is composed by a linear capacitor (poly1-poly2) in parallel with a non-linear capacitor (PMOS). So the equation that describes this combined device is:

$$Q = Q_{Linear} + Q_{PMOS} = C_{poly} \cdot V + Q_{PMOS}(V)$$

(3.1)

Where  $Q_{PMOS}(V)$  is described with a curve extracted from electrical simulations, so equation (3.1) must be solved numerically.

#### 3.1.2. Switches Resistances

Resistance of CMOS switches are calculated from two curves(one for PMOS and one for NMOS transistors) extracted from electrical simulations. These curves have the resistance per width unit (in  $\Omega.\mu m$ )<sup>1</sup> as function of the source (drain) voltage. The gate voltage is supposed constant, equal to the supply voltage (2,8V) of the converter.

The curves were introduced in a matrix into a user defined function. This function, that uses linear interpolation needs the width of the transistor, the type of transistor ("n" or "p"), and source (drain) voltage. The function returns the resistance of the transistor.

To calculate the resistance of a complementary switch (one "n" transistor in parallel with a "p" transistor) it is necessary to calculate the two resistances separately and then calculate the parallel equivalent.

#### 3.1.3. Representation in the State Space

If  $\vec{Q}$  is the state vector composed by the charge of the n + 1 capacitors,  $V_{DD}$  is the source voltage and  $I_L$  the load current, equation 3.2 shows the general model for the converter. Function f is different for each phase (T1 and T2) so we will develop two different functions which we will call  $\vec{f}^{T1}$  and  $\vec{f}^{T2}$ .

$$\dot{\vec{Q}} = \begin{pmatrix} \dot{Q}_1 \\ \vdots \\ \dot{Q}_{m-1} \\ \dot{Q}_m \\ \dot{Q}_{m+1} \\ \vdots \\ \dot{Q}_n \\ \dot{Q}_L \end{pmatrix} = \begin{pmatrix} f_1(\vec{Q}, \vec{u}) \\ \vdots \\ f_{m-1}(\vec{Q}, \vec{u}) \\ f_m(\vec{Q}, \vec{u}) \\ f_m(\vec{Q}, \vec{u}) \\ \vdots \\ f_n(\vec{Q}, \vec{u}) \\ f_L(\vec{Q}, \vec{u}) \end{pmatrix} = \vec{f}(\vec{Q}, \vec{u})$$

(3.2)

With:

$$\overrightarrow{u} = (V_{DD}, I_L)$$

<sup>1</sup>As all switches were designed with minimum length the only geometrical parameter considered is the width.

Figure 3.1: N Basic Capacitor Cells Converter

To develop a numerical model we must make the following approximation:

$$\frac{\dot{\vec{Q}}}{\vec{Q}} \simeq \frac{\Delta \vec{Q}}{\Delta t} \tag{3.3}$$

Where  $\Delta t$  is a differential time. So if we want to solve the differential equation in each phase in NumSteps steps we have the following equations  $\Delta t = \frac{T1}{NumSteps}$  or  $\Delta t = \frac{T2}{NumSteps}$  that are equal in our case because  $T1 = T2 = \frac{T_{SW}}{2}$ .

$$\Delta \vec{Q} = \vec{Q}(t + \Delta t) - \vec{Q}(t) \tag{3.4}$$

So from equations (3.2), (3.3) and (3.4) we have that:

$$\overrightarrow{Q}(t + \Delta t) \simeq \overrightarrow{Q}(t) + \overrightarrow{f}(\overrightarrow{Q}, \overrightarrow{u}).\Delta t$$

Or for numerical models:

$$\overrightarrow{Q}(k+1) = \overrightarrow{Q}(k) + \overrightarrow{f}(\overrightarrow{V}(\overrightarrow{Q}(k)), u).\Delta t$$

With:

$$\vec{V}(\vec{Q}) = \begin{pmatrix} V_n(Q_1) \\ \vdots \\ V_{m+1}(Q_{m-1}) \\ V_m(Q_m) \\ V_{m-1}(Q_{m+1}) \\ \vdots \\ V_1(Q_n) \\ V_{C_L}(Q_{C_L}) \end{pmatrix}$$

Where  $V_k(Q_k) \quad \forall k = 1 : n \text{ and } V_{C_L}(Q_{C_L})$  means the dependence of the voltage of the capacitor with its own charge. The dependence of f with Q was written in this way because it is more convenient for the equations developed in next sections.

$$\begin{pmatrix} Q_{1}(k+1) \\ \vdots \\ Q_{m-1}(k+1) \\ Q_{m}(k+1) \\ Q_{m+1}(k+1) \\ \vdots \\ Q_{n}(k+1) \\ Q_{C_{L}}(k+1) \end{pmatrix} = \begin{pmatrix} Q_{1}(k) \\ \vdots \\ Q_{m-1}(k) \\ Q_{m}(k) \\ Q_{m+1}(k) \\ \vdots \\ Q_{n}(k) \\ Q_{C_{L}}(k) \end{pmatrix} + \begin{pmatrix} f_{1}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \\ \vdots \\ f_{m-1}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \\ f_{m}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \\ f_{m+1}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \\ \vdots \\ f_{n}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \\ f_{C_{L}}(\overrightarrow{V}(\overrightarrow{Q}(k)), \overrightarrow{u}) \end{pmatrix} \Delta t \quad (3.5)$$

The output for the two phases is given by:

$$V_{OUT} = V_{C_L}(Q_{C_L})$$

(3.6)

Here it is important to notice that despite in all the equations the supply voltage is considered as a parameter that can be changed, this change must take into account the data extracted from electrical simulations. In particular the switches resistances and the buffers consumption are extracted from electrical simulations for a particular supply voltage, so it is needed to make a different extraction for each supply voltage value. Look appendix A for more details.

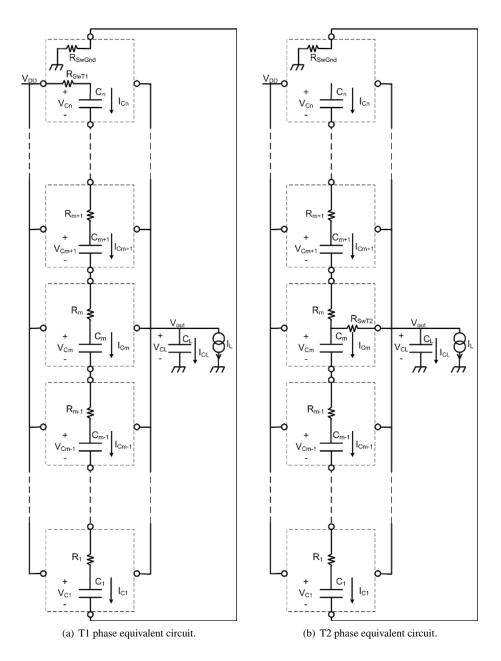

## **3.2.** Phase T1

The equivalent circuit for the phase T1 is shown in figure 3.2(a) so we have the next equations:

$$I_{Cn} = \ldots = I_{Cm+1} = I_{Cm} = I_{Cm-1} = \ldots = I_{C1} = \dot{Q}_k; \quad \forall k = 1:n$$

(3.7)

$$\dot{Q_{CL}} = I_{CL} = -I_L \tag{3.8}$$

$$V_{DD} = \sum_{r=1}^{n} V_{C_r}(Q_r) + \sum_{z=1}^{n-1} V_{R_z} + V_{R_{SwGnd}} + V_{R_{SwT1}}$$

(3.9)

If we make the following definition:

$$R_{T1} = \sum_{z=1}^{n-1} R_z + R_{SwGnd} + R_{SwT1}$$

(3.10)

From equations (3.7), (3.9), (3.10) and the Ohm law we have that:

$$V_{DD} = \sum_{r=1}^{n} V_{C_r}(Q_r) + R_{T1}.\dot{Q}_k; \quad \forall k = 1:n$$

(3.11)

So

$$\dot{Q}_k = \left[ V_{DD} - \sum_{r=1}^n V_{C_r}(Q_r) \right] \cdot \frac{1}{R_{T1}}; \quad \forall k = 1:n$$

(3.12)

Using equations (3.8) and (3.12) we have the function  $\overrightarrow{f}(\overrightarrow{Q}, \overrightarrow{u})$  in the phase T1:

$$\vec{f}^{T1}(\vec{Q},\vec{u}) = \begin{pmatrix} [V_{DD} - \sum_{r=1}^{n} V_{C_r}(Q_r)] \cdot \frac{1}{R_{T1}} \\ \vdots \\ [V_{DD} - \sum_{r=1}^{n} V_{C_r}(Q_r)] \cdot \frac{1}{R_{T1}} \\ [V_{DD} - \sum_{r=1}^{n} V_{C_r}(Q_r)] \cdot \frac{1}{R_{T1}} \\ [V_{DD} - \sum_{r=1}^{n} V_{C_r}(Q_r)] \cdot \frac{1}{R_{T1}} \\ \vdots \\ [V_{DD} - \sum_{r=1}^{n} V_{C_r}(Q_r)] \cdot \frac{1}{R_{T1}} \\ -I_L \end{pmatrix}$$

(3.13)

Therefore the equation to use in the numerical model during the phase T1 is:

$$\begin{bmatrix}

\begin{pmatrix}

Q_{1}^{T1}(k+1) \\

\vdots \\

Q_{m-1}^{T1}(k+1) \\

Q_{m-1}^{T1}(k+1) \\

Q_{m}^{T1}(k+1) \\

Q_{m+1}^{T1}(k+1) \\

\vdots \\

Q_{m+1}^{T1}(k+1) \\

Q_{m+1}^{T1}(k+1) \\

Q_{m+1}^{T1}(k) \\

Q_{m+$$

## **3.3.** Phase T2

The equivalent circuit for the phase T2 is shown in Figure 3.2(b) so we have the next equations:

$$I_{Cm} = I_{Cm-1} = \dots = I_{C1} = \dot{Q}_k; \quad \forall k = 1 : m$$

$$0 = I_{Cn} = \dots = I_{Cm+1} = \dot{Q}_k; \quad \forall k = m+1 : n$$

(3.15)

$$\dot{Q}_{CL} = I_{CL} = -(I_L + \dot{Q}_k); \quad \forall k = 1:m$$

(3.16)

$$V_{OUT} = \sum_{r=1}^{m} V_{C_r}(Q_r) + \sum_{z=1}^{m-1} V_{R_z} + V_{R_{SwGnd}} + V_{R_{SwT2}}$$

(3.17)

If now the make the following definition:

$$R_{T2} = \sum_{z=1}^{m-1} R_z + R_{SwGnd} + R_{SwT2}$$

(3.18)

From equations (3.6), (3.15), (3.17), (3.18) and the Ohm law we have that:

$$V_{C_L}(Q_{C_L}) = \sum_{r=1}^m V_{C_r}(Q_r) + R_{T2}.\dot{Q}_k; \quad \forall k = 1:m$$

(3.19)

and

$$\dot{Q}_k = \left[ V_{C_L}(Q_{C_L}) - \sum_{r=1}^m V_{C_r}(Q_r) \right] \cdot \frac{1}{R_{T2}} \quad \forall k = 1:m$$

(3.20)

So from equations (3.15) and (3.20) we have that

$$\dot{Q}_{k} = \begin{cases} \left[ V_{C_{L}}(Q_{C_{L}}) - \sum_{r=1}^{m} V_{C_{r}}(Q_{r}) \right] \cdot \frac{1}{R_{T2}} & \forall k = 1 : m \\ 0 & \forall k = m+1 : n \end{cases}$$

(3.21)

Then form equations (3.16) and (3.20):

Figure 3.2: N Basic Capacitor Cells ring circuits for numerical model

$$\dot{Q}_{CL} = \left[\sum_{r=1}^{m} V_{C_r}(Q_r) - V_{C_L}(Q_{C_L})\right] \cdot \frac{1}{R_{T2}} - I_L$$

(3.22)

Using equations (3.21) and (3.22) we have the function  $\overrightarrow{f}(\overrightarrow{Q}, \overrightarrow{u})$  in the phase T2:

$$\vec{f}^{T2}(\vec{Q},\vec{u}) = \begin{pmatrix} [V_{C_L}(Q_{C_L}) - \sum_{r=1}^m V_{C_r}(Q_r)] \cdot \frac{1}{R_{T2}} \\ \vdots \\ [V_{C_L}(Q_{C_L}) - \sum_{r=1}^m V_{C_r}(Q_r)] \cdot \frac{1}{R_{T2}} \\ [V_{C_L}(Q_{C_L}) - \sum_{r=1}^m V_{C_r}(Q_r)] \cdot \frac{1}{R_{T2}} \\ 0 \\ \vdots \\ 0 \\ [\sum_{r=1}^m V_{C_r}(Q_r) - V_{C_L}(Q_{C_L})] \cdot \frac{1}{R_{T2}} - I_L \end{pmatrix}$$

(3.23)

Then

$$\begin{pmatrix} Q_{1}^{T2}(k+1) \\ \vdots \\ Q_{m-1}^{T2}(k+1) \\ Q_{m-1}^{T2}(k+1) \\ Q_{m+1}^{T2}(k+1) \\ Q_{m+1}^{T2}(k+1) \\ \vdots \\ Q_{m+1}^{T2}(k+1) \\ \vdots \\ Q_{m+1}^{T2}(k+1) \\ Q_{m+1}^{T2}(k+1) \\ \vdots \\ Q_{m+1}^{T2}(k+1) \\ Q_{m+1}^{T2}(k) \\ Q_{m+1}^{T2$$

## 3.4. Energy Losses

There are essentially four types of energy losses that were presented in section 1.2. This section describes them and shows how they were estimated.

#### 3.4.1. Parasitic Capacitances Losses

As derived in section 2.4, the equation (2.31) describes the losses in charging and discharging the parasitic capacitances. So this one is the equation used.

#### 3.4.2. Gate-drive Losses

To calculate Gate-drive losses two curves extracted from electrical simulations were used, one for "n" transistors and the second one for "p" transistors. These curves have the switching losses per width unit (in  $Jouls/\mu m$ )<sup>2</sup> as function of the source

$<sup>^{2}</sup>$ As all switches were designed with minimum length the only geometrical parameter considered is the width.

(drain) voltage.

The curves were introduced in a matrix into a user defined function. This function needs the width of the transistors of the switch (the "n" and the "p") and source (drain) voltage. It returns the energy consumed in a on-off cycle of the switch.

#### 3.4.3. Conduction Losses

There are two equivalent resistors (see equations (3.10) and (3.18)) that dissipate energy, each one associated with one phase of the converter. As the equations (3.14)and (3.24) were solved step by step, the resistance was calculated in every step to take into account its dependence on system state. So to calculate the dissipated energy we must use for each step the equation:

$$\Delta E_{R_{Ti}}(k) = R_{Ti}(k).i_{R_{Ti}}^2(k).\Delta t \quad i = 1:2$$

(3.25)

Then, the energy dissipated in one period of switching (T1 + T2) is:

$$E_{ResLoss}^{T1+T2} = \sum_{k=i}^{NumSteps} \left( R_{T1}(k).i_{R_{T1}}^2(k).\Delta t \right) + \sum_{k=i}^{NumSteps} \left( R_{T2}(k).i_{R_{T2}}^2(k).\Delta t \right)$$

(3.26)

#### 3.4.4. Digital and Analog Control Circuits Losses

The Digital Circuits losses are considered in two different ways. The first one is the logic consumption that is needed to implemente the two phases of the converter. The second one is the logic consumption to implement the rotation process. It is needed to have these two values to calculate the performance of the circuit.

After each execution of the phases T1 and T2 the logic consumption used to implement these phases is added in a variable that accumulate the total logic losses. The same happens when a rotation is performed with the logic consumption used to implement the rotation.

As mentioned in the introduction, analog circuit losses are considered into the logic losses. The bias current considered is 100nA so the energy si calculated as:

$$E_{Analog} = V_{DD}.I_{BIAS}.(t_f - t_i) \tag{3.27}$$

Where  $I_{BIAS}$  is the total bias current of the analog circuits, and  $t_i$  and  $t_f$  are the initial and final time where the power was integrated.

## 3.5. How the Model Works

For the model we have two kind of magnitudes: those associated to the dynamic of charging and discharging capacitors that have variation with continuous time, and those associated to events such as closing and opening switches that are associated to discrete times. This section describe all the considered magnitudes and shows how the model integrates them to calculate the performance of the circuit. It exists in the model the possibility to calculate the performance in steady state or including the transient.

#### **3.5.1.** Magnitudes That Change With Each Time Step

#### Charge