| AD-A087 041<br>UNCLASSIFIED | MODULAR DIGI                                | BEDFORD MA M<br>Tal Missile G<br>Langley, J De | ISSILE<br>UIDANCE | .(U)<br>≠ F MAR | DIV | N0001 | F/G 17,<br>-0549<br>NL | 7 |  |

|-----------------------------|---------------------------------------------|------------------------------------------------|-------------------|-----------------|-----|-------|------------------------|---|--|

| L or 2<br>Ac<br>Art c       | 240<br>•••••••••••••••••••••••••••••••••••• |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     |       |                        |   |  |

|                             |                                             |                                                |                   |                 |     | 1     | <br>                   |   |  |

ADA 08704

くく

# OFFICE OF

#### MODULAR DIGITAL MISSILE GUIDANCE

RESEA

Phase VI Final Report

FRANK J. LANGLEY

JOHN DEMETRICK

#### FRANK S. MARCHILENA

Raytheon Company Missile Systems Division Bedford, MA 01730

Contract N00014-75-C-0549 ONR Task 233-052

30 JANUARY 1980

Technical Report for Period 1 Jan. 79 - 31 Oct. 79 Approved for Public Release; Distribution Unlimited

30

136

DOC FILE COPY

PREPARED FOR THE

OFFICE OF NAVAL RESEARCH GOOD N. QUINCY ST. GARLINGTON GVA G 22217

80 6

#### NOTICES

#### Change of Address

Organizations receiving reports on the initial distribution list should confirm correct address. This list is located at the end of the report. Any change of address or distribution should be conveyed to the Office of Naval Research, Code 200, Washington, D.C. 22217.

U

U

#### Disposition

When this report is no longer needed, it may be transmitted to other authorized organizations. Do not return it to the originator or the monitoring office.

#### Disclaimer

The findings in this report are not to be construed as an official Department of Defense or Military Department position unless so designated by other official documents.

#### Reproduction

Reproduction in whole or in part is permitted for any purpose of the United States Government.

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) READ INSTRUCTIONS BEFORE COMPLETING FORM 19 **REPORT DOCUMENTATION PAGE** 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER NUMBER A087 041 ONR\CR233-052-6 5. TYPE OF REPORT & PERIOD COVERED TITLE (and Subtitle) Final Report Modular Digital Missile Guidance 1/1/79 to 10/31/79 PERFORMING ORG. REPORT NUMBER BR-11856 AUTHOR(S) NG0014-75-C-0549 Frank J./Langley, John/Demetrick 15 V Frank Marchilena PERFORMING ORGANIZATION NAME AND ADDRESS PROGRAM ELEMENT PROJECT, TASK AREA & WORK UNIT NUMBERS Raytheon Company Missile Systems Division 2 Bedford, MA. 01730 REPORT DAT 11 CONTROLLING OFFICE NAME AND ADDRESS 39 Jane Office of Naval Research Code 200 NUMBER O 154 Arlington, Virginia 22217 15. SECURITY CLASS. (of this report) A MONITORING AGENCY NAME & ADDRESS(it different from Controlling Office) UNCLASSIFIED 154. DECLASSIFICATION DOWNGRADING SCHEDULE 16 DISTRIBUTION STATEMENT (of this Report) Approved for public release; distribution unlimited DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Report) SUPPL-SME 18 KEY WORDS (Continue on reverse aide if necessary and identify by block number) Missile Guidance and Control Microcomputer Modular Systems Multi-processor Modular Software ABSTRACT Continue on reverse side If necessary and identify by block number) Higher throughput general-purpose processors have traditionally been the domain of Schottky-bipolar or CMOS-SOS integrated circuit technology with attendant multi-component packaging logistics and support software problems. In addition, the modular operational software has proven difficult to achieve in practice. To combat these deficiencies, a super-federated DD FORM 1473 EDITION OF 1 NOV 55 IS OBSOLETE UNCLASSIFIED SECURITY CLASSIFICATION OF THIS FA

## ECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

high-speed, multi-processor architecture has been explored using standard industry 16-bit microprocessors. The resulting design evolved in this study employs a time-phased ring approach to high throughput with single processor programming simplicity. Further, modular software has been achieved by assigning one microcomputer to each major algorithm.

#### UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE/When Data Entered)

0

Π

## PREFACE

This technical report covers the work performed under Contract No. N00014-75-C-0549 from 1 January through 31 October 1979.

The purpose of this contract together with the work performed in the previous phases, was to provide the means of achieving improved performance, modularity and flexibility in the design of next generation microcomputer-based missile guidance and control systems.

LCDR. W. Savage, Office of Naval Research Arlington, VA, was the Navy LCDR Scientific Officer.

Mr. F.J. Langley was the Principal Investigator for Raytheon, Mr. J. Demetrick was the Hardware Design Engineer and Mr. F.S. Marchilena the Software Design Engineer.

Publication of this report does not constitute Navy approval of the report's findings or conclusions. It is published only for the exchange and stimulation of ideas.

E

l

| ACCESSION for                       |                    |

|-------------------------------------|--------------------|

| NTIS                                | White Section      |

| DDC                                 | Butf Section       |

| UNANNOUNCED                         |                    |

| JUSTI: ICATION                      |                    |

| BY<br>DISTRIBUTION//<br>Dist. AVAIL | NYATLABILITY CODES |

UNCLASSIFIED

I

Ī.

1

## TABLE OF CONTENTS

| 1. | INTROD | OCTION                                                    |

|----|--------|-----------------------------------------------------------|

|    | 1.1    | Background                                                |

|    | 1.2    | Objectives and Scope                                      |

|    | 1.3    | Publications and Presentations                            |

|    |        |                                                           |

| 2. | SUMMAR | Y AND CONCLUSIONS                                         |

|    | 2.1    | Conclusions                                               |

|    |        |                                                           |

| 3. | DIGITA | L MISSILE GUIDANCE AND CONTROL                            |

|    | 3.1    | Motivations for Federated and Super-Federated Systems 3-1 |

|    |        | 3.1.1 Hardware                                            |

|    |        | 3.1.2 Software                                            |

|    |        | 3.1.3 Throughput                                          |

|    | 3.2    | Defining/Identifying System Structures                    |

|    |        | 3.2.1 System Timing Considerations                        |

|    |        | 3.2.2 System Parallelism                                  |

|    |        | 3.2.3 Macro-Structure System                              |

|    |        | 3.2.4 Super-Federated Systems                             |

|    | 3.3    | Microcomputer Modularity                                  |

|    |        | 3.3.1 Programmable Microbus Interface Module 3-17         |

|    |        | 3.3.2 Spectrum Analyzer Module                            |

|    |        | 3.3.3 Serial-Digital Input-Output (SDIO) Module 3-18      |

|    | 3.4    | Navy Demonstration System                                 |

|    | 3.5    | Summary                                                   |

|    |        |                                                           |

| 4. | CLASSI | C MULTIPROCESSOR ARCHITECTURES                            |

|    | 4.1    | Multiprocessor and Computer Systems                       |

|    |        | 4.1.1 Single Time-Shared Bus                              |

|    |        | 4.1.2 Multiple Bus                                        |

|    |        | 4.1.3 Cross-Point Switch                                  |

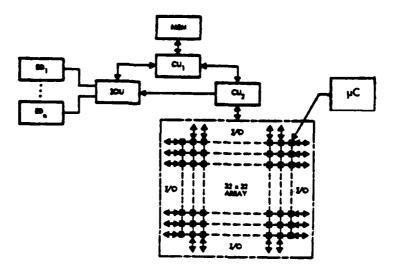

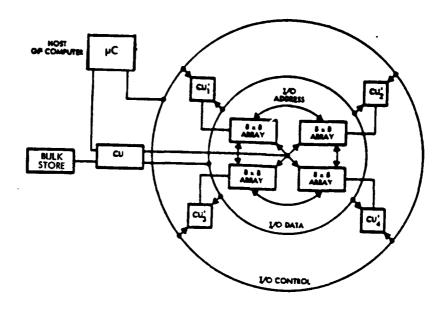

|    |        | 4.1.4 Array Processor Systems                             |

|    |        | iv                                                        |

|    |        | UNCLASSIFIED                                              |

|    |        |                                                           |

#### TABLE OF CONTENTS (Cont.)

I

L

l

Ŀ

l, ₹.

|    |                                                          | 766 |

|----|----------------------------------------------------------|-----|

|    | 4.1.5 Associative Processor Systems                      | -11 |

|    | 4.1.6 "Hybrid" Processor Systems 4                       | -12 |

|    | 4.1.7 FFT Processor Architectures 4                      | -14 |

|    | 4.1.8 Conclusions                                        | -15 |

| 5. | SUPER-FEDERATED MICROCOMPUTER SYSTEM (SFMCS)             | -1  |

|    | 5.1 Modifying/Optimizing the Single-Bus Multiprocessor - |     |

|    | Architecture                                             | -1  |

|    | 5.1.1 Memory Mapping and Single Computer                 |     |

|    | Programmability                                          | -2  |

|    | 5.1.2 High Throughput Refinements                        | -3  |

|    | 5.1.3 Time-Phased Ring, Practical Case 5                 | -5  |

| ·  | 5.2 Expanded System Architecture                         | -6  |

|    | 5.3 Physically Distributed Systems                       | -7  |

| 6. | SFMCS SOFTWARE                                           | -1  |

|    | 6.1 Distribution of Programs and Data 6                  | -2  |

|    | 6.2 Modular Software                                     | -5  |

|    | 6.2.1 Table Driven Software Modules 6                    | -7  |

|    | 6.2.2 Composition of Software Modules 6                  | -8  |

|    | 6.3 SFMCS Control Software                               | -10 |

|    | 6.3.1 Master/Slave                                       | -10 |

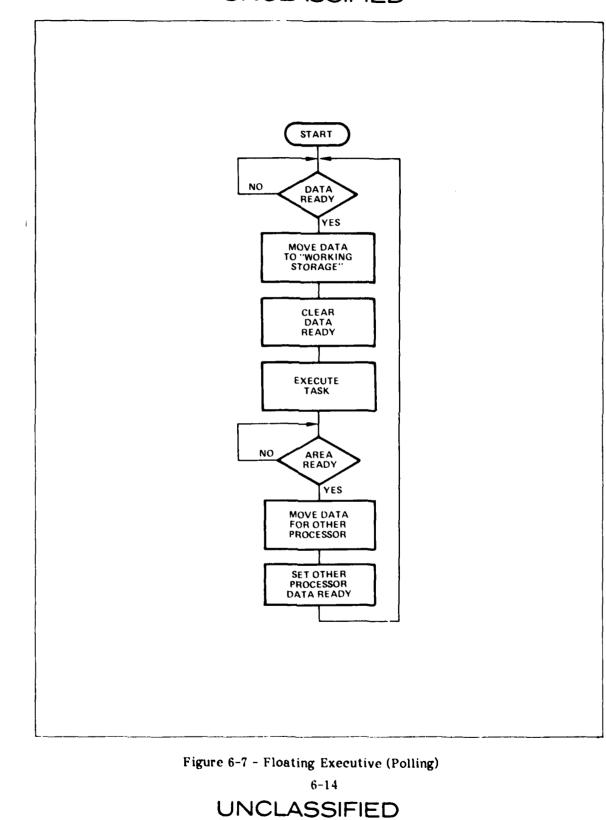

|    | 6.3.2 Floating Executive (Polling) 6                     | -13 |

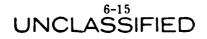

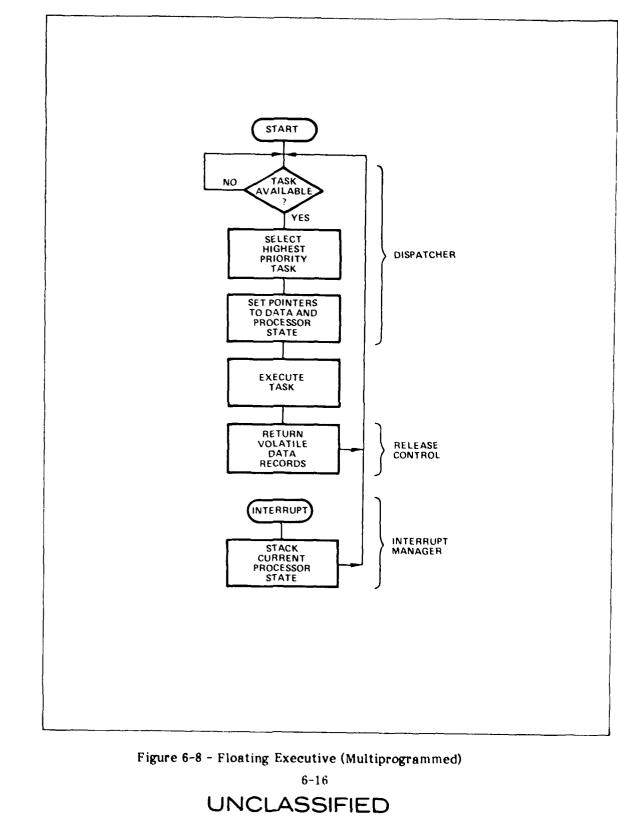

|    | 6.3.3 Floating Executive (Multiprogrammed) 6             | -15 |

|    | 6.4 High Order Language/Advanced Software Tools 6        | -19 |

| 7. | SFNCS SIMULATION MODELING (Expanded System)              | -1  |

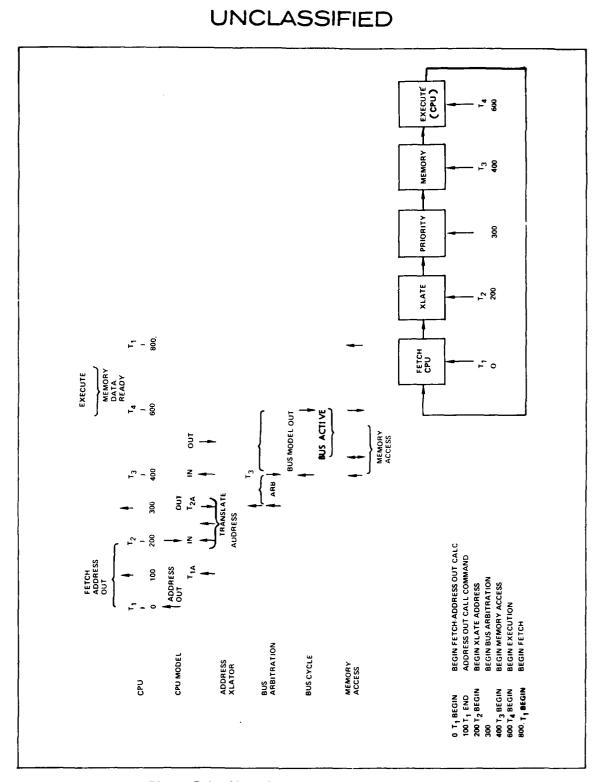

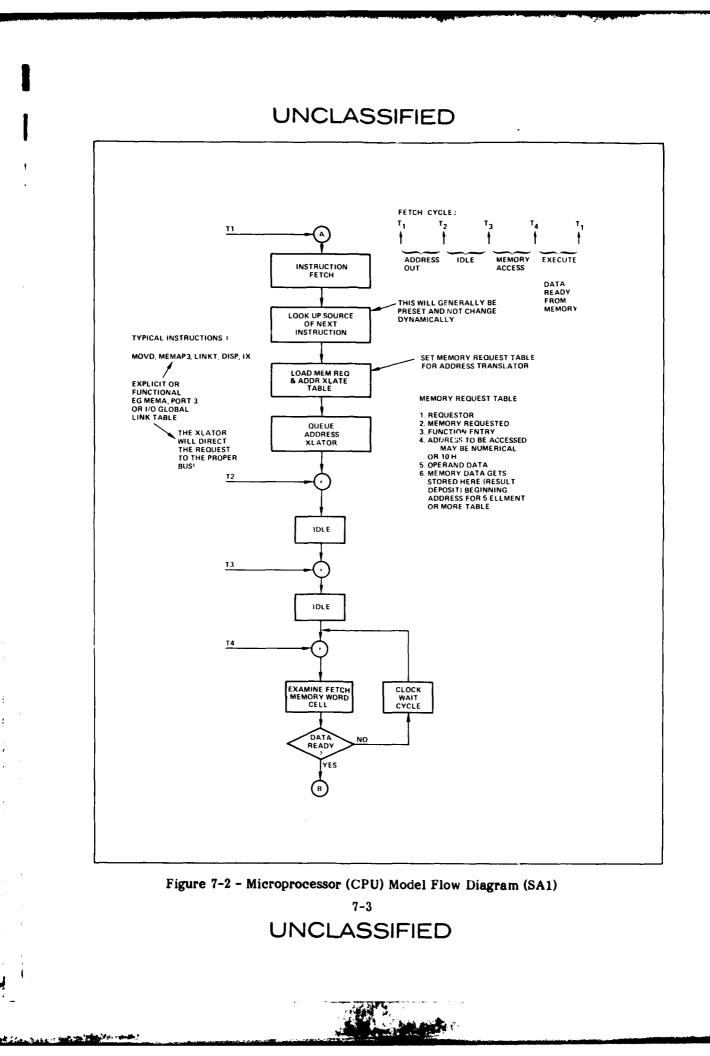

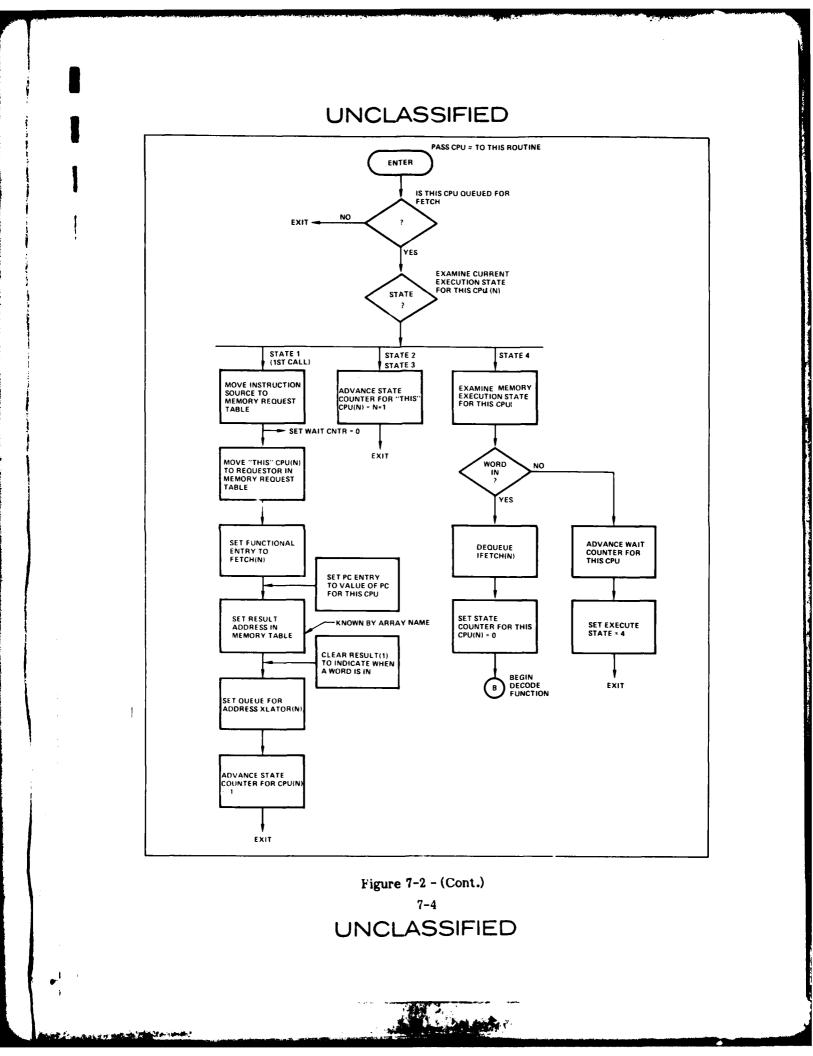

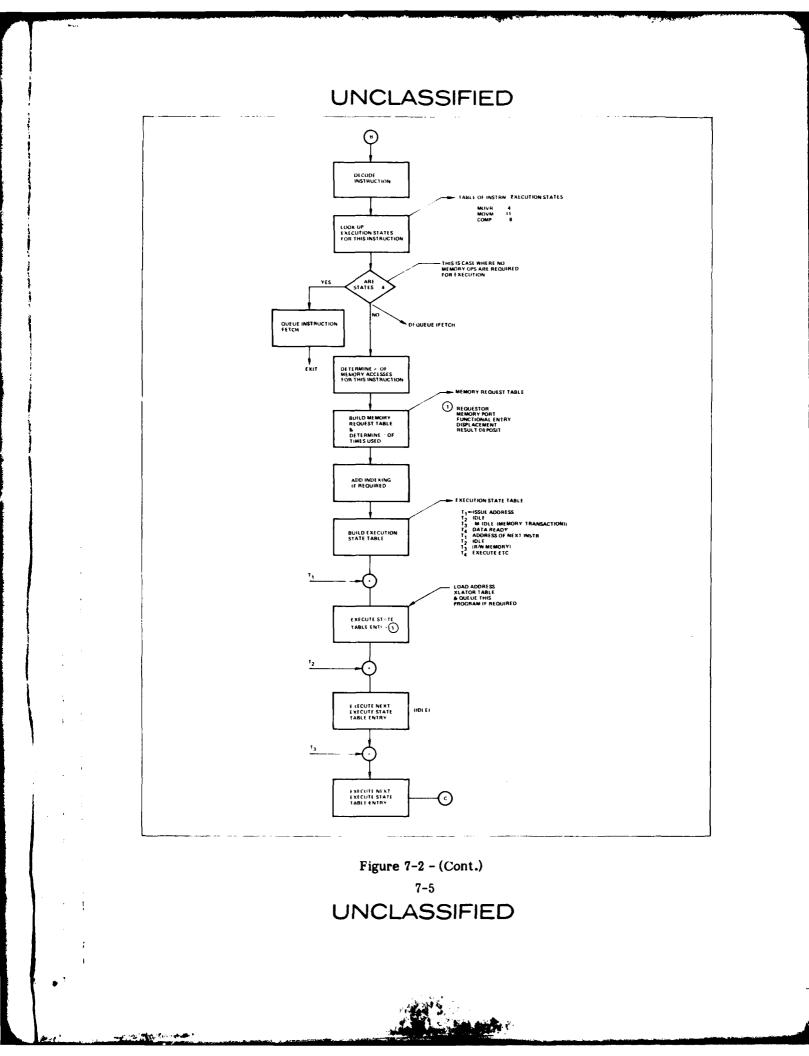

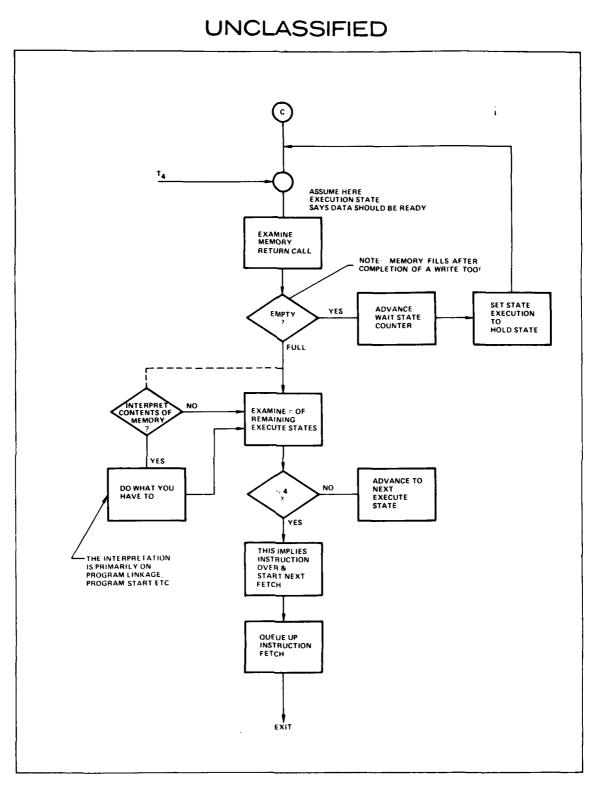

|    | 7.1 Microprocessor/CPU Model                             | -1  |

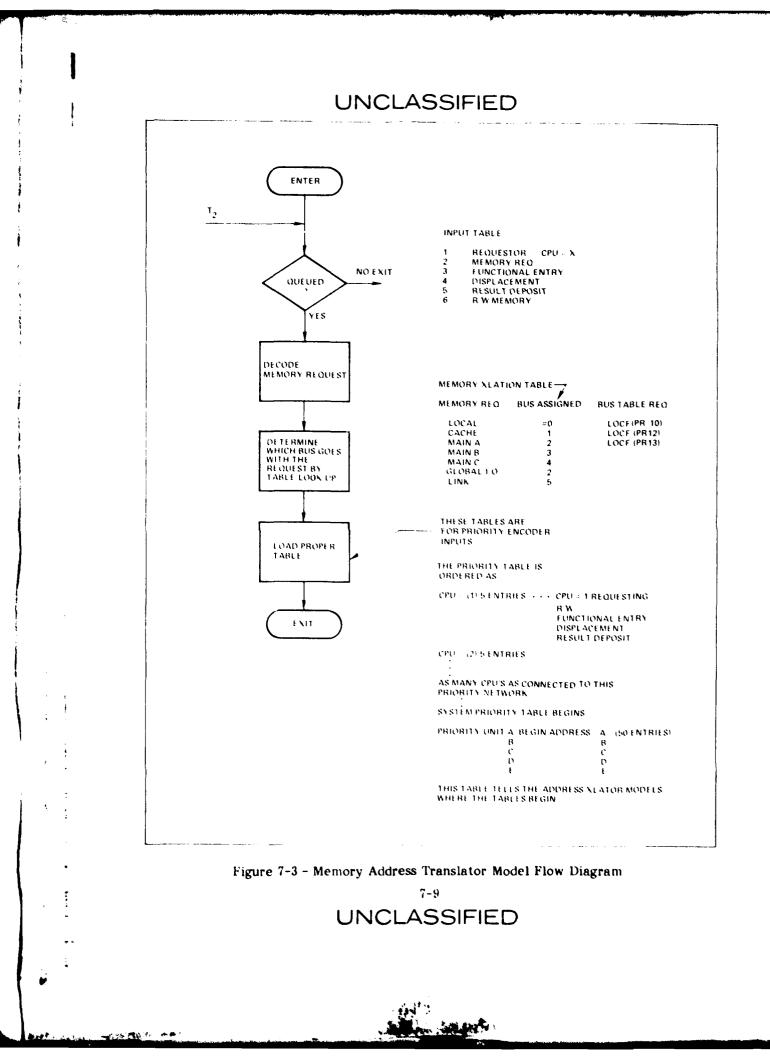

|    | 7.2 Address Translation Model                            | -8  |

UNCLASSIFIED

I

· •

## TABLE OF CONTENTS (Cont.)

|            |                                                     | age |

|------------|-----------------------------------------------------|-----|

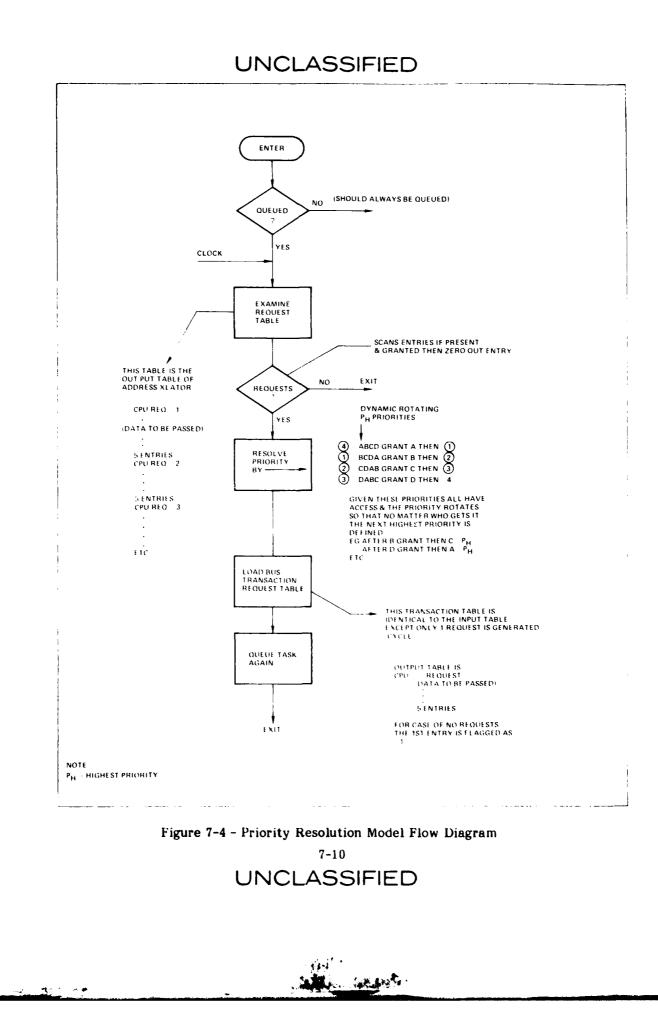

| 7.3        | Priority Resolution (Bus Access)                    | -8  |

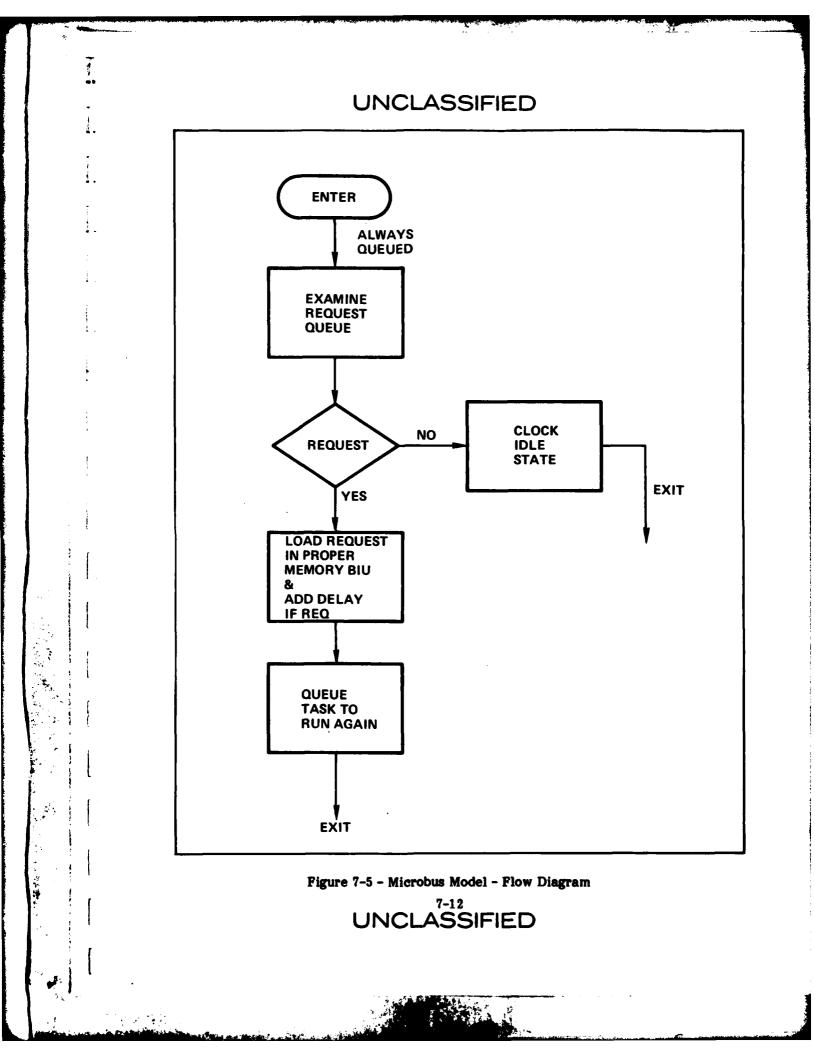

| 7.4        | Microbus Model                                      | -11 |

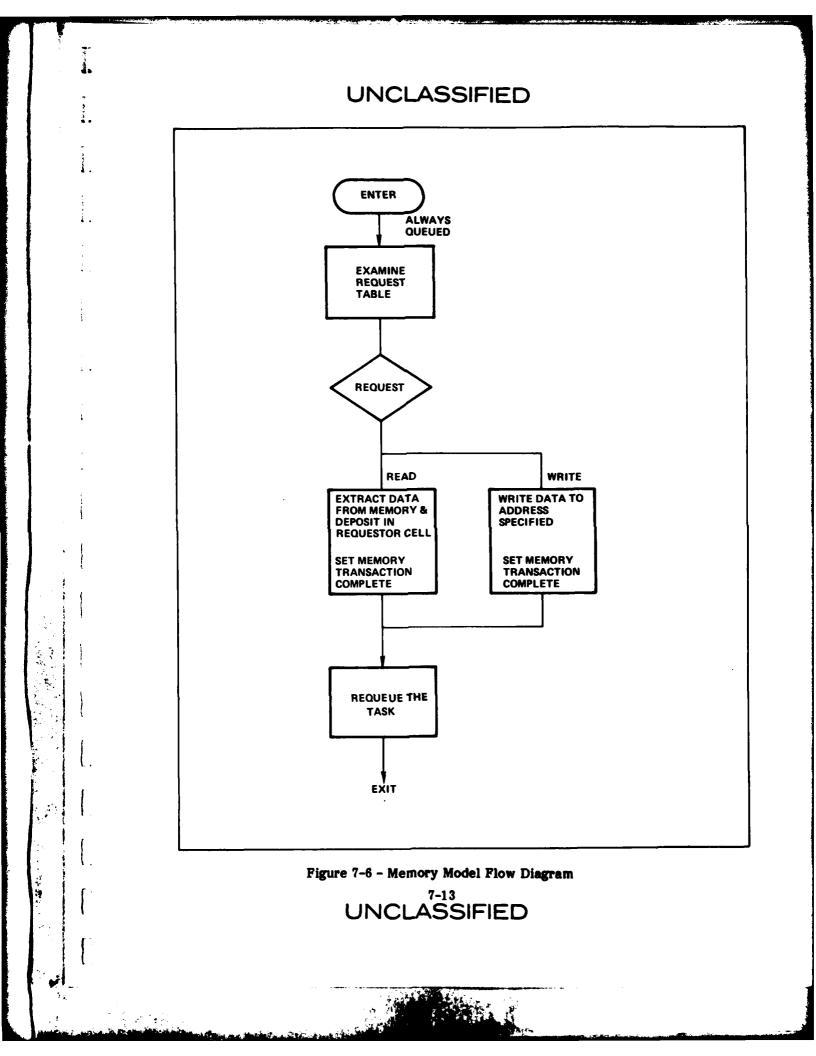

| 7.5        | Memory Model                                        | -11 |

| 8. REPERE  | INCES                                               | -1  |

| APPENDIX A | Super-Federated Microcomputer System (SFMCS) Timing |     |

|            | and Throughput Analysis                             | -1  |

| APPENDIX E | 3 Real-Time Missile Simulation with SFMCS           | -1  |

| APPENDIX ( | C SFMCS Functional Block Diagrams                   | -1  |

## LIST OF ILLUSTRATIONS

I

Ì.

Ì.

3

1.

ŧ,

| Figure | Page                                                        |

|--------|-------------------------------------------------------------|

| 1-1    | Generic Missile Classes                                     |

| 3-1    | Single versus Federated Missile Guidance and                |

|        | Control Systems                                             |

| 3-2    | Modular Hierarchical Software Control Structure for Single  |

|        | Computer Missile Guidance and Control System                |

| 3-3    | Single Computer System Software is Inaccessible to          |

|        | Subsystem Designers                                         |

| 3-4    | Single Computer System General-Purpose Throughput           |

|        | Requirements                                                |

| 3-5    | Missile Guidance and Control System - Functional Block      |

|        | Diagram                                                     |

| 3-6    | Digital System Timing Considerations                        |

| 3-7    | System Partitioning by Control Channel                      |

| 3-8    | Macro-Structure Partitioning                                |

| 3-9    | Macro-Structure Control Hierarchy                           |

| 3-10   | Microcomputer Throughput Requirements for Macro-Structured  |

|        | System                                                      |

| 3-11   | Super-Federated Subsystem Processing, Target Seeker and     |

|        | Autopilot                                                   |

| 3-12   | Software Change by Hardware Substitution in Super-Federated |

|        | Systems                                                     |

| 3-13   | Modular Federated Microcomputer Missile Guidance and        |

|        | Control System                                              |

| 3-14   | Radar Signal Processing Throughput Requirements 3-18        |

| 3-15   | Fiber-Optic Ring Communications Between Missile             |

|        | Subsystems                                                  |

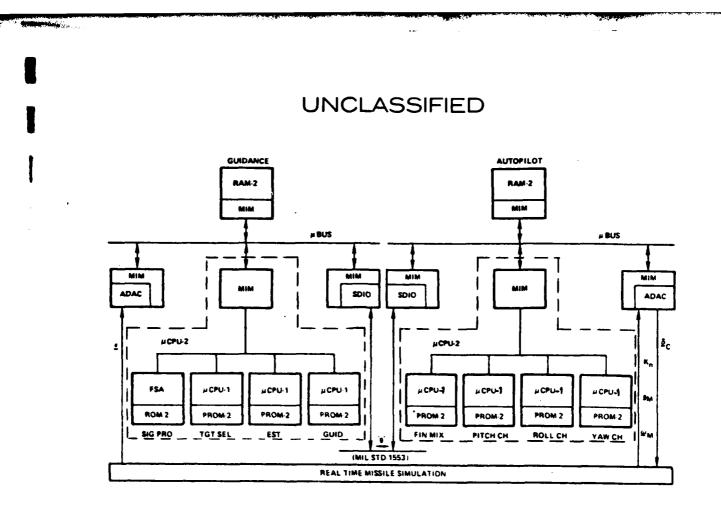

| 3-16   | Navy/Raytheon Hardware-in-the-Loop Federated µC System for  |

|        | Missile Performance Simulation                              |

| 3-17   | Federated Microcomputer Macromodules Using MIM              |

|        | Interface                                                   |

vii

#### LIST OF ILLUSTRATIONS (Cont.)

Ţ

| 3-18 Super-Federated Microcomputer System for Higher Performance   | 9-22       |

|--------------------------------------------------------------------|------------|

| Mignile Cuidence and Control                                       | 8-22       |

| Missile Guidance and Control                                       |            |

| 4-1 Multiprocessor System - Single Time-Shared Memory              |            |

| Access Bus                                                         | -3         |

| 4-2 Multicomputer System - Single Time-Shared Communications       |            |

| Bus                                                                | I-3        |

| 4-3 Multicomputer System - Fiber-Optic Round-Robin                 |            |

| Serial-Digital I/O                                                 | -4         |

| 4-4 Multiprocessor System ~ Multiple Memory Access Bus 4           | -5         |

| 4-5 Multicomputer System - Multiple I/O Communications             |            |

| Bus                                                                | -6         |

| 4-6 High-Availability Multiprocessor System - Cross-Point          |            |

| Switch Communications                                              | -6         |

| 4-7 Multicomputer System - Cross-Point Switch I/O                  |            |

| Communications                                                     | -7         |

| 4-8 Tactical Multimicrocomputer System - Serial Cross-Point Switch | - /        |

| I/O Communications                                                 |            |

|                                                                    |            |

|                                                                    | -9         |

| · · · · · · · · · · · · · · · · · · ·                              | -10        |

| 4-11 Array Microprocessor System - Single External                 |            |

|                                                                    | -10        |

| 4-12 Associative Processor System                                  | -11        |

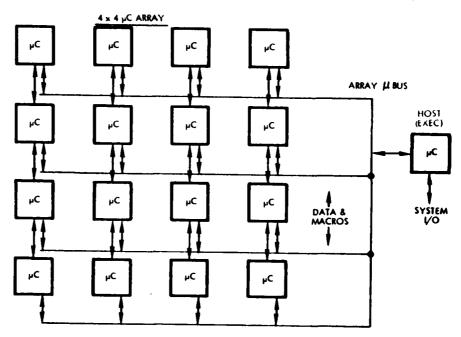

| 4-13 "Hybrid" Processor Systems - Dual Bus                         | -12        |

| 4-14 "Hybrid" Processor Systems Multiple-Bus                       |            |

| Integrated Ensemble, (Original Navy AADC)                          | -14        |

| 4-15 FFT Processor Architectures                                   | -15        |

| 5-1 Single Time-Shared Bus Multi-Microprocessor - Separate         |            |

| Program Memories                                                   | 5-1        |

| 5-2 Super-Federated Multiprocessor-Memory Mapping Class III        |            |

| Seeker Processing                                                  | <u>i-2</u> |

viii

UNCLASSIFIED

## LIST OF ILLUSTRATIONS (Cont.)

I

1.

6 (1) S

1

| Figure      |                                                              | Page |

|-------------|--------------------------------------------------------------|------|

| 5-3         | Super Federated Multiprocessor-Extended Memory-Mapping       |      |

|             | For Host Processor                                           | 5-3  |

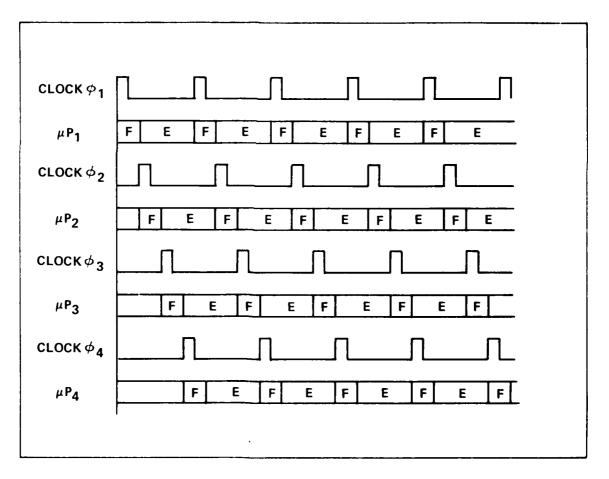

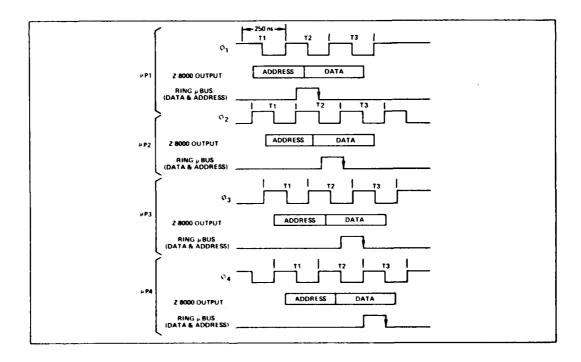

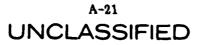

| 5-4         | Time-Phased Ring Bus Memory/Instruction Fetch (F) and        |      |

|             | Execute (E) Sequences Four Microprocessors Identical         |      |

|             | Instruction Streams                                          | 5-4  |

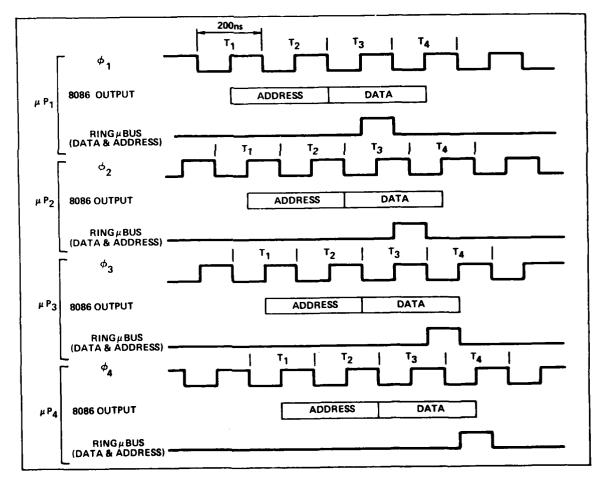

| 5-5         | Time-Phased Ring Bus Intel 8086 Timing Compatibility         | 5-5  |

| 5-6         | Time-Phased Ring Bus - Zilog Z-8000 Timing                   |      |

|             | Compatibility                                                | 5-6  |

| 5-7         | Expanded Super-Federated Microcomputer System For Physically |      |

|             | Centralized Applications                                     | 5-7  |

| 5-8         | Physically Distributed Super-Federated Microcomputer         |      |

|             | System                                                       | 5-8  |

| 5 <b>-9</b> | Low-Performance Federated Microcomputer Missile Guidance     |      |

|             | and Control System (NSWC System)                             | 5-9  |

| 5-10        | High-Performance Super-Federated Microcomputer System For    |      |

|             | Higher Performance Missile Guidance and Control              |      |

|             | (NSWC System)                                                | 5-10 |

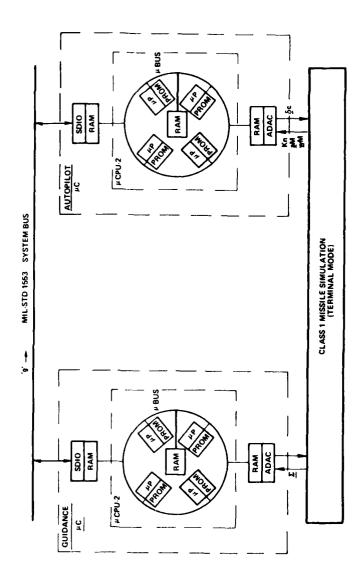

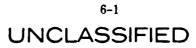

| 6-1         | Typical Serial Process                                       | 6-3  |

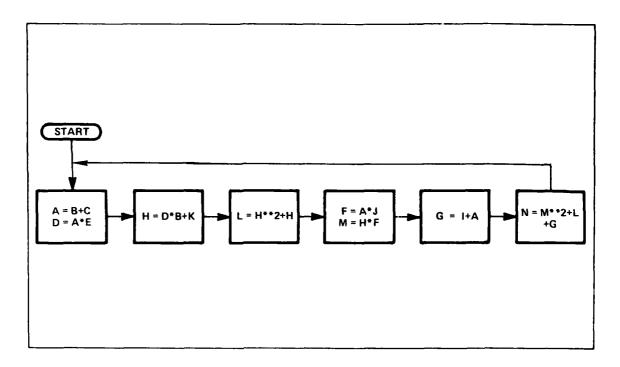

| 6-2         | Distribution of Figure 6-1 Statements                        | 6-4  |

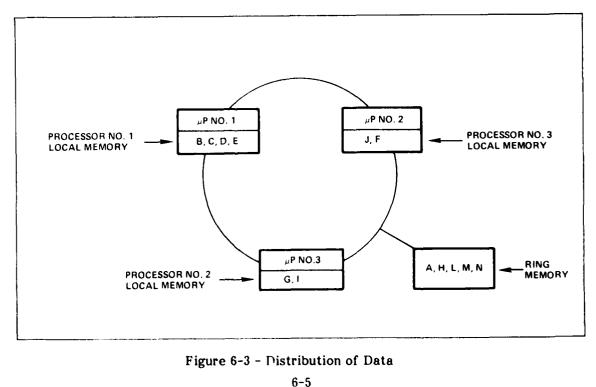

| 6-3         | Distribution of Data                                         | 6-5  |

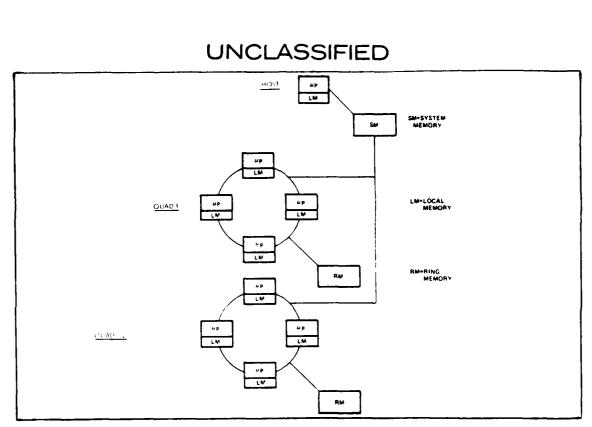

| 6-4         | SFMCS, Host and Dual-Quad Configuration                      | 6-11 |

| 6-5         | Master/Slave (Polling)                                       | 6-12 |

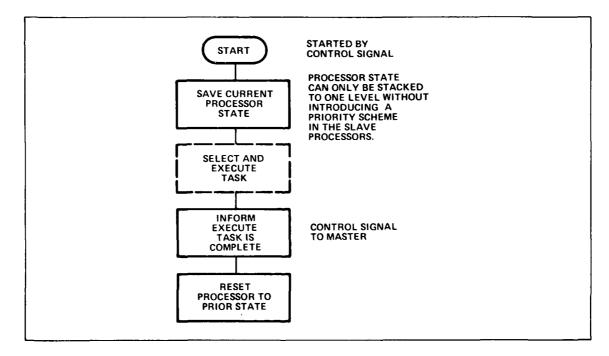

| 6-6         | Master/Slave (Control Signal)                                | 6-12 |

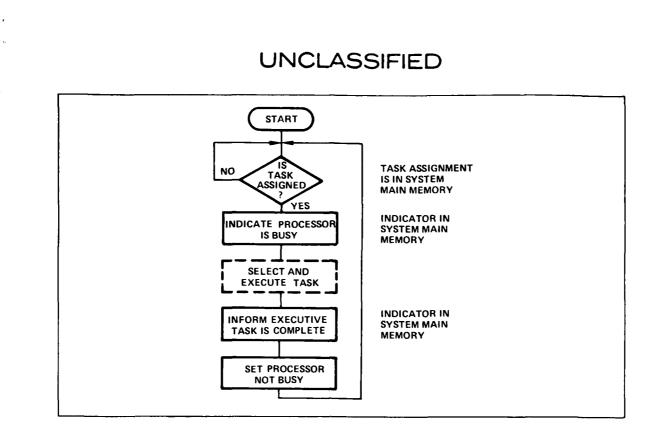

| 6-7         | Floating Executive (Polling)                                 | 6-14 |

| 6-8         | Floating Executive (Multiprogrammed)                         | 6-16 |

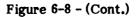

| 7-1         | SFMCS Major Elements and Timing                              | 7-2  |

| 7-2         | Microprocessor (CPU) Model Flow Diagram                      | 7-3  |

| 7-3         | Memory Address Translator Model Flow Diagram                 | 7-9  |

| 7-4         | Priority Resolution Model Flow Diagram                       | 7-10 |

| 7-5         | Microbus Model - Flow Diagram                                | 7-12 |

| 7-6         | Memory Model Flow Diagram                                    | 7-13 |

|             |                                                              |      |

#### LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                         | Page         |

|--------|---------------------------------------------------------|--------------|

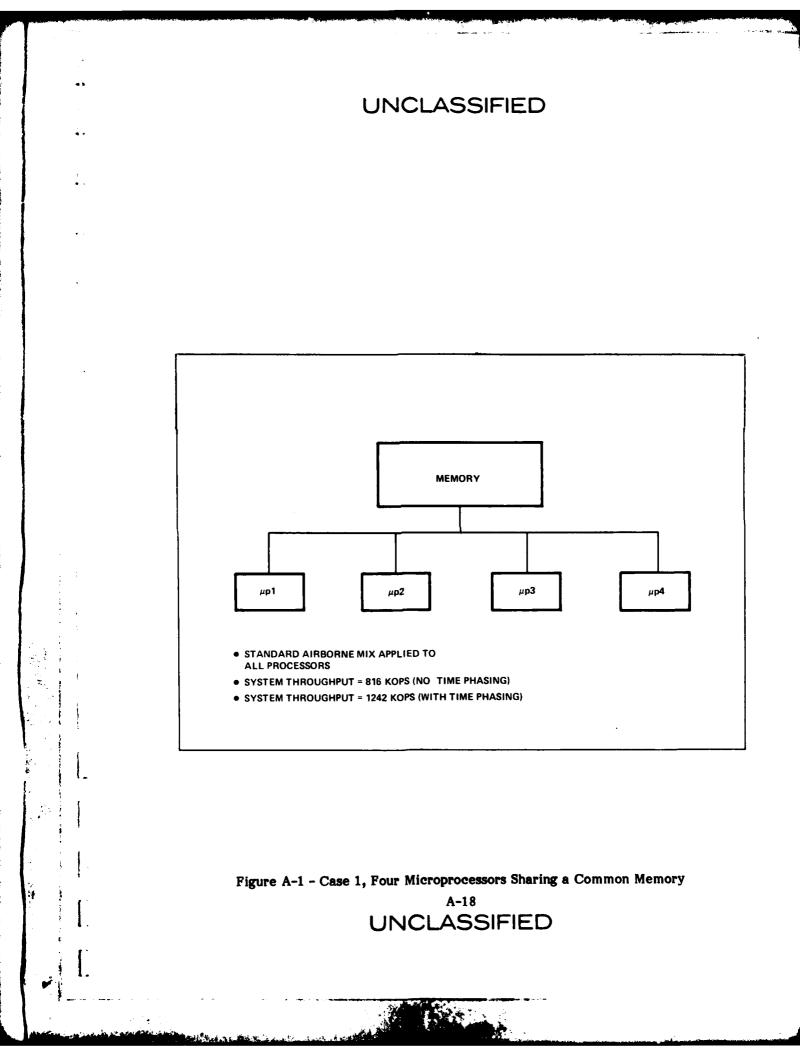

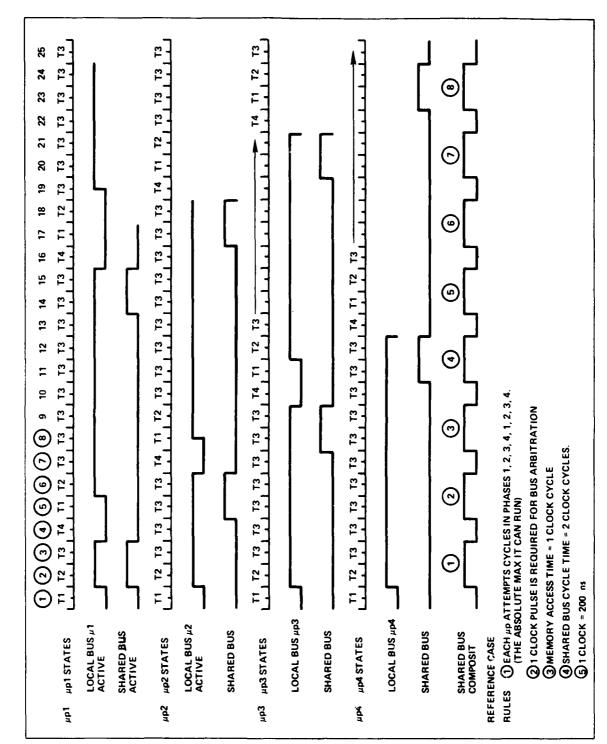

| A-1    | Case 1, Four Microprocessors Sharing a Common Memory    | <b>A-18</b>  |

| A-2    | Case 1, Four Processors with Shared Memory,             |              |

|        | No Time Phasing                                         | A-19         |

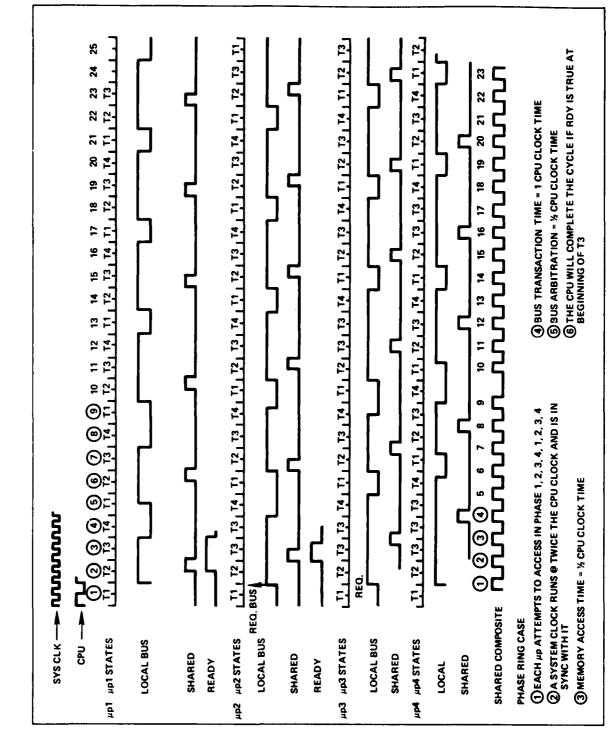

| A-3    | Case 2, Four Processors with Shared Memory              |              |

|        | using Time-Phased Ring Technique                        | A-22         |

| A-4    | Case 3, Four Processors with Dedicated Program Memories |              |

|        | and Shared Data Memory Without Time Phasing             | A-24         |

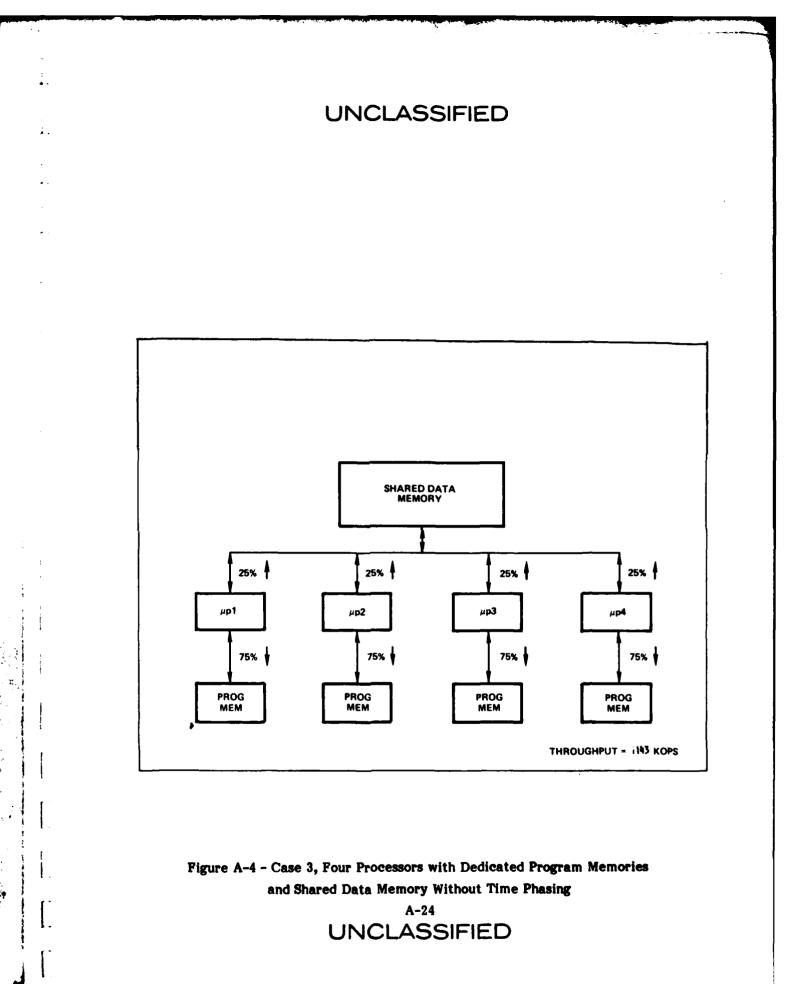

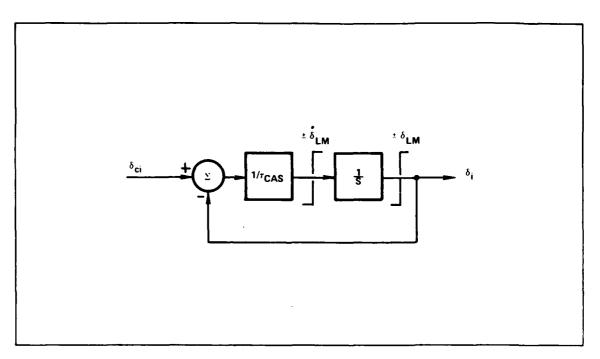

| B-1    | High-Performance Super-Federated Microcomputer System   |              |

|        | for Missile Simulation                                  | B-2          |

| B-2    | Control Actuator Section                                | B-9          |

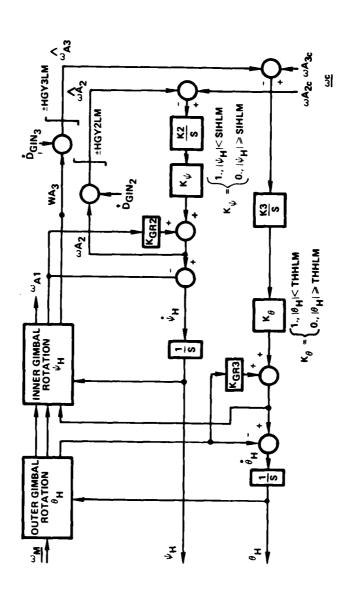

| B-3    | Head Control and Stabilization Model                    | B-12         |

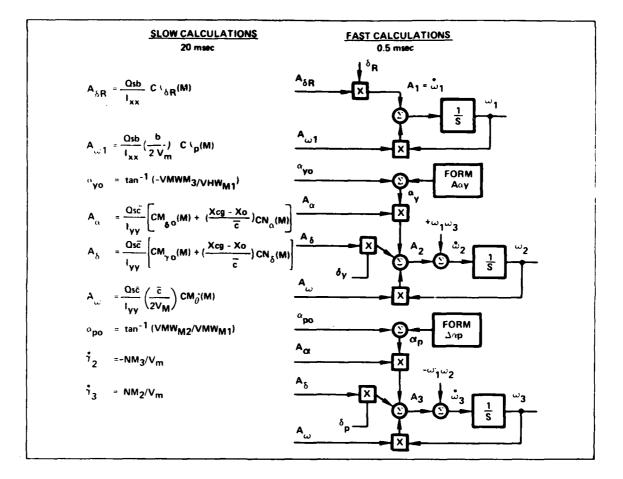

| B-4    | Reciever/Error Source Model                             | <b>B-1</b> 5 |

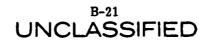

| B-5    | Aeromodel Partitioning                                  | B-17         |

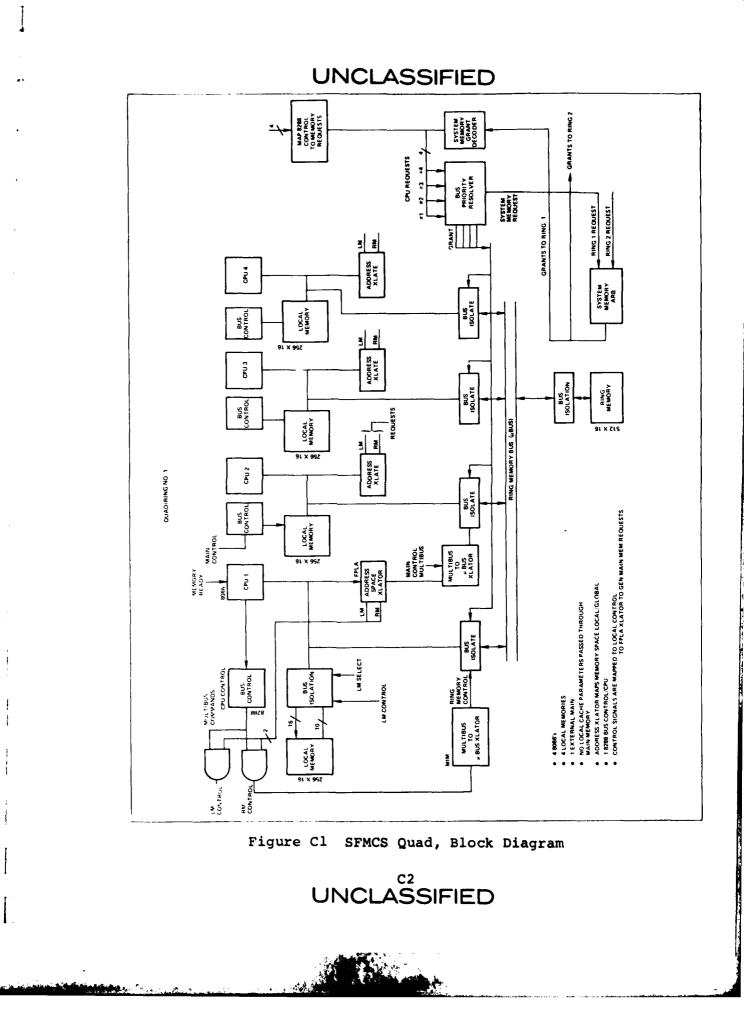

| C-1    | SFMCS Quad, Block Diagram                               | C-2          |

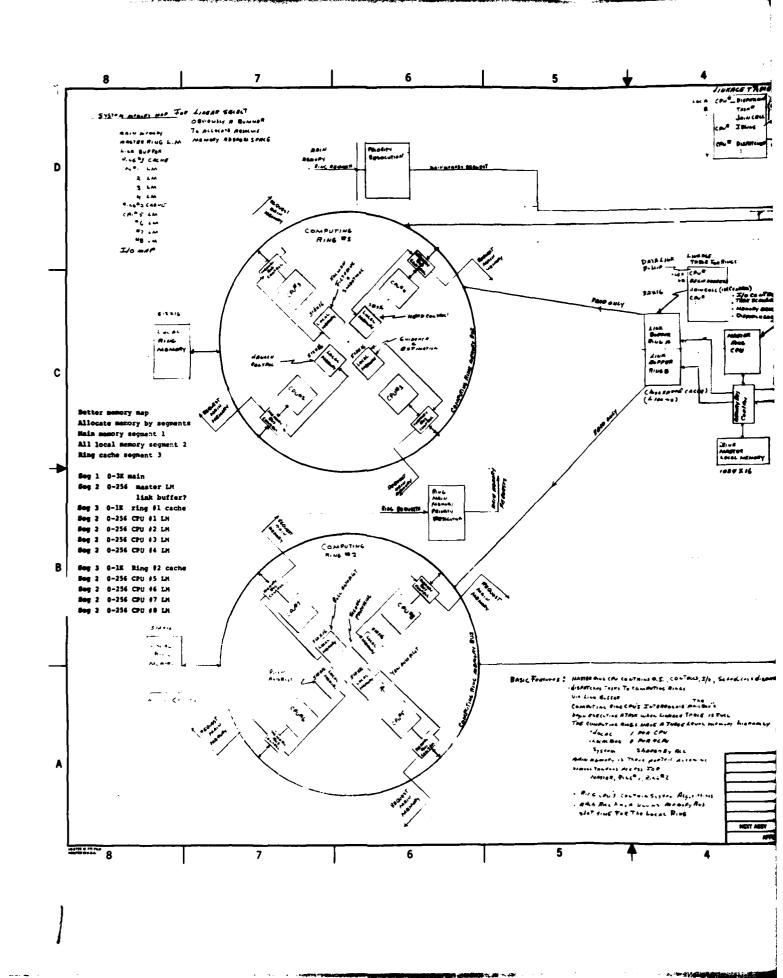

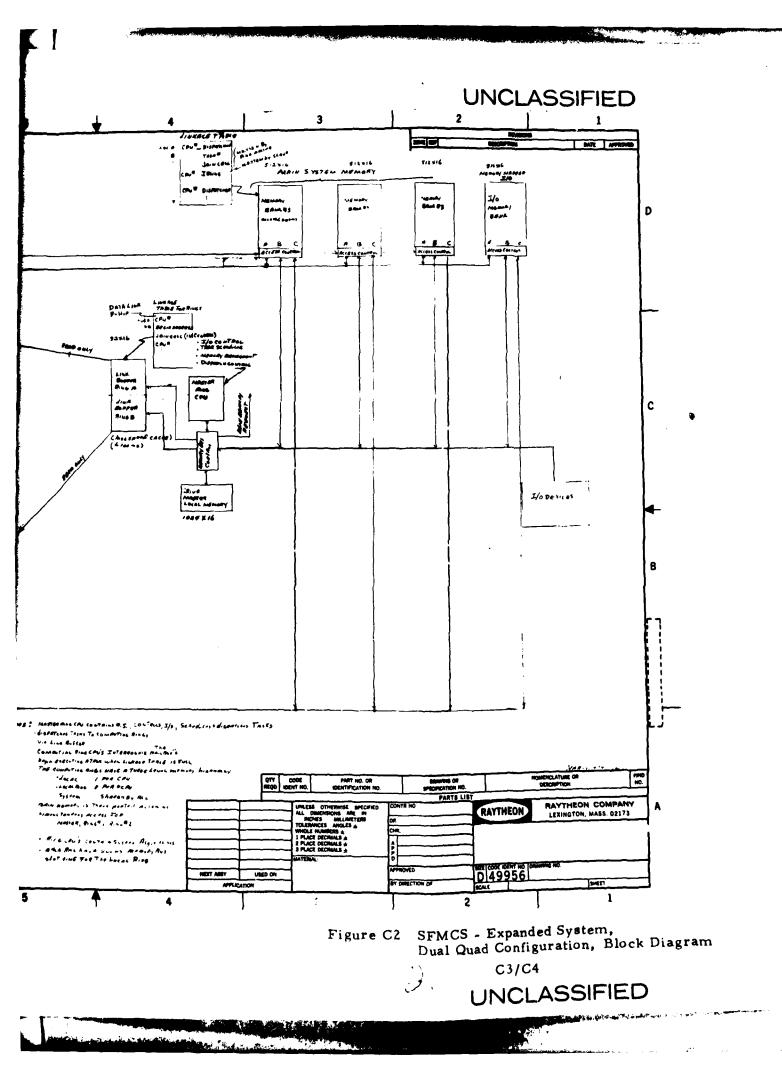

| C-2    | SFMCS - Expanded System, Dual Quad Configuration, Block |              |

|        | Diagram                                                 | C-3          |

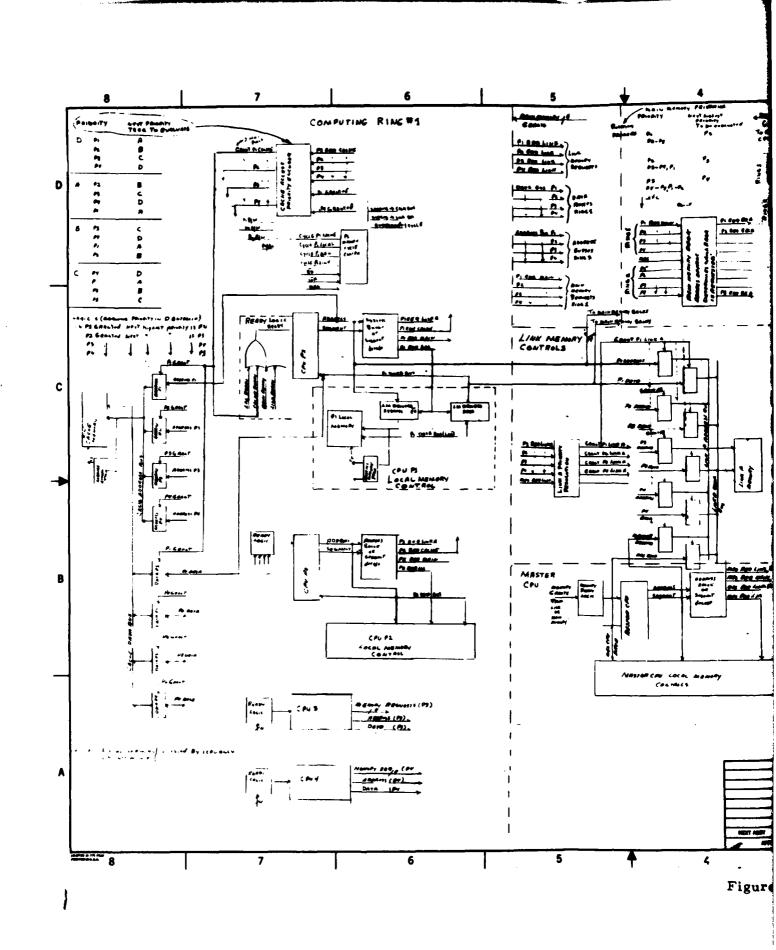

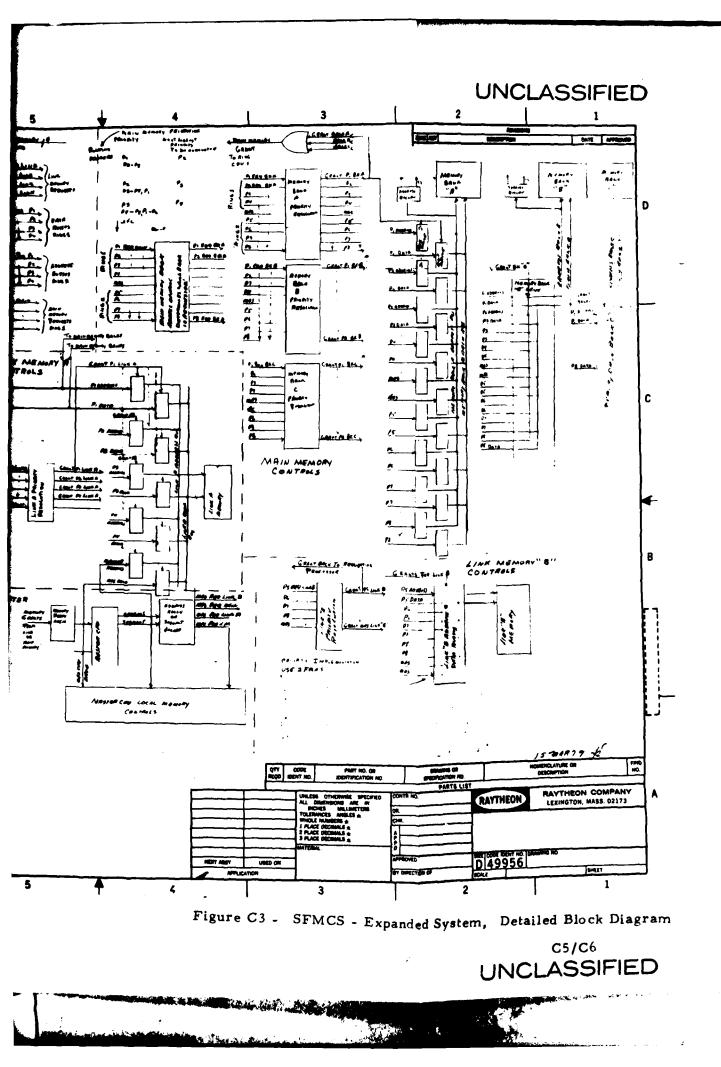

| C-3    | SFMCS - Expanded System, Detailed Block Diagram         | C-5          |

## LIST OF TABLES

.

4

| Table |                                              | Page       |

|-------|----------------------------------------------|------------|

| 3-1   | Microcomputer Macromodules                   | 3-15       |

| 6-1   | Comparison of SFMCS Software Control Methods | 6-18       |

| A-1   | Candidate Instruction Mixes                  | <b>A-2</b> |

| A-2   | INTEL 8086 Throughput for Candidate          |            |

|       | Instruction Mixes                            | A-15       |

| B-1   | CAS Model Quantities                         | B-9        |

|       |                                              |            |

xi

## **1. INTRODUCTION**

This report presents the results of the final phase of the Navy Modular Digital Missile Guidance study which culminates in the design of a high speed "super-federated" microcomputer system. The latter obviates the need to resort to multi component, bitslice computer architectures to meet the higher throughput processing requirements of missile guidance and control and, more importantly, super-federation supports modular software by assigning one microcomputer circuit to each major algorithm.

1.1 Background

In the previous study phases (References R-1 through R-18), programmable digital techniques were shown to offer improved performance and greater flexibility than the traditional hardwired analog implementations of seeker head control, signal processing, estimation, guidance, autopilot, warhead fuzing, telemetry and test functions.

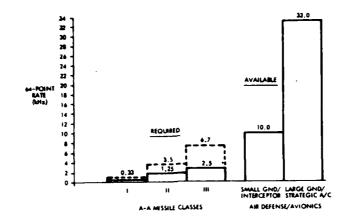

To achieve modularity and growth in hardware and software, a top-down system study approach was adopted, by first dividing the entire range of air-to-air missiles into three distinguishable generic classes, including upper and lower performance boundaries within each class (Figure 1-1). The major functions and data rates amenable to digital processing were then defined, determining their constituent software modules and sizing these in terms of computer throughput and memory requirements, (References R-1, R-2, R-3 and R-6).

Such a modular breakdown of on-board missile guidance and control functions, together with their associated interfaces, provided the option of configuring and evaluating either single or multiple federated/distributed computer system implementations according to the design constraints of a given missile.

Simulation analyses were also performed to confirm computer requirements and relate algorithm complexity to performance improvements for the guidance, estimation and autopilot/control functions, (Reference R-3).

With the computer design requirements determined from these studies, a set of microcomputer "macromodules" was defined to support the entire range of air-to-air missile functions, in either single or multiple/federated microcomputer system configurations (References R-3 through R-7). The modules were simulated individually and collec-

UNCLASSIFIED

EITHER 2 OR 3 OF: IR, PD RADAR, AR SEEKERS AND MID-COURSE GUIDANCE MULTI-MISSION/MODE LONG-RANGE **MULTI-MODE** ADAPTIVE AUTOPILOT 日 EITHER 1 OR 2 OF: IR, PULSE-DOPPLER (PD) RADAR OR ANTI-RADIATION (AR) SEEKERS HIGH-PERFORMANCE MEDIUM-RANGE SINGLE/DUAL-MODE **BANDSWITCHED** AUTOPILOT EITHER INFRA-RED (IR) OR CW-DOPPLER RADAR SEEKER SHORT-RANGE SINGLE-MODE FIXED-GAIN AUTOPILOT LOW-COST

I

÷.,

11.00

į l

[ [

ſ

. ș

Figure 1-1 - Generic Missile Classes

UNCLASSIFIED

# UNCLASSIFIED

tively, as whole microcomputer configurations (References R-8 and R-12) in order to validate their effectiveness in missile guidance and control applications to the point where realistic product function specifications could be prepared, (Reference R-14). To broaden the effectiveness of these specifications with respect to current technology developments, the compatibility of the Navy AN/UYK-30 microprocessor for general-purpose processing; charge-coupled device (CCD) technology for signal processing, (Reference R-17); and fiber-optic data link device technology for the serial digital system bus were explored (Reference R-14) through NOSC support.

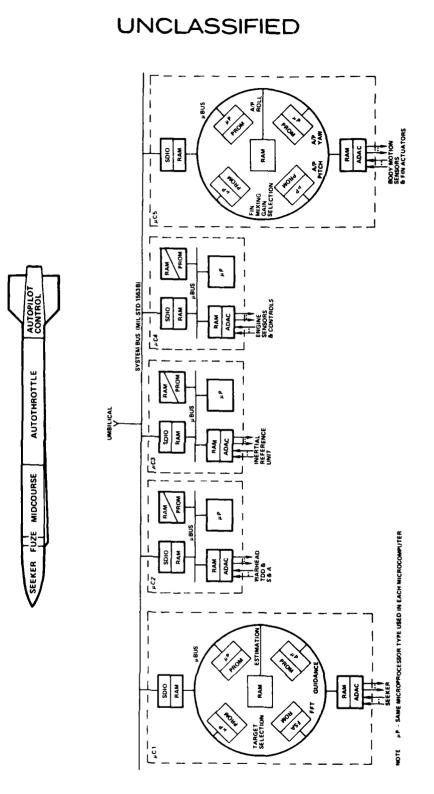

A similar study was then performed under NSWC sponsorship to address the ship-toair and ship-to-ship missile requirements, which led to the fabrication of selected microcomputer macromodules and their application to a Class I missile guidance and control system, (Reference R-19).

To accommodate improvements in microcomputer circuit technology without major redesign and provide flexible memory-mapping of input-output and main memory storage space, a programmable Microbus Interface Module (MIM) was designed and incorporated in each macromodule, (References R-16 and R-18).

While standard industry, single chip microprocessors could be used for certain missile functions, their throughput was insufficient for high-performance (Class III) applications such as target seeker and autopilot processing. To avoid the design and fabrication of a high-speed, general purpose processor in Schottky-bipolar or CMOS/SOS circuit technology, with its attendant multicomponent logistics and support software problems, a "super-federated" multimicroprocessor architecture was proposed for investigation and design during this phase of the program (References R-20 and R-21). The goals of this study are described in the following Subsection.

#### 1.2 Objectives and Scope

The objectives and scope of the Phase VI study under the modification of Contract N00014-75-C-0549 are as follows.

The contractor shall continue the Digital Missile Guidance study by performing fundamental hardware and software analysis to determine the feasibility of utilizing one common microcomputer type throughout the modular digital missile concept. In this Phase VI, the following tasks shall be performed:

- Task 1 Microstructural Analysis Analyze the high throughput requirement functional groups defined in the previous phases to determine the practicality of decomposing these into microstructures that can utilize one common, single chip microcomputer as the basic computing cell. Investigate the feasibility of software compatibility throughout the functional groups emphasizing replacing software program linkages with hardware interfaces.

- 2) Task 2 Microstructure Simulation and Evaluation Perform a digital simulation of the microstructures defined in Task 1 to prove the intermicrocomputer timing and interface and verify that the throughput of each microcomputer group meets the requirements for the complex, Class III missile defined in previous work.

#### 1.3 Publications and Presentations

Throughout the Modular Digital Missile Guidance Program the results of each phase have been widely published and presented to various Government Agencies and Industry. The work has proven timely not only in the field of missile guidance and control but in the design of any microcomputer-based system.

Twenty-two papers and reports have been published. The papers were presented at various conferences sponsored by: IEEE Computer Society, AFIPS/NCC, NASA/JPL, AIAA, DDR&E/IDA, SAE, SPIE, DPMA, NATO/AGARD.

Requests for these papers were received from several overseas countries, viz: Swedish National Defense Research Institute; Center for Applied Research in Electronics, India; Institute of Nuclear Research, Poland; Central Research Laboratory, Mitsubishi Electric Corp., Japan; Rijks University, Holland; The Weizmann Institute of Science, Israel; Institute of Radio and Electronics, Czechoslovakia; Centre National De La Recherche Scientifique, France.

Presentations and briefings were made to several branches of the Navy, Air Force, Army, NASA and allied groups viz: NAVAIR, NOSC, NWC, NPGS, NSWC, SSPO, NAAFI, AFATL, MICOM, ABMDA, NASA/JPL, MIT/Draper Lab.

# UNCLASSIFIED

## 2. SUMMARY AND CONCLUSIONS

Two serious problems exist in military computer-based systems:

- 1) The seemingly exorbitant cost of operational software and

- 2) The absence of a standard microprocessor-on-a-chip for all computing applications.

The first problem has been linked to the size, complexity, and testability of computer programs as well as the level of the programming language and more importantly, the fundamental structure and modularity of the program assigned to a computer, (Reference R-3).

The second problem is purely a technology advancement issue, and the recent advent of commercial 16-bit microprocessor chips with speeds of the order of 500,000 instructions per second (References R-22 and R-23), presents an opportunity to solve both of the above imperfections in the state-of-the-art.

Hence, the main thrust of this phase in the Modular Digital Missile Guidance Program has been to exploit the low cost of the 16-bit microprocessor and microcomputer to solve the high cost of software and computer commonality problems.

The basic concept uses what has been 'ermed "super-federated" computer system design techniques, (References R-20 and R-21) where each major function/algorithm is assigned to a separate microcomputer. A software change is then identified with a specific integrated circuit which, in turn, is part of an overall modular structure. As such, the super-federated design approach reduces program size and complexity, supports software modularity, and uses one microprocessor type. The latter, however, must be configured in a suitable multiprocessor architecture which achieves high throughput in cases where the speed of a single microprocessor chip is inadequate.

This study addresses two major design goals, software modularity and high throughput, while avoiding the pitfalls, (both hardware and software) of earlier multiprocessor designs. The results of the study, which are manifested in the super-federated microcomputer design drawings given at the end of this report, can be summarized in Subsection 2.1.

2-1 UNCLASSIFIED

#### 2.1 Conclusions

Super-federation of individual functions among separate microcomputers in a practical multiprocessor architecture provides the following advantages and/or solutions to computer system software and hardware design problems:

- Software Modularity By assigning one major algorithm/program module per microcomputer, a software change can be identified with and confined to a replaceable integrated circuit.

- 2) Software Control Structure The interface between major program modules is a fixed hardware interface which facilitates software changes and bounds the domain of each module. Further, the control hierarchy is implicit in the multiprocessor hardware structure.

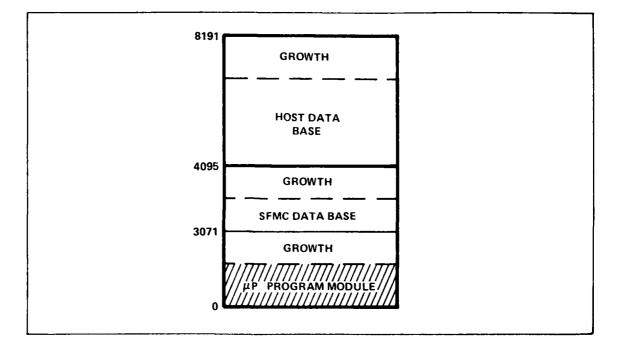

- 3) **Programming Simplicity** Single computer programming simplicity has been achieved within a common memory map. Each microprocessor is programmed as an entity with the base page of the memory space dedicated to the operational program.

- 4) High Throughput The high throughput functions in some missiles, (guidance and autopilot, for example), can be performed with several medium performance microcomputers of the same type by exploiting parallelism and overlap in the execution of their constituent program modules.

- 5) Standard Mircrocomputer Super-federation allows the use of one microcomputer type throughout the missile guidance and control system, singly in such cases as warhead fuzing or in a multiprocessor configuration for the more complex high-speed functions.

- 6) Common Support Software The use of one microcomputer type for both high and low throughput requirements obviates the need to design and build a high speed processor with a unique instruction set and its attendant support software development cost and risk.

## 3. DIGITAL MISSILE GUIDANCE AND CONTROL

Despite the many functional advantages of digital versus analog systems, the simple substitution of a small general purpose computer in place of the former analog circuits does not in itself solve all the problems encountered in the life cycle of a missile. The hardcore problems of advancing technology, changing threat situations, systems integration and logistics, together with the ever increasing cost of software, can result in an excessive premium paid for digital missiles.

While throughput could be satisfied with a single, high performance, miniclass computer and a dedicated, special-purpose target sensor signal processor, form-factor and electrical interface problems arise due to the many analog and digital discrete signals being converted and processed at a central point as opposed to being handled at the source. In addition, the design, assembly and checkout of major missile sections/functions, (e.g., seeker, warhead, flight control, telemetry), as completely operational modules are not possible with a single computer design approach.

From a software viewpoint, programming complexity increases with program size and the time multiplexing of individual missile functions to meet the sampling and computational delay requirements of the various control loops. This resulting modification or updating of any given function within the total program is then fraught with virtually unknown and complex software interface problems, a situation which worsens as the level of coding diminishes. In other words, the interface problems cited for analog systems can reappear in digital missiles at the computer input-output interface and in a more devious manner within the invisible internal software. Although software modularity supports the system flexibility requirement for changing threat/mission situations, it has nevertheless proven difficult to achieve and maintain through a development cycle.

#### 3.1 Motivations for Federated and Super-Federated Systems

The motivations for designing and building federated systems stem from the shortcomings of single computer systems cited in the previous paragraphs and the availability of low-cost, large-scale integrated (LSI) circuit microcomputers and associated I/O support circuits.

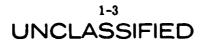

#### 3.1.1 Hardware

Federated microcomputer systems simplify subsystem design, manufacture, interface, test and the inevitable modifications and updates. Figure 3-1 serves to illustrate the major differences between single and federated computer design approaches. In the case of the single computer system, a relatively large high performance minitype computer is subject to the varying form factor constraints of a missile. To move the computer to a different location invariably entails the repackaging of hardware to fit the space available. A multiwire analog and digital interface problem also results from the concentration of data processing and conversion in one place.

In contrast, the federated microcomputer system performs the data conversion and processing tasks at source, within each major subsystem, and allows a standard serial digital multiplex interface to be used between subsystems and the launcher. This partitioning is discussed at greater length in subsequent sections of this report.

#### 3.1.2 Software

1.

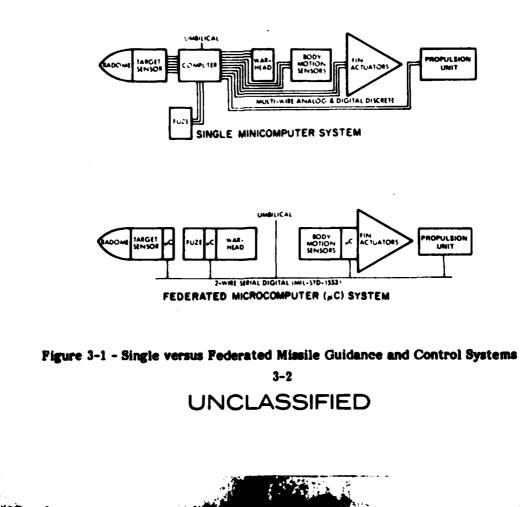

The merits of modular structured software, although well appreciated in this day and age, are somewhat idealistic and difficult to achieve and maintain. Figure 3-2 illustrates a rational, modular, hierarchical control structure for a single computer missile guidance and control system. All calls are made downward from the executive to subordinate mode supervisors and supporting functional program modules. However, under the normal pressure of tight development schedules the finished software is subject to shortcuts which invariably violate the original clean modular lines of the control structure. The outcome of a degradation in software modularity is realized more in the later phases of the development process when changes and substitutions are required (Figure 3-3). Since software costs are pegged to ever-increasing labor rates, the impact of the deficiencies in the design structure, together with other significant factors outlined below, are not apparent until the total cost of the finished product is paid.

Figure 3-2 - Modular Hierarchical Software Control Structure for Single Computer Missile Guidance and Control System

> 3-3 UNCLASSIFIED

> > 1. 1. 1. 1.

Figure 3-3 - Single Computer System Software Is inaccessible to Subsystem Designers

Cost Per Instruction =

1

## Design Cost+Coding Cost+Verification Cust+Maintenance Cost No. Lines of Code

**Determining factors:**

- 1) Predominantly labor costs, dependent upon:

- a) Firmness of Requirements

- b) Proportion New versus Proven Algorithms

- c) Size

- d) Complexity

2) Number lines of code, dependent upon:

- a) Number Functions Assigned to Software

- b) Level of Programming Language

Experienced software costs over the past few years indicate an average cost of \$40 to \$60 per instruction for a fully commissioned system in terms of new, real-time, operational programs, and between \$8 and \$30 per instruction for more standard routines. Whereas the cost of semiconductor memory is estimated to be in the order of millicents per bit, a 50-word subroutine typically costs \$3000 as a finished product. Microcomputer hardware, on the other hand, enjoys a volume market with modules selling in the tens of dollars. This situation emphasizes the need to be able to reuse or recycle program modules and to curb the tendency of designers to "do it in software" when in doubt about the requirements of a specific system function.

#### 3.1.3 Throughput

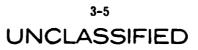

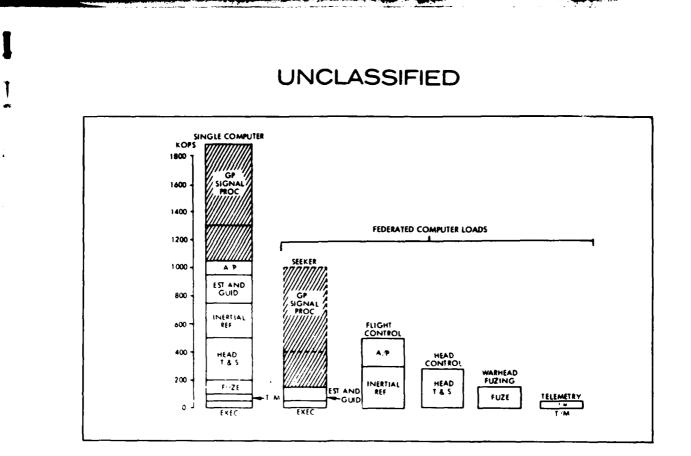

Studies have shown that the throughput requirements for single computer systems can reach the two million operations per second (two MOPS) mark (Figure 3-4). While a machine could be designed and built to meet the speed requirement, the tendency has been to add more functions, during the initial system development cycle and later, throughout the life span of the missile. Since there is a finite limit to the speed of the original computer, the increased load must either be accommodated by redesigning the machine or outrigging satellite processors to absorb the overflow which, in turn, tends toward a distributed system of haphazard design.

## 3.2 Defining/Identifying System Structures

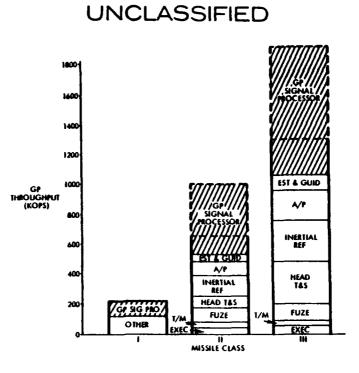

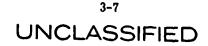

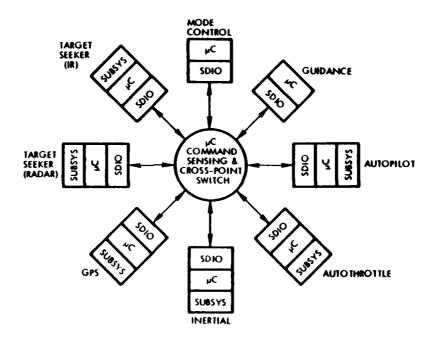

Before embarking upon the design of any federated system, it is important to consider the whole system as opposed to applying federated techniques on a piecemeal basis. The reason for this is to identify the characteristic structure of the system in terms of its constituent functions, data flow and data rates. Figure 3-5 shows the major functions of a typical missile system and their relationship to one another.

## Figure 3-5 - Typical Missile Guidance and Control System -Functional Block Diagram

In the system shown, the target sensor is mounted on a gimballed platform stabilized against missile body motion by platform-mounted rate gyros and torquers in conjunction with the seeker head control electronics. Target sensor, e.g., radar, infrared (IR) electro-optical (EO), outputs are processed by the signal processor which provides target range and angle data (angle only for IR and EO sensors), for subsequent filtering and processing into boresight error and 'g' commands using appropriate estimation and guidance law algorithms. The latter "steering" data controls the seeker platform and autopilot for target intercept. The autopilot also stabilizes the airframe against body motion and bending effects using body gyros and accelerometers as data sources and outputting fin deflection commands to fin control actuators. Detonation of the warhead is determined by the detection of the target by the warhead's target detection device augmented with end game geometry data from the primary target sensor signal processor and estimator. The form of motor control can vary from a simple squibbing signal from the weapon control system, via the umbilical, to sophisticated fuel control based on temperature, pressure and aerodynamic data in the case of ramjet propulsion units.

The degree of interaction between the functional components of the system, their physical relationship, system modularity requirements, and the magnitude of the processing task in each case, influences the structure of the practical distributed microcomputer system.

#### 3.2.1 System Timing Considerations

The basic or characteristic structure of a system, as far as its implementation with distributed microcomputers is concerned, is determined by the system timing constraints and the autonomy of functions. Figure 3-6 shows the system of the previous figure with switches interposed between the major functional blocks and the associated sampling or update rates indicated to satisfy the Nyquist criteria. Three major control loops are visible: seeker head, autopilot and steering command. The first two of the latter require relatively high sampling rates (125-500 Hz), to meet the bandwidths involved, whereas the steering command update rate is quite low (10-20 Hz). Also, the two high speed loops are virtually autonomous with their respective sensors and torquers/actuators.

Figure 3-6 - Digital System Timing Considerations 3-8 UNCLASSIFIED

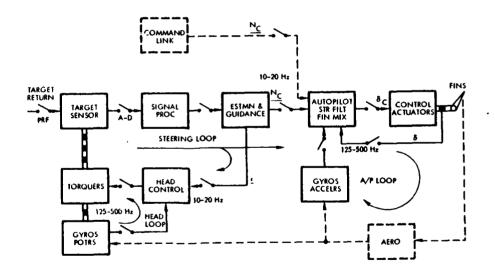

#### 3.2.2 System Parallelism

Figure 3-6 views the system as a set of functional blocks, but if the system is redrawn to reflect the planar control channels of pitch and yaw, for the seeker gimballed platform, pitch, roll and yaw for the autopilot, branching out into four fin control channels, then parallelism becomes evident (Figure 3-7). The latter system characteristic offers potential for using several low throughput microcomputers as opposed to a few high throughput machines.

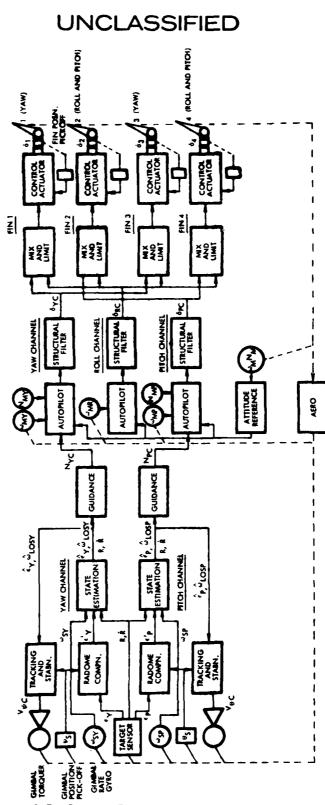

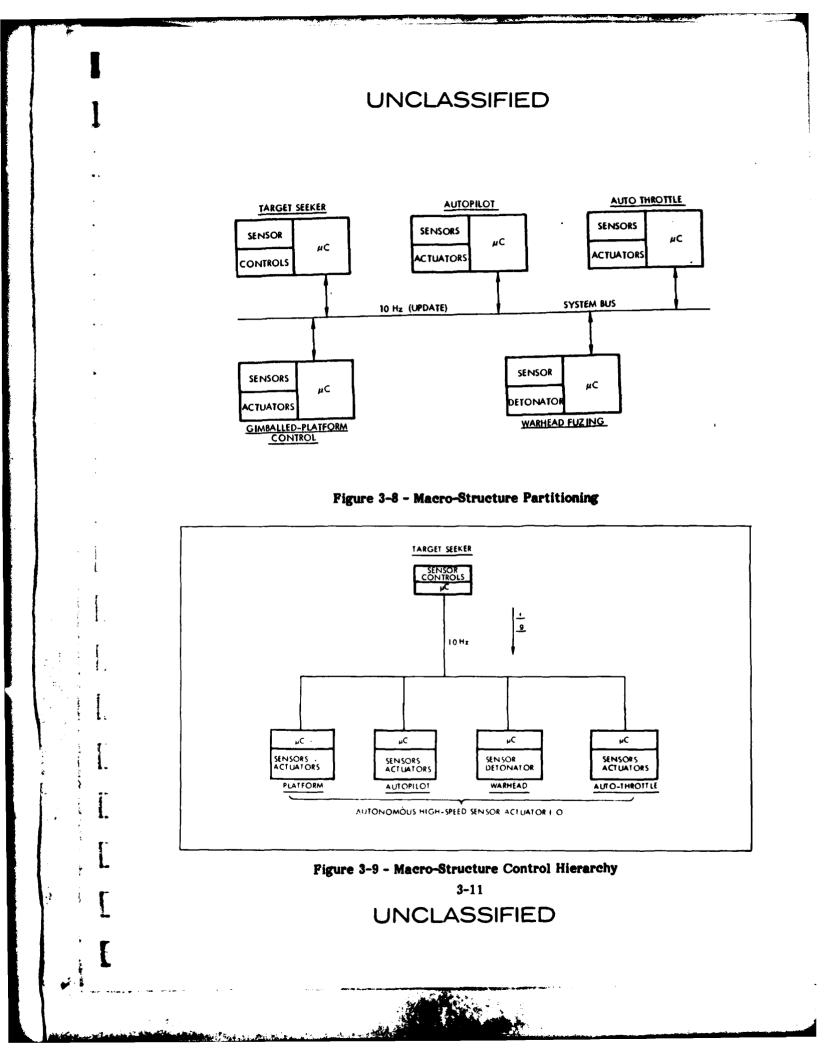

#### 3.2.3 Macro-Structure System

Based upon the system as it appears in Figure 3-6, the obvious macrostructure which exploits subsystem autonomy and low intersubsystem data rates is as shown in Figure 3-8. One microcomputer is assigned to each major subsystem and a common input-output (I/O) interface interconnects subsystems via a system bus at the low 10 Hz update rate. In terms of control hierarchy, the target seeker microcomputer controls the system bus since all other subsystems are subordinate "users" of the seeker data (Figure 3-9). This form of distributed microcomputer system is a true federated system, since each microcomputer operates virtually autonomously. Further, it meets the subsystem modularity design goal whether subsystems are colocated physically or not. However, there is one major drawback to this level of partitioning, as shown in Figure 3-10.

Throughput requirements for the individual microcomputers vary widely from up to one MOPS to as low as 50 KOPS. As a result, the high throughput requirements of the seeker, flight control and head control functions indicate a bit-slice Schottkybipolar or complimentary metal-oxide semiconductor, silicon-on-sapphire (CMOS-SOS) device technology machine, and the remaining low throughput functions as a singlechip microcomputer. The cost of designing and building the bit-slice  $\mu$ Cs and necessary support software is something to be avoided if possible; hence the need arises to explore alternative implementations using one type of microcomputer-on-a-chip throughout the system.

4

L

3-10 UNCLASSIFIED

#### 3.2.4 Super-Federated Systems

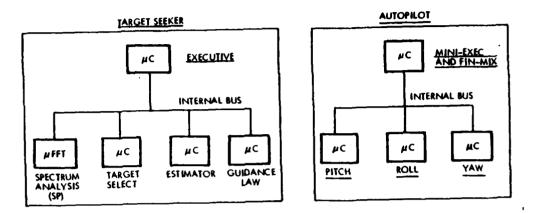

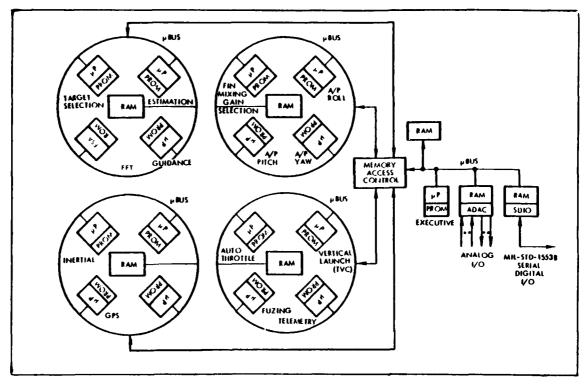

The high throughput macro functions identified in the previous paragraphs have the potential of being broken down into "microstructures" exploiting the intrinsic parallelism and overlap timing characteristics of the system. Figure 3-11 illustrates the use of separate single-chip microcomputers for each subfunction within the major functions of target seeker and autopilot.

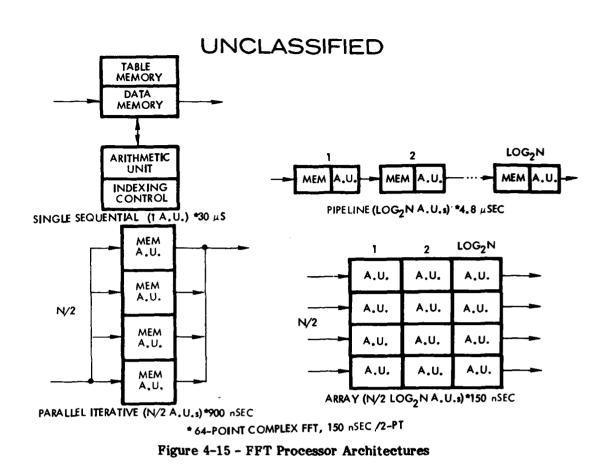

In the case of the target seeker processing group a "heel-to-toe" computing sequence is evident since each microcomputer is waiting for the output of a preceding subfunction. However, certain preliminary operations can proceed while waiting for real-time update information, e.g., state estimation. Further, since the spectrum analysis subfunction is a fixed entity i.e., either a 64, 128 or 256-point fast Fourier transform (FFT) process, then this should be executed in a high-speed special purpose processor to allow more time in the overall budget of 20 or so milliseconds for the slower general-purpose  $\mu$ Cs to execute their respective tasks. In other words, software is used where flexibility is required.

3-12

## UNCLASSIFIED

#### Figure 3-11 - Super-Federated Subsystem Processing, Target Seeker and Autopilot

The autopilot case is quite different. As was noted earlier (Figure 3-7), threeaxis control can be exploited through parallel processing, thereby allowing several relatively low speed  $\mu$  Cs to be used to perform a high-speed composite function.

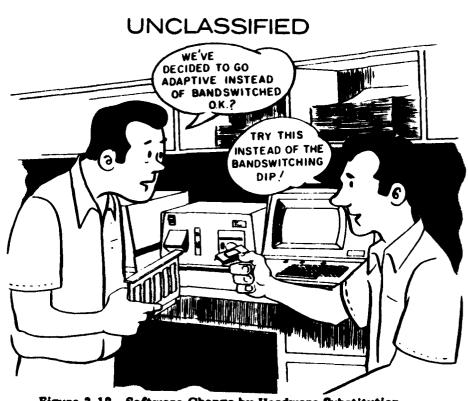

Software modularity is enhanced in each of the above cases, since the functional program modules shown in Figure 3-2 are now visible as separate single-chip microcomputers. Taken to an extreme, a 1:1 correlation between the program modules of Figure 3-2 and  $\mu$ Cs would ensure software modularity and provide a fixed hardware interface between software routines. Subroutine calls would then be handled by hardware linkages between  $\mu$ Cs. The situation depicted in Figure 3-3 could conceivably be transformed into the more desirable state of affairs shown in Figure 3-12, where a subfunction change is performed by the simple replacement of a single-chip microcomputer with the correctly programmed alternative.

## 3-13 UNCLASSIFIED

Figure 3-12 - Software Change by Hardware Substitution in Super-Federated Systems

#### 3.3 Microcomputer Modularity

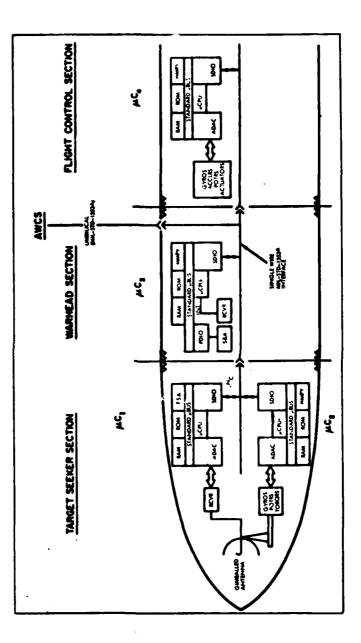

To cover the range of missile throughput requirements, a set of microcomputer macromodules was defined (Tabel 3-1). Memory-mapped I/O is used to eliminate Direct Memory Access (DMA) to "main" memory and the associated control circuits. Figure 3-13 shows the grouping together of modules to form a federated missile guidance and control system.

The crux of modularity at the microcomputer level was the definition of a standard microbus, (Reference R-14) oriented toward standard industry semiconductor memory circuit interfaces, i.e., read-write/random-access memories (RAMs) for data storage and read-only memories (ROMs) for programs.

3-14 UNCLASSIFIED

| nology Application      | 0                                       | o fuzing<br>o Hard Control                                 | o Autopliot                    | o Autopilot                         | (Adaptive)                            | e signal receasing<br>e Estimation<br>e cristance |                                   |                         | r Bybrid o Throughput<br>Enhancement                                      | for LCPU E.G. | Class I Sig. | • |                                          | for uCPUs 2.6.                         | Class II 6 | III Sig. Proc. | Z                                        | o Telemetry                    | o Fuzing         | o Read Control<br>o Autopliot | I | for id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | : Nybrid Deta<br>O sin Droot                                                  | o Estimation | o Guidance | o Head Control | o ruchtor<br>o fucing | rograma Programa                                                               |                 |                         | e Chip or Pydrid o Telemetry                                                                     | Morid o Head Control                |                                      | o Telemetry                              | o Radar Naceiver | a Mybrid o Avionics                  | o Inter Micro-                   |

|-------------------------|-----------------------------------------|------------------------------------------------------------|--------------------------------|-------------------------------------|---------------------------------------|---------------------------------------------------|-----------------------------------|-------------------------|---------------------------------------------------------------------------|---------------|--------------|---|------------------------------------------|----------------------------------------|------------|----------------|------------------------------------------|--------------------------------|------------------|-------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------|------------|----------------|-----------------------|--------------------------------------------------------------------------------|-----------------|-------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------------------------------------|------------------|--------------------------------------|----------------------------------|

| VLSI Circuit Technology | N-MOS, CPU-on a Chip,                   |                                                            |                                | Multi-                              | pCPU-1 Processor.                     |                                                   | HIGH-SPEED ALITHETIC AND HONORIDS | VLSI Circuit Technology | CHOS-SOS Single Chip of                                                   |               | -            |   |                                          |                                        |            |                | N-NOS Bingle Chip or Bybrid              |                                |                  |                               |   | N-NOS Bingle Chip or Mybrid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CHOS-BOG Single Chip or Bybrid                                                |              |            |                |                       | CHOS/808 Single Chip or Rybrid                                                 | <br>DRVF-OUTPUT | VLAI CITCUIT Technology | CHOS-BOS/Bipolar Bingle Chip or hybrid                                                           | Cros-Bos Single Chip of Micid       |                                      |                                          |                  | CHOS-BOS Single Chip or Bybrid       |                                  |

| 1 1                     | Medium-Speed ( 0.5Mips) Microprocessor/ | Central Processing Unit, 16-Bit W.rd,<br>View Construction | rixed-rollo, ceneral-regizere. | Bigh-Speed ( 2Mips) Microprocessor/ | Central Processing Unit, 16-Bit Word, |                                                   | ALCH-SPEED AL                     | Description             | Bigh Speed Multiplier, Memory-Mapped 200<br>nast. Max. ]6x]6-bit Multiply |               |              |   | Memory-Manmad, 150 Heat Mar. for 64-Dts. | B + JB. Preprodramable for 128. 256 or | 512 pts.   |                | Random-Access, Read/Write Nemory, Nedium | Speed, 128-2Kx16-Bits 300 nsec | Max. Access Time |                               |   | Programmable (Mask/Electrically) Meed-<br>Only Memory, Medium Speed, 1K-16Kri6-Sita,<br>2005-2005 - 2005-2005 - 2005-2005 - 2005-2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 - 2005 | Random-Access, Read/Write Memory, High-<br>Sneed 244-12414-1444 100 near Mer. | Access Time  |            |                |                       | Programmable (Mask/Electrically) Read-<br>onto monton sich const to serie bios |                 | Description             | Parailel Digital Input-Output Channel.<br>Memory-Happed. Parailel Word and<br>Discrete Transfers | Analog to Digital/Digital to Analog | Input-Output Channel. Memory-Mapped. | A-D: 8 Chs., Mux. 0/12-Bit, A-D 3/8 µsec |                  | Berial Digital Input-Output Channel. | Hemory-Happed. Word 6 Bit Serial |

| Module                  | uCF0-1                                  |                                                            |                                | JC70-2                              |                                       |                                                   |                                   | Module                  | 1.com                                                                     |               |              | i | 5                                        |                                        |            |                | NNH-1                                    | •                              |                  |                               |   | 1-101/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PAR-2                                                                         |              |            |                |                       | P/NOH-2                                                                        |                 | MORNTO                  | DIGA                                                                                             | ADAC                                |                                      |                                          |                  | . 0105                               |                                  |

# UNCLASSIFIED

## TABLE 3-1

-end-hold

utto S/N - sen Mux - mult Denst - de

Figure 3-13 - Modular Federated Microcomputer Missile Guidance and Control System 3-16 UNCLASSIFIED

ł

4

#### 3.3.1 Programmable Microbus Interface Module

In the microcomputer industry no two microbus interface schemes are the same, e.g., S-100 Bus, Intel MULTIBUS, National Microbus, etc., and similarly, the electrical interfaces of available support modules varies, e.g., analog-to-digital (A-D) and digitalto-analog (D-A) converters, memory modules, and serial digital interface modules.

Through the definition of an independent microbus interface a programmable microbus interface module (MIM), (References k-16 and R-18) was designed. This module employs high-speed field programmable logic arrays (FPLAs) and programmable read-only memories (PROMs), to interface standard-industry microcomputer components, i.e., microprocessors, RAMs, ROMs, multiplexer A-D converters, D-A converters and serial digital I/O modules with the microbus. Further, each individual component can be replaced with a more desirable product from a different manufacturer, at any time during the life cycle of the system, by reprogramming the MIM to accommodate the interface peculiarities of the new product.

#### 3.3.2 Frequency Spectrum Analyzer Module

Missile radar target seeker signal processing requirements are low compared to avionic and ground-based air defense systems (Reference R-3) (Figure 3-14). Nevertheless, the frequency spectrum analyzer (FSA) module of Table 3-1 using bit-slice microprocessor circuits, requires approximately 150 LSI/MSI/SSI circuits, dissipates approximately 50 W, using Schottky-bipolar circuit technology, and executes a 64-point complex FFT in approximately 300 µsec, meeting only Class I and II missile performance requirements (References R-6, R-14 and R-17). Such a processor dwarfs the single-chip microcomputer (Figure 3-15). In contrast, a charge-coupled device (CCD) processor using the chirp-Z transform (CZT) and transversal filters, executes an equivalent 64-point analysis in approximately 13  $\mu$ sec, with a power dissipation of less than 5 W. meeting all three missile class requirements (References R-17, R-24 and R-25). While dark current is a limiting factor in the dynamic range of analog CZT processors at the upper end of the MIL temperature range, recent improvements in prototype surface channel CCDs at Kaytheon and elsewhere (Reference R-26) indicate a temporary situation in this performance deficiency. Further, based on recent NASA/TI work, a 2-chip CCD C21 processor appears feasible in the near future.

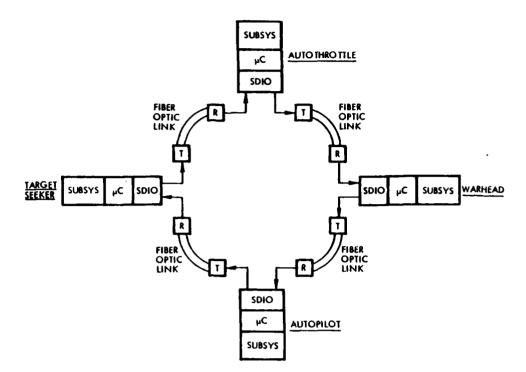

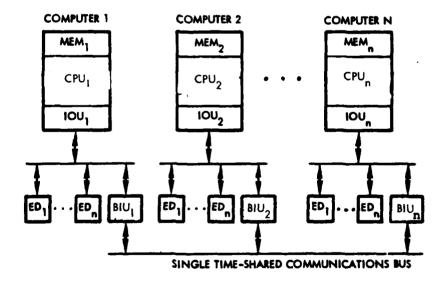

### 3.3.3 Serial-Digital Input-Output (SDIO) Module

The SDIO module provides a MIL-STD-1553B- compatible serial digital multiplex bus interface between microcomputers in the missile and the external weapon control system (Reference R-27). Using conventional transformer coupling to the transmission line requires relatively large, high-current, line driver, receiver and transformer components which, in turn, are inconsistent with today's single-chip microcomputers and the small size, weight and power limitations of a missile. Fiber-optic coupling between subsystem microcomputers, using simple LED/PIN diode/ $T^2L$  interface components (Reference R-28) and single-chip Manchester II/NRZ code converters (Reference R-29) reduces the serial I/O interface hardware to more realistic proportions (Reference R-14). However, the single party-line bus is not currently amenable to fiber-optic technology, since T-couplers introduce a 3 dB loss at each drop point. A simple alternative is the ring system of Figure 3-15, using a round-robin protocol (Reference R-30). A

Figure 3-15 - Fiber-Optic Ring Communications Between Missile Subsystems

more complex multiline approach is the star configuration which would be suitable for a simple, single-mode, short-range missile where the seeker becomes the focalpoint. Eight-port couplers have been built under Air Force contracts (Reference R-31).

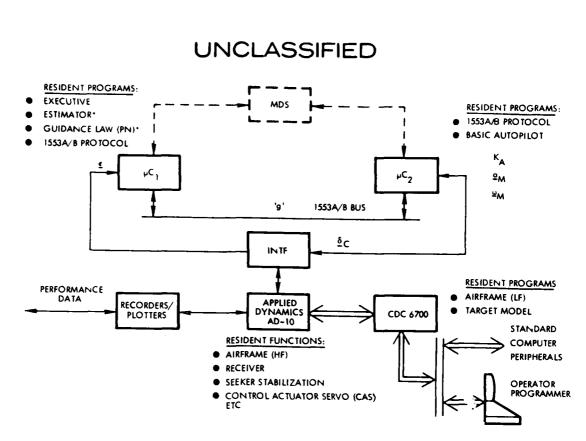

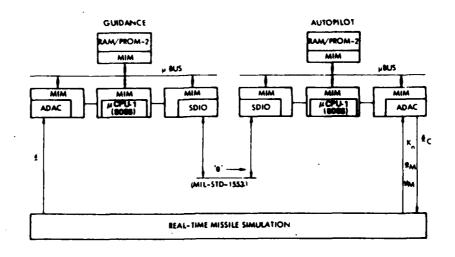

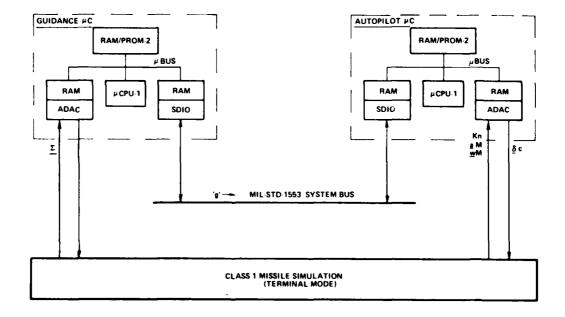

#### 3.4 Navy Demonstration System

The culmination of the above work has been the fabrication of a basic federated microcomputer guidance and control system under a NSWC contract (Reference R-19). This microcomputer system constitutes the "hardware-in-the-loop" element of a real-time missile simulation to evaluate the performance of the federated approach under the constraints of a MIL-STD-1553B I/O protocol (Figure 3-16).

Breadboard versions of the  $\mu$ C macromodules have been designed and built using standard industry  $\mu$ C components integrated with microbus interface modules (MIMs), Figure (3-17). The simulation is based upon a modular digital missile guidance simulation

Figure 3-16 Navy/Raytheon Hardware-in-the-Loop Federated  $\mu C$  System for Missile Performance Simulation

Figure 3-17 - Federated Microcomputer Macromodules Using MIM Interface

3-20 UNCLASSIFIED

Charles and the second of the

system developed for NSWC under a separate contract, (Reference R-32). System growth is achieved by adding additional microcomputers to the system bus and transferring/recoding simulation program modules to be executed by the appropriate microcomputer(s).

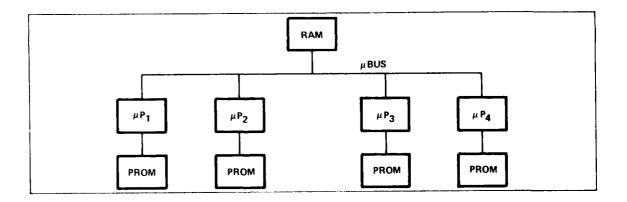

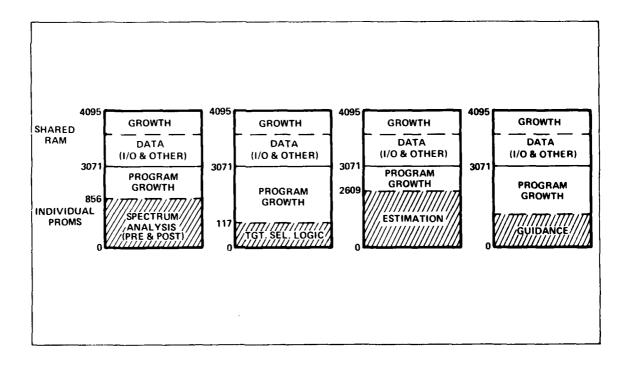

Figure 3-18 shows modular growth from the simple low-performance guidance and control system of Figure 3-17 to a high-performance super-federated system using several microprocessors of the same type and maintaining the original data memory and I/O modules. Each microprocessor executes only one algorithm using a dedicated program memory chip. This arrangement ensures software modularity and programming simplicity while minimizing  $\mu$  bus traffic.

#### 3.5 Summary

Federated microcomputer systems provide the flexibility to design, develop, modify and update missile guidance and control systems on an individual subsystem basis, thereby enhancing system modularity. Standard industry microcomputer components which meet military environmental specifications can be integrated into a set of microcomputer macromodules using a standard programmable interface module and microbus. To achieve and maintain modularity in software, the potential exists to assign each major program module to a separate single-chip microcomputer, placing a fixed hardware interface between major function algorithms. Furthermore, by exploiting parallelism and/or the time overlapping of function execution, the use of several standard-industry, singlechip microcomputers in a "super-federated" configuration eliminates the need to resort to one-of-a-kind, high-speed, bit-slice processors for high performance missiles, with their attendant hardware and software logistics support problems. In terms of signal processing, improved charge-coupled device technology, in the form of chirp-Z transform processors using transversal filters, offers a solution to the high chip/parts count of current fast Fourier transform processors. A two-chip CZT processor would match the level of largescale circuit integration presently available in microcomputer technology.

In cases where federated microcomputer systems are distributed physically throughout a missile, relatively low performance, fiber-optic, serial-digital communications between microcomputer-based subsystems using a round-robin protocol eliminates the high power, transformer-coupled interface of traditional electrical bus systems.

Figure 3-18 - Super-Federated Microcomputer System for Higher Performance Missile Guidance and Control

Mer 10

is ne ville

### 4. CLASSIC MULTIPROCESSOR ARCHITECTURES

Before embarking on the super-federated microcomputer system architectural design, a review of earlier multiprocessor architectures was performed to determine their respective merits and failings both from a hardware and software viewpoint.

Although large physically, due to the state-of-the-art in hardware at the time of construction, these earlier architectures become classical in terms of the various approaches adopted to solve such problems as throughput, availability and growth for both random and highly repetitive computing tasks.

Further, the deficiencies experienced in these architectures (particularly software), are as important today as earlier, except of course for the shortcomings resulting from the number of discrete components and their associated failure rates.

#### 4.1 Multiprocessor and Computer Systems

1

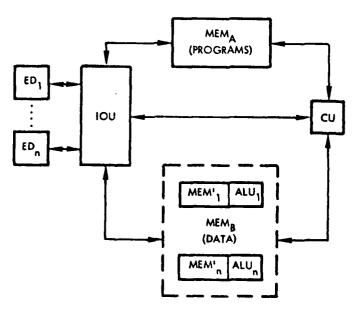

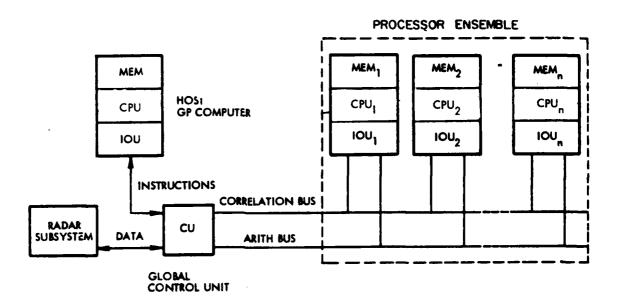

To overcome the deficiencies of single, uniprocessor computer systems for highperformance, high-availability applications, viz: limited throughput; failure upon a single fault; restricted growth in size and performance; various architectures incorporating either several of the basic elements of a computer, i.e. CPUs, memories, and IOUs, (multiprocessor systems), or several whole computers (multicomputer systems) have been designed and built. These systems are characterized by their ability to perform the simultaneous or parallel execution of similar and/or different tasks at several times the speed of a single sequential machine.

Multiprocessor systems are essentially expanded and more complex versions of the basic Von Neumann uniprocessor, (Reference R-33), usually performing a centralized role in a given system. However, a significant drawback to certain types of past multiprocessor systems has been the executive processing load associated with the efficient utilization of processors in a multi-task operating environment, (Reference R-34). Since this overhead remains sequential, system throughput is not linearly proportional to the number of processors employed.

Multicomputer systems, on the other hand, are composed of several relatively simple and familiar computers interconnected via their I/O units (IOUs). Multicomputer

systems normally function as decentralized, distributed/federated systems with each computer dedicated to a specific set of interrelated tasks and external devices (EDs).

Communication within a multiprocessor system involves megaword per second information transfer rates whereas within a multicomputer system, i.e., between IOUs, functional partitioning is designed to achieve transfer rates in the kiloword per second range.

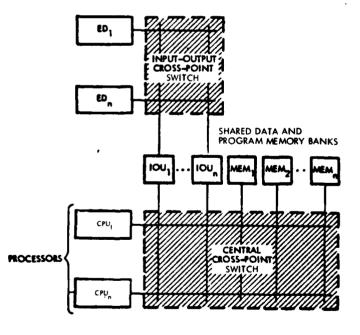

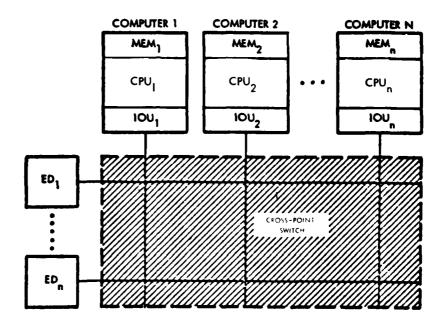

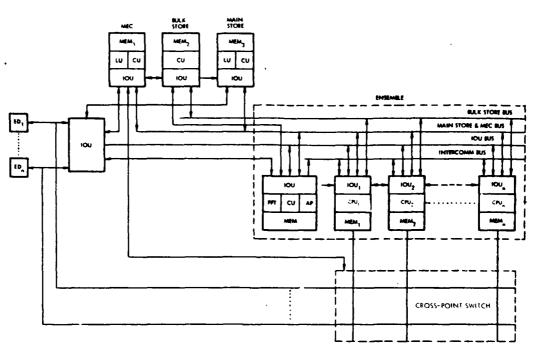

The various characteristic forms of multiprocessor and multicomputer systems built to date involve either single or multiple data busses, or a cross-point switching matrix for communication between major computer elements or computers respectively. In the following examples reviewed it car. be seen that it is both the type of communication employed and the degree of customization of the architecture to the type of processing task to be executed which characterizes the system, whether multiprocessor or multicomputer.

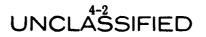

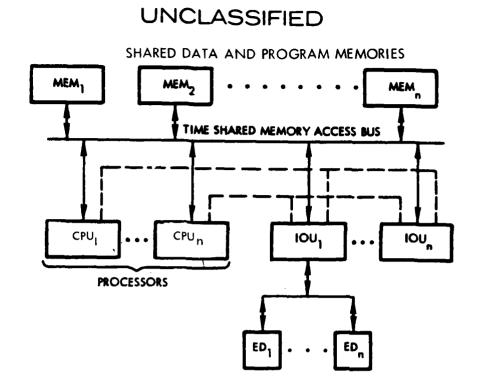

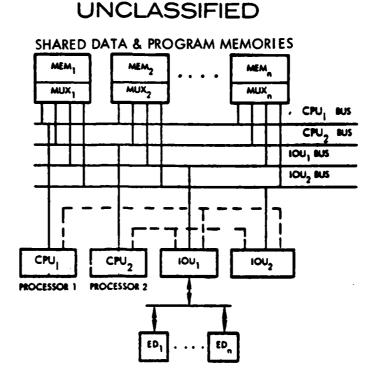

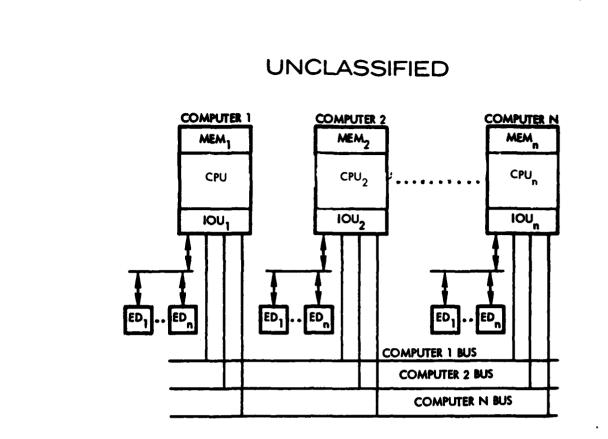

#### 4,1.1 Single Time-Shared/Party-Line Bus

The most simple form of multiprocessor and multicomputer system employs a single, time-shared/party-line communications bus. These architectures achieve the highest throughput only when accesses to the bus can be scheduled to avoid user conflicts. Of the two types of computer system, the multiprocessor (Figure 4-1) is more throughput limited by the single bus than its multicomputer counterpart due to the lack of autonomy of the individual processors and their dependence upon access to a common/shared "main" memory. The multicomputer system (Figure 4-2) however is far more amenable to the single-bus for inter-IOU communication due to the low transfer rates in a properly partitioned system. In the example shown, bus accesses can either be controlled by a masterslave hierarchy or on a round-robin basis to eliminate conflicts. Furthermore, the low inter-IOU transfer rates in a well designed multicomputer system enables a serial digital multiplex bus to be employed, affording higher reliability through simple duplication. Current technology in serial data transmission also offers virtually error-free performance at 1 MHz bit rates and using a ring bus with a round-robin I/O protocol, a low cost fiberoptic data link becomes practicable. Figure 4-3 shows a simple missile guidance and control system using one microcomputer ( $\mu c$ ) per subsystem, serial digital input-output (SDIO) channel and fiber-optic/ $T^2L$  transmitter (T) and receiver (R) interface circuits.

Figure 4-2 - Multicomputer System - Single Time-Shared Communications Bus

4-3