Open access · Journal Article · DOI:10.1063/1.4861168

## Molecular doping for control of gate bias stress in organic thin film transistors — Source link [2]

Moritz Hein, Alex Zakhidov, Björn Lüssem, Jens Jankowski ...+3 more authors Institutions: Dresden University of Technology Published on: 09 Jan 2014 - <u>Applied Physics Letters</u> (American Institute of Physics) Topics: Gate oxide, Organic semiconductor, Pentacene and Thin-film transistor

Related papers:

- Doped Organic Transistors.

- Doped organic transistors operating in the inversion and depletion regime

- · Contact doping and ultrathin gate dielectrics for nanoscale organic thin-film transistors

- Use of a 1H-Benzoimidazole Derivative as an n-Type Dopant and To Enable Air-Stable Solution-Processed n-Channel Organic Thin-Film Transistors

- Ultralow Doping in Organic Semiconductors: Evidence of Trap Filling

## Molecular doping for control of gate bias stress in organic thin film transistors

Moritz P. Hein, Alexander A. Zakhidov, Björn Lüssem, Jens Jankowski, Max L. Tietze, Moritz K. Riede, and Karl Leo

Citation: Applied Physics Letters **104**, 013507 (2014); doi: 10.1063/1.4861168 View online: http://dx.doi.org/10.1063/1.4861168 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/104/1?ver=pdfcov Published by the AIP Publishing

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 163.1.240.244 On: Fri, 14 Feb 2014 18:21:35

## Molecular doping for control of gate bias stress in organic thin film transistors

Moritz P. Hein,<sup>1,a)</sup> Alexander A. Zakhidov,<sup>2</sup> Björn Lüssem,<sup>1</sup> Jens Jankowski,<sup>1</sup> Max L. Tietze,<sup>1</sup> Moritz K. Riede,<sup>1,b)</sup> and Karl Leo<sup>1,2</sup> <sup>1</sup>Institut für Angewandte Photophysik, Technische Universität Dresden, George-Bähr-Straße 1, 01069 Dresden, Germany <sup>2</sup>Fraunhofer COMEDD, Maria-Reiche-Str. 2, 01109 Dresden, Germany

(Received 23 October 2013; accepted 17 December 2013; published online 9 January 2014)

The key active devices of future organic electronic circuits are organic thin film transistors (OTFTs). Reliability of OTFTs remains one of the most challenging obstacles to be overcome for broad commercial applications. In particular, bias stress was identified as the key instability under operation for numerous OTFT devices and interfaces. Despite a multitude of experimental observations, a comprehensive mechanism describing this behavior is still missing. Furthermore, controlled methods to overcome these instabilities are so far lacking. Here, we present the approach to control and significantly alleviate the bias stress effect by using molecular doping at low concentrations. For pentacene and silicon oxide as gate oxide, we are able to reduce the time constant of degradation by three orders of magnitude. The effect of molecular doping on the bias stress behavior is explained in terms of the shift of Fermi Level and, thus, exponentially reduced proton generation at the pentacene/oxide interface. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4861168]

A continuously driven organic thin film transistor (OTFT) shows a decreasing current between source and drain electrode,  $I_{\rm D}$ , over time. Commonly, this behavior is described by a stretched exponential decay of the threshold voltage,  $V_T$ , and explained with a slow charge trapping within the channel—at the gate-insulator interface of the transistor.<sup>1</sup> Therefore,  $V_T$  shifts towards the applied value of gate voltage, lowering  $I_{\rm D}$ . The observation of gate bias stress has been reported for widely different material systems,<sup>2–6</sup> such as OTFTs based on silicon oxide (SiO<sub>2</sub>),<sup>7,8</sup> organic dielectric layers,<sup>9–11</sup> as well as for thin-film transistors using a-Si:H, poly-Si, and metal-oxide semiconductor materials.<sup>12–16</sup> Equation (1) describes this stretched exponential decay, where  $V_{T,max}$  is the maximum threshold shift after infinite time,  $\tau$  is the time constant, and  $\beta$  is the stretching exponent

$$\Delta V_T = V_{T,\max}\left(1 - \exp\left[-\left(\frac{t}{\tau}\right)^{\beta}\right]\right). \tag{1}$$

Typical values for  $\tau$  are in the range of  $10^3$  s and usually strongly depend on transistor preparation and measurement conditions. In particular, temperature, ambient conditions (humidity),<sup>17</sup> light exposure, and gate voltage were found to have a major impact. Meanwhile,  $\beta$  was observed to be more or less constant in the range of about 0.2 to 0.4.<sup>18</sup> Several fundamentally different underlying mechanisms were proposed to explain bias stress behavior, including: (i) proton generation at the organic/dielectric interface and further migration into the dielectric,<sup>7</sup> (ii) slow trapping of mobile charges,<sup>8</sup> (iii) bipolaron formation mechanism,<sup>10</sup> and (iv) migration of carriers into electronic states of the dielectric.<sup>9</sup>

In particular, for p-type OTFTs with SiO<sub>2</sub> as gate dielectric, the bias stress mechanism of proton generation at the organic/SiO<sub>2</sub> interface and their migration into the bulk of SiO<sub>2</sub> is widely accepted.<sup>18</sup> This mechanism includes two steps that differ in timescale:

(1) Fast (<1 ms) proton generation is governed by the oxygen/water redox couple  $4H^+ + O_2 + 4e^- \leftrightarrow 2H_20$ , where holes in pentacene (p5+) are in equilibrium with protons on the surface of the SiO<sub>2</sub> in the redox half reaction  $p5^+ + e^ \leftrightarrow$  p5. The rate of reaction is proportional to exp( $-E_a/kT$ ), where  $E_a$  is an activation energy which, according to Bobbert et al., is proportional to the HOMO level of the organic semiconductor.<sup>18</sup> Consequently, the only way to alleviate the bias stress for a given semiconductor and interface would be to minimize the supply of water at the organic/oxide interface. (2) After protons are generated, a slow (>1 s)reversible migration of the protons into the bulk of SiO<sub>2</sub> towards the gate electrode is observed (Figure 1(a)). Mobile protons, located between the accumulation channel and the gate, are thus screening the gate electric field. Therefore, the effective electric field,  $E_G$ , in the channel becomes

$$E_G = \frac{V_{GS}}{d} - \frac{n(t)}{\varepsilon \varepsilon_0},\tag{2}$$

where  $V_{GS}$  is the applied gate voltage, e is the elementary charge,  $\varepsilon \varepsilon_0$  is the dielectric permittivity of the insulator, n(t)is the density of protons, and d is the thickness of the dielectric. Consequently, this screening of the electric field leads to a shift of  $V_T$  and a decrease of  $I_D$ . The proton migration mechanism has also a characteristic feature, observed in experiments, which is called anomalous bias stress effect.<sup>7</sup> Anomalous bias stress occurs, when the stressing voltage is

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 163.1.240.244 On: Fri. 14 Feb 2014 18:21:35

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: hein@iapp.de

<sup>&</sup>lt;sup>b)</sup>Present address: Department of Physics, University of Oxford, Clarendon Laboratory, Parks Road, Oxford OX1 3PU, England.

reduced to a lower value after a previous stress period. In this case,  $I_{\rm D}$  recovers up to a certain maximum, before it starts to follow the normal bias stress characteristic again.

In this Letter, we report a study of the effect of molecular p- and n-type doping of the OTFT channel on the bias stress behavior. For our experiments, we chose pentacene on  $SiO_2$  as a well-known, high mobility benchmark material. We show that even marginal doping has a very pronounced effect on the bias stress time constant  $\tau$  and, thus, the reliability of OTFTs.

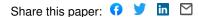

The general setup of the coplanar transistors is sketched in Figure 1(a). These transistors were prepared on chips of a highly conductive p-doped silicon wafer with a 230 nm thick thermally grown oxide ( $C_i = 14.6 \text{ nF/cm}^2$ ). On top of the silicon dioxide, interdigitated 30 nm thick Au finger structures were deposited in a lift-off process (Fraunhofer IPMS, Dresden, Germany). As a result, for source and drain electrode, a channel length, L, of 20  $\mu$ m and a channel width, W, of 10 mm were realized. These chips were cleaned in an ultrasonic bath with acetone, ethanol, and isopropanol for 10 min each and treated with an O2-plasma for an additional 10 min.<sup>19</sup> Subsequently, the chips were transferred to a UHV evaporation system with a base pressure below  $10^{-7}$  mbar and heated for 30 min at 100 °C. Afterwards, pentacene was evaporated, with a layer thickness of 30 nm. In case of the doped transistors, either the p-dopant 2,2'-(perfluoronaphthalene-2,6-divlidene)dimalononitrile (F6-TCNNQ) or the n-dopant tetrakis(1,3,4,6,7,8-hexahydro-2H-pyrimido[1,2-a] pyrimidinato)ditungsten (W2(hpp)4) (Novaled AG, Dresden, Germany) was coevaporated.<sup>20,21</sup> Here, only the first 10 nm of the pentacene film were doped to avoid poor on/off ration of the OTFTs.<sup>23</sup> Furthermore, in order to keep high mobility of OTFTs, we only used low doping concentrations, since higher concentrations cause a drop of mobility due to the structural changes in the pentacene film.<sup>24</sup> A rotary shutter, described by Tietze et al., was used to ensure high accuracy FIG. 1. Experimental observation of influence of molecular doping on bias stress of pentacene based OTFTs. (a) Scheme of the used transistor geometry. The red dots symbolize protons that are diffusing into the dielectric and screening the gate electric field. Furthermore, the chemical structures of the used materials pentacene, F6-TCNNQ, and W2(hpp)4 are shown. (b) Anomalous bias stress of a pentacene transistor p-doped with 0.25 wt. % F6-TCNNQ. The transistor is stressed at  $V_{GS} = -60 \text{ V}$  for 4 h before the voltage is reduced to its half. At the reduced voltage, the current starts to increase, as it recovers from the previous stressing period. (c) Time dependent current decrease of p- and n-type doped pentacene transistors. A stretched exponential fit with Eq. (4) for each curve is plotted in dashed lines. (d) Bias stress time constant  $\tau$  as a function of molecular doping concentration (blue) and, thus, correlated Fermi level (red). The errors of the UPS measurements are estimated to be smaller than 0.05 eV.

of the doping concentration.<sup>22</sup> Afterwards, the chips were transferred to a measurement station under nitrogen atmosphere without exposure to air.

Characteristics of transistors were measured with two Keithley source measurement units (SMU), one Keithley 2611A for the source/drain contacts and Keithley 2400 for the gate contact. All measurements were done without illumination of the samples.  $V_T$  and charge carrier mobility,  $\mu$ , were extracted from the transfer characteristic in the saturation regime<sup>25</sup> on the basis of formula (4), with drain current,  $I_D$ , gate-source voltage,  $V_{GS}$ , channel length, L, channel width, W, and dielectric capacity,  $C_i$

$$I_D = \frac{WC_i \mu}{2L} (V_{GS} - V_T)^2.$$

(3)

Actual bias stress measurements were started after the initial characterization and 30 min waiting period that is appropriate for a recovery of the transistor. During the measurement process, constant voltages were applied to drain and gate electrode. The bias stress behavior is often described with the decrease of  $V_T$  according to formula (1), but such measurements lead to an interruption of the bias stress for each measurement point. Alternatively, we directly measured current decrease during stress time. Under the condition that  $V_T$  will ultimately reach the value of the applied  $V_{GS}$  ( $V_{T,max} = V_{GS} - V_{T,0}$ ),  $I_D$  will decrease in a similar behavior

$$I_D = I_0 \exp(-2(t/\tau)^{\beta}).$$

(4)

The scheme of the studied devices is shown in Figure 1(a). Transistors based on pentacene with doping ratios of 1 wt. %, 0.5 wt. %, and 0.25 wt. % F6-TCNNQ (p-dopant) or 1 wt. % of W2(hpp)4 (n-dopant) are measured and compared to intrinsic pentacene. For intrinsic samples, neither a variation of channel length, L, nor a change in the semiconductor layer thickness shows an influence on the bias stress behavior.

TABLE I. Characteristic parameters of measured bottom-contact transistors.

| Doping material     | Fermi level<br>(eV) | Ion/Ioff<br>ratio | $\mu (cm^2/V s)$ | τ<br>(s) | β    |

|---------------------|---------------------|-------------------|------------------|----------|------|

| 1.0 wt. % W2(hpp)4  | 2.12 <sup>a</sup>   | 69 600            | 0.036            | 2.21     | 0.21 |

| 0.0 wt. % Intrinsic | 1.31 <sup>a</sup>   | 35 200            | 0.12             | 605      | 0.32 |

| 0.25 wt. % F6-TCNNQ | N/A                 | 507               | 0.22             | 160 000  | 0.21 |

| 0.5 wt. % F6-TCNNQ  | 0.46 <sup>a</sup>   | 93.6              | 0.54             | 442000   | 0.27 |

| 1.0 wt. % F6-TCNNQ  | 0.43 <sup>a</sup>   | 49.4              | 0.20             | 67 3000  | 0.28 |

<sup>a</sup>cf. supplementary material.

This indicates that the observed charging effect happens at the interface or at least close-by in the accumulation channel. Degradation of  $I_D$  is found to be reversible. After a certain time of relaxation, correlated to the previous stress time, the initial performance of the transistor is restored. Without a recovery time and subsequently performed stress periods at various gate voltages, the transistors show anomalous behavior as reported by Matters *et al.*<sup>7</sup> (Figure 1(b)). In accordance with literature,<sup>9,18</sup> charge-carrier mobility is not affected during the stress period and remains constant (Table I). Thus, the current decrease is directly connected to a shift of  $V_T$ . Hence, we can discuss the typical bias stress behavior without influence of irreversible transistor degradation. Figure 1(c) shows the result of time-dependent current measurements during the applied bias stress. A dashed line illustrates a stretched exponential fit with formula (4). Fitting parameters are listed in Table I. While the stretching parameter  $\beta$  is always in the range of 0.21 to 0.32, the time constant  $\tau$  is dramatically affected by doping. With p-doping, the bias stress time constant is significantly increased, while n-doping reduces  $\tau$  by two orders of magnitude.

Since we observe anomalous bias stress in all our experiments, as exemplarily shown for the p-doped transistor (0.25 wt. %) in Figure 1(b), we conclude that proton migration indeed remains the underlying mechanism of the observed bias stress. Thus, we argue that a significant change of  $\tau$  is caused by a change of the rate of proton generation happening during step (1) of the mechanism described above. Since the entire sample set is prepared under the same conditions, the amount of available water remains the same as well as mobility of ions in the bulk of SiO<sub>2</sub>. Therefore, the only possible explanation left is that the proton generation rate is changed. This rate is given by the rate of electrochemical reaction, which in turn depends on the position of the Fermi level (i.e., electrochemical potential) of the doped film. In Figure 1(d),  $\tau$  is plotted over the molecular doping ratio. The doped pentacene films are investigated on separate substrates via ultraviolet photoelectron spectroscopy (UPS). See supplementary material for the UPS measurement data.<sup>29</sup> These measurements were already published elsewhere<sup>26</sup> and allow an estimation of the Fermi level in the pentacene layer depending on its doping concentration. Within this estimation, an error smaller than 0.05 eV can be assumed. The results are listed in Table I and are also plotted in Figure 1(d) (red squares). From this plot, we can deduce an exponential correlation between Fermi level and  $\tau$  that supports our explanation.

resistance in the off-state of the transistor. This problem is especially true for the coplanar transistor geometries used here. See supplementary material for the corresponding transfer characteristics. Staggered depletion or inversion transistors<sup>26,27</sup> with only very thin p-type doped channel layers retain the possibility to control the bias stress time constant without influencing the off-current as it was shown in a separate experimental series of pentacene transistors in a staggered geometry on an aluminum oxide as a gate dielectric. See supplementary material for preparation details and bias stress measurement data. In these samples, the doped channel layer is thin enough that the channel can be fully depleted and the transistors can be turned off completely.

As presented, molecular doping is able to control the time constant of the bias stress effect in OTFTs over orders of magnitude. Thus, it can significantly improve device-stability of OTFTs for their application in logic circuits. The processing of doped layers is already established in the OLED industry and can be easily adopted. With the design of staggered transistors having a thin doped layer at the interface to the gate oxide only,<sup>26–28</sup> this effect can be used without a strong disturbance for the normal transistor performance. On the contrary, controlled escalation of bias stress allows investigations for electrical memory device operation mechanisms. However, the relation between bias stress time constant and Fermi level above shown contributes an important argument in the discussion and a deeper understanding of bias stress phenomena, in general.

The authors would like to thank the CfAED for financial support and Novaled AG for materials supply.

- <sup>1</sup>H. Sirringhaus, Adv. Mater. 21, 3859–3873 (2009)

- <sup>2</sup>J. Zaumseil and H. Sirringhaus, Chem. Rev. 107, 1296 (2007).

- <sup>3</sup>H. Klauk, Chem. Soc. Rev. **39**, 2643 (2010).

- <sup>4</sup>A. Sharma, S. G. J. Mathijssen, E. C. P. Smits, M. Kemerink, D. M.

- de Leeuw, and P. A. Bobbert, Phys. Rev. B 82, 075322 (2010).

- <sup>5</sup>M. Tello, M. Chiesa, C. M., Duffy, and H. Sirringhaus, Adv. Funct. Mater. **18**, 3907–3913 (2008).

- <sup>6</sup>R. Street, A. Salleo, and M. Chabinyc, Phys. Rev. B 68, 085316 (2003).

- <sup>7</sup>M. Matters, D. M. De Leeuw, P. T. Herwig, and A. R. Brown, Synth. Met. **102**, 998–999 (1999).

- <sup>8</sup>K. P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D. J. Gundlach, B. Batlogg, A. N. Rashid, and G. Schitter, J. Appl. Phys. **96**, 6431 (2004).

- <sup>9</sup>W. L. Kalb, T. Mathis, S. Haas, A. F. Stassen, and B. Batlogg, Appl. Phys. Lett. **90**, 092104 (2007).

- <sup>10</sup>B. Lee, A. Wan, D. Mastrogiovanni, J. E. Anthony, E. Garfunkel, and V. Podzorov, Phys. Rev. B 82, 085302 (2010).

- <sup>11</sup>K. Fukuda, T. Suzuki, D. Kumaki, and S. Tokito, Phys. Status Solidi A **209**, 2073–2077 (2012).

- <sup>12</sup>M. Powell, IEEE Trans. Electron Devices **36**, 2753–2763 (1989).

- <sup>13</sup>J. Park, M. Cho, H. B. Park, T. J. Park, S. W. Lee, S. H. Hong, D. S. Jeong, C. Lee, and C. S. Hwang, Appl. Phys. Lett. **85**, 5965 (2004).

- <sup>14</sup>S. J. Rhee, C. Y. Kang, C. S. Kang, C. H. Choi, R. Choi, M. S. Akbar, and J. C. Lee, Appl. Phys. Lett. 85, 3184 (2004).

- <sup>15</sup>H. Gleskova and S. Wagner, IEEE Trans. Electron Devices **48**, 1667 (2001).

- <sup>16</sup>W.-S. Kim, Y.-K. Moon, K.-T. Kim, S.-Y. Shin, and J.-W. Park, Thin Solid Films **520**, 578 (2011).

- <sup>17</sup>H. L. Gomes, P. Stallinga, M. Coülle, D. M. De Leeuw, and F. Biscarini, Appl. Phys. Lett. 88, 082101 (2006).

- <sup>18</sup>P. A. Bobbert, A. Sharma, S. G. J. Mathijssen, M. Kemerink, and D. M. De Leeuw, Adv. Mater. 24, 1146 (2012).

The disadvantage of p-type doped pentacene transistors is a reduced on/off-ratio, as the doped layer still has a low

<sup>19</sup>M. S. Wrackmeyer, M. Hein, A. Petrich, J. Meiss, M. Hummert, M. K. Riede, and K. Leo, Sol. Energy Mater. Sol. Cells 95, 3171 (2011). <sup>20</sup>K. Walzer, B. Maennig, M. Pfeiffer, and K. Leo, Chem. Rev. **107**, 1233 (2007).

- <sup>21</sup>B. Maennig, M. Pfeiffer, A. Nollau, X. Zhou, and K. Leo, Phys. Rev. B 64, 195208 (2001).

- <sup>22</sup>M. L. Tietze, K. Leo, and B. Lüssem, Org. Electron. **14**, 2348 (2013).

- <sup>23</sup>R. Ruiz, A. Papadimitratos, A. C. Mayer, and G. G. Malliaras, Adv. Mater. 17, 1795 (2005).

- <sup>24</sup>H. Kleemann, C. Schuenemann, A. Zakhidov, M. Riede, B. Lüssem, and K. Leo, Org. Electron. 13, 1 (2012).

- <sup>25</sup>G. Horowitz, Adv. Mater. **10**, 365 (1998).

- <sup>26</sup>B. Lüssem, M. L. Tietze, H. Kleemann, C. Hoßbach, J. W. Bartha, A. Zakhidov, and K. Leo, Nat. Commun. 4, 2775 (2013).

- <sup>27</sup>S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Shimoda, T. Mitani, H. Shimotani, N. Yoshimoto, S. Ogawa, and Y. Iwasa, Nature Mater. 3, 317–322 (2004).

- <sup>28</sup>Y. Abe, T. Hasegawa, Y. Takahashi, T. Yamada, and Y. Tokura, Appl. Phys. Lett. 87, 153506 (2005).

- <sup>29</sup>See supplementary material at http://dx.doi.org/10.1063/1.4861168 for the transfer characteristics of the transistors, UPS measurement data and data of the staggered transistor series.