# ESCOLA POLITÉCNICA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO DOUTORADO EM CIÊNCIA DA COMPUTAÇÃO

#### FELIPE AUGUSTO KUENTZER

MORE THAN A TIMING RESILIENT TEMPLATE: A CASE STUDY ON RELIABILITY-ORIENTED IMPROVEMENTS ON BLADE

Porto Alegre 2018

PÓS-GRADUAÇÃO - STRICTO SENSU

# PONTIFICAL CATHOLIC UNIVERSITY OF RIO GRANDE DO SUL FACULTY OF INFORMATICS COMPUTER SCIENCE GRADUATE PROGRAM

## MORE THAN A TIMING RESILIENT TEMPLATE: A CASE STUDY ON RELIABILITY-ORIENTED IMPROVEMENTS ON BLADE

#### FELIPE AUGUSTO KUENTZER

Dissertation submitted to the Pontifical Catholic University of Rio Grande do Sul in partial fullfillment of the requirements for the degree of Ph. D. in Computer Science.

Advisor: Prof. Alexandre de Morais Amory

Porto Alegre 2018

### Ficha Catalográfica

#### K95m Kuentzer, Felipe Augusto

More than a timing resilient template: a case study on reliability-oriented improvements on Blade / Felipe Augusto Kuentzer. – 2018.

100 f.

Tese (Doutorado) – Programa de Pós-Graduação em Ciência da Computação, PUCRS.

Orientador: Prof. Dr. Alexandre de Morais Amory.

1. Timing resilient design. 2. Asynchronous design. 3. Design for testability. 4. Functional testing. 5. Blade. I. Amory, Alexandre de Morais. II. Título.

Elaborada pelo Sistema de Geração Automática de Ficha Catalográfica da PUCRS com os dados fornecidos pelo(a) autor(a).

#### Felipe Augusto Kuentzer

# More than a Timing Resilient Template: A Case Study on Reliability-Oriented Improvements on Blade

This Dissertation/Thesis has been submitted in partial fulfillment of the requirements for the degree of Doctor/Master of Computer Science, of the Graduate Program in Computer Science, School of Technology of the Pontificia Universidade Católica do Rio Grande do Sul.

Sanctioned on March 28th, 2018.

#### **COMMITTEE MEMBERS:**

Prof. Dr. Peter Anthony Beerel (USC)

Prof. Dr. Marcelo Soares Lubaszewski (PGMicro/UFRGS)

Prof. Dr. Ney Laert Vilar Calazans (PPGCC/PUCRS)

Prof. Dr. Alexandre de Morais Amory (PPGCC/PUCRS - Advisor)

# MAIS DO QUE UM CIRCUITO RESILIENTE A VARIAÇÕES DE ATRASO: UM ESTUDO DE CASO SOBRE MELHORIAS ORIENTADAS À CONFIABILIDADE NO BLADE

#### **RESUMO**

À medida que o projeto de VLSI avança para tecnologias ultra submicron, as margens de atraso adicionadas para compensar variabilidades de processo de fabricação, temperatura de operação e tensão de alimentação, tornam-se uma parte significativa do período de relógio em circuitos síncronos tradicionais. As arquiteturas resilientes a variações de atraso surgiram como uma solução promissora para aliviar essas margens de tempo projetadas para o pior caso, melhorando o desempenho do sistema e reduzindo o consumo de energia. Essas arquiteturas incorporam circuitos adicionais para detecção e recuperação de violações de atraso que podem surgir ao projetar o circuito com margens de tempo menores. Os sistemas assíncronos apresentam potencial para melhorar a eficiência energética e o desempenho devido à ausência de um sinal de relógio global. Além disso, os circuitos assíncronos são conhecidos por serem robustos a variações de processo, tensão e temperatura. Blade é um modelo que incorpora as vantagens de projeto assíncrono e resilientes a variações de atraso. No entanto, o Blade ainda apresenta desafios em relação à sua testabilidade, o que dificulta sua aplicação comercial ou em larga escala. Embora o projeto visando testabilidade com Scan seja amplamente utilizado na indústria, os altos custos de silício associados com o seu uso no Blade podem ser proibitivos. Por outro lado, os circuitos assíncronos podem apresentar vantagens para testes funcionais, enquanto o circuito resiliente fornece feedback contínuo durante o funcionamento normal do circuito, uma característica que pode ser aplicada para testes concorrentes. Nesta Tese, a testabilidade do Blade é avaliada sob uma perspectiva diferente, onde o circuito implementado com o Blade apresenta propriedades de confiabilidade que podem ser exploradas para testes. Inicialmente, um método de classificação de falhas que relaciona padrões comportamentais com falhas estruturais dentro da lógica de detecção de erro e uma nova implementação orientada para teste desse módulo de detecção são propostos. A parte de controle é analisada para falhas internas, e um novo projeto é proposto, onde o teste é melhorado e o circuito pode ser otimizado pelo fluxo de projeto. Um método original de medição de tempo das linhas de atraso também é abordado. Finalmente, o teste de falhas de atrasos em caminhos críticos do caminho de dados é explorado como uma consequência natural de um circuito implementado com Blade, onde o monitoramento contínuo para detecção de violações de atraso fornece a informação necessária para a detecção concorrente de violações que extrapolam a capacidade de recuperação do circuito resiliente. A integração de todas as contribuições fornece uma cobertura de falha satisfatória para um custo de área que, para os circuitos avaliados nesta Tese, pode variar de 4,24% a 6,87%, enquanto que a abordagem *Scan* para os mesmos circuitos apresenta custo que varia de 50,19% a 112,70% em área, respectivamente. As contribuições desta Tese demonstraram que, com algumas melhorias na arquitetura do Blade, é possível expandir sua confiabilidade para além de um sistema de tolerância a violações de atraso no caminho de dados, e também um avanço para teste de falhas (inclusive falhas online) de todo o circuito, bem como melhorar seu rendimento, e lidar com questões de envelhecimento.

**Palavras-Chave:** projeto resiliente a variações de atraso, projeto assíncrono, projeto visando testabilidade, teste funcional, falhas de stuck-at, falhas de atraso, blade.

# MORE THAN A TIMING RESILIENT TEMPLATE: A CASE STUDY ON RELIABILITY-ORIENTED IMPROVEMENTS ON BLADE

#### **ABSTRACT**

As the VLSI design moves into ultra-deep-submicron technologies, timing margins added due to variabilities in the manufacturing process, operation temperature and supply voltage become a significant part of the clock period in traditional synchronous circuits. Timing resilient architectures emerged as a promising solution to alleviate these worst-case timing margins, improving system performance and/or reducing energy consumption. These architectures embed additional circuits for detecting and recovering from timing violations that may arise after designing the circuit with reduced time margins. Asynchronous systems, on the other hand, have a potential to improve energy efficiency and performance due to the absence of a global clock. Moreover, asynchronous circuits are known to be robust to process, voltage and temperature variations. Blade is an asynchronous timing resilient template that leverages the advantages of both asynchronous and timing resilient techniques. However, Blade still presents challenges regarding its testability, which hinders its commercial or large-scale application. Although the design for testability with scan chains is widely applied in the industry, the high silicon costs associated with its use in Blade can be prohibitive. Asynchronous circuits can also present advantages for functional testing, and the timing resilient characteristic provides continuous feedback during normal circuit operation, which can be applied for concurrent testing. In this Thesis, Blade's testability is evaluated from a different perspective, where circuits implemented with Blade present reliability properties that can be explored for stuck-at and delay faults testing. Initially, a fault classification method that relates behavioral patterns with structural faults inside the error detection logic and a new test-driven implementation of this detection module are proposed. The control part is analyzed for internal faults, and a new design is proposed, where the test coverage is improved and the circuit can be further optimized by the design flow. An original method for time measuring delay lines is also addressed. Finally, delay fault testing of critical paths in the data path is explored as a natural consequence of a Blade circuit, where the continuous monitoring for detecting timing violations provide the necessary feedback for online detection of these delay faults. The integration of all the contributions provides a satisfactory fault coverage for an area overhead that, for the evaluated circuits in this thesis, can vary from 4.24% to 6.87%, while the scan approach for the same circuits implies an area overhead varying from 50.19% to 112.70%, respectively. The contributions of this Thesis demonstrated that with a few improvements in the Blade architecture it is possible to expand its reliability beyond a timing resilient system to delay violations in the data path, but also advances for fault testing (including online faults) of the entire circuit, yield, and aging.

**Keywords:** timing resilient design, asynchronous design, design for testability, functional testing, stuck-at faults, delay faults, blade.

## LIST OF FIGURES

| Figure 2.1 – (a) Bundled-data block diagram. (b) The 4-phase handshake protocol. (c)                                                                       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| The 2-phase handshake protocol                                                                                                                             | 28 |

| Figure 2.2 - Razor flip-flop [ERN03]                                                                                                                       | 30 |

| Figure 3.1 — Razor II flip-flop [DAS09]                                                                                                                    | 32 |

| Figure 3.2 - Razor-Lite schematic [KWO14]                                                                                                                  | 33 |

| Figure 3.3 - Bubble Razor schematic [FOJ13]                                                                                                                | 33 |

| Figure 3.4 – (a) TDTB circuit [BOW09]; (b) DSTB circuit [BOW09]                                                                                            | 34 |

| Figure 3.5 – SafeRazor module [CAN15]                                                                                                                      | 35 |

| Figure 3.6 - Blade template [HAN15]                                                                                                                        | 36 |

| Figure 3.7 $-$ Blade flow, adapted from [HAN15]                                                                                                            | 37 |

| Figure 3.8 - The Sharp controller [WAU17]                                                                                                                  | 38 |

| Figure 3.9 – (a) DSTB circuit [BOW09]; (b) Scan-based DSTB circuit [YUA13]                                                                                 | 40 |

| Figure 4.1 - Blade error detection logic diagram, adapted from [HAN15]                                                                                     | 44 |

| Figure 4.2 — Timing diagram of a timing violation being detected inside the EDL, adapted                                                                   |    |

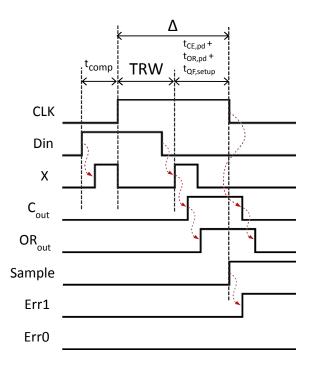

| from [HAN15]                                                                                                                                               | 45 |

| Figure 4.3 – A proposed ATPG test scenario. Transition detectors (TD) are connected                                                                        |    |

| to four-input (CLK plus three TDs) C-elements (C) and the C-elemets connected to two-input OR gates. In total there are 6 TDs to each OR gate. The OR gate |    |

|                                                                                                                                                            | 46 |

|                                                                                                                                                            | 47 |

|                                                                                                                                                            | 48 |

|                                                                                                                                                            | 49 |

|                                                                                                                                                            | 50 |

| Figure 4.8 – TEDL diagram and labeled wires. The dark gates represent the additional                                                                       |    |

|                                                                                                                                                            | 57 |

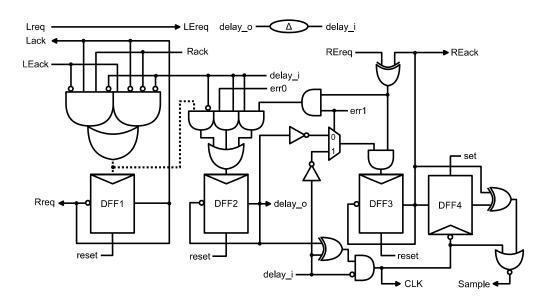

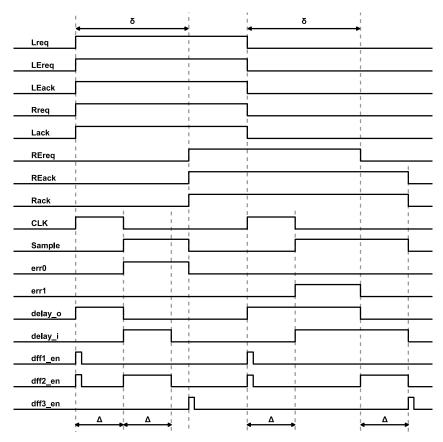

| Figure 5.1 – Blade speculative handshaking protocol [HAN15]                                                                                                | 63 |

| Figure 5.2 – Description of Blade's Burst-Mode controller using 3D syntax                                                                                  | 63 |

| Figure 5.3 – Burst-mode state machines for the Blade controller [HAN15]                                                                                    | 64 |

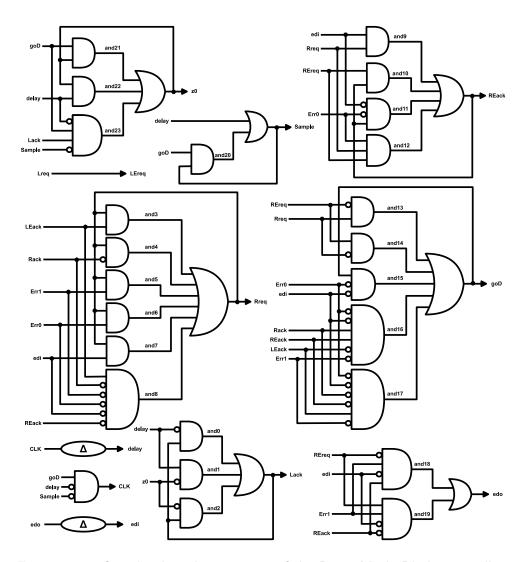

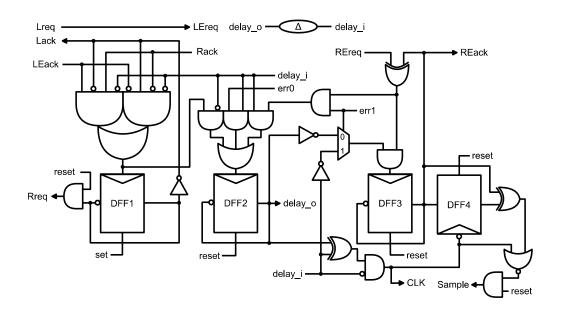

| Figure 5.4 - Gate level implementation of the Burst-Mode Blade controller                                                                                  | 65 |

| Figure 5.5 – Click-based controller design for the EDL stages                                                                                              | 67 |

| Figure 5.6 – Speculative handshake protocol timing diagram with the Click-based con-                                                                       |    |

| troller                                                                                                                                                    | 68 |

| Figure 5.7 — Delay lines test scenario with Blade design                                                                                                   | 72 |

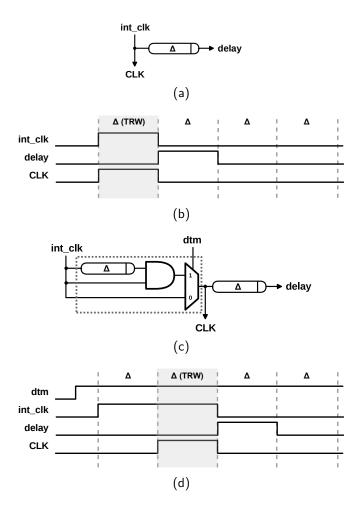

| ı | Figure $6.1 - (a)$ Original Blade burst-mode controller CLK output circuit. (b) Timing          |     |

|---|-------------------------------------------------------------------------------------------------|-----|

|   | diagram of the original controller circuit. (c) Modified CLK output circuit. (d)                |     |

|   | Timing diagram of the modified circuit                                                          | 78  |

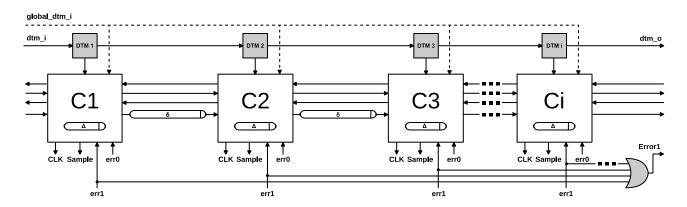

| ļ | Figure 6.2 – An alternative design with individual control over the $dtm$ signal                | 79  |

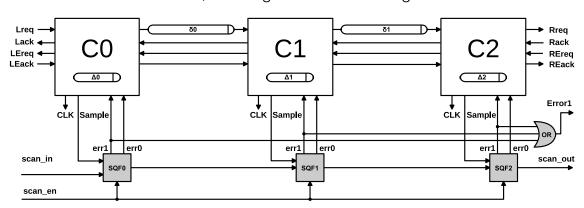

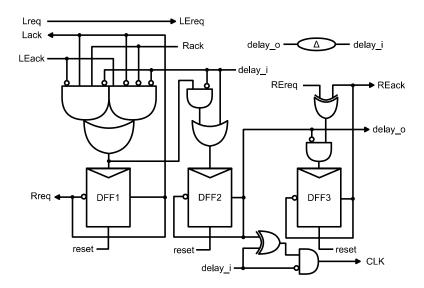

|   | Figure A.1 — Click-based token controller for EDL stages                                        | 99  |

| l | Figure A.2 — Click-based controller circuit                                                     | 99  |

| l | Figure A.3 — Click-based token controller circuit                                               | 100 |

| I | Figure A.4 $-$ Click-based controller for EDL stages modified for the delay test mode $(dtm)$ . | 100 |

|   |                                                                                                 |     |

## LIST OF TABLES

| Table 3.1 – Summary of timing resilient architectures                                     | 43  |

|-------------------------------------------------------------------------------------------|-----|

| Table 4.1 – TetraMAX stuck-at fault summary report for an EDL block                       | 48  |

| Table 4.2 - Relevant effects for the fault classification                                 | 53  |

| Table 4.3 - Blade EDL classification for the stuck-at fault model. Timing Violation (TV). | 54  |

| Table 4.4 – Blade EDL classification for the propagation delay fault model. Timing        |     |

| Violation (TV)                                                                            | 54  |

| Table 4.5 $-$ Blade EDL fault coverage obtained per test approach. (*) Fault Detected     | 55  |

| Table 4.6 - TEDL operation modes and their expected outputs                               | 58  |

| Table 4.7 - EDL vs. TEDL area overhead with the Plasma CPU case study                     | 60  |

| Table 4.8 – Comparison of Plasma-EDL vs Plasma-TEDL in terms of area ( $\mu m^2$ )        | 60  |

| Table 5.1 – List of undetected faults in the Burst-Mode controller                        | 66  |

| Table 5.2 - Comparison of Burst-Mode controller vs Click-based controllers in terms of    |     |

| area                                                                                      | 70  |

| Table 6.1 – Fault coverage for critical paths of Blade implementations of the Plasma      |     |

| CPU and XTEA crypto core                                                                  | 81  |

| Table 6.2 - Comparison between Blade implementations with and without the proposed        |     |

| DTM circuitry. Blade Plasma vs Blade Plasma-DTM (PDTM) and Blade XTEA                     | 0.1 |

| vs Blade XTEA-DTM (XDTM) in terms of area                                                 | 81  |

| Table 7.1 – Synthesis results for the Blade XTEA (B-XTEA) and Blade Plasma (B-            |     |

| Plasma) designs with scan DfT approach [JUR18a] and the implementations of                | 0.4 |

| this work                                                                                 | 84  |

| Table 7.2 – Supported fault models by the proposed test methods for each Blade block.     | 85  |

| Table 7.3 – Test phase classification of the proposed test methods                        | 85  |

| Table 7.4 - High level test phase comparison with three different approaches for testing  |     |

| timing resilient circuits                                                                 | 86  |

#### LIST OF ACRONYMS

ATPG – Automatic Test Pattern Generation

$\mathsf{BIST}-\mathsf{Built}$ -in  $\mathsf{Self}$ -test

DC - Detection Clock

DFT - Design for Testability

DIB - Delayed-Input-Based

DSTB - Double Sampling With Time Borrowing

DVS - Dynamic Voltage Scaling

EDA - Electronic Design Automation

EDL - Error Detection Logic

EDS - Error Detecting Sequential

ERR\_NST - Errors in the Next Stage

ERR\_ST - Errors in the Faulty Stage

GALS - Globally Asynchronous Locally Synchronous

ITRS - International Technology Roadmap for Semiconductors

LPD - Longer Propagation Delay

LSSD – Level Sensitive Scan Design

MSFF - Master-Slave Flip-Flop

PH - Pipeline Halted

PLA - Programmable Logic Array

PST - Pipeline Output Stuck at a Value

PVT - Process, Voltage and Temperature

RTL – Register-Transfer Level

RTZ - Return-to-Zero

SDF - Standard Delay Format

SLB - Shadow-Latched-Based

SPD - Shorter Propagation Delay

SQF - Scan Q-Flop

SSI - Small Scale Integration

ST0 - Stuck-at-0

ST1 - Stuck-at-1

TD - Transition Detector

TDC – Time to Digital Converter

TDTB - Transition Detector With Time Borrowing

TEDL – Testable Error Detection Logic

TEDL – Testable Error Detection Logic

TRW - Timing Resiliency Window

TV – Timing Violation

UN – Undetectable

VLSI – Very Large Scale Integration

### **CONTENTS**

| 1     | INTRODUCTION                                                | 20 |

|-------|-------------------------------------------------------------|----|

| 1.1   | OBJECTIVES                                                  | 22 |

| 1.2   | CONTRIBUTIONS                                               | 22 |

| 1.3   | DOCUMENT STRUCTURE                                          | 24 |

| 2     | CONCEPTS                                                    | 25 |

| 2.1   | DESIGN FOR TESTABILITY                                      | 25 |

| 2.2   | OVERVIEW ON STUCK-AT AND DELAY FAULT MODELS                 | 26 |

| 2.3   | ASYNCHRONOUS CIRCUITS                                       | 27 |

| 2.4   | TIMING RESILIENT ARCHITECTURES                              | 29 |

| 3     | STATE OF THE ART                                            | 31 |

| 3.1   | TIMING RESILIENT TEMPLATES                                  | 31 |

| 3.1.1 | RAZOR                                                       | 31 |

| 3.1.2 | RAZOR II                                                    | 31 |

| 3.1.3 | RAZOR LITE                                                  | 32 |

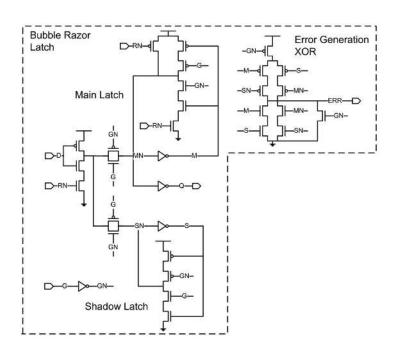

| 3.1.4 | BUBBLE RAZOR                                                | 33 |

| 3.1.5 | TRANSITION DETECTOR WITH TIME BORROWING AND DOUBLE SAMPLING |    |

|       | WITH TIME BORROWING                                         |    |

| 3.1.6 | SAFE RAZOR                                                  |    |

| 3.1.7 | BLADE TEMPLATE                                              |    |

| 3.1.8 | SHARP AND ERROR DETECTING LATCH                             |    |

| 3.2   | TESTING TIMING RESILIENT CIRCUITS                           |    |

| 3.3   | TESTING ASYNCHRONOUS CIRCUITS                               |    |

| 3.4   | STATE OF THE ART CONCLUSION                                 | 43 |

| 4     | ERROR DETECTION LOGIC TESTABILITY                           | 44 |

| 4.1   | BLADE EDL                                                   | 44 |

| 4.2   | ATPG FAULT COVERAGE ANALYSIS                                | 46 |

| 4.2.1 | TEST SCENARIO                                               | 46 |

| 4.2.2 | FAULT COVERAGE RESULTS                                      | 47 |

| 4.3   | BEHAVIORAL FAULT COVERAGE ANALYSIS                          | 47 |

| 4.3.1 | FAULT SIMULATION ENVIRONMENT                                | 48 |

| 4.3.2 | STUCK-AT FAULT ANALYSIS                       | 50 |

|-------|-----------------------------------------------|----|

| 4.3.3 | DELAY FAULT ANALYSIS                          | 51 |

| 4.3.4 | DISCUSSION ABOUT THE FAULT EFFECTS ON THE EDL | 52 |

| 4.3.5 | FAULT CLASSIFICATION                          | 53 |

| 4.4   | TESTABLE ERROR DETECTION LOGIC                | 55 |

| 4.4.1 | PROPOSED ARCHITECTURE                         | 56 |

| 4.4.2 | TEDL OPERATIONAL MODES                        | 58 |

| 4.4.3 | FAULT CLASSIFICATION                          | 58 |

| 4.4.4 | TEDL CASE STUDY: PLASMA CPU                   | 59 |

| 4.4.5 | FAULT COVERAGE                                | 59 |

| 4.4.6 | AREA COMPARISON                               | 60 |

| 5     | CONTROLLER TESTABILITY                        | 62 |

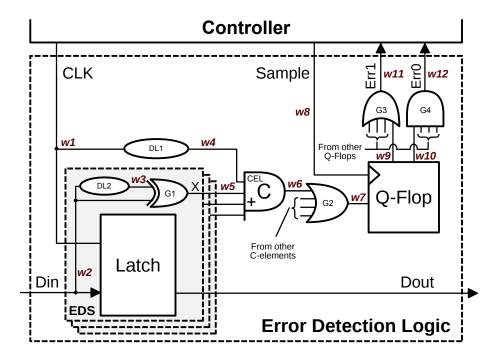

| 5.1   | BLADE CONTROLLER                              | 62 |

| 5.1.1 | STUCK-AT FAULT ANALYSIS                       | 64 |

| 5.1.2 | FAULT COVERAGE                                | 65 |

| 5.2   | CLICK-BASED CONTROLLER                        | 66 |

| 5.2.1 | FAULT COVERAGE                                | 69 |

| 5.2.2 | AREA COMPARISON                               | 70 |

| 5.3   | DELAY LINES TESTABILITY                       | 71 |

| 5.3.1 | PROPOSED METHOD                               | 71 |

| 5.3.2 | TEST ARCHITECTURE                             | 72 |

| 5.3.3 | TEST PROCEDURE                                | 73 |

| 5.3.4 | TEST SIMULATION EXAMPLE                       | 74 |

| 6     | DELAY FAULT TESTING OF CRITICAL PATHS         | 76 |

| 6.1   | PROPOSED TEST METHOD                          | 77 |

| 6.1.1 | TEST ARCHITECTURE                             | 77 |

| 6.1.2 | YIELD IMPROVEMENT AND AGING MONITORING        |    |

| 6.2   | EXPERIMENTS AND RESULTS                       | 80 |

| 7     | CONTRIBUTIONS OVERVIEW                        | 83 |

| 7.1   | SCAN COMPARISON                               | 83 |

| 7.2   | PROPOSED TEST METHODS APPLICATION             | 84 |

| 8     | CONCLUSION                                    | 88 |

|     | APPENDIX A – Click Controllers | 99 |

|-----|--------------------------------|----|

|     | REFERENCES                     | 92 |

| 8.2 | FUTURE WORKS                   | 89 |

| 8.1 | CONTRIBUTIONS                  | 88 |

#### 1. INTRODUCTION

Energy efficiency has become one of the most constant and important demands for contemporary applications, such as for mobile devices, high-performance data centers, and embedded systems. As VLSI design technologies approach more and more in the domain of low power, timing margins become a significant factor when designing traditional synchronous circuits with optimal clock period. These circuits must incorporate timing margins to ensure correct operation under worst-case conditions. The designer must account for timing variability due to the manufacturing process, circuit aging and circuit operation under a wide range of temperatures. Also, voltage supply must also be conservative, even though the chip has the potential to operate at lower voltages, which could help to reduce energy consumption. These timing uncertainties increase the delay margins that must be incorporated to the clock period, which limits the performance gains and increases the power consumption.

According to the 2011 ITRS (International Technology Roadmap for Semiconductors) [ITR11], one of the main challenges in the development of modern integrated circuits is the distribution of a single clock signal for controlling the entire circuit. The asynchronous design style removes the need of a global clock signal, thus eliminating problems related to clock skew and clock distribution. Instead, synchronization occurs using a handshake protocol between circuit elements. Asynchronous circuits are often implemented with one of two designs styles, quasi-delay-insensitive (QDI) and bundled-data (BD). The first one embeds a completion signal in the data representation, which makes the design robust to PVT variations [BEE07], but they are often larger (4x) if compared to traditional synchronous implementations. The second one presents lower area than QDI, but similar to synchronous circuits, they must also be implemented with sufficiently large margins to account for PVT variations. Regarding these timing margins in BD designs, different solution were proposed, such as duplicating the BD delay lines [CHA10] and constraining the design to regular structures such as programmable logic array (PLA) [JAY06].

Timing resilient architectures also emerged as a promising solution to alleviate these process, voltage and temperature (PVT) timing margins in synchronous designs [ERN03] [DAS09] [FOJ13] [KWO14] and in asynchronous BD designs [HAN15] by allowing timing violations. However, these architectures need additional circuitry to detect and recover from these timing violations, leading to high area and recovery penalties. Moreover, some of these architectures are susceptible to metastability problems [BEE14] that can prevent their use.

The Blade template [HAN15] is an alternative that combines the advantages of the asynchronous BD designs and timing resilient techniques to alleviate timing margins and address the metastability issues of previous works. Blade uses two reconfigurable delay lines and error detection logic to detect timing violations coupled to a novel speculative handshake protocol that improves average-case performance. A Blade circuit can achieve as much as 30% power reduction at the same performance, when compared to a similar synchronous circuit, for an area overhead of about 10%. Despite these promising results and increasing evolution of timing resilient architectures,

Blade's practical usage (as other timing resilient circuits) is still hindered by the challenges regarding testability. In general, the Design for Testability (DfT) is a well established research area. Even for asynchronous circuits a lot has been done in the last decades [PAG92] [KHO94] [PET95b] [RON96a] [PET97] [KAN99] [BER02] [BEE03] [SHI05] [GIL06] [RON15].

In classic design style (synchronous non-timing resilient) the most common DfT approach is to apply scan chains to add observability and controllability, and the internal states of the circuit can be initialized by test patterns and the resulting computation of these patterns extracted for analysis. It is further explained later that the fault models (e.g., stuck-at and delay) for synchronous and asynchronous circuits are the same. The difference is how fault effects express themselves. Another difference that affects the testability of asynchronous circuits is the absence of a global clock, which provides a lock-stepped computation that eases the test control on synchronous circuits. Some works address this problem by adding a synchronous test mode to the asynchronous implementation [BEE03], so that a dedicated clock controls the sequential elements only during the test. In this scenario, traditional static timing analysis is performed to identify critical paths in the circuit, and scan-based structural approach with automatic test pattern generator (ATPG) is applied for testing these paths. However, with increasing delay variations in modern technologies, static timing analysis becomes inaccurate [KRS98], even for the classic synchronous design approach. With timing resilient circuits, testing can become even more complicated, since now the timing analysis must not only account for the PVT delay variabilities but it must also consider that a given path can produce timing violations that are only observable and handled during at-speed functional operation.

Delay fault testing of timing resilient circuits is fundamentally different from testing conventional circuits because the former tolerates some timing violations, and not all timing violations become a fault. The work of Yuan [YUA13] is one of the first to address the testing challenges of timing resilient architectures. Yuan proposed a scan-based approach for testing a synchronous timing resilient architecture, where the error detection logic is reused as a fault detection mechanism for path delay faults. To accomplish this task a clock divider and a duty-cycle controller are responsible for creating specific clock configurations that allow delay fault detection through the detection mechanism.

Although the work of Yuan presents a possible solution for testing Blade through a dedicated synchronous mode implementation, the proposed scan design is custom made for the analyzed architecture, and also rely on an additional clock divider and a duty-cycle controller circuitry, which leads to another critical aspect of testing timing resilient architectures. As already mentioned, detection mechanisms in resilient circuits incur area overheads. Thus, the area for test circuitry is constrained. For example, when comparing Blade [HAN15] and Bubble Razor [FOJ13] to a classical synchronous design, the overall area overhead for the Blade implementation is 8.4%, and 21% increase in combinational logic and 280% in the sequential area for the Bubble Razor implementation. The area overhead for DfT on Bubble Razor can be prohibitive, mainly due to the significant increase in sequential area which leads to longer scan chains.

In this sense, the usage of non-standard sequential components in asynchronous circuits hinders the scan-based approach because it incurs in high area penalties. On the other hand, asynchronous designs have some advantages over synchronous regarding its testability. For instance, a stuck-at fault in the asynchronous controller can halt the entire circuit, making such fault detectable with a functional test [PAG92]. Furthermore, timing resilient circuits provide constant time checking, which can be explored for concurrent testing during functional operation.

#### 1.1 Objectives

The Thesis general objective is to demonstrate that the Blade template, with few proposed improvements, is more than an asynchronous timing resilient template. It is a possible DfT approach for asynchronous BD design style, that can cover stuck-at and path delay faults in Blade's specific modules through different testing phases, from online testing to structural testing. The proposed implementation present lower area overheads when compared to classic scan approach, and increased yield and aging properties when compared to synchronous timing resilient and non-timing resilient designs. To reach this goal, the following specific objectives were addressed during this Thesis:

- Implement a test environment to simulate and analyze the behavior of stuck-at and path delay faults on Blade: This includes the description of a high-level simulation environment to experiment and validate different approaches for testing Blade.

- Propose a test method for detecting faults in Blade: A circuit implemented with Blade is divided into four blocks: (i) controller; (ii) error detection logic; (iii) delay lines; (iv) data path. Each block is individually analyzed for its testability, and a method for detecting stuck-at and/or path-delay faults is presented;

- Propose alternative implementations to improve fault coverage and area overhead

in Blade: A design implementation aiming testability to improve fault coverage and area

overhead for the proposed test method. Thus alternative designs of the controller and error

detection logic are considered;

- Modify the Blade design flow to allow automatic insertion of the proposed test methods: One goal of this work is to modify Blade's original synthesis flow to support automated insertion of the proposed test methods;

- Evaluate area overhead and fault coverage of the proposed implementations: The area overhead and fault coverage of each block is compared to the original implementation.

#### 1.2 Contributions

The main contributions of the Thesis are:

- A fault classification method for Blade: A fault classification method and the fault analysis

of Blade's error detection logic was proposed and published in [KUE16] (Section 4.3). The

presence of unconventional sequential cells inside the error detection logic prevents the use of

standard ATPG. In this case, the fault classification relates behavioral patterns generated by

the detection logic to existing faults;

- 2. **A testable error detection logic for Blade:** Based on the fault analysis of the original error detection logic, a testable architecture of this block was proposed (Section 4.4). This approach removes the necessity of making the data path scannable. Instead of standard ATPG, faults are detected through the proposed fault classification method;

- 3. A Click-based controller for Blade: A controller with a single internal delay line implementation using Click [PEE10] was proposed. (Section 5.2). The Click-based design overcome a limitation of the original Blade flow where the original Burst-Mode controller could not be further optimized by the synthesys tool. Moreover, it presents higher fault coverage with functional testing and lower overall area than the original controller;

- 4. A method for testing delay lines with Blade: An offline method for testing the Blade delay lines according to the design specification and constraints (Section 5.3). Timing resilient circuits account for process variabilities in the data path, but not for process variability in Blade's delay lines. Thus a method for properly measuring the path delay of the delay elements is proposed;

- 5. A new method for testing path delay faults in critical paths: A concurrent test method for detecting path delay faults in the critical path was proposed (Chapter 6). Path delay faults are detected by transforming the error detection logic into a fault detection mechanism. The proposed method presents minimal impact in the area while expanding Blade's usage to yield and aging improvements.

The following papers were derived from this Thesis:

#### As first author:

- On the Reuse of Timing Resilient Architecture for Testing Path Delay Faults in Critical Paths, F. A. Kuentzer, L. R. Juracy, and A. M. Amory: accepted for publication in DATE 2018 (Qualis A1);

- Fault Classification of the Error Detection Logic in the Blade Resilient Template, F. A.

Kuentzer, L. R. Juracy, and A. M. Amory: published on IEEE ASYNC 2016 (Qualis B2)

- Testable Error Detection Logic Design Applied to an Asynchronous Timing Resilient

Template: submitted to IEEE ISCAS 2018 (Qualis A1);

#### As co-author:

- Optimized Design of an LSSD Scan Cell, L. R. Juracy, M. T. Moreira, F. A. Kuentzer, and A. M. Amory: published on IEEE Transaction on VLSI 2017 (Qualis A1);

- Testable Q-Flop: A Scannable Metastability-free Memory Element, L. R. Juracy, M. T. Moreira, F. A. Kuentzer, and A. M. Amory: accepted for publication in IEEE Transaction on VLSI 2018 (Qualis A1);

- An LSSD Compliant Scan Cell for Flip-Flops, L. R. Juracy, M. T. Moreira, F. A. Kuentzer,

and A. M. Amory: published on IEEE ISCAS 2018 (Qualis A1);

#### 1.3 Document Structure

The rest of the document is organized as follows. Chapter 2 provides relevant background information. Chapter 3 presents state of the art in timing resilient circuits and their testability. This chapter also summarizes the main works in asynchronous BD design testing. Chapter 4 presents the fault analysis and fault classification for Blade's error detection logic along with the proposed testable design. Chapter 5 evaluates the functional testing coverage for the original controller and presents an alternative design that achieves higher coverage. Also, a method for testing the delay lines is proposed. Next, Chapter 6 explores the reuse of Blade's error detection mechanism for detecting path delay faults in the critical paths. Chapter 7 summarizes the different test methods proposed in this Thesis and their applications. All proposed methods were integrated into two case studies to evaluate area overhead and compare these with the classic scan approach. Finally, Chapter 8 presents the final considerations of this work and discusses future works.

#### 2. CONCEPTS

This Chapter presents some basic concepts on DfT, an overview of two common fault models, asynchronous circuits and some relevant BD templates, as well as timing resilient architectures.

#### 2.1 Design for Testability

As designs moved from small scale integration (SSI) to VLSI the complexity to test such circuits became harder. A standard approach to test these VLSI circuits during the 1980s relied mainly on fault simulation of functional patterns to extract a fault coverage. These patterns were developed to exercise the internal states and detect manufacturing defects. Several functional patterns were applied to increase fault coverage. Unfortunately, this approach typically reached a fault coverage around 80%. The design quality dropped, and the costs increased, which led to the development and deployment of Design for Testability (DfT).

The first challenge was to find simpler ways of exercising all internal states of design and increase fault coverage. Initially, ad hoc techniques were proposed to aid the testability and improve the controllability and observability of the circuit. These techniques relied on making local modifications, such as insert test points, avoid combinational feedback loops, avoid asynchronous logic and partition the circuit into small blocks. Even though these methods have substantially improved the testability of a design, it was difficult to reach more than 90% of fault coverage for large designs. Their effects are not systematic, and they have to be custom made for each new project, often with unpredictable results.

An alternative approach for controlling and observing the internal states of sequential circuits is the structured DfT, which allows direct external access to internal storage elements. These storage elements with direct external access are called scan cells. This approach allows full controllability and observability of internal states of the design and reduces the problem of testing the sequential circuit to testing the combinational logic, for which many solutions and tools for automatic test pattern generation (ATPG) already existed.

Scan design is probably the most popular structured DfT approach. Scan designs have the storage elements replaced by scan cells to gain external access. These cells are interconnected to additional scan input ports and shared/additional scan output ports, forming one or more shift registers, called scan chains.

Numerous scan cell designs and scan architectures have been developed. The full-scan architecture consists in replacing all memory elements by scan cells, and combinational ATPG is used for test generation. In partial-scan architecture, only a subset of memory elements is replaced by scan cells and connected into the scan chain, but sequential ATPG is typically used for test generation, increasing the test complexity. The designer's decision will depend on project constraints

regarding area and performance overheads, test complexity and the fault coverage goal. As for the scan technique, the edge-triggered mux-D scan [BUS02] and the level sensitive scan design (LSSD) [EIC77] [JUR17] are best known and most widely practiced for synchronous circuits cells types.

Scan design has also become the basis of more advanced DfT techniques, such as logic built-in self-test (BIST). In such architecture, circuits that generate test patterns and analyze the output responses of the functional circuitry are embedded in the chip or elsewhere on the same board where the chip resides. These techniques emerged as an alternative to reduce the high test expenses of traditional test techniques that use ATPG tools, and to alleviate some test problems that appeared as the semiconductors manufacturing technologies advanced, for instance, the test of assembled boards, system test, periodic maintenance and repair test [WAN06a].

Despite the extensive use of the scan-based approach for testing sequential designs in at speed-tests, functional testing is an alternative way of testing a circuit, that consists in identifying the functions that the circuit is expected to perform, create input data patterns based on these function specifications and determine the expected output pattern for each input. As presented in [KRS03], functional testing may translate into delay fault under-testing, where non-functional delay paths are not covered. On the other hand, structural testing can over-test paths that are not functionally activated, resulting in yield loss. Software-based functional testing can be used to improve the fault coverage of processors [LAI00] [KRA05] [SIN06]. Functional test can also be applied in-field to check the reliability of a device [TEH11].

#### 2.2 Overview on Stuck-at and Delay Fault Models

Fault models are a computational abstraction used to represent defects [MOU00]. In the context of manufacturing defects, the stuck-at fault model is one of the most common to detect defects in integrated circuits. The fault is modeled by assigning a fixed logic value (0 or 1) to a circuit wire. A line consists of an input or output of a logic gate, flip-flop or latch. The most popular is the single stuck-at-1 and single stuck-at-0. For example, a logic OR gate of two inputs with stuck-at-0 at the output will never assume the logical value 1, even in the presence of logic value 1 at both its inputs.

Another type of manufacturing fault is a speed defect, which can be modeled as a delay fault. A circuit has a delay fault when its output fails to reach the correct value within a predefined time constraint. A signal transition is required to observe a delay defect, which involves the application of vector pairs that affect the design delay significantly. One of these vectors is responsible for initializing the circuit under test to a known state. The other is responsible for stimulating the circuit so that, if the delay of a location or path exceeds the timing constraints of the project, invalid values are captured by sequential cells or primary outputs, deviating from the expected values, which characterizes the fault.

Many delay fault models and test techniques have been proposed and used in digital circuits [TEH08] [RED09] [BUS02] [JHA03] [CRO99]. The three basic models for delay faults are transition fault model, gate-delay fault model, and path delay fault model [KRS98]. The transition fault model [LEV86] [CHE93] assumes that the defect affects a single gate in the circuit, and each gate can be associated with a slow-to-rise and a slow-to-fall transition fault. To detect a fault, the transition model assumes that the extra delay prevents a transition from reaching a primary output at the observation time. The advantage of the transition fault model is that the number of faults is linear to the number of gates in the circuit, but expect that the delay fault is large enough to be observed might not be realistic.

The gate delay fault model [CAR87] [PRA97] also assumes that the delay fault affects only one gate, but unlike the transition model, the gate delay fault model implies that an increase in delay might affect the performance. Since it takes into account the circuit delays, it is related to a quantitative model and the transition model to a qualitative one. The limitations of the gate delay model are similar, due to the single gate fault assumption, that may fail to detect delay faults that are a sum of small delay defects. On the other hand, the path delay fault model [SMI85] can detect small distributed delay defects. The delay of a path represents the sum of the gate delays and interconnections on the path. A delay defect on a path can be observed by applying a transition at the beginning of the path and observing its effect during the propagation through this path. A limitation of this fault model is that the number of paths in the circuit can be very large, most often exponential on the number of gates. For this reason, not all paths are tested. Usually, the longest path containing a given signal or paths where the expected delay is greater than a specified threshold are selected.

#### 2.3 Asynchronous Circuits

Most currently fabricated digital circuits follow the paradigm of synchronous clocked design. In synchronous circuits, all components share a common discrete notion of time defined by a global clock signal that significantly simplifies their design. On the other hand, asynchronous circuits have no common notion of a discrete time. To perform synchronization, communication, and sequencing of operations, asynchronous circuits use local handshake between communicating components. In synchronous terms, it would be like having a circuit where registers are only clocked where and when needed.

Asynchronous designs have showed advantages in different aspects compared to synchronous designs, like: (i) low power consumption, due to power consumption in standby mode; (ii) high operation speed, where speed is determined by local latencies instead of global worst-case delay (the clock period); (iii) less emission of electromagnetic noise; (iv) robustness towards process, voltage, and temperature variations; (v) no clock distribution and skew [SPA01].

The choice of a handshake protocol and a data encoding scheme is called a template [BEE10]. Currently, there are two main design styles of asynchronous templates, QDI and BD [BEE10]. The first relies on multi-rail data encoding, where the completion signal is embedded into the data representation. For instance, the dual-rail protocol uses two wires to represent one bit of data and the corresponding request signal. Even though they provide relaxed timing constraints, the circuits from this family are usually larger and have higher power consumption than their synchronous counterparts. Since BD is the design style used in the asynchronous timing resilient template that will be further treated here, the discussion focus on BD templates only.

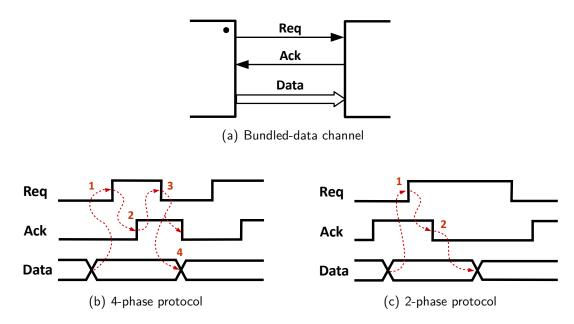

BD templates use standard Boolean encoding to represent information, and separate, request and acknowledge wires, are bundled with data signals to provide synchronization, see Figure 2.1(a). BD designs can employ 2-phase or 4-phase handshake protocols. The 4-phase term refers to the number of communication actions. Figure 2.1(b) illustrates the waveform for a possible 4-phase protocol: (1) the sender issues data and sets Req high, (2) the receiver stores the data and sets Ack high, (3) the sender responds by taking Req low (at this point data is no longer guaranteed to be valid) and (4) the receiver acknowledges by taking Ack low. At this moment the sender may initiate a new communication cycle.

Figure 2.1 - (a) Bundled-data block diagram. (b) The 4-phase handshake protocol. (c) The 2-phase handshake protocol.

The 4-phase protocol has the disadvantage of requiring return-to-zero (RTZ) transitions that cost unnecessary time and energy, and potentially reduce the performance of the circuit. The 2-phase bundled-data protocol shown in Figure 2.1(c) avoids the RTZ. The request and acknowledge are encoded as signal transitions. There is no consensus about the protocol type, while the 2-phase improves performance, the 4-phase requires less complex control circuitry.

There are different design styles for implementing BD control blocks. The main available templates in the literature use 2-phase handshake protocols. The concept of Micropipelines, introduced in [SUT89], is implemented with particular capture-pass latches that are event-controlled,

being these capable of sensing transitions at its inputs. Another approach is Mousetrap [SIN07], which implements 2-phase BD circuits using level-sensitive latches and XOR gates.

A more recent template is Click [PEE10]. Instead of using latches and C-elements, that are common in many asynchronous designs, the authors proposed a 2-phase BD template that only uses edge-triggered flip-flops in both data path and control path. This approach facilitates the asynchronous circuit design flow using standard (third-party) EDA tools, especially for physical synthesis and static timing analysis.

Another template is a 2-phase BD that, different from the previous ones, does not avoid RTZ. In the GasP [SUT01] template, instead of separate request and acknowledgment wires, a single wire represents the full or empty states. With this template, in the first phase the sender rises the state wire when valid data is available, and in the second phase, the receiver lowers the same state wire, indicating that the data was consumed.

#### 2.4 Timing Resilient Architectures

Scalability in circuit manufacturing processes allowed performance improvements and increased energy efficiency, but it also led to undesirable side effects, such as PVT variations, and reliability issues due to transistor degradation, which can cause premature failure of the system [TSC09]. Circuit designers add delay margins to compensate for PVT variations and achieve good yield, thus affecting system performance. An alternative for removing some of the increasingly large delay margins is the timing resilient design technique.

Different research areas use the resilient term. In physics, for instance, resiliency is a property of materials that accumulate energy when subjected to stressful situations, such as ruptures. In other words, resiliency is the ability to return something to its natural state, especially after some critical or unusual condition. Thus, a circuit is said to be resilient when it can recover its normal operating status, even after an internal error or caused by external factors.

Different timing resilient architectures have been proposed until now [ERN03] [DAS09] [FOJ13] [KWO14] [HAN15]. These techniques allow the circuit to operate with relaxed timing constraints that eventually cause a timing violation. For such cases, these techniques rely on some error detection logic and on an error recovery mechanism.

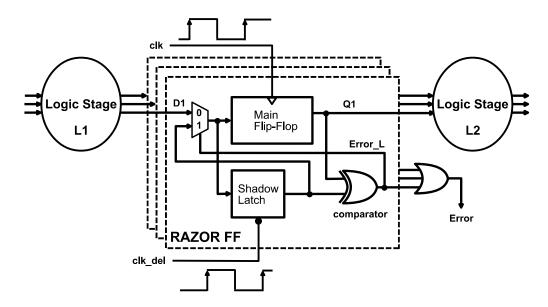

For instance, the Razor [ERN03] family was one of the first timing resilient architectures for synchronous circuits to be proposed. This synchronous approach consists in replacing flip-flops (FF) on critical paths of the circuit by special ones called Razor Flip-flops. Figure 2.2 presents the basic diagram of this implementation. The clk signal is designed with less pessimistic time margins, and it controls the regular FF (Main Flip-flop) data sampling, while the Shadow Latch data sampling is controlled by a delayed clock ( $clk\_del$ ) that meets the worst-case timing constraints that guarantee valid data at the output of the latch. The comparison between the values of the Main Flip-flop and the Shadows Latch flags a timing violation. The error signal causes the circuit to redirect the valid

Figure 2.2 – Razor flip-flop [ERN03].

data stored at the latch to be sampled by the FF with a one cycle penalty. The previous stage must stall, and data at the following stages must be flushed.

Timing resilient circuits benefit from average-case performance. They rely on the fact that errors have a low probability of occurrence and the recover penalties have a small effect on performance. At this point, the error rate becomes a vital parameter of this type of design. In this sense, it becomes a challenge to the designer to dominate and solve the trade-off between allowed error rate and the performance, power, and reliability of the circuit.

#### 3. STATE OF THE ART

This Chapter presents an overview of current timing resilient architectures found in the literature and their testability. The works are divided into four categories: Timing resilient architectures, covering the Razor family and its successive developments and the synchronous Blade template and other relevant timing resilient circuits; Testability of synchronous timing resilient circuits; Testability of asynchronous BD circuits since there are no previous works on testing asynchronous timing resilient circuits. The last section presents conclusions about these topics.

#### 3.1 Timing Resilient Templates

#### 3.1.1 Razor

The Razor architecture [ERN03] emerged as an alternative for eliminating worst-case safety margins by using a novel voltage management technique, where the processor operates with dynamic voltage scaling (DVS). As mentioned in Section 2.4, in this technique, Razor FFs replace FFs in critical paths of the circuit. The circuit then can have the supply voltage scaled down to the point of the first failure for a given frequency, eliminating all margins due to global and local PVT variation, thus resulting in energy savings. The supply voltage can be scaled even lower than the first failure point to achieve additional energy savings. In this case, a targeted error rate is deliberately tolerated, although this must be carefully considered, since the correction cost is 18 times more expensive regarding energy than regular operation, as in a 64-bit Kogge-Stone adder.

Based on a set of simulated benchmark experiments, an error rate of 1.5% allows average energy savings of 41% with a maximum performance slowdown of 6%. A 64-bit Alpha processor using the Razor technique was manufactured in a  $0.18~\mu m$  technology. The circuit operates at 200MHz, and the clock for the shadow latch was delayed by 1/2 the clock cycle from the system clock. Results also show the error detection and correction circuitry represent a 3.1% total power overhead in an error-free configuration.

#### 3.1.2 Razor II

Razor II [DAS09] is a simplification of the original Razor FF. The Razor II FF removes the error recovery mechanism from the original proposal and error recovery takes place through architectural replay. The authors based their new approach on the fact that the error rate at the point of the first failure is in the order of 1 error in 10 million cycles, which makes recovery energy negligible. Substantially below the point of the first failure, the energy saving was small ( $\approx 10\%$ ) compared to the energy gain from eliminating the PVT margins ( $\approx 35\%$  to 45%).

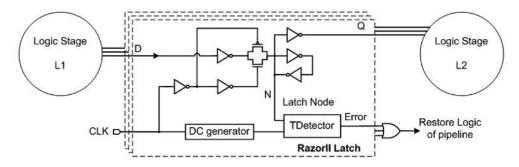

The Razor II FF uses a positive level-sensitive latch instead of a master-slave FF. It also combines a transition detector (TD) controlled by a detection clock (DC) as presented in Figure 3.1. Valid data is captured if data stabilizes before the rising edge of the clock. If data changes during the high-phase of the clock, while the latch is transparent, an error signal is flagged. To prevent valid data transition from being flagged as a timing violation, a short negative pulse on DC is used to disable the transition detector for a small period. It is equivalent to the propagation delay from D to Q after the rising edge of the clock. When a timing violation occurs, the whole pipeline is flushed, and the failing instruction is re-executed. If successive failures occur, the clock frequency is reduced by half during 8 cycles.

Figure 3.1 – Razor II flip-flop [DAS09].

As a case study, a 64-bit 7-stage Alpha processor featuring Razor II was manufactured in 0.13  $\mu$ m technology. Results show that with an error rate of 0.04%, energy savings reach up to 37.4%, if compared to the worst-case when the supply voltage is set to ensure correct operation. The total overhead due to the presence of the Razor II circuitry in error-free operation is up to 1.2% of the total power.

#### 3.1.3 Razor Lite

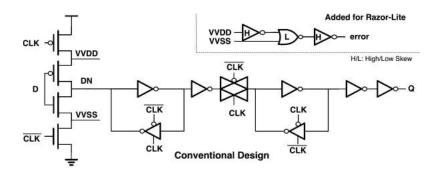

Razor-Lite [KWO14] uses a side-channel detection strategy compatible with standard D FF to reduce additional error detection circuitry. This approach is intended to well-balanced pipeline implementations, which present a large number of critical paths. Thus the number of FFs that must detect timing violations is high.

Figure 3.2 illustrates a conventional FF design and the added logic required by Razor-Lite. The additional circuit connected to the virtual VDD (VVDD) and virtual VSS (VVSS) rails of the FF acts as a transition detector. Under normal operation, after the rising edge of the clock VVDD and VVSS are kept charged and discharged, respectively, and no error is flagged. A timing violation is flagged if D changes after the rising edge of the clock. If D transition to logic level 0 VVDD is discharged through node DN and VVSS is charged if D transitions to logic level 1. After the falling edge of clock VVDD and VVSS are restored to their original state.

A 64-bit 7-stage Alpha architecture pipeline demonstrates the use of Razor-Lite. The processor was prototyped in 45nm SOI CMOS technology, and all 492 decode and execute registers,

Figure 3.2 – Razor-Lite schematic [KWO14].

which are the processor's critical path, were replaced by Razor-Lite registers. Error outputs are grouped via an OR-tree and recorded at a pipeline register. After the rollback, the clock frequency is reduced by half during 4 cycles to allow the problematic instruction to execute correctly. The total penalty for an error is 11 cycles. Razor-Lite circuitry increased area in 4.42% and power in 0.3%. Peak energy efficiency is improved by 83% compared to the baseline processor.

#### 3.1.4 Bubble Razor

Bubble Razor [FOJ13] is an architecturally independent approach to timing error detection and correction. Bubble Razor uses a two-phase latch-based data path instead of a flip-flop based data path. The error detection circuit presented in Figure 3.3 is similar to the one used in the original Razor. It is based on a shadow latch that captures the data before the main latch. An error is flagged if the value at the main latch changes after it becomes transparent.

Figure 3.3 – Bubble Razor schematic [FOJ13].

Error correction is accomplished by local stalling. When a timing violation is detected, an error signal (bubble) is propagated to neighboring latches, preventing them from becoming transparent. Propagating bubbles gate off clock pulses throughout the circuit. This is done by a clock gating logic connected at each stage and adds time for the correct data to arrive at the latch that identified the timing violation. Once a neighbor latch receives a bubble, the bubble is propagated to the next stage and so on. For the cases where loops are present, the authors propose a bubble propagation algorithm to avoid indefinite bubble propagation.

An ARM Cortex-M3 microcontroller with Bubble Razor was implemented at a 45nm SOI CMOS technology. A flop-based design was converted to a latch-based implementation. The error detection logic was added to all latches, resulting in 87% area overhead. When considering reduced margins, this implementation enables 100% throughput increase or 60% energy reduction when compared to the microcontroller with worst-case timing margins.

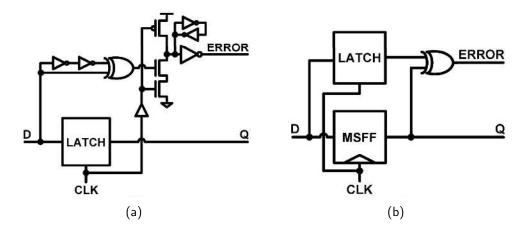

#### 3.1.5 Transition Detector With Time Borrowing and Double Sampling With Time Borrowing

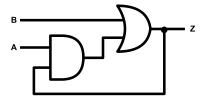

Bowman [BOW09] proposed two error detecting registers, the Transition Detector With Time Borrowing (TDTB) and the Double Sampling With Time Borrowing (DSTB), and also an instruction replay-based error recovery mechanism. The TDTB circuit illustrated in Figure 3.4(a) is a latch-based register that detects input transitions during the high phase of the clock. A data transition generates a pulse at the XOR output. The XOR output and the Clock feed a gate that produces the ERROR signal. This gate is equivalent to an asymmetric C-element, a sequential component used in asynchronous designs. This design removes the risks of metastability being propagated to the data path. However, there is still the risk of the error signal becoming metastable. This may happen if the data transitions occur slightly before the rising edge of CLK. In this case, the metastability is propagated to the control path, compromising circuit operation.

Figure 3.4 – (a) TDTB circuit [BOW09]; (b) DSTB circuit [BOW09].

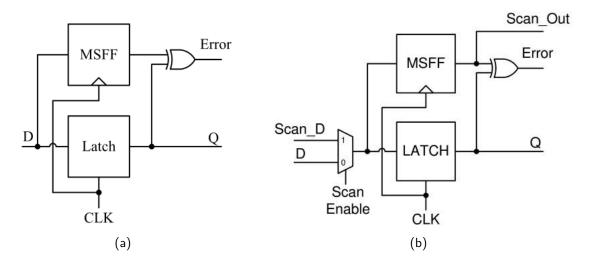

The DSTB depicted in Figure 3.4(b) replaces the transition detector of the TDTB by a shadow flip-flop. On the rising edge of CLK, the latch becomes transparent, and the input data

is sampled by the Master-Slave Flip-Flop (MSFF). The latch remains transparent during the CLK high phase. At the end of the CLK's high phase, if the values from the latch and the MSFF differ, an error is detected. Similar to TDTB, this approach eliminates data path metastability but also introduces the risk of metastability on the error signal.

The error recovery mechanism proposed is based on instruction replay. When a timing violation is detected, the erroneous data is invalidated, and the controller determines the appropriate instruction replay. During this process, the clock frequency is halved, and once the replay is complete, the clock is scaled back to its original frequency. A test chip using this technology was manufactured in a 65nm technology. Results show throughput gains up to 32% when operating at nominal supply voltage and up to 37% reduction in power consumption when reducing power supply while maintaining the nominal throughput.

#### 3.1.6 Safe Razor

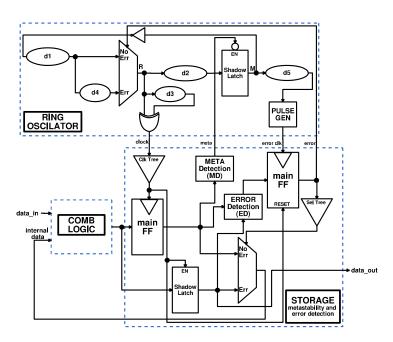

All known implementations are prone to failures due to the nondeterministic timing behavior producing metastability. SafeRazor [CAN15] is a Razor-based design that combines the Razor principle with globally asynchronous locally synchronous (GALS) design. This approach removes the metastability problems reported in [BEE14], and do not require a pipeline flush once a timing error is detected.

Figure 3.5 – SafeRazor module [CAN15]

Figure 3.5 shows the SafeRazor diagram. In the STORAGE block, a metastability detector and a timing error detector are implemented. If metastability is detected, the MD stalls the ring oscillator until resolving the metastability. If a timing error is detected, the *Err* input of the multiplexer inside the ring oscillator is selected and the cycle period is extended by the delay *d4*.

As a case study, a SafeRazor circuit with 3 GALS islands was implemented. Each island contains a 4-stage pipeline multiplier. Also, a standard flip-flop version and a Razor version were compared to SafeRazor. The designs were synthesized with Synopsys Design Compiler targeting 90nm standard cell library. Compared to the synchronous circuit, the total area overhead for Razor is 27.7%, while for the SafeRazor the overhead is 50.6%. The area increase is mainly due to the ring oscillator. The performance speeds up linearly, and for a higher operation frequency (60%) the performance is 15% better than Razor, while for a doubled frequency it is 7% worse.

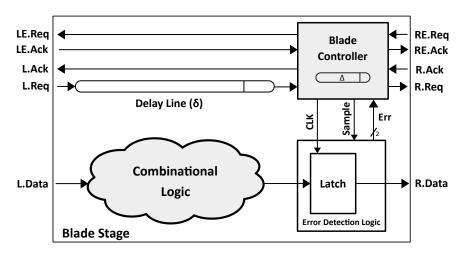

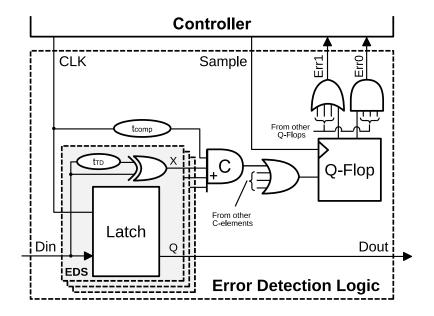

## 3.1.7 Blade Template

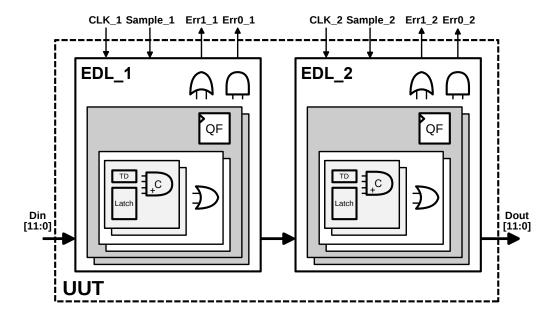

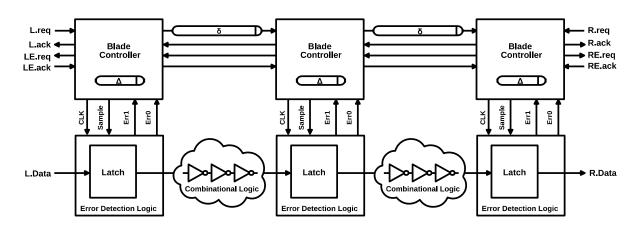

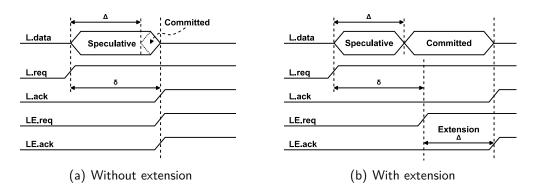

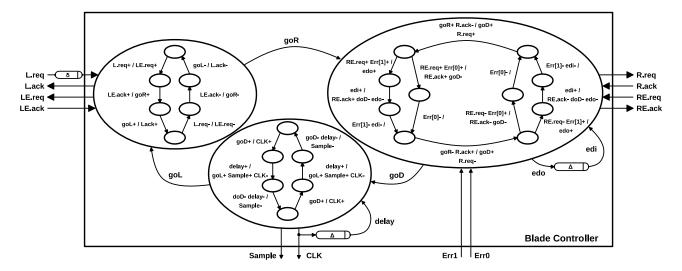

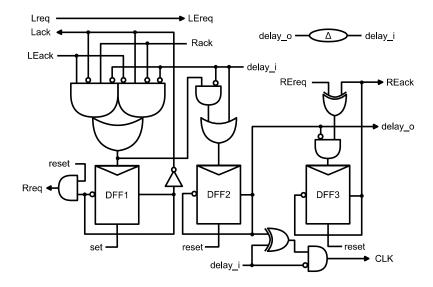

Blade [HAN15] is a bundled-data timing resilient asynchronous template that, similar to the SafeRazor [CAN15], was proposed to overcome metastability issues in many of the proposed timing resilient architectures reported in [BEE14], but also to reduce high timing error penalties originated by the recovering mechanism of resilient architectures. Figure 3.6 illustrates the basic Blade architecture. A circuit implemented with Blade can be divided into four main blocks: (i) controller; (ii) delay lines (iii); error detection logic (EDL); (iv) data path. The Blade controller communicates with other stages using typical bundled-data channels. The  $\delta$  delay controls the moment that data at the output of the combinational logic can be sampled and propagated through the latch. The  $\Delta$  delay defines the amount of time that the latch is transparent, and is defined as the timing resiliency window (TRW). A timing violation is flagged if data changes during the TRW. The delay values  $\delta$  and  $\Delta$  must be designed to be sufficiently large to cover the longest critical path in their corresponding pipeline stage.

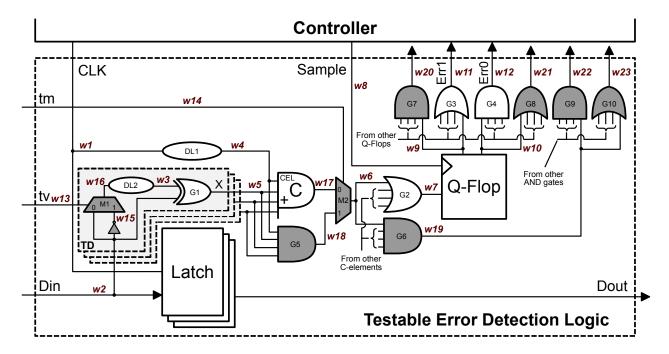

Figure 3.6 – Blade template [HAN15].

The EDL flags a timing violation by asserting its Err signal. To recover from the timing violation, the next stage delays by  $\Delta$  its latch opening, until the correct data is propagated through the combinational logic. The Blade controller then communicates with its neighbors using channel L/R and an additional error channel LE/RE. These two channels are used to implement a new form of asynchronous handshaking protocol, called *speculative handshaking* [HAN15]. The implementation

is divided into three interacting Burst-Mode state machines [FUH95]. A more complete description of these blocks is presented in the following Chapters along with their fault analysis.

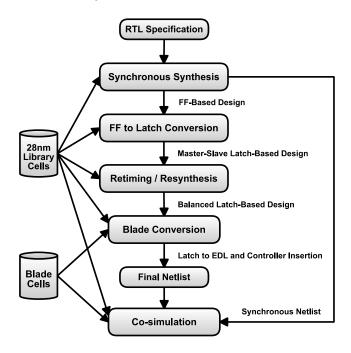

Blade's automated flow uses industry standard tools, including DesignCompiler and Prime-Time from Synopsys and NC-Sim from Cadence. A set of TCL and Shell scripts are used to automate the design flow, which converts a single CLK domain synchronous RTL design to an asynchronous Blade design. Figure 3.7 shows the synthesis flow and its five main circuit conversion steps:

Figure 3.7 – Blade flow, adapted from [HAN15].

- Synchronous Synthesis: The synchronous RTL description is synthesized to a flip-flop based design at a given clock frequency;

- 2. **FF to Latch Conversion**: Flip-flops are converted to a master-slave latches;

- 3. **Retiming**: The latch-based netlist is retimed using a target TRW. In this step latches that are near-critical path and thus should be converted to EDLs are identified;

- 4. **Resynthesis**: Minimize the area and timing overhead by reducing the number of EDLs. This is done by constraining some latches in near-critical path to have a delay no greater than the target frequency, which allows the use of standard latches rather than EDLs;

- 5. **Blade Conversion**: The resynthesized latch-based netlist is then converted to the Blade template. Clock trees are replaced by Blade controllers, delay lines, and error detection logic is also inserted, resulting in the final Blade netlist.

To validate the implementation a 3-stage version of the microprocessor Plasma [PLA14] targeting a 28nm FD-SOI technology is used as a case study. The circuit was converted from a 666MHz synchronous design to a Blade implementation with a TRW 30% of the clock period. After

retiming, a total of 456 latches were required to be converted to EDLs, and after the resynthesis, the number of EDLs decreased 27%. Results show that the overall area overhead of the Blade version is 8.4% when compared to the original synchronous design. The standard benchmark CoreMark was used to evaluate performance. Performance of the Blade version increased 19%, with an average frequency of 793MHz.

### 3.1.8 Sharp and Error Detecting Latch

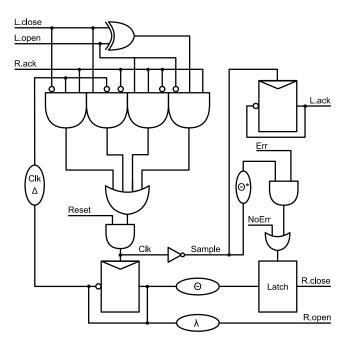

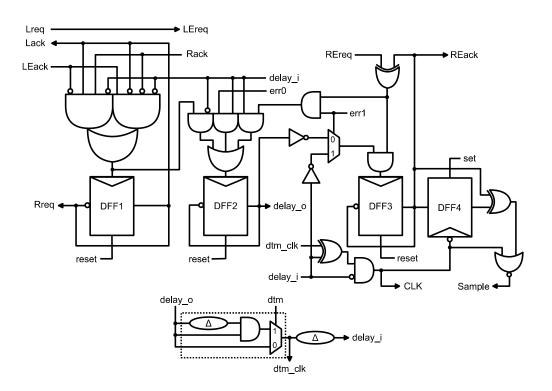

Sharp [WAU17] derived from the Blade template [BEE17]. As shown in Figure 3.8, there is one channel on each side of a controller. Both channels include three signals: Open, Close, and Acknowledge. The open signal tells the controller to open the latches and close tells to close the latches and acknowledge indicates that the close signal was received. The open signal speculates that the input data is valid, while the close signal guarantees a valid data.

Figure 3.8 – The Sharp controller [WAU17].

Sharp uses a two-phase protocol. Latches are only opened when all neighboring blocks acknowledge that their latches are closed. That means Clk goes high when the XOR output is low and R.ack transitions. Open and close signals control the TRW in a Sharp controller. Sharp uses error detecting latches (EDLs) to signal when data at the latches changes while the latches are transparent [HUA16]. If an error is captured while the clock is high, instead of delaying the opening of later stages, Sharp delays the closing of all the immediate downstream latches, so that valid data propagates through those stages. Simulation results show that Sharp achieves 8% higher throughput when compared to Blade controllers.

An important aspect of timing resilient circuits is the need to detect timing violations. However, the area and power overheads resulting from replacing conventional sequential elements

with their equivalent error detection version can be substantial. In this sense, Sharp uses a new EDL architectures to detect timing violations [HUA16]. The two novel elements are the shadow-latched-based (SLB) EDL, which favors robustness and sensitivity, and the delayed-input-based (DIB) EDL that favors lower energy. Results show that proposed designs can achieve as much as 11.2% less overall power consumption and 7.8% smaller area when compared to state-of-the-art EDLs TDTB [BOW09], Sense-amp [TAD16] and Charge-sharing [KIM15]. Despite these results, neither Sharp or the new EDLs have had their testability addressed.

## 3.2 Testing Timing Resilient Circuits

A conventional VLSI chip is defective if it cannot pass at-speed delay tests, but timing resilient circuits are inherently tolerant to timing violations [YUA13]. Therefore, the pass/fail criteria for these circuits need to be re-examined. Furthermore, the additional circuitry for timing resiliency, including the error detection logic and the recovery mechanism need to be fully tested.

There are few works in this area. In [ANA15] a Scan Razor flip-flop (SR-FF) is proposed. This work is focused on reducing the power consumption by reusing the existing additional circuitry of the Razor architecture to build a scan cell instead of adding a typical scan design. Another similar approach is the Time Dilation (TimeD) scan architecture proposed in [FLO08]. In this case, a classic mux-D is modified to act as a timing violation detector and recovery mechanism. Besides the support for traditional off-line scan testing, the TimeD architecture is suitable for online (concurrent) timing error detection and recovery. Like the previous work, the authors are more concerned with a design that presents low area and performance overheads but do not show results about the testability of the resilient circuit itself, neither address the supported fault models and fault coverage results. On the other hand, the work of [YUA13], besides the DfT circuit design, it also addresses the new challenges of testing timing resilient designs.

The work of Yuan [YUA13] is probably the first and only to the date that evaluates the problems of testing timing resilient circuits, or as the authors refer to, timing speculative circuits. The proposed test methodology is based on the DSTB design presented in [BOW09], that consists of a latch, a shadow master-slave FF (MSFF) and an XOR gate, as depicted in Figure 3.9(a). The latch operates as a data path memory element for regular computation, while the MSFF captures the input value for timing violation detection. The latch is transparent on the high clock phase while the MSFF samples at the rising edge of the clock. If a timing violation occurs the values stored at the latch and the MSFF will be different, and the XOR gate sets the error signal accordingly. Consequently, with such a timing speculator design, the high clock phase is the detection window for timing violations. The Scan-based version of the DSTB is shown in Figure 3.9(b).

The test flow presented by [YUA13] consists of three parts. First, static fault testing (e.g., stuck-at faults) is performed in the combinational logic and the Error Generation and Propagation (EGP) circuit that is used by the system recovery. Next, the delay test of the combinational logic

Figure 3.9 – (a) DSTB circuit [BOW09]; (b) Scan-based DSTB circuit [YUA13].

is performed, and at last, the delay testing of the EGP is conducted. As a way to identify delay faults that exceed the detection window, the authors propose that during the test, the clock cycle be increased, so that the high phase (detection window) is equivalent to the worst-case of the combinational logic. If a timing violation is identified at this stage, it means that when in normal operation the designed detection window is not able to detect a timing violation in the tested path. This test approach assumes clock cycle controllability. Results show 100% coverage for the EGP circuits, but despite the author's comments about the low DfT costs, numbers about area overhead are not explicitly shown. Even though the work has proposed an attractive solution for structural testing of path delay and stuck-at faults, the test methodology is designed for synchronous circuits, and the absence of a global clock may hinder the use of such approach with asynchronous timing resilient circuits.

# 3.3 Testing Asynchronous Circuits

As previously discussed in Section 2.3, asynchronous circuits promise advantages over synchronous circuits, such as lower power consumption, average-case rather than worst-case timing behavior, improved modularity and more tolerance towards PVT variations. Moreover, in [WOJ14], according to 2012 ITRS [ITR12], the asynchronous design style will be widely applied in future nanoelectronics. Even though this design style provides advantages, there are two factors that hinder its massive use: (i) lack of mature design tools; (ii) test related approaches.

From the test perspective, the primary difference between asynchronous and synchronous is the self-timed computation versus the lock-stepped computation. From the technology perspective, there is no distinction between manufacturing asynchronous or synchronous CMOS circuits, which means that defects are similar in both designs [RON99]. For this reason, synchronous test techniques have been adapted to address the asynchronous test problem.

Fault models are the same for synchronous counterparts, i.e., stuck-at faults, bridging faults, delay faults, functional faults, etc. However, fault effects may be different when shifting from synchronous to asynchronous circuits. For example, a stuck-at fault in the handshake control signals (e.g., request or acknowledge) of an asynchronous template can result in a system halt, but a stuck-at within the data path of the asynchronous circuit has the same effect as in its synchronous counterpart.

According to Section 2.3, there are two main asynchronous design styles, QDI and BD. As for testability, this division persists, and different test techniques have been proposed for both styles. Remember that this research is focused on BD templates, more specifically, Micropipelines, Mousetrap, GasP, and Click templates, which were recently addressed in works that deal with the test of asynchronous circuits [RON15].

The Micropipeline concept was introduced in the late 80's, and the papers about the test of such circuits are from the early 90's. The test problem is divided into three classes: (i) testing the control part; (ii) testing the combinational logic in the data path; (iii) testing the memory element (latches). This division is still used nowadays. Note that this division does not cover the delay lines required for the correct operation of the Micropipelines. Despite the challenges of testing asynchronous circuits, the authors state that the control part is easily testable, because a stuck-at fault in this part halts the circuit. However, this is not entirely true for other approaches [SHI05], such as Mousetrap. The test strategy proposed by Pagey [PAG92] consists in putting all latches in transparent mode, creating a big and unique combinational circuit, where standard ATPG tools for combinational circuits can be used. This approach can be applied for detecting stuck-at faults and delay faults, except that for delay faults only the overall delay of the combinational logic is evaluated, and not the individual blocks between stages. However, test pattern generation for this technique becomes a complex task as the circuit size scales.