# MOSFET Replacement Devices for Energy-Efficient Digital Integrated Circuits

Hei Kam

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-182 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-182.html

December 17, 2009

Copyright © 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. MOSFET Replacement Devices for Energy-Efficient Digital Integrated Circuits

by

Hei Kam

B.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Elad Alon Professor Tarek I. Zohdi

Fall 2009

The dissertation of Hei Kam is approved:

| Chair | <br>Date |

|-------|----------|

|       |          |

| _     | Date     |

|       |          |

| -     | <br>Date |

|       |          |

University of California, Berkeley

MOSFET Replacement Devices for Energy-Efficient Digital Integrated Circuits

Copyright © 2009

by

Hei Kam

#### Abstract

MOSFET Replacement Devices for Energy-Efficient Digital Integrated Circuits

by

Hei Kam

Doctor in Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Increasing power density is a daunting challenge for continued MOSFET scaling due to non-scalability of the thermal voltage  $k_{\rm B}T/q$ . To circumvent this CMOS power crisis and to allow for aggressive supply voltage reduction, alternative switching device designs have been proposed and demonstrated to achieve steeper than 60mV/dec subthreshold swing (*S*). This dissertation begins with a general overview of the physics and operation of these MOSFET-replacement devices. It then applies circuit-level metrics to establish evaluation guidelines for assessing the promise of these alternative transistor designs.

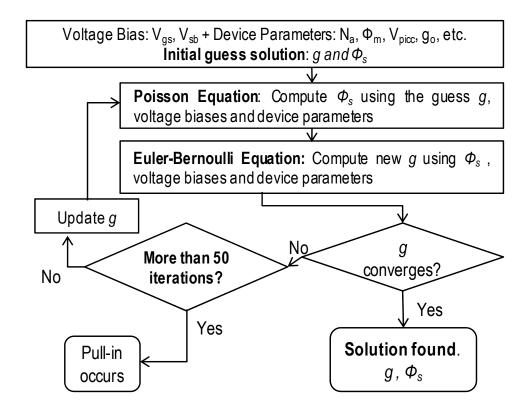

This dissertation then investigates the abrupt "pull-in" effect of an electrostatically actuated beam to achieve abrupt switching behavior in the nanoelectro-mechanical field effect transistor (NEMFET). To facilitate low-voltage NEMFET design, the Euler-Bernoulli beam equation is solved simultaneously with the Poisson equation in order to accurately model the switching behavior of a NEMFET. The impact of various transistor design parameters on the gate pull-in voltage and release voltage are examined. A unified pull-in/release voltage model is developed.

Finally, this dissertation proposes the use of micro-relays for zero-standbypower digital logic applications. To mitigate the contact reliability issue, it is demonstrated that since relatively high on-state resistance can be tolerated while extremely high endurance is a necessity, hard contacting electrode materials and operation with low contact force are preferred for reliable circuit operation. Using this contact design approach, a reliable relay technology that employs titanium dioxide (TiO<sub>2</sub>) coated tungsten (W) electrodes is developed for digital logic applications. Relay miniaturization will lead to improvements in density (for lower cost per function), switching delay (for higher performance), and power consumption. A scaled relay technology is projected to provide  $>10\times$  energy savings for digital circuits operating at up to  $\sim100$ MHz.

Professor Tsu-Jae King Liu

Dissertation Committee Chair

## Acknowledgements

"Physics isn't the most important thing, Love is." — Richard P. Feynman

Finally, my eight-year-and-a-half journey in Berkeley is approaching to its end. I still remember every little thing in this journey, as if it happened only yesterday. I could never come so far and see so much without the help, love and support of many people. I would like to formally thank them all here.

I would first like to express my deepest and most sincere gratitude to my advisor, Professor Tsu-Jae King Liu. I would like to thank her for giving me the great opportunity to work for her as an undergraduate researcher six years ago. She gave me the freedom to pursue my research interest, while at the same time provided me valuable insights, guidance and support at all stages of my research. Her breadth and depth of knowledge in solid state devices and microfabrication technologies were exceptionally helpful to this thesis. Without her support, this thesis can never be completed.

I would also like to thank Professor Elad Alon in unofficially advising my research even though I am not his student. His intelligence, speed of thought and enthusiasm for research has always been a source of motivation and inspiration.

I am also grateful for Professor Vivek Subramanian for teaching the wonderful EE130 and EE231 in fall 2002 and spring 2003, respectively. I would also thank him for his valuable feedback as a member of my qualifying

i

examination and insightful advice on my career path. I would like to thank Professor Roger T. Howe and Professor Tarek I. Zohdi as well.

I have also had a lot of pleasure working with all the device group members who "live" in 373 Cory Hall and work endlessly in the microlab. I would like to thank them for their technical discussion and personal friendship. They include Anupama Bowonder, Andrew Carlson, Jaeseok Jeon, Sung Hwan Kim (I particular would like to thank him for sharing his measured data on Ge-source TFET), Joanna Lai, Blake Lin, Donovan Lee, Darsen Lu, Cheuk Chi Lo, Rhesa Nathanael, Pratik Patel, Kinyip Phoa, Vincent Pott, Changhwan Shin, Xin Sun and Reinaldo Vega.

I truly owe a debt to my birthplace, Hong Kong. Her restless energy is always a source of motivation and inspiration. I am also fortunate enough to still be close with friends from my childhood. In particular I would like to thank Yip Kwong Lo, Ken Hui, David Lee, James Wong, Andy Tam, Chris Ng, Anthony Wong, Dennis Chan and May Chui for their friendship.

Most of all, I would like to thank my family. I thank my grandma, my parents, my brother Henry and my sister Kylie for all their unbounded love. This dissertation is dedicated to them.

This work was supported in part by the GAANN fellowship, the FCRP and DARPA.

Hei Kam December 4, 2009 Cory Hall, Berkeley "Who sees the future? Let us have free scope for all directions of research."

- Adapted from Ludwig Boltzmann

# Contents

| 1 | Intro                                                      | duction: The CMOS Power Crisis                                    | 1 |  |

|---|------------------------------------------------------------|-------------------------------------------------------------------|---|--|

|   | 1.1                                                        | CMOS Scaling Trend                                                | 1 |  |

|   | 1.2                                                        | MOSFET Physics in the Subthreshold Regime                         | 3 |  |

|   | 1.3                                                        | Various MOSFET Replacement Devices                                | 7 |  |

|   | 1.4                                                        | Objectives1                                                       | 1 |  |

|   | 1.5                                                        | References                                                        | 4 |  |

| 2 | Circu                                                      | it-Driven Requirements for MOSFET-Replacement Devices1            | 7 |  |

|   | 2.1                                                        | Introduction                                                      | 7 |  |

|   | 2.2                                                        | Simplified Energy-Performance Analysis                            | 8 |  |

|   | 2.3                                                        | Optimal <i>I</i> <sub>on</sub> / <i>I</i> <sub>off</sub> for CMOS | 1 |  |

|   | 2.4                                                        | Optimal $I_{on}/I_{off}$ for CMOS Replacement Devices             | 4 |  |

|   | 2.5                                                        | Benchmarking CMOS Replacement Devices                             | 7 |  |

|   | 2.6                                                        | TFET Comparisons with CMOS: An Example                            | 1 |  |

|   | 2.7                                                        | Conclusion                                                        | 9 |  |

|   | 2.8                                                        | References                                                        | 3 |  |

| 3 | 3 Nano-Electro-Mechanical Field Effect Transistor Design47 |                                                                   |   |  |

|   | 3.1                                                        | Introduction                                                      | 7 |  |

|   | 3.2                                                        | Physics of NEMFET Operation                                       | 9 |  |

|   | 3.3                                                        | Results and Discussion                                            | 9 |  |

| 3.4    | Unified Model for $V_{pi}$ and $V_{rl}$                    | 78     |

|--------|------------------------------------------------------------|--------|

| 3.5    | NEMFET Scalability                                         | 79     |

| 3.6    | Summary                                                    | 80     |

| 3.7    | References                                                 | 82     |

| 4 Des  | ign and Reliability of Micro-Relays for Logic Applications | 86     |

| 4.1    | Introduction                                               | 86     |

| 4.2    | Relay Structure and Operation                              | 87     |

| 4.3    | Reliable Micro-Relay Technology                            | 90     |

| 4.4    | Results and Discussion                                     | 94     |

| 4.5    | Conclusion                                                 | 110    |

| 4.6    | References                                                 | 111    |

| 5 Opti | mization and Scaling of Micro-Relays for Logic Application | ıs 115 |

| 5.1    | Introduction                                               | 115    |

| 5.2    | Relay Energy-Delay Optimization                            | 116    |

| 5.3    | Relay Scaling                                              | 128    |

| 5.4    | Conclusion                                                 | 132    |

| 5.5    | References                                                 | 134    |

| 6 Con  | clusion                                                    | 137    |

| 6.1    | Summary                                                    | 137    |

| 6.2    | Recommendations for Future Work                            | 140    |

# **Chapter 1**

# Introduction:

# The CMOS Power Crisis

## 1.1 CMOS Scaling Trend

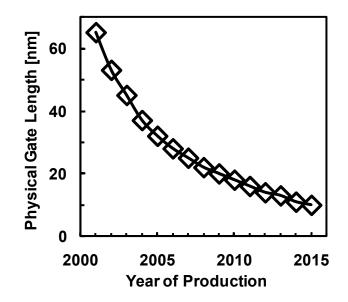

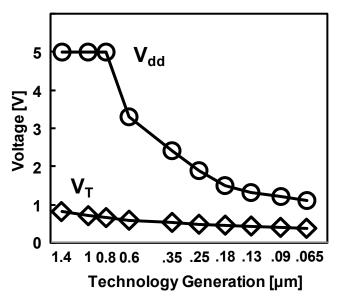

The steady reduction in the dimensions of <u>c</u>omplementary <u>m</u>etal-<u>o</u>xide-<u>s</u>emiconductor (CMOS) transistors from one technology to another has provided for dramatic improvements in the switching speed, density, cost and functionality of CMOS chips. As shown in Fig. 1.1, the physical gate length of a CMOS transistor has been reducing at an exponential rate and is expected to be scaled down to the sub-20nm regime in year 2010 [1.1]. However, due to the fact that the thermal voltage  $k_{\rm B}T/q$  does not scale, the threshold voltage ( $V_{\rm T}$ ) of CMOS transistors can no longer be reduced along with their lithographic dimensions. This non-scaling of the threshold voltage forces the supply voltage ( $V_{\rm dd}$ ) to remain constant across technologies for a given switching speed, as shown in Fig. 1.2,  $V_{\rm dd}$ has saturated at around 1V from the 130nm technology forward [1.1]. Therefore, the power density of integrated circuits has increased drastically. As an example, the power dissipation in Intel's state-of-the-art microprocessors has already reached the level of 100W or more [1.2]. Power is now a major constraint for modern day CMOS chip design.

**Fig. 1.1** Improvements in the switching speed, density, cost and functionality of CMOS chips have been enabled by the steady miniaturization of the transistor over the past four decades. By the year 2010, the physical gate length of a CMOS transistor is expected to be scaled down to the sub-20nm regime [1.1].

Fig. 1.2 To maintain constant power density, both the supply and the threshold voltages of a CMOS integrated circuit should be reduced along with the lithographic dimension of CMOS transistors. But due to MOSFET subthreshold leakage, both  $V_{dd}$  and  $V_T$  scaling have slowed down in recent technology generations [1.1].

### 1.2 MOSFET Physics in the Subthreshold Regime

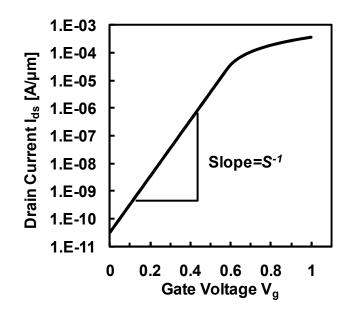

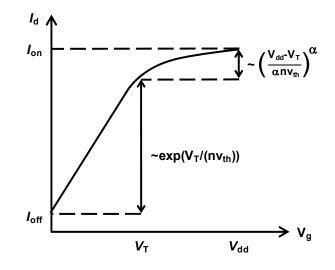

The CMOS power crisis is fundamentally due to the non-scaling of the thermal voltage  $k_{\rm B}T/q$ , which sets a lower limit for the subthreshold swing (S) of a MOSFET. Fig. 1.3 shows the  $I_{\rm ds}$ - $V_{\rm gs}$  characteristics of a MOSFET. Below the threshold voltage ( $V_{\rm T}$ ), the MOSFET does not turn off completely; instead,  $I_{\rm ds}$  decreases exponentially with  $V_{\rm gs}$  with an inverse slope ("subthreshold swing")  $S \ge 60 \text{mV/dec}$  at room temperature. Thus, in the off state ( $V_{\rm gs}$ =0V), CMOS transistors still dissipate leakage energy.

Fig. 1.3 The subthreshold swing S of a MOSFET is limited by the thermal voltage  $k_BT/q$ ; it is greater than or equal to 60mV/dec at room temperature.

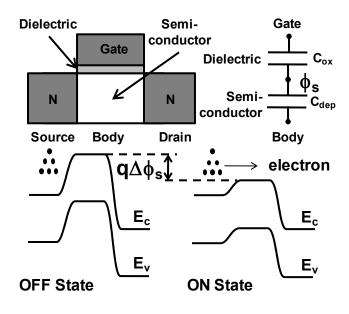

Fig. 1.4 The potential barrier for thermionic emission can be modulated ( $\Delta \phi_s$ ) by the gate voltage; and according to Boltzmann statistics [1.3], electron concentration is exponentially proportional to  $q\phi_s/k_BT$ . This sets a lower limit for the MOSFET subthreshold swing, which is at least 60mV/dec at room temperature.

The origin of  $S \ge 60 \text{mV/dec}$  can be explained by the electron energy band profile of a MOSFET, which is shown in Fig. 1.4. As  $V_{gs}$  increases, the channel potential is modulated by the capacitive divider:

$$\frac{d\phi_s}{dV_{gs}} = \frac{C_{ox}}{C_{ox} + C_{dep}} \quad \text{for } V_{gs} < V_T \tag{1.1}$$

where  $C_{ox}$  and  $C_{dep}$  are the oxide and depletion capacitances, respectively.

Increasing the channel potential ( $\phi_s$ ) reduces the potential barrier for electron injection, and hence the electron energy (*E*) increases. According to the Boltzmann statistics [1.3], electron concentration *n*(*E*) increases exponentially with electron energy; therefore, the drain-to-source current flow ( $I_{ds}$ ) depends exponentially on channel potential:

$$I_{ds} \propto n(E) \propto exp\left(\frac{E}{k_BT}\right) \propto exp\left(\frac{q\phi_s}{k_BT}\right) \propto exp\left(\frac{q}{k_BT}\frac{C_{ox}}{C_{ox}+C_{dep}}V_{gs}\right)$$

(1.2)

And the subthreshold swing of the MOSFETs can therefore be expressed as:

$$S \equiv \left(\frac{d \log_{10} I_{ds}}{d V_{gs}}\right)^{-1} = \frac{d \log_{10} I_{ds}}{d \phi_s} \times \frac{d \phi_s}{d V_{gs}} = \ln(10) \frac{k_B T}{q} \left(1 + \frac{c_{dep}}{c_{ox}}\right)$$

(1.3)

which is at least 60 mV/dec at room temperature. Due to the non-zero depletion capacitance in the transistor, *S* is typically ~100 mV/dec for state-of-the-art MOSFETs.

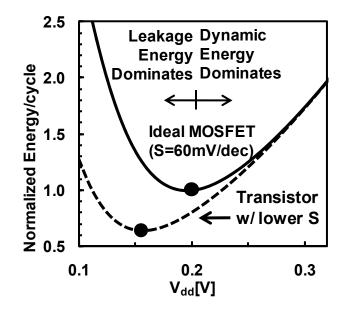

The subthreshold swing determines the lower energy limit for CMOS electronics. Fig. 1.5 illustrates the dependence of MOSFET energy consumption on the power supply voltage for a given switching speed. As the supply voltage is scaled down, the dynamic energy ( $\sim CV_{dd}^2$ ) reduces quadratically; but to maintain the same switching speed ( $\propto (V_{dd}-V_T)$ ),  $V_T$  must be decreased together with  $V_{dd}$  to

maintain the same on-state current. This, as a result, exponentially increases offstate leakage (Eqn. 1.2) and static energy. To reach the minimum operation energy, the dynamic and the leakage energies must be properly balanced; and for most digital designs, this optimal ratio is roughly 30-50% [1.4]. As previously alluded to, both the  $V_{dd}$  and  $V_T$  have remained roughly unchanged from the 130nm technology node and onwards; therefore the CMOS energy efficiency has not improved proportionately as the transistor dimensions have been scaled down.

Fig. 1.5 Dynamic energy reduces quadratically as the supply voltage is scaled down; but to maintain a certain switching speed, the threshold voltage of the MOSFET must be scaled down as well, which increases the leakage energy. Therefore there exists an optimal  $V_{dd}$  that minimizes the energy dissipation. Transistor designs with lower *S* value reduce the leakage energy; they therefore improve the energy efficiency.

## 1.3 Various MOSFET Replacement Devices

To overcome the CMOS energy efficiency limit, alternative transistor designs which can achieve a steeper sub-threshold swing (*i.e.* more abrupt transition between on- and off-states) have been proposed. As shown in Fig. 1.5, transistor designs with lower *S* value reduce the leakage energy; this allows for more aggressive  $V_{dd}$  scaling and improvement in the energy efficiency.

To reach this goal, alternative transistor designs such as the tunneling based field effect transistors [1.5, 1.6], impact ionization MOS [1.7, 1.8], ferroelectric FETs [1.9, 1.10] and electromechanical devices [1.11-1.17] have been proposed and demonstrated to achieve subthreshold swing (S) < 60mV/dec. Among these, the tunneling field effect transistor (TFET) and electromechanical devices show the most promise for low power electronics applications.

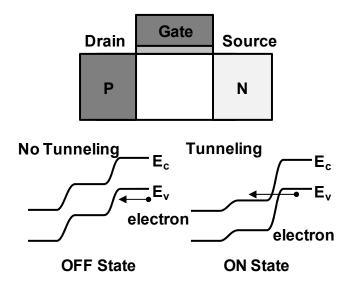

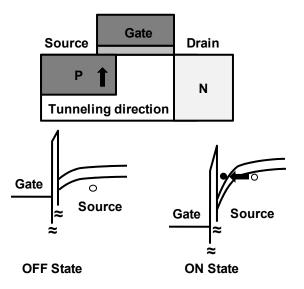

#### 1.3.1 Tunneling Field Effect Transistor (TFET)

Among all the alternative transistor designs, the tunnel field effect transistor (TFET) shows the most promise due to its relative simplicity and resemblance to the conventional MOSFET. The TFET utilizes band-to-band tunneling (BTBT) current to achieve a more abrupt on-to-off transition than what is achievable through thermionic emission. Fig. 1.6 shows the energy band diagram of the TFET in on and off states. In the off state, the wide energy barrier prohibits quantum tunneling between the source and channel regions. When a large  $V_{gs}$  is applied, the energy barrier narrows, and allowed energy states in the channel conduction band

align with allowed energy states in the source valence band, so that electrons can tunnel from the source to the channel. Since the TFET utilizes a different source injection mechanism from the MOSFET, it can potentially achieve lower *S* values, which has already been experimentally demonstrated [1.5]. Note, however, that a TFET achieves *S*<60mV/dec only at low current levels and that *S* increases as  $I_{ds}$ increases. Consequently, at high  $V_{dd}$  (~1V) values, a silicon TFET has a significantly lower on-state current  $I_{on}$  (~1 $\mu$ A/ $\mu$ m at 1V) than a silicon MOSFET (1mA/ $\mu$ m at 1V). This remains a principal challenge for TFET designers.

**Fig. 1.6** Schematic diagram of a tunneling field effect transistor and its energy band diagram in the off and on states (n-channel operation).

## **1.3.2 Electromechanical Devices**

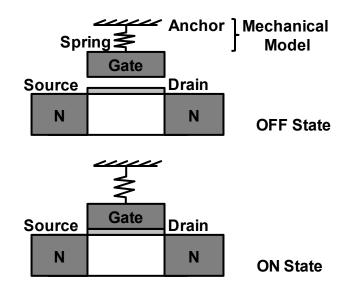

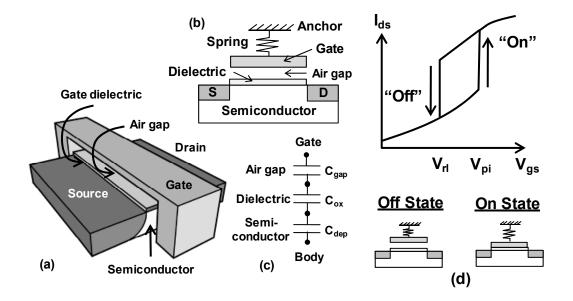

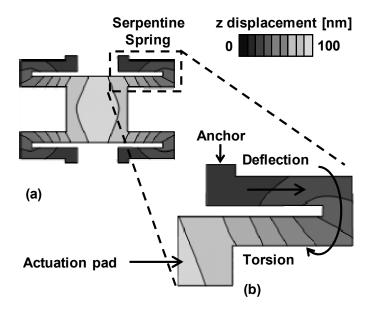

Besides band-to-band tunneling, the abrupt "pull-in" effect in microelectromechanical systems (MEMS) has also been harnessed to realize new switching device designs with higher  $I_{on}/I_{off}$  ratio for a given gate voltage swing. These devices utilize a movable beam for switching, and they can roughly be divided into two categories: the nano-electro-mechanical field effect transistor (NEMFET) and the micro-electro-mechanical relay (micro-relay).

**Fig. 1.7** Schematic diagram of a nano-electro-mechanical n-channel enhancement mode field effect transistor in off and on states.

#### a. Nano-Electro-Mechanical Field Effect Transistor (NEMFET)

A nano-electro-mechanical field effect transistor [1.11-1.13] is essentially a MOSFET with a movable gate electrode which can be physically separated from the gate dielectric layer by an air gap (or vacuum gap). As shown in Fig. 1.7, the gate, which is a mechanical beam anchored on both sides of the semiconducting channel, can be modelled as a simple linear spring (with a characteristic spring constant *k*) suspended over the semiconductor channel. The gate and the channel form a parallel-plate capacitor with an equivalent air-gap.

In the off-state ( $V_{gs}=0V$ ), the gate is separated from the gate dielectric; the gate coupling to the channel is weak and the transistor is therefore turned off. When a positive  $V_{gs}$  is applied, the electrostatic force attracts the mechanical gate towards the gate dielectric. While the electrostatic force increases quadratically with increasing displacement, the spring restoring force, which counteracts the electrostatic force, increases only linearly with displacement. Hence, there is a critical pull-in voltage ( $V_{pi}$ ) beyond which the electrostatic force is always larger than spring restoring force, causing the gap to close abruptly. When the gate is in contact with the gate dielectric, the gate coupling to the channel is maximized and the transistor is turned on. Taking advantage of this pull-in phenomenon, a NEMFET with perfectly abrupt switching transition (S=0mV/dec) at  $V_{gs}=V_{pi}$  have been utilized for logic, memory and resonator applications [1.11-1.13].

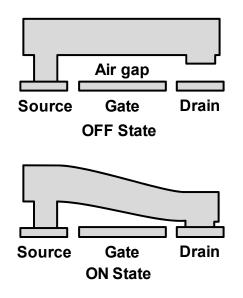

#### b. Micro-electro-Mechanical Relay (Micro-Relay)

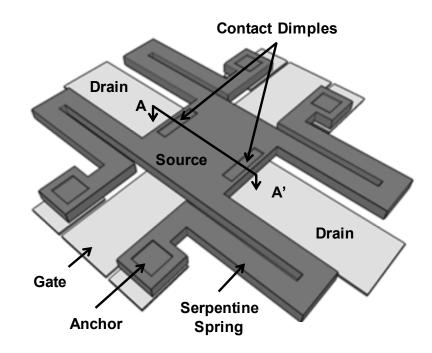

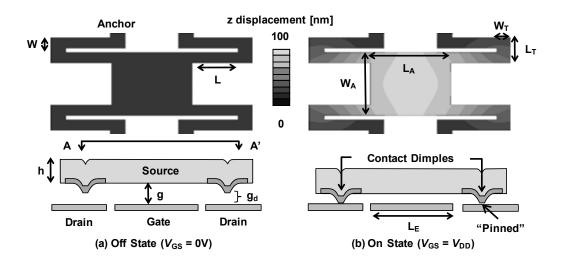

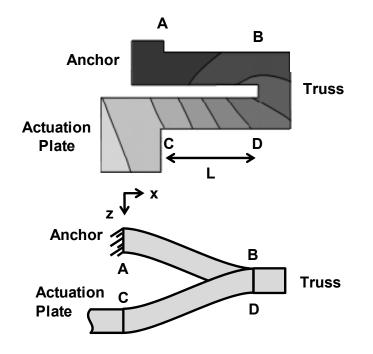

The abrupt pull-in effect has also been harnessed for micro-electromechanical relays ("micro-relays") [1.14-1.17]. The attractiveness of micro-relays stems from the fact that a mechanical switch offers nearly ideal switching characteristics: zero off-state drain-to-source and gate leakage currents, and perfectly abrupt off-to-on transition. Since there is no trade-off between off-state leakage current and on-state drive current, the relay threshold voltage and therefore  $V_{dd}$  can in principal be reduced much more aggressively than for MOSFETs, potentially leading to improved energy efficiency. In terms of device structure and operation (shown in Fig. 1.8), a micro-relay for digital logic applications ("logic relays") is very similar to one targeted for radio-frequency signal DC switching applications ("RF relays"). In the off state, an air gap separates the source from the metallic drain electrode so that no current can flow. In the on state where the gate-to-source voltage is greater than the pull-in voltage ( $V_{pi}$ ), the source, which is a movable beam, comes down and touches the drain electrode, providing a conductive path for current to flow. Since the relay switches on abruptly as  $V_{gs}$  is increased above  $V_{pi}$ , the  $I_d$ - $V_g$  characteristic of the relay exhibits an extremely steep (nearly infinite) subthreshold slope.

Fig. 1.8 Schematic diagram of a micro-relay in off and on states

## **1.4 Objectives**

This research focuses on the analysis, design and applications of MOSFETreplacement devices, with emphasis on the TFET and electromechanical devices. As alluded to previously, TFETs often have small *S* value at low current levels but fail to achieve the required on-to-off current ratio across a range of  $V_{dd}$ . To investigate whether TFETs can effectively replace MOSFETs, one needs to compare the energy-performance tradeoff of a TFET with that of a MOSFET. To achieve this goal, chapter 2 first reviews the energy-performance tradeoffs of CMOS, and shows that the optimal  $I_{on}/I_{off}$  value for most CMOS replacement devices at the optimum energy depends only on the average activity factor and the logic depth, and that its value is roughly insensitive to all other device parameters. Thus, it is the device's effective subthreshold swing ( $S_{eff}$ ) over a range of voltage rather than the steepest local subthreshold swing (*S*) value that determines the energy efficiency. With this in mind, simple guidelines for assessing the energy efficiency of CMOS replacement are established. As a concrete example, we use this methodology to compare TFETs against CMOS, showing that TFETs may offer substantial (~5x) energy savings for performance up to the 100MHz range.

To alleviate the issue of *S* degradation at high current level, the use of the abrupt gate pull-in effect in NEMFET to achieve the required  $I_{on}/I_{off}$  ratio with a smaller  $V_{dd}$  appears to be an attractive solution. To facilitate this goal, NEMFET device physics and operation are studied in Chapter 3. Due to the beam bending of the mechanical gate, the channel potential is non-uniform in the semiconductor. The Euler-Bernoulli beam equation is solved simultaneously with the Poisson equation in order to accurately model the switching behavior of NEMFETs. Using this approach, the shape of the movable gate electrode and semiconductor potential

across the width of the channel are derived for the various regimes of transistor operation (before gate pull-in, after gate pull-in, and at the point of gate release). The impact of various transistor design parameters such as the body doping concentration, gate work function, gate stiffness, and as-fabricated actuation gap thickness, as well as source-to-body bias voltage and surface forces, on the gate pull-in voltage and gate release voltage are examined. A unified pull-in/release voltage model is developed, to facilitate NEMFET design for digital and analog circuit applications.

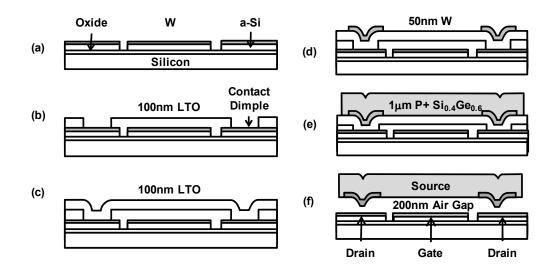

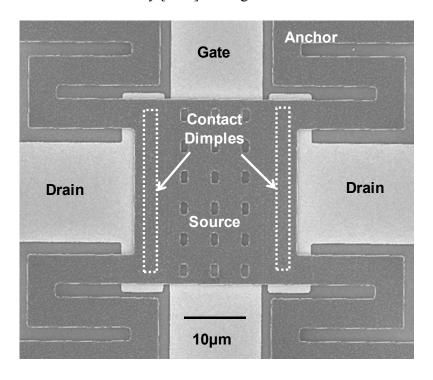

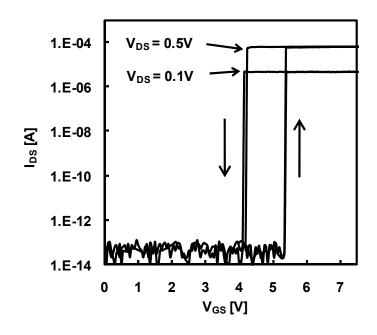

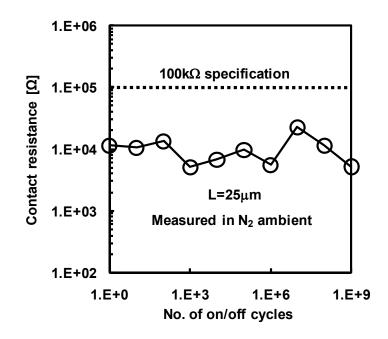

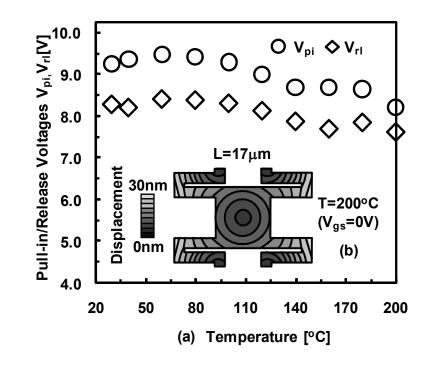

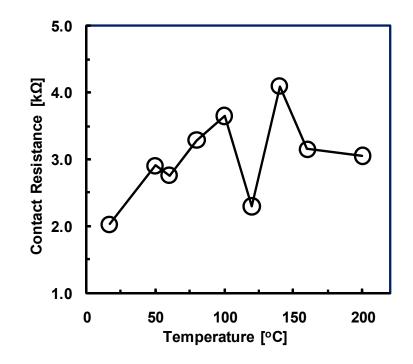

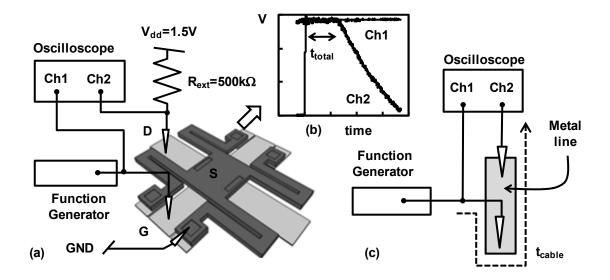

Although the pull-in effect can be harnessed to achieve a perfectly abrupt off-to-on switching transition for NEMFET; the presence of the air-gap in the offstate also severely decreases the gate-to-channel capacitive coupling in the offstate, limiting NEMFET scalability. In light of this limitation, chapter 4 discusses the use of micro-relays for zero-standby power logic applications. Contact design techniques to achieve reliable (high-endurance) micro-relay operation are described. Utilizing TiO<sub>2</sub>-coated tungsten contacting electrodes, prototype relays fabricated using a CMOS-compatible process are demonstrated to operate with low surface adhesion force, adequately low on-state resistance (< 100k $\Omega$ ) over a wide temperature range (20°C-200°C), and >10<sup>9</sup> on/off switching cycles in N<sub>2</sub> ambient without stiction- or welding induced failure. These results pave the pathway to realizing reliable micro-relays for digital logic applications.

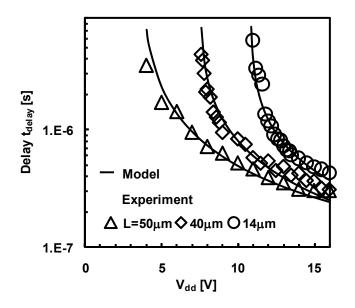

Using calibrated relay delay and energy models, a sensitivity-based relay energy-delay optimization methodology is developed in Chapter 5, in which simple relay design guidelines are established. The proposed scaling methodology for micro-relays is then presented, which leads to systematic improvements in device density, performance, and energy consumption. Simulation results indicate that scaled relay technology can potentially offer  $>10\times$  improvement in energy efficiency for applications requiring performance up to  $\sim100$ MHz.

Chapter 6 summarizes the key results and contributions of this dissertation; future research directions are also suggested.

#### 1.5 References

- [1.1] The International Technology Roadmap for Semiconductors (ITRS), 2007.[Online]. Available: <u>http://public.itrs.net</u>

- [1.2] B. Nikolic, "Design in the power-limited scaling regime," *IEEE Trans. Electron Devices*, vol. 55, pp. 71, Jan. 2008.

- [1.3] R. S. Muller and T. I. Kamins with M. Chan, Device Electronics for Integrated Circuits, 3rd ed. New York: Wiley, 2003, pp. 16.

- [1.4] K. Nose and T. Sakurai, "Optimization of V<sub>DD</sub> and V<sub>TH</sub> for low-power and high-speed applications," in *Proc. Asia South Pacific Design Automation Conf.*, Jan. 2000, pp. 469–474.

- [1.5] S. H. Kim, H. Kam, C. Hu and T.-J. King-Liu, "Germanium-Source Tunnel Field Effect transistors with Record High I<sub>ON</sub>/I<sub>OFF</sub>", *Symposium on VLSI Technology Digest of Technical Papers*, pp. 178-179, 2009.

- [1.6] K. K. Bhuwalka, J. Schulze, and I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp<sup>+</sup> layer," *Jpn. J. Appl. Phys.*, vol. 43, no. 7A, pp. 4073-4078, Jul. 2004.

- [1.7] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, "I-MOS: A novel semiconductor device with a subthreshold slope lower than kT/q," in IEDM Tech. Dig., 2002, pp. 289–292.

- [1.8] W. Y. Choi , J. Y. Song , J. D. Lee , Y. J. Park and B.-G. Park "A novel biasing scheme for I-MOS (impact-ionization MOS) devices," *IEEE Trans. Nanotechnol.*, vol. 4, pp. 322, May 2005.

- [1.9] S. Salahuddin and S. Datta, "Use of negative capacitance to provide a subthreshold slope lower than 60 mV/decade," Nanoletters, vol. 8, No. 2, 2008.

- [1.10] S. Salahuddin and S. Datta, "Can the subthreshold swing in a classical FET be lowered below 60 mV/decade?," in *IEDM Tech. Dig.*, 2008, pp. 693– 696.

- [1.11] N. Abele, N. Fritschi, K. Boucart, F. Casset, P. Ancey, and A. M. Ionescu, "Suspended-gate MOSFET: Bringing new MEMS functionality into solidstate MOS transistor," in *IEDM Tech. Dig.*, 2005, pp. 1075–1077.

- [1.12] H. Kam, D. T. Lee, R. T. Howe, and T.-J. King, "A new nanoelectromechanical field effect transistor (NEMFET) design for low-power electronics," in *IEDM Tech. Dig.*, 2005, pp. 463–466.

- [1.13] K. Akarvardar, C. Eggimann, D. Tsamados, Y. Singh Chauhan, G. C. Wan,A.M. Ionescu, R.T. Howe, and H.-S.P. Wong, "Analytical Modeling of the

Suspended-Gate FET and Design Insights for Low-Power Logic," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 48-59, Jan. 2008.

- [1.14] F. Chen, H. Kam, D. Markovic, T.J. King, V. Stojanovic, and E. Alon, "Integrated Circuit Design with NEM Relays," in *Proc. IEEE/ACM Int. Conf. Computer Aided Design*, 2008, pp. 750-757.

- [1.15] K. Akarvardar, D. Elata, R. Parsa, G. C. Wan, K. Yoo, J. Provine, P. Peumans, R. T. Howe, H.-S. P. Wong, "Design Considerations for Complementary Nanoelectromechanical Logic Gates," in *IEDM Tech. Dig.*, 2007, pp. 299-302.

- [1.16] H. Kam, V. Pott, R. Nathanael, J. Jeon, E. Alon and T.-J. King-Liu, "Design and Reliability of a Micro-Relay Technology for Zero-Standby-Power Digital Logic Applications," in *IEDM Tech. Dig.*, 2009, pp. 809–812.

- [1.17] R. Nathanael, V. Pott, H. Kam, J. Jeon and T.-J. King-Liu,, "4-Terminal Relay Technology for Complementary Logic," in *IEDM Tech. Dig.*, 2009, pp. 223–226.

# **Chapter 2**

# Circuit-Driven Requirements for MOSFET-Replacement Devices

#### 2.1 Introduction

As alluded to in Chapter 1, many alternative switching devices [2.1-2.14] have been proposed and demonstrated to achieve subthreshold swing (*S*) <60mV/dec to allow for power supply ( $V_{dd}$ ) and threshold voltage ( $V_T$ ) scaling to alleviate the CMOS power crisis. However, many of these devices (e.g. the TFET) achieve *S*<60mV/dec only at low on-current levels, and fail to maintain improved  $I_{on}/I_{off}$  across a range of  $V_{dd}$ . In addition, some of these devices (e.g., the NEMFET and NEM relay) do not begin to conduct current until sometime after the control voltage arrives, leading to an additional delay. To investigate whether these devices can effectively replace MOSFETs, one needs to compare the energy-performance tradeoff of these new logic devices with that for MOSFETs. To achieve this goal, this chapter starts by describing the energy-performance tradeoffs of CMOS gates in section 2.2. It is then shown in section 2.3 that for a given performance target, the optimal  $I_{on}/I_{off}$  value of CMOS at the optimum energy depends only on the average activity factor and the logic depth. In section 2.4, this optimal  $I_{on}/I_{off}$  value is shown to remain roughly the same for most CMOS replacement devices. With this optimal  $I_{on}/I_{off}$  fixed, it is shown in section 2.5 that the device's effective subthreshold swing ( $S_{eff}$ ) over a range of voltage (rather than the steepest local subthreshold swing (S) value) determines the device's energy efficiency. With this in mind, simple guidelines for assessing the energy efficiency of MOSFET replacement devices are then established. Finally, as a concrete example, this methodology is used to compare TFETs against CMOS, showing that TFETs may offer substantial (~5x) energy savings for performance up to the 100MHz range.

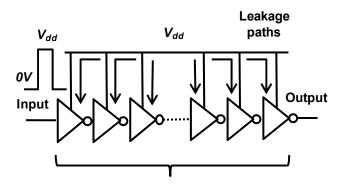

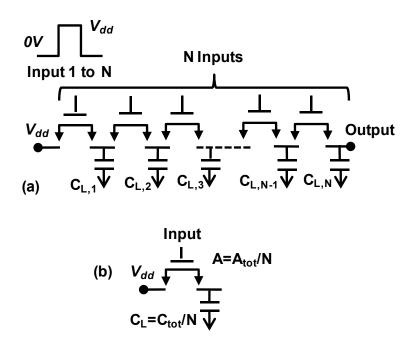

### 2.2 Simplified Energy-Performance Analysis

Although digital chips clearly consist of a broad variety of circuit types, the tradeoffs between energy and delay for the majority of CMOS gates on a chip are similar to those of an inverter. Therefore, at least for devices whose qualitative behavior is similar to a MOSFET, we can approximately compare the energy and delay tradeoffs by using an inverter chain, as shown in Fig. 2.1. The total energy consumption per operation of an inverter chain with logic depth  $L_d$ , average activity factor a, electrical fanout (FO) f, and capacitance/stage C can be computed by adding the dynamic and the leakage energy components:

$$E = E_{dyn} + E_{leak} = aL_d V_{dd}^2 C \cdot f + L_d f I_{off} V_{dd} t_{delay}$$

(2.1)

where the  $t_{delay}$  is simply:

$$t_{delay} = \frac{L_d C \cdot f V_{dd}}{2I_{on}} \tag{2.2}$$

$L_d$ -stage, average fanout=f, activity factor = a, Gate capacitance per minimum sized inverter = C

Fig. 2.1  $L_d$ -stage inverter chain considered for energy efficiency. For most digital circuit, the energy delay tradeoffs of CMOS gates are similar to the tradeoff for an inverter chain.

Optimized circuit design entails the choice of parameters such as supply  $(V_{dd})$  and threshold voltage  $(V_T)$  that minimize the energy dissipation (Eqn. 2.1) subject to a given delay target (Eqn. 2.2). To reach this goal, the dynamic and static energies must be properly balanced. For CMOS circuits, dynamic energy can be reduced quadratically by decreasing  $V_{dd}$ . However, in order to avoid increased circuit delay,  $V_T$  must be decreased along with  $V_{dd}$  to maintain a high on-state drive current ( $I_{on}$ ) [2.15]. This results in increased off-state leakage current ( $I_{off}$ ) and hence increased static energy. For alternative devices that are MOSFET-like [2.1-2.9], [2.12-2.14], the tradeoff between the dynamic and the leakage energies is similar. Note that Nose and Sakurai [2.15] have previously proven that for an optimized CMOS circuit design, the leakage-to-dynamic-energy-ratio of is roughly

0.3-0.5 across wide range of parameters. In this dissertation, we follow a similar derivation approach, but now from a device designer's perspective, to show that such an optimal energy ratio can equivalently be expressed as an optimal  $I_{on}/I_{off}$  ratio for CMOS. To reach this goal, in Appendix I, the method of Lagrange multipliers is used to show that a generalized logic device is energy-delay optimized if the device  $I_{on}$  and  $I_{off}$  values satisfy the following condition:

$$\frac{4a}{L_{df}}\frac{I_{on}}{I_{off}} + 1 + \frac{I_{on}}{I_{off}}\frac{dI_{off}}{dI_{on}} = 0$$

$$(2.3)$$

As shown by (Eqn. (2.3)), the optimum  $I_{on}/I_{off}$  depends only on the circuit topology and  $dI_{off}/dI_{on}$ , a parameter which is related to the subthreshold swing, as will be explained later.

Once the optimal  $I_{on}/I_{off}$  value is found, the energy minimum can readily be obtained by Eqn. (2.1), which can equivalently be expressed by:

$$E = V_{dd}^2 C L_d^2 f^2 \left( \frac{a}{L_{df}} + \frac{I_{off}}{2I_{on}} \right)$$

(2.4)

where  $V_{dd}$  is the supply voltage required to reach the target performance. Since the optimal  $I_{on}/I_{off}$  is set by the circuit topology, we can see from Eqn. (2.4) that the minimum energy is proportional to the dynamic energy  $CV_{dd}^2$ . This implies that, as will be explained more in detail later, any logic device that can achieve the required  $I_{on}/I_{off}$  value at a lower  $V_{dd}$  than CMOS is going to be more energy-efficient. To assess the promise of alternative switching devices for replacing the MOSFET, one needs to know how  $I_{on}/I_{off}$  of these devices depend on  $L_df/a$ . To reach this goal, the optimal  $I_{on}/I_{off}$  for CMOS is first derived and then shown to be relatively constant across regions of operation (strong inversion versus subthreshold).

## 2.3 Optimal *I*<sub>on</sub>/*I*<sub>off</sub> for CMOS

To find the optimal the I-V characteristics of MOSFETs are first approximated as:

$$I_{ds} = I_s exp\left(\frac{V_{gs} - V_T}{nv_{th}}\right) \quad V_{gs} \le V_T + \alpha n v_{th}$$

(2.5a)

$$I_{ds} = I_s e^{\alpha} \left(\frac{V_{gs} - V_T}{\alpha n v_{th}}\right)^{\alpha} \quad V_{gs} > V_T + \alpha n v_{th}$$

(2.5b)

where *n* is the subthreshold slope factor ( $n \approx 1.67$  for *S*=100mV/dec),  $\alpha \approx 1.2$  and  $v_{\text{th}}$  is the thermal voltage.

Using this I-V model, the optimal  $I_{on}/I_{off}$  can be found by first differentiating  $I_{off}$  with respect to  $I_{on}$  (Eqn. (2.3)):

$$\frac{dI_{off}}{dI_{on}} = \frac{-I_{off}}{nv_{th}} \frac{dV_T}{dI_{on}}$$

(2.6)

High performance CMOS digital circuits often operate in the strong inversion region ( $V_{gs} > V_T$ ), therefore  $dV_T/dI_{on}$  can be found by differentiating Eqn. (2.5b) with respect to  $I_{on}$ , which gives the following expression:

$$1 = I_s \left(\frac{e}{\alpha n v_{th}}\right)^{\alpha} \alpha (V_{dd} - V_T)^{\alpha - 1} \left(\frac{dV_{dd}}{dI_{on}} - \frac{dV_T}{dI_{on}}\right)$$

(2.7)

Substituting Eqn. (2.6) into Eqn. (2.7), we obtain the expression for  $dI_{off}/dI_{on}$ :

$$\frac{dI_{off}}{dI_{on}} = \frac{1}{\alpha n v_{th}} \frac{I_{off}}{I_{on}} \left( V_{dd} (1 - \alpha) - V_T \right)$$

(2.8)

Finally, substituting Eqn. (2.8) into Eqn. (2.3), the optimal  $I_{on}/I_{off}$  can be expressed by the following equation:

$$\frac{I_{on}}{I_{off}} = \frac{L_{df}}{4a} \left( \frac{V_{dd}(\alpha - 1) + V_T - \alpha n v_{th}}{\alpha n v_{th}} \right)$$

(2.9)

where  $V_{dd}$  and  $V_T$  are set by the performance target (Eqn. (2.2)):

$$t_{delay} = \left(\frac{L_d C \cdot f(\alpha n v_{th})^{\alpha}}{2I_s e^{\alpha}}\right) \frac{V_{dd}}{(V_{dd} - V_T)^{\alpha}}$$

(2.10)

Typically, the threshold and supply voltages lie within the following bounds:  $1 \ge V_{dd} \ge 0.4$ ,  $0.5 \ge V_T \ge 0.3$ ; substituting these  $V_{dd}$  and  $V_T$  values together with  $\alpha \cong 1.2$  into Eqn. (2.9), the optimal  $I_{on}/I_{off}$  can be expressed by the following equation:

$$\frac{l_{on}}{l_{off}} \approx K_1 \frac{L_d f}{a} \tag{2.11}$$

where  $K_1$  lies within the range 1.6 to 3.2. This verifies that for CMOS circuits operated in strong inversion region,  $I_{on}/I_{off}$  at the energy optimum is mainly set by the circuit topology.

Thus far in this discussion, the MOSFET has been assumed to operate in the strong inversion region ( $V_{dd}>V_T$ ); however, many alternative devices such as TFETs achieve low on-current levels (~10µA/µm) at supply voltages similar to those used in current high performance CMOS circuits (~1V). These devices will therefore only be competitive with subthreshold MOSFETs (operated with  $V_{dd}<V_T$ ), which dissipate the minimum energy required for CMOS to perform a given operation [2.16, 2.17]. At the energy optimum, the optimal  $I_{on}/I_{off}$  ratio for subthreshold CMOS similarly can be derived by first expressing off-state current in terms on the on-state current (Eqn. (2.5a)) and the delay (Eqn. (2.2)):

$$I_{off} = I_s exp\left(\frac{-V_T}{nv_{th}}\right) = I_{on} exp\left(-\frac{V_{dd}}{nv_{th}}\right) = I_{on} exp\left(-\frac{2t_{delay}}{nv_{th}L_dC_f}I_{on}\right)$$

(2.12)

Therefore,  $dI_{off}/dI_{on}$  is:

$$\frac{dI_{off}}{dI_{on}} = \left(1 + ln\left(\frac{I_{off}}{I_{on}}\right)\right) \frac{I_{off}}{I_{on}}$$

(2.13)

Substituting Eqn. (2.7) into Eqn. (2.3), the optimal  $I_{on}/I_{off}$  ratio can be expressed by the following equation:

$$\frac{I_{on}}{I_{off}} = -\frac{L_d f}{4a} lambert W\left(-\frac{4a}{L_d f}e^2\right) \approx \frac{L_d f}{4a} \ln\left(\frac{L_d f}{4a}\right) \approx K_2 \frac{L_d f}{a}$$

(2.14)

where *lambertW(y)* is the *x* that solves the equation  $y=xe^x$  and  $K_2$  lies within the range 1.9 to 3.6. This result is consistent with previous published work [2.16, 2.17]. From Eqn. (2.14), it can be seen that the optimal  $I_{on}/I_{off}$  depends only on  $f \times L_d /a$ , and also that even in subthreshold operation, the optimal  $I_{on}/I_{off}$  ratio stays roughly the same as that for super-threshold MOSFETs (Eqn. (2.11)). This is because, as shown in Fig. 2.2, most of the change in  $I_{on}/I_{off}$  (as a function of  $V_{dd}$ ) occurs in the subthreshold region, and therefore even in strong inversion, the ratio is relatively insensitive to small changes in  $V_{dd}$ . As a result, the optimal  $I_{on}/I_{off}$  depends mainly on  $f \times L_d /a$  and is relatively insensitive to all other device parameters.

**Fig. 2.2.** Most of the change in  $I_{on}/I_{off}$  (as a function of  $V_{dd}$ ) for MOSFET occurs in the subthreshold region (approximately five orders of magnitude) rather than in the strong inversion region (approximately 25), and therefore the ratio is relatively insensitive to small changes in  $V_{dd}$ . Thus the optimal  $I_{on}/I_{off}$  is roughly the same for both sub-threshold and super-threshold MOSFETs.

#### 2.4 Optimal *I*<sub>on</sub>/*I*<sub>off</sub> for CMOS Replacement Devices

Thus far the discussion has only focused on optimizing MOSFETs. To assess the promise of alternative switching devices for replacing the MOSFET, similar analysis can be applied to CMOS replacement devices. To reach this goal, as derived in Appendix II, Eqn. (2.3) is equivalently expressed by the following equation:

$$\frac{4a}{L_{df}}\frac{I_{on}}{I_{off}} + 2 - ln\left(\frac{I_{on}}{I_{off}}\right)\left(1 - log_{10}\left(\frac{I_{on}}{I_{off}}\right)\frac{dS_{eff}}{dV_{dd}}\right) = 0$$

(2.15)

where  $S_{\rm eff}$  is the effective subthreshold swing:

$$S_{eff} \equiv \left(\frac{1}{V_{dd}} \log_{10}\left(\frac{I_{on}}{I_{off}}\right)\right)^{-1}$$

(2.16)

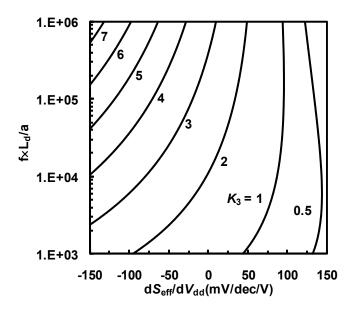

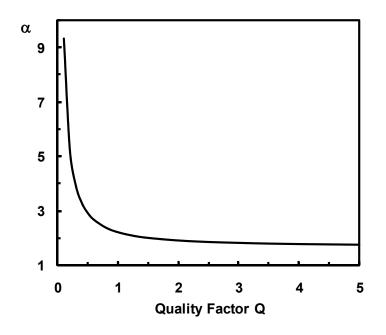

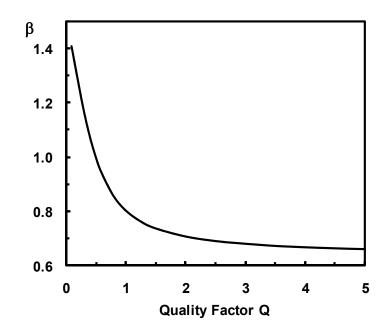

Thus, the optimal  $I_{on}/I_{off}$  of the generalized logic device depends only on  $f \times L_d / a$  and  $dS_{eff}/dV_{dd}$ , where  $dS_{eff}/dV_{dd}$  is related to the log-concavity of the transfer characteristics. For a broad variety of different logic devices that are MOSFET-like, the *S* value degrades as the current level increases, i.e. their transfer characteristics are logarithmically concave with  $dS_{eff}/dV_{dd} \sim 0$ . Therefore, even without knowing the exact characteristics of a new device, one can still approximate the optimal  $I_{on}/I_{off}$  from Eqn. (15), which gives the following expression:

$$\frac{I_{on}}{I_{off}} = K_3 \times \frac{L_d f}{a} \tag{2.17}$$

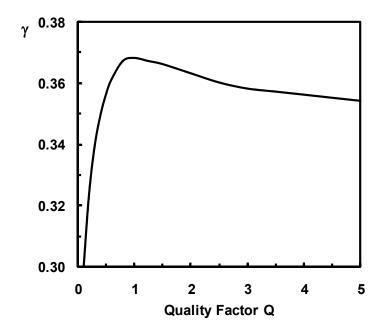

where  $K_3$  is set by the exact of  $dS_{eff}/dV_{dd}$  value, and  $K_3$  lies within the range ~2-8 for most logic devices, as shown in Fig. 2.3.

**Fig. 2.3.** The optimal  $I_{on}/I_{off}$  of a generalized logic device depends on the logic style  $(f \times L_d/a)$  and the log-concavity of the device transfer characteristics  $(dS_{eff}/dV_{dd})$ .  $dS_{eff}/dV_{dd}$  are approximately zero for most MOSFET-like devices, therefore  $I_{on}/I_{off}=K_3 \times f \times L_d/a$ , where  $K_3 \sim 2$ -8.

By comparing  $K_3$  against  $K_1$  and  $K_2$  (Eqns. (2.11) and Eqn. (2.14)), the optimal  $I_{on}/I_{off}$  ratio is roughly the same for MOSFET-like devices. This is because, as was discussed earlier, most of the change in  $I_{on}/I_{off}$  (as a function of  $V_{dd}$ ) occurs in the region with the largest the steepest effective subthreshold slope, and therefore the ratio is relatively insensitive to small changes in  $V_{dd}$ . Using the fact that the optimal  $I_{on}/I_{off}$  ratio is fixed across a wide range of switching devices, simple guidelines can be derived to assess the promise of MOSFET replacement devices, which is the focus of the following section.

### 2.5 Benchmarking CMOS Replacement Devices

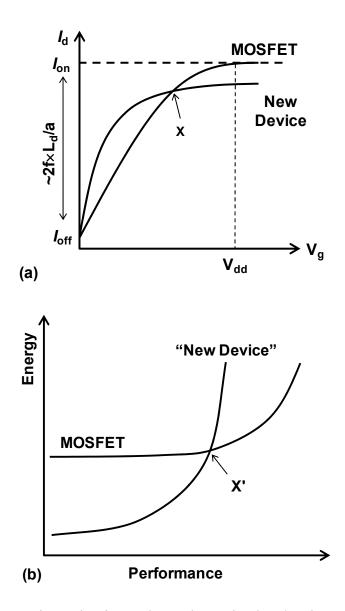

#### 2.5.1 General Considerations

As previously alluded to, for a given performance target and logic style, there exists an optimal  $I_{on}/I_{off}$  ratio to minimize the total energy, and this value is roughly the same for most MOSFET-like devices. Therefore if a logic device with a small subthreshold swing can reach the required  $I_{on}/I_{off}$  at a lower supply voltage, it will achieve the same performance with lower energy dissipation. With this said, merely focusing on the steepest local subthreshold slope (S) is misleading, since devices with very small S only at low current levels may not achieve the required performance. To compare the true energy efficiency, Fig. 2.4 summarizes a simple method to assess the promise of alternative devices for replacing MOSFETs. For a given the circuit topology, one first determines the optimal  $I_{on}/I_{off} \sim 2fL_d/a$ . With a fixed reasonable off-state current (for instance  $I_{off}$ ~1pA/µm) for both devices, one can then determine the required on state current. The supply voltage required for each device to reach such on state current is then graphically determined. With all these parameters determined, the new device is both faster and energy more efficient than the MOSFETs if it can achieve the required  $I_{on}/I_{off}$  at a lower  $V_{dd}$  (i.e. with a lower  $S_{\text{eff}}$ ). Notice that a device with a small S value at low current levels but which require a large  $V_{dd}$  to reach the required  $I_{on}/I_{off}$  for the performance target, like the one shown in Fig. 2.4, does not improve the overall energy efficiency. Furthermore, the point at which the  $I_{ds}$ - $V_{gs}$  curves intersect roughly corresponds to the point where the energy-delay curves cross over.

**Fig. 2.4 (a)** For a given circuit topology, the optimal  $I_{on}/I_{off}$  is set (~2 $f \times L_d/a$ ). To compare any new device against the MOSFET, a reasonable off-state current is first fixed. The new device will be energy more efficient if it can achieve the required current ratio at a lower  $V_{dd}$ , i.e. at a lower effective subthreshold slope ( $S_{eff}$ ). (b) The  $V_{dd}$  value at the point where the transfer characteristics intersect in (a) (denoted as X) is roughly the same for the intersection point in the energy-performance space (point X').

### 2.5.2 Additional Considerations

Some alternative devices (e.g., the NEMFET and the IMOS) do not begin to conduct current until sometime after the control voltage arrives, leading to an additional setup delay ( $t_{su}$ ). The delay time is therefore:

$$t_{delay} = t_{RC} + t_{su} = \frac{L_d C f V_{dd}}{2I_{on}} (1 + \gamma_{su}), \text{ where } \gamma_{su} \equiv t_{su}/t_{RC}$$

(2.18)

Following a similar procedure as shown in Appendix I, the optimal  $I_{on}$  and  $I_{off}$  is determined by the following condition:

$$\frac{4a}{L_{df}(1+\gamma_{su})} \frac{I_{on}}{I_{off}} + 1 + \frac{I_{on}}{I_{off}} \frac{dI_{off}}{dI_{on}} = 0$$

(2.19)

Comparing Eqn. (2.18) and Eqn. (2.19) with Eqn. (2.2) and Eqn. (2.3), we can see that these devices not only need to have  $1+\gamma_{su}$  times higher on current, but also  $1+\gamma_{su}$  times higher  $I_{on}/I_{off}$  (i.e.  $1+\gamma_{su}$  times smaller in  $S_{eff}$  than the MOSFET) to compensate for the increased leakage energy.

Furthermore, for devices with a large setup time, circuit topologies with short logic depth but large fan-out per stage are preferred to minimize the overall delay. For the case of a simple buffer chain, the optimal fan out per stage  $f_{opt}$  and optimal logic depth  $L_{opt}$  can be estimated [2.18] by the following equations:

$$f_{opt} = exp\left(1 + \frac{\gamma_{su}}{f_{opt}}\right), L_{opt} = ln\left(C_L/C_{in}\right)/ln f_{opt}$$

(2.20)

where  $C_{in}$  in the input capacitance of the inverter chain.

In addition to the non-zero setup time, many MOSFET replacement devices may have gate or other parasitic capacitance (denoted as C'); the switching delay for these devices are:

$$t_{delay} = \frac{L_d C f V_{dd}}{2I_{on}} \gamma_c, \text{ where } \gamma_c = C'/C$$

(2.21)

For these devices, the optimal  $I_{on}/I_{off}$  remains unchanged, but the on current can be  $\gamma_c$  times lower for the same performance target. However, it should be noted that for a given switching energy, even if a device has a low gate capacitance, it may not necessarily allow for higher supply voltage. This is because the device layout area impacts capacitance (*e.g.* of interconnect wires) and thereby impacts circuit switching energy and constrains the supply voltage that can be used.

In setting device and circuit design parameters to optimally balance leakage and dynamic energies, it is critical to consider the impact of variations. For example, since  $I_{off}$  varies exponentially with the  $V_T$  of a MOSFET, the average  $I_{off}$ is much higher than  $I_{off}(V_{Taverage})$ ; thus, maintaining the appropriate energy ratio requires a lower nominal  $I_{off}$ . In contrast to energy, the performance of a synchronous digital circuit is set by the critical paths. While there is some summing of delay variations along the path, the paths are not very long, so variations remain. Thus  $I_{on}$  must be increased to ensure all paths meet the performance target for the worst-case variations.

Applications with low performance demands or large amounts of parallelism can tolerate reduced device performance [2.19], so that  $V_{dd}$  can be scaled more aggressively (with margin for variation) to reduce energy. It can be shown that for these applications,  $I_{on}/V_{dd}$  is not as critical as the minimum supply voltage  $V_{dd,min}$ , which depends only on maintaining the optimal  $I_{on}/I_{off}$  ratio and is proportional to  $S_{eff}$ . Before moving on, it should be noted that even if a device has low  $S_{\text{eff}}$  but requires a non-zero output voltage ( $V_{ds}$ ) [2.6, 2.14] to conduct, it may not improve the overall energy efficiency. This is because digital gates built which such a device would either dissipate significant static power, or would be significantly constrained in terms of the number of devices that can be connected in series.

### 2.6 TFET Comparisons with CMOS: An Example

To illustrate how the aforementioned methodology can be used to assess the promise of a MOSFET replacement device, we herein use the TFET as an example and compare it against the MOSFET. The TFET (Fig. 2.5) utilizes band-to-band tunneling (BTBT) current to achieve a more abrupt on-to-off transition than what is achievable through thermionic emission. For the purposes of this study, it is adequate to simply approximate  $I_{ds}$  using the band-to-band tunneling model [2.20, 2.21], which predicts:

$$I_{ds} = AE_s exp\left(-\frac{\pi\sqrt{m^*}E_g^{3/2}}{2\sqrt{2}q\hbar E_s}\right) = AE_s exp\left(-\frac{B}{E_s}\right)$$

(2.22)

where  $E_s$  is the electric field in the region where the tunneling occurs, which can be estimated for a source-tunneling FET by the following simple expression:

$$E_s = \frac{(v_{gs} + v_{tunnel})}{\kappa t_{ox}} \tag{2.23}$$

where  $qV_{tunnel}$  is the minimum energy-band bending needed for band-to-band tunneling to occur,  $\kappa$  is the ratio of the semiconductor permittivity to the gate oxide permittivity and  $t_{ox}$  is the gate-oxide thickness over the source [2.22].

**Fig. 2.5** A schematic diagram and the energy band diagram in the OFF/ON state of a source-tunneling field effect transistor.

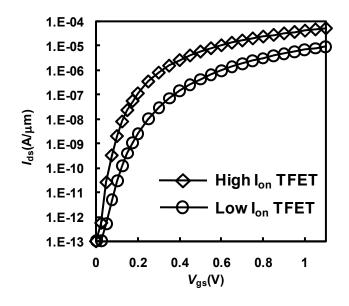

This band-to-band-tunneling current model is used as it matches well with the measured data of the germanium-source TFET [2.23] and the BTBT off-state leakage current in silicon MOSFETs [2.22]. Note that a TFET has a very small *S* value at low current levels, but that *S* increases as  $I_{ds}$  increases. Furthermore, at high  $V_{dd}$  (~1V) values, a silicon TFET has a significantly lower on-state current  $I_{on}$ (~1 $\mu$ A/ $\mu$ m at 1V) than a MOSFET (1mA/ $\mu$ m at 1V). Current research efforts focus on improving  $I_{on}$ , for instance, by using a smaller-bandgap material such as germanium [2.23, 2.24]. Therefore, two representative TFET technologies are compared herein: a normal low  $I_{on}$  TFET technology ("low  $I_{on}$  TFET technology") and an advanced TFET technology that provides a high  $I_{on}$  ("high  $I_{on}$  TFET technology") to show the implications of the energy-performance analysis. The device design parameters and the I-V characteristics of both TFET devices are shown in Table I and in Fig. 2.6.

**Fig. 2.6** Simulated I-V characteristic of two representative TFET technologies: the "low  $I_{on}$ " and "high  $I_{on}$ " TFET technologies. The  $V_{tunnel}$  values for low  $I_{on}$  and high  $I_{on}$  TFETs are respectively 0.13V and 0.07V.

Assuming  $V_{\text{tunnel}}$  is a parameter that can be adjusted by utilizing advanced processing technologies (e.g. gate work function engineering), the optimal  $I_{\text{on}}/I_{\text{off}}$  can readily be found from Eqn. (2.22) and Eqn. (2.23):

$$\frac{I_{on}}{I_{off}} \frac{dI_{off}}{dI_{on}} \approx \frac{(0.1 \sim 0.3 - V_{dd})}{V_{tunnel}} \left(1 + \frac{B'}{V_{tunnel}}\right)$$

(2.24)

where  $B' = \kappa t_{ox}B$ . For typical values of B' = 3V,  $V_{tunnel} = 0.2V$  and  $V_{dd} = 0.5V$ ,  $I_{on}/I_{off} \times dI_{off}/dI_{on}$  can be computed from Eqn. (2.24) and its value is roughly -30; the optimal  $I_{on}/I_{off}$  is therefore roughly  $8 \times L_d f/a$ , which matches the prediction of Eqn. 2.17.

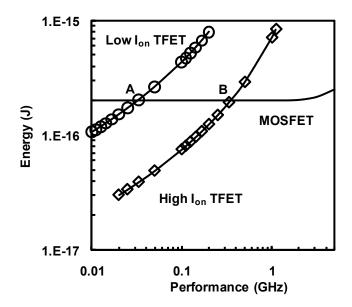

**Fig. 2.7** Energy-Performance comparison of 30-stage FO4 65nm CMOS inverter chain with a 65nm-equivalent two different TFET technology.

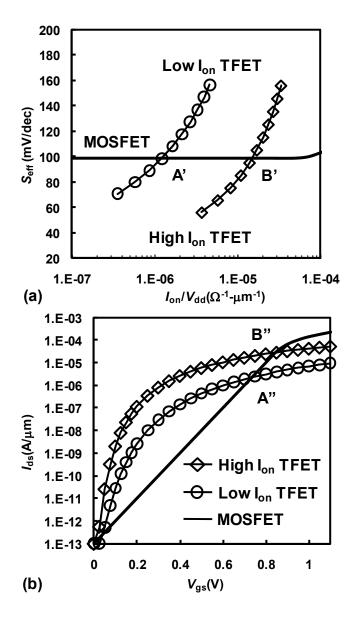

With this in mind, Fig. 2.7 shows the simulated energy-performance comparison of a 65nm MOSFET vs. a 65nm-equivalent TFET, for a 30-stage fanout-4 inverter chain (transition probability=0.01, with optimized  $V_{dd}$ ,  $V_T$ , and  $V_{tunnel}$ values). The device parameters for the MOSFET (Table 2.2) are chosen according to the ITRS specifications for the 65nm LSTP technology [2.25]. With these circuit design parameters ( $L_{d,}$ =30 a=0.01 and f=4) given, the optimal  $I_{on}/I_{off}$  ratio for both CMOS and TFET is approximately 2.4×10<sup>4</sup>. The  $S_{eff}$  values for the two TFETs to reach this  $I_{on}/I_{off}$  ratio at different  $I_{on}/V_{dd}$  values are plotted in Fig. 2.8. By overlapping the I-V characteristics of the TFET with that of MOSFET (with  $I_{off}$ fixed at 0.1pA/µm for both devices), one can see that for relatively slow (sub-50 MHz) applications where  $I_{on}/V_{dd}$  is not critical, both high- $I_{on}$  and low- $I_{on}$  TFETs have smaller  $S_{eff}$  values and hence can be more energy-efficient than a MOSFET. For moderate (50-500MHz) performance applications, only the high- $I_{on}$  TFET can achieve  $S_{eff} < 100$ mV/dec ; and for high-performance applications (beyond 1GHz) requiring  $I_{on} > 100\mu$ A/ $\mu$ m, both TFET technologies have  $S_{eff} > 100$ mV/dec and they therefore would consume more energy than a MOSFET. At the  $I_{on}/V_{dd}$  where the TFET achieves the same  $S_{eff}$  value as a MOSFET (denoted as A' and B' in Fig. 2.8a and A" and B" in Fig. 2.8b), both devices consume roughly the same amount of energy (points A and B in Fig. 2.7). Based on this analysis, the high- $I_{on}$  TFET technology appears to be compelling for low power applications up to ~100MHz.

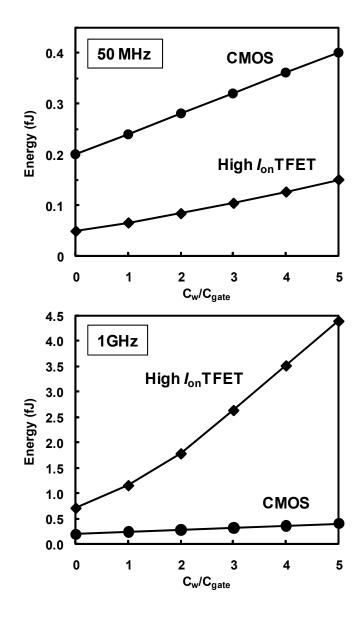

This simplified energy-performance analysis thus far assumes logic devices just drive other devices; in reality, however, extrinsic wire capacitance ( $C_w$ ) must be considered in the analysis too, especially if the device has an area overhead. Fig. 2.9 shows the sensitivity of the energy consumption as a function of the wiring capacitance. For slow (50MHz) applications, a TFET operates at a lower  $V_{dd}$  than a MOSFET and hence its energy consumptions ( $\propto C_w V_{dd}^2$ ) is less sensitive to  $C_w$ ; for high performance applications (1GHz), the TFET operates at a higher  $V_{dd}$  and hence the energy consumption is more sensitive to  $C_w$ .

|                                 | Low I <sub>on</sub> TFET | High I <sub>on</sub> TFET |  |

|---------------------------------|--------------------------|---------------------------|--|

| Physical Gate Length (nm)       | 45nm                     |                           |  |

| A (Α/V/μm)                      | 3.82E-13                 | 7. 26E-13                 |  |

| B (MV/cm)                       | 7.78                     | 4.09                      |  |

| Equivalent oxide thickness (nm) | 1                        |                           |  |

| κ                               | 4                        |                           |  |

| C (fF)                          | 0.741fF                  |                           |  |

**Table 2.1.** Summary of device parameters for the 65nm equivalent TFETtechnology used in this work.

|                               | Value   |

|-------------------------------|---------|

| Physical Gate Length (nm)     | 45nm    |

| α                             | 1.18    |

| n                             | 1.667   |

| <i>I</i> <sub>s</sub> (μA/μm) | 8.259   |

| C (fF)                        | 0.741fF |

**Table 2.2.** Summary of device parameters for the 65nm MOSFET technology used

in this work.

**Fig. 2.8 (a)** Effective subthreshold values of TFET and MOSFET as different  $I_{on}/V_{dd}$  values for a given circuit topology. For low-performance applications, a TFET can achieve the optimal  $I_{on}/I_{off}$  ratio with a small  $S_{eff}$  and therefore it is more energy efficient than a MOSFET Note that the cross-over points (denoted as A' and B' in the figure) roughly correspond to the cross-over points (denoted as A and B in the Fig. 2.7) in the energy-performance space and in transfer characteristics (denoted as A" and B" (b)).

**Fig. 2.9** Impact of wiring capacitance on energy dissipation. For low performance application, a TFET is operated at a lower  $V_{dd}$  and wiring capacitance is less of an impact to the energy consumption. For high performance application, however, a TFET needs a higher  $V_{dd}$  to provide for the high on-state current. Therefore the energy consumption is more sensitive to wiring capacitance.

### 2.7 Conclusion

In this chapter, a simple evaluation guideline is established to assess the promise of new device technologies. Based upon the energy-performance tradeoff of logic gates, it is shown that the optimal  $I_{on}/I_{off}$  ratio for logic devices depends largely only on the circuit topology, and that this optimal  $I_{on}/I_{off}$  stays roughly constant across a wide range of switching devices. With this optimal  $I_{on}/I_{off}$  ratio in mind, it is then shown that the effective subthreshold swing, rather than the steepest local subthreshold swing determines the energy efficiency of logic devices. As a concrete example, this methodology is used to compare TFETs against MOSFETs, showing that TFETs may offer substantial (~5×) energy savings for performance up to the 100MHz range.

### Appendix I. Energy-Delay Optimization of the Generalized Logic Device

To minimize energy consumption subject to a delay constraint, the Lagrange multiplier method is used to set up the following expression:

$$L(V_{dd}, I_{on}) = E(V_{dd}, I_{on}) - \lambda \left( t_{delay} I_{on} - \frac{L_d f C}{2} V_{dd} \right)$$

(A.1)

Where  $E(V_{dd}, I_{on})$  is the energy consumption

$$E(V_{dd}, I_{on}) = aL_d V_{dd}^2 Cf + L_d f I_{off} V_{dd} t_{delay}$$

(A.2)

And  $D(V_{dd}, I_{on})$  is the delay constraint

$$D(V_{dd}, I_{on}) = t_{delay}I_{on} - \frac{L_dfC}{2}V_{dd}$$

(A.3)

For a broad variety of different alternative devices, the off state leakage current depends only on  $I_{on}$  and  $V_{dd}$ . Hence differentiating  $L(V_{dd}, I_{on})$  with respect to  $V_{dd}$ :

$$\frac{\partial L}{\partial V_{dd}}: 2aL_d V_{dd} Cf + L_d f I_{off} t_{delay} + L_d f V_{dd} t_{delay} \frac{\partial I_{off}}{\partial V_{dd}} + \lambda \frac{L_d f C}{2} = 0$$

(A.4)

which can be simplified to:

$$4aV_{dd} + \frac{2I_{off}t_{delay}}{c} + \frac{2V_{dd}t_{delay}}{c}\frac{\partial I_{off}}{\partial V_{dd}} = -\lambda$$

(A.5)

As the total differential of  $I_{\text{off}}$  is:

$$dI_{off} = \frac{\partial I_{off}}{\partial V_{dd}} dV_{dd} + \frac{\partial I_{off}}{\partial I_{on}} dI_{on}$$

(A.6)

$\frac{\partial I_{off}}{\partial V_{dd}}$  can therefore be expressed by:

$$\frac{\partial I_{off}}{\partial V_{dd}} = \frac{dI_{off}}{dV_{dd}} - \frac{\partial I_{off}}{\partial I_{on}} \frac{dI_{on}}{dV_{dd}} = \frac{dI_{off}}{dI_{on}} \left(\frac{dI_{on}}{dV_{dd}}\right) - \frac{\partial I_{off}}{\partial I_{on}} \frac{dI_{on}}{dV_{dd}}$$

Since  $t_{delay} = \frac{L_d f C}{2I_{on}} V_{dd}, \frac{dI_{on}}{dV_{dd}} = \frac{I_{on}}{V_{dd}}$ . Therefore,

$$\frac{\partial I_{off}}{\partial V_{dd}} = \left(\frac{dI_{off}}{dI_{on}} - \frac{\partial I_{off}}{\partial I_{on}}\right) \frac{I_{on}}{V_{dd}}$$

(A.7)

Hence (A.5) is

$$4aV_{dd} + \frac{2I_{off}t_{delay}}{c} + L_d f V_{dd} \left(\frac{dI_{off}}{dI_{on}} - \frac{\partial I_{off}}{\partial I_{on}}\right) = -\lambda \tag{A.8}$$

On the other hand, if  $L(V_{dd}, I_{on})$  is differentiated with respect to  $I_{on}$

$$\frac{\partial L}{\partial I_{on}} : L_d f V_{dd} t_{delay} \frac{\partial I_{off}}{\partial I_{on}} - \lambda t_{delay} = 0$$

(A.9)

$$L_d f V_{dd} \frac{\partial I_{off}}{\partial I_{on}} = \lambda \tag{A.10}$$

Equating (A.8) and (A.10), we get

$$4aV_{dd} + \frac{2I_{off}t_{delay}}{c} + L_d f V_{dd} \left(\frac{dI_{off}}{dI_{on}} - \frac{\partial I_{off}}{\partial I_{on}}\right) = -L_d f V_{dd} \frac{\partial I_{off}}{\partial I_{on}}$$

(A.11)

which is equivalent to:

$$\frac{4aC}{2I_{off}t_{delay}}V_{dd} + 1 + \frac{L_dfV_{dd}C}{2I_{off}t_{delay}}\frac{dI_{off}}{dI_{on}} = 0$$

(A.12)

Substituting the delay expression to (A.12), we finally obtain (2.3):

$$\frac{4a}{L_{df}}\frac{I_{on}}{I_{off}} + 1 + \frac{I_{on}}{I_{off}}\frac{dI_{off}}{dI_{on}} = 0$$

(A.13)

### Appendix II. Derivation of Equation (2.15)

Equation (2.3) can equivalently be expressed by (2.15) by first knowing that:

$$\frac{I_{on}}{I_{off}}\frac{dI_{off}}{dI_{on}} = \frac{dlog_{10}I_{off}}{dlog_{10}I_{on}} = \frac{dlog_{10}I_{on} - S_{eff}^{-1}V_{dd}}{dlog_{10}I_{on}} = 1 - \frac{dS_{eff}^{-1}V_{dd}}{dlog_{10}I_{on}}$$

(A.14)

And for a fixed performance, (2.2) can be expressed by:

$$\log_{10} I_{on} = \log_{10} \left( \frac{L_d C \cdot f}{2t_{delay}} \right) + \log_{10} V_{dd}$$

(A.15)

Therefore, using the chain rule, (A.14) can be simplified:

$$1 - \frac{dS_{eff}^{-1}V_{dd}}{dlog_{10}V_{dd}} = 1 - \left(V_{dd}S_{eff}\frac{dS_{eff}^{-1}}{dV_{dd}} + 1\right)S_{eff}^{-1}V_{dd}\ln 10$$

(A.16)

After simplification, (A.16) becomes:

$$= 1 - ln \left(\frac{l_{on}}{l_{off}}\right) \left(1 - log_{10} \left(\frac{l_{on}}{l_{off}}\right) \frac{dS_{eff}}{dV_{dd}}\right)$$

(A.17)

Substituting (A.17) into (2.3), we obtain (2.15):

$$\frac{4a}{L_{df}}\frac{I_{on}}{I_{off}} + 2 - ln\left(\frac{I_{on}}{I_{off}}\right)\left(1 - log_{10}\left(\frac{I_{on}}{I_{off}}\right)\frac{dS_{eff}}{dV_{dd}}\right) = 0$$

(A.18)

### 2.8 References

- [2.1] B. Nikolic, "Design in the power-limited scaling regime," *IEEE Trans. Electron Devices*, vol. 55, pp. 71, Jan. 2008.

- [2.2] T. Baba, "Proposal for surface tunnel transistor", Jpn J Appl Phys 31 (1992)

(4B), pp. L455–L457

- [2.3] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 743–745, Aug. 2007.

- [2.4] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, "I-MOS: A novel semiconductor device with a subthreshold slope lower than *kT/q*," in *IEDM Tech. Dig.*, 2002, pp. 289–292.

- [2.5] C. Shen, J.-Q.Lin, E.-H.Toh, K.-F. Chang, P. Bai, C.-H. Heng, G.S.Samudra, and Y.-C.Yeo, 'On the performance limit of impact ionization transistors,' in *IEDM Tech. Dig.*, 2007, pp. 117-120.

- [2.6] W. Y. Choi , J. Y. Song , J. D. Lee , Y. J. Park and B.-G. Park "A novel biasing scheme for I-MOS (impact-ionization MOS) devices," *IEEE Trans. Nanotechnol.*, vol. 4, pp. 322, May 2005.

- [2.7] N. Abele, N. Fritschi, K. Boucart, F. Casset, P. Ancey, and A. M. Ionescu, "Suspended-gate MOSFET: Bringing new MEMS functionality into solidstate MOS transistor," in *IEDM Tech. Dig.*, 2005, pp. 1075–1077.

- [2.8] H. Kam, D. T. Lee, R. T. Howe, and T.-J. King, "A new nanoelectromechanical field effect transistor (NEMFET) design for low-power electronics," in *IEDM Tech. Dig.*, 2005, pp. 463–466.

- [2.9] K. Akarvardar, C. Eggimann, D. Tsamados, Y. Singh Chauhan, G. C. Wan, A.M. Ionescu, R.T. Howe, and H.-S.P. Wong, "Analytical Modeling of the Suspended-Gate FET and Design Insights for Low-Power Logic," IEEE Trans. Electron Devices, vol. 55, no. 1, pp. 48-59, Jan. 2008.

- [2.10] F. Chen, H. Kam, D. Markovic, T.J. King, V. Stojanovic, and E. Alon, "Integrated Circuit Design with NEM Relays," in *Proc. IEEE/ACM Int. Conf. Computer Aided Design*, 2008, pp. 750-757

- [2.11] K. Akarvardar, D. Elata, R. Parsa, G. C. Wan, K. Yoo, J. Provine, P. Peumans, R. T. Howe, H.-S. P. Wong, "Design Considerations for Complementary Nanoelectromechanical Logic Gates," in *IEDM Tech. Dig.*, 2007, pp. 299-302.

- [2.12] S. Salahuddin and S. Datta, "Use of negative capacitance to provide a subthreshold slope lower than 60 mV/decade," Nanoletters, vol. 8, No. 2, 2008.

- [2.13] S. Salahuddin and S. Datta, "Can the subthreshold swing in a classical FET be lowered below 60 mV/decade?," in *IEDM Tech. Dig.*, 2008, pp. 693–696

- [2.14] A. Padilla, C.W. Yeung, C. Shin, M.H. Cho, C. Hu and T.-J. King Liu, "Feedback FET: A Novel Transistor Exhibiting Steep Switching Behavior at Low Bias Voltages," in *IEDM Tech. Dig.*, 2008, pp. 171–174

- [2.15] K. Nose and T. Sakurai, "Optimization of V<sub>DD</sub> and V<sub>TH</sub> for low-power and high-speed applications," in *Proc. Asia South Pacific Design Automation Conf.*, Jan. 2000, pp. 469–474.

- [2.16] B.H. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and Sizing for Minimum Energy Operation in Subthreshold Circuits," *IEEE Journal of Solid-State* Circuits, vol. 50 n.9, p.1778-1786 Sept. 2005.

- [2.17] S. Hanson , B. Zhai , K. Bernstein , D. Blaauw , A. Bryant , L. Chang , K. K. Das , W. Haensch , E. J. Nowak , D. M. Sylvester, Ultralow-voltage, minimum-energy CMOS, IBM Journal of Research and Development, vol.50 n.4/5, p.469-490, July 2006

- [2.18] J. Rabaey, A. Chandrakasan and B. Nikolic, Digital Integrated Circuits: A Design Perspective, second edition, Prentice Hall, NJ, 2003

- [2.19] A. P. Chandrakasan, S. Sheng and R. W. Brodersen "Low-power CMOS digital design," *IEEE J. Solid-State Circuits*, vol. 27, pp. 473, Apr. 1992

- [2.20] J. L. Moll, *Physics of Semiconductors*, New York: McGraw-Hill, 1964.

- [2.21] Q. Zhang , W. Shao and A. Seabaugh "Low-subthreshold-swing tunnel transistors," *IEEE Electron Device Lett.*, vol. 27, pp. 297, Apr. 2006.

- [2.22] J. Chen, T. Y. Chan, P. K. Ko, and C. Hu, "Subbreakdown drain leakage current in MOSFET," *IEEE Electron Device Lett.*, vol. EDL-8, no. 11, pp. 515–517, Nov. 1987.

- [2.23] S. H. Kim, H. Kam, C. Hu and T.-J. King-Liu, "Germanium-Source Tunnel Field Effect Transistors with Record High I<sub>ON</sub>/I<sub>OFF</sub>." in Symposium on VLSI Technology *Tech. Dig*, 2009., pp.178 – 179

- [2.24] K. K. Bhuwalka, J. Schulze, and I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp<sup>+</sup> layer," *Jpn. J. Appl. Phys.*, vol. 43, no. 7A, pp. 4073-4078, Jul. 2004.

- [2.25] The International Technology Roadmap for Semiconductors (ITRS), 2007.[Online]. Available: <u>http://public.itrs.net</u>

### **Chapter 3**

### Nano-Electro-Mechanical

## **Field Effect Transistor Design**

### 3.1 Introduction

In Chapter 2, it was shown that the effective subthreshold swing (rather than the steepest, local subthreshold swing) determines a device's energy efficiency. With this consideration in mind, alternative transistor designs which offer perfectly abrupt off-to-on transition to provide for high on/off current ratio with a smaller supply voltage (i.e. small  $S_{eff}$  value) are attractive for energy-efficient electronics. One such device is the nano-electro-mechanical field effect transistor (NEMFET) [3.1-3.10], which utilizes the pull-in and release behavior of a mechanical beam to achieve a perfectly abrupt switching transition, and an effective subthreshold swing *S* that is less than 60mV/dec.

In addition to low-power digital logic applications, NEMFETs also have been proposed for analog circuit applications such as resonators and sensors [3.8-3.10]. The motion of the mechanical gate (or body) changes the equivalent gateoxide thickness and hence the transistor current, so that a mechanical signal can be effectively converted into an electrical signal with high transduction efficiency [3.9].

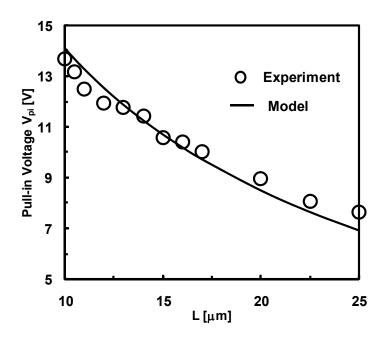

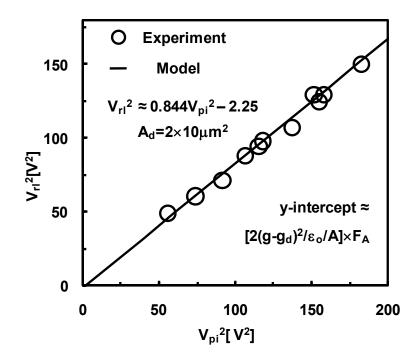

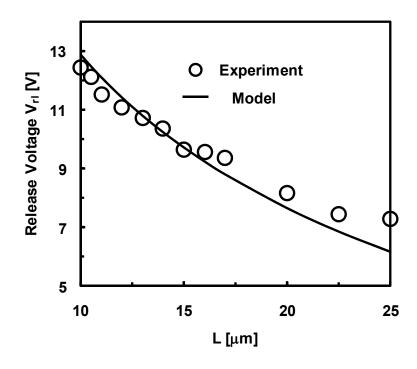

For digital logic applications, the pull-in voltage  $V_{pl}$  and the release voltage  $V_{rl}$  of a NEMFET are important performance parameters since they determine the turn-on and turn-off voltages of the transistor, respectively [3.1-3.7]. Ideally, pullin should occur in the sub-threshold regime of operation, *i.e.*  $V_{pi}$  should be less than  $V_T$  (defined as the gate-to-source voltage  $V_{gs}$  at which the transistor current becomes linearly dependent on  $V_{gs}$ ) to achieve the highest on/off current ratio for a given gate-voltage swing.  $|V_{rl}|$  should be greater than zero to ensure that the transistor turns off properly, *i.e.* that it is in the off state for  $V_{gs} = 0V$ . On the other hand, for analog circuit applications [3.8-3.10],  $V_{pl}$  sets an upper limit for the bias voltage and should be much higher than  $V_T$  to allow for a large DC bias current. Thus, an accurate model for the pull-in/release voltages, as well as the threshold voltage, is needed to guide NEMFET design for various applications.

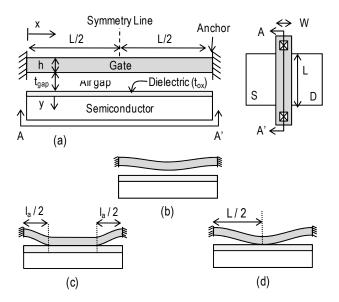

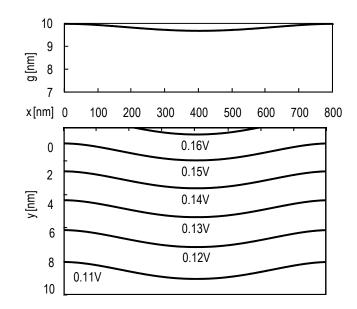

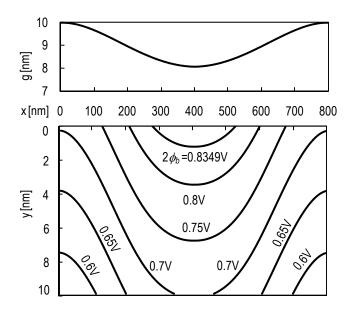

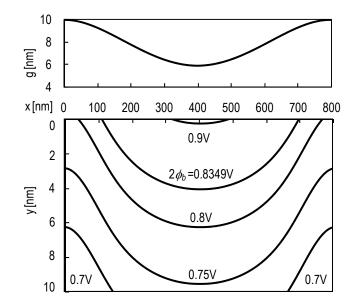

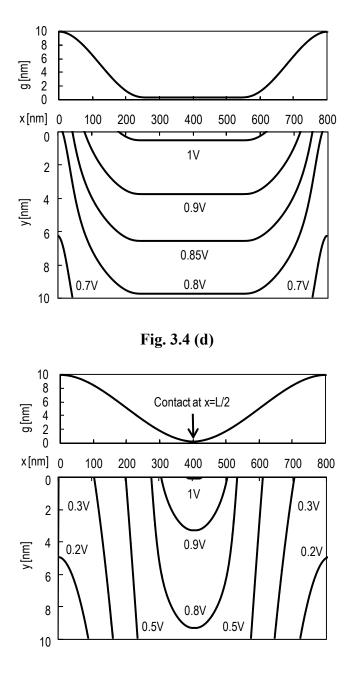

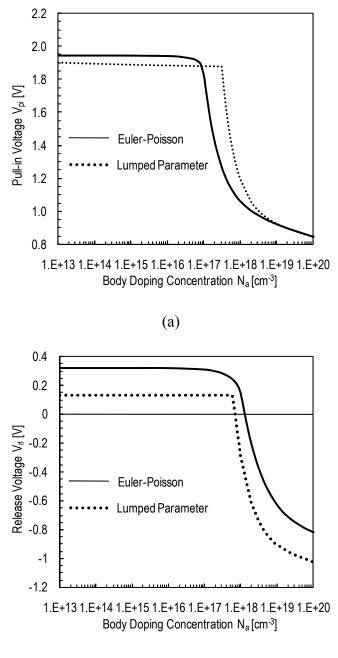

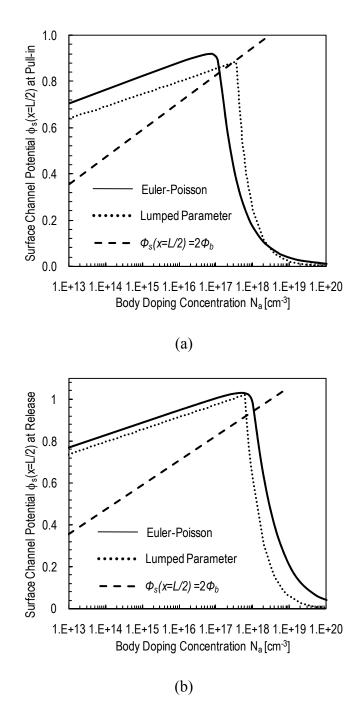

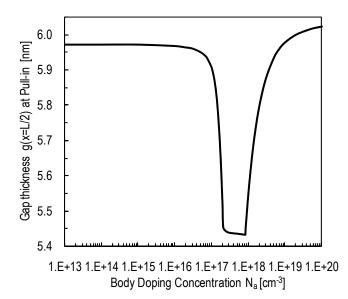

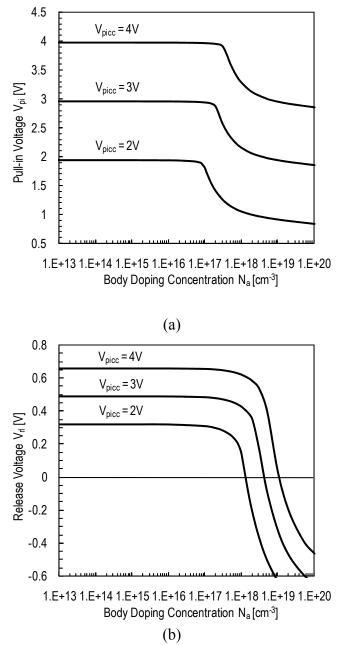

Previous modeling efforts used a simple lumped parameter model [3.1-3.3] to study the behavior of NEMFETs. While this approach provides intuition for NEMFET design, it does not account for two-dimensional effects, *e.g.* a non-uniform actuation gap thickness due to bending of the gate electrode. Furthermore, previous efforts lacked a discussion of the conditions necessary for pull-in/release to occur in the sub-threshold *vs.* inversion regime of FET operation. To address these shortcomings, in this chapter, the Euler-Bernoulli equation (applicable to mechanical beams and widely used for modeling micro-electromechanical systems

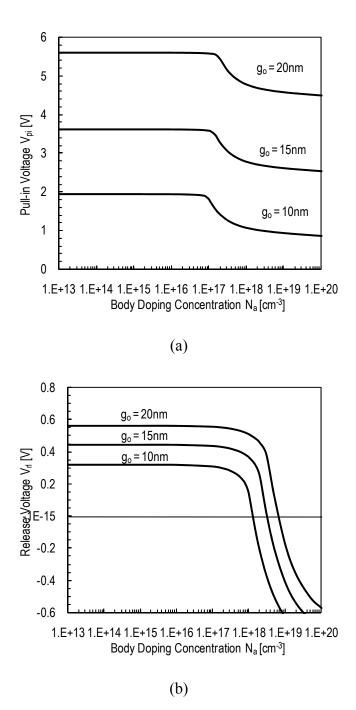

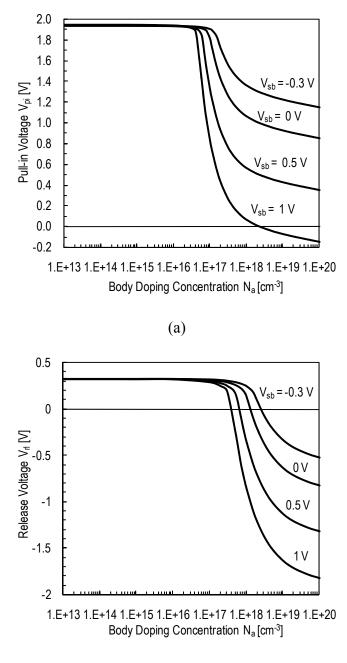

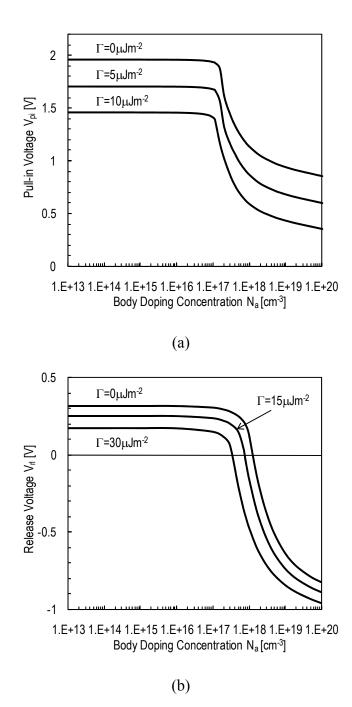

[3.11-3.14]) is solved simultaneously with the Poisson equation to accurately model  $V_{pi}$  and  $V_{rl}$  of a mechanically gated FET. Using this model, the effects of various device design parameters (*e.g.* body doping concentration, gate stiffness, as-fabricated actuation gap thickness, and source-to-body bias voltage) and surface adhesion force are assessed in Section 3.3. A unified pull-in/release voltage model which accounts for these effects is then provided in Section 3.4.

Although the NEMFET effective subthreshold swing is reduced by utilizing the pull-in effect, the presence of an air-gap in the transistor drastically worsens the short channel effects; the impact of such effects on the NEMFET's scalability for logic applications is discussed in Section 3.5.

### 3.2 Physics of NEMFET Operation

Fig. 3.1 illustrates the NEMFET structure, which is essentially a <u>metal-oxide-semiconductor field effect</u> transistor (MOSFET) with a movable gate electrode that can be physically separated from the gate dielectric layer by an air gap (or vacuum gap). As shown in the cross-sectional schematic in Fig. 3.2a, the suspended gate is a doubly-clamped beam anchored on each side of the semiconductor channel.

Fig. 3.1 also presents the NEMFET operation. In the off state, an air gap separates the gate from the gate dielectric; as  $V_{gs}$  increases, the electrostatic force attracts the gate to the gate dielectric. In the on state (Fig. 3.1d) where the gate-to-source voltage is greater than the pull-in voltage ( $V_{pi}$ ), the gate is pulled down and is in contact with gate dielectric, which increases the gate-to-channel coupling,

Once the gate is pulled in, the thin dielectric thickness ensures that the electrostatic force is larger than the spring restoring force, and therefore the NEMFET exhibits hysteretic switching (Fig. 3.1 (d)) - i.e. the release voltage  $V_{gs}=V_{rl}$  value is lower than  $V_{pi}$ .

**Fig. 3.1**. (a) Schematic diagrams of a nano-electro-mechanical field effect transistor (NEMFET). (b,c) Simple lumped-parameter model for a NEMFET. (d) the abrupt pull-in/ release of the gate electrode provide for perfectly abrupt on/ off transitions.

The change in the gap thickness at  $V_{gs}=V_{pi}$  (or  $V_{gs}=V_{rl}$ ) can be equivalently described as a dynamic reduction (or increase) in the threshold voltage  $V_T$ . If  $V_T$  for a MOSFET is defined as the value of  $V_{gs}$  for which the channel is just barely inverted, then the change in  $V_T$  due to the movement of the gate at  $V_{gs}=V_{pi}$  and  $V_{gs}=$  $V_{rl}$  is approximately  $|\Delta V_T| \approx t_{gap} \frac{\sqrt{4\varepsilon_{sl}qN_a\phi_b}}{\varepsilon_o}$  [3.1], where  $t_{gap}$  is the as-fabricated air-gap thickness,  $N_a$  is the body doping concentration, and  $2\phi_b$  is the channel potential at the onset of strong inversion in the channel. Since the threshold voltage changes abruptly as  $|V_{gb}|$  is increased above  $V_{pi}$ , (or decreased below  $V_{rl}$ ) the  $I_d$ - $V_g$  characteristic of the NEMFET exhibits an extremely steep (nearly infinite) subthreshold slope [3.1-3.4] at  $V_{pi}$  and  $V_{rl}$ . To achieve low  $S_{eff}$  value, the supply voltage must be scaled down. To achieve this goal,  $V_{pi}$  and  $V_{rl}$  need to be minimized. In the pursuit of this goal and to facilitate NEMFET design, this section aims at developing an accurate model for  $V_{pi}$  and  $V_{rl}$ .

### 3.2.1 Lumped Parameter Model

A simple lumped parameter model previously has been used to study the behavior of NEMFETs [3.1-3.3]. In this model, as depicted in Fig. 3.1b, the gate is treated as a simple linear spring (with a characteristic spring constant k) suspended over the semiconductor channel. The gate and the channel form a parallel-plate capacitor with an equivalent air-gap that is uniform in thickness across the transistor channel. The details of this lumped parameter model are well covered in the literature [3.1-3.3]; the key results are summarized herein.

**Fig. 3.2:** (a) Schematic diagrams illustrating the physical parameters of the NEMFET. (b-d) Shapes of the deflected gate beam, corresponding to the different regions of NEMFET operation: (b) Before pull-in, (c)  $V_{gs} > V_{pi}$ , (d)  $V_{gs} = V_{rl}$ .

Current flow in the semiconductor channel is controlled by the voltage applied between the gate and the source,  $V_{gs}$ . Because the gate beam is assumed not to bend, the voltage drops across the air gap  $V_{gap}$ , the dielectric  $V_{ox}$  and the semiconductor surface potential  $\phi_s$  are assumed to be independent of x:

$$V_{gs} + V_{sb} = V_{fb} + V_{gap} + V_{ox} + \phi_s = V_{fb} + V_{eff} + \phi_s$$

(3.1)

where the flat-band voltage  $V_{\rm fb}$  is a function of the channel dopant concentration  $N_{\rm a}$ :  $V_{fb} = \Phi_m - \Phi_s = C - \frac{kT}{q} ln\left(\frac{N_a}{n_i}\right)$  where C is a constant and  $\Phi_{\rm m}$  and  $\Phi_{\rm s}$  are the work functions of the gate and the semiconductor channel, respectively.  $V_{\rm eff} = V_{\rm gap}$   $+ V_{\rm ox}$  is the voltage drop across an equivalent air gap. If the gate beam is not pulled in, the spring restoring force is equal to the electrostatic force:

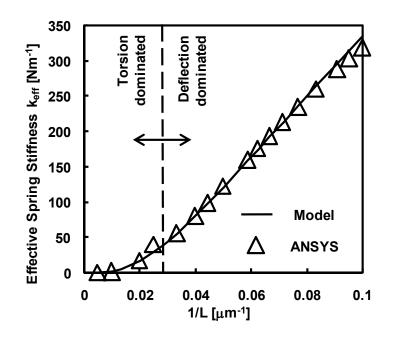

$$k\left(t_{gap} + \frac{t_{ox}}{\kappa_{ox}} - g\right) = \frac{\varepsilon_o W L V_{eff}^2}{2g^2}, \qquad k \approx 39.5 \frac{EW h^3}{L^3}$$

(3.2)

where  $g = d + t_{gap} + t_{ox}/\kappa_{ox}$  is the equivalent air-gap thickness, d<0 is the displacement of the mechanical gate,  $t_{ox}$  and  $\kappa_{ox}$  are the thickness and dielectric constant of the gate dielectric, k is the spring constant for a clamped-clamped beam, h and W and L are the thickness width and length of the gate beam, respectively. E is the Young's modulus of the gate beam material. Non-ideal effects such as dielectric charges and fringing capacitances are assumed to be negligible.

To ensure proper NEMFET operation, the spring restoring force must be significantly greater than the surface adhesion force,  $F_{a}$ . In the absence of capillary forces, the adhesive interactions are dominated by the attractive van der Waals force between non-contacting surfaces [3.15]:

$$F_a \cong \frac{2\Gamma}{d_o} WL, \text{ for } 0 < |d| \le t_{gap}$$

(3.3)

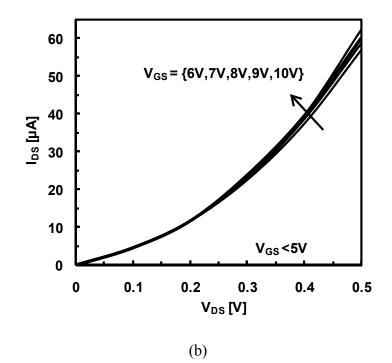

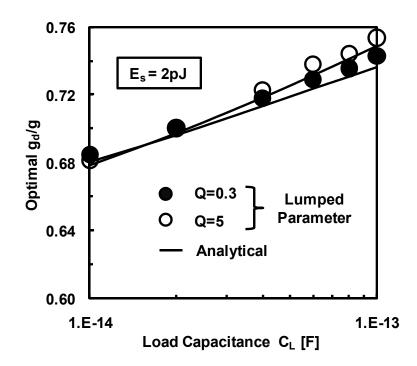

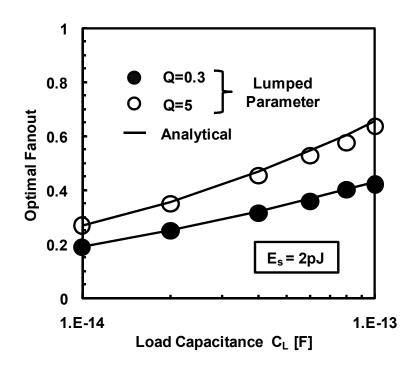

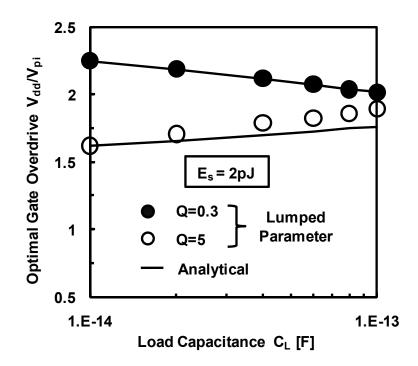

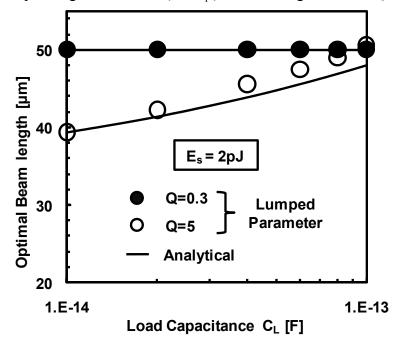

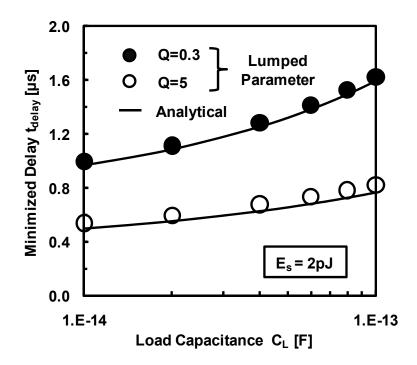

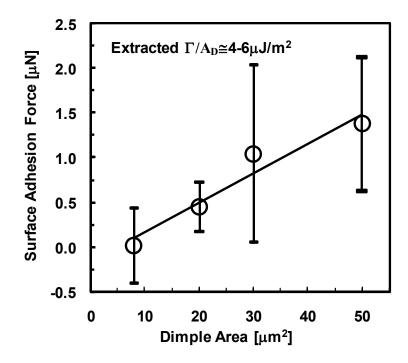

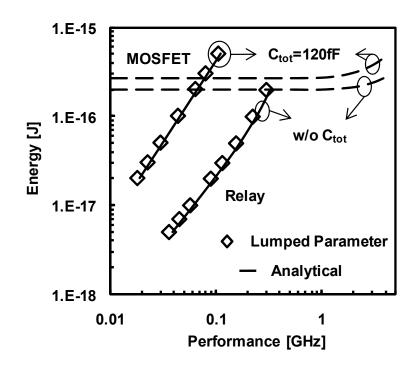

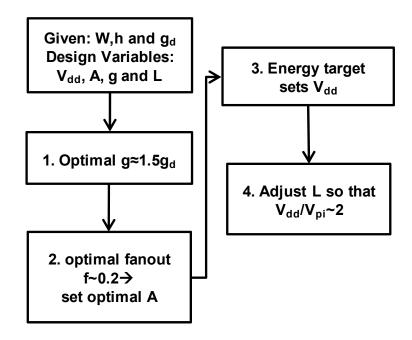

where  $\Gamma$  is the adhesion energy per unit area and  $d_0$  is the average distance between the two surfaces.