## Multi-carrier single-DAC transmitter approach applied to digital cable television

Citation for published version (APA): Beek, van, P. C. W. (2011). Multi-carrier single-DAC transmitter approach applied to digital cable television. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR716353

DOI: 10.6100/IR716353

#### Document status and date:

Published: 01/01/2011

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Multi-Carrier single-DAC transmitter approach applied to digital cable television

P.C.W. van Beek

This Ph.D. work is supported by Philips Research Laboratories and NXP Semiconductors, Eindhoven, the Netherlands, as part of the Philips/NXP research program.

P.C.W. van Beek

Multi-Carrier single-DAC transmitter approach applied to digital cable television

Proefschrift Technische Universiteit Eindhoven, 2011

Trefwoorden: Digital-to-Analog Conversion, Broadband, Multi-Carrier transmitter, DOCSIS

A catalogue record is available from the Eindhoven University of Technology Library ISBN: 978-90-386-2590-4

> © P.C.W. van Beek, 2011 All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

## Multi-carrier single-DAC transmitter approach applied to digital cable television

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 4 oktober 2011 om 16.00 uur

$\operatorname{door}$

Pieter Cornelis Willemijndert van Beek

geboren te Waalwijk

Dit proefschrift is goedgekeurd door de promotor:

prof.dr.ir. A.H.M. van Roermund

Copromotor: dr.ir. J.A. Hegt

## List of abbreviations

| ACLR            | Adjacent Channel Leakage Ratio                      |

|-----------------|-----------------------------------------------------|

| BER             | Bit Error Rate                                      |

| CATV            | Cable Television                                    |

| CIC             | Cascaded Integrator Comb                            |

| CM              | Cable Modem                                         |

| CML             | Current Mode Logic                                  |

| CMTS            | Cable Modem Termination System                      |

| CORDIC          | COordinate Rotation DIgital Computer                |

| CSD             | Canonical signed digit                              |

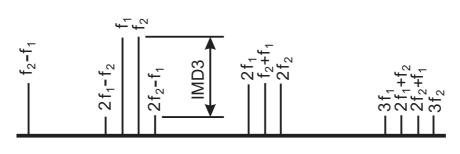

| CSO             | composite second order                              |

| CTB             | composite triple beat                               |

| DDS             | Direct digital synthesizer                          |

| DNL             | Differential nonlinearity                           |

| DOCSIS          | Data Over Cable Service Interface Specification     |

| DSP             | Digital Signal Processor                            |

| EMI             | Electromagnetic interference                        |

| EVM             | Error Vector Magnitude                              |

| FEC             | Forward Error Correction                            |

| FoM             | Figure of Merit                                     |

| HFC             | Hybrid Fibre-Coaxial                                |

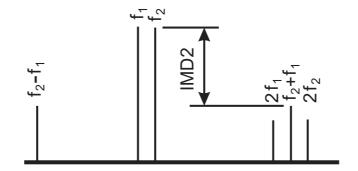

| IMD             | Intermodulation Distortion                          |

| INL             | Integral nonlinearity                               |

| ISI             | Intersymbol Interference                            |

| ITRS            | International Technology Roadmap for Semiconductors |

| LUT             | Lookup Table                                        |

| MER             | Modulation Error Rate                               |

| MSE             | mean square error                                   |

| NCO             | Numeric Controlled Oscillator                       |

| NORA            | No Race Logic                                       |

| NTSC            | National Television System Committee                |

| OFDM            | Orthogonal frequency-division multiplexing          |

| OSI             | Open Systems Interconnect                           |

| $\mathbf{PAPR}$ | Peak-to-Average Power Ratio                         |

| PCB             | Printed Circuit Board                               |

| PLL             | Phase Lock Loop                                     |

| $\mathbf{PSRR}$ | Power Supply Rejection Ratio                        |

| $\mathbf{QAM}$  | Quadrature Amplitude Modulation                     |

| QPSK            | Quadrature phase-shift keying                       |

| RRC             | Root Raised Cosine                                  |

| $\mathbf{RS}$   | Read-Solomon                                        |

| RTZ             | Return-to-Zero                                      |

- SDR Signal-to-distortion ratio

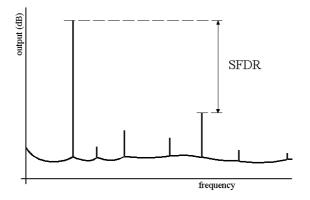

- SFDR Spurious-Free Dynamic Range

- SNDR Signal-to-noise and distortion ratio

- SOI Silicon on Insulator

- SPI Serial Peripheral Interface

- SSB Single Sideband

- TCP Transmission Control Protocol

- THD Total Harmonic Distortion

- TSPC True Single Phase Clock Logic

- VCO Voltage Controlled Oscillator

- VHDL Hardware Description Language

## Contents

| <b>1</b> | Intr                   | oduction                                                         | 1 |

|----------|------------------------|------------------------------------------------------------------|---|

|          | 1.1                    | Motivation                                                       | 2 |

|          | 1.2                    | Aim                                                              | 3 |

|          | 1.3                    | Scope                                                            | 4 |

|          | 1.4                    | Original contributions                                           | 4 |

|          | 1.5                    | Outline                                                          | 6 |

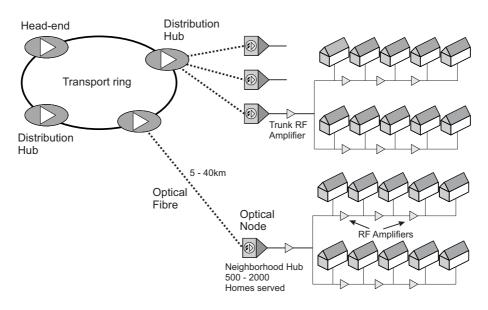

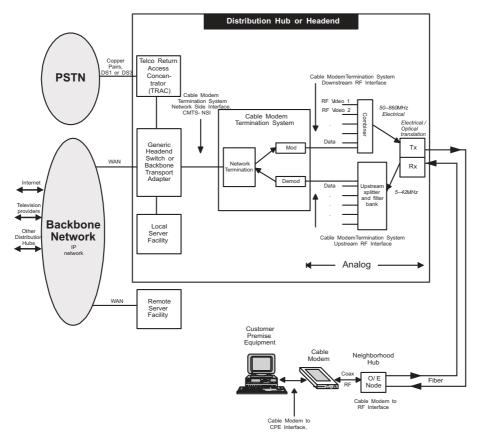

| <b>2</b> | Mu                     | ti-carrier broadcast system overview                             | 7 |

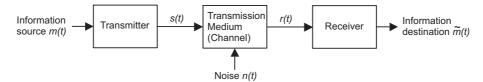

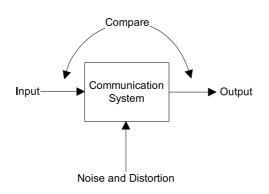

|          | 2.1                    | The communication channel                                        | 8 |

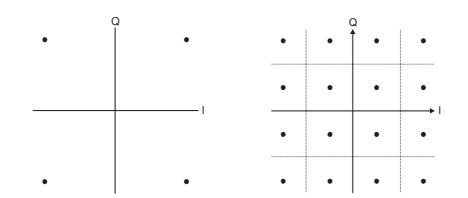

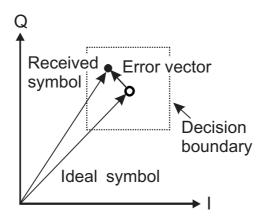

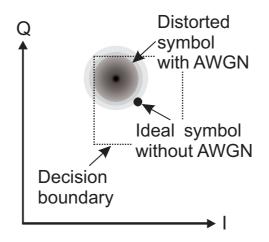

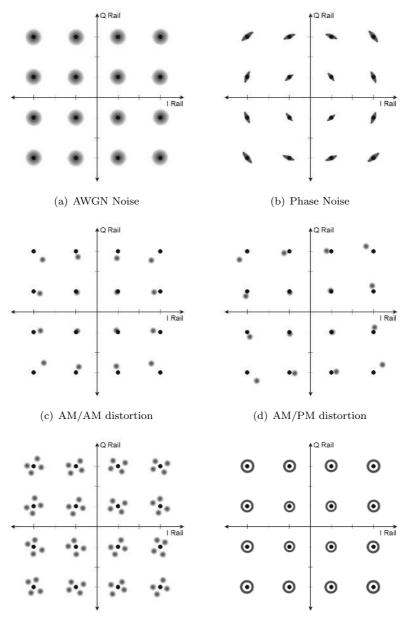

|          | 2.2                    | Signal quality evaluation of QAM signals 13                      | 8 |

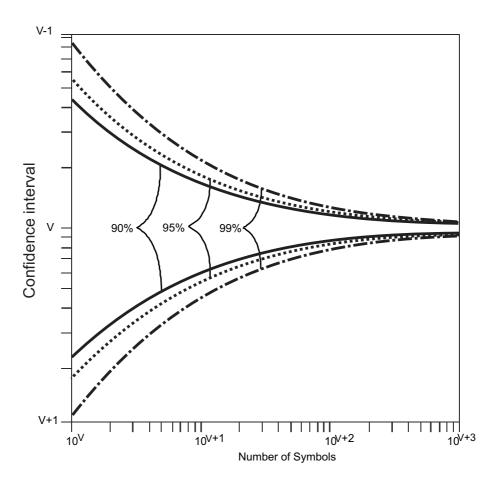

|          |                        | 2.2.1 Monte Carlo analysis to estimate the BER $\ldots \ldots 2$ | 1 |

|          |                        | 2.2.2 Semi-analytical method to estimate the BER 2               | 3 |

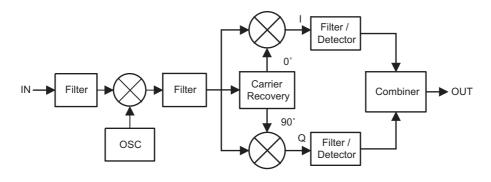

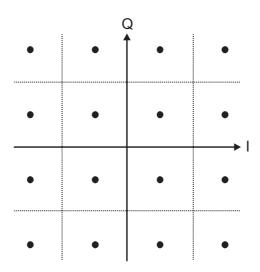

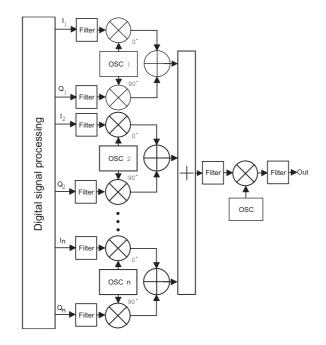

|          | 2.3                    | Multi-carrier QAM transceiver                                    | 8 |

|          | 2.4                    | Signal properties of multi-carrier QAM                           | 1 |

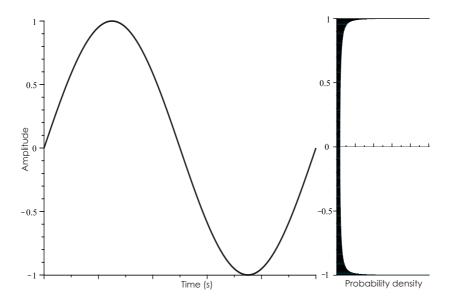

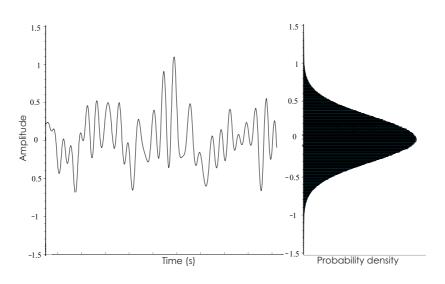

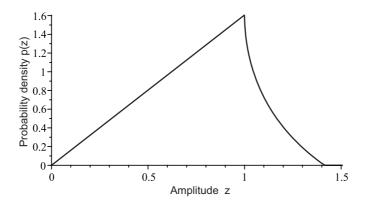

|          |                        | 2.4.1 Multi-carrier versus single sinewave signals               | 1 |

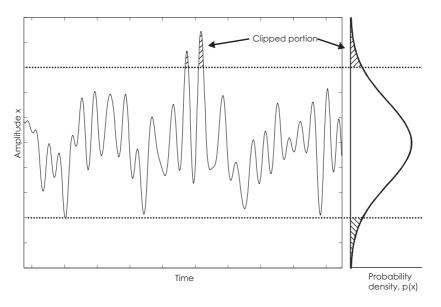

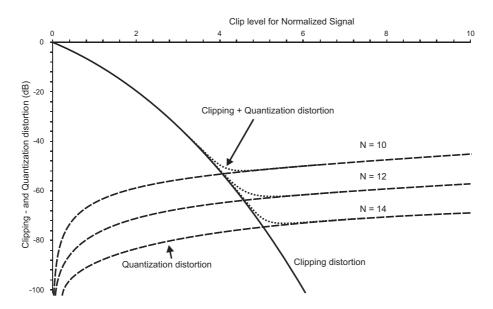

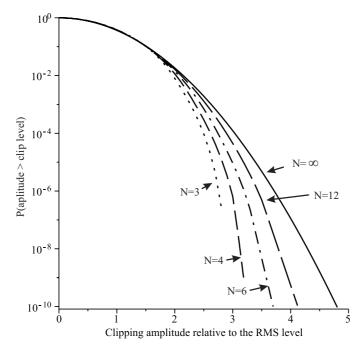

|          |                        | 2.4.2 Signal clipping                                            | 2 |

|          |                        | 2.4.3 Preventing clipping                                        | 5 |

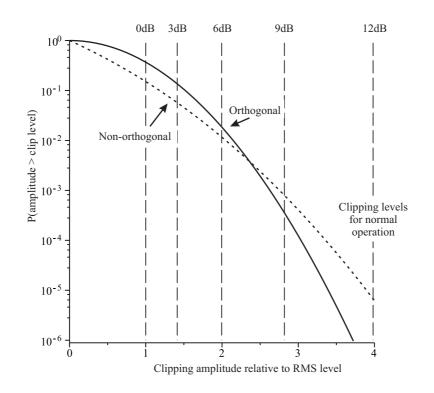

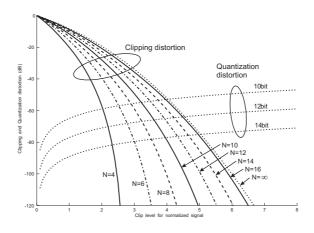

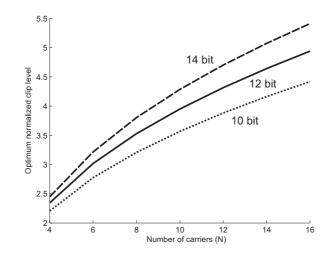

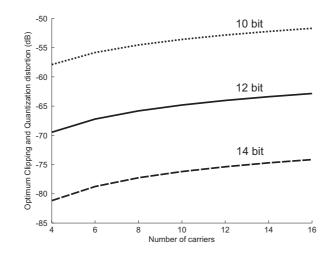

|          |                        | 2.4.4 Optimum clip level                                         | 6 |

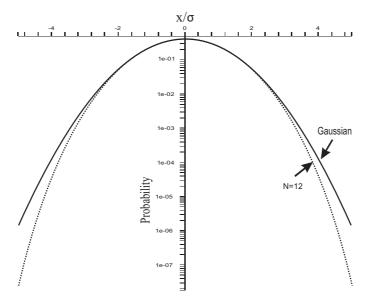

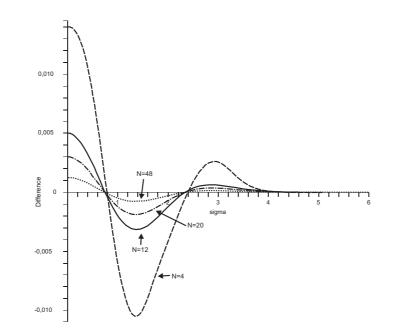

|          |                        | 2.4.5 Optimum clip level with low number of carriers 4           | 2 |

|          | 2.5                    | Conclusion                                                       | 3 |

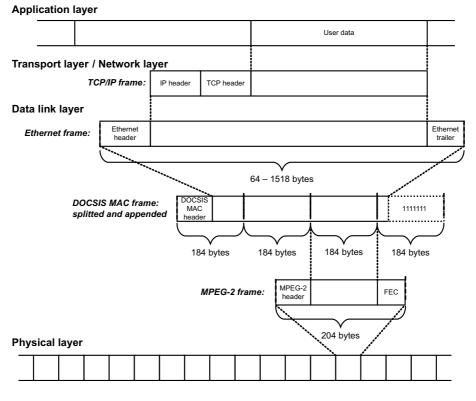

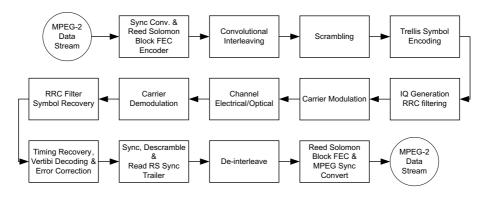

| 3        | $\mathbf{M}\mathbf{u}$ | ti-carrier DOCSIS transmitter 55                                 | 5 |

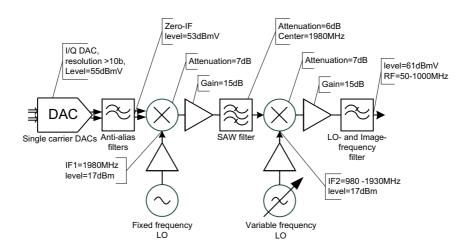

|          | 3.1                    | DOCSIS system architecture                                       | 5 |

|          |                        | 3.1.1 DOCSIS downstream data flow                                | 9 |

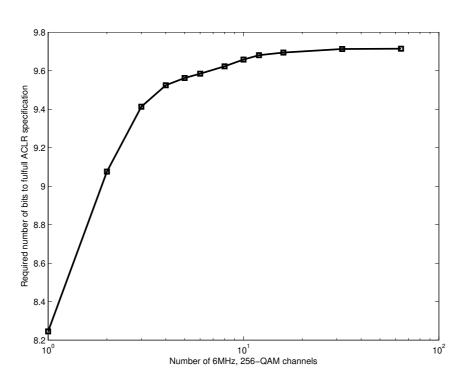

|          | 3.2                    | DOCSIS transmitter requirements                                  | 2 |

|          |                        | 3.2.1 Frequency range                                            | 3 |

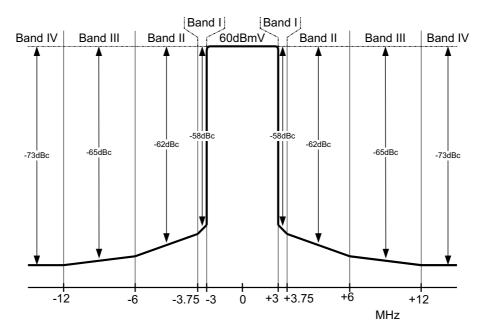

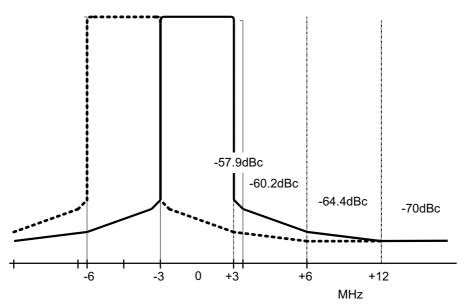

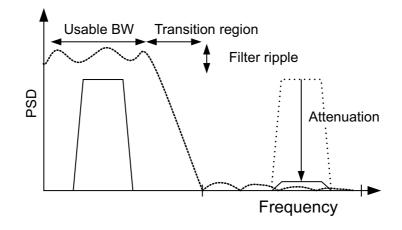

|          |                        | 3.2.2 Spectral requirements                                      | 3 |

|   |     | 3.2.3    | Signal level requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66  |

|---|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 3.3 | Conclu   | asion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68  |

| 4 | Mu  | lti-DA   | C DOCSIS transmitter system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69  |

|   | 4.1 | Archit   | ecture options and selection $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69  |

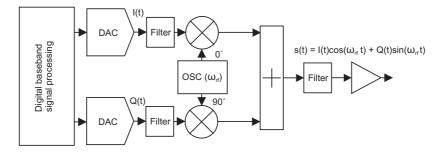

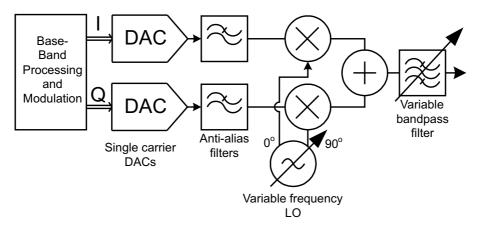

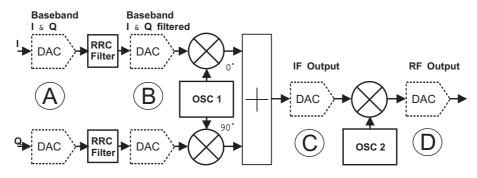

|   |     | 4.1.1    | Direct conversion transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70  |

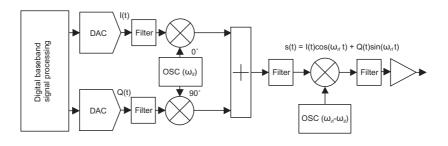

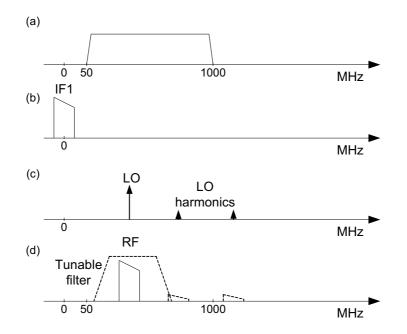

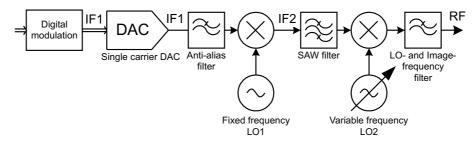

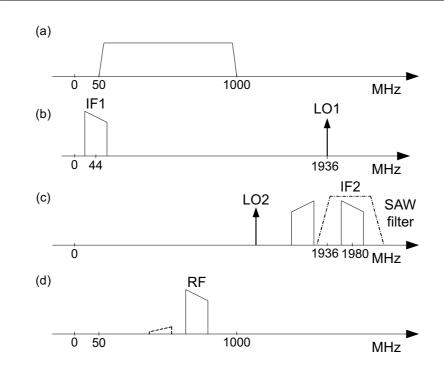

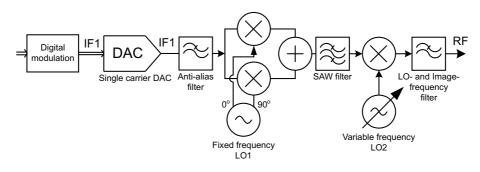

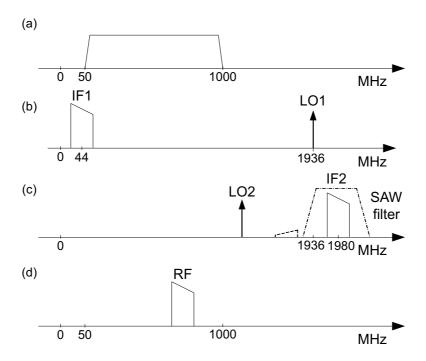

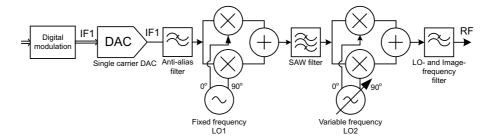

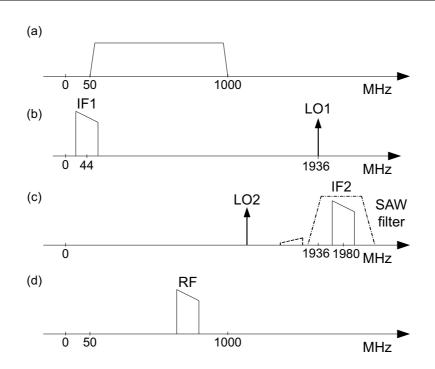

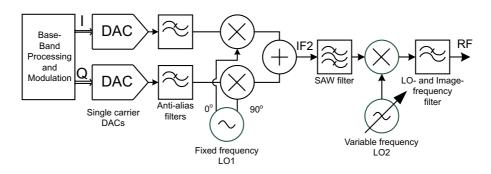

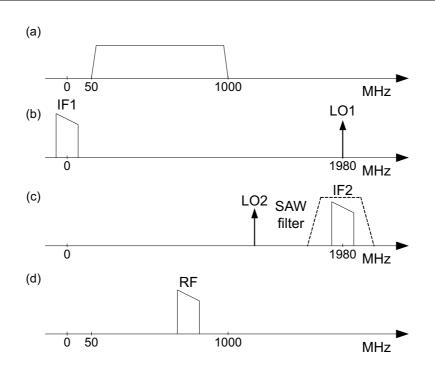

|   |     | 4.1.2    | Dual conversion transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72  |

|   | 4.2 | Comp     | onents options and selections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82  |

|   |     | 4.2.1    | Single carrier DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82  |

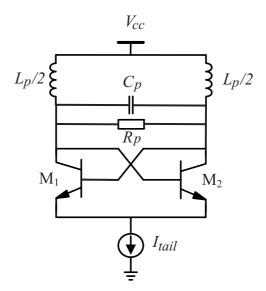

|   |     | 4.2.2    | Local oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83  |

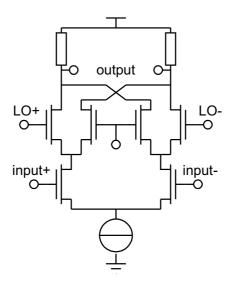

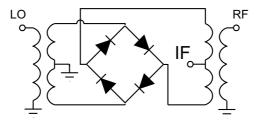

|   |     | 4.2.3    | Mixers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88  |

|   |     | 4.2.4    | IF filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 93  |

|   | 4.3 | Power    | estimation of a transmitter $\hfill \hfill \ldots \hfill \hfil$ | 94  |

|   |     | 4.3.1    | DAC power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97  |

|   |     | 4.3.2    | LC oscillator power consumption $\hdots \hdots \hd$      | 97  |

|   |     | 4.3.3    | Amplifiers and buffers power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98  |

|   |     | 4.3.4    | Total power consumption $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

|   | 4.4 | Conclu   | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100 |

| 5 | Dig | itizatio | on of multi-carrier DOCSIS transmitter system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101 |

|   | 5.1 | Increa   | sed digitization of a single carrier transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102 |

|   |     | 5.1.1    | Before Nyquist filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 103 |

|   |     | 5.1.2    | After Nyquist filter before first mixer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 104 |

|   |     | 5.1.3    | After first mixer and combiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 105 |

|   |     | 5.1.4    | At RF signal $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105 |

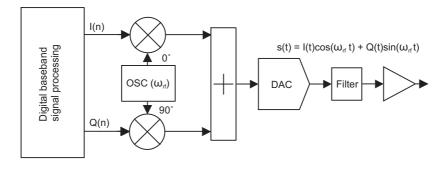

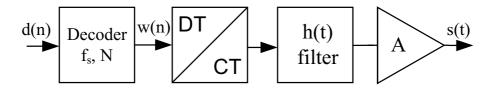

|   | 5.2 | Single   | -carrier 'all-digital' transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106 |

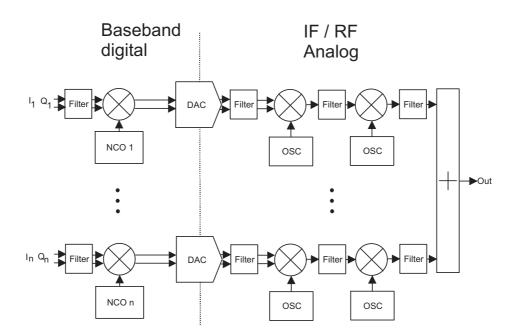

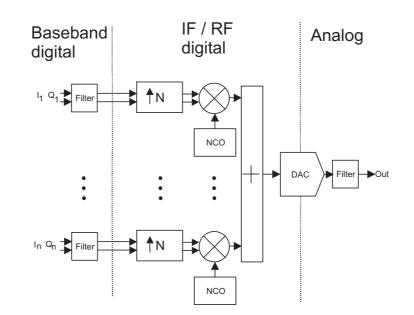

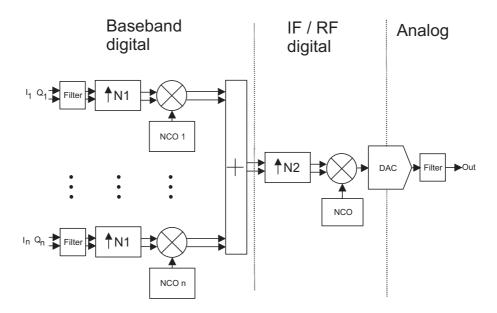

|   | 5.3 | Multi-   | carrier DOCSIS transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 107 |

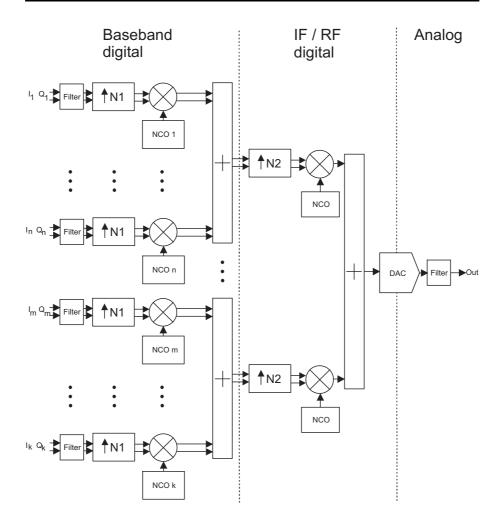

|   | 5.4 | Multi-   | carrier 'all-digital' transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 109 |

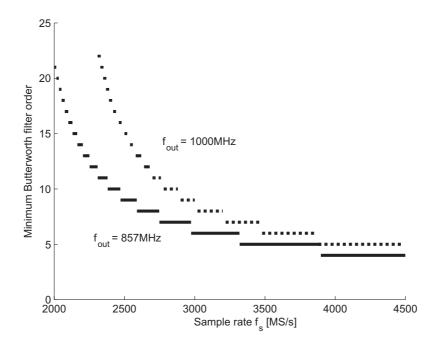

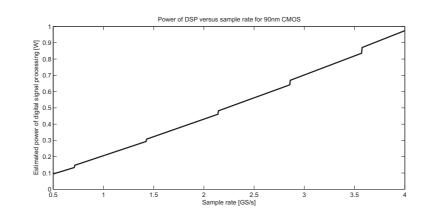

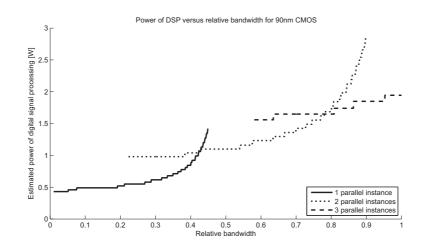

|   | 5.5 | Sampl    | e rate selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 111 |

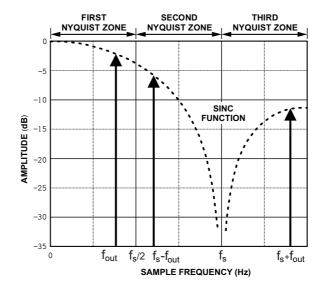

|   |     | 5.5.1    | Band repetition used for upconversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 112 |

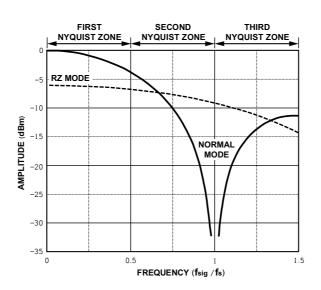

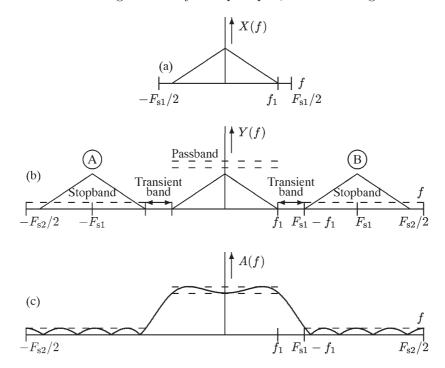

|     |       | 5.5.2   | Sample rate vs analog low-pass filtering                                 | 113 |

|-----|-------|---------|--------------------------------------------------------------------------|-----|

|     |       | 5.5.3   | Sample rate vs symbol rate                                               | 116 |

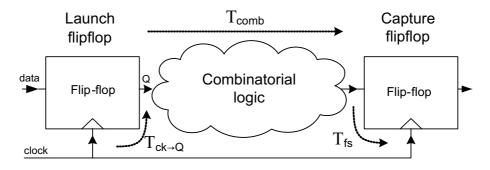

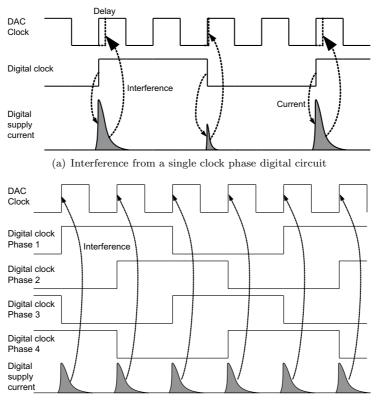

| 5.  | .6    | Digita  | l logic                                                                  | 116 |

|     |       | 5.6.1   | Conventional static CMOS logic implementation aspects                    | 117 |

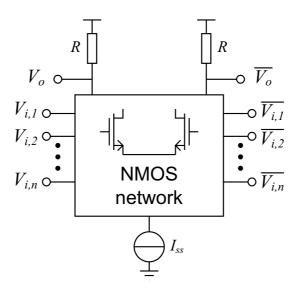

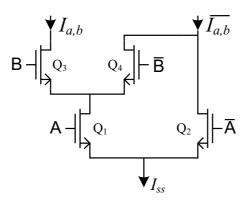

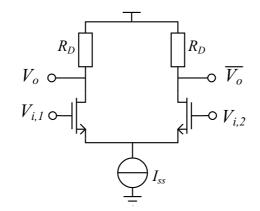

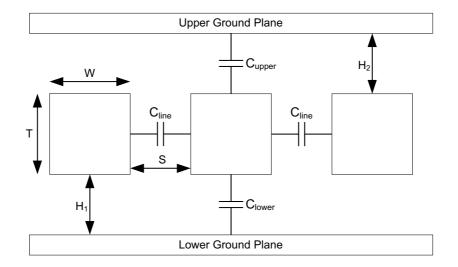

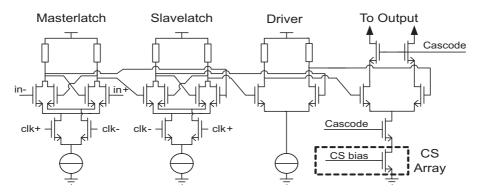

|     |       | 5.6.2   | Current mode logic implementation aspects $\ldots$ .                     | 118 |

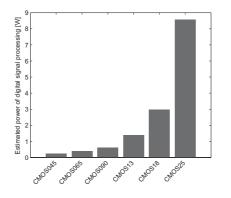

|     |       | 5.6.3   | Technology scaling of conventional static CMOS logic $$ .                | 124 |

|     |       | 5.6.4   | Technology scaling of CML                                                | 126 |

| 5.  | .7    | Conclu  | isions                                                                   | 127 |

| 6 A | .11-0 | digital | multi-carrier single-DAC transmitter                                     | 129 |

| 6.  | .1    | Single  | DAC transmitter architecture                                             | 130 |

| 6.  | .2    | Comp    | onents options and selections                                            | 130 |

|     |       | 6.2.1   | Clock source                                                             | 130 |

|     |       | 6.2.2   | Data rate converter                                                      | 132 |

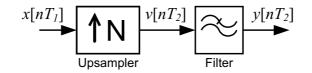

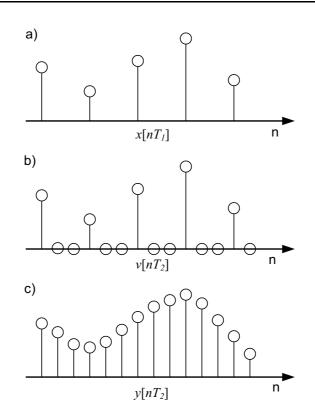

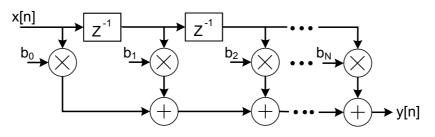

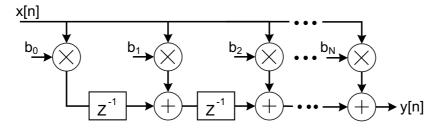

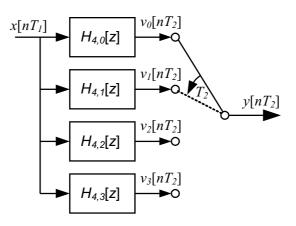

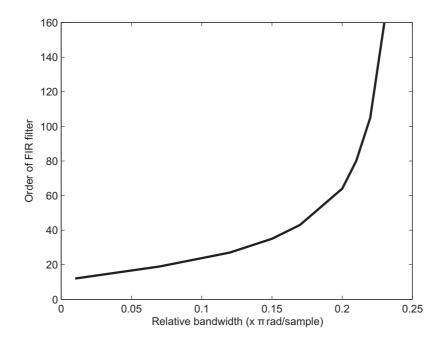

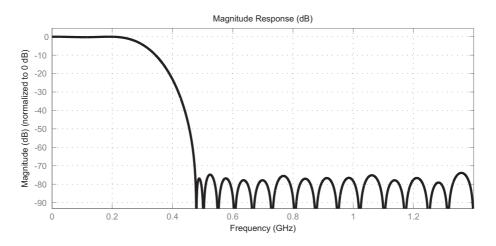

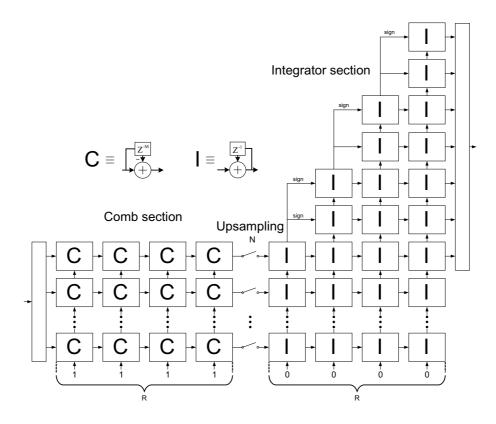

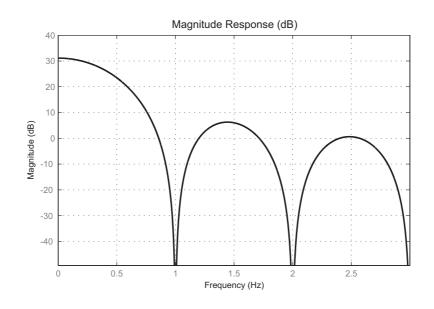

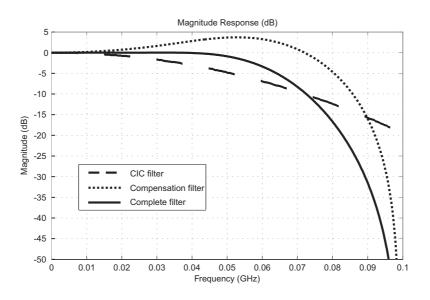

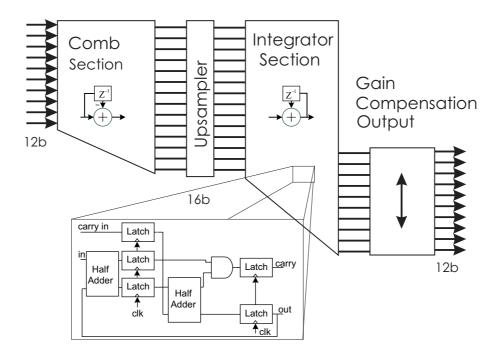

|     |       | 6.2.3   | Upsample filters                                                         | 134 |

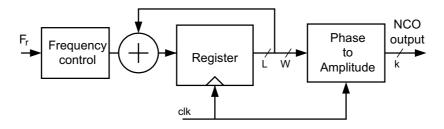

|     |       | 6.2.4   | Numerically controlled oscillator $\ldots \ldots \ldots \ldots \ldots$   | 155 |

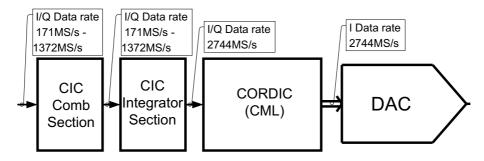

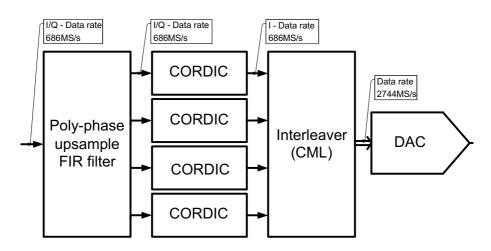

| 6.  | .3    | Digita  | l signal processing architecture                                         | 164 |

| 6.  | .4    | Power   | consumption in digital logic $\ldots \ldots \ldots \ldots \ldots \ldots$ | 169 |

|     |       | 6.4.1   | Power consumption in CMOS logic                                          | 169 |

|     |       | 6.4.2   | Power consumption in CML logic                                           | 175 |

|     |       | 6.4.3   | The power consumption estimation of the DSP $\ . \ . \ .$                | 176 |

| 6.  | .5    | Conclu  | usion                                                                    | 179 |

| 7 D | A     | C anal  | ysis, design and implementation                                          | 181 |

| 7.  | .1    | DAC l   | pasics                                                                   | 181 |

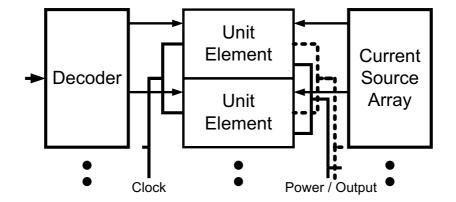

|     |       | 7.1.1   | Digital-to-Analog Converter subfunctions $\ldots \ldots \ldots$          | 181 |

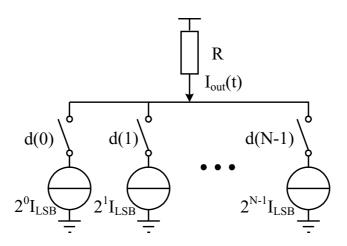

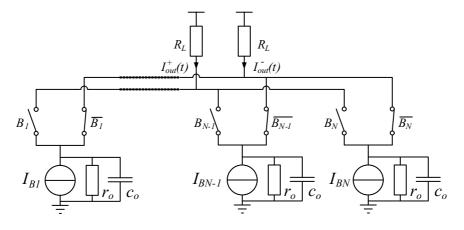

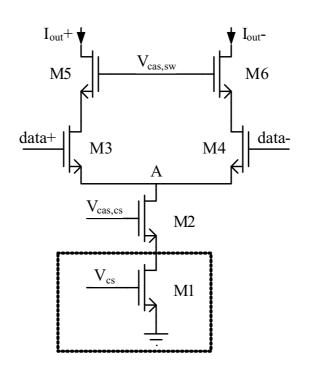

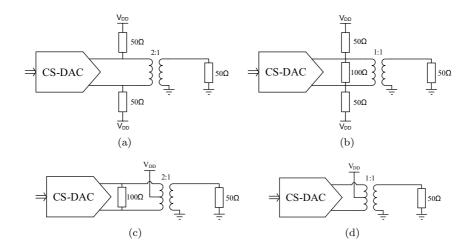

|     |       | 7.1.2   | Current steering D/A Converter $\ldots \ldots \ldots \ldots$             | 183 |

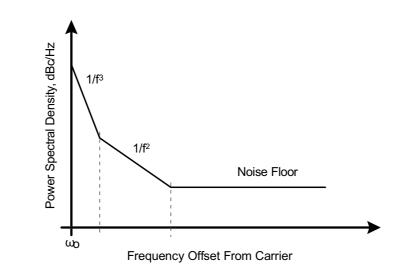

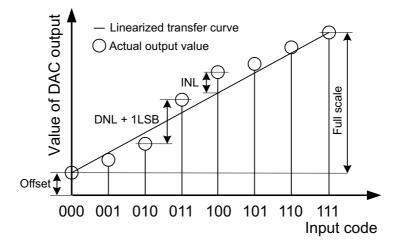

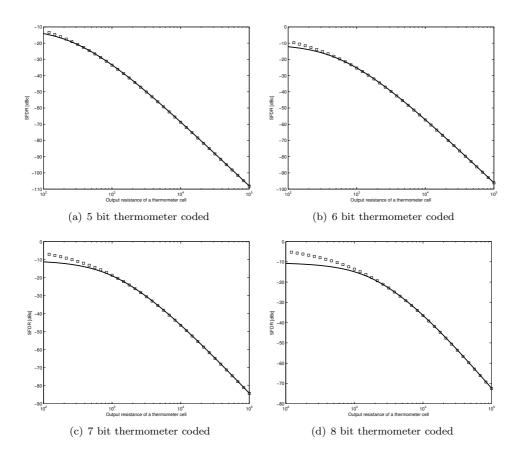

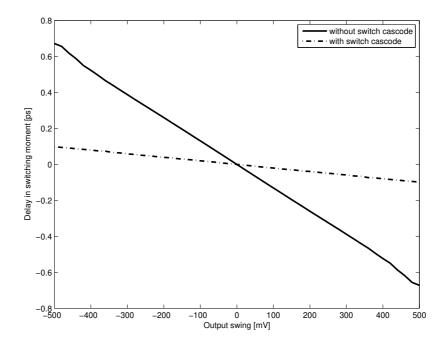

|     |       | 7.1.3   | Performance characterization                                             | 186 |

| 7.  | .2    | Signal  | quality in case of DAC imperfections $\ldots \ldots \ldots \ldots$       | 195 |

|     |       | 7.2.1   | Noise by quantization                                                    | 196 |

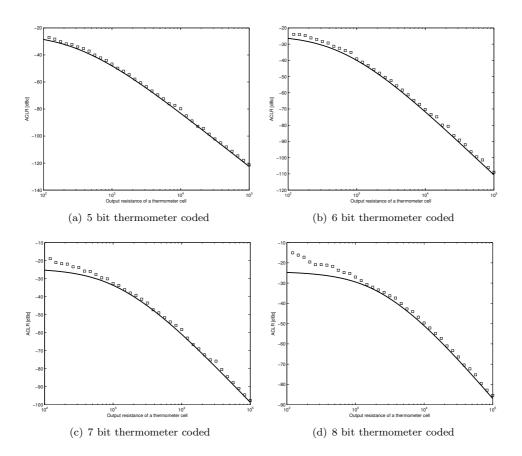

|              |      | 7.2.2 Amplitude error by output impedance $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 198 |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

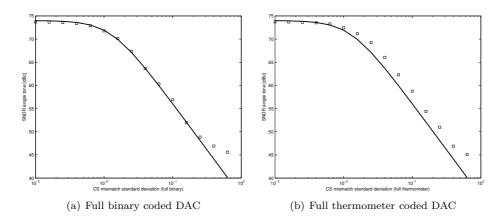

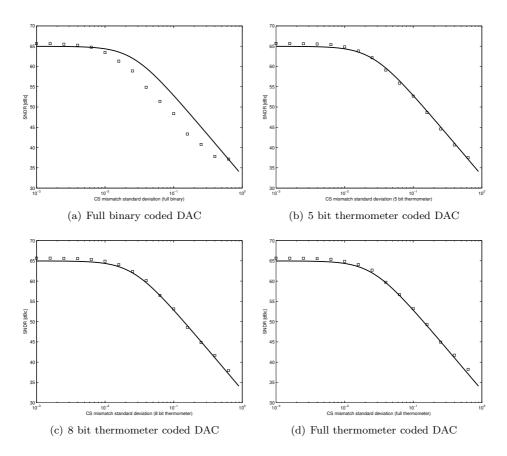

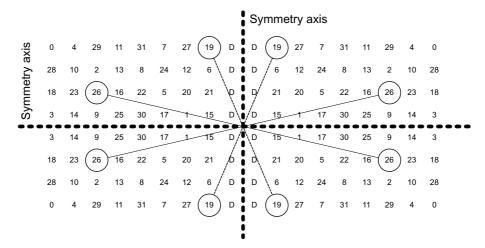

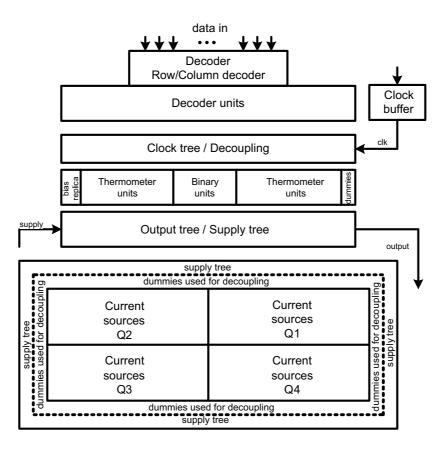

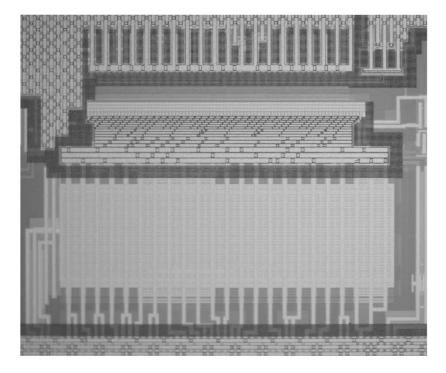

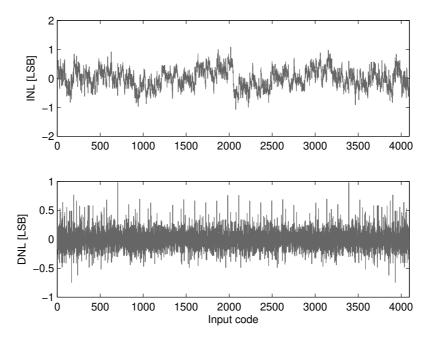

|              |      | 7.2.3 Amplitude error by current source mismatch $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 206 |