## THE UNIVERSITY of EDINBURGH

## Edinburgh Research Explorer

## Multi-State Memristors and Their Applications: An Overview

### Citation for published version:

Wang, C, Si, Z, Jiang, X, Malik, A, Pan, Y, Stathopoulos, S, Serb, A, Wang, S, Prodromakis, T & Papavassiliou, C 2022, 'Multi-State Memristors and Their Applications: An Overview', *IEEE Journal of* Emerging and Selected Topics in Circuits and Systems. https://doi.org/10.1109/JETCAS.2022.3223295

### **Digital Object Identifier (DOI):**

10.1109/JETCAS.2022.3223295

#### Link:

Link to publication record in Edinburgh Research Explorer

**Document Version:** Peer reviewed version

**Published In:** IEEE Journal of Emerging and Selected Topics in Circuits and Systems

#### **General rights**

Copyright for the publications made accessible via the Edinburgh Research Explorer is retained by the author(s) and / or other copyright owners and it is a condition of accessing these publications that users recognise and abide by the legal requirements associated with these rights.

Take down policy The University of Edinburgh has made every reasonable effort to ensure that Edinburgh Research Explorer content complies with UK legislation. If you believe that the public display of this file breaches copyright please contact openaccess@ed.ac.uk providing details, and we will remove access to the work immediately and investigate your claim.

# Multi-State Memristors and Their Applications: An Overview

Chaohan Wang<sup>®</sup>, Graduate Student Member, IEEE, Zhaoguang Si<sup>®</sup>, Graduate Student Member, IEEE,

Xiongfei Jiang<sup>®</sup>, Graduate Student Member, IEEE, Adil Malik<sup>®</sup>, Graduate Student Member, IEEE,

Yihan Pan<sup>®</sup>, Graduate Student Member, IEEE, Spyros Stathopoulos<sup>®</sup>,

Alexander Serb<sup>(D)</sup>, Senior Member, IEEE, Shiwei Wang<sup>(D)</sup>, Senior Member, IEEE,

Themis Prodromakis<sup>(b)</sup>, Senior Member, IEEE, and Christos Papavassiliou<sup>(b)</sup>, Senior Member, IEEE

Abstract-Memristors show great potential for being integrated into CMOS technology and provide new approaches for designing computing-in-memory (CIM) systems, brain-inspired applications, trimming circuits and other topologies for the beyond-CMOS era. A crucial characteristic of the memristor is multi-state<sup>1</sup> switching. Memristors are capable of representing information in an ultra-compact fashion, by storing multiple bits per device. However, certain challenges remain in multistate memristive circuits and systems design such as device stability and peripheral circuit complexity. In this paper, we review the state of the art of multi-state memristor technologies and their associated CMOS/Memristor circuit design, and discuss the challenges regarding device imperfection factors, modelling, peripheral circuit design and layout. We present measurement results of our in-house fabricated multi-state memristor as an example to further illustrate the feasibility of applying multistate memristors in CMOS design, and demonstrate their related future applications such as multi-state memristive memories in machine learning, memristive neuromorphic applications, trimming and tuning circuits, etc. In the end, we summarize past and present efforts done in this field and envisage the direction of multi-state memristor related research.

Index Terms—Memristor, RRAM, memristive circuits and systems, multi-state memristors, multi-bit RRAM, AI hardware.

#### I. INTRODUCTION

I N the past decades, the semiconductor industry has steadily followed Moore's law by advancing to deeper technology nodes. In view of the possibility that CMOS technology may eventually approach its physical limit, new devices have been proposed to be integrated with the existing technology. At the same time, the pursuit of novel computing architectures such

Chaohan Wang, Zhaoguang Si, Adil Malik, and Christos Papavassiliou are with the Department of Electrical and Electronic Engineering, Imperial College London, London SW7 2AZ, U.K. (e-mail: chaohan.wang18@imperial.ac.uk; zhaoguang.si20@imperial.ac.uk; muhammad.malik15@imperial.ac.uk; c.papavas@imperial.ac.uk).

Xiongfei Jiang, Yihan Pan, Spyros Stathopoulos, Alexander Serb, Shiwei Wang, and Themis Prodromakis are with the School of Engineering, University of Edinburgh, Edinburgh EH8 9YL, U.K. (e-mail: xiongfei.jiang@ed.ac.uk; yihan.pan@ed.ac.uk; s.stathopoulos@ed.ac.uk; aserb@ed.ac.uk; shiwei.wang@ed.ac.uk; t.prodromakis@ed.ac.uk). as neuromorphic computing has been driven by the need for addressing the data scalability limits in the traditional von-Neumann architectures. The rapid technological advances of memristors promise to resolve both issues, improving the capability of electronics beyond what the CMOS cannot achieve alone and rendering unconventional computing architectures that are becoming viable [1].

Since Leon Chua postulated the concept of the memristor in 1971 [2], several devices with similar characteristics to the conceptual memristor had been reported in the literature [3-7], but the conceptual memristor was not linked to any physical devices in the following three decades. In the early 2000s, an increasing number of Metal-Oxide-Metal (MOM) devices with non-volatile resistive switching behaviour started to emerge, such as the ones in [8-11]. One typical example is a solidstate non-volatile device based on the Copper-Tungsten oxide whose resistance can be switched by the applied write current [12]. In 2008, HP lab first linked a non-volatile resistive switching device based on Pt- $TiO_2$ -Pt layered structure [13] to the theoretical concept of a memristor. Since then, memristors have attracted increasing attention from the research community, and memristors based on different types of materials have been reported. More importantly, memristors' unique features such as non-volatility, small feature size (down to 2nm [14]), low power consumption, and compatibility with CMOS technology for monolithic integration render them good candidates for using in various applications [15-21].

Among all of the promising advantages of the memristor, the multi-state switching capability is a unique feature. Since 2008, using the multi-state characteristic of memristors in next-generation electronics has become a popular research direction because a single memristor can potentially replace multiple transistors, while performing the same logic function [22]. Nevertheless, multi-state memristors still face various challenges including retention degradation, vulnerability, device-to-device variations, cycle-to-cycle variations, process voltage temperature (PVT) variations, inaccurate modelling, complex control logic and excitation circuits, etc [23–26].

<sup>1</sup>also often referred as multibit, multi-state, and multi-level

In this paper, we review multi-state memristors with different bi-layer oxide combinations and the state-of-the-art

Manuscript received XXX; revised XXX

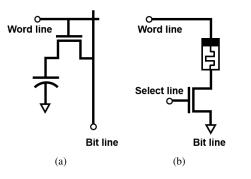

Fig. 1: (a) A conventional DRAM consists of 1T1C cells. Each capacitor stores 1-bit information. (b) A multi-state 1T1R memristor cell can in principle store up to 5.5-bit of information [28].

memristive systems. We mainly analyse the difficulties and challenges that lie in the memristive circuits and systems design, and provide an overview of the multi-state memristors related applications. The rest of the paper is organized as follows: Section II reviews multi-state memristors and the state-of-the-art CMOS/Memristor systems. Section III illustrates the design challenges of multi-state memristive systems including device defects, device modelling, peripheral circuits design, and layout and post-processing in CMOS. Section IV introduces three major categories of applications where multistate memristors can enhance overall performance. Section V discusses high-level insights and research directions for multistate memristive systems, and Section VI concludes the paper.

#### II. MULTI-STATE MEMRISTOR DEVICES AND SYSTEMS

Shortly after the memristor was realised as a solid-state device in [13], the concepts of exploiting a multi-state memristor to realise logic functions [22] and memory [27] were proposed. Taking a random-access-memory (RAM) as an example, as shown in Fig.1, traditional DRAM employs 1 transistor and 1 capacitor (1T1C) to store 1-bit information in one cell, whereas in a multi-state 1 transistor and 1 memristor (1T1R) cell, a single memristor can store up to 5.5-bit information in principle [28]. In addition, the capacitor in the DRAM cell needs to be refreshed periodically to deal with charge leakage. The memristor's non-volatility not only prevents the information loss due to the leakage, but also enables fast and safe power-cycling. Compared with other RAMs such as SRAM, memristive RAM can achieve higher density while maintaining the same speed [29]. In this section, we review the multi-state memristor devices based on different bi-layer oxides and the performance of the state-of-the-art multi-state memristors in integrated 1T1R crossbar arrays.

#### A. Multi-State Memristor Device

Metal-oxide-metal (MOM) memristors have been reported with many electrode material and active material combinations, which lead to different specifications and performance. For example, a  $TiO_x$  memristor with gold electrodes is almost completely volatile, while the one with platinum electrodes is

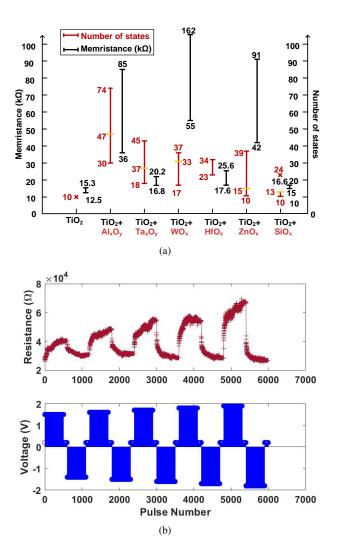

Fig. 2: (a) Memristors based on different oxide combinations exhibit different resistive state ranges and multi-state switching capabilities. The monolayer device (only  $TiO_2$ ) has lower resistance range and number of states compared with the bi-layer devices. (b) The Pt- $TiO_2$ + $Al_2O_3$ -Pt memristor exhibits multi-state switching behaviour. The stimulus consists of sets of programming voltage pulses with increasing amplitude at 500 pulses per voltage level and pulse width of  $10\mu s$ . Between each programming process, there are 100 reading pulses with the same amplitude of 0.2V and the same pulse width of  $10\mu s$ .

almost completely non-volatile. Besides the electrode materials which determine the volatility of a memristor, active materials determine the multi-state switching behaviour. Among different bi-layer oxide combinations, the most popular ones use  $Ta_2O_5$ ,  $HfO_2$  and  $TiO_2$  as their main active oxides and a variety of metals as electrodes [30-34]. Every combination behaves differently as a multi-state device. These differences include the values of the high and low resistive states (HRS, LRS) and the number of distinguishable states indicated by different resistive switching ranges. The resistive switching range is important because it affects the trade-off among power consumption, linearity, and resolution of the peripheral circuit design, whereas independent and distinguishable states affect the stability, reliability, and reconfigurability of the multistate memristor. Here, a comparison is made based on the work in [28] analysing 7x types of memristors, of which

| Bi-layer Oxide               | TiO <sub>2</sub> | $\begin{array}{ccc} TiO_2 & TiO_2 \\ +Al_xO_y & +Ta_xO_y \end{array}$ |      | $TiO_2$<br>+ $WO_x$ | $TiO_2$<br>+ $HfO_x$ | $TiO_2$<br>+ $ZnO_x$ | $TiO_2$<br>+ $SiO_x$ |  |

|------------------------------|------------------|-----------------------------------------------------------------------|------|---------------------|----------------------|----------------------|----------------------|--|

| Number of<br>States          | 10               | 47                                                                    | 37   | 33                  | 23                   | 15                   | 13                   |  |

| LRS (kΩ)                     | 12.5             | 36                                                                    | 16.8 | 55                  | 17.6                 | 42                   | 15                   |  |

| HRS $(k\Omega)$              | 15.3             | 85                                                                    | 20.2 | 162                 | 25.6                 | 91                   | 16.6                 |  |

| Range (kΩ)                   | 2.8              | 49                                                                    | 3.4  | 107                 | 8                    | 49                   | 1.6                  |  |

| HRS/LRS<br>Ratio             | 1.2              | 2.4                                                                   | 1.2  | 2.9                 | 1.5                  | 2.1                  | 1.1                  |  |

| Equivalent<br>Number of Bits | 3.3              | 5.5                                                                   | 5.2  | 5                   | 4.5                  | 3.9                  | 3.7                  |  |

TABLE I: SUMMARY OF BEHAVIOUR OF MULTI-STATE MEMRIS-TORS BASED ON DIFFERENT BI-LAYER STRUCTURES [28]

6x feature different bilayer oxide combinations  $(TiO_x)$  is the "base layer" in all cases) and 1x is a simple monolayer device (only  $TiO_x$  "base layer" oxide). As shown in Fig.2 (a) and Table I. The monolayer memristor exhibits the lowest number of states, smallest resistive switching range, and low HRS/LRS ratio. On the other hand, memristors based on  $TiO_2$ with  $Al_xO_y^2$ ,  $WO_x$ , and  $ZnO_x$  exhibit promising multi-state capability. In particular, the  $TiO_2+Al_2O_3$  bi-layer shows the highest number of states and has been leveraged in different integrated applications such as a one-time-programming memristive memory (RRAM) in [35]. Fig.2 (b) shows an example of the measurement result of a Pt- $TiO_2+Al_2O_3$ -Pt memristor. After applying voltage pulses with an increasing amplitude, the memristor can be written to different resistance states.

The retention measurement is another important process for characterizing a memristor. Memristors experience retention degradation after a certain time or in different temperatures, which leads to undesired volatile behaviours. For example, in the study reported in [28], at room temperature, the Pt- $TiO_2+Al_2O_3$ -Pt memristor in Table I only achieves 10 states after 8 hours of electroforming<sup>3</sup>. When baking the memristor with 85°C, the memristor can only retain 4 states. Similarly, the SiN- $TiNO_x+WO_x+TiNO_x$ -SiN memristor with 8 states in [36], the W-Ta+ $TaO_x$ -Pt memristor with 8 states in [37], and the Au- $Al_2O_3+HfO_2$ -TiN memristor with 16 states in [38] only retain their states up to 85°C. Since retention is an inevitable problem when employing memristor's multi-state characteristic, it has to be carefully considered and handled.

#### B. Multi-State Memristive System State of the Art

Although stand-alone memristors range from supporting 10 to 47 states (Table I), an essential problem is assessing this capability within a CMOS/Memristor system. The highest reported number of independent states in a memristive neural network is 32 [24], which is equivalent to 5x bits. Yet, when employing these states, multi-state memristors in an array are unreliable and experience high device-to-device and cycle-to-cycle variations, low yield rate, and limited precision [24], which limit applicability in multi-state memristive systems.

The past five years have seen the emergence of fully integrated memristive systems, especially RRAM in neuromorphic computing [35, 39–48]. Among these works, the multi-state

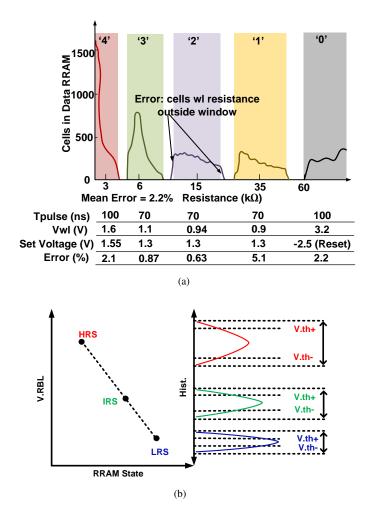

Fig. 3: (a) The RRAM design in [40] presents 5 independent states in a single cell. Each state is defined within a resistance range, and error windows are defined between each resistance range. (b) The fully integrated RRAM in [46] exhibits three resistance states (i.e HRS, IRS and LRS) and can store 1.58 bit/cell.

RRAM exhibits its advantage of storing more information in a single cell [35, 40, 45, 46]. Table II shows the state-ofthe-art RRAM systems, and few observations are acquired. Although weight resolution in an RRAM system can reach up to 20-bit in [47], the highest reported number of states in a single RRAM cell is 5, which is equivalent to 2.3-bit information storage per cell [40]. As shown in Fig.3 (a), in this work, error windows are defined between resistance ranges to avoid the collision. When writing to a desired state, write voltages are precisely controlled. This method is also adopted in other multi-state RRAM designs such as the one proposed in [29]. In 2021, a fully integrated RRAM exhibiting 3 independent states that can be employed to store 1.58 bit/cell of information was reported [46]. As shown in Fig.3 (b), by using this approach, an intermediate resistance state (IRS) is used to achieve 3 states. Another RRAM employing 3 states is also adopted in [35], a fuse state is employed beyond the HRS. Nevertheless, the multi-bit weight does not correspond to a true multi-state memristor cell, among all the state-of-theart memristive systems, most of them still only employ two states, HRS and LRS, to achieve reliable switching.

$<sup>^{2}</sup>Al_{x}O_{y}$  stands for Aluminum Oxide such as  $Al_{2}O_{3}$

<sup>&</sup>lt;sup>3</sup>An electrical biasing routine undertaken to electrochemically activate a device after manufacturing and before it is used for the first time. This can frequently involve voltages many times larger than normal operating conditions.

|                                 | ISSCC 18  | VLSI 18       | ISSCC 19                | ISSCC 19  | ISSCC 20  | ISSCC 20  | ISSCC 20  | SSCL 20    | CICC 21       | ISSCC 21  | ISSCC 21   |

|---------------------------------|-----------|---------------|-------------------------|-----------|-----------|-----------|-----------|------------|---------------|-----------|------------|

|                                 | [39]      | [35]          | [40]                    | [41]      | [42]      | [43]      | [44]      | [45]       | [46]          | [47]      | [48]       |

| Technology                      | 65nm      | 14nm          | 130nm                   | 55nm      | 130nm     | 130nm     | 22nm      | 90nm       | 40nm          | 40nm      | 22nm       |

| Supply (Volt)                   | 1.0 V     | 5.5 V         | 0.71-1.2 V              | 1.0 V     | 4.2 V     | 1.8 V     | 0.7-0.9 V | 1.2 V      | 0.9 V         | 0.9 V     | 0.8 V      |

| Multi-bit Weight Memristor Cell | No        | Yes           | Yes                     | No        | No        | No        | No        | Yes        | Yes           | No        | No         |

| RRAM Type                       | Digital   | Digital       | Digital                 | Digital   | Analog    | Analog    | Digital   | Digital    | Digital       | Digital   | Digital    |

| Array Size                      | 512 x 256 | n/a           | 256 x 16                | 256 x 512 | 784 x 784 | 256 x 256 | 512 x 512 | 128 x 64   | 256 x 256     | 256 x 256 | 1024 x 512 |

| Array Type                      | 1T1R      | 1S1R          | 1T1R                    | 1T1R      | 2T2R      | 1T1R      | 1T1R      | 1T1R       | 1T1R          | 1T1R      | 1T1R       |

| Max Input Resolution            | 1 bit     | n/a           | 1 bit                   | 2 bit     | 1 bit     | 1 bit     | 4 bit     | 1 bit      | 1 bit         | 8 bit     | 8 bit      |

| Max Weight Resolution           | Ternary   | 1.58 bit/cell | 5.6 bit<br>2.3 bit/cell | 3 bit     | Ternary   | Analog    | 4 bit     | 2 bit/cell | 1.58 bit/cell | 8 bit     | 8 bit      |

| Max Output Resolution           | 3 bit     | n/a           | 1 bit                   | 3 bit     | 8 bit     | 1 bit     | 11 bit    | 1 bit      | 4 bit         | 20 bit    | 14 bit     |

| Write Verification              | No        | No            | Yes                     | No        | No        | No        | No        | Yes        | Yes           | Yes       | No         |

| Sensing mode                    | Current   | Current       | n/a                     | Current   | Current   | Voltage   | Current   | Voltage    | Voltage       | Voltage   | Voltage    |

TABLE II: COMPARISON OF THE STATE-OF-THE-ART RRAM DESIGNS

#### III. MULTI-STATE CMOS/MEMRISTOR SYSTEM DESIGN CHALLENGES

Multi-state memristors provide different methodologies for designing future electronics and applications. In the previous section, a few integrated multi-state RRAM systems have shown their promising potential. However, not all technical details about the technologies are publicly available. In this section, we analyse the feasibility and challenges of the multistate memristor technologies and we combine the analysis with the measurement results from our in-house fabricated memristor devices.

#### A. Multi-State Memristor Device-Level Imperfection Factors

Multi-state memristors of different structures have been reviewed in Section II-A, however, memristors still suffer from device and process variations, inaccurate writing process, retention degradation, low yield rate, etc. Combining with the observations and measurement results of our in-house fabricated Pt- $TiO_2$ -Pt memristor, we analyse the challenges of using multi-state memristors in a large CMOS array.

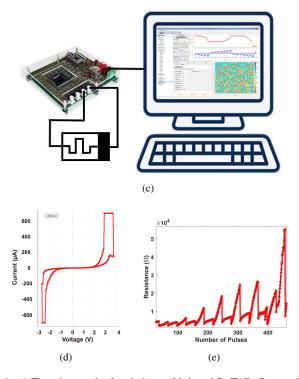

1) Case Study: Measurement Result of an in-house Fabricated Memristor: Fig.4 (a) shows the micrograph of the multi-state  $Pt-TiO_2$ -Pt memristor. To fully characterize the memristor, a complete testing platform is set up as shown in Fig.4 (c). A customised memristor testing platform and a software interface developed in [49] are adopted to write and read the memristor-under-test (MUT) with adjustable voltage pulses of different amplitude, number, and frequency. In Fig.4 (b), two probes are connected to the positive and negative terminals of a single memristor to minimize the factors that can potentially affect its characteristics. Fig.4 (d) shows the IV characteristics of the MUT. A pinched hysteresis loop is formed successfully. By applying different amplitudes of voltage pulses while fixing equal pulse number and pulse width and vice versa, the memristor can be written to different states. An example of the measurement results is shown in Fig.4 (e).

While these measurements were performed and results were obtained, we identified a few difficulties of using the multistate memristors in integrated circuits design. First of all, multi-state switching specification in integrated circuits design is stricter. A properly defined state has to be accurately rewritten by the same pulse train which is often measured within 2-3 $\sigma$ . This needs a "program and verify" approach to guarantee the switching behaviour, but it adds circuit

(a)

Fig. 4: (a) The micrograph of an in-house fabricated  $Pt-TiO_2$ -Pt memristor. (b) Two probes are connected to the terminals of the memristor to minimize the undesired effects. (c) The complete testing setup. (d) The pinched hysteresis loop of the memristor after electroforming. (e) An example of the measured results indicates the  $Pt-TiO_2$ -Pt memristor reaches different resistive states.

complexity. Under the same testing condition and voltage pulses, we observed that the MUT did not always reach the desired state, the successful forming and writing process are not always perfectly repeatable. This leads to some states becoming incompatible and cannot be considered as a stable state. Moreover, memristors are sensitive to the voltage above their threshold, and they can be damaged with high voltage when performing electroforming. Yet, there is not a constant threshold voltage observed that can be applied to all the MUTs. Thus, when designing a crossbar array, this variation has to be considered to avoid broken memristors. Furthermore, based on our measurements, "designed non-volatile" memristors are not non-volatile under all possible configurations: it depends on the forming process, pulse amplitude, and the current resistance state (e.g. larger resistance state is more volatile). This has been discussed in [50], and needs further investigation. In addition, as discussed in Section II-A, retention degradation must be considered in a CMOS/Memristor system. Although there are reported investigations of retention such as in [23], and methods to improve the stability such as the multilevel incremental step pulse with verify algorithm in [51], there is not a commonly adopted method to overcome the volatile behaviour and guarantee data retention.

#### B. Memristor Modelling

Practically exploiting the existence of multiple states of a memristive device for circuit applications requires a compact device model. The model must accurately simulate the nature of the various states observed in real devices. Measurements have shown that not all aforementioned device states are sufficiently reliable for circuit applications. For instance, certain states are meta-stable, and this means a device in such state cannot persist its state over our interested timescales. Stable states on the other hand are more useful for traditional multi-bit circuit and memory applications. From a circuit applications point of view, we are interested in constructing the relationship between the characteristics of the applied stimulus and the subset of device states that can be accessed by the device from some initial states, upon the application of the stimulus. Furthermore, we are interested in the relationship among different states for a given input (i.e. determining whether a given state can be obtained by using alternative sets of programming pulses).

A large class of models in literature such as [52-54] are deterministic models that are constructed as a set, consisting of a differential equation and an algebraic equation. A typical set is shown in (1) and (2).

$$\frac{ds}{dt} = f_u(u,s)f_w(s) \tag{1}$$

$$i(t) = G(s, u) \cdot u(t) \tag{2}$$

Here, s is the internal modelling state variable,  $f_u(u, s)$  is the input sensitivity function, and  $f_w(s)$  is a window function. The memristor conductance can be derived from the state variable governed by (1) and the input u(t) using an appropriate function G(s, u). The current through the device i(t) and voltage across it u(t) are therefore related by (2).

In such a model, a given input stimulus and an initial condition specify a unique deterministic trajectory in the statespace, towards a terminal state. Upon reaching the terminal state, no further change in state occurs despite the application of input. In practice, these terminal states are defined by using suitable window functions. In most models the window functions simply bind the state variable into a valid range used for modelling. In more complex models such as [55], the window is a function of the state variable and the input stimulus and can therefore additionally describe input-dependent stable states to which the memristance saturates. Whilst this is useful in cases where the device can be allowed to reach a steady state, the models are not yet upgraded to account for the transient volatility that describes the state of the device shortly after the stimulus is removed. In practice, all valid values of the memristance are not stable and the memristance typically decays to another more stable value. The basic state evolution differential equation (1) can be extended to model such behaviour by dividing the state space into stable regions and unstable regions. Furthermore, relaxation dynamics can also be introduced to describe volatile behaviour from the unstable states towards the stable states. The modelling approach of [56] introduces a single stable state into the dynamics via the following addition to (1):

$$\frac{ds}{dt} = \left(f_u(u,s) - \frac{s-\epsilon}{\tau}\right)f_w(s) \tag{3}$$

In (3) the only stable state is the value of s for which  $\frac{ds}{dt} = 0$ . Typically  $f_u(u = 0, s) = 0$ , thus the parameter  $\epsilon$ is equal to the value of this single stable state in this model. The models presented in [57] and [58] extend this further by allowing the parameter  $\epsilon$  to be a dynamic variable, governed by its own differential equation, driven by the input stimulus. Therefore, in these models, the stable state of (3) is variable and depends on the history of the input stimulus. Another approach to introduce a series of stable and unstable states in the governing dynamics is to impose a potential-energylike function on the dynamics, whose minima correspond to stable states and maxima correspond to unstable states. For example, [59] introduces a combination of exponential functions and a sinusoid function to model the interfacial energy and periodicity of the transport dynamics respectively. While the model accuracy issue caused by numerical integration of model equations have been addressed [60, 61] and there are ongoing efforts to develop accurate models for specific applications [62-64], the multi-state switching behaviour has not been modelled to the comprehensiveness required for robust circuit design. With more and more characterization data becoming available, it is expected that the memristor model will be extended to cover switching metastability, temperature dependencies, and also the electroforming process [65].

#### C. Circuits Design and Implementation

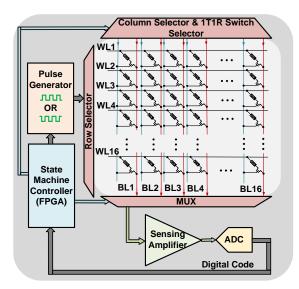

Peripheral circuit design in multi-state memristor arrays is more challenging than in bi-state memristor arrays. Fig. 5 shows a common 1T1R architecture of the memristor crossbar array. When writing a memristor to the desired state, row and column selectors are used to select a device from the array. One terminal of the memristor is connected to a pulse generator and other terminals are connected to the ground or a virtual ground. The pulse generator then sends programming signals to the selected memristor. The read operation faces more difficulties than the write operation. When reading the

Fig. 5: A common architecture of a 1T1R RRAM architecture. The pulse generator generates either writing or reading pulses depending on the instructions from the processor. Either the readout current or voltage is sensed by the peripheral circuitry and converted to digital codes by an ADC. The converted digital codes are sent back to the processor for signal processing.

memristance<sup>4</sup>, low voltage pulses are applied to the selected memristor, while the resulting current is measured. The readout voltage has to be sufficiently low to avoid changing the memristance. The resulting current is interfaced with dedicated readout circuitry and gets digitized. Referring to Table II, both voltage mode and current mode sensing are adopted in stateof-the-art designs. Current mode sensing provides higher speed and larger sensing margin [26]. However, current mode sensing is not preferred in a multi-state memristive system due to its higher noise nature than voltage mode sensing, which leads to inaccurate readout result when the memristor has more states. Besides, current mode sensing also leads to large static power dissipation [26]. On the other hand, in voltage mode sensing, a current-to-voltage (I2V) circuitry is required. It has been demonstrated in Table I that multi-state memristor with higher HRS/LRS ratio leads to a larger current range. For instance, if an amplifier is used to sense the current, the trade-off among large dynamic range, low input offset, low input referred noise, high open-loop gain, and high linearity must be optimized. When the I2V conversion is finished, a high resolution analogto-digital converter (ADC) and a digital quantizer are needed to precisely categorize the I2V output voltage to different digital ranges which correspond to different distinguishable resistance states such as the approach shown in Fig.3 (a) [42]. The more states that a 1T1R cell aims to achieve, the higher resolution of ADC is needed. This leads to another trade-off among multi-state switching, power consumption, chip area, and circuit complexity. In addition, to ensure the memristor is written to a desired state, a write-verify circuit is needed [40, 45-47], which leads to a more sophisticated peripheral circuit design. Thus, there is a wide Pareto surface to optimise over and every bit of resolution requested from the memristive

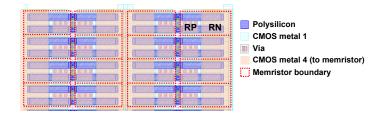

Fig. 6: Layout of a 1T1R array corner with CMOS layers indicating memristor placements. RP links to memristor top electrode and RN connects to its bottom electrode. The insufficient layout data regarding the post-processed memristor hinders the way to perform post-layout analysis for a whole picture.

devices has to be carefully balanced against the costs of the corresponding peripherals.

Hybrid CMOS/Memristor circuits are typically fabricated in two steps: the CMOS parts including the peripheral circuits and the selecting transistors in the 1T1R cells are fabricated using standard CMOS process, and then the memristors are integrated on top of the CMOS through wafer-level post-CMOS processing. Fig. 6 shows an example layout of a 1T1R array chip corner showing the CMOS layers and the boundaries of custom memristor layers. There has been progressed in process design kit development to allow hybrid CMOS/Memristor circuit design using design flows compatible to standard CMOS process [66]. When designing circuit especially for interfacing memristors at a large scale, both layout-dependent and processing-dependent parasitic effects need to be modelled. This will become possible as more data becomes available from post-processed devices on top of CMOS, and a dedicated characterization platform has been constructed to facilitate this development [67].

#### IV. MULTI-STATE MEMRISTOR APPLICATIONS

A multi-state memristor can be understood as a device that manifests variable resistance values in response to certain input stimulus patterns. This feature means it can be used as a multibit memory cell or a resistive trimmer, and also be used to encode or process temporal dynamic signals such as physiological signals. In this section we will discuss about three potential applications corresponding to these characteristics respectively.

#### A. Next-generation Memory and Computing

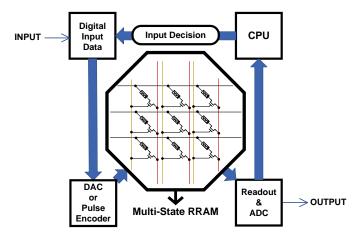

The potential to store multiple states in a single memristor cell makes it promising for high-density memory implementation, potentially paving the way for the development of digital and analog memory which will impact the technology landscape of future computing systems. As shown in Fig. 7, a multi-state memristor array is adopted in a conventional von-Neumann computing architecture as an example. The CPU is responsible for constantly adjusting the input data until multibit information is stored at a specific memory cell. The high density and low power advantages of the multi-state memristor memory make it a potential candidate to compete with DRAM in the future [1]. However, adopting multi-state RRAM in the von-Neumann architecture leads to the long-distance data

Fig. 7: Multi-state RRAM applied von-Neumann computing architecture. For a typical writing process, the input data is firstly applied to the RRAM as read voltage without changing the memristor's state, the readout data will then be transmitted to the CPU for comparison with an expected value, and a proper write voltage is generated from the CPU to change the state (weight). The closed-loop process continues to work until the information is stored to the multi-state memristor cells.

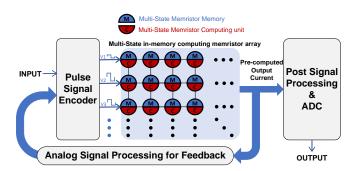

Fig. 8: Analog-based RRAM computing architecture. In a machine learning training process, the input signals are encoded by a pulse signal encoder and then applied to the memristor array. Each memristor cell works as a multi-state memory but also as a computing unit, the computed MAC result is carried by the readout current of every column to realise in-memory processing. The result is transmitted to an analog signal processing circuit and then fed back to the pulse signal encoder to update the write voltage. The final result is post-processed and digitized to the output.

transmission between the CPU and the RRAM, which costs considerable power, area, and more importantly, leads to low processing efficiency [1]. As a multi-bit memory cell, the memristor facilities computing-in-memory (CIM) which addresses this inefficiency, and because it stores the weight and performs Multiple-and-Accumulate (MAC) operation in the analog domain, faster and more power-efficient neuromorphic and artificial neural network hardware were built thanks to this advantage [68–77]. Compared with an SRAM-based CIM, the analog-based RRAM CIM eliminates excess full adders and logic gates, substantially reducing chip area and power consumption. An example of such analog-based in-memory computing array is shown in Fig. 8. Notably, a fully integrated CMOS/Memristor CIM chip which incorporates 3 million analog RRAM cells was presented recently [78]. This chip demonstrates directly the advantages of multi-state memristors for building large-scale artificial intelligence hardware with high energy efficiency, application versatility, and softwarecomparable accuracy.

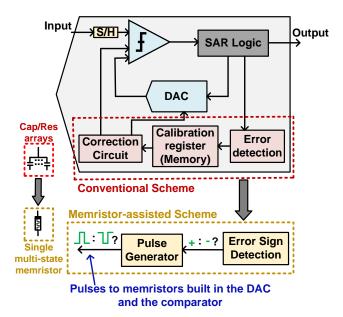

Fig. 9: Conventional SAR ADC calibration scheme assisted by capacitor/resistor arrays and a substitute scheme assisted by multi-state memristors [79]. The MSB of the R-2R DAC is replaced by a memristor and this memristor is considered as a trimming element. The error sign detection logic is similar to the one proposed in [80], and the pulse generator is used to write the memristor to a certain state based on the feedback error sign, the updated memristance leads to a correction on the DAC output level, and thus improve the accuracy of the A/D conversion.

#### B. Multi-state Memristor for Analog Trimming & Tuning

As early as 1976, laser trimming was used to improve the linearity of an R-2R digital-to-analog converter (DAC) that was constructed by thin-film resistors [81]. The resistance can be adjusted by means of irradiating thin-film resistors with the laser, thus the DAC output level can be trimmed. Compared to the conventional scheme, this laser-trimming approach reduced the complexity of the peripheral calibration circuit but the laser is difficult to be applied to today's integrated circuits. Alternatively, memristors can be used for calibration in the similar way as laser-irradiated thin-film resistors because they both offer variable resistance in principle. In recent years, some studies show that memristors tunability can be employed to trim circuit imperfections (i.e mismatches, offsets) in amplifiers [82] and ADCs [79].

Taking the successive-approximation ADC (SAR ADC) as an example, as shown in Fig.9, in a conventional SAR ADC calibration scheme, the calibration information needs to be stored in calibration registers in advance of trimming the DAC mismatches and comparator offsets. When the resolution of the SAR ADC is increased, more calibration bits are required to maintain good linearity, thus demanding more registers and calibration components (i.e capacitor and resistor arrays) to store the calibration information and correct the errors, which induces larger latency, power consumption, and area. Thanks to the in-memory processing nature of memristor, a smaller, faster and more power-efficient design can be realised by replacing conventional calibration with a memristor-assisted calibration scheme. In Fig.9, calibration registers and correction circuits are no longer required as the memristor itself

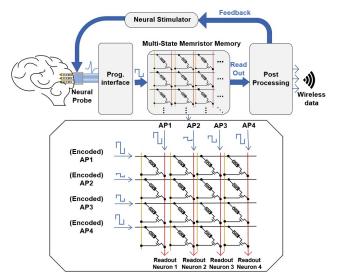

Fig. 10: An envisaged memristor-centric neural interface system. A multi-state memristor array can be used to construct a matching template [83], performing spike sorting algorithms to process the raw data from the high-density neural probe at the front end. After spike sorting, the output data rate is significantly reduced and can thus be transmitted wirelessly to the external hardware. Closed-loop neuromodulation for brain disorder (eg. epilepsy) treatment can be achieved using multi-state memristors to analyse the neural states in real time, providing feedback to the brain through neural stimulation.

can store the calibration information. The calibration can be conducted by applying programming pulses to increase or decrease the memristor resistance according to the error polarity so that the mismatch errors in the DAC and the comparator are minimized. In addition, the multi-state switching property also provides a wider calibration range for the ADC mismatches, which can potentially realise more precise trimming than the conventional approach.

#### C. Multi-State Memristor for Neural Interfaces

The emerging techniques for using multi-state memristors to perform bio-signal processing have shown promising results in energy efficiency improvement, which is vital for embedding intelligence in future biomedical implants [83-85]. Encoding the neuronal spikes into multi-state memristors results in real-time sub- $\mu$ V/ch spike detection [84]. In [85], memristors with conductance states programmed to multiple values (1 $\sim$ 20 $\mu$ S) were used to construct coefficients in a lowpower finite impulse response (FIR) filter bank, which can process neural local field potentials with two orders of magnitude better energy efficiency than conventional CMOS filters. Significant reductions in circuit area, power consumption, and processing latency in neural spike sorting were achieved using the multi-state memristors to construct template coefficients (4-bit resolution) for template-matching-based classification algorithms [83]. Notably, the retention characteristics reported in [83] ensures a reliable storage of the neuron templates for over 2.7 hours. This satisfies the requirement in typical neural electrophysiological experiments, while periodic refresh operation could be applied for longer experiments or in clinical application scenarios. A multi-state memristor array will prospectively be the core part of a closed-loop

neural interface system shown in Fig.10. The state-of-theart neural probe technologies today support implantation of over 10,000 microelectrodes acquiring a large volume of data from the brain [86, 87]. Multi-state memristor arrays provide a promising solution to process these data in situ, extracting the key information in real time to facilitate closed-loop neuromodulation and wireless data connection to the external hardware.

#### V. DISCUSSION

Permeating throughout this work are a number of key observations and trends. We begin by noting the gradual move towards analog memristive devices. Central to this has been efforts to increase the resistive state resolution, and yet now we seem to have reached the point where the bottleneck is no longer the device, but our ability to read it precisely. As such, in the future the new "spec battleground" is likely to revolve around obtaining reliability and predictability of behaviour, which disaggregates into high retention, predictable resistive state change given input parameters, good cycling endurance, etc. The ultimate limits of what memristors can achieve in terms of these specs are unclear at the moment. What is certain, however, is that large-scale characterisation studies that are increasingly comprehensive (i.e. attack multiple operating parameters and multiple behavioural tests) will become increasingly important.

Next, we notice that as memristive technologies mature, their interaction with peripherals becomes increasingly important. This manifests itself into two major directions: First, an increasingly pressing need for comprehensive memristor models is likely to drive the need for large-scale characterisation. This includes low-level (electrochemistry-level) modelling, which we expect will be essential for providing reliable models of what is a time-varying component; the very configuration of atoms within a memristor changes during operation, which excluding ageing and other undesirable effects is not the case for any other component. The limits of predictability (and therefore modelability) of memristive devices of various underlying electrochemical mechanisms are still unclear to us and a very big question to answer. Secondly, we already observe a very pressing imperative to engineer devices that do not require electroforming and that can exhibit switching with voltage/current combinations that are sufficiently low to admit provision by typical peripheral circuits in modern CMOS. Specifically, the series resistance of CMOS switches and the <2V head-rooms seen starting from CMOS techs going as far back as 180nm realistically demand devices that can switch in sub-V and sub- $10\mu$ A conditions (and yet still feature a "safe zone" of biases that allow read-out without disturbing the underlying resistive state). Despite the very beneficial, exponential trade-off noted between write voltage and duration [88, 89], it is unclear how much voltage headrooms can be squeezed before it becomes exceedingly difficult to support both non-invasive read operations and effective write operations.

Finally, we note the large variety of applications in which memristors have found very promising paths of exploitation. A potentially interesting observation is that in most applications (excluding standard memory storage), memristors seem to have found a very solid niche as parameter-setting elements. This seems to be highly beneficial even for systems where most of the signal processing around them is performed in the digital (or even time) domain. The idea of "using analog to trim digital", as in the cases where analog weights trim the decision surface of an artificial neural network or analog parameters determine the "hit" window for a template-matching function, seems to be very fundamental and powerful. At its limit it may generate a powerful "technological resonance" with standard digital techniques, by enabling futuristic systems where extremely down-scaled digital circuits are held within their operating parameters via aid from analog trimming (imagine a nanoscale resistor near every 2nm transistor, trimmed to ensure an entire array of nano-transistors has exactly the same channel on resistance). Once again, it is unclear exactly how far this concept may go.

#### VI. CONCLUSION

Memristor related research has provided a practical solution in the era beyond CMOS. Nevertheless, precisely executing write and read, select and control, and verifying the nonvolatility of a multi-state memristor are still a leading-edge research direction in both material science and electrical engineering. In this paper, we introduced and reviewed the state-of-the-art multi-state memristive systems. More importantly, combining the most advanced research results with our previous studies and observations, we analysed the challenges of designing a multi-state CMOS/Memristor system in the aspect of device, memristor modelling, peripheral circuits design, and layout and post-processing. While memristor is an emerging device and as of today there are still areas which require further research and improvement, we have also highlighted a number of promising applications where the multi-state memristor technology could be game changers as the technology advances. We believe the promising results obtained recently in these applications (e.g. the AI accelerator [78] and neural signal processing [83] chips reported very recently) will drive the research community to improve the technology further. Overall, the picture for the field of multistate memristive technologies seems to consist of two major elements: a) the past and present, where a host of applications and intriguing ideas have been demonstrated and are maturing on the back of what the technology can already deliver or is judged to be very likely to deliver in the not too distant future and b) the future, where the big questions to be uncovered revolve around exactly how much more potential memristors have; this in terms of everything from down-scaling and multistate precision to retention, richness of internal mechanics and even manufacturing costs, material choice (e.g. what can we achieve using only Silicon and a few relatively abundant dopants?). Thus, in our view, the field promises an exciting future spanning new technologies and science from fundamental electrochemistry and fabrication and all the way up to largescale memristor-enabled systems.

#### REFERENCES

- M. A. Zidan, J. P. Strachan, and W. D. Lu, "The future of electronics based on memristive systems," *Nature electronics*, vol. 1, no. 1, pp. 22–29, 2018.

- [2] L. Chua, "Memristor-the missing circuit element," *IEEE Transactions on Circuit Theory*, vol. 18, no. 5, pp. 507–519, 1971.

- [3] D. Oxley, "Electroforming, switching and memory effects in oxide thin films," *Electrocomponent Science and Technology*, vol. 3, no. 4, pp. 217–224, 1977.

- [4] H. Pagnia and N. Sotnik, "Bistable switching in electroformed metal-insulator-metal devices," *physica status solidi* (a), vol. 108, no. 1, pp. 11–65, 1988.

- [5] A. Asamitsu, Y. Tomioka, H. Kuwahara, and Y. Tokura, "Current switching of resistive states in magnetoresistive manganites," *Nature*, vol. 388, no. 6637, pp. 50–52, 1997.

- [6] F. Chudnovskii, L. Odynets, A. Pergament, and G. Stefanovich, "Electroforming and switching in oxides of transition metals: The role of metal–insulator transition in the switching mechanism," *Journal of Solid State Chemistry*, vol. 122, no. 1, pp. 95–99, 1996.

- [7] A. Beck, J. Bednorz, C. Gerber, C. Rossel, and D. Widmer, "Reproducible switching effect in thin oxide films for memory applications," *Applied Physics Letters*, vol. 77, no. 1, pp. 139–141, 2000.

- [8] B. Choi, D. Jeong, S. Kim, C. Rohde, S. Choi, J. Oh, H. Kim, C. Hwang, K. Szot, R. Waser *et al.*, "Resistive switching mechanism of tio 2 thin films grown by atomic-layer deposition," *Journal of applied physics*, vol. 98, no. 3, p. 033715, 2005.

- [9] D. Kim, S. Seo, S. Ahn, D.-S. Suh, M. Lee, B.-H. Park, I. Yoo, I. Baek, H.-J. Kim, E. Yim *et al.*, "Electrical observations of filamentary conductions for the resistive memory switching in nio films," *Applied physics letters*, vol. 88, no. 20, p. 202102, 2006.

- [10] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," *Nature Materials*, vol. 6, no. 11, pp. 833–840, 2007.

- [11] K. M. Kim, B. J. Choi, Y. C. Shin, S. Choi, and C. S. Hwang, "Anode-interface localized filamentary mechanism in resistive switching of ti o 2 thin films," *Applied physics letters*, vol. 91, no. 1, p. 012907, 2007.

- [12] M. N. Kozicki, C. Gopalan, M. Balakrishnan, and M. Mitkova, "A low-power nonvolatile switching element based on copper-tungsten oxide solid electrolyte," *IEEE Transactions on Nanotechnology*, vol. 5, no. 5, pp. 535– 544, 2006.

- [13] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *nature*, vol. 453, no. 7191, pp. 80–83, 2008.

- [14] S. Pi, C. Li, H. Jiang, W. Xia, H. Xin, J. J. Yang, and Q. Xia, "Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension," *Nature nanotechnology*, vol. 14, no. 1, pp. 35–39, 2019.

- [15] L. V. Gambuzza, M. Frasca, L. Fortuna, V. Ntinas, I. Vourkas, and G. C. Sirakoulis, "Memristor crossbar for adaptive synchronization," *IEEE Transactions on Circuits*

and Systems I: Regular Papers, vol. 64, no. 8, pp. 2124–2133, 2017.

- [16] M. Weiher, M. Herzig, R. Tetzlaff, A. Ascoli, T. Mikolajick, and S. Slesazeck, "Pattern formation with locally active s-type nbo x memristors," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 7, pp. 2627–2638, 2019.

- [17] J. Gomez, I. Vourkas, A. Abusleme, G. C. Sirakoulis, and A. Rubio, "Voltage divider for self-limited analog state programing of memristors," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 67, no. 4, pp. 620–624, 2019.

- [18] I.-A. Fyrigos, V. Ntinas, N. Vasileiadis, G. C. Sirakoulis, P. Dimitrakis, Y. Zhang, and I. G. Karafyllidis, "Memristor crossbar arrays performing quantum algorithms," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2021.

- [19] M. Weiher, M. Herzig, R. Tetzlaff, A. Ascoli, T. Mikolajick, and S. Slesazeck, "Improved vertex coloring with nbo memristor-based oscillatory networks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 5, pp. 2082–2095, 2021.

- [20] N. Vasileiadis, P. Dimitrakis, V. Ntinas, and G. C. Sirakoulis, "True random number generator based on multistate silicon nitride memristor entropy sources combination," in 2021 International Conference on Electronics, Information, and Communication (ICEIC). IEEE, 2021, pp. 1–4.

- [21] A. Ascoli, A. S. Demirkol, R. Tetzlaff, and L. Chua, "Edge of chaos theory resolves smale paradox," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2022.

- [22] J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, "'memristive' switches enable 'stateful' logic operations via material implication," *Nature*, vol. 464, no. 7290, pp. 873–876, 2010.

- [23] M. Zhao, H. Wu, B. Gao, Q. Zhang, W. Wu, S. Wang, Y. Xi, D. Wu, N. Deng, S. Yu *et al.*, "Investigation of statistical retention of filamentary analog rram for neuromophic computing," in 2017 IEEE International Electron Devices Meeting (IEDM). IEEE, 2017, pp. 39–4.

- [24] P. Yao, H. Wu, B. Gao, J. Tang, Q. Zhang, W. Zhang, J. J. Yang, and H. Qian, "Fully hardware-implemented memristor convolutional neural network," *Nature*, vol. 577, no. 7792, pp. 641–646, 2020.

- [25] A. Malik, C. Papavassiliou, and S. Stathopoulos, "A stochastic compact model describing memristor plasticity and volatility," in 2021 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS). IEEE, 2021, pp. 1–4.

- [26] D. Kim, C. Yu, S. Xie, Y. Chen, J.-Y. Kim, B. Kim, J. Kulkarni, and T. T.-H. Kim, "An overview of processing-in-memory circuits for artificial intelligence and machine learning," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, 2022.

- [27] H. Kim, M. P. Sah, C. Yang, and L. O. Chua, "Memristorbased multilevel memory," in 2010 12th International

Workshop on Cellular Nanoscale Networks and their Applications (CNNA 2010). IEEE, 2010, pp. 1–6.

- [28] S. Stathopoulos, A. Khiat, M. Trapatseli, S. Cortese, A. Serb, I. Valov, and T. Prodromakis, "Multibit memory operation of metal-oxide bi-layer memristors," *Scientific reports*, vol. 7, no. 1, pp. 1–7, 2017.

- [29] C. Wang, L. Xie, X. Jiang, R. Ge, and C. Papavassiliou, "Design of a multi-state memristive memory," in 2021 28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), 2021, pp. 1–6.

- [30] H.-S. P. Wong, H.-Y. Lee, S. Yu, Y.-S. Chen, Y. Wu, P.-S. Chen, B. Lee, F. T. Chen, and M.-J. Tsai, "Metal– oxide rram," *Proceedings of the IEEE*, vol. 100, no. 6, pp. 1951–1970, 2012.

- [31] M.-J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, Y.-B. Kim, C.-J. Kim, D. H. Seo, S. Seo *et al.*, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric ta2o5- x/tao2- x bilayer structures," *Nature materials*, vol. 10, no. 8, pp. 625– 630, 2011.

- [32] A. C. Torrezan, J. P. Strachan, G. Medeiros-Ribeiro, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor," *Nanotechnology*, vol. 22, no. 48, p. 485203, 2011.

- [33] B. Murdoch, D. McCulloch, R. Ganesan, D. McKenzie, M. Bilek, and J. Partridge, "Memristor and selector devices fabricated from hfo2- xnx," *Applied Physics Letters*, vol. 108, no. 14, p. 143504, 2016.

- [34] J. J. Yang, M. D. Pickett, X. Li, D. A. Ohlberg, D. R. Stewart, and R. S. Williams, "Memristive switching mechanism for metal/oxide/metal nanodevices," *Nature nanotechnology*, vol. 3, no. 7, pp. 429–433, 2008.

- [35] H. Cheng, E. Hsieh, Z. Huang, C. Chuang, C. Chen, F. Li, Y. Lo, C. Liu, and S. S. Chung, "A novel rewritable onetime-programming otp (rw-otp) realized by dielectricfuse rram devices featuring ultra-high reliable retention and good endurance for embedded applications," in 2018 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA). IEEE, 2018, pp. 1–2.

- [36] W.-C. Chien, M.-H. Lee, F.-M. Lee, Y.-Y. Lin, H.-L. Lung, K.-Y. Hsieh, and C.-Y. Lu, "Multi-level 40nm wo x resistive memory with excellent reliability," in 2011 International electron devices meeting. IEEE, 2011, pp. 31–5.

- [37] A. Prakash, J. Park, J. Song, J. Woo, E.-J. Cha, and H. Hwang, "Demonstration of low power 3-bit multilevel cell characteristics in a tao x-based rram by stack engineering," *IEEE Electron Device Letters*, vol. 36, no. 1, pp. 32–34, 2014.

- [38] G. H. Kim, H. Ju, M. K. Yang, D. K. Lee, J. W. Choi, J. H. Jang, S. G. Lee, I. S. Cha, B. K. Park, J. H. Han *et al.*, "Four-bits-per-cell operation in an hfo2-based resistive switching device," *Small*, vol. 13, no. 40, p. 1701781, 2017.

- [39] W.-H. Chen, K.-X. Li, W.-Y. Lin, K.-H. Hsu, P.-Y. Li, C.-H. Yang, C.-X. Xue, E.-Y. Yang, Y.-K. Chen, Y.-S. Chang *et al.*, "A 65nm 1mb nonvolatile computing-in-memory reram macro with sub-16ns multiply-and-accumulate for

binary dnn ai edge processors," in 2018 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2018, pp. 494–496.

- [40] T. F. Wu, B. Q. Le, R. Radway, A. Bartolo, W. Hwang, S. Jeong, H. Li, P. Tandon, E. Vianello, P. Vivet *et al.*, "A 43pj/cycle non-volatile microcontroller with 4.7 μs shutdown/wake-up integrating 2.3-bit/cell resistive ram and resilience techniques," in 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2019, pp. 226–228.

- [41] C.-X. Xue, W.-H. Chen, J.-S. Liu, J.-F. Li, W.-Y. Lin, W.-E. Lin, J.-H. Wang, W.-C. Wei, T.-W. Chang, T.-C. Chang *et al.*, "A 1mb multibit reram computing-inmemory macro with 14.6 ns parallel mac computing time for cnn based ai edge processors," in 2019 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2019, pp. 388–390.

- [42] Q. Liu, B. Gao, P. Yao, D. Wu, J. Chen, Y. Pang, W. Zhang, Y. Liao, C.-X. Xue, W.-H. Chen *et al.*, "A fully integrated analog reram based 78.4 tops/w compute-inmemory chip with fully parallel mac computing," in 2020 *ieee international solid-state circuits conference-(isscc)*. IEEE, 2020, pp. 500–502.

- [43] W. Wan, R. Kubendran, S. B. Eryilmaz, W. Zhang, Y. Liao, D. Wu, S. Deiss, B. Gao, P. Raina, S. Joshi et al., "A 74 tmacs/w cmos-rram neurosynaptic core with dynamically reconfigurable dataflow and in-situ transposable weights for probabilistic graphical models," in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 498–500.

- [44] C.-X. Xue, T.-Y. Huang, J.-S. Liu, T.-W. Chang, H.-Y. Kao, J.-H. Wang, T.-W. Liu, S.-Y. Wei, S.-P. Huang, W.-C. Wei *et al.*, "A 22nm 2mb reram compute-in-memory macro with 121-28tops/w for multibit mac computing for tiny ai edge devices," in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 244–246.

- [45] W. He, S. Yin, Y. Kim, X. Sun, J.-J. Kim, S. Yu, and J.-s. Seo, "2-bit-per-cell rram-based in-memory computing for area-/energy-efficient deep learning," *IEEE Solid-State Circuits Letters*, vol. 3, pp. 194–197, 2020.

- [46] J.-H. Yoon, M. Chang, W.-S. Khwa, Y.-D. Chih, M.-F. Chang, and A. Raychowdhury, "A 40nm 100kb 118.44 tops/w ternary-weight computein-memory rram macro with voltage-sensing read and write verification for reliable multi-bit rram operation," in 2021 IEEE Custom Integrated Circuits Conference (CICC). IEEE, 2021, pp. 1–2.

- [47] J.-H. Yoon, M. Chang, W.-S. Khwa, Y.-D. Chih, M.-F. Chang, and A.Raychowdhury, "29.1 a 40nm 64kb 56.67tops/w read-disturb-tolerant compute-inmemory/digital rram macro with active-feedback-based read and in-situ write verification," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64, 2021, pp. 404–406.

- [48] C.-X. Xue, J.-M. Hung, H.-Y. Kao, Y.-H. Huang, S.-P. Huang, F.-C. Chang, P. Chen, T.-W. Liu, C.-J. Jhang, C.-I. Su *et al.*, "A 22nm 4mb 8b-precision reram computing-

in-memory macro with 11.91 to 195.7 tops/w for tiny ai edge devices," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64. IEEE, 2021, pp. 245–247.

- [49] R. Berdan, A. Serb, A. Khiat, A. Regoutz, C. Papavassiliou, and T. Prodromakis, "A μ-controller-based system for interfacing selectorless rram crossbar arrays," *IEEE Transactions on Electron Devices*, vol. 62, no. 7, pp. 2190–2196, 2015.

- [50] C. Giotis, A. Serb, S. Stathopoulos, L. Michalas, A. Khiat, and T. Prodromakis, "Bidirectional volatile signatures of metal–oxide memristors—part i: Characterization," *IEEE Transactions on Electron Devices*, vol. 67, no. 11, pp. 5158–5165, 2020.

- [51] E. Perez, C. Zambelli, M. K. Mahadevaiah, P. Olivo, and C. Wenger, "Toward reliable multi-level operation in rram arrays: Improving post-algorithm stability and assessing endurance/data retention," *IEEE Journal of the Electron Devices Society*, vol. 7, pp. 740–747, 2019.

- [52] S. Kvatinsky, E. G. Friedman, A. Kolodny, and U. C. Weiser, "TEAM: ThrEshold Adaptive Memristor Model," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 1, pp. 211–221, Jan. 2013, conference Name: IEEE Transactions on Circuits and Systems I: Regular Papers.

- [53] S. Kvatinsky, M. Ramadan, E. G. Friedman, and A. Kolodny, "VTEAM: A General Model for Voltage-Controlled Memristors," *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS*, vol. 62, no. 8, p. 5, 2015.

- [54] T. Prodromakis, B. P. Peh, C. Papavassiliou, and C. Toumazou, "A versatile memristor model with nonlinear dopant kinetics," *IEEE transactions on electron devices*, vol. 58, no. 9, pp. 3099–3105, 2011.

- [55] I. Messaris, A. Serb, S. Stathopoulos, A. Khiat, S. Nikolaidis, and T. Prodromakis, "A data-driven verilog-a reram model," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 37, no. 12, pp. 3151–3162, 2018.

- [56] T. Chang, S.-H. Jo, K.-H. Kim, P. Sheridan, S. Gaba, and W. Lu, "Synaptic behaviors and modeling of a metal oxide memristive device," *Applied Physics A*, vol. 102, no. 4, pp. 857–863, Mar. 2011.

- [57] R. Berdan, E. Vasilaki, A. Khiat, G. Indiveri, A. Serb, and T. Prodromakis, "Emulating short-term synaptic dynamics with memristive devices," *Scientific Reports*, vol. 6, no. 1, p. 18639, Jan. 2016, number: 1 Publisher: Nature Publishing Group. [Online]. Available: https://www.nature.com/articles/srep18639

- [58] L. Chen, C. Li, T. Huang, Y. Chen, S. Wen, and J. Qi, "A synapse memristor model with forgetting effect," *Physics Letters A*, vol. 377, no. 45, pp. 3260–3265, Dec. 2013. [Online]. Available: http://www.sciencedirect.com/ science/article/pii/S0375960113009778

- [59] Z. Wang, S. Joshi, S. E. Savel'ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, J. P. Strachan, Z. Li, Q. Wu, M. Barnell, G.-L. Li, H. L. Xin, R. S. Williams, Q. Xia, and J. J. Yang, "Memristors with diffusive dynamics as synaptic emulators for

neuromorphic computing," *Nature Materials*, vol. 16, no. 1, pp. 101–108, Jan. 2017. [Online]. Available: http://www.nature.com/articles/nmat4756

- [60] A. Ascoli, F. Corinto, V. Senger, and R. Tetzlaff, "Memristor model comparison," *IEEE Circuits and Systems Magazine*, vol. 13, no. 2, pp. 89–105, 2013.

- [61] A. Ascoli, R. Tetzlaff, Z. Biolek, Z. Kolka, V. Biolkova, and D. Biolek, "The art of finding accurate memristor model solutions," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 5, no. 2, pp. 133–142, 2015.

- [62] S. M. Kang, D. Choi, J. K. Eshraghian, P. Zhou, J. Kim, B.-S. Kong, X. Zhu, A. S. Demirkol, A. Ascoli, R. Tetzlaff *et al.*, "How to build a memristive integrate-andfire model for spiking neuronal signal generation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 12, pp. 4837–4850, 2021.

- [63] A. S. Demirkol, A. Ascoli, I. Messaris, M. M. Al Chawa, R. Tetzlaff, and L. O. Chua, "A compact and continuous reformulation of the strachan tao memristor model with improved numerical stability," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2021.

- [64] V. Ntinas, A. Ascoli, I. Messaris, Y. Wang, V. Rana, S. Menzel, and R. Tetzlaff, "Toward simplified physicsbased memristor modeling of valence change mechanism devices," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 69, no. 5, pp. 2473–2477, 2022.

- [65] S. Stathopoulos, L. Michalas, A. Khiat, A. Serb, and T. Prodromakis, "An electrical characterisation methodology for benchmarking memristive device technologies," *Scientific Reports*, vol. 9, no. 19412, 2019.

- [66] S. Maheshwari, S. Stathopoulos, J. Wang, A. Serb, Y. Pan, A. Mifsud, L. B. Leene, J. Shen, C. Papavassiliou, T. G. Constandinou, and T. Prodromakis, "Design flow for hybrid cmos/memristor systems—part ii: Circuit schematics and layout," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 12, pp. 4876– 4888, 2021.

- [67] A. Mifsud, J. Shen, P. Feng, L. Xie, C. Wang, Y. Pan, S. Maheshwari, S. Agwa, S. Staphopoulos, S. Wang, A. Serb, C. Papavassiliou, T. Prodromakis, and T. G. Constandinou, "A cmos-based characterisation platform for emerging rram technologies," in 2022 IEEE International Symposium on Circuits and Systems (IS-CAS), 2022.

- [68] S. B. Eryilmaz, D. Kuzum, S. Yu, and H.-S. P. Wong, "Device and system level design considerations for analog-non-volatile-memory based neuromorphic architectures," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, pp. 4.1.1–4.1.4.

- [69] D. Lee, J. Park, K. Moon, J. Jang, S. Park, M. Chu, J. Kim, J. Noh, M. Jeon, B. H. Lee, B. Lee, B.-G. Lee, and H. Hwang, "Oxide based nanoscale analog synapse device for neural signal recognition system," in 2015 *IEEE International Electron Devices Meeting (IEDM)*, 2015, pp. 4.7.1–4.7.4.

- [70] P. Yao, H. Wu, B. Gao, S. B. Eryilmaz, X. Huang, W. Zhang, Q. Zhang, N. Deng, L. Shi, H.-S. P. Wong, and

H. Qian, "Face classification using electronic synapses," *Nature Communications*, vol. 8, no. 1, p. 15199, 2017.

- [71] M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, "Training and operation of an integrated neuromorphic network based on metal-oxide memristors," *Nature*, vol. 521, no. 7550, pp. 61–64, 2014.

- [72] S. Yu, B. Gao, Z. Fang, H. Yu, J. Kang, and H.-S. P. Wong, "A low energy oxide-based electronic synaptic device for neuromorphic visual systems with tolerance to device variation," *Advanced Materials*, vol. 25, no. 12, pp. 1774–1779, 2013. [Online]. Available: https://onlinelibrary.wiley.com/doi/ abs/10.1002/adma.201203680

- [73] I. Hubara, M. Courbariaux, D. Soudry, R. El-Yaniv, and Y. Bengio, "Quantized neural networks: Training neural networks with low precision weights and activations," 2016. [Online]. Available: https://arxiv.org/abs/1609. 07061

- [74] K. Ando, K. Ueyoshi, K. Orimo, H. Yonekawa, S. Sato, H. Nakahara, S. Takamaeda-Yamazaki, M. Ikebe, T. Asai, T. Kuroda, and M. Motomura, "Brein memory: A singlechip binary/ternary reconfigurable in-memory deep neural network accelerator achieving 1.4 tops at 0.6 w," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 4, pp. 983– 994, 2018.

- [75] H. Valavi, P. J. Ramadge, E. Nestler, and N. Verma, "A 64-tile 2.4-mb in-memory-computing cnn accelerator employing charge-domain compute," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 6, pp. 1789–1799, 2019.

- [76] S. K. Gonugondla, M. Kang, and N. Shanbhag, "A 42pj/decision 3.12tops/w robust in-memory machine learning classifier with on-chip training," in 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 490–492.

- [77] J.-M. Hung, C.-J. Jhang, P.-C. Wu, Y.-C. Chiu, and M.-F. Chang, "Challenges and trends of nonvolatile inmemory-computation circuits for ai edge devices," *IEEE Open Journal of the Solid-State Circuits Society*, vol. 1, pp. 171–183, 2021.

- [78] W. Wan, R. Kubendran, C. Schaefer, S. B. Eryilmaz, W. Zhang, D. Wu, S. Deiss, P. Raina, H. Qian, B. Gao, S. Joshi, H. Wu, H. S. P. Wong, and G. Cauwenberghs, "A compute-in-memory chip based on resistive random-access memory," *Nature*, vol. 608, no. 7923, pp. 504–512, 2022. [Online]. Available: https://doi.org/10.1038/s41586-022-04992-8

- [79] Z. Si, C. Wang, A. Malik, S. Wang, T. Prodromakis, and C. Papavassiliou, "Memristor-assisted background calibration for analog-to-digital converter," in 2022 20th IEEE International New Circuits and Systems Conference (NEWCAS), 2022.

- [80] M. Ding, P. Harpe, Y.-H. Liu, B. Busze, K. Philips, and H. de Groot, "A 46 μW 13 b 6.4 ms/s sar adc with background mismatch and offset calibration," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 2, pp. 423– 432, 2017.

- [81] P. Holloway and M. Norton, "A high yield, second

generation 10-bit monolithic dac," in 1976 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, vol. XIX, 1976, pp. 106–107.

- [82] J. Wang, A. Serb, C. Papavassiliou, S. Maheshwari, and T. Prodromakis, "Analysing and measuring the performance of memristive integrating amplifiers," *International Journal of Circuit Theory and Applications*, vol. 49, no. 11, pp. 3507–3525, 2021.

- [83] Y. Shi, A. Ananthakrishnan, S. Oh, X. Liu, G. Hota, G. Cauwenberghs, and D. Kuzum, "High throughput neuromorphic brain interface with cuo x resistive crossbars for real-time spike sorting," in 2021 IEEE International Electron Devices Meeting (IEDM). IEEE, 2021, pp. 16–5.

- [84] I. Gupta, A. Serb, A. Khiat, R. Zeitler, S. Vassanelli, and T. Prodromakis, "Real-time encoding and compression of neuronal spikes by metal-oxide memristors," *Nature communications*, vol. 7, no. 1, pp. 1–9, 2016.

- [85] Z. Liu, J. Tang, B. Gao, P. Yao, X. Li, D. Liu, Y. Zhou, H. Qian, B. Hong, and H. Wu, "Neural signal analysis with memristor arrays towards high-efficiency brainmachine interfaces," *Nature communications*, vol. 11, no. 1, pp. 1–9, 2020.

- [86] S. Wang, S. K. Garakoui, H. Chun, D. G. Salinas, W. Sijbers, J. Putzeys, E. Martens, J. Craninckx, N. Van Helleputte, and C. M. Lopez, "A compact quadshank cmos neural probe with 5,120 addressable recording sites and 384 fully differential parallel channels," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 13, no. 6, pp. 1625–1634, 2019.

- [87] N. A. Steinmetz, C. Aydin, A. Lebedeva, M. Okun, M. Pachitariu, M. Bauza, M. Beau, J. Bhagat, C. Bhm, M. Broux, S. Chen, J. Colonell, R. J. Gardner, B. Karsh, F. Kloosterman, D. Kostadinov, C. Mora-Lopez, J. Oallaghan, J. Park, J. Putzeys, B. Sauerbrei, R. J. J. van Daal, A. Z. Vollan, S. Wang, M. Welkenhuysen, Z. Ye, J. T. Dudman, B. Dutta, A. W. Hantman, K. D. Harris, A. K. Lee, E. I. Moser, J. Oeefe, A. Renart, K. Svoboda, M. Husser, S. Haesler, M. Carandini, and T. D. Harris, "Neuropixels 2.0: A miniaturized high-density probe for stable, long-term brain recordings," *Science*, vol. 372, no. 6539, p. eabf4588, 2021. [Online]. Available: https: //www.science.org/doi/abs/10.1126/science.abf4588

- [88] J. Xing, A. Serb, A. Khiat, R. Berdan, H. Xu, and T. Prodromakis, "An fpga-based instrument for en-masse rram characterization with ns pulsing resolution," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 6, pp. 818–826, 2016.

- [89] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories – nanoionic mechanisms, prospects, and challenges," *Advanced Materials*, vol. 21, no. 25-26, pp. 2632–2663, 2009. [Online]. Available: https://onlinelibrary.wiley.com/doi/ abs/10.1002/adma.200900375

**Chaohan Wang** (Graduate Student Member, IEEE) received the B.Eng. degree in electrical engineering from McGill University, Montréal, Canada, in 2017 and the M.Sc. degree in analogue and digital integrated circuit design from Imperial College London, U.K., in 2019. He is currently pursuing the Ph.D. degree at Imperial College London, London, U.K. His research interest includes hybrid CMOS/Memristor systems, data converters, and mixed-signal integrated circuit design.

**Zhaoguang Si** (Graduate Student Member, IEEE) received the B.Eng. degree in electrical and electronic engineering from University of Liverpool, Liverpool, U.K., in 2020 and the M.Sc. degree in analogue and digital integrated circuit design from Imperial College London, London, U.K., in 2021. He is currently pursuing the Ph.D. degree at Imperial College London. His research interests include memristive analog applications and memristor-associated data converters.

Xiongfei Jiang (Graduate Student Member, IEEE) received the B.Eng degree in optoelectronic information science and engineering at UESTC, Chengdu, China, in 2020 and the M.Sc degree in analogue and digital integrated circuit design from Imperial College London, London, U.K, in 2020. He was a circuit design engineer at ARM Western Technology Research and Development Co. in China, and responsible for integrated circuit standard cell design. He is currently pursuing the Ph.D. degree at the University of Edinburgh. His research interests

include ultra-low power integrated circuits for in-sensor and near-sensor computing in neuromorphic electronics and neural interfaces.

Adil Malik (Graduate Student Member, IEEE) received the M.Eng degree in Electrical and Electronic Engineering from Imperial College London, London, U.K., in 2020. He is currently pursuing his Ph.D. degree at Imperial College London. His current research interests include the stochastic modelling and analogue circuit applications of memristors.

Yihan Pan (Graduate Student Member, IEEE) received the B.Eng. degree in electronic engineering from University of Manchester, Manchester, U.K., in 2018 and the M.Sc. degree in analogue and digital integrated circuit design from Imperial College London, London, U.K., in 2019. She is currently pursuing the Ph.D. degree at the University of Edinburgh. Her research interests include RRAM-based memory architectures and hardware topologies for symbolic processing.

**Spyros Stathopoulos** received the Ph.D. degree in applied physics researching on shallow junction engineering in silicon and germanium from the National Technical University of Athens, Greece. He is currently with the Centre for Electronics Frontiers, University of Edinburgh, working on the fabrication, characterization, and CMOS integration of memristive devices.

Christos Papavassiliou (Senior Member, IEEE) received the B.Sc. degree in Physics from the Massachusetts Institute of Technology, and the Ph.D. degree in Applied Physics from Yale University. He has worked on GaAs monolithic microwave integrated circuit (MMIC) design and measurements with Foundation for Research and Technology, Hellas, Crete, Greece, and was involved in several European and regional projects on GaAs MMIC technology. He joined Imperial College London in 1996, where he has worked on SiGe technology

development, RF IC, and instrumentation. He currently works on memristor array programming and testing, integration with CMOS, and memristor applications.

Alexander Serb (Senior Member, IEEE) received the degree in biomedical engineering and the Ph.D. degree in electrical and electronics engineering from Imperial College in 2009 and 2013, respectively. He was a Research Fellow at the Zepler Institute (ZI), University of Southampton, U.K. He joined University of Edinburgh as a Reader in School of Engineering in 2022, where his research interests are cognitive computing, neuroinspired engineering, algorithms, and applications using RRAM, RRAM device modeling, and instrumentation design.

Shiwei Wang (Senior Member, IEEE) received the B.Eng degree (Outstanding Honor) in electronic engineering from Zhejiang University, China, in 2010, and the Ph.D. degree in microelectronics from the University of Edinburgh, U.K., in 2014. He was a Research Assistant Professor at SIAT, Chinese Academy of Sciences, China (2014-2015), a Senior Researcher at IMEC, Belgium (2015-2020), and an Associate Professor at the ECS department, University of Southampton, U.K. (2020-2022). He joined University of Edinburgh as a Reader in

School of Engineering in 2022. His research interests lie in the field of analog mixed signal integrated circuits for emerging applications, such as AI, implantable/wearable electronics, brain machine interface, and sensor instrumentation.

Themis Prodromakis (Senior Member, IEEE) received the bachelor's degree in electrical and electronic engineering from the University of Lincoln, U.K., the M.Sc. degree in microelectronics and telecommunications from the University of Liverpool, U.K., and the Ph.D. degree in electrical and electronic engineering from Imperial College London, U.K. He then held a Corrigan Fellowship in nanoscale technology and science with the Centre for Bio-Inspired Technology, Imperial College London, and a Lindemann Trust Visiting Fellowship

with the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, USA. He was a Professor of nanotechnology at the University of Southampton, U.K. He holds the Regius Chair of Engineering at the University of Edinburgh and is Director of the Centre for Electronics Frontiers. He is currently a Royal Academy of Engineering Chair in emerging technologies and a Royal Society Industry Fellowship. His background is in electron devices and nanofabrication techniques. His current research interests include memristive technologies for advanced computing architectures and biomedical applications. He is a fellow of the Royal Society of Chemistry, the British Computer Society, the IET, and the Institute of Physics.