# Multidimensional device architectures for efficient power electronics

Yuhao Zhang<sup>a,1</sup>, Florin Udrea<sup>b,1</sup>, Han Wang<sup>c,1</sup>

<sup>a</sup>Center for Power Electronics Systems, Bradley Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University (Virginia Tech), 1185 Perry St, Blacksburg, Virginia 24060, USA.

<sup>b</sup>Department of Engineering, University of Cambridge, Cambridge CB3 0FA, UK.

<sup>c</sup>Ming Hsieh Department of Electrical Engineering, University of Southern California, 3737 Watt Way, Los Angeles, California 90089, USA.

<sup>1</sup>E-mails: yhzhang@vt.edu, fu10000@cam.ac.uk, han.wang.4@usc.edu

# Abstract

Power semiconductor devices are key to delivering high efficiency energy conversion in power electronics systems, which is critical towards efforts in reducing energy loss, cutting carbon dioxide emissions and creating more sustainable technology. While the use of wide or ultra-wide bandgap materials will be required in order to create improved power devices, multidimensional architectures can also improve performance, regardless of the underlying material technology. In particular, multidimensional device architectures — such as superjunction, multi-channel and multi-gate technologies — can enable advances in the speed, efficiency, and form factor of power electronics systems. Here we review the development of multidimensional device architectures for efficient power electronics. We explore the rationale for using multidimensional architectures and the different architectures available. We also consider the performance limits, scaling, and material figure-of-merits of the architectures, and identify key technological challenges that need to be addressed in order to realize the full potential of the approach.

# Introduction

Power electronics technologies provide electrical energy conversion, primarily using solid-state semiconductor devices and passive components. The global power device market reaches US\$ 40 billion (https://www.imarcgroup.com/power-semiconductor-market) and is rapidly expanding, driven by emerging applications such as electric vehicles, data centres, electric grids, and renewable energy processing. In power electronic systems, power devices are used as solid-state switches. Ideal power devices should be able to conduct infinite current with minimal resistance, block infinite voltage, and switch at infinite frequency with zero power loss. Translated to practical devices, these conditions equate to low on-state resistance ( $R_{ON}$ ), high breakdown voltage (BV), and small switching losses. The trade-offs between these device metrics usually determine the efficiency, frequency, and power density of an entire power electronic system. Thus, innovation in power device engineering is a key driver for energy savings and associated reductions in carbon dioxide emission.

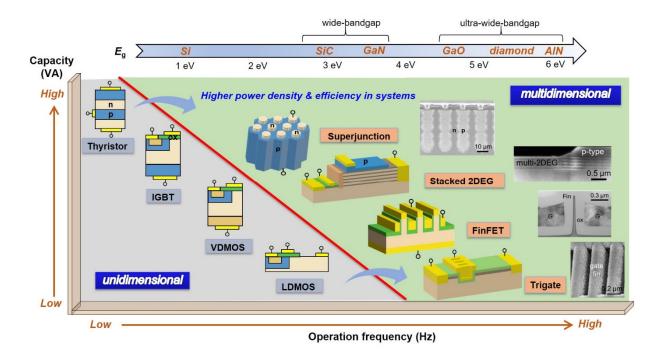

Power device performance relies on material choice and also device concept and architecture. Conventional power devices — such as the insulated-gate bipolar transistor (IGBT) and the power metal–oxide–semiconductor field-effect transistor (MOSFET) — rely on a semiconductor layer to conduct current and block voltage, and an in-plane gate or base for current modulation. The main current flow and blocking electric field follow the same direction, producing an effective unidimensional (1D) device. These devices are limited by a fundamental trade-off between the volt-amp capacity and switching frequency of the device (Fig. 1). This is because the conduction and switching losses usually upscale with the conduction current and blocking voltage, and the sum of these losses is inversely proportional to the maximum switching frequency under the system efficiency requirement. For unipolar devices, which switch faster than their bipolar counterparts, there is another strong trade-off between *BV* and specific  $R_{ON}$  ( $R_{ON,SP} = R_{ON} \cdot A$ , where *A* is the device area).<sup>1</sup> This trade-off comes from the application of the 1D Poisson theory and reflects the physical origin of the capacity-frequency trade-off for unipolar devices. Such device trade-offs limit a concurrent realization of high power, high frequency, high efficiency, and small form factor in power electronic systems.

There are two main approaches to improve these trade-offs in power devices. The first approach is to employ semiconductors with superior properties for power switching, such as wide-bandgap (WBG) materials. The last decade has seen WBG devices based on silicon carbide (SiC) and gallium nitride (GaN) reach mass production and commercialization. Since the critical electric field ( $E_C$ ) roughly scales with the square of the bandgap, SiC and GaN — both with bandgaps about three times larger than silicon — can have an  $E_C$  10 times higher than silicon. Compared to bipolar silicon devices (such as IGBTs), commercial WBG devices such as SiC MOSFET and GaN high-electron-mobility transistor (HEMT) are unipolar and can enable a much higher frequency of operation and provide system benefits.<sup>2–6</sup> Ultra-wide-bandgap (UWBG) materials — including gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), aluminium nitride (AlN) and diamond — are also under development and promise an  $E_{\rm C}$  at least twice that of SiC and GaN. UWBG devices possess a theoretical  $R_{\rm ON,SP}$ ~BV trade-off limit superior to WBG devices.<sup>7–10</sup> However, their current performance is still far below their intrinsic limits due to many material challenges.

The second approach involves innovation in device architecture. The impact of device architecture evolution on power device performance can be seen in the history of 1D silicon power devices before the advent of WBG materials, from the commercialization of thyristors in the 1950s to power MOSFETs in the 1970s to IGBTs in the 1980s. Recently, several innovative architectures have been developed with a common feature of introducing electrostatic engineering in at least one additional geometrical dimension in either the drift or channel region. Superjunctions incorporate the electric field modulation in a plane perpendicular (transversal) to the current conduction direction, breaking by several orders of magnitude the  $R_{ON,SP} \sim BV$  trade-off of 1D devices.<sup>11</sup> The superjunction changed the limit of silicon power devices and has been commercially successful. Another example is to employ a multi-channel stack of two dimensional electron gas (2DEG) channels displaced in the third dimension (perpendicular to the current conduction plane) in a lateral HEMT structure. This parallel conduction reduces R<sub>ON,SP</sub> and can push performance beyond the limits of 1D HEMTs. Another example is the use of FinFET and similar multi-gate electrostatics engineering, which create additional dimensions for current modulation in the gated channel. The highlyscaled fin-shape channel allows a high channel density and concomitantly results in a shift of the carrier transport towards the path with the highest mobility. The gated channel resistance, which dominates  $R_{ON,SP}$ in many conventional device structures, is therefore aggressively reduced.

While the move from planar MOSFETs to multidimensional device structures such as FinFETs has allowed continuous scaling in CMOS logic electronics, multidimensional power device architectures can break the trade-off between power capacity and frequency in power devices and systems (Fig. 1). For a given capacity, the  $R_{ON,SP}$  reduction allows for smaller A, capacitances and switching losses, and thereby higher frequency (or higher system efficiency at the same frequency). Moreover, this advance is device inherent and applicable to all materials. Such architectures have recently demonstrated encouraging capabilities in silicon, SiC, and GaN, and may offer even greater potential in UWBG materials. Moreover, many multidimensional architectures promise improvements to device performance as their sizes are reduced. This is contrary to most 1D unipolar power devices, which are known to gain little improvement with geometrical scaling. This suggests that the current performance limit and figure-of-merit (FOM) defined for 1D power devices may not be suitable for multidimensional architectures and could underestimate considerably the potential of these device architectures.

In this Review, we explore the potential value of multidimensional architectures in power devices. We consider the rationale for using multidimensional architectures, and the different architectures available:

superjunction, multi-channel, FinFET and trigate devices. We also consider the performance limits, scaling, and material figure-of-merits of the architectures, and discuss the critical challenges that lie ahead for the field.

## The rationale for using multidimensional architectures

Power transistors are built on a vertical or lateral structure and mainly comprise a gated channel for current modulation and a drift region for voltage blocking. Taking into account the specific resistance of the Ohmic contacts ( $R_c$ ), gated channel ( $R_{ch}$ ) and drift region ( $R_{dr}$ ), the theoretical  $R_{ON,SP} \sim BV$  trade-off of a 1D vertical unipolar transistor can be written as

$$R_{ON,SP} = R_C + R_{ch} + \frac{4BV^2}{\varepsilon\mu E_C^3} \tag{1}$$

where  $\varepsilon$  and  $\mu$  are the material permittivity and majority carrier mobility in the drift region, respectively. Here the  $R_{dr}$  limit represents the widely-used 1D FOM introduced by Baliga in the 1980s.<sup>12</sup> If the doping dependence of  $\mu$  and  $E_c$ , punch-through design, and impact ionization are further considered, the  $R_{dr}$  limit is proportional to  $BV^{\alpha}$ , in which  $\alpha$  ranges from 2.18<sup>13</sup> to 2.5<sup>14</sup>.

The  $R_{ch}$  of vertical GaN and SiC MOSFETs is limited by the low channel mobility ( $\mu_{ch}$ ) in either the inversion mode or accumulation mode, which could be 10 times lower than in Si. This is usually believed to be due to interface states (which affects the Columbic mobility) and carrier trapping.<sup>3,15</sup> The highest  $\mu_{ch}$  reported in SiC and GaN MOS channels is 130~150 cm<sup>2</sup>/Vs<sup>3,15</sup> and 150~185 cm<sup>2</sup>/Vs<sup>16,17</sup>, respectively, which are much lower than the bulk mobility of SiC and GaN (800~1200 cm<sup>2</sup>/Vs). Limited by  $\mu_{ch}$ , the smallest  $R_c + R_{ch}$  reported in SiC MOSFETs<sup>18</sup> and GaN MOSFETs<sup>16,17</sup> is about 0.65 m $\Omega \cdot cm^2$  and 0.45 m $\Omega \cdot cm^2$ , respectively. In UWBG devices,  $\mu_{ch}$  is even lower, and it is very challenging to form low-resistance contact.<sup>7</sup>

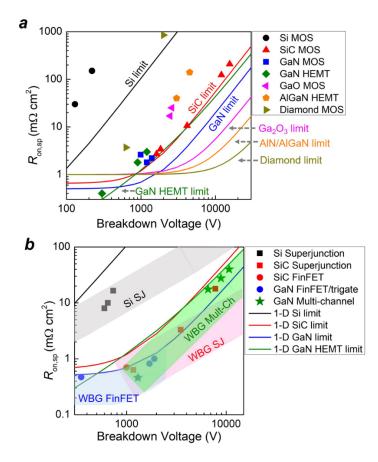

Fig. 2(a) shows the 1D limits of Si, WBG and UWBG unipolar devices calculated using their material properties,<sup>19</sup> the smallest  $R_C + R_{ch}$  reported in SiC and GaN MOSFETs, and an optimistic estimation for the  $R_C + R_{ch}$  limit of UWBG devices (1 m $\Omega \cdot \text{cm}^2$ ). It is evident that  $R_{ON,SP}$  of 1D WBG and UWBG devices is dominated by the gated channel at low voltage up to at least kilovolt, from which  $R_{dr}$  takes over and the WBG/UWBG material properties can be exploited to improve device performance.

In some materials like GaN,  $R_{ch}$  can be reduced by using the 2DEG channel in a lateral HEMT, which has a high mobility of ~2000 cm<sup>2</sup>/Vs. The  $R_{ON,SP}$ ~BV trade-off of a 1D HEMT can be written as<sup>20,21</sup>

$$R_{ON,SP} = R_C + R_{CH} \frac{BV}{\eta E_C} + \frac{BV^2}{q n_{2D} \mu_{2D} \eta^2 E_C^2}$$

(2)

where  $n_{2D}$  and  $\mu_{2D}$  are the 2DEG concentration and mobility, respectively.  $\eta E_c$  is the average lateral electric field ( $\eta < 1$ ).  $R_{CH}$  is the channel resistivity in  $\Omega$ ·mm, and the corresponding  $R_{ch}$  (in m $\Omega$ ·cm<sup>2</sup>) scales

with *BV* in lateral devices due to the increased device area. Using the typical  $R_{CH}$  of p-gate GaN HEMTs<sup>22</sup> and a typical  $\eta E_C$  of 1 MV/cm<sup>23</sup>, the GaN HEMT limit shows advantages over SiC at low voltage (Fig. 2(a)). This is partly why GaN HEMTs are currently commercialized in the voltage classes lower than SiC.

In addition to the 1D limits, Fig. 2(a) also shows the state-of-the-art performance of Si MOSFETs,<sup>24</sup> SiC MOSFETs,<sup>25</sup> GaN MOSFETs,<sup>16,17,26</sup> GaN HEMTs,<sup>5</sup> Ga<sub>2</sub>O<sub>3</sub> MOSFETs,<sup>27,28</sup> AlN/AlGaN HEMTs,<sup>29,30</sup> and diamond FETs.<sup>31,32</sup> Lateral GaN HEMTs and vertical SiC MOSFETs are close to their 1D limits, while emerging UWBG devices are still far away from their limits as a result of their relative immaturity.

These 1D limits in Si, SiC and GaN have been recently broken by several multidimensional device architectures, which either alter the  $R_{dr} \sim BV$  trade-off or aggressively reduce  $R_{ch}$  (Fig. 2(b)). Superjunction reshapes the electric field in the drift region and allows for linear dependence of  $R_{dr}$  on BVto replace the quadratic limit in (1). After reaching a commercial success in Si,<sup>11</sup> superjunction was recently also demonstrated in SiC, enabling device performance beyond the 1D SiC limit across a wide BV range from 1170 V to 7800 V.<sup>33-35</sup> In the lateral HEMT, the use of stacked 2DEG channels increases the effective  $n_{2D}$  without compromising  $\eta E_c$  due to the balanced polarization charges. Multi-channel GaN HEMTs have been demonstrated beyond the 1D WBG limits with a BV from 1300 V<sup>36</sup> up to 10 kV.<sup>37</sup>

Channel innovation is essential to enable the benefits of superjunction and multi-channel to reach low voltage devices. The use of multi-gate architectures and submicron-meter-sized fin-shaped channels can significantly increase the channel density,<sup>38</sup> and more fundamentally, shift the carrier transport away from the low-mobility MOS channels.<sup>39,40</sup> This circumvents the  $\mu_{ch}$  limitation in WBG/UWBG devices. FinFET and trigate devices have been demonstrated in SiC<sup>39-42</sup> and GaN<sup>38</sup>, and in both vertical MOSFETs and lateral HEMTs, with the state-of-the-art performance exceeding the 1D  $R_{ch}$  limit.<sup>19,36,42-44</sup>

The device physics of these multidimensional device architectures will be elaborated in the following sections. Interestingly, their performance limits can be continuously enhanced by scaling certain structural parameters, resulting in a new band of device limits beyond the 1D limit line for each power semiconductor material (Fig. 2(b)). It should be noted that there are other multidimensional structures in power devices. We believe that the three mentioned above are representative as they have enabled device performance to break 1D limits. For example, the junction barrier Schottky diode comprises alternative p-and n-type grids below the contact, which is multidimensional in nature but may be considered as a special form of superjunction that does not possess its full functionality (e.g., charge balance) to break the 1D limits.

# Superjunction

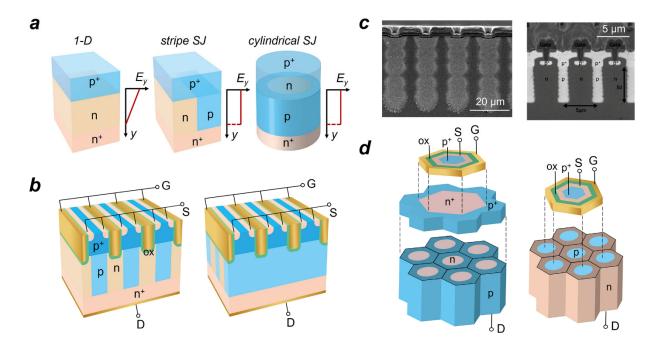

The  $R_{ON,SP} \sim BV$  limit in (1) comes from the basic intuition that the higher the resistivity of a drift region (e.g., thicker or more lowly doped), the higher the *BV*. Analytically this trade-off is described by the solution of the 1D Poisson theory. The field distribution for which the minimum  $R_{ON,SP}$  happens has a well-known

triangular shape with the maximum electrical field occurring at the junction and the triangular shape filling the drift region at breakdown (Fig. 3(a)). One can immediately spot that this triangular field shape may not be optimum as the area under the electrical field when the maximum electric field reaches  $E_{\rm C}$  represents the *BV*. Unfortunately, the only way a rectangle shape can be obtained is by lowering the doping to an intrinsic level which has the adverse effect of increasing  $R_{\rm ON,SP}$  immensely. Therefore the 1D Poisson theory does not result in an ideal field distribution and moreover, the optimal doping is relatively low, thus putting a firm limit on the minimum  $R_{\rm ON,SP}$ .

Superjunction spectacularly broke the limit of the 1D theory by using a 2D design for which the 1D Poisson limitations no longer apply. The superjunction delivers a rectangular distribution of the electric field in a line across the drift region, and, even more importantly, does so while increasing the doping level by one to two orders of magnitude as compared to the 1D design. Fig. 3(a) shows a 1D design, versus a 2D superjunction and a cylindrical superjunction which can be effectively employed in a 3D drift region.

The drift region of a superjunction comprises multiple, alternate n and p semiconductor pillars with relatively high doping. Provided that the pillars are fairly narrow and the net doping charge in the alternate pillars is approximately equal (i.e., charge balance), it is possible to deplete such pillars at relatively low voltages applied between the main terminals. Upon depletion, the entire drift region appears to be a single block of "intrinsic" semiconductor with a near-uniform electric field distribution. The thinner the pillars, the higher the charge that can be placed inside the n-pillars, and therefore the lower the  $R_{ON,SP}$  the device can achieve, without compromising the *BV*. In theory, these pillars can be nanometers in dimensions and the ultimate limitation of their dimension is given by the parasitic junction field-effect-transistor (JFET) effect that appears in the on-state. The parasitic JFET effect can be described as a constriction of the on-state current due to the intrinsic depletion generated between the n and p pillars and the additional depletion region created by the application of the drain voltage, which acts as a reverse bias on the pn junction formed between the pillars.<sup>45</sup> The JFET effect sets a minimum, "ultimately optimum" width for the superjunction drift region which is material dependent (will be elaborated in section 6).<sup>46,47</sup>

Following the introduction of CoolMOS<sup>TM</sup> in 1998<sup>48,49</sup>, the superjunction field has delivered some of the best unipolar Si power devices in the market for the last two decades. The latest Si CoolMOS<sup>TM</sup> has been commercialized from 500 V to 950 V. Fig. 3(b) shows two implementations of a 2D superjunction design in a trench MOSFET. The superjunction pillars can run in the third dimension parallel to the trench width or perpendicular to it.<sup>50</sup> The latter has the advantage that no precise alignment is needed between the superjunction structures and the gated channels. Such design is more appropriate for very narrow superjunction pillars.

Superjunction has been largely described as a Si concept, as it provided Si with a tool to fight against the WBG newcomers in the field. However, the superjunction concept is material agnostic and can be employed very efficiently in various forms for SiC and GaN devices. In 2016-2018, SiC superjunction diodes and MOSFETs were first demonstrated with performance beyond the 1D SiC limit at a voltage class around 1.2 kV.<sup>33,51</sup> The breaking 1D limit performance was later realized in 3.3 kV and 6.5 kV class SiC superjunction MOSFETs.<sup>34,35</sup> In addition to the MOSFETs, SiC superjunction has also been demonstrated in JFETs recently.<sup>52</sup>

The Si and SiC generations of superjunction structures employed a 2D pillar geometry for the p-n pillars. Owing to its simplicity, this arrangement can be modeled by using 1D Poisson equations applied to two axes (i.e. longitudinal and transversal).<sup>11,53,54</sup> Indeed, several analytical models based on these simplified assumptions have been used to find a limit for  $R_{ON,SP}$  with respect to each cell pitch for a given BV.<sup>45,53,55–57</sup> *Fujihira*'s ideal 2D superjunction model unveiled a linear relationship between  $R_{ON,SP}$  and BV.<sup>53</sup> Kang and *Udrea* expanded *Fujihira*'s 2D model, by accounting for the parasitic JFET effect, and derived a new theoretical  $R_{ON,SP}$  limit for Si and WBG superjunctions.<sup>46,58</sup> According to these analytical models, WBG superjunctions possess an optimal cell pitch narrower than the Si superjunction, as well as higher optimal doping concentration, therefore enabling a much lower  $R_{ON,SP}$ . This narrower cell pitch can be seen from the cross-sections of experimental Si and SiC superjunctions (Fig. 3(c)).<sup>11,59</sup>

Building on the cylindrical superjunction unit-cell shown in Fig. 3(a), 3D superjunction architectures have been recently proposed and scrutinized for Si and WBG materials.<sup>47</sup> The 3D superjunction's doping can be increased by a factor of 2 over that of the 2D structure. This is because, intuitively, the depletion region across the radial p-n junction spreads more extensively than that of stripe pillars, for the same bias condition and doping levels.<sup>47</sup> Fig. 3(d) shows two transistor implementations of a 3D superjunction drift region aligned to the top gated channel.<sup>47</sup> The two show a nanowire-style and a nanomesh, shell-style (honeycomb structure) implementations of the n-pillars, respectively. For these 3D superjunction transistors, a precise match of size and form factor is not required between the gated channel and the superjunction structure, which can facilitate the geometrical scaling in the superjunction.

Finally, the superjunction can be used as a powerful concept in different types of multidimensional architectures, from 2D extension in the third dimension of n-p stripes or n-p sheet charges in a lateral device,<sup>60</sup> to cylindrical n-p stripes between p+ floating rings in termination regions in a vertical device.<sup>61</sup> Some interesting forms of lateral superjunction will be introduced in the next section.

# **Multi-channel**

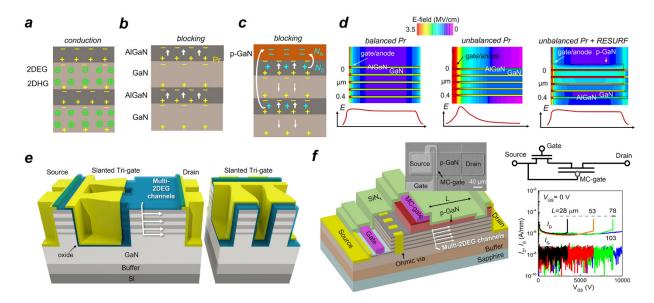

Multi-channel heterostructures reduce the sheet resistance ( $R_{SH}$ ) by spreading a large  $n_{2D}$  into stacked channels with the  $n_{2D}$  in each channel not too high to compromise  $\mu_{2D}$  due to carrier scattering. The GaNbased multi-channel heterostructures can be either undoped<sup>62–65</sup> or doped,<sup>36,43,66,67</sup> and an  $R_{SH}$  3-10 times lower than the single-channel has been reported in both schemes. In an ideal undoped multi-channel, parallel 2DEGs and two-dimensional-hole gases (2DHGs) with equal  $n_{2D}$  are induced on the top and bottom sides of each GaN layer (Fig. 4(a)). A  $R_{SH}$  of 37  $\Omega$ /sq was demonstrated in a 7-channel AlN/GaN heterostructure,<sup>63</sup> and the 4-inch, 5-channel AlGaN/GaN wafer is commercially available with a  $R_{SH}$  of 115  $\Omega$ /sq.<sup>64</sup> On the other hand, the doped multi-channel usually has impurity<sup>43,67</sup> or modulation doping<sup>66</sup> selectively introduced in each barrier layer to boost 2DEG densities, leaving the quantum well in GaN undoped to minimize the ion scattering and preserve  $\mu_{2D}$ . A  $R_{SH}$  of 67  $\Omega$ /sq was reported in a modulationdoped 8-channel heterostructure<sup>66</sup>.

Despite the low  $R_{SH}$ , multi-channel power devices face major challenges in electric field management and gate modulation. In the multi-channel drift region, the possible large volume charge would result in a quick drop in electric field and thus a low *BV*. It was proposed that the undoped multi-channel naturally forms a polarization superjunction, as the precise balance of positive and negative polarization charges on both sides of the GaN layer results in a nearly zero net charge and thus a uniform electric field (Fig. 4(b)).<sup>62</sup> For the doped or unintentionally doped multi-channels with net donors, a p-GaN cap layer was proposed to balance these depletion charges in the multi-channel at high voltage, serving as a reduced-surface-field (RESURF) structure (Fig. 4(c)).<sup>68</sup> The REUSRF is a primitive form of a superjunction based on a 2D curved junction rather than multiple junctions. The double RESURF and multiple RESURF are also proved to be effective in lateral Si devices.<sup>11</sup>

With the natural or p-GaN assisted charge balance, a linear BV increase with the multi-channel length has been demonstrated up to ~10 kV.<sup>62,68</sup> Fig. 4(d) shows the simulated electric field contours at high voltage in an undoped multi-channel as well as two doped multi-channels with and without the p-GaN RESURF layer, showcasing the significance of the charge balance (enabled by polarization superjunction or RESURF structure) on enabling a high lateral field strength. This BV scalability with the device length, together with the low  $R_{SH}$ , makes the multi-channel architecture an excellent platform for high-voltage devices.

Electric field management is also critical at the device edge, especially in Schottky barrier diodes (SBDs), as the concurrence of high electric field and parallel current channels could induce a large leakage current. Several effective edge terminations for multi-channel SBDs include the trigate field plate,<sup>69</sup> planar p-GaN,<sup>64</sup> and junction-fin-anode.<sup>70</sup> Leveraging the MOS structure or p-n junction at the planar surface or fin sidewalls, these designs allow the depletion of  $n_{2D}$  near the Schottky contact and thus reduce the peak electric field and move it away from the Schottky contact. The p-GaN and junction-fin termination also allow the electric field to spread into p-type materials, further suppressing the field crowding. These terminations enabled GaN multi-channel SBDs to achieve significant improvements in *BV*, from 900 V,<sup>69</sup> 3.3 kV,<sup>64</sup> to 5.2 kV<sup>70</sup>, and ultimately to 10 kV.<sup>68</sup> The *R*<sub>ON,SP</sub> of all these GaN SBDs are 2-3 times lower than the similarly-rated SiC SBDs.

Gate modulation is a pressing challenge for multi-channel transistors, as the indirect gate control over the buried channels results in a deep depletion-mode (D-mode) operation with low transconductance. This is partly why the polarization superjunction HEMTs were demonstrated only on a single pair of 2DEG and 2DHG without reaching the multi-channel.<sup>71</sup> Later, the use of trigate was demonstrated as an effective solution in radio-frequency multi-channel HEMTs, which provides sidewall gate control for the buried 2DEGs.<sup>72</sup> A high-voltage trigate HEMT with a  $R_{ON,SP}$  of 0.46 m $\Omega \cdot cm^2$  and a BV of 1300 V was recently demonstrated on a 4-channel doped AlGaN/GaN heterostructure.<sup>36</sup> The enhancement-mode (E-mode) operation was realized by shrinking the fin width to 15 nm. A slanted trigate profile was used in each fin to relax the electric field stress at the gate edge (Fig. 4(e)). Similar to n-type transistors, trigate p-type multichannel HEMTs were also demonstrated with an E-mode operation.<sup>73</sup>

An alternative gate design for multi-channel transistors is employing an integrated Cascode structure<sup>37</sup> (Fig. 4(f)). This device monolithically integrates a low-voltage (LV), E-mode HEMT based on a single 2DEG channel and a high-voltage (HV), deep D-mode HEMT based on the multi-channel. The HV-HEMT gate is connected to the LV-HEMT source, forming a Cascode configuration, which enables the E-mode operation with the device gate shielded from high voltage and high field. By further incorporating a p-GaN RESURF layer, this multi-channel monolithic-Cascode HEMT demonstrated a *BV* up to 10 kV with  $R_{ON,SP}$  well below the 1D WBG limits, setting a performance record in multi-kilovolts transistors.

# **FinFET and trigate**

FinFET and trigate devices comprising multi-gate architectures and nanometer-sized fin channels have become the backbone device technology for Si CMOS electronics at deeply scaled logic technology nodes.<sup>74,75</sup> The fin width of state-of-the-art Si FinFETs at the sub-10 nm node has been scaled down to 7 nm.<sup>76</sup> Beyond FinFETs, gate-all-around nanowire and nanosheet FETs are being extensively studied for more advanced technology nodes.<sup>76</sup> These devices show a good success of multidimensional architectures in the digital world.

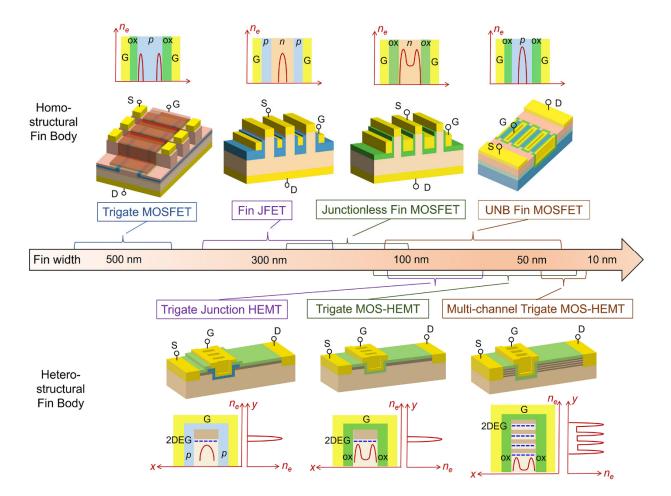

In the last few years, the FinFET concept has also been leveraged in WBG and UWBG power transistors for two major objectives: (a) realizing a superior gate control and the E-mode operation, exemplified by the trigate multi-channel HEMT discussed in the last section, and (b) increasing channel density and thereby shrinking the  $R_{ch}$  that dominates  $R_{ON,SP}$  of WBG and UWBG transistors up to the kilovolt voltage class. Other merits reported for power FinFETs included the alleviated current collapse and enhanced thermal management.<sup>38</sup> Note that these benefits of FinFET in power are different from those offered to digital electronics. Some benefits of digital FinFETs such as the low subthreshold swing, enhanced transistor compactness and reduced short channel effects, are less relevant in the power domain. A unique feature of power FinFETs and trigate devices that differ from Si digital FinFETs is a large diversity in the fin body (homo- or hetero-structure), device structure (lateral or vertical), and sidewall gate stacks (Schottky, MOS, or p-n junction), as shown in Fig. 5. For example, while the fin body is typically un-doped in digital FinFETs, the n-type and p-type doping as well as heterojunction-based quantum wells have all been demonstrated in power FinFETs. These structural variations, in conjunction with the fin dimension, result in different carrier profiles and transport characteristics within the fin channel. Below we introduce major power FinFETs and trigate devices as well as their distinct channel electrostatics.

A straightforward approach to reduce  $R_{ch}$  using the scaled fins is to increase the channel density without altering the inherent channel electrostatics, as demonstrated in vertical trigate MOSFETs and fin-channel JFETs (Fin-JFETs). SiC trigate MOSFETs employed ~0.5 µm-wide fin channels to increase the effective width of the MOS inversion layer, realizing a 3.6 times reduction in  $R_{ch}$  and up to a twofold reduction in  $R_{ON,SP}$ .<sup>41</sup> The use of sub-micron fin channels in WBG JFETs has allowed for a shift from the D-mode to Emode operation.<sup>77,78</sup> As the fin dimension reduces in SiC Fin-JFETs, however, the sidewall ion implantation used for p-gate formation would degrade the channel mobility, which offsets the benefits of high channel density and results in a higher  $R_{ch}$ . This processing issue is not present for GaN Fin-JFETs due to their implantation-free fabrication.<sup>44</sup> In conjunction with the fin scaling, GaN fin channels can be doped 10 times higher than the drift region without impairing the E-mode operation, further lowering  $R_{ch}$ . An industrial vertical GaN Fin-JFET was demonstrated with an  $R_{ON,SP}$  of 0.82  $\Omega \cdot cm^2$  and BV over 1700 V,<sup>44,78</sup> rendering the highest FOM in kilovolt-class transistors.

As the fin width scales down to ~200 nm, the E-mode operation can be realized in a junctionless fin due to the workfunction difference between the gate metal and semiconductor; meanwhile, the junctionless Fin-MOSFET can avoid the punch through up to a kilovolt drain bias at zero gate bias.<sup>79</sup> Such a junctionless fin accommodates two sidewall accumulation-mode MOS channels in parallel with the bulk fin channel, significantly boosting the total carrier concentration and exploiting the higher bulk mobility as compared to the MOS mobility.<sup>19</sup> E-mode GaN Fin-MOSFETs with fin width of 180~200 nm have been demonstrated, achieving  $R_{ON,SP}$  of 1 m $\Omega \cdot cm^2$ ,<sup>80</sup> BV close to 2 kV,<sup>19</sup> as well as low junction capacitances and charges.<sup>81</sup> Similar Fin-MOSFETs have also been demonstrated in UWBG Ga<sub>2</sub>O<sub>3</sub> with a BV up to 2.6 kV.<sup>27</sup>

As the fin width further scales to below 100 nm, channel electrostatics become distinct in the inversiontype MOSFET. The inversion layers formed on two sidewalls overlap, forcing the entire fin channel (interface layers and volume) into the strong inversion. This phenomenon is similar to that observed first in low-voltage, double-gate silicon-on-insulator devices,<sup>82</sup> the structure of which is similar to FinFETs, and is known as the 'volume inversion'. Due to this effect, carrier transport is shifted to the center of the fin, allowing the full exploitation of the higher bulk mobility. The fabricated ultra-narrow-body (UNB) SiC MOSFETs with 55-nm-wide fins show channel mobility of 276 cm<sup>-2</sup>V<sup>-1</sup>s<sup>-1</sup>, being 10 times higher than that in conventional SiC MOSFETs.<sup>39</sup> Further studies reveal that the FinFET effect can allow for up to an 18 times increase in channel mobility.<sup>40</sup> An fin-width window of about 30-50 nm is predicted to be optimal for UNB SiC MOSFETs.<sup>40</sup> The FinFET effect has also been leveraged to demonstrate a vertical SiC FinFET with an  $R_{ON,SP}$  of 0.7  $\Omega \cdot cm^2$  and BV over 1000 V.<sup>42</sup>

When the FinFET concept is brought into HEMTs, the heterostructure fin is wrapped by the gate stack, forming a trigate control over the 2DEG channel. In AlGaN/GaN HEMTs, this narrow fin reduces the piezoelectric polarization and 2DEG density due to the partial strain relaxation in the AlGaN barrier,<sup>83</sup> facilitating the E-mode realization. As compared to other E-mode gate structures, trigate HEMTs retain high  $n_{2D}$  and  $\mu_{2D}$  and allow for a lower gate channel resistivity.<sup>22</sup> The early power trigate HEMTs in GaN were demonstrated based on Schottky-type gates.<sup>84</sup> Later, the MOS gate stack became the prevailing choice in GaN trigate HEMTs, as it reduces the gate leakage current and increases the gate overdrive range.<sup>85</sup> A critical trade-off of these trigate HEMTs lies between  $n_{2D}$  and the fin width needed for realizing the E-mode operation. A fin width down to 20~30 nm is usually required for achieving the E-mode operation in trigate GaN MOS-HEMTs.<sup>38</sup> This requirement could be relaxed to 100-200 nm if an additional barrier recess<sup>85</sup> or a trap charge oxide<sup>86</sup> is employed, or it could be tightened to below 15 nm for multi-channel trigate MOS-HEMTs.<sup>36</sup>

Similar to Fin-JFETs, a junction trigate HEMT was recently demonstrated with a p-n junction wrapping around the heterojunction fins in the gate region.<sup>22</sup> Owing to a higher built-in potential of the p-n junction, the junction trigate provides a stronger depletion, enabling the E-mode operation with a fin width over 60 nm.<sup>22</sup> This stronger depletion in the junction trigate also minimizes the short-channel effects, particularly at high temperatures, enabling the demonstration of kilovolt blocking capability at 150 °C in GaN trigate HEMTs.<sup>87</sup> More interestingly, the junction trigate congregates 2DEG towards the center of the fin body, and therefore, enables higher effective mobility and lower gate capacitance as compared to the MOS trigate, in which the 2DEG density usually peaks near the sidewall.<sup>87</sup>

#### Performance limits, scaling, and material figure-of-merits

Power loss occurs during the device conduction and switching as well as at its gate driver. It is thus dependent on switching scheme and circuit topology. A few device-level FOMs (DFOMs) that incorporate  $R_{ON}$ , which determines the conduction loss, and the switching/driver related device parameters, are routinely used for device selection in various applications.<sup>88</sup> In hard switching, voltage and current waveforms intersect during the time of device transition between on and off states. For fast switching with minimal circuit parasitic, the hard-switching loss in each cycle approaches the energy stored in the device output capacitor.<sup>89,90</sup> Hence,  $R_{ON} \cdot Q_{OSS}$  (output charge) is widely used as a DFOM for hard switching. By contrast, soft switching enables a nearly zero switching loss by minimizing voltage-current intersections, leaving

only  $R_{ON}$  to dominate the device loss. Finally, the driver loss is related to the gate charge ( $Q_G$ ) that needs to be supplied or extracted for device turn-on/off. Hence,  $R_{ON} \cdot Q_G$  is a DFOM relevant for applications where the driver loss is significant, such as the high-frequency driving.

The  $R_{ON,SP} \sim BV$  trade-off is an overarching limit for most DFOMs.  $R_{ON,SP}$  not only determines  $R_{ON}$  but also impacts  $Q_{OSS}$  and  $Q_G$ , as for the same  $R_{ON}$ , the device with lower  $R_{ON,SP}$  possesses a smaller A, and generally, smaller charges. Particularly, this trade-off dictates the device performance limit in soft switching applications with small driver loss. To this end, in this section, we will first discuss the  $R_{ON,SP} \sim BV$  trade-off and then revisit  $R_{ON} \cdot Q_{OSS}$  and  $R_{ON} \cdot Q_G$  for multidimensional devices.

As illustrated in section 2, for conventional 1D vertical devices, if contact and channel resistances are neglected, the  $R_{ON,SP}$  limit is proportional to  $BV^2$  with their ratio only dependent on material properties. This relation no longer holds for multidimensional devices. As shown in Table I, the  $R_{ON,SP}$ -BV limits of 2D and 3D superjunction devices<sup>46,47</sup> as well as multi-channel devices (with naturally balanced polarization charges) hinge on not only material properties but also device geometries, e.g., superjunction cell pitch (dor r), radius ratio ( $\beta$ ), and channel number (N). In these devices, the electrostatics in the additional dimension breaks a new path beyond the material innovation for advancing the device performance.

The performance limits of 2D and 3D superjunctions can be continuously advanced by downscaling the cell pitch, and this scaling is typically limited by the process technology available. An additional geometry parameter,  $\beta$ , can be also downscaled in 3D superjunctions to improve the device performance. Recently, it was found that this geometrical downscaling cannot continue indefinitely and, by accounting for the parasitic JFET effect, there is a material-dependent intrinsic limit being no longer related to geometry (and technology).<sup>46</sup> The minimum cell pitch is inversely proportional to the bandgap of semiconductor materials, e.g., around 180 nm, 50 nm and 40 nm for 2D superjunctions based on Si, SiC and GaN, respectively, and the ultimate minimum  $R_{ON,SP}$  is only material dependent. A material FOM can be therefore defined to describe the material limit of superjunction performance, as shown in Table I. This new FOM is proportional to  $E_C^{2.5}$ , while the 1D FOM is to  $E_C^3$ .

The  $R_{ON,SP}$  limit of ideal lateral multi-channel devices is proportional to  $BV^2$ , which is similar to 1D devices but different from superjunction (proportional to BV). In theory, this limit can be indefinitely downscaled by increasing the number of channels. A merit of the multi-channel with naturally balanced polarization charges is the almost zero vertical electric field in each channel layer (e.g., GaN layer in the AlGaN/GaN structure, see Fig. 3(d)), allowing for a lateral field near  $E_C$ . The practical scaling limit of channel numbers could be more process-related, e.g., challenges in contact and gate formation, than material-related, particularly if the lattice-matched heterostructure is used to minimize epitaxial challenges.<sup>91</sup> The material's FOM is proportional with  $E_C^2$  as well as the density and mobility of the 2DEG and 2DHG. It is worth noting that the vertical polarization superjunction with heterostructure pillars was

also studied theoretically;<sup>92,93</sup> its performance limit and material FOM are similar to 2D superjunctions but distinct from the lateral multi-channel devices.

The hard-switching DFOM,  $R_{ON} \cdot Q_{OSS}$ , has been recently analyzed for 2D superjunctions.<sup>94</sup> While  $R_{ON,SP}$  can be continuously reduced by scaling *d* and increasing the doping concentration accordingly, the price it has to pay is the increased specific  $Q_{OSS}$ . The  $R_{ON} \cdot Q_{OSS}$  limit of the 2D superjunction,  $2BV^2/\mu E_c^2$ , turns out to be *d* independent and less than 2 times lower than the limit of 1D devices,  $4BV^2/\mu E_c^2$  (note that the mobility  $\mu$  in superjunction is usually lower than 1D devices due to a higher doping concentration). While no quantitative  $R_{ON} \cdot Q_{OSS}$  modeling of 3D superjunction and multi-channel devices have been reported, a similar increase in specific  $Q_{OSS}$  along with the  $R_{ON,SP}$  downscaling could be expected, which may result in a  $R_{ON} \cdot Q_{OSS}$  independent of the scaling parameter. This suggests that soft switching circuit topologies are preferable to exploit the inherent performance superiority of multidimensional devices.

Similar to the scaling effect in superjunction and multi-channel, geometrical scaling is expected to be also preferable in FinFET and trigate architectures to enable continuous  $R_{ch}$  reduction. The design of finbased gates centers on concurrently realizing the E-mode operation, increasing the channel density, and tuning the carrier transport towards the higher-mobility body region. The downscaling of the fin width is beneficial to all these three design objectives. On the other hand,  $Q_G$  of a power transistor usually consists of gate-to-source charge ( $Q_{GS}$ ) and gate-to-drain charge ( $Q_{GD}$ ), which not only depend on the gate structure but also the drift region. For example, the  $Q_{GD}$  limit of a planar gate superjunction MOSFET hinges on the gate oxide capacitance and superjunction pitch width.<sup>94</sup> This coupling effect suggests that the  $Q_G$ optimization for fin-based gates may require a co-design between gate and drift region. Further investigations are desired to explore the scaling laws of  $R_{ch}$  and  $Q_G$  as well as the associated material FOMs for the diverse fin gates in power devices.

# Multidimensional architectures in radio-frequency devices

Over the past decades, radio-frequency (RF) electronics is another field that has witnessed the success of WBG devices. Despite the distinct operation principles of RF and power devices (function as amplifiers and switches, respectively), they share some common device platforms and structural concepts (e.g., HEMT). Emerging RF applications, such as 5G communications, are migrating to millimeter-wave frequencies and require concurrent advancements in the power, frequency and dynamic range of RF transistor technologies. Multidimensional architectures have been recently introduced to RF devices to achieve these targets.<sup>95</sup> Hence, it is interesting to briefly mention these multidimensional RF devices.

Parasitic capacitance is the key limiting factor for upscaling the cutoff frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{max}$ ) of RF transistors, and it usually increases with device area. The superjunction and multi-channel structures can maximize the chip real estate utilization to boost the blocking voltage and

conduction current, potentially breaking the power-frequency trade-off of conventional RF transistors. For example, excellent trade-offs between  $f_T$ ,  $f_{max}$  and BV were reported in Si superjunction MOSFETs;<sup>96</sup> trigate multi-channel GaN HEMTs demonstrated higher current and power densities as compared to their single-channel counterpart at 30 GHz.<sup>97</sup> The incorporation of a top p-diamond RESURF layer for this multi-channel GaN HEMT achieved a further capacitance reduction and BV enhancement.<sup>98</sup>

Linearity is a key metric of RF transistors that determine their dynamic range, which could also be improved by the deployment of multidimensional structures. Due to the presence of multiple channels, the transconductance ( $g_m$ ) of multi-channel HEMTs was found to exhibit broad plateau characteristics, which lead to higher device linearity.<sup>38,97</sup> In single-channel HEMTs, a linearized and broad  $g_m$  plateau was realized by using a trigate comprising multiple fins with variable widths.<sup>99,100</sup> These channels and fins in the additional dimension provides the new flexibility to tune the device RF characteristics.

#### Summary and outlook

Multidimensional architectures in silicon, SiC and GaN power devices have advanced rapidly over the last two decades. State-of-the-art multidimensional devices have broken the 1D unipolar limits over a wide range of voltages — from 100 V to 10000 V — and shown encouraging capabilities in terms of power capacity, frequency, efficiency, and form factor of power electronic systems. Due to their electrostatics in additional dimensions, these architectures enable new material FOMs and device scaling theories for power devices. Thus, power device advancement is envisioned to no longer solely rely on material innovation.

Further efforts in physics, material science, devices, processing technologies, packaging, and circuits are however needed to push multidimensional power devices towards their limits. Many knowledge gaps exist in the fundamental electrical and thermal transport properties within multidimensional devices. For example, a strong thermal interaction between the 3D gate and multi-channel was recently revealed<sup>101</sup> and electric field mapping and imaging<sup>102</sup> are also desirable to help further visualize the electrostatics in multidimensional structures. From a material standpoint, the use of multidimensional architectures in UWBG devices promises a further performance leap, but the relevant demonstrations are still in their infancy.

Another key area of development is the switching characteristics of multidimensional architectures, particularly at high frequency. For example, interesting dynamic phenomena such as output capacitance hysteresis<sup>103</sup> were reported in superjunction devices and the inter-fin design in FinFETs, which is not critical for  $R_{ON,SP}$  and BV, was found to play a determining role in the switching speed and losses.<sup>104</sup> Reliability and robustness are also important aspects of these devices and work in this areas is increasing with reports looking at their avalanche and short circuit robustness,<sup>105–107</sup> gate reliability and stability,<sup>108</sup> as well as the cosmic ray robustness.<sup>109</sup>

A recent example illustrates valuable robustness characteristics enabled by multidimensional device architectures where a GaN Fin-JFET was used as an avalanche GaN transistor.<sup>78</sup> Its avalanche current could flow either through the p-type gate or the n-type fin, depending on whether the gate was off or on.<sup>110</sup> With the gate on, GaN Fin-JFET shows a unique short-circuit capability at breakdown voltage,<sup>105</sup> and it fails with an open-circuit signature due to the spatial separation of electric field and current stresses, which is desirable for module and circuit safety.<sup>106</sup> By contrast, most other types of power transistors fail short-circuit and cannot survive the concurrence of avalanche and short-circuit currents.

While multidimensional devices offer a breakthrough trade-off between the power capacity and frequency, the driving circuitry and heat extraction are key to exploiting their full capabilities in power electronics systems. To minimize circuit parasitics and allow for high-temperature operation, monolithic WBG/UWBG integrated circuits (ICs) are desirable for device drive and control.<sup>111–113</sup> Power devices and ICs could also share the same multidimensional device platform. For example, Intel recently demonstrated the monolithic integration of GaN power FinFETs and GaN NMOS FinFETs, where the latter is 3D stacked with a Si PMOS FinFET to form GaN-Si CMOS for driving circuitry.<sup>114</sup> Finally, due to a higher power density, the device packaging and thermal management will be important, and a device-package, electrothermal co-design would be beneficial.

## Acknowledgment

Y.Z. acknowledges support from the National Science Foundation (grants ESSC-2036740 and ESSC-2045001). F.U. acknowledges support from the Engineering and Physical Science Research Council (grant EP/W007614/1). H.W. acknowledges support from the National Science Foundation (grant ESSC-2036915). We thank Prof. Dushan Boroyevich and Prof. Khai Ngo at Virginia Tech for valuable feedback on the manuscript. We thank the support by Ming Xiao for designing Figs. 1, 4, 5, Xiaodong Yan for designing Fig. 3, and Hengyu Wang for designing Fig. 1.

#### **Author Contributions**

Y.Z., F.U. and H.W. conceived the concepts and perspectives in this article together and co-wrote the manuscript.

# **Competing interests**

The authors declare no competing financial or non-financial interest.

#### Reference

- 1. Baliga, B. J. Fundamentals of Power Semiconductor Devices. (Springer Science & Business Media, 2010).

- 2. She, X., Huang, A. Q., Lucía, Ó. & Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. *IEEE Transactions on Industrial Electronics* 64, 8193–8205 (2017).

- 3. Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. *Jpn. J. Appl. Phys.* **54**, 040103 (2015).

- Jones, E. A., Wang, F. F. & Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. *IEEE Journal of Emerging and Selected Topics in Power Electronics* 4, 707–719 (2016).

- 5. Amano, H. et al. The 2018 GaN power electronics roadmap. J. Phys. D: Appl. Phys. 51, 163001 (2018).

- 6. Chen, K. J. et al. GaN-on-Si Power Technology: Devices and Applications. *IEEE Transactions on Electron Devices* 64, 779–795 (2017).

- 7. Tsao, J. Y. *et al.* Ultrawide-Bandgap Semiconductors: Research Opportunities and Challenges. *Advanced Electronic Materials* **4**, 1600501 (2018).

- 8. Green, A. J. et al. β-Gallium oxide power electronics. APL Materials 10, 029201 (2022).

- 9. Kaplar, R. J. et al. Review—Ultra-Wide-Bandgap AlGaN Power Electronic Devices. ECS J. Solid State Sci. Technol. 6, Q3061 (2016).

- 10. Donato, N., Rouger, N., Pernot, J., Longobardi, G. & Udrea, F. Diamond power devices: state of the art, modelling, figures of merit and future perspective. *Journal of Physics D: Applied Physics* 53, 093001 (2020).

- 11. Udrea, F., Deboy, G. & Fujihira, T. Superjunction Power Devices, History, Development, and Future Prospects. *IEEE Transactions on Electron Devices* **64**, 720–734 (2017).

- 12. Baliga, B. J. Semiconductors for high-voltage, vertical channel field-effect transistors. *Journal of Applied Physics* **53**, 1759–1764 (1982).

- 13. Cooper, J. A. & Morisette, D. T. Performance Limits of Vertical Unipolar Power Devices in GaN and 4H-SiC. *IEEE Electron Device Letters* **41**, 892–895 (2020).

- 14. Hudgins, J. L., Simin, G. S., Santi, E. & Khan, M. A. An assessment of wide bandgap semiconductors for power devices. *IEEE Transactions on Power Electronics* **18**, 907–914 (2003).

- 15. Liu, G., Tuttle, B. R. & Dhar, S. Silicon carbide: A unique platform for metal-oxide-semiconductor physics. *Applied Physics Reviews* **2**, 021307 (2015).

- 16. Ji, D. *et al.* Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of large-area devices. in 2017 IEEE International Electron Devices Meeting (IEDM) 9.4.1-9.4.4 (2017). doi:10.1109/IEDM.2017.8268359.

- Tanaka, R., Takashima, S., Ueno, K., Matsuyama, H. & Edo, M. Demonstration of 1200 V / 1.4 mΩ cm<sup>2</sup> vertical GaN planar MOSFET fabricated by an all ion implantation process. *Jpn. J. Appl. Phys.* 59, SGGD02 (2020).

- 18. Nakamura, T. *et al.* High performance SiC trench devices with ultra-low ron. in 2011 International *Electron Devices Meeting* 26.5.1-26.5.3 (2011). doi:10.1109/IEDM.2011.6131619.

- 19. Zhang, Y. & Palacios, T. (Ultra)Wide-Bandgap Vertical Power FinFETs. *IEEE Transactions on Electron Devices* 67, 3960–3971 (2020).

- 20. Kaminski, N. & Hilt, O. SiC and GaN devices-wide bandgap is not all the same. *IET Circuits, Devices & Systems* 8, 227-236 (2014).

- 21. Saito, W., Omura, I., Ogura, T. & Ohashi, H. Theoretical limit estimation of lateral wide band-gap semiconductor power-switching device. *Solid-State Electronics* **48**, 1555–1562 (2004).

- 22. Ma, Y. et al. Tri-gate GaN junction HEMT. Appl. Phys. Lett. 117, 143506 (2020).

- 23. Zhang, Y. *et al.* Electrothermal Simulation and Thermal Performance Study of GaN Vertical and Lateral Power Transistors. *IEEE Transactions on Electron Devices* **60**, 2224–2230 (2013).

- 24. Williams, R. K. *et al.* The Trench Power MOSFET: Part I—History, Technology, and Prospects. *IEEE Transactions on Electron Devices* **64**, 674–691 (2017).

- 25. Palmour, J. W. *et al.* Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV. in 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD) 79–82. doi:10.1109/ISPSD.2014.6855980.

- 26. Oka, T. Recent development of vertical GaN power devices. Jpn. J. Appl. Phys. 58, SB0805 (2019).

- 27. Li, W. *et al.* Single and multi-fin normally-off Ga2O3 vertical transistors with a breakdown voltage over 2.6 kV. in *2019 IEEE International Electron Devices Meeting (IEDM)* 12.4.1-12.4.4 (2019). doi:10.1109/IEDM19573.2019.8993526.

- Bhattacharyya, A. *et al.* Multi-kV Class β-Ga<sub>2</sub>O<sub>3</sub> MESFETs With a Lateral Figure of Merit Up to 355 MW/cm<sup>2</sup>. *IEEE Electron Device Letters* 42, 1272–1275 (2021).

- 29. Wu, Y. *et al.* More Than 3000 V Reverse Blocking Schottky-Drain AlGaN-Channel HEMTs With >230 MW/cm<sup>2</sup> Power Figure-of-Merit. *IEEE Electron Device Lett.* **40**, 1724–1727 (2019).

- 30. Abid, I. *et al.* Remarkable Breakdown Voltage on AlN/AlGaN/AlN double heterostructure. in 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD) 310–312. doi:10.1109/ISPSD46842.2020.9170170.

- 31. Kitabayashi, Y. *et al.* Normally-Off C–H Diamond MOSFETs With Partial C–O Channel Achieving 2-kV Breakdown Voltage. *IEEE Electron Device Letters* **38**, 363–366 (2017).

- 32. Iwasaki, T. *et al.* 600 V Diamond Junction Field-Effect Transistors Operated at 200 °C. *IEEE Electron Device Letters* **35**, 241–243 (2014).

- Masuda, T., Saito, Y., Kumazawa, T., Hatayama, T. & Harada, S. 0.63 mΩ·cm<sup>2</sup> / 1170 V 4H-SiC Super Junction V-Groove Trench MOSFET. in 2018 IEEE International Electron Devices Meeting (IEDM) 8.1.1-8.1.4 (2018). doi:10.1109/IEDM.2018.8614610.

- Baba, M. et al. Ultra-Low Specific on-Resistance Achieved in 3.3 kV-Class SiC Superjunction MOSFET. in 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD) 83–86 (2021). doi:10.23919/ISPSD50666.2021.9452273.

- 35. Kosugi, R. *et al.* Breaking the Theoretical Limit of 6.5 kV-Class 4H-SiC Super-Junction (SJ) MOSFETs by Trench-Filling Epitaxial Growth. in 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD) 39–42 (2019). doi:10.1109/ISPSD.2019.8757632.

- 36. Nela, L. *et al.* Multi-channel nanowire devices for efficient power conversion. *Nat Electron* **4**, 284–290 (2021).

- Xiao, M. *et al.* Multi-Channel Monolithic-Cascode HEMT (MC2-HEMT): A New GaN Power Switch up to 10 kV. in 2021 IEEE International Electron Devices Meeting (IEDM) 5.5.1-5.5.4 (2021). doi:10.1109/IEDM19574.2021.9720714.

- 38. Zhang, Y. *et al.* GaN FinFETs and trigate devices for power and RF applications: review and perspective. *Semicond. Sci. Technol.* **36**, 054001 (2021).

- 39. Kato, T. *et al.* Enhanced Performance of 50 nm Ultra-Narrow-Body Silicon Carbide MOSFETs based on FinFET effect. in 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD) 62–65 (2020). doi:10.1109/ISPSD46842.2020.9170182.

- 40. Udrea, F. *et al.* The FinFET effect in Silicon Carbide MOSFETs. in 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD) 75–78 (2021). doi:10.23919/ISPSD50666.2021.9452282.

- 41. Ramamurthy, R. P., Islam, N., Sampath, M., Morisette, D. T. & Cooper, J. A. The Tri-Gate MOSFET: A New Vertical Power Transistor in 4H-SiC. *IEEE Electron Device Letters* **42**, 90–93 (2021).

- 42. Udrea, F. *et al.* Experimental demonstration, challenges, and prospects of the vertical SiC FinFET. in 2022 34rd International Symposium on Power Semiconductor Devices and ICs (ISPSD) 253–256 (2022). doi: 10.1109/ISPSD49238.2022.9813617.

- 43. Ma, J. et al. 1200 V Multi-Channel Power Devices with 2.8 Ω•mm ON-Resistance. in 2019 IEEE International Electron Devices Meeting (IEDM) 4.1.1-4.1.4 (2019). doi:10.1109/IEDM19573.2019.8993536.

- 44. Liu, J. *et al.* 1.2-kV Vertical GaN Fin-JFETs: High-Temperature Characteristics and Avalanche Capability. *IEEE Transactions on Electron Devices* **68**, 2025–2032 (2021).

- 45. Disney, D. & Dolny, G. JFET Depletion in SuperJunction Devices. in 2008 20th International Symposium on Power Semiconductor Devices and IC's (ISPSD) 157–160 (2008). doi:10.1109/ISPSD.2008.4538922.

- 46. Kang, H. & Udrea, F. True Material Limit of Power Devices -Applied to 2-D Superjunction MOSFET. *IEEE Transactions on Electron Devices* **65**, 1432–1439 (2018).

- 47. Kang, H. & Udrea, F. Theory of 3-D Superjunction MOSFET. *IEEE Transactions on Electron Devices* 66, 5254–5259 (2019).

- 48. Deboy, G. *et al.* A new generation of high voltage MOSFETs breaks the limit line of silicon. in 1998 IEEE International Electron Devices Meeting (IEDM) 683–685 (1998). doi:10.1109/IEDM.1998.746448.

- Lorenz, L., Deboy, G., Knapp, A. & Marz, M. COOLMOS<sup>TM</sup>-a new milestone in high voltage power MOS. in *1999 11th International Symposium on Power Semiconductor Devices and IC's (ISPSD)* 3–10 (1999). doi:10.1109/ISPSD.1999.764028.

- 50. Hattori *et al.* Design of a 200V super junction MOSFET with n-buffer regions and its fabrication by trench filling. in 2004 16th International Symposium on Power Semiconductor Devices and IC's (ISPSD) 189–192 (2004). doi:10.1109/WCT.2004.239903.

- Zhong, X., Wang, B. & Sheng, K. Design and experimental demonstration of 1.35 kV SiC super junction Schottky diode. in 2016 28th International Symposium on Power Semiconductor Devices and IC's (ISPSD) 231–234 (2016). doi:10.1109/ISPSD.2016.7520820.

- 52. Wang, H., Wang, C., Wang, B., Ren, N. & Sheng, K. 4H-SiC Super-Junction JFET: Design and Experimental Demonstration. *IEEE Electron Device Letters* **41**, 445–448 (2020).

- 53. Fujihira, T. Theory of semiconductor superjunction devices. Jpn. J. Appl. Phys. 36 6254 (1997).

- 54. Kang, H., Lee, J., Lee, K. & Choi, Y. Trench angle: a key design factor for a deep trench superjunction MOSFET. *Semicond. Sci. Technol.* **30**, 125008 (2015).

- 55. Chen, X.-B. & Sin, J. K. O. Optimization of the specific on-resistance of the COOLMOS<sup>™</sup>. *IEEE Transactions on Electron Devices* **48**, 344–348 (2001).

- 56. Saito, W. Comparison of theoretical limits between superjunction and field plate structures. in 2013 25th International Symposium on Power Semiconductor Devices IC's (ISPSD) 241–244 (2013). doi:10.1109/ISPSD.2013.6694461.

- 57. Saito, W. Theoretical limits of superjunction considering with charge imbalance margin. in 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD) 125–128 (IEEE, 2015). doi:10.1109/ISPSD.2015.7123405.

- 58. Kang, H. & Udrea, F. Material Limit of Power Devices—Applied to Asymmetric 2-D Superjunction MOSFET. *IEEE Transactions on Electron Devices* **65**, 3326–3332 (2018).

- 59. Harada, S. *et al.* First Demonstration of Dynamic Characteristics for SiC Superjunction MOSFET Realized using Multi-epitaxial Growth Method. in *2018 IEEE International Electron Devices Meeting (IEDM)* 8.2.1-8.2.4 (2018). doi:10.1109/IEDM.2018.8614670.

- 60. Udrea, F., Popescu, A. & Milne, W. I. 3D RESURF double-gate MOSFET: a revolutionary power device concept. *Electronics Letters* **34**, 808–809 (1998).

- 61. Udrea, F. *et al.* Ultra-high voltage device termination using the 3D RESURF (super-junction) concept experimental demonstration at 6.5 kV. in 2001 13th International Symposium on Power Semiconductor Devices IC's (ISPSD) 129–132 (2001). doi:10.1109/ISPSD.2001.934573.

- 62. Ishida, H. *et al.* GaN-based natural super junction diodes with multi-channel structures. in 2008 *IEEE International Electron Devices Meeting* 1–4 (2008). doi:10.1109/IEDM.2008.4796636.

- 63. Cao, Y. *et al.* MBE growth of high conductivity single and multiple AlN/GaN heterojunctions. *Journal of Crystal Growth* **323**, 529–533 (2011).

- 64. Xiao, M. *et al.* 3.3 kV Multi-Channel AlGaN/GaN Schottky Barrier Diodes With P-GaN Termination. *IEEE Electron Device Letters* **41**, 1177–1180 (2020).

- 65. Lingaparthi, R. *et al.* Source of two-dimensional electron gas in unintentionally doped AlGaN/GaN multichannel high-electron-mobility transistor heterostructures. *Appl. Phys. Lett.* **118**, 122105 (2021).

- 66. Heikman, S., Keller, S., Green, D. S., DenBaars, S. P. & Mishra, U. K. High conductivity modulation doped AlGaN/GaN multiple channel heterostructures. *Journal of Applied Physics* **94**, 5321–5325 (2003).

- 67. Nela, L., Xiao, M., Zhang, Y. & Matioli, E. A perspective on multi-channel technology for the next-generation of GaN power devices. *Appl. Phys. Lett.* **120**, 190501 (2022).

- 68. Xiao, M., Ma, Y., Liu, K., Cheng, K. & Zhang, Y. 10 kV, 39 mΩ·cm2 Multi-Channel AlGaN/GaN Schottky Barrier Diodes. *IEEE Electron Device Letters* **42**, 808–811 (2021).

- 69. Ma, J., Kampitsis, G., Xiang, P., Cheng, K. & Matioli, E. Multi-Channel Tri-Gate GaN Power Schottky Diodes With Low ON-Resistance. *IEEE Electron Device Letters* **40**, 275–278 (2019).

- Xiao, M. et al. 5 kV Multi-Channel AlGaN/GaN Power Schottky Barrier Diodes with Junction-Fin-Anode. in 2020 IEEE International Electron Devices Meeting (IEDM) 5.4.1-5.4.4 (2020). doi:10.1109/IEDM13553.2020.9372025.

- Nakajima, A., Sumida, Y., Dhyani, M. H., Kawai, H. & Narayanan, E. M. S. GaN-Based Super Heterojunction Field Effect Transistors Using the Polarization Junction Concept. *IEEE Electron Device Letters* 32, 542–544 (2011).

- Howell, R. S. *et al.* The Super-Lattice Castellated Field Effect Transistor (SLCFET): A novel high performance Transistor topology ideal for RF switching. in 2014 IEEE International Electron Devices Meeting 11.5.1-11.5.4 (2014). doi:10.1109/IEDM.2014.7047033.

- Raj, A. *et al.* GaN/AlGaN superlattice based E-mode p-channel MES-FinFET with regrown contacts and gt;50 mA/mm on-current. in 2021 IEEE International Electron Devices Meeting (IEDM) 5.4.1-5.4.4 (2021). doi:10.1109/IEDM19574.2021.9720496.

- 74. Hisamoto, D. et al. FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. *IEEE Transactions on Electron Devices* 47, 2320–2325 (2000).

- 75. Bohr, M. T. & Young, I. A. CMOS Scaling Trends and Beyond. *IEEE Micro* 37, 20–29 (2017).

- 76. Razavieh, A., Zeitzoff, P. & Nowak, E. J. Challenges and Limitations of CMOS Scaling for FinFET and Beyond Architectures. *IEEE Transactions on Nanotechnology* **18**, 999–1004 (2019).

- 77. Veliadis, V. 1200 V SiC vertical-channel-JFETs and cascode switches. *physica status solidi (a)* **206**, 2346–2362 (2009).

- Liu, J. et al. 1.2 kV Vertical GaN Fin JFETs with Robust Avalanche and Fast Switching Capabilities. in 2020 IEEE International Electron Devices Meeting (IEDM) 23.2.1-23.2.4 (2020). doi:10.1109/IEDM13553.2020.9372048.

- 79. Xiao, M., Gao, X., Palacios, T. & Zhang, Y. Leakage and breakdown mechanisms of GaN vertical power FinFETs. *Appl. Phys. Lett.* **114**, 163503 (2019).

- 80. Zhang, Y. et al. 1200 V GaN vertical fin power field-effect transistors. in 2017 IEEE International Electron Devices Meeting (IEDM) 9.2.1-9.2.4 (2017). doi:10.1109/IEDM.2017.8268357.

- 81. Zhang, Y. *et al.* Large-Area 1.2-kV GaN Vertical Power FinFETs With a Record Switching Figure of Merit. *IEEE Electron Device Letters* **40**, 75–78 (2019).

- Balestra, F., Cristoloveanu, S., Benachir, M., Brini, J. & Elewa, T. Double-gate silicon-on-insulator transistor with volume inversion: A new device with greatly enhanced performance. *IEEE Electron Device Letters* 8, 410–412 (1987).

- 83. Alsharef, M. A., Granzner, R. & Schwierz, F. Theoretical Investigation of Trigate AlGaN/GaN HEMTs. *IEEE Transactions on Electron Devices* **60**, 3335–3341 (2013).

- 84. Tamura, T., Kotani, J., Kasai, S. & Hashizume, T. Nearly Temperature-Independent Saturation Drain Current in a Multi-Mesa-Channel AlGaN/GaN High Electron Mobility Transistor. *Appl. Phys. Express* 1, 023001 (2008).

- 85. Lu, B., Matioli, E. & Palacios, T. Tri-Gate Normally-Off GaN Power MISFET. *IEEE Electron Device Letters* 33, 360–362 (2012).

- 86. Wu, C.-H. *et al.* Normally-Off Tri-Gate GaN MIS-HEMTs with 0.76 mΩ·cm<sup>2</sup> Specific On-Resistance for Power Device Applications. *IEEE Trans. Electron Devices* **66**, 3441–3446 (2019).

- 87. Ma, Y., Xiao, M., Du, Z., Wang, H. & Zhang, Y. Tri-Gate GaN Junction HEMTs: Physics and Performance Space. *IEEE Transactions on Electron Devices* 68, 4854–4861 (2021).

- Huang, A. Q. Power Semiconductor Devices for Smart Grid and Renewable Energy Systems. *Proceedings of the IEEE* 105, 2019–2047 (2017).

- 89. Xiong, Y., Sun, S., Jia, H., Shea, P. & John Shen, Z. New Physical Insights on Power MOSFET Switching Losses. *IEEE Transactions on Power Electronics* **24**, 525–531 (2009).

- 90. Li, X. et al. A SiC Power MOSFET Loss Model Suitable for High-Frequency Applications. *IEEE Transactions on Industrial Electronics* 64, 8268–8276 (2017).

- 91. Li, A. *et al.* Lattice-matched AlInN/GaN multi-channel heterostructure and HEMTs with low onresistance. *Appl. Phys. Lett.* **119**, 122104 (2021).

- Zhou, X., Howell-Clark, J. R., Guo, Z., Hitchcock, C. W. & Chow, T. P. Performance limits of vertical GaN of conventional doped pn and natural polarization superjunction devices. *Appl. Phys. Lett.* 115, 112104 (2019).

- 93. Huang, H., Cheng, J., Yi, B., Zhang, W. & Ng, W. T. A unified model for vertical doped and polarized superjunction GaN devices. *Appl. Phys. Lett.* **116**, 102103 (2020).

- 94. Kang, H. & Udrea, F. Static and Dynamic Figures of Merits (FOM) for Superjunction MOSFETs. in 2019 31st International Symposium on Power Semiconductor Devices and IC's (ISPSD) 319–322 (2019). doi:10.1109/ISPSD.2019.8757689.

- Chen, Y.-K., Sivananthan, A. & Chang, T.-H. Emerging High Power mm-Wave RF transistors. in 2020 IEEE/MTT-S International Microwave Symposium (IMS) 562–565 (2020). doi:10.1109/IMS30576.2020.9224064.

- Chen, B.-Y., Chen, K.-M., Chiu, C.-S., Huang, G.-W. & Chang, E. Y. High-frequency performances of superjunction laterally diffused metal–oxide–semiconductor transistors for RF power applications. *Jpn. J. Appl. Phys.* 55, 04ER09 (2016).

- 97. Chang, J. et al. The Super-Lattice Castellated Field-Effect Transistor: A High-Power, High-Performance RF Amplifier. *IEEE Electron Device Letters* **40**, 1048–1051 (2019).

- Afroz, S. *et al.* Diamond Superjunction (SJ) Process Development: Super-Lattice Power Amplifier with Diamond Enhanced Superjunction (SPADES). in 2019 IEEE BiCMOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS) 1–4 (2019). doi:10.1109/BCICTS45179.2019.8972725.

- Joglekar, S., Radhakrishna, U., Piedra, D., Antoniadis, D. & Palacios, T. Large signal linearity enhancement of AlGaN/GaN high electron mobility transistors by device-level Vt engineering for transconductance compensation. in 2017 IEEE International Electron Devices Meeting (IEDM) 25.3.1-25.3.4 (2017). doi:10.1109/IEDM.2017.8268457.

- Choi, W. *et al.* Intrinsically Linear Transistor for Millimeter-Wave Low Noise Amplifiers. *Nano* Lett. 20, 2812–2820 (2020).

- 101. Middleton, C. *et al.* Thermal Transport in Superlattice Castellated Field Effect Transistors. *IEEE Electron Device Letters* **40**, 1374–1377 (2019).

- 102. Cao, Y., Pomeroy, J. W., Uren, M. J., Yang, F. & Kuball, M. Electric field mapping of widebandgap semiconductor devices at a submicrometre resolution. *Nat Electron* **4**, 478–485 (2021).

- Zulauf, G. D., Roig-Guitart, J., Plummer, J. D. & Rivas-Davila, J. M. C<sub>OSS</sub> Measurements for Superjunction MOSFETs: Limitations and Opportunities. *IEEE Transactions on Electron Devices* 66, 578–584 (2019).

- 104. Wang, H., Xiao, M., Sheng, K., Palacios, T. & Zhang, Y. Switching Performance Analysis of Vertical GaN FinFETs: Impact of Interfin Designs. *IEEE Journal of Emerging and Selected Topics in Power Electronics* 9, 2235–2246 (2021).

- 105. Zhang, R. *et al.* Breakthrough Short Circuit Robustness Demonstrated in Vertical GaN Fin JFET. *IEEE Transactions on Power Electronics* **37**, 6253–6258 (2022).

- 106. Zhang, R. *et al.* Robust Through-Fin Avalanche in Vertical GaN Fin-JFET With Soft Failure Mode. *IEEE Electron Device Letters* **43**, 366–369 (2022).

- 107. Okada, M. et al. Superior Short-Circuit Performance of SiC Superjunction MOSFET. in 2020 32nd International Symposium on Power Semiconductor Devices and IC's (ISPSD) 70–73 (2020). doi:10.1109/ISPSD46842.2020.9170126.

- 108. Fabris, E. *et al.* Trapping and Detrapping Mechanisms in β-Ga<sub>2</sub>O<sub>3</sub> Vertical FinFETs Investigated by Electro-Optical Measurements. *IEEE Transactions on Electron Devices* **67**, 3954–3959 (2020).

- 109. Antoniou, M., Udrea, F. & Bauer, F. Robustness of SuperJunction structures against cosmic ray induced breakdown. *Solid-State Electronics* 54, 385–391 (2010).

- 110. Liu, J. et al. Tuning Avalanche Path in Vertical GaN JFETs By Gate Driver Design. *IEEE Transactions on Power Electronics* **37**, 5433–5443 (2022).

- 111. Alexandru, M. *et al.* SiC Integrated Circuit Control Electronics for High-Temperature Operation. *IEEE Transactions on Industrial Electronics* **62**, 3182–3191 (2015).

- 112. Zheng, Z. *et al.* Gallium nitride-based complementary logic integrated circuits. *Nat Electron* **4**, 595–603 (2021).

- 113. Bader, S. J. et al. Prospects for Wide Bandgap and Ultrawide Bandgap CMOS Devices. *IEEE Transactions on Electron Devices* 67, 4010–4020 (2020).

- 114. Then, H. W. et al. Advanced Scaling of Enhancement Mode High-K Gallium Nitride-on-300mm-Si(111) Transistor and 3D Layer Transfer GaN-Silicon Finfet CMOS Integration. in 2021 IEEE International Electron Devices Meeting (IEDM) 11.1.1-11.1.4 (2021). doi:10.1109/IEDM19574.2021.9720710.

**Figure 1** | **Power capacity and frequency trade-off of 1D and multidimensional power devices.** The schematic of thyristor, IGBT, vertically-diffused MOSFET (VDMOS) and laterally-diffused MOSFET (LDMOS) are shown in the left portion of the figure. The red line illustrates the approximate limit of 1D power devices. The schematic of a superjunction, multi-channel cascode transistor, Fin-MOSFET and trigate HEMT are presented in the middle portion of the figure. The n-type and p-type semiconductors, oxide, and metal are plotted in orange, blue, green and yellow, respectively. The circle symbols represent electrodes. The cross-sectional scanning electron microscopy (SEM) images of a Si superjunction MOSFET, GaN multi-channel transistor, SiC Fin-MOSFET and GaN trigate HEMT are presented in the right portion of the figure. The bandgaps of Si, WBG and UWBG semiconductor are illustrated in the top panel. The multidimensional architectures are material agnostic; their implementations in WBG and UWBG materials can bring advances over the limit of 1D devices. SEM images adapted with permission from: ref. 11, © 2017 IEEE; ref. 37, @ 2021 IEEE; ref. 40, @ 2021 IEEE; ref. 22, @ 2020 AIP.

Figure 2 | Specific on-resistance and breakdown voltage trade-off of 1D and multidimensional power devices. a,  $R_{ON,SP} \sim BV$  trade-off of the state-of-the-art Si MOSFETs, SiC MOSFETs, GaN MOSFETs, GaN HEMTs, Ga<sub>2</sub>O<sub>3</sub> MOSFETs, AlN/AlGaN HEMTs and diamond MOSFETs. 1D limits of Si, WBG and UWBG vertical unipolar devices and GaN lateral HEMTs are also plotted. The device data are collected from (5, 16-17, 24-32). b,  $R_{ON,SP} \sim BV$  trade-off of the state-of-the-art Si and WBG multidimensional devices. The device data are collected from (19, 33-37, 42-44). The four bands illustrate the performance limits of Si and WBG superjunction devices, WBG multi-channel devices, as well as WBG FinFETs and trigate devices. The geometrical scaling in these multidimensional architectures results in a band of theoretical limits beyond the limit lines of 1D power devices.

**Figure 3** | **Superjunction power devices. a**, schematic of the 1D drift region, 2D superjunction and cylindrical superjunction. The electric field distribution along the thickness direction is illustrated for three drift region designs. **b**, two implementations of the 2D superjunction trench MOSFET. The superjunction pillars can be parallel to the trench width or perpendicular to it. **c**, cross-sectional microscopic images of a Si superjunction (left) and a SiC superjunction (right). **d**, exploded views of two implementations of the 3D superjunction trench MOSFET. The left device shows a nanowire-style implementation of n-pillars in the superjunction, a honeycomb channel unit-cell, and a current spreading layer in between. The channel unit-cell can be larger than the superjunction unit-cell, and the current spreading layer connects all n-type nanowires to the gated channel. The right device shows a nanomesh, shell-style implementation of n-pillars in the superjunction and a honeycomb channel unit-cell. Figure adapted with permission from: **c**, ref. 11, © 2017 IEEE; ref. 59, @ 2018 IEEE.

**Figure 4** | **Multi-channel heterostructures and multi-channel power HEMTs. a**, Illustration of an undoped multi-channel with balanced polarization charges (Pr) in the forward conduction state, in which alternative pairs of 2DEG and 2DHG are formed. **b**, Illustration of an undoped multi-channel with balanced polarization charges in the high-voltage blocking state, forming a polarization superjunction. **c**, Illustration of a doped multi-channel in the blocking state, on top of which a p-GaN RESURF layer provides charges to balance the net donors in the multi-channel. **d**, Simulated electric field contours in two undoped multi-channel with and without balanced polarization charges as well as a doped multi-channel with the p-GaN RESURF structure, all at a high blocking voltage. The lateral electric field distribution is schematically illustrated below each structure. **e**, Schematic of a multi-channel trigate HEMTs with a slanted trigate design. **f**, Schematic, top-view SEM image, and the equivalent circuit model of a multi-channel monolithic-cascode HEMT, in which the multi-channel gate (MC-gate) is connected to the source. Off-state current-voltage characteristics of devices with different multi-channel lengths (*L*), showing the scalability of *BV* to over 10 kV. Figure adapted with permission from: **d**, ref. 68, @ 2021 IEEE; **e**, ref. 36, Nature Publishing Group; **f**, ref. 37, @ 2021 IEEE.

**Figure 5** | **Power FinFETs and trigate HEMTs covering a broad range of the fin dimension.** Power FinFETs with a bulk fin body are presented on top of the scale bar. The schematic and channel carrier profile of trigate MOSFET, Fin-JFET, junctionless Fin-MOSFET, and ultra-narrow-body Fin-MOSFET are shown from left to right. Trigate HEMTs with a hetero-structural fin body are presented below the scale bar. The schematic and channel carrier profile of trigate junction HEMT, trigate MOS-HEMT, and multi-channel trigate MOS-HEMT are shown from left to right. The approximate fin width range experimentally demonstrated in each device is indicated using colored curly brackets.

| drift region design               | 1D                                                  | 2D superjunction                                  | 3D superjunction                                       | multi-channel (PSJ)                                           |

|-----------------------------------|-----------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|

| structure                         | 784, 784,<br>                                       | n p                                               | p n Kg                                                 | ₩ <u></u><br>                                                 |

| performance limit                 | $R_{on,sp} = \frac{4}{\varepsilon \mu E_c^3} B V^2$ | $R_{on,sp} = \frac{4d}{\varepsilon \mu E_c^2} BV$ | $R_{on,sp} = \frac{r}{\beta \varepsilon \mu E_c^2} BV$ | $R_{on,sp} = \frac{BV^2}{NqE_c^2 n_{2D} \sum_{e,h} \mu_{2D}}$ |

| scaling parameter                 | N/A                                                 | cell pitch (d)                                    | radius ( $r$ ), radius ratio ( $\beta$ )               | channel number (N)                                            |

| scaling limit                     | N/A                                                 | $d = \frac{50E_g}{9qE_c}$                         | $r = \frac{98\sqrt{2}E_g\beta}{27qE_c}$                | process- and technology-<br>related                           |

| minimum specific<br>on-resistance | $\frac{4BV^2}{\varepsilon\mu E_c^3}$                | $\frac{20E_gBV}{q\varepsilon\mu E_c^3}$           | $\frac{16E_gBV}{q\epsilon\mu E_c^3}$                   |                                                               |

| material<br>figure-of-merit       | $\varepsilon \mu E_C^3$                             | $arepsilon\mu E_{C}^{2.5}$                        | $\varepsilon\mu E_c^{2.5}$                             | $E_C^2 n_{2D} \sum_{e,h} \mu_{2D}$                            |

$\varepsilon$ : permittivity.  $\mu$ : mobility of the major carrier.  $E_C$ : critical electric field.  $n_{2D}$ : 2DEG or 2DHG density.  $\mu_{2D}$ : 2DEG or 2DHG mobility.  $E_g$ : bandgap. PSJ: polarization superjunction.