# **MULTILEVEL INVERTER WITH LEVEL SHIFTING SPWM TECHNIQUE USING** FEWER NUMBER OF SWITCHES FOR SOLAR APPLICATIONS

Mahajan Sagar Bhaskar Ranjana<sup>1</sup>, Pandav Kiran Maroti<sup>2</sup>, Ruchita Maheshwari<sup>3</sup>, Pachagade Ruchi M.<sup>4</sup>

<sup>1,2,3,4</sup>Department of Electrical and Electronics Engineering Marathwada Institute of Technology (MIT), Aurangabad, INDIA- 431028

sagar25.mahajan@gmail.com<sup>1</sup>, kiranpandav88@yahoo.co.in<sup>2</sup>, rchitadahad@gmail.com<sup>3</sup>, ruchi.pachagade@gmail.com<sup>4</sup>

### Abstract

A multilevel inverter (MLI) is a popular inverter for solar based high power applications. The drawback of conventional H-bridge inverter is non-sinusoidal output voltage, which reduces the output quality of inverter. Later, the drawback of conventional Hbridge was overcome by conventional MLI. But, conventional MLI needs maximum number of diodes and switches. In order to overcome this drawback proposed MLI topology with level shifting sinusoidal pulse width modulation (SPWM) technique can be employed. Proposed MLI contain fewer number of switches and diodes, which helps in optimizing the circuit layout, reducing gate driver circuit for those switches. SPWM technique uses multicarrier waveforms with level shifting ensuring the reduction in total harmonics distortion (THD). In this Paper level shifting SPWM technique has been incorporated in which 5 kHz carrier wave is compare with 50Hz of sinusoidal wave with a modulation index of 0.8. THD of proposed 9-level inverter is 17.27% without filter and 4.29% with LC filter. Simulation of proposed inverter is carried out in MATLAB/SIMULINK.

Key Words: Solar, 9-level inverter, Level shifting SPWM, Power diodes and switches, Total Harmonics Distortion (THD)

\*\*\*

## 1. INTRODUCTION

Renewable energy sources have gained wide importance due to the depletion of fossil fuels. Also the problem of pollution caused by fossil fuels can be solved by using clean and freely available renewable energy. Solar energy is one of the renewable energy in which most of the researchers are showing interests as it can be responsible for green energy concept.

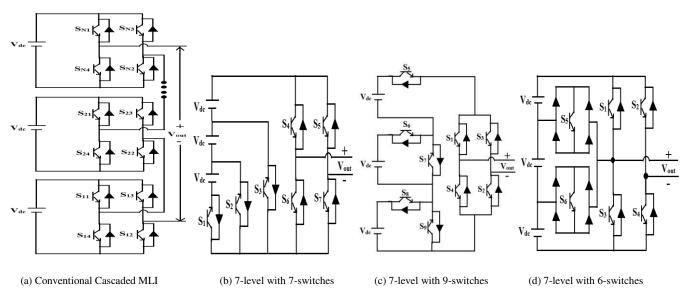

In case of solar energy system, voltage generated from solar array is needed to be converted into ac signal for high power AC application. Conventional H-bridge inverter is not a practical solution for DC-AC conversion because of large harmonics distortion and switching losses. Later, the drawbacks of conventional inverter are overcome by multilevel inverter (MLI) [1]-[2]. The increased number of level reduces the harmonic content and brings the output voltage waveform closer to sinusoidal. Conventional MLI include diode clamped, flying capacitors and cascaded Hbridge. In diode clamped MLI, diodes are used in majority and number of diode increases with increase in levels. In flying capacitor MLI, number of capacitor is increases with increase in levels. In cascaded MLI, as the cascade stage increases, certainly the number of switches and sources also increases [3]-[6]. In Fig.1 (a), cascaded MLI for N-stages is shown. But, these conventional MLI's requires large number of power devices to generate maximum number of levels. Further, this drawback is overcome by modifying the conventional MLI's circuits. Diode clamped MLI has been discussed with lesser number of diodes in [7]. Modified flying capacitor topology is discussed in [8]. In [9], cascade MLI topology with reduced number of switches is discussed. In [10]-[12], 7-level inverter using 7 switches and 9 switches has been discussed. In Fig.1 (b) and Fig.1 (c), 7level with 9-switches and 7-level with 7-switches are shown respectively. In [13], 7-level with 6-switches MLI is explained. In Fig.1 (d), the schematic of 7-level with 6switches MLI is shown. In [13], though the number of switches is less; but the number of diodes increases with number of levels. The above discussed MLI's gives more number of levels as compared to conventional MLI using minimum number of switches. In the above topology, the emphasis is on minimizing the number of switches but it still requires large number of voltage sources. This drawback is overcome by advanced MLI [14] and asymmetrical MLI. Single phase MLI with single PV source and less number of switches is proposed in [15]. The drawback of advance MLI is that it requires inductor and a switch operating at high frequency. The cost and design complexity of advance MLI is increased due to the use of inductor.

Generally, asymmetrical multilevel inverters are used to increase the number of levels. In [16], 25-level asymmetrical inverter with 12 switches for renewable power grid applications is proposed. In [17], 25-level asymmetrical inverter with 10 switches for solar application is proposed. In [18], modified cascaded H-bridge inverter is proposed with three different algorithms to generate 9, 13 and 17 levels. It is observed that THD for 9-level, 13-level and 17level inverter without filter is 17.22%, 10.74% and 7.76% respectively. Also the THD for 9-level, 13-level and 17level inverter with filter is 5.86%, 5.18% and 4.71% respectively.

Asymmetric multilevel inverter is more advantageous than symmetric multilevel inverter in obtaining more number of output levels using same number of voltage sources. But the main drawback of asymmetrical inverter is that it increases the complexity of gate triggering pulses. The other drawback is that the required rating of the power devices is not same. Due to complexity of gate triggering pulses asymmetrical MLI's are not beneficial to use. The proposed MLI requires fewer number of power devices and nearly removes all major above discussed drawbacks. In this paper, a novel 9-level MLI with 7-switches is proposed. The SPWM technique is used to reduce the THD and improve the quality of output voltage.

#### 2. PROPOSED TOPOLOGY

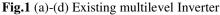

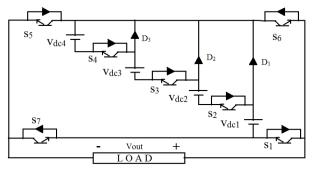

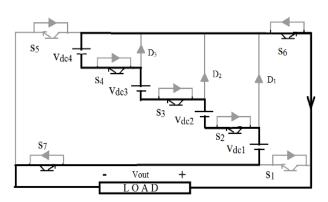

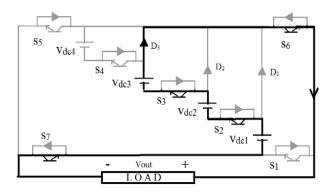

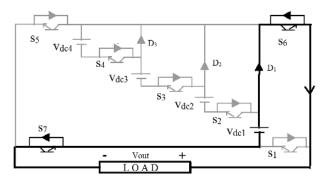

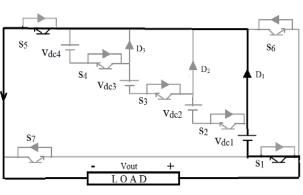

The proposed MLI is designed for 9-level using 7 switches as shown below in Fig. 2. This topology is modification of conventional H-bridge inverter where number of levels can be increased by stacking specific combination of diode, switch and voltage source. Switches  $S_1$ ,  $S_5$ ,  $S_6$  and  $S_7$ represent H-bridge in which  $S_1$ ,  $S_5$  are used for generating negative voltage levels whereas  $S_6$ ,  $S_7$  are used for positive voltage levels. In addition switches  $S_2$ ,  $S_3$  and  $S_4$  are used to increase the number of levels. The proposed scheme 9-level inverter requires 7-switches, 3-diodes and 4-voltage sources. Fig. 3 shows circuit diagram of N-level proposed MLI.

Fig.2 Circuit diagram of proposed 9- level inverter.

Fig.3 N-level proposed MLI.

The relationship between number of output levels, switches, diodes and voltage sources is stated in TABLE-I. It can be depicted that this topology is suitable only for odd number of output levels. (N+5)/2 switches with anti-parallel diodes, (N-3)/2 clamping diodes and (N-1)/2 sources are needed to design N-Level proposed inverter.

**Table-I** Relationship between number of output levels, switches, diodes and voltage sources

| No. of | No. of   | No. of          | No. of  |

|--------|----------|-----------------|---------|

| levels | switches | clamping diodes | sources |

| 3      | 4        | 0               | 1       |

| 5      | 5        | 1               | 2       |

| 7      | 6        | 2               | 3       |

| 9      | 7        | 3               | 4       |

| N      | (N+5)/2  | (N-3)/2         | (N-1)/2 |

#### **3. OPERATION OF PROPOSED TOPOLOGY**

The operation for 9-level MLI with 7-switches as shown in Fig. 2 is discussed below. Switches  $S_1$  and  $S_5$ ,  $S_6$  and  $S_7$  are complementary to each other.  $S_1$ ,  $S_5$  are turned 'ON' to generate negative output levels and  $S_6$ ,  $S_7$  are turned 'ON' to generate positive output levels. The switches  $S_2$ ,  $S_3$  and  $S_4$

are turned 'ON' and turned 'OFF' accordingly to increase the number of output levels.

| Voltage Levels             |   | $S_2$ | <b>S</b> <sub>3</sub> | $S_4$ | <b>S</b> <sub>5</sub> | <b>S</b> <sub>6</sub> | <b>S</b> <sub>7</sub> |

|----------------------------|---|-------|-----------------------|-------|-----------------------|-----------------------|-----------------------|

| $Vdc_4+Vdc_3+Vdc_2+Vdc_1$  |   | 1     | 1                     | 1     | 0                     | 1                     | 1                     |

| $Vdc_3+Vdc_2+Vdc_1$        |   | 1     | 1                     | 0     | 0                     | 1                     | 1                     |

| $Vdc_2+Vdc_1$              | 0 | 1     | 0                     | 0     | 0                     | 1                     | 1                     |

| Vdc <sub>1</sub>           | 0 | 0     | 0                     | 0     | 0                     | 1                     | 1                     |

| 0                          | 0 | 0     | 0                     | 0     | 0                     | 0                     | 0                     |

| -Vdc <sub>1</sub>          | 1 | 0     | 0                     | 0     | 1                     | 0                     | 0                     |

| $-Vdc_2-Vdc_1$             | 1 | 1     | 0                     | 0     | 1                     | 0                     | 0                     |

| $-Vdc_3-Vdc_2-Vdc_1$       | 1 | 1     | 1                     | 0     | 1                     | 0                     | 0                     |

| $-Vdc_4-Vdc_3-Vdc_2-Vdc_1$ |   | 1     | 1                     | 1     | 1                     | 0                     | 0                     |

**Table-II** Switching states with corresponding voltage levels

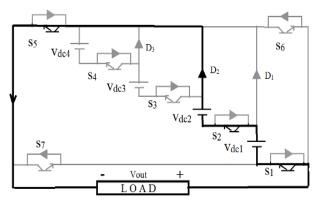

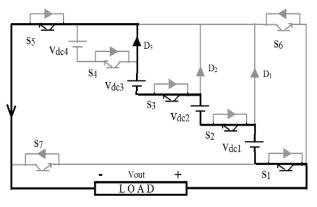

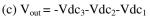

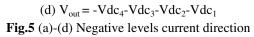

Switches S2, S3, and S4 are turned 'ON' when maximum positive and negative output level is required and are turned 'OFF' with corresponding levels as shown in TABLE-II. The current flow direction through the circuit for positive and negative voltage levels is shown in Fig.4 (a)-(d) and Fig.5 (a)-(d) respectively.

#### 3. SPWM TECHNIQUE FOR PROPOSED TOPOLOGY

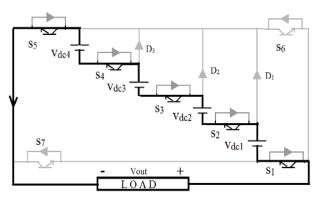

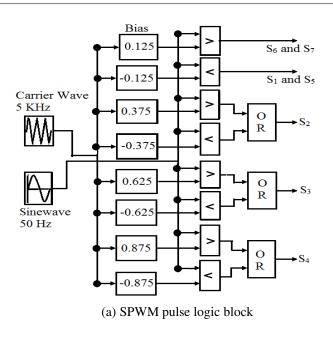

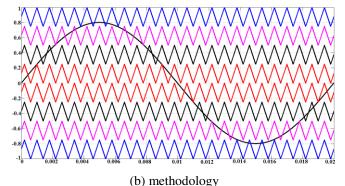

Sinusoidal pulse width modulation (SPWM) technique is used for pulse generation where reference wave is sinusoidal and carrier wave is high frequency triangular wave. The comparison of both these waves gives rise to the pulses to trigger the switches. Level shifting SPWM technique is employed in order to reduce THD. Multiple carrier waves are compared with single reference wave with 0.8 modulation index. Three schemes of level shifting SPWM involve phase disposition, phase opposition disposition and alternate phase opposition disposition. In this paper phase disposition has been used for the pulse generation for the proposed MLI.

Fig.6 (a) shows the internal circuitry of SPWM pulse logic block for 9-level proposed MLI. The internal circuitry of SPWM block contains bias, relational operator, followed by logic operators. The inputs for SPWM logic block are sinusoidal waveform and triangular waveform. Pulses are generated according to switching logic and amplitude modulation index. The methodology of generating pulses for 9-level MLI is shown in Fig.6 (b). Phase opposition disposition and alternate phase opposition disposition SPWM techniques are also suitable for proposed converter.

The modulation index for SPWM Technique is the ratio of Amplitude of reference wave  $(A_R)$  to the product of number of positive or negative level and amplitude of carrier wave  $(A_C)$ .

Modulation Index =

$$\frac{A_R}{\frac{(N-1)}{2} \times A_C}$$

(1)

(a)  $V_{out} = Vdc_4 + Vdc_3 + Vdc_2 + Vdc_1$

(c)  $V_{out} = Vdc_2 + Vdc_1$

(d) V<sub>out =</sub> Vdc1 Fig.4 (a)-(d) positive levels current direction

(b)  $V_{out} = -Vdc_2 - Vdc_1$

Fig.6 (a)-(b) methodology for generation of pulses.

#### 4. SIMULATION RESULTS

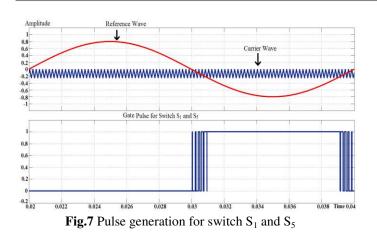

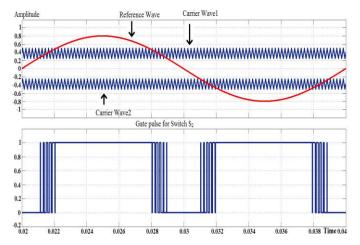

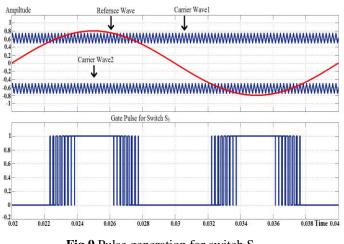

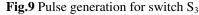

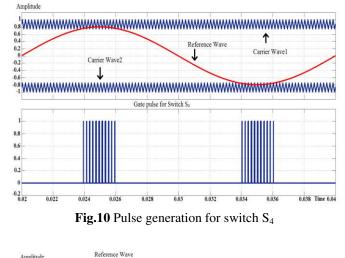

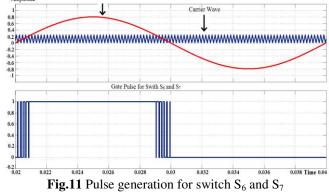

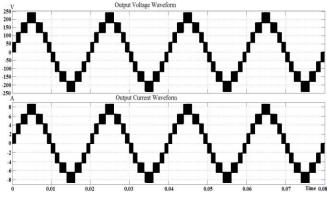

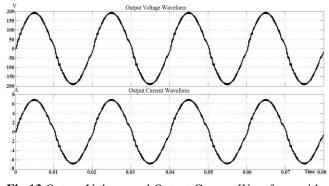

The proposed MLI has been designed for 2kW, 9-level output voltage using 7-switches for solar application. Four input voltage sources are used and each voltage source is equal to 60V. Phase disposition level shifting SPWM technique is used with 50 Hz reference sinusoidal wave and 5 KHz carrier wave with modulation index 0.8. The proposed 9-level inverter is designed with or without filter LC Filter. LC filter has been used with inductance of 0.5mH and capacitance of 15µF to reduce higher order harmonics. The simulation has been performed in MATLAB/SIMULINK. The switching pulse generation for switches S<sub>1</sub> and S<sub>5</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>6</sub> and S<sub>7</sub> has been shown in Fig.7 to Fig.11 respectively. It is observed that switches  $S_2$ , S<sub>3</sub> and S<sub>4</sub> required two carrier waveforms to obtain switching pulses whereas S1, S5, S6 and S7 required single carrier waveform. 9-level output voltage and output current waveforms without LC filter are shown in Fig.12. It is observed that 4 positive, 4 negative and 1 zero level is obtained with amplitude of each level is 60V. The highest positive level is 240V which is the positive addition of all input voltage sources. The highest negative level is -240V which is the negative addition of all input voltage sources. Fig.13 shows the output voltage and output current sinusoidal.

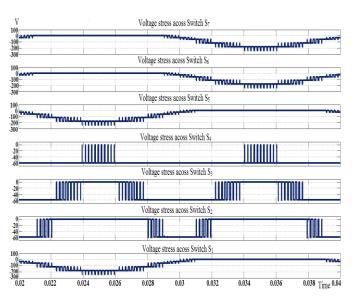

**Fig.8** Pulse generation for switch S<sub>2</sub>

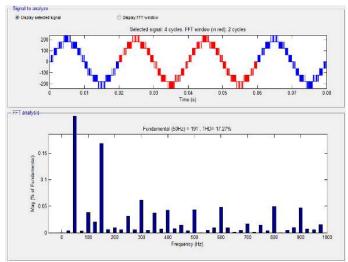

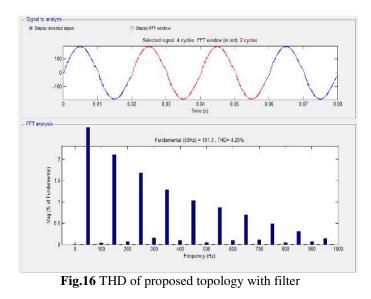

The voltage stress across each switch is shown in Fig.14. It is observed that the voltage stress across switches S1, S5, S6 and S7 is 240V which is equal to the addition of all input voltage source. The voltage stress across switches S2, S3 and S4 is 60V which is equal to single input voltage source. The THD of output voltage without filter is 17.27% which is calculated by using Fast Fourier Transform (FFT) analysis window shown in Fig.15. Afterwards, higher order harmonics are eliminated by using LC filter. Fig.16 shows the THD of filtered output is 4.29%.

Fig.12 Output Voltage and Output Current Waveform without filter

Fig.13 Output Voltage and Output Current Waveform with filter

Fig.14 Voltage stress across switches

Fig.15 THD of proposed topology without filter

5. COMPARISON OF PROPOSED MLI WITH

# CONVENTIONAL AND EXISTING MLI

Conventional MLI includes diode clamped, flying capacitors and cascaded MLI. Diode clamped MLI required more number of diodes and switches. Flying capacitor MLI required more number of clamping capacitors and switches. Cascaded MLI required separate DC source and more number of switches. Later the above discussed drawback is overcome by modifying conventional MLI. The proposed modified H-bridge cascaded MLI consists of fewer diodes than diode clamped MLI, fewer capacitors than flying capacitor MLI, fewer switches than conventional cascaded MLI. TABLE-III shows the comparison between diode clamped, flying capacitance, cascaded H-bridge MLI and proposed MLI, where N is the level generated by single phase MLI.

Table-III COMPARISON BETWEEN SINGLE PHASE MLI

| 14010                | Table-III Comparison Between Single Thase MEI |                                          |                                |                 |  |  |  |

|----------------------|-----------------------------------------------|------------------------------------------|--------------------------------|-----------------|--|--|--|

| MLI<br>Types         | Switches                                      | clamping and<br>anti- parallel<br>diodes | capacitor                      | source          |  |  |  |

| Diode<br>clamped     | 2(N-1)                                        | $\frac{N^2-1}{2}$                        | $\frac{N-1}{2}$                | 1               |  |  |  |

| Flying<br>Capacitor  | 2(N-1)                                        | 2(N-1)                                   | $\frac{\left(N-1\right)^2}{4}$ | 1               |  |  |  |

| Cascaded<br>H-Bridge | 2(N-1)                                        | 2(N-1)                                   | $\frac{N-1}{2}$                | $\frac{N-1}{2}$ |  |  |  |

| Proposed<br>MLI      | $\frac{N+5}{2}$                               | N+1                                      | $\frac{N-1}{2}$                | $\frac{N-1}{2}$ |  |  |  |

Fig.17 shows the graphs between required number of switches, diodes, capacitors and sources versus number of levels for proposed and conventional MLI. Proposed MLI reduces the complexity of circuit design and cost because less number of power devices required for designing the proposed MLI.

#### 6. CONCLUSION

In this paper, a new topology of Multilevel Inverter (MLI) with fewer number of switches is designed for solar applications which overcomes the drawbacks of conventional multilevel inverter. (N+5)/2 switches with antiparallel diodes, (N-3)/2 clamping diodes and (N-1)/2 sources are needed to design N-Level proposed inverter. The proposed MLI advantages include fewer number of switches which in turn reduced the corresponding gate driving circuitry, made the circuit compact in size. Due to which optimization of circuit layout is possible. The proposed MLI is designed for 9-level with power 2kW and In-Phase level shifting SPWM technique is used for the generate switching pulses for switches of the MLI. It is observed that output voltage total harmonics distortion (THD) of 9 level proposed MLI without filter is 17.27% whereas with filter is 4.29%. The simulation results and pulse generation using SPWM technique also discussed. The simulation results show that proposed MLI has the characteristics which are desirable for solar based high power applications.

#### REFERENCES

- J.S. Lai and F.Z. Peng, "Multilevel Converters- A new breed of power converters" IEEE transactions on industrial applications, Vol.32,pp.509-517, May-June1996.

- [2] Rodriguez. J; J. S. Lai; F. Z. Peng; "Multilevel Inverters: A Survey of Topologies, Controls and Applications" IEEE transactions on Industrial Electronics, Vol.49, No.4, August 2002.

- [3] Malinowski. M; Gopakumar. K; Rodriguez. J; Perez, M. A; "A survey on cascaded multilevel inverters", IEEE, Transactions on industrial electronics, Vol.57, 2009.

- [4] Wei Zhao; Hyuntae Choi; G. Konstantinou; M. Ciobotaru; and V.G. Agelidis "Cascaded H-bridge Multilevel Converter for Large-scale PV Grid-Integration with Isolated DC-DC stage" PEDG, IEEE 2012.

- [5] S. Rivera; S. Kouro; B. Wu; J. I. Leon; J. Rodriguez; and L. G. Franquelo "Cascaded H-bridge multilevel converter multistring topology for large scale photovoltaic systems," IEEE, ISIE 2011, pp.1837-1844.

- [6] B. Singh; N. Mittal; and K. S. Verma "Multi-Level Inverter: A Literature Survey On Topologies And Control Strategies", International Journal of Reviews in Computing, Vol. 10, July 2012, pp. 1-16

- [7] Zhiguo pan; F. Z. Peng; Victor Stefanoic and Mickey Leuthen "A Diode-Clamped Multilevel Converter with Reduced Number of Clamping Diodes." IEEE 2004.

- [8] N. Maheshkumar; V. Maheskumar; and M. Divya "The New Topology In Flying Capacitor Multilevel Inverter"

International Conference on Computer Communication and Informatics, IEEE-2013.

- [9] Ebrahim. Babaei "A Cascade Multilevel Converter Topology with Reduced Number of Switches" IEEE Transaction on Power Electronics, Vol. 23,issue 6, pp. 2657-2664, 2008.

- [10] T.v.v.s Lakshmi; Noby George; Umashankar. S and Kothari .D. P "Cascaded seven level inverter with reduced number of switches using level shifting PWM technique" ICPEC, IEEE 2013.

- [11] K.Gobinath, S.Mahendran, I.Gnanambal, "Novel cascaded H-Bridge Multilevel Inverter with harmonic elimination", IEEE International Conference on Green High Performance Computing ICGHPC, March 2013.

- [12] J. J. Nedumgatt; Vijayakumar; Kirubakarann. A; and Umashankar S; "A Multilevel Inverter with Reduced Number of Switches" Conference on Electrical, Electronics and Computer Science, IEEE 2012.

- [13] Nurul Aisyah Yusof; Norazliani Md Sapari; Hazlie Mokhlis; Jeyraj Selvaraj "A Comparative Study of 5level and 7-level Multilevel Inverter Connected to the Grid" international conference on power and energy, IEEE, PEcon, 2012.

- [14] Mahajan Sagar Bhaskar Ranjana, Nandyala Sreeramula Reddy, Repalle Kusala Pavan Kumar "A novel single phase advanced multilevel inverter with adjustable amplitude of voltage levels" IEEE International Conference on Circuit, Power and Computing Technologies, ICCPCT 2014, nagarcoil,

- [15] Mahajan Sagar Bhaskar Ranjana; Pandav Kiran Maroti; B. Sri Revathi; "A Novel Single Phase Multilevel Inverter with Single Photovoltaic Source and Less Number of switches" IEEE, International Conference On Devices, Circuits And Systems – ICDCS 2014, Coimbatore.

- [16] Mahajan Sagar Bhaskar; Kaustubh P. Draxe; Kiran M. Pandav "A Novel Asymmetric Multilevel Inverter with Minimum Number of Switches in Renewable Power Grid Applications" IEEE, International conference on Green Computing, Communication and Conservation of Energy, ICGCE-2013.

- [17] Kaustubh P. Draxe; Mahajan Sagar Bhaskar Ranjana; Kiran M. Pandav "A Cascaded Asymmetric Multilevel Inverter with Minimum Number of Switches for Solar Applications" IEEE, International Conference on Power and Energy Systems: Towards Sustainable Energy, PESTSE 2014, Bangalore.

- [18] Mahajan Sagar Bhaskar Ranjana; Prasad S Wankhade; Niraj D Gondhalekar; "A Modified Cascaded H-Bridge Multilevel Inverter For Solar Applications" IEEE, International Conference on Green Computing, Communication and Conservation of Electrical Energy ICGCCEE'14.