# Louisiana State University LSU Digital Commons

LSU Historical Dissertations and Theses

**Graduate School**

2000

#### Multiple Bus Networks for Binary -Tree Algorithms.

Hettihewage Prasanna Dharmasena Louisiana State University and Agricultural & Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_disstheses

#### **Recommended Citation**

Dharmasena, Hettihewage Prasanna, "Multiple Bus Networks for Binary -Tree Algorithms." (2000). *LSU Historical Dissertations and Theses*. 7190. https://digitalcommons.lsu.edu/gradschool\_disstheses/7190

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Historical Dissertations and Theses by an authorized administrator of LSU Digital Commons. For more information, please contact gradetd@lsu.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### MULTIPLE BUS NETWORKS FOR BINARY-TREE ALGORITHMS

A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Department of Electrical and Computer Engineering

by H. P. Dharmasena B.S., University of Moratuwa, 1983 M.S., Louisiana State University, 1987 May 2000

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

UMI Number: 9979254

# UMI®

#### UMI Microform 9979254

Copyright 2000 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

## Acknowledgments

I would like to express my sincere gratitude to Dr. R. Vaidyanathan for his guidance, wisdom and especially his patience during the course of this research. I would also like to thank members of my committee Dr. S. Kundu, Dr. A. El-Amawy, Dr. J. L. Trahan, Dr. K. Zhou and Dr. L. J. Smolinsky.

This work would have been impossible without the support of various individuals at my work. I wish to express my sincere appreciation to the members of the instrument development group for their understanding and support.

# **Table of Contents**

| A  | CKNO  | WLEDGMENTS                                                                                                                 | ii         |

|----|-------|----------------------------------------------------------------------------------------------------------------------------|------------|

| Lı | ST OI | TABLES                                                                                                                     | <i>r</i> i |

| Lı | ST OI | FIGURES v                                                                                                                  | ii         |

| A  | BSTRA | ACT                                                                                                                        | x          |

| CI | HAPT  | ER                                                                                                                         |            |

| 1  | Inte  | RODUCTION                                                                                                                  | 1          |

|    | 1.1   |                                                                                                                            | 4          |

|    | 1.2   |                                                                                                                            | 6          |

|    | 1.3   |                                                                                                                            | 9          |

|    | 1.4   | Organization of the Dissertation                                                                                           | 0          |

| 2  | Pre   | LIMINARIES                                                                                                                 | 1          |

|    | 2.1   | Binary Tree Algorithms 1                                                                                                   | 1          |

|    | 2.2   | Multiple Bus Networks                                                                                                      | 3          |

|    | 2.3   | Running Binary Tree Algorithms on MBNs                                                                                     | 4          |

|    |       | 2.3.1 Direct and Indirect Mapping                                                                                          | 6          |

|    | 2.4   | Prefix Computations on Binary-Tree MBNs 1                                                                                  | 7          |

| 3  | Deg   | REE, LOADING, TIME TRADE-OFFS                                                                                              | 0          |

|    | 3.1   | Preliminaries                                                                                                              | 1          |

|    | 3.2   | Lower Bound for Direct Mapping                                                                                             |            |

|    | 3.3   | An $\Omega(\sqrt{n})$ Lower Bound $\ldots \ldots 24$ | -          |

|    |       | 3.3.1 Strategy and Definitions                                                                                             | _          |

|    |       | 3.3.2 Basic Results                                                                                                        | _          |

|    |       | 3.3.3 The Accounting Scheme                                                                                                | -          |

|    |       | 3.3.4 Non-Uniform Bus Usage 30                                                                                             |            |

|    |       | 3.3.5 The Lower Bound                                                                                                      | _          |

|    | 3.4   | An $\Omega\left(n^{\frac{2}{3}}\right)$ Lower Bound                                                                        |            |

|    |       | 3.4.1 Additional Results                                                                                                   |            |

|    |       | 3.4.2 Tighter Lower Bound                                                                                                  |            |

|    | 3.5   | An $\Omega\left(\frac{n}{\log n}\right)$ Lower Bound                                                                       |            |

|    |       | 3.5.1 Initial Condition                                                                                                    | 8          |

|   |         | 3.5.2 The New Accounting Scheme                           | 9        |

|---|---------|-----------------------------------------------------------|----------|

|   |         | 3.5.3 Tighter Lower Bound                                 | 3        |

|   | 3.6     | The Tree MBN                                              | 4        |

|   | 3.7     | Loading-Speed Tradeoff                                    | 7        |

|   |         | 3.7.1 Lower Bound                                         | 17       |

|   |         | 3.7.2 Upper Bound                                         | 9        |

|   | 3.8     | Extension to k-ary Tree Algorithms                        | 52       |

|   | 3.9     | Concluding Remarks                                        | 8        |

| 4 | Mu      | TIPLE-BUS ENHANCED MESHES                                 | <b>9</b> |

|   | 4.1     | Preliminaries                                             | 3        |

|   |         | 4.1.1 MBN Measures                                        | 4        |

|   |         | 4.1.2 Multiple-Bus Enhanced Meshes                        | 5        |

|   | 4.2     | Binary-Tree MBN Extensions                                | 6        |

|   | 4.3     | Meshes with Tree MBNs                                     | 9        |

|   | 4.4     | MBEMs with Segment Switches                               | 4        |

|   |         | 4.4.1 Binary-Tree MBNs with Segment Switches              | 4        |

|   |         |                                                           | 0        |

|   | 4.5     | -                                                         | 3        |

| 5 | FAU     | <b>т</b> Tolerance                                        | 4        |

| U | 5.1     |                                                           | 5        |

|   | 5.2     |                                                           | 6        |

|   |         | 5.2.1 Adding Redundant Connections                        | 7        |

|   |         | 5.2.2 Definition of $\mathcal{R}_k$                       | 7        |

|   |         | 5.2.3 The Designated Set                                  | 9        |

|   |         | 5.2.4 Fault Tolerance Properties of $\mathcal{R}_k$       | 5        |

|   |         | 5.2.5 Processor Faults                                    | 6        |

|   |         | 5.2.6 Fault Tolerant Binary-Tree MBNs                     | 7        |

|   | 5.3     | Recursive Scheduling                                      | 1        |

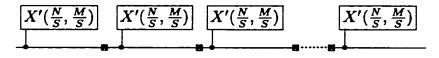

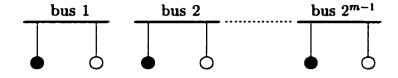

|   |         | 5.3.1 An MBN, $\mathcal{M}'_1$ , with $2^m - 1$ Buses     | 2        |

|   |         | 5.3.2 Recursive Scheduling with 2 <sup>s</sup> Bus Faults | 0        |

|   |         | 5.3.3 Putting it All Together                             | 1        |

|   | 5.4     | Comparison of Results                                     | 2        |

|   | 5.5     | Concluding Remarks                                        | 3        |

| 6 | VLS     | I LAYOUT LOWER BOUND                                      | 5        |

| Ŭ | 6.1     | Preliminaries                                             | 8        |

|   | <b></b> | 6.1.1 VLSI Model                                          |          |

|   |         | 6.1.2 Definitions and Figure Conventions                  |          |

|   | 6.2     | Towards the Lower Bound                                   |          |

|   |         | 6.2.1 Minimum Communication Structure                     |          |

|   |         | 6.2.2 Labeling Links                                      |          |

|   |         |                                                           |          |

|              | 6.2.3     | Collapsing Li | nks . | ••• | ••• | ••  | • •   |    | ••  | ••• | <br>• • • • • | 130 |

|--------------|-----------|---------------|-------|-----|-----|-----|-------|----|-----|-----|---------------|-----|

| 7            | Summary   | AND FUTURE    | Work  | ••  | ••  | • • |       |    | ••  |     | <br>          | 136 |

| B            | BLIOGRAPH | Υ             |       | ••• | ••• |     | • • • |    | ••• |     | <br>• • • • • | 140 |

| $\mathbf{V}$ | <b>TA</b> |               |       | ••• |     | ••  |       | •• | ••  |     | <br>          | 147 |

# **List of Tables**

| 4.1 | Some results for meshes with Tree MBN                                 | 73  |

|-----|-----------------------------------------------------------------------|-----|

| 4.2 | Some results for meshes with Tree MBN and Segment Switches $\ldots$ . | 82  |

| 5.1 | Summary of results                                                    | 114 |

# List of Figures

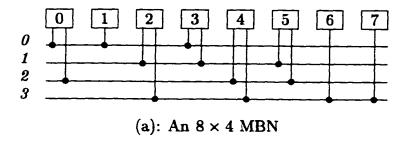

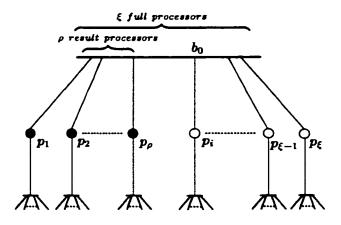

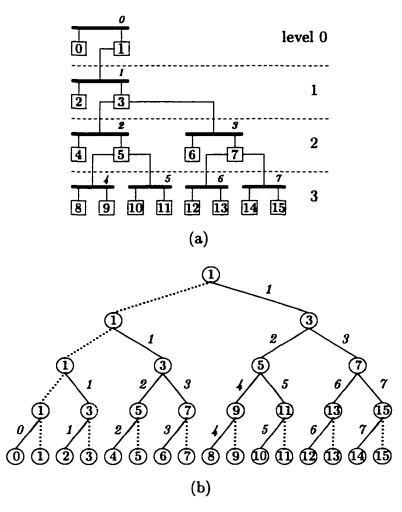

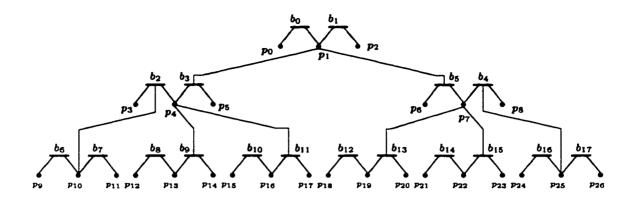

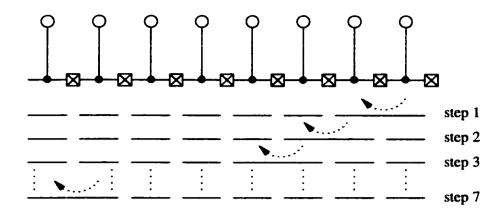

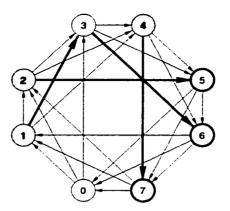

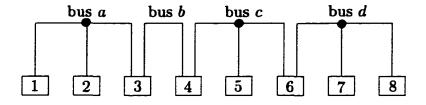

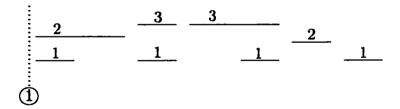

| 2.1 | Running $Bin(3)$ on an $8 \times 4$ MBN                                                                                             | 12 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

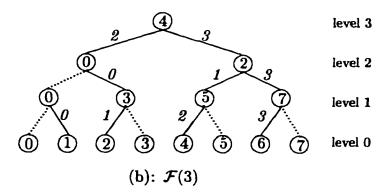

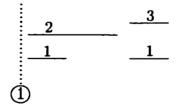

| 2.2 | A $16 \times 8$ MBN and its matrix $\ldots$                                                                                         | 14 |

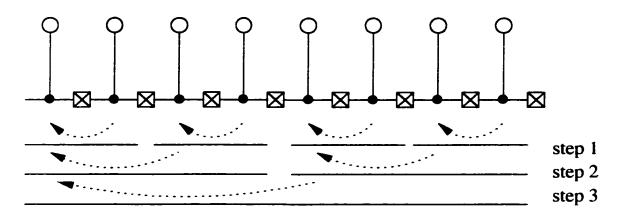

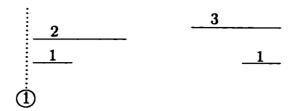

| 2.3 | Steps of running prefix computation on binary-tree MBNs                                                                             | 18 |

| 3.1 | $\mathcal{F}(n)$ with a direct mapping $\ldots \ldots \ldots$ | 23 |

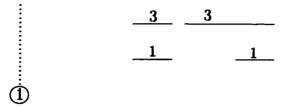

| 3.2 | Step 1 of $X_1(n)$                                                                                                                  | 25 |

| 3.3 | Processors and buses in the neighborhood of bus $b_0$                                                                               | 36 |

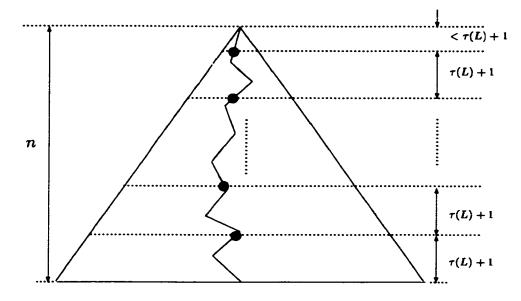

| 3.4 | Subintervals of $[L, n]$                                                                                                            | 37 |

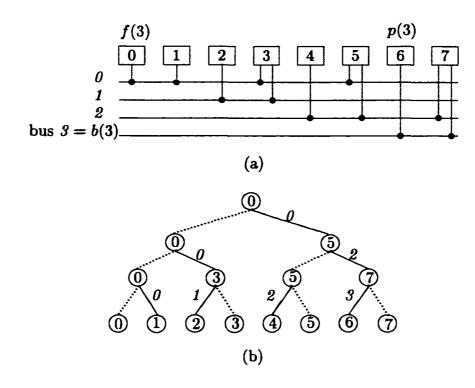

| 3.5 | The connections on bus $b_0$                                                                                                        | 44 |

| 3.6 | Running $Bin(4)$ on $\mathcal{T}(4)$                                                                                                | 46 |

| 3.7 | Path with $t$ delays $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 48 |

| 3.8 | Running $Bin(3)$ on $8 \times 4$ MBN, $\mathcal{D}(3)$                                                                              | 50 |

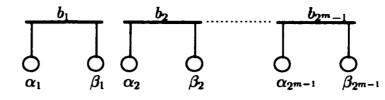

| 3.9 | MBN for ternary tree algorithms                                                                                                     | 58 |

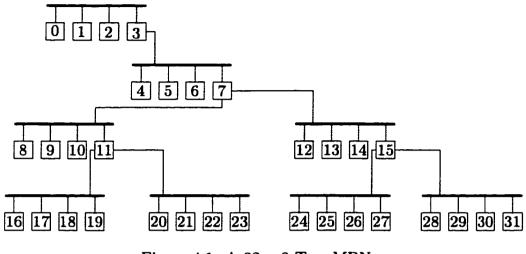

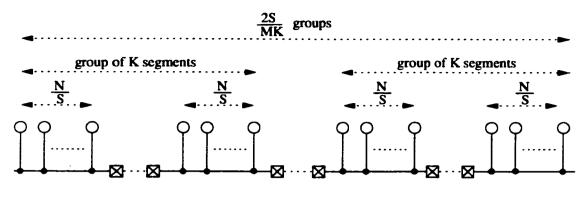

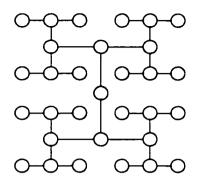

| 4.1 | A $32 \times 8$ Tree MBN                                                                                                            | 68 |

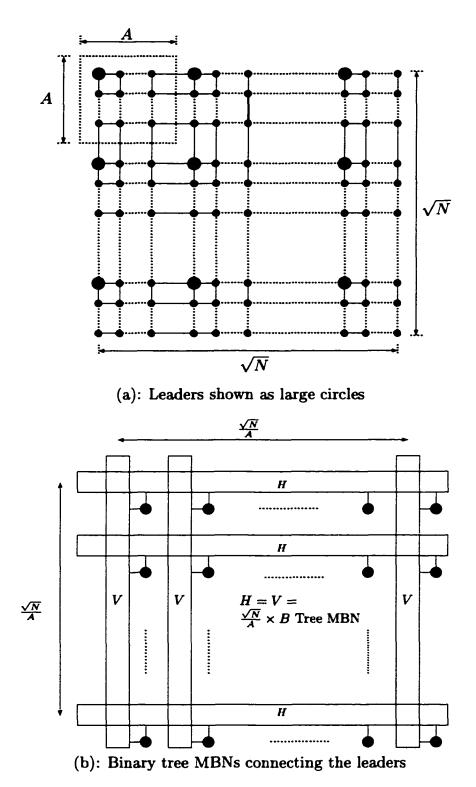

| 4.2 | Structure of a mesh with binary-tree MBN                                                                                            | 71 |

| 4.3 | Steps of method 1                                                                                                                   | 76 |

| 4.4 | Steps of the method 2                                                                                                               | 77 |

| 4.5 | Construction 1                                                                                                                      | 78 |

| 4.6 | Construction 2                                                                                                                      | 79 |

| 5.1  | The MBN of Figure 2.2 augmented to handle 3 bus faults                                                                      | 88  |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

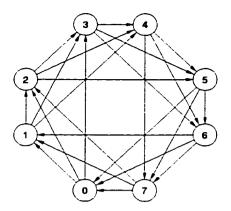

| 5.2  | Graph $\mathcal{G}_{3,8}$                                                                                                   | 90  |

| 5.3  | An illustration of the proof of Lemma 5.1                                                                                   | 92  |

| 5.4  | Node disjoint correspondences for an example                                                                                | 95  |

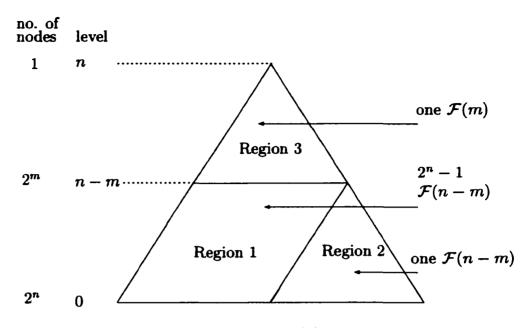

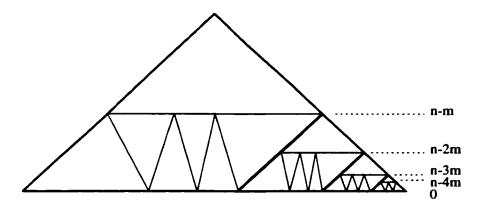

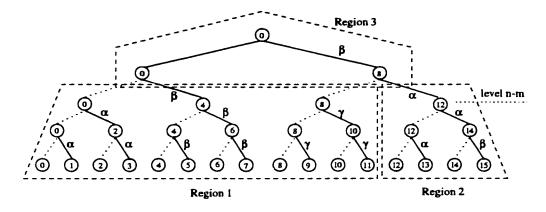

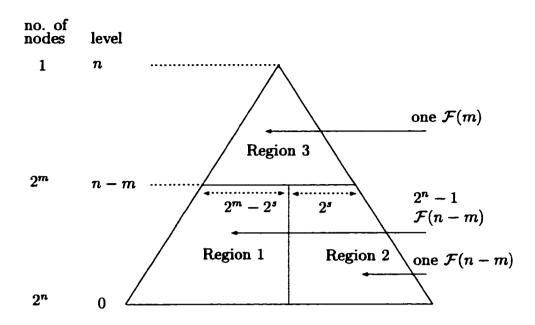

| 5.5  | Regions of $\mathcal{F}(n)$                                                                                                 | 103 |

| 5.6  | Recursive decomposition of $\mathcal{F}(n)$                                                                                 | 104 |

| 5.7  | Running the first step of Region 3                                                                                          | 105 |

| 5.8  | An example of a $8 \times 4$ MBN                                                                                            | 105 |

| 5.9  | Connections of processors and buses with one bus fault                                                                      | 106 |

| 5.10 | Connection of processors and buses in Region 3                                                                              | 108 |

| 5.11 | Regions of $\mathcal{F}(n)$ for k bus faults $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 110 |

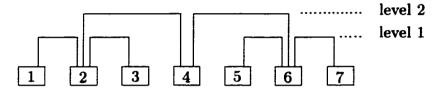

| 6.1  | H-Tree layout of a 31-processor binary tree                                                                                 | 116 |

| 6.2  | 7-node binary tree layout                                                                                                   | 116 |

| 6.3  | 8-processor MBN layout                                                                                                      | 117 |

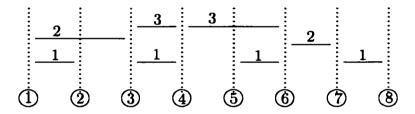

| 6.4  | 8 processor MBN running $Bin(3)$                                                                                            | 117 |

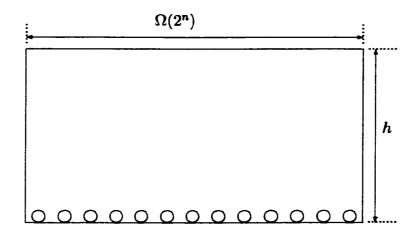

| 6.5  | A perimeter layout                                                                                                          | 119 |

| 6.6  | Links between processors                                                                                                    | 120 |

| 6.7  | View from processor 1                                                                                                       | 120 |

| 6.8  | Subset view I                                                                                                               | 121 |

| 6.9  | Subset view II                                                                                                              | 122 |

| 6.10 | Subset view III                                                                                                             | 122 |

.

| 6.11 | Subset view from processor 1                    | 122 |

|------|-------------------------------------------------|-----|

| 6.12 | Subset view from processor 4                    | 123 |

| 6.13 | Equivalent views                                | 123 |

| 6.14 | Symbolic representation of a subset view        | 123 |

| 6.15 | Communication Structure for $\mathcal{F}(3)$    | 124 |

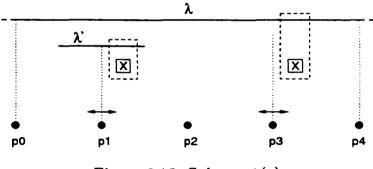

| 6.16 | Subcase 1(a)                                    | 125 |

| 6.17 | Subcase 1(b): $p_2$ - $p_1$ - $p_0$ link        | 126 |

| 6.18 | Subcase 1(b): $p_2$ - $p_3$ - $p_0$ link        | 126 |

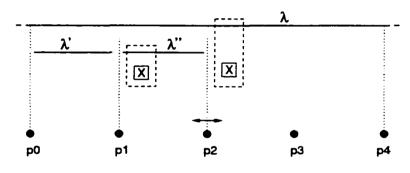

| 6.19 | Case 2                                          | 127 |

| 6.20 | Case 2: $p_2$ - $p_1$ - $p_0$ link              | 127 |

| 6.21 | Case 2: $p_2$ - $p_3$ - $p_0$ link              | 127 |

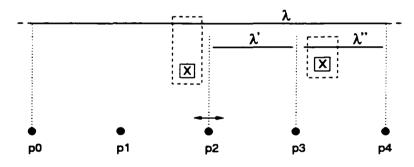

| 6.22 | Subcase 3(a)                                    | 128 |

| 6.23 | Subcase 3(b): $p_2$ - $p_1$ - $p_0$ link        | 128 |

| 6.24 | Subcase 3(b): $p_2$ - $p_3$ - $p_0$ link        | 129 |

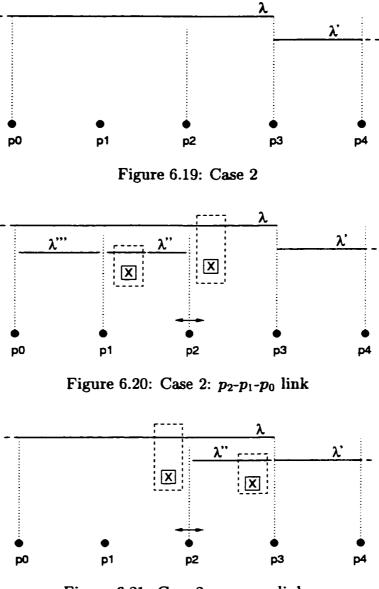

| 6.25 | $\mathcal{F}(n)$                                | 130 |

| 6.26 | View from final result processor                | 130 |

| 6.27 | A maximal collapse of a structure with 4 levels | 132 |

| 6.28 | A different collapse                            | 134 |

# Abstract

Multiple bus networks (MBN) connect processors via buses. This dissertation addresses issues related to running binary-tree algorithms on MBNs. These algorithms are of a fundamental nature, and reduce inputs at leaves of a binary tree to a result at the root. We study the relationships between running time, degree (maximum number of connections per processor) and loading (maximum number of connections per bus). We also investigate fault-tolerance, meshes enhanced with MBNs, and VLSI layouts for binary-tree MBNs.

We prove that the loading of optimal-time, degree-2, binary-tree MBNs is nonconstant. In establishing this result, we derive three loading lower bounds  $\Omega(\sqrt{n})$ ,  $\Omega(n^{\frac{2}{3}})$  and  $\Omega(\frac{n}{\log n})$ , each tighter than the previous one. We also show that if the degree is increased to 3, then the loading can be a constant. A constant loading degree-2 MBN exists, if the algorithm is allowed to run slower than the optimal.

We introduce a new enhanced mesh architecture (employing binary-tree MBNs) that captures features of all existing enhanced meshes. This architecture is more flexible, allowing all existing enhanced mesh results to be ported to a more implementable platform.

We present two methods for imparting tolerance to bus and processor faults in binary-tree MBNs. One of the methods is general, and can be used with any MBN and for both processor and bus faults. A key feature of this method is that it permits the network designer to designate a set of buses as "unimportant" and consider all faulty buses as unimportant. This minimizes the impact of faulty elements on the MBN. The second method is specific to bus faults in binary-tree MBNs, whose features it exploits to produce faster solutions.

We also derive a series of results that distill the lower bound on the perimeter layout area of optimal-time, binary-tree MBNs to a single conjecture. Based on this we believe that optimal-time, binary-tree MBNs require no less area than a balanced tree topology even though such MBNs can reuse buses over various steps of the algorithm.

# Chapter 1

### Introduction

In a parallel processing system, the interprocessor communication network plays a very important role. In this dissertation, we deal with one class of such networks called *multiple bus networks* (*MBNs*). An MBN consists of a set of processors and a set of buses, with each processor connected to at least one bus. Any processor connected to a bus can access the bus. However, the bus can convey only one piece of information at a time.

MBNs have several advantages over traditional point-to-point networks (such as the ring, mesh, torus and hypercube). In a point-to-point network, each communication link is dedicated to a pair of processors. In an MBN, on the other hand, the communication medium (bus) is shared among several processors and could, therefore, be used more efficiently. This sharing of the communication medium also allows for a graceful degradation of performance in the presence of faults. Because the communication medium is shared, MBNs lend themselves to easy broadcasting. An MBN can be used to emulate several point-to-point topologies or set of interconnection functions [26, 27, 33, 47, 48] as each bus could serve as a communication link between different processor pairs at different times. An MBN is representative of any hypergraph based system [6], and a bus can be viewed as an abstraction of any shared resource, for example a memory module in shared memory systems, or a transmission frequency in systems with frequency division multiplexing (such as wireless [18, 22, 35, 52, 61] and optical [5, 20, 65]). Therefore, this work may find applicability in other settings as well.

Traditionally, MBNs have been used in an asynchronous environment with relatively few processors. Most of this work has been on analyzing data throughput of multiprocessor systems under various traffic models, arbitration schemes, and relationship between numbers of processors/buses [12, 14, 21, 28, 32, 36, 55, 56, 66, 94]. Work also exists on variations on the basic MBN model [9, 16, 37, 39, 43, 53, 90] and on the pattern of connections between processors and buses [12, 31, 39, 42, 54, 81]. Traditionally, MBNs have been used in asynchronous systems with a small number of processors partly because of the fact that physical loading due to capacitive coupling limits the number of connections to a bus. In an optical bus, loading is caused by a receiver on the bus drawing some of the available power, thus limiting the number of receivers that can be connected to the bus. The asynchronous bus model also requires a complex arbitration scheme to resolve bus contention.

In this dissertation we primarily consider a synchronous bus model, though most results apply to asynchronous MBNs as well. Technological advances have made it feasible to connect more loads on a bus. This, in turn, makes fine-grained synchronous MBNs (with a large number of processors) possible. The synchronous environment also removes the need for arbitration. Feldman *et al.* [29] recently proposed an optical slab waveguide bus capable of connecting a large number of processors at very high data rates. Qiao and Melhem [70] proposed a communication scheme called timedivision source-oriented multiplexing (TDSM) for synchronous optical buses that can be used for large systems. Their method takes advantage of unidirectional propagation and predictable delay of optical fibers to achieve reliable communication among a large number of processors. Lin *et al.* [51] have proposed "precharged" buses to facilitate concurrent broadcasts.

Much work on synchronous MBNs has centered around topologies (primarily the two-dimensional mesh) enhanced with buses (for example [1, 4, 10, 17, 19, 64, 69, 71, 75]). There has also been some work on running algorithm classes and implementing interconnection functions [2, 23, 24, 25, 26, 40, 46, 47, 50, 63, 83, 85]. Another class of MBNs that uses synchronous buses is reconfigurable models, that allow the connection pattern between processors to change dynamically (Nakano [59] provides an extensive bibliography). Under current technological constraints, however, fixed connection MBNs, such as those considered in this work, are easier to implement than reconfigurable networks. Commercially available field programmable gate arrays (FPGAs) have also been proposed as reconfigurable computational platforms [34, 41, 58, 74, 88, 91, 92]. The programmable interconnections between "configurable logic blocks" in FPGAs show some features of MBNs in that they are often implemented as wires with taps (buses) [89, 93].

In this dissertation we address various issues related to running a well-known class of algorithms called *binary-tree algorithms* on MBNs. (Other researchers have also studied algorithm classes on MBNs and other networks [2, 40, 47, 62, 63, 73, 82].) A binary-tree algorithm reduces N inputs to a single result. The computation performed by such an algorithm can be represented as a balanced binary tree with the inputs at the leaves and the result at the root. Several fundamental algorithms involving semigroup operations and prefix computations such as maximum/minimum, parity, polynomial evaluation and barrier synchronization can be implemented as binary-tree algorithms. Binary-tree algorithms require a rich communication pattern,

so a network suitable for running binary-tree algorithm is likely to be suitable for many other applications as well. Because of the fundamental nature of binary-tree algorithms, a dedicated hardware module to run these algorithms could aid solution to a large number of problems. Any insights gained by studying binary-tree algorithms will be useful in designing such modules. In the past, binary-tree algorithms and MBNs for them have been in setting of enhanced meshes [1, 4, 10, 19, 64, 69, 75, 76]. Other work on binary-tree MBNs addresses issues such as design, fault-tolerance and VLSI layouts [2, 25, 26, 27, 57, 63, 83, 84, 85].

#### 1.1 MBNs and Binary-Tree Algorithms

In this section we present a broad picture of the issues related to MBNs running binary-tree algorithms (or "binary tree MBNs"). An  $N \times M$  Multiple Bus Network MBN has N processors and M buses. Each processor is connected to a subset of the set of buses. Two processors may communicate in one unit of time, provided they are connected to a common bus. However, the bus may carry only one piece of information on it at any given point in time. Two important parameters of an MBN are its degree (maximum number of buses connected to a processor) and loading (maximum number of processors connected to a bus). These parameters determine the cost and implementability of the MBN. A large degree requires a processor to have a large number of input/output ports, while a large loading can reduce the data rate of the system.

One direction of research on MBNs considers a given pattern of interconnections between processors and buses and investigates the capabilities of the resulting MBN architecture. Often this takes the form of emulating other architectures (for example [26, 27, 40]) or developing algorithms on models ([52, 60, 61]); the enhanced mesh results cited earlier also fall in this category The second direction considers the problem of designing an MBN suited to a particular interconnection requirement. This dissertation and others [48, 57, 63] represent work in this direction.

As mentioned earlier, degree and loading are important considerations for MBNs. Clearly, the MBN should also be evaluated on how well it provides the interconnection requirements in question; this would consider issues such as number of hops and congestion on buses. Constructing an "optimal" MBN to run a given set of interconnection functions is a non-trivial task. Kulasinghe and El-Amawy [46] showed that the general problem of designing an optimal interconnecting network for a given set of interconnection functions is NP-Hard. The criteria they used for measuring the cost is the of number of buses and interfaces (connections between processors and buses). They showed [47] that this problem can be solved in polynomial time for certain "symmetric" interconnections, and presented a methodology for such implementations. Though such symmetries exist in interconnection topologies, it is not the case for many algorithm classes. Moreover, their analysis does not address the interplay between speed, degree and loading of the MBN.

With a single bus, the solution is simple as the only possibility is to connect all processors to the bus; this approach is used in most enhanced meshes and traditional multiprocessor systems. This method has the disadvantage of high loading and bus contention, limiting the size of the network. At the other extreme, all the processors could be connected to all buses. The Broadcast Communication Model (BCM) [60, 61] adopts this approach. This increases the loading and degree, and consequently, the cost of the MBN.

Thus an intermediate solution (that connects each processor to a subset of buses) is important. Optimal MBNs for binary-tree algorithms are particularly challenging to design. On one hand, for an N input algorithm the MBN needs sufficient bandwidth to sustain  $\Theta(N)$  simultaneous communications; the lower (near leaf) levels of the tree involve a large number of simultaneous communications. On the other hand, because of its similarity to a binary tree the MBN should be fairly sparse. Thus, a small number of connections needs to be distributed over a large number of buses, lowering the acceptable values for both degree and loading. Most previous results have completely ignored degree and loading, or have reduced one at the expense of the other. For example Vaidyanathan and Padmanabhan [85] have proposed an *N*-input binary-tree algorithm that runs optimally in log *N* steps. Though the degree of this MBN is 2, its loading is  $\Theta(\log N)$ . On the other hand, Ragavendra [71] proposed a mesh with a hierarchy of broadcast buses in each row and column. For a given parameter *k*, this MBN has a loading *k*, but the degree of  $O\left(\frac{\log N}{\log k}\right)$ . Thus if the degree is small, the loading is large and vice versa. In this dissertation we construct an MBN that runs binary-tree algorithms optimally and which has both constant degree and loading. We now describe results of this dissertation in more detail.

#### **1.2** Scope of the Dissertation

Because of its fundamental nature, binary-tree algorithms have been studied in almost all facets of computing. As mentioned earlier, most previous work on binary-tree MBNs has focused on enhanced mesh architectures. Very little work has been done on identifying fundamental properties of binary-tree MBNs and to establish relationships between running time, loading and the degree. In Chapter 3, we study these relationships, and establish lower-bounds on degree-2, binary-tree MBNs. We identify two important mappings and establish that it is essential to have a mapping called indirect mapping to achieve low loading. We do this by establishing a series of lower bounds on loading, each one tighter than the previous bound. Specifically, for a  $2^n$ -input, optimal-time, binary-tree MBN we first prove the loading to be  $\Omega(\sqrt{n})$ . We then improve this bound to  $\Omega(n^{\frac{2}{3}})$  by deriving some additional results. Finally the lower bound is further tightened to  $\Omega(\frac{n}{\log n})$  by refining the method used to count connections on buses. (The lower bound restriction requires the MBN to have at least  $2^{n-1}$  buses.) These lower bound results (and indeed most other results of this work) are general and apply to any binary-tree MBN satisfying the conditions of the problem, rather than a given MBN instance. Although a degree of 2 necessitates nonconstant loading, this is not the case for degree 3. We construct a binary-tree MBN called the Tree MBN that has degree 3 and loading 3, which is the best possible.

Also in Chapter 3 we investigate trade-offs between the loading and running time. We show that if the running time is allowed to increase by a factor of 2, then a degree-2, binary-tree MBN with constant loading exists. We establish that if the additional time (beyond the optimal) used by the MBN is t, and if the largest problem that can be solved on a degree-2, loading-L, optimal-time MBN has size  $2^{\tau(L)}$ , then  $t \ge \left\lfloor \frac{n}{\tau(L)+1} \right\rfloor$ . We present an example of a degree-2, loading-4, (2n-3)-step binary-tree MBN that matches this bound for constant L.

Chapter 4 explores the idea of using binary-tree MBNs to enhance meshes. Here we show that an architecture using multiple buses has significant advantages over traditional enhanced meshes that employ single-bus networks to connect processor sets. We also study buses with segment switches (each of which can break a bus into two) and use it to reduce the loading. Other parameters of the proposed architecture can be selected for various trade-offs between the cost and performance. (Performance measures include running time, degree, loading, VLSI area and the aspect ratio; many exiting architectures require highly elongated rectangular layouts that are difficult to implement on a chip.) The architecture we propose improves on all previous results in at least one of the measures. It provides more choices to the network designer than any other architecture in the literature. Tables 4.1 and 4.2 (pages 73 and 82) summarize the results of this chapter.

In Chapter 5 we study methods for imparting fault tolerance to binary-tree MBNs. This complements the use of binary-tree MBNs as building blocks for general-purpose computing platforms (described in Chapter 4). Redundant connections can also be used to increase the yield for chips with binary-tree MBNs. In Chapter 5, we present two methods for constructing fault tolerant MBNs from any given binary-tree MBN. One of these methods (replication) is a general method that can be applied to processor and bus faults on any type of MBN. The other method (recursive scheduling) exploits features particular to binary-tree MBNs to produce better results, but handles only bus-faults. The general results of this chapter are too involved to state here; we state results for some particular cases instead. Replication constructs a binarytree MBN that requires at most 5 extra steps, even if half the buses fail. Also, even if half the processors fail, the number of the extra steps required is at most 2.

In Chapter 6 we investigate the VLSI area required for optimal-time, binary-tree MBNs. The corresponding problem for the balanced tree topology is well studied [80]. The binary-tree algorithm is different from a balanced tree topology in that only one level of the tree is active (or used) in any step of a binary-tree algorithm. Therefore, binary-tree MBNs can reuse the same buses or wires at different levels. This is not possible in a balanced tree topology, where all edges could be active simultaneously. This raises the possibility that the VLSI area for a binary-tree MBN is less than that required for a balanced tree topology. We specifically consider the "perimeter layout" case where all the processors of the MBN are laid out on the periphery of the layout;

allowing the processors to be placed in the interior can trivially use a solution for the balanced tree topology. Our work on this topic leads us to conjecture that the perimeter area required for optimal-time N-input binary-tree MBNs is  $\Omega(N \log N)$ . Simulations seem to indicate that this conjecture is true.

#### **1.3 Contribution of this Work**

This dissertation studies various facets of running binary-tree algorithms on MBNs, providing a better understanding of the abilities and limitations of binary-tree MBNs. Most of our results are general in nature, applicable to <u>any</u> binary-tree MBN rather than particular cases. Many of these results extend to k-ary tree algorithms (for k > 2) as well.

Chapter 3 establishes important relationships between key parameters, namely running time, loading and degree. We develop a novel accounting scheme to keep track of the connections on a bus. It is possible that this method of counting connections may be useful in other algorithms as well. We also identify two mappings (called direct and indirect) of binary-tree algorithms on MBNs that impact the loading and degree of binary-tree MBNs. We show that indirect mapping is essential to achieving constant loading. Considering that indirect mapping increases the amount of communication, this result is rather counter-intuitive. Equally surprising is the result of Section 3.7 that shows that by increasing the running time by a constant factor, loading can be reduced by a non-constant factor.

In Chapter 4 we provide a general framework for connecting processors in a 2dimensional mesh that, among other things, captures all the features of previous enhanced-mesh architectures but with a more realistic loading. Thus, our work provides the means to automatically translate all existing algorithms on enhanced meshes to a more implementable platform. In addition, our approach affords much more flexibility to the network designer than traditional methods.

The contribution of Chapter 5 is in providing a framework that adds redundancy in a controlled manner to convert <u>any</u> binary-tree MBN to one that is resilient to processor and bus faults. In particular, one of the methods, replication, works for any MBN (not just binary-tree MBNs) and uses an approach to rename elements and convert faulty components into ones that have the least impact on performance.

Although Chapter 6 does not derive a lower bound on the area, it distills the argument to a single conjecture. It also develops some satellite results (such as an 8-processor, optimal-time MBN with "one layer" of buses) that may have independent significance.

#### **1.4** Organization of the Dissertation

In the next chapter we discuss some preliminary ideas and introduce some definitions. Chapter 3 deals with loading, running time and degree trade-offs. In Chapter 4 we describe meshes enhanced with binary-tree MBNs. Chapter 5 deals with fault-tolerant MBNs. In Chapter 6 we describe the basis of our conjecture on the lower bound of the area required for a "perimeter layout" of optimal-time binary-tree MBNs. Finally in Chapter 7 we summarize this work, and identify areas for future research.

# Chapter 2

### Preliminaries

In this chapter we discuss some basic ideas used in the rest of the dissertation. We define binary-tree algorithms in Section 2.1 and multiple bus networks (MBNs) in Section 2.2. In Section 2.3 we discuss issues related to running binary-tree algorithms on MBNs. In particular, Section 2.3.1 identifies two types of mappings of MBN processors to "nodes" of binary-tree algorithms. These mappings are important factors, determining the loading of MBNs that run binary-tree algorithms. Finally, in Section 2.4, we prove that an MBN running a binary-tree algorithm can also perform prefix computations in the same order of time.

#### 2.1 Binary Tree Algorithms

A binary-tree algorithm, Bin(n), reduces  $2^n$  inputs to a single result. The computation performed by a binary-tree algorithm can be represented as a complete binary tree. For integer  $n \ge 1$ , and any associative binary operation  $\circ$ , a binary-tree algorithm, Bin(n) accepts  $N = 2^n$  inputs  $a_0, a_1, \dots, a_{N-1}$  at the leaves of a complete binary tree (denoted by  $\mathcal{F}(n)$ ) and produces one output,  $a_0 \circ a_1 \circ \dots \circ a_{N-1}$ , at the root of  $\mathcal{F}(n)$ . The algorithm proceeds level by level from the leaves to the root, applying the

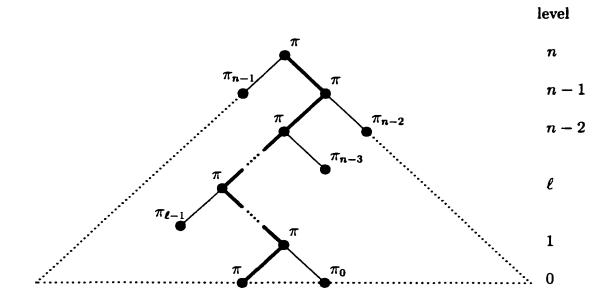

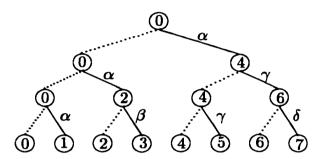

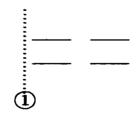

Figure 2.1: Running Bin(3) on an  $8 \times 4$  MBN

operation  $\circ$  at each internal node to the *partial results* at its children. Figure 2.1(b) shows  $\mathcal{F}(3)$ ; the numbers associated with nodes and edges are explained later.

The tree  $\mathcal{F}(n)$  has *n* levels, and at level  $\ell$  (where  $0 \leq \ell \leq n$ ), there are  $2^{n-\ell}$  nodes. Clearly, Bin(n) can be used to apply a semigroup operation on a set of  $2^n$  inputs. Any network that runs Bin(n) in T(n) steps can also be used to perform a prefix computation on  $2^n$  inputs in O(T(n)) steps (see Section 2.4). It must be noted that Bin(n) is a description of a class of algorithms, rather than the solution to a particular problem (such as a reduction operation) that can be implemented as a binary-tree algorithm. Thus Bin(n) requires at least *n* steps as the height of  $\mathcal{F}(n)$  is *n*; on the other hand, particular reduction problems such as finding the OR of *N* bits can be solved on some models in O(1) time [51, 77]. To run Bin(n) on a network with  $2^n$ processors, each of the  $2^{n+1}-1$  nodes of  $\mathcal{F}(n)$  is mapped to one of the  $2^n$  processors of

12

the network (Figure 2.1(b)). We elaborate further on running binary-tree algorithms on MBNs in Section 2.3.

#### 2.2 Multiple Bus Networks

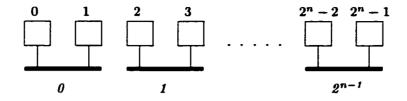

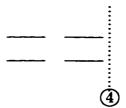

An  $N \times M$  Multiple Bus Network (MBN) has N processors and M buses. Each processor is connected to a subset of the set of buses. Figure 2.2(a) shows a 16  $\times$  8 MBN. Two processors connected to the same bus can communicate with each other in one unit of time. A bus can carry only one piece of information at any given point in time.

The number of buses to which a processor is connected is called the *degree of the processor*. The largest of the degrees of all processors is called the *degree of the MBN*. The number of processors connected to a bus is called the *loading of the bus*. The largest of the loadings of all the buses is called the *loading of the MBN*. The MBN of Figure 2.1(a) has a degree of 2 and a loading of 4, while that of Figure 2.2(a) has a degree of 2 and a loading of 5. The degree and loading are important parameters that determine the cost, speed of operation and implementability of an MBN. The degree of an MBN is analogous to the degree of a graph representing a point-to-point network and is indicative of the number of input/output ports needed per processor. A large loading can introduce a significant delay or attenuation of the signal. High loading in electrical buses introduces capacitive coupling that limits the rate at which data can be transmitted. In an optical bus with high loading, the signal is excessively attenuated by power drawn by photodetectors connected to the bus [29]. Therefore, an MBN implementation should attempt to minimize both degree and loading.

An  $N \times M$  MBN can be represented as an  $N \times M$  Boolean matrix that has a 1 in row p and column b iff processor p is connected to bus b. Figure 2.2(b) shows the matrix representation of the  $16 \times 8$  MBN of Figure 2.2(a). Observe that the rows and columns of the matrix can be permuted without affecting the connectivity properties

Figure 2.2: A  $16 \times 8$  MBN and its matrix; blank entries in the matrix represent 0's.

of the MBN. This is because permuting amounts to just renumbering processors and buses. We use this fact later, when doing so is advantageous.

#### 2.3 Running Binary Tree Algorithms on MBNs

We assume that Bin(n) is run on a  $2^n \times M$  MBN. Using more than  $2^n$  processors has no advantage. If the number of processors is  $2^{n'} < 2^n$ , then the  $2^n$  inputs can be divided among the available  $2^{n'}$  processors, so that there are  $2^{n-n'}$  inputs per processor. Each processor then sequentially reduces the  $2^{n-n'}$  inputs to one result in  $2^{n-n'}-1$  steps. The reminder of the algorithm is run as a Bin(n') on a  $2^{n'} \times M$  MBN.

To run a binary-tree algorithm, Bin(n), on a  $2^n \times M$  MBN, each node of  $\mathcal{F}(n)$  is mapped to a processor. Each edge of  $\mathcal{F}(n)$  that connects nodes mapped to distinct processors represents a communication; such edges are called *non-trivial edges* [27]. Consider the example in Figure 2.1(b). Here the nodes of  $\mathcal{F}(3)$  are labeled with (mapped to) processor indices  $0, 1, \dots, 7$ . This indicates the processor responsible for the action (if any) at a node. Consider the node labeled 0 at level 1 (call it node vfor this discussion). Its two children are labeled 0 and 1. The edge from node v to its left child has end vertices, both of which are labeled by the same processor index (0 in this case). Therefore, this edge does not represent a communication and is called a *trivial edge* (shown dotted in the figure). On the other hand, the edge from node v to its right child is *non-trivial* as its end points have different labels (0 and 1 in this case); hence, the edge represents a communication between processors 0 and 1. Figure 2.1(b) shows non-trivial edges as solid lines; the remaining trivial edges are shown dotted. Each non-trivial edge of  $\mathcal{F}(n)$  is mapped to a bus of the MBN.

Conversely, an MBN to run Bin(n) can be specified by mapping nodes and nontrivial edges of  $\mathcal{F}(n)$  to processors and buses, respectively, of the MBN. Thus  $\mathcal{F}(n)$ (with nodes and non-trivial edges appropriately labeled) completely specifies a  $2^n \times M$  MBN and the method used to run Bin(n) on it. Figure 2.1(b) shows  $\mathcal{F}(3)$ corresponding to the MBN in Figure 2.1(a). We will loosely use the term "binarytree MBNs" to refer to MBNs suitable for running binary-tree algorithms.

In running a binary-tree algorithm on an MBN, we assume that in one "step" a processor can read from or write on each bus it is connected to and perform an internal operation using operands from its local memory or input ports. This assumption is reasonable when the number of ports in a processor is small—all of the MBNs considered in this work have a (small) constant degree. Since the focus of this work is on the network connecting processors, there is no advantage in separately considering the time required for internal operations. The following restrictions apply, however: (i) Each value sent or received by a processor during a step uses a different bus, and (ii) the pair of processors sending and receiving a value must be connected to a common bus. Under these assumptions, a processor is permitted to (a) send a partial result of the binary-tree algorithm, (b) receive two partial results, and (c) perform the operation  $\circ$  (associated with the binary-tree algorithm) on the partial results received, all in one step. This is not very different from the usual assumption that a processor can access operands from its local memory and perform an operation on them, all in one step.

#### 2.3.1 Direct and Indirect Mapping

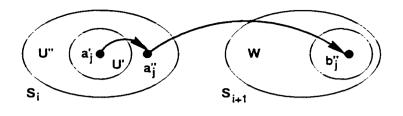

As noted earlier, running Bin(n) on an MBN requires mapping nodes to processors. In this section we identify two types of mappings, direct and indirect, that greatly impact the degree and loading of binary-tree MBNs.

For any node u of  $\mathcal{F}(n)$ , let  $\mu(u)$  denotes the processor to which u is mapped. Let u be an internal node of  $\mathcal{F}(n)$  with children v and w. Node u is said to be a *direct* node iff  $\mu(u) = \mu(v)$  or  $\mu(u) = \mu(w)$ ; otherwise, node u is said to be *indirect*. A direct node is mapped to the same processor as one of its children while an indirect node is mapped to a processor which is different from both of its children. This implies that an indirect node is connected to each of its children by non-trivial edges, whereas a direct node is connected to one of its children by a trivial edge. A processor mapped to a direct node is called a *direct processor* of the step in question; otherwise, it is

called an *indirect processor* of the step. Since a processor may be mapped to more than one node of  $\mathcal{F}(n)$ , it is possible for the same processor to be a direct processor at one step and an indirect processor at another. Any mapping that has an indirect node is called an *indirect mapping*; otherwise it is called a *direct mapping*.

As an example, in Figure 2.1(b) all nodes except the root and its right child are direct. Therefore the entire Bin(3) or  $\mathcal{F}(3)$  uses an indirect mapping (as there is an indirect node). On the other hand, the  $\mathcal{F}(2)$  consisting of the left subtree of the root represents a direct mapping.

Observe that an indirect node involves two communications (one from each child), whereas a direct node requires only one. Thus a direct mapping minimizes the number of communications. Notwithstanding the fact that an indirect mapping entails more communications, we show in Section 3.2 that this mapping is necessary for constant loading.

#### 2.4 Prefix Computations on Binary-Tree MBNs

Given N inputs,  $a_1, a_2, \dots, a_N$ , and an associative operation  $\circ$ , the  $i^{th}$  prefix (where  $1 \leq i \leq N$ ) is the quantity  $a_1 \circ a_2 \circ \cdots \circ a_i$ . A prefix computation for the above inputs and operation computes the  $i^{th}$  prefix for each  $1 \leq i \leq N$ . The relationship between reduction algorithms and prefix computations is well known in the context of a PRAM [38, pp. 44-49] and a fixed-degree topology [49, pp. 37-43]. This relationship has not been studied for binary-tree MBNs, however. We prove here that a binary-tree MBN is suitable for prefix computations as well.

**Theorem 2.1** If X(n) is an MBN that runs Bin(n) in T(n) steps, then X(n) can run a prefix algorithm in 2T(n) steps.

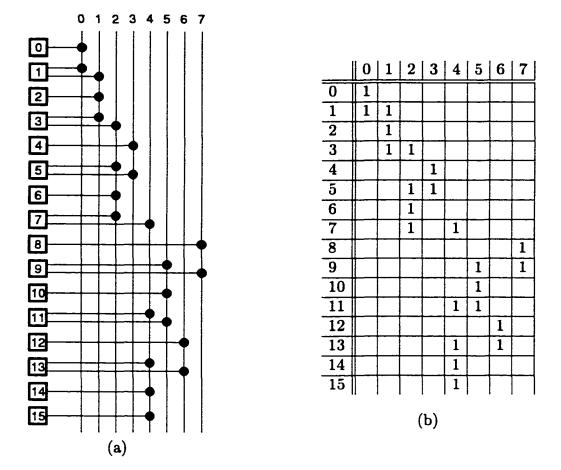

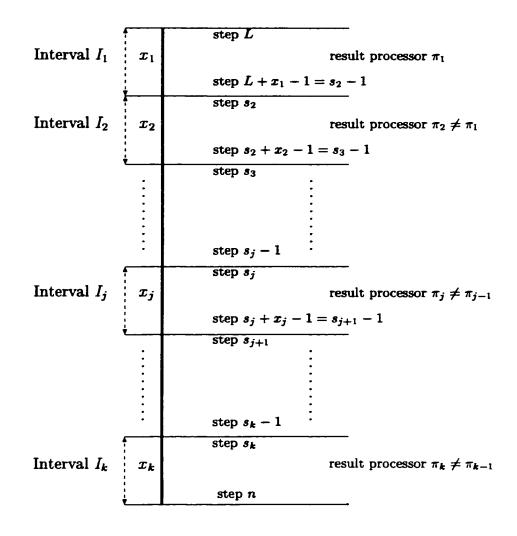

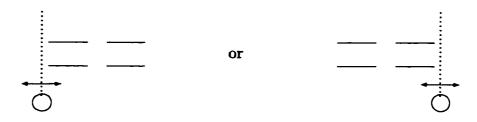

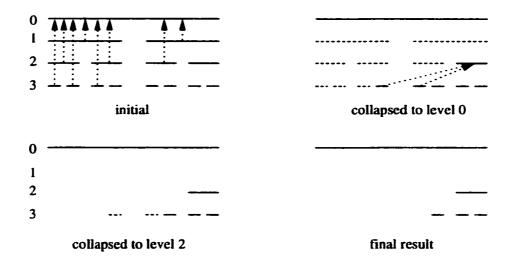

Figure 2.3: Steps of running prefix computation on binary-tree MBNs

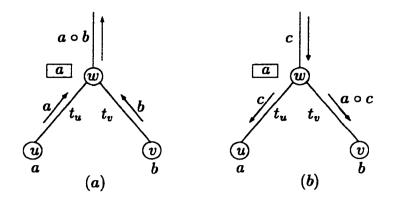

<u>Proof:</u> When an MBN runs a binary-tree algorithm, the nodes of Bin(n) are executed in a manner that respects the precedence relationship described by the tree  $\mathcal{F}(n)$ . Figure 2.3(a) shows three nodes of  $\mathcal{F}(n)$  (corresponding to two levels) where nodes u and v are children of node w. Let the two partial results (or inputs) held by nodes u and v be a and b respectively, and let the associative operation performed by the binary-tree algorithm be  $\circ$ .

The prefix computation runs on the binary-tree MBN in two phases. The first phase runs the binary-tree algorithm from the leaves to the root. The only difference here (from running a regular binary-tree algorithm) is that a node saves the value it receives from the left child, unlike the usual form of the algorithm that simply computes the partial result. For example, node w receives a and b from nodes u and v and computes  $a \circ b$ . In addition to computing this quantity, node w also saves the value "a" (shown in a box in Figure 2.3). Node w sends partial result  $a \circ b$  to the next higher level in the next step (Figure 2.3(a)). The time to run this phase is clearly the same as that of the binary-tree algorithm, namely T(n). The second phase of the prefix computation also proceeds level by level, starting from the top most level (level n) down to the leaves. This can be viewed as reversing the binary-tree algorithm where value(s) from top of the tree propagates to the leaves. Figure 2.3(b) describes the action at each node during this phase. The root of  $\mathcal{F}(n)$  sends the value it stored (one received from its left child in the first phase) to the right child. It sends the identity<sup>1</sup> of operation "o" to the left child. A processor with stored value a and that receive value c from its parent (i) sends c unaltered to its left child and (ii) sends  $a \circ c$  to the right child. This phase mimics the binary-tree algorithm (phase 1) in reverse, so its time is T(n) as well. Therefore, the time required to run a prefix computation on a binary-tree MBN is twice as much as the time required for running a binary-tree algorithm. (The correctness of this method follows from the results in [38, 49].)

<sup>&</sup>lt;sup>1</sup>The identity  $\iota$  has the property that for any value x from the domain of  $\circ$ ,  $\iota \circ x = x \circ \iota = x$ . If  $\circ$  does not have an identity, then the root could simply send a special signal indicating to its left child that it need not apply  $\circ$  to the value received.

# Chapter 3

# Degree, Loading, Time Trade-Offs

This chapter establishes non-trivial relationships between the degree, loading and running time of binary-tree MBNs. We first show by a trivial connectivity argument that any binary-tree MBN has a degree of at least 2 and a loading of at least 2; the loading is at least 3 if no more than  $2^{n-1}$  buses are used for  $2^n$  processors. Next we show that for a direct mapping, constant degree can never yield constant loading, and vice-versa. We then establish a series of results that successively bound the loading of degree-2, optimal-time binary-tree MBNs for Bin(n) to first  $\Omega(\sqrt{n})$ , then to  $\Omega(n^{\frac{2}{3}})$ and finally to  $\Omega(\frac{n}{\log n})$ , where  $2^n$  is the size of the problem. These results make no assumptions about the type of mapping (direct or indirect) and the number of buses, although the optimal-time restriction indirectly requires the MBN to have at least  $2^{n-1}$  buses. Considering that increasing the degree by just 1 can yield a constant loading MBN (see Section 3.6), these lower bound results are quite surprising.

Further, if we relax the optimal-time requirement, then we show the existence of a degree-2, loading-4 MBN that runs Bin(n) in 2n-3 steps. However, the extra time needed (beyond n) still bounds the loading. We show that if a degree-2 MBN runs Bin(n) in n + t steps, for some 0 < t < n, then the loading is  $\Omega\left(\frac{n}{t\log(\frac{n}{t})}\right)$ .

In Section 3.1 we introduce some preliminary ideas used in this chapter and Section 3.2 bounds the loading for binary-tree MBNs with a direct mapping. In Section 3.3 we derive the first of the general lower bounds and lay most of the ground work necessary for the tighter lower bounds of Sections 3.4 and 3.5. We explore loading-time tradeoffs in Section 3.7. We extend the lower bound results of Sections 3.3, 3.4 and 3.5 to k-ary tree algorithms in Section 3.8.

#### 3.1 Preliminaries

As mentioned in Section 2.3, we will consider a  $2^n$ -processor MBN to run Bin(n). An optimal-time MBN requires at least  $2^{n-1}$  buses. If the number of buses is less than  $2^{n-1}$ , at least the first level of  $\mathcal{F}(n)$  requires more than one step to schedule, so optimal time is not possible. Therefore, we consider optimal-time  $2^n \times M$  binary-tree MBNs for Bin(n) with  $M \geq 2^{n-1}$  buses. If such an MBN has degree 2, then it has at most  $2^{n+1}$  connections (at most 2 per processor). If these connections are evenly distributed among the buses, then the loading would be  $\left\lceil \frac{2^{n+1}}{M} \right\rceil \leq 4$ . In this chapter we show that such a uniform distribution of connections is not possible and that a large number of connections is concentrated on a small number of buses resulting in a large non-constant loading.

An MBN is said to be *connected* iff there is a path (possibly via several buses and processors) between any pair of processors. We now derive trivial lower bounds on the degree and loading of a connected binary-tree MBN.

**Lemma 3.1** For  $n \ge 1$  and  $M \ge 2$ , any connected  $2^n \times M$  binary-tree MBN has a degree of at least 2 and a loading of at least  $\max\left(2, \left\lceil \frac{2^n+1}{M} \right\rceil\right)$ .

<u>Proof:</u> If the degree is 1 and if the MBN has connections to each of its  $M \ge 2$  buses, then the MBN cannot be connected; each processor connected to a bus b

can only communicate with other processors connected to bus *b*. Thus at least one processor must be connected to 2 or more buses. This implies that the total number of connections in the MBN is at least  $2^n + 1$ . These connections are distributed over *M* buses, so the loading is at least  $\left\lceil \frac{2^n+1}{M} \right\rceil$ . Since each bus must have at least 2 connections (otherwise it cannot be used for a communication), the loading is max  $\left(2, \left\lceil \frac{2^n+1}{M} \right\rceil\right)$ .

<u>Remark:</u> If  $M = 2^m$  for some  $1 \le m < n$ , then the minimum loading is  $2^{n-m} + 1$ . The  $2^n \times 2^m$  Tree MBN of Section 4.2 has an optimal loading of 3.

## 3.2 Lower Bound for Direct Mapping

To run a binary-tree algorithm on an MBN, the nodes of the tree  $\mathcal{F}(n)$  are mapped to processors, and non-trivial edges are mapped to buses. Recall the definitions of direct and indirect mapping (see Section 2.3.1, page 16). In a direct mapping, each internal node of  $\mathcal{F}(n)$  is mapped to the same processor as one of its children; that is, a processor applying the operation  $\circ$  (associated with a binary-tree algorithm) holds one of the operands as a partial result from the previous step. On the other hand, in an indirect mapping, two processors with partial results may send them to a third processor that applies  $\circ$  on these. The direct mapping may appear to be a better choice as it reduces communication requirements by maximizing the number of trivial edges. This is not true for the loading of the MBN, as we show below. Indeed, the MBN proposed by Vaidyanathan and Padmanabhan [85] uses a direct mapping and has a non-constant loading.

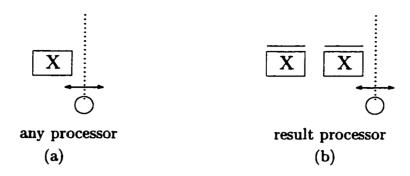

Lemma 3.2 For any  $n \ge 1$ , an MBN with degree d that runs Bin(n) optimally in n steps using a direct mapping has a loading of at least  $\left\lceil \frac{n}{d} \right\rceil + 1$ .

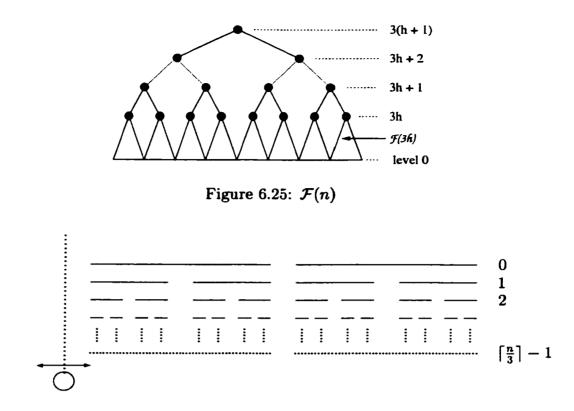

Figure 3.1:  $\mathcal{F}(n)$  with a direct mapping

<u>Proof:</u> Consider MBN  $\mathcal{M}$  with nodes labeled by a direct mapping. Observe first that for any node u that is mapped to some processor  $\mu(u)$ , there exists a path from u to a leaf, such that all nodes on the path are mapped to  $\mu(u)$ . (This follows from the definition of direct mapping.) Let the root of  $\mathcal{M}$  be mapped to processor  $\pi$ . From the above observation, there is a path from the root to a leaf such that all nodes on this path are mapped to  $\pi$  (see Figure 3.1). Clearly, there are n internal nodes on this path, each of which has one of its two children also on the path. Let the children not included in the above path be mapped to processors  $\pi_{\ell}$  (where  $0 \leq \ell < n$ ) as shown in Figure 3.1. Each leaf of  $\mathcal{M}$  is mapped to a different processor (as each input of Bin(n) is in a different processor). This coupled with the observation at the beginning of this proof, establishes that all of  $\pi_0, \pi_1, \dots, \pi_{n-1}$  are distinct. Thus processor  $\pi$  is required to communicate with n different processors.

23

Let processor  $\pi$  be connected to buses  $b_i$  (where  $0 \le i < d' \le d$ ). Since the MBN runs Bin(n) in n steps, each of the processors  $\pi_0, \pi_1, \dots, \pi_{n-1}$  must also be connected to at least one bus  $b_i$  (where  $0 \le i < d'$ ). Thus the total number of connections to all buses  $b_i$  is at least n + d'. This implies that the loading of the MBN is at least  $\left\lfloor \frac{n+d'}{d'} \right\rfloor = \left\lfloor \frac{n}{d'} \right\rfloor + 1 \ge \left\lfloor \frac{n}{d} \right\rfloor + 1$ .

<u>Remark:</u> Lemma 3.2 implies that an indirect mapping is essential for any optimaltime binary-tree MBN with constant degree and loading.

## **3.3** An $\Omega(\sqrt{n})$ Lower Bound

In this section, we develop the first of a series of non-trivial lower bounds on the loading of degree-2, optimal-time, binary-tree MBNs. Here we will prove that if an MBN runs Bin(n) in n steps and if its degree is 2, then its loading is  $\Omega(\sqrt{n})$ .

### **3.3.1 Strategy and Definitions**

We prove this lower bound result by showing that the connections in any degree-2, optimal-time binary-tree MBN are distributed unevenly over the buses. Our strategy here (and to a large extent in Sections 3.4 and 3.5 as well) is to identify (or prove the existence of) a small number,  $\beta$ , of buses that collectively have a large number,  $\gamma$ , of connections. This will establish that the loading is at least  $\frac{\gamma}{\beta}$ .

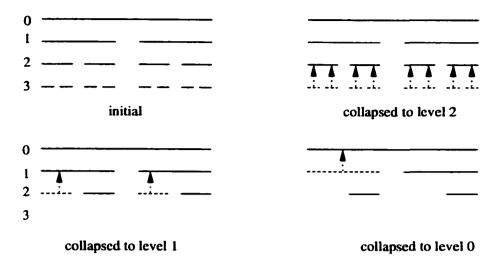

For  $M \ge 2^{n-1}$ , consider a  $2^n \times M$  MBN, X(n), that runs Bin(n) in n steps (numbered  $1, 2, \dots, n$ ) and whose degree and loading are 2 and L, respectively. We will use the terms "end of step s" and "beginning of step s + 1" synonymously. For any  $1 \le s \le n$ , let  $X_s(n)$  denote a  $2^n \times M$  MBN that includes only those connections of X(n) that are used in at least one of steps  $1, 2, \dots, s$ . Then  $X_0(n)$  is a  $2^n \times M$ MBN with no connections and  $X_n(n) = X(n)$ .

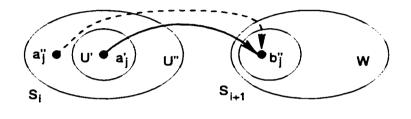

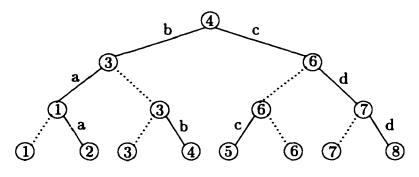

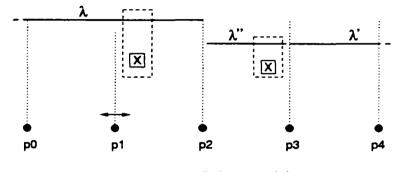

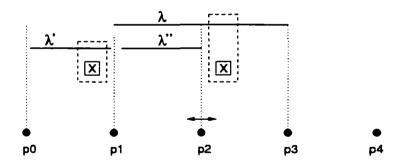

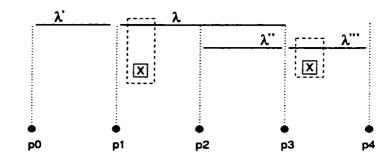

Figure 3.2: Step 1 of  $X_1(n)$

At each step s we will consider an  $2^n \times 2^{n-1}$  "sub-MBN",  $Y_s(n)$ , of  $X_s(n)$ ; i.e., connections of  $Y_s(n)$  are also connections of  $X_s(n)$ . Sub-MBN  $Y_s(n)$  consists of those connections of  $X_s(n)$  whose existence has been established. We say that a connection is *added* to mean that a previously unaccounted for connection has been detected. Therefore, the degree and the loading of the MBN changes from step to step. Running Bin(n) on an MBN can be viewed as a step by step construction of the MBN with the counted connections added at each step.

An intermediate result of Bin(n) (value at any non-root or non-leaf node of tree  $\mathcal{F}(n)$ ) is called a *partial* result. A processor p holding a partial result or an input at the end of step s (where  $0 \le s \le n$ ) is called a *result processor* of step s. Otherwise p is a *non-result processor* of step s. If the degree of the processor p at the end of step is 2, then it is called a *full processor* of step s; otherwise, p is a *non-full processor* of step s.

Clearly, all  $2^n$  processors are non-full, result processors of step 0; i.e., at the start of the algorithm. Step 1 (the first step) requires at least  $2^{n-1}$  communications (exactly  $2^{n-1}$ , if all  $2^{n-1}$  partial results generated at the end of step 1 are obtained by a direct mapping). Therefore  $X_1(n)$  is isomorphic to the MBN shown in Figure 3.2. Thus for  $1 \le s \le n$ , the terms "full" and "non-full" are synonymous with "degree-2" and "degree-1," respectively. We now list four simple consequences of X(n) being a degree-2, optimal-time, binarytree MBN; these facts are used, often without explicit mention, in subsequent discussion.

- 1. All partial results received in a step are used in the same step, and a partial result generated in a step is used up in the next step. This is because the algorithm runs optimally, so partial results cannot idle.

- 2. A direct (resp., indirect) processor of a step receives one (resp., two) partial results in that step; this follows from 1 above.

- 3. A processor receiving two partial results at a step must do so from different processors; otherwise the step will not be executed in unit time.

- 4. A processor sending a partial result cannot receive one at the same step. This is because it will have to receive two partial results and send one partial result as a processor can hold only one partial result. This is not possible on a degree-2, optimal-time MBN.

**Lemma 3.3** For any  $1 < s \le n$ , if p is a non-full, result processor of step s, then p is a non-full, result processor of steps  $1, 2, \dots, s$ .

<u>Proof:</u> It suffices to prove that if p is a non-full, result processor of step s, then it is a result processor of step s - 1. If p holds a result at the end of step s, but not at the end of step s - 1, then it must have obtained two partial results during step s. This requires p to have two connections and be a full processor of step s.

Corollary 3.4 For any  $L \leq s \leq n$ , each result processor of step s is a full processor of step s.

<u>Proof:</u> Let p be a non-full, result processor of step s. Then by Lemma 3.3, it is also a result processor of steps  $1, 2, \dots, s$ . Therefore to prove the lemma, it is sufficient to prove that s < L. Let p receive a partial result for step t (where  $1 \le t \le s$ ) from processor  $p_t$ , via the only bus b (say) to which p is connected. Therefore, bus b is connected to processors in the set  $\{p\} \cup \{p_t : 1 \le t \le s\}$ .

Consider processor  $p_t$  that sends a partial result to p during step t. If  $p_t$  is a result processor of step t, then it must receive two partial results from processors different from p (in addition to sending a partial result to p). This is not possible as one of the (at most 2) buses to which  $p_t$  is connected is used by p. Since this bus (bus b) is used by p during steps  $1, 2, \dots, s$ , processor  $p_t$  cannot be a result processor of steps  $t, t + 1, \dots, s$ . Therefore,  $p_t \notin \{p_x : t < x \le s\}$  and so  $\{p\} \cup \{p_t : 1 \le t \le s\}$  has s + 1 processors, all of which are connected to bus b. Since the loading of X(n) is L, we have  $s + 1 \le L$  (or s < L).

From this point on, we will only consider step  $s \ge L$ . Since our aim is to prove that  $L = \Omega(\sqrt{n}) \ (\Omega(\frac{n}{\log n}))$  in Section 3.5), we may assume that L < n. By Corollary 3.4, all result processors (of any step) can be assumed to be connected to 2 buses.

### 3.3.3 The Accounting Scheme

In determining a lower bound on the loading L of X(n), we will count connections between processors and buses of X(n). Let  $\langle p, b \rangle$  denote a connection between processor p and bus b. In our analysis, we will consider only those connections  $\langle p, b \rangle$  for which p is a full processor, and which participates in some step  $s \ge L$ . Since a lower bound on the loading is sought, some connections can be ignored. To account for the connections considered, we now associate each such connection with a processor. For each processor p and step  $s \ge L$ , define a set,  $\Gamma_s(p)$ , of connections owned by processor p in step s. (We will show later that if  $p_1 \neq p_2$ , then  $\Gamma_s(p_1)$  and  $\Gamma_s(p_2)$  are disjoint.) We now define  $\Gamma_s(p)$ .

- If p is a result processor of step L, then it is also a full processor of step L (by Corollary 3.4). Let p be connected to buses b<sub>1</sub> and b<sub>2</sub>. For each such p, define Γ<sub>L</sub>(p) = {⟨p, b<sub>1</sub>⟩, ⟨p, b<sub>2</sub>⟩}. If p is not a result processor of step L, then define Γ<sub>L</sub>(p) to be empty.

- 2. For s > L, let p be a result processor of step s that receives partial result(s) from (not necessarily distinct) processor(s) p' and p'' via bus(es) b' and b'', respectively. Define  $\Gamma_s(p)$ ,  $\Gamma_s(p')$  and  $\Gamma_s(p'')$  as follows.

$$\Gamma_{s}(p) = \Gamma_{s-1}(p) \cup \{ \langle p_{1}, b' \rangle, \langle p_{2}, b'' \rangle \}$$

$$\Gamma_{s}(p') = \Gamma_{s-1}(p') - \{ \langle p_{1}, b' \rangle \}$$

$$\Gamma_{s}(p'') = \Gamma_{s-1}(p'') - \{ \langle p_{2}, b'' \rangle \}$$

where  $\langle p_1, b' \rangle \in \Gamma_{s-1}(p')$  and  $\langle p_2, b'' \rangle \in \Gamma_{s-1}(p'')$ ; since we are interested primarily in the cardinality,  $|\Gamma_s(p)|$ , of  $\Gamma_s(p)$ ,  $\langle p_1, b' \rangle$  (resp.,  $\langle p_2, b'' \rangle$ ) can be any element of  $\Gamma_{s-1}(p')$  (resp.,  $\Gamma_{s-1}(p'')$ ). Note that if p receives only one value in step s, then p' = p'', b' = b'' and  $p_1 = p_2$ .

In summary, for each partial result received by processor p from processor p'via bus b, processor p' transfers ownership of a connection on bus b to processor p. If processor p does not send or receive any partial result in step s, then  $\Gamma_s(p) = \Gamma_{s-1}(p)$ .

#### Lemma 3.5 For any $s \geq L$ ,

- (i) For distinct processors  $p_1, p_2$ ,  $\Gamma_s(p_1)$  and  $\Gamma_s(p_2)$  are disjoint.

- (ii) For any processor p, if  $\langle p', b \rangle \in \Gamma_s(p)$ , then processor p is connected to bus b.

- (iii) If p is a result processor of step s, then  $\Gamma_s(p)$  has a connection of the form

- $\langle p', b \rangle$ , for each bus b to which p is connected.

<u>Proof:</u> At step L, by definition of  $\Gamma_L$ , all result processors own their connections to the two buses to which they are connected. Therefore, Lemma 3.5 holds at step L. Observe that in part 2 of the definition of  $\Gamma_s(p)$ , the sets  $\Gamma_s(p)$  and  $(\Gamma_s(p'), \Gamma_s(p''))$ are disjoint, and the connections added to  $\Gamma_s(p)$  are  $\langle p_1, b' \rangle$  and  $\langle p_2, b'' \rangle$ , where b' and b'' are buses to which p is connected. These observations, coupled with the fact that Lemma 3.5 holds for step L, completes the proof.

<u>Remarks</u>: If the sets  $\Gamma_s(p)$  are used to count the number of connections in  $X_s(n)$ , then part (i) of Lemma 3.5 ensures that no connection is counted more than once. However, some connections may not be counted at all. Part (ii) is used later in Theorem 3.9. Part (iii) ensures that the transfer of ownership in part 2 of the definition of  $\Gamma_s(p)$  is always possible.

**Lemma 3.6** For any step s > L and any processor p,  $|\Gamma_s(p)| = |\Gamma_{s-1}(p)| + \delta$ , where

$$\delta = \begin{cases} 1, & \text{if } p \text{ is a result processor of steps } s \text{ and } s - 1. \\ 2, & \text{if } p \text{ is a result processor of step } s \text{ and a non-result processor} \\ & \text{of step } s - 1. \\ -1, & \text{if } p \text{ is a non-result processor of step } s \text{ and a result processor} \\ & \text{of step } s - 1. \\ 0, & \text{if } p \text{ is a non-result processor of steps } s \text{ and } s - 1. \end{cases}$$

<u>Proof:</u> Observe that  $\delta$  is the number of partial results received by processor p in step s;  $\delta = -1$  indicates that p sends a partial result. The lemma now follows from this observation and part 2 of the definition of  $\Gamma_s(p)$ .

Corollary 3.7 For any step  $s \ge L$ , if p is a result processor of  $\alpha$  of the steps  $L, L + 1, \dots, s$ , then  $|\Gamma_s(p)| \ge \alpha$ .

<u>Proof:</u> The first time p becomes a result processor at step  $s_0$ , say, (even if  $s_0 = L$ ),  $|\Gamma_{s_0}(p)| = 2$ . For each of the remaining  $\alpha - 1$  times it is a result processor in some step  $s' > s_0$ , we consider two cases:

- Case 1: Suppose p is a result processor of steps s' 1 and s'. Here  $|\Gamma_{s'}(p)| = |\Gamma_{s'-1}(p)| + 1$  (Lemma 3.6).

- Case 2: Suppose p is a result processor of step s' and a non-result processor of step s'-1. Since  $s' > s_0$ , there is a step s'' ( $s_0 < s'' < s'$ ) such that p is a result processor of step s''-1 and a non-result processor of steps  $s'', s''+1, \dots, s'-1$ . Here  $|\Gamma_{s'}(p)| = |\Gamma_{s'-1}(p)| + 2$ ,  $|\Gamma_{s'-1}(p)| = |\Gamma_{s''}(p)|$ , and  $|\Gamma_{s''}(p)| = |\Gamma_{s''-1}(p)| - 1$  (again by Lemma 3.6). Therefore,  $|\Gamma_{s'}(p)| = |\Gamma_{s''-1}(p)| + 1$ .

In any case, for each step  $s' > s_0$  of which p is a result processor,  $\Gamma_{s'}(p)$  increases by one. Thus at the last step  $t \leq s$  of which p is a result processor,  $|\Gamma_t(p)| = 2 + (\alpha - 1) = \alpha + 1$ . If t < s, then  $|\Gamma_{t+1}(p)| = |\Gamma_s(p)| = \alpha$ .

### 3.3.4 Non-Uniform Bus Usage

In this section we show that as the binary-tree algorithm proceeds towards the root of  $\mathcal{F}(n)$ , most of the activity in the MBN centers around few buses that ultimately incur a high loading.

30

For any step  $s \ge L$ , a bus b of X(n) is said to be active in step s iff it is connected to at least one result processor of step s. If a bus is used to carry a partial result in step s, then it must be active in step s. However, a bus that is active in step s need not be used in step s. In the following lemma, we prove that the pool of buses that could be active at a step shrinks with each step, thereby forcing a few buses to have a large number of connections.

Lemma 3.8 For any step s > L, bus b is active in step s, then it is also active in step s - 1.

**Proof:** Let bus b not be active in step s - 1. Then by definition of a non-active bus, all the processors connected to b are non-result processors of step s - 1. Suppose at step s, processor p connected to b becomes a result processor of step s, thereby making b active in step s. Since p cannot be a result processor of step s - 1 (otherwise b would be an active bus in step s - 1), p must receives two results in step s from distinct processors p' and p". One of these partial results must be via bus b. Clearly the two sending processors p' and p" are full (Corollary 3.4), result processors of step s - 1. Thus, one of them must be connected to b in step s - 1, which contradicts the assumption that b is not active in step s - 1.

### 3.3.5 The Lower Bound

We are now in a position to prove the main result of this section.

**Theorem 3.9** For any  $n \ge 2$ , if a  $2^n$ -processor MBN with degree 2 and loading L runs Bin(n) optimally in n steps, then  $L = \Omega(\sqrt{n})$

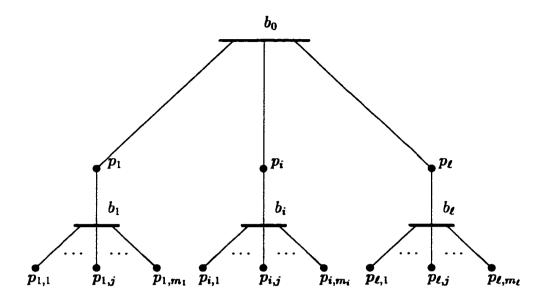

<u>Proof:</u> From Lemma 3.8, there exists a bus,  $b_0$ , that is active in steps  $L, L+1, \dots, n$ . Let  $b_0$  be connected to  $\ell \leq L$  full processors,  $p_1, p_2, \dots, p_\ell$ . For  $1 \leq i \leq \ell$ , let the two buses to which processor  $p_i$  is connected be  $b_0$  and  $b_i$ . Also let processor  $p_i$  be a result processor  $\alpha_i$  times from step L to step n.

From Lemma 3.5(*ii*), each element of  $\Gamma_n(p_i)$  is a connection to either  $b_0$  or  $b_i$ . Since the loading of the MBN is L,  $\sum_{i=1}^{\ell} |\Gamma_n(p_i)| \le \ell + \ell L \le L^2 + L$ . From Corollary 3.7 we also have  $\sum_{i=1}^{\ell} |\Gamma_n(p_i)| \ge \sum_{i=1}^{\ell} \alpha_i$ . Since  $b_0$  is an active bus of steps  $L, L+1, \dots, n$ ,  $\sum_{i=1}^{\ell} \alpha_i \ge n - L + 1$ . Thus,  $n - L + 1 \le \sum_{i=1}^{\ell} \alpha_i \le \sum_{i=1}^{\ell} |\Gamma_n(p_i)| \le L^2 + L$ , which implies that  $n \le L^2 + 2L - 1$  or  $L = \Omega(\sqrt{n})$ .

<u>Remark:</u> Theorem 3.9 proves that for large problem sizes, the product of the degree and loading of any MBN that runs a binary-tree algorithm in optimal time is at least 9, thereby establishing that the MBN,  $\mathcal{T}(n)$ , proposed in Section 3.6 has the best possible "degree-loading" product.

# **3.4** An $\Omega\left(n^{\frac{2}{3}}\right)$ Lower Bound

In the lower bound of Section 3.3, we selected a bus  $b_0$  and proved that its neighborhood (consisting of processors on  $b_0$  and buses connected to these processors) had a large number of connections. In restricting our consideration to the neighborhood of bus  $b_0$ , the technique used undercounted the number of connections in the neighborhood. Here we develop additional results that provide a more accurate count of connections, even though the consideration is expanded to a larger neighborhood.

### **3.4.1 Additional Results**

Recall the definitions of direct and indirect nodes and processors (Section 2.3.1, page 16).

**Lemma 3.10** For any  $s \ge L$ , let p be a result processor of step s + 1.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

- (i) If p is a result processor of step s, then it is a direct processor of step s + 1.

- (ii) If p is a non-result processor of step s, then the following assertions hold:

- (a) Processor p is an indirect processor of step s + 1.

- (b) The two buses to which processor p is connected are active in step s.

- (c) For each bus b to which processor p is connected, a result processor of step s (that is also connected to b) becomes a non-result processor of step s + 1.