# Multithreading Issues on Contemporary PowerPC Microprocessors

**Hugh Blemings**

A Masters Thesis. Part of the course requirements of COMP6702, Masters in eScience, The Department of Computer Science Australian National University

November 2006

© Hugh Blemings

Typeset in Palatino by  $T_E X$  and  $I A T_E X 2_{\mathcal{E}}$ .

Except where otherwise indicated, this document is my own original work. Any trademarks and product names that appear in this document are the property of their respective owners.

Hugh Blemings 29 November 2006

This thesis is respectfully dedicated to Dr. Mark Jarnyk (1963-2006). A dear friend, a mentor in all things academic, scientific & technical, a connoisseur of tea and a fine hacker. Greatly missed.

## Acknowledgements

I thank Dr Peter Strazdins, my project supervisor for his encouragement, support, guidance and input into this work. My thanks also to Dr Alistair Rendell, the convener of the COMP6702 course for his support and input along the way.

I am fortunate to work with a tremendous group of people at IBM. Thankyou to Ralph Christ, my manager at IBM, for his support in allowing me to undertake the Masters course. Just about everyone at OzLabs fielded a question from me in the last six months in relation to this work, thanks guys. My thanks also to the broader group of colleagues at The Linux Technology Centre, Systems and Technology Group and IBM Research for their support.

While personal acknowledgements are unconventional, I none the less thank my wife Lucy and daughter Rachael for their support throughout my studies. I'm looking forward to a bit more family time in 2007...

# Abstract

Contemporary high performance microprocessors are moving beyond faster clocks and wider busses to meet the growing demands for computational power. Techniques such as multiple threads of execution and heterogeneous processing cores are becoming more mainstream bringing with them interesting challenges for operating system and application developers alike.

We sought to quantitatively assess the benefit or otherwise of Chip Multi-Processing (CMP) and Simultaneous Multi-Threading (SMT) using a number of low level and artificial benchmarks, and contrast these results with those for more conventional SMP.

In this Thesis we present the results of our research and experiments on the POWER5 microprocessor.

For the majority of codes enabling SMT was shown to increase performance by 20% or more. Conversely a small number of cases saw performance drop by up to 96%.

We also demonstrate the benefit of CMP for codes such as NAS parallel when benchmarked against an SMP equivalents, improvements of 2.5x being observed in some instances.

Results from measuring low level barrier and lock performance underscores the need for hierarchical algorithms to be refined to be aware of SMT, CMP and SMP characteristics.

Overall our investigations suggest that both SMT and CMP are of benefit, often considerable, but aren't without subtle quirks.

Contents

# Contents

| Ac | knov   | vledge  | ments                                            | vii |

|----|--------|---------|--------------------------------------------------|-----|

| Al | ostrac | zt      |                                                  | ix  |

| 1  | Proj   | ect Ove | erview                                           | 1   |

|    | 1.1    | Basis o | of this Work                                     | 1   |

|    | 1.2    | Proces  | ssor Architectures Examined                      | 1   |

|    | 1.3    | Bench   | marks                                            | 2   |

|    | 1.4    | Organ   | isation                                          | 2   |

| 2  | Ben    | chmark  | S                                                | 3   |

|    | 2.1    | STREA   | AM                                               | 3   |

|    |        | 2.1.1   | Background                                       | 3   |

|    |        | 2.1.2   | Benchmark Internals                              | 3   |

|    |        |         | 2.1.2.1 Copy Kernel                              | 4   |

|    |        |         | 2.1.2.2 Scale Kernel                             | 4   |

|    |        |         | 2.1.2.3 Add Kernel                               | 4   |

|    |        |         | 2.1.2.4 Triad Kernel                             | 5   |

|    |        | 2.1.3   | Stream bandwidth calculations                    | 5   |

|    |        | 2.1.4   | Stream on MP systems                             | 5   |

|    | 2.2    |         | Parallel                                         | 5   |

|    | 2.3    | Other   | Benchmarks - Apex-Map and perflab                | 5   |

| 3  | Proc   | essor A | Architectures                                    | 7   |

|    | 3.1    | Introd  | uction                                           | 7   |

|    |        | 3.1.1   | Multithreading and Multi-Processing - A timeline | 7   |

|    |        | 3.1.2   | Chip Multi-Processing - An Overview              | 8   |

|    |        | 3.1.3   | Multithreading - An Overview                     | 8   |

|    | 3.2    | POWE    |                                                  | 9   |

|    |        | 3.2.1   | Background                                       | 9   |

|    |        | 3.2.2   | Threading Models                                 | 10  |

|    |        | 3.2.3   | Instruction Fetching on POWER5                   | 11  |

|    |        | 3.2.4   | Thread Priority                                  | 11  |

|    |        |         | 3.2.4.1 Thread Priority in Linux                 | 11  |

|    |        | 3.2.5   | Dynamic Resource Balancing                       | 12  |

|    |        | 3.2.6   | Single-threaded Operation                        | 12  |

|    |        | 3.2.7   | Memory Subsystem on POWER5                       | 12  |

|   |      |                   | 3.2.7.1        | Cache c    | n POWI                                                                                                                | ER5 .    |        |                  |     |     |     |     |     | • |     | 12       |

|---|------|-------------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------|----------|--------|------------------|-----|-----|-----|-----|-----|---|-----|----------|

|   |      |                   | 3.2.7.2        | Main M     | lemory c                                                                                                              | on POV   | VER5   |                  | ••• |     |     |     |     | • |     | 14       |

| 4 | Expe | eriment           | tal Setup      |            |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     | 15       |

|   | 4.1  |                   | -              |            |                                                                                                                       |          |        |                  |     |     |     |     |     | • |     | 15       |

|   | 4.2  | 2                 |                | emory Af   |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   |      | 4.2.1             |                | or Affinit |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   |      | 4.2.2             |                | Processor  |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   |      | 4.2.3             |                | y Affinity |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.3  | Thread            |                | , Dies, Oł |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.4  |                   |                | T and ST   | -                                                                                                                     |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.5  | -                 | -              | em         |                                                                                                                       |          | -      |                  |     |     |     |     |     |   |     | 19       |

|   | 4.6  | -                 | •••            |            |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     | 19       |

|   | 4.7  |                   |                |            |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.8  |                   |                | affinity   |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.9  | STREA             | AM Bencl       | hmark .    |                                                                                                                       |          |        |                  |     |     |     |     |     | • |     | 20       |

|   |      | 4.9.1             | Baseline       | e Setup .  |                                                                                                                       |          |        |                  |     |     |     |     |     | • |     | 20       |

|   |      | 4.9.2             | Details        | of change  | es                                                                                                                    |          |        |                  | ••• |     |     |     |     | • |     | 20       |

|   |      | 4.9.3             |                | emory &    |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 4.10 | Barrie            | r & Lock       | Benchma    | irks                                                                                                                  |          |        |                  | ••• |     |     |     |     | • |     | 21       |

|   |      | 4.10.1            | Time Ke        | eping .    |                                                                                                                       |          |        |                  | ••• |     |     |     |     | • |     | 21       |

|   |      | 4.10.2            | Barrier        | Codes .    |                                                                                                                       |          |        |                  |     |     |     |     |     | • |     | 22       |

|   |      | 4.10.3            | Round-         | Robin Lo   | ck Code                                                                                                               | s        |        |                  |     |     |     |     |     | • |     | 23       |

|   |      | 4.10.4            | Overall        | Benchma    | ırk                                                                                                                   |          |        |                  |     |     |     |     |     | • |     | 23       |

|   | 4.11 | NAS F             | Parallel B     | enchmarl   | <s< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>•</td><td></td><td>23</td></s<> |          |        |                  |     |     |     |     |     | • |     | 23       |

|   |      | 4.11.1            | Basic Se       | tup        |                                                                                                                       |          |        |                  | ••• |     |     |     |     | • |     | 23       |

| 5 | A Pe | erforma           | ance Mod       | lel for Ro | ound-Ro                                                                                                               | bin Lo   | ocking |                  |     |     |     |     |     |   |     | 29       |

|   | 5.1  |                   |                |            |                                                                                                                       |          | -      |                  |     |     |     |     |     | • |     | 29       |

|   | 5.2  | 0                 |                | model .    |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 5.3  |                   | -              | actice .   |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   | 5.4  |                   | 0 1            | overhead   |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

| 6 | Rosi | 1]te <i>k</i> - I | Discussio      |            |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     | 33       |

| 0 | 6.1  |                   |                |            |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     | 33       |

|   | 0.1  | 6.1.1             |                | ials       |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     | 33       |

|   |      | 6.1.2             |                | emory Ba   |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   |      | 0.1.2             | 6.1.2.1        | 2          | lemory E                                                                                                              |          |        |                  |     |     |     |     |     |   |     |          |

|   |      |                   | 6.1.2.1<br>6.1 |            | lemory E                                                                                                              |          |        |                  |     |     |     |     |     |   |     |          |

|   |      |                   | 6.1.2.3        |            | lemory E                                                                                                              |          |        |                  |     |     |     |     |     |   |     |          |

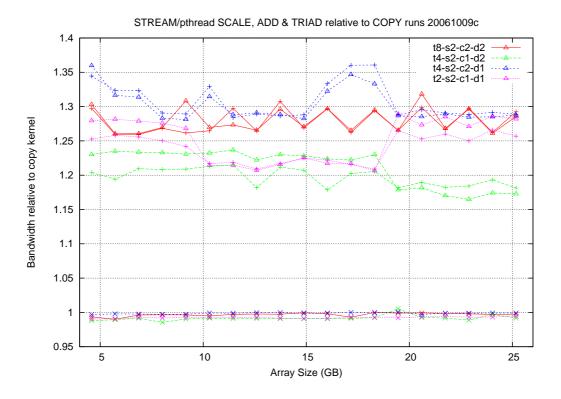

|   |      | 6.1.3             |                | Bandwidt   | 2                                                                                                                     |          |        |                  |     |     |     |     |     |   |     | 30<br>37 |

|   |      | 0.1.3             | 6.1.3.1        |            | sting Cac                                                                                                             |          |        |                  |     |     |     |     |     |   |     | 57       |

|   |      |                   | 0.1.3.1        |            | ns                                                                                                                    |          |        |                  |     |     |     |     |     |   |     | 38       |

|   |      | 6.1.4             | Compar         | rison of C |                                                                                                                       |          |        |                  |     |     |     |     |     |   |     |          |

|   |      | 0.1.4             | Compai         |            | opy with                                                                                                              | II JCale | , nuu  | <del>с</del> 111 | auc | oue | . ق | ••• | • • | • | • • | 59       |

|   |     |          | 6.1.4.1   | Specifics of non-SMT cases                      | 39  |

|---|-----|----------|-----------|-------------------------------------------------|-----|

|   |     |          | 6.1.4.2   | Specifics of SMT enabled cases                  |     |

|   |     | 6.1.5    | Conclus   | sions about STREAM results                      |     |

|   |     |          | 6.1.5.1   | A word from McCalpin                            |     |

|   |     |          | 6.1.5.2   | SMT mostly harmless?                            |     |

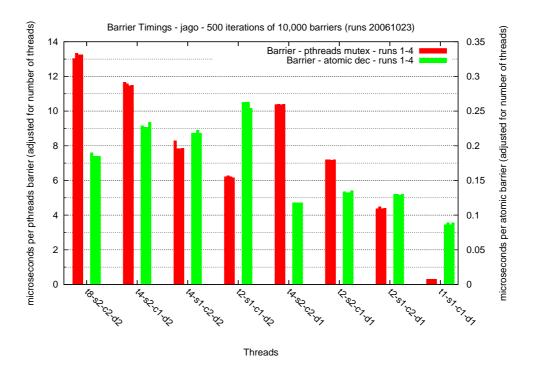

|   | 6.2 | Barrie   | r & Locki | ing Measurements                                |     |

|   |     | 6.2.1    |           | Results                                         |     |

|   |     |          | 6.2.1.1   | pthread results                                 |     |

|   |     |          | 6.2.1.2   | atomic results                                  |     |

|   |     |          | 6.2.1.3   | Influence of SMT                                | 44  |

|   |     |          | 6.2.1.4   | Conclusions for Barriers                        |     |

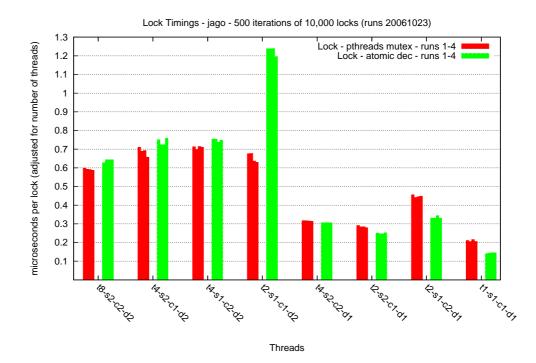

|   |     | 6.2.2    | Round-    | Robin Locking Results                           |     |

|   |     |          | 6.2.2.1   | Influence of SMT                                |     |

|   |     | 6.2.3    | Summa     | ry of SMT effects on Barrier and Locking trials |     |

|   |     | 6.2.4    |           | rison of results against model                  |     |

|   |     | 6.2.5    |           | nal Barrier and Locking Results                 |     |

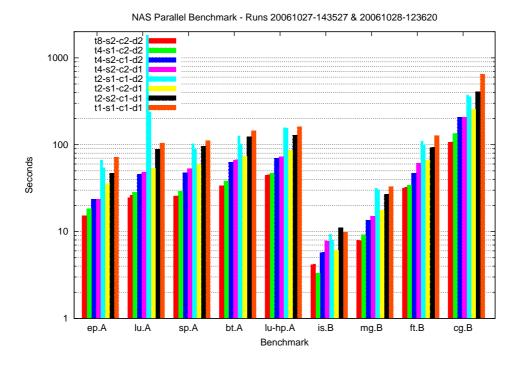

|   | 6.3 | NAS I    |           | enchmarks                                       |     |

|   |     | 6.3.1    |           | with an Outlier                                 |     |

|   |     | 6.3.2    | -         | s of non-SMT cases                              |     |

|   |     | 6.3.3    | •         | s of SMT cases                                  |     |

|   |     | 6.3.4    | 5         | inear Speedup                                   |     |

|   |     |          | 1         | 1 1                                             |     |

| 7 | Con |          | ns & Futu |                                                 | 51  |

|   | 7.1 | Concl    |           | · · · · · · · · · · · · · · · · · · ·           |     |

|   |     | 7.1.1    |           | worth it ?                                      |     |

|   |     | 7.1.2    |           | ity of selected benchmarks                      |     |

|   |     | 7.1.3    |           | for Hierarchical Barriers & Locks               |     |

|   |     | 7.1.4    | Disablir  | ng CPUs                                         | 52  |

|   |     | 7.1.5    | Multico   | re is here to stay                              | 52  |

|   | 7.2 | Future   |           |                                                 |     |

|   |     | 7.2.1    | Recordi   | ng Amount of Funny $\ldots$                     | 53  |

|   |     | 7.2.2    |           | y Bandwidth vs Locality Measurements            |     |

|   |     | 7.2.3    | Hardwa    | are Assisted Barrier Techniques                 | 54  |

|   |     | 7.2.4    | Physical  | l address chasing Kprobes                       | 54  |

|   |     | 1        | D 1/      |                                                 |     |

| Α |     |          | Results   |                                                 | 57  |

|   | A.1 | Addit    | ional Bar | rier/Lock Results                               | 57  |

| В | Oth | er artic | les       |                                                 | 59  |

| D | om  | ci uitic | 105       |                                                 | 0,0 |

| С | Oth |          | chmarks   |                                                 | 61  |

|   | C.1 | Apex-    | map       |                                                 | 61  |

|   |     | C.1.1    | Backgro   | ound                                            | 61  |

|   |     |          |           | ark Internals                                   |     |

|   | C.2 |          |           |                                                 |     |

|   |     | -        |           |                                                 |     |

xiii

| C.2.1        | Background & Benchmark Operation | 62 |

|--------------|----------------------------------|----|

| C.2.2        | Perflab in Our Work              | 62 |

|              |                                  |    |

| Bibliography |                                  | 63 |

## **Project Overview**

Simultaneous Multi Threading (SMT) and Chip Multi-Processing (CMP) have become commonplace in the last few years. The Australian National University's Department of Computer Science (DCS) had recently taken delivery of a pair of OpenPOWER 720 systems. The machines came courtesy of the Canberra based "OzLabs" group within IBM's Linux Technology Centre. The desire to make use of the latter to better understand the former was formalised in a proposal for a Masters literature review and subsequent research project.

In this thesis we start with relevant findings in the earlier literature review [Blemings 2006]. From here we explore the POWER5 processor architecture in some detail, conduct a series of experiments to quantify memory bandwidth, barrier/locking primitives and overall system performance using NAS Parallel.

Results are provided and discussed, particularly the contrast of SMP, SMT and CMP. We conclude with some thoughts on potential future work and lessons learned.

## **1.1 Basis of this Work**

Simply put, we took two of the benchmarks identified in the Literature Review, added one of our own and proceeded to run this on the OpenPOWER720 system in a variety of CPU configurations.

From this we were able to determine the differing performance traits of SMP, CMP and SMT, discovering a couple of surprises along the way.

## **1.2 Processor Architectures Examined**

This thesis focuses on IBM's POWER5 architecture which we describe in detail in Section 3.2.

Both the Sun UltraSPARC T1 (aka Niagara) and Sony/Toshiba/IBM Cell Broadband Engine (CBE - aka the Playstation3 chip) were discussed in our earlier literature review [Blemings 2006] and represent two other approaches to multiprocessing.

## 1.3 Benchmarks

Based on our earlier work we describe two benchmarks in Chapter 2, STREAM §2.1 and NAS Parallel §2.2.

In §4.10 we describe some code written to allow us to quantify low level barrier and locking performance.

## 1.4 Organisation

This thesis is divided into seven chapters. This chapter provides an overview of the work and it's motivations. Chapter 2 introduces the STREAM and NAS benchmarks and makes note of two other benchmarks that, while not used in this work, are relevant to the general area of study. Chapter 3 discusses microprocessor architectures in particular IBM's POWER5 design which is the centre piece of this work. Chapter 4 details the experimental setup used, including code specifically written for the project and modifications to existing codes. Chapter 5 proposes a simple model for the performance of round-robin locking algorithms. Chapter 6 details our results and Chapter 7 provides some conclusions and direction for future work.

## **Benchmarks**

In this chapter we describe two benchmarks that are used in our experiments and give pointers to two others that warrant consideration in future work.

## 2.1 STREAM

#### 2.1.1 Background

The STREAM benchmark is a tool that allows memory bandwidth to be measured. Aimed at high performance systems or supercomputers, it is the work of John D. McCalpin, then of University of Delaware, now at AMD by way of SGI and IBM. To keep STREAM vendor independent it is hosted and overseen by two academics at the University of Virginia.

The intent of STREAM is not to suggest that "real" applications have no data re-use, but rather to decouple the measurement of the memory subsystem from the hypothetical "peak" performance of the machine. In this respect the test is quite complementary to the LINPACK benchmark test, which is typically optimised to the point that a very large fraction of full speed is obtained on modern machines, independent of the performance of their memory systems. [McCalpin 1995]

On uniprocessor machines, the benchmark can be trivially compiled and run. For use on multiprocessor systems, STREAM is designed to make use of OpenMP or MPI libraries for SMP and cluster machines respectively. As we cover in Section 4.9, we ended up modifying STREAM quite extensively for our work.

Data is available from the University of Virginia web site for a large range of machines. We make use of the data for the OpenPOWER 720 to validate our results.

#### 2.1.2 Benchmark Internals

STREAM does some initial setup to attempt to determine timer accuracy on the host system and work out sane values for the amount of memory to use.

Thus equipped, it repeats four simple kernels ten times, each kernel working on several tens megabytes of data assuming default settings. This data set size ensures that main memory must be used - the benchmark cannot "fit" purely within cache.

The four kernels are Copy, Scale, Add, and Triad. McCalpin describes them thus;

Each of the four tests adds independent information to the results:

- "Copy" measures transfer rates in the absence of arithmetic.

- "Scale" adds a simple arithmetic operation.

- "Sum" adds a third operand to allow multiple load/store ports on vector machines to be tested.

- "Triad" allows chained/overlapped/fused multiply/add operations.

We now examine each kernel. N is the size of the arrays (2,000,000 by default), a[], b[], c[] are the three pre-allocated arrays of doubles which are used in various ways by each kernel. scalar is a double set to 3 before the kernels are run, this value ensuring the compiler will not optimise the multiplication to bitwise shifts.

#### 2.1.2.1 Copy Kernel

The Copy kernel has one read and one write operation per iteration for a total of two memory operations per iteration.

```

for (j=0; j<N; j++)

c[j] = a[j];</pre>

```

#### 2.1.2.2 Scale Kernel

The Scale kernel is effectively one read and one write operation per iteration. As McCalpin alludes to, on modern machines we can assume that scalar will be held in a register and that the execution time for the multiply operation will be insignificant compared to the main memory accesses. Like Copy this gives a total of two memory operations per iteration.

```

for (j=0; j<N; j++)

b[j] = scalar * c[j];</pre>

```

#### 2.1.2.3 Add Kernel

The Add kernel is two reads, one write and one arithmetic operation per loop iteration - a total of three memory operations.

for (j=0; j<N; j++)

c[j] = a[j] + b[j];</pre>

#### 2.1.2.4 Triad Kernel

The Triad kernel is effectively two reads and one write, we again assume that the multiply operation will be insignificant relative to the memory accesses and that scalar will be held in a register. Like Add this gives three memory operations per cycle.

#### 2.1.3 Stream bandwidth calculations

As each benchmark is run the time taken for the specified number of trials is measured and from this the number of iterations per second calculated. This is then multiplied by the number of memory operations per iteration (two or three) and the size of the data structures in use to arrive at the final bandwidth figure.

#### 2.1.4 Stream on MP systems

Stream is designed to make use of OpenMP if it is available and parallelise the kernels appropriately through use of #pragma omp parallel for.

If OpenMP is unavailable, the author of stream suggests running one instance per CPU as separate processes with large values of N so they keep going for some time. The final instance is then run "normally" and the results manually calculated on the basis of these figures multiplied by the number of instances running. [McCalpin 2006]

As is discussed in Section 4.9 we followed this approach to begin with and then moved to customise STREAM to provide better control over memory and processor affinity.

### 2.2 NAS Parallel

The NAS Parallel Benchmarks (NPB) are a set of programs that assist in evaluation the performance of parallel supercomputers. The work of NASA, NPB 1.0 was developed in the late 1980's and published shortly thereafter [Bailey et al. 1991] Derived from CFD applications NPB 1.0 consists of five kernels and three pseudo-applications.

The 1991 work is updated in [Bailey et al. 1994] and [Bailey et al. 1995] sees substantial changes to NPB with the release of NPB 2.0.

The NPB have been investigated within DCS before on several occasions including work done by Jean [Jean 2005] and the SPARC-Sulima team<sup>1</sup>

Jean provides a concise description of NPB in his 2005 paper which we commend to the reader for further information.

## 2.3 Other Benchmarks - Apex-Map and perflab

Two other benchmarks were discussed in the literature review [Blemings 2006] which preceded our work this semester: Apex-Map, a memory benchmark, and perflab, a set of codes for evaluating locking algorithms.

<sup>&</sup>lt;sup>1</sup>http://cs.anu.edu.au/Peter.Strazdins/postgrad/completed/NPBArchEvals.html. This work sought to explore the effects of architectural changes on system performance when running these benchmarks.

We ran Apex-map in a single thread configuration to get some experience with it but ultimately, largely due to time constraints, elected to stick with STREAM.

perflab was not used as we lacked time to fully understand its operation and elected to concentrate on lower level locking codes.

While in we did not make use of either they both have the potential to be useful in future work in this area and so we have included our original observations about them, slightly updated, in Appendix C.1 (Apex-map) and Appendix C.2 (perflab).

## **Processor Architectures**

## 3.1 Introduction

In the literature review that preceded this work we examined three process architectures in varying degrees of detail: IBM's POWER5, The Sony/Toshiba/IBM Cell Broadband Engine (CBE) and Sun's UltraSPARC T1 (aka Niagara). All three provide multiple threads on a single core but beyond that they are quite different devices.

The focus on our research was the IBM POWER5 and accordingly it is this architecture we detail in the following sections. First however a general perspective on Multithreading and Multi-processing.

#### 3.1.1 Multithreading and Multi-Processing - A timeline

Symmetric Multi-Threading (SMT) and Chip Multi-Processing (CMP) are not new concepts. In 1995 Tullsen, Eggers and Levy made a case for SMT [Tullsen et al. 1995] and 1996 saw Olukotun et al. advancing an argument for CMP [Olukotun et al. 1996]. The following year Hammond, Nayfeh and Olukotun contributed to a Theme Feature on Billion Transistor Microprocessors in IEEE Computer, once again putting the case for CMP [Hammond et al. 1997].

All three works have a common theme - that conventional uniprocessor models will only get us so far into the future before thread level parallelism of some form or other will be required. They argue that in order to meet the growing demands for computational power, it will no longer be sufficient to rely on faster clock rates and increasingly aggressive out of order execution and pipelining.

While on the basis of various vendors marketing, one might assume otherwise, implementations of SMT and/or CMP are not all that new either. In 2000 IBM's RS64 IV processors provided coarse grained SMT capability [Borkenhagen et al. 2000] and CMP was a centrepiece of the IBM POWER4 line in 2001 [Tendler et al. 2002]. SMT also appeared as in Intel Xeon (HT)<sup>1</sup> offerings in late 2000.<sup>2</sup>

That said, it could be fairly argued that SMT only reached mainstream consciousness with the release of the Intel Pentium4 (HT) microprocessor circa 2004. While CMP has been commonplace in IBM's POWER CPUs for some time now, being server oriented parts they are perhaps rather less visible than Intel's offerings.

In early 2006 we find it starting to sink in within industry that multiple threads of execution, be they SMT, CMP or both is indeed the direction of the future and that accordingly there

<sup>&</sup>lt;sup>1</sup>Pentium4 CPUs implemented what Intel called Hyper-Threading Technology - using the nomenclature of this paper, HT is SMT as we define below.

<sup>&</sup>lt;sup>2</sup>Implementations may go back further than this to the mid 1960's - we were reminded that the I/O processors of the CDC6600 system were multithreaded.

is a need to adopt threading in their applications.

In their work on CMP, the authors of [Spracklen and Abraham 2005] present an interesting mental picture: "In our taxonomy, SMT and CMP are two extremes of a continuum characterised by varying degrees of sharing of on-chip resources among the strands." As we shall see, many contemporary microprocessors all but span this continuum on a single die.

#### 3.1.2 Chip Multi-Processing - An Overview

CMP is conceptually straightforward. Take two or more normal processor cores, put a standard SMP interconnect between them, possibly share some cache, shared or separate memory controllers and there's your design. This simplicity is of course attractive to designers as it reduces design complexity and test overhead. There are some variations on this basic approach, for example having a FPU shared between cores as is seen on the UltraSPARC T1, but the essence of the CMP approach remains.

CMP is also attractive from a software standpoint - they appear as a conventional SMP. Depending on the design there may be NUMA effects, the details of the particular design will dictate to what extent this is the case.

#### 3.1.3 Multithreading - An Overview

Multithreading is a more subtle approach to achieving multiple threads of execution. Several different approaches are used, defined in [Sinharoy et al. 2005] as Coarse-grain Multithreading, Fine-grain Multithreading and Simultaneous Multithreading.

The three approaches differ in the detail of how threads are run. For example switching threads every cycle versus switching due to a long latency event and/or whether different execution units on the core allow instructions from different threads to run simultaneously or not.

Armed with these initial remarks, we quote from [Sinharoy et al. 2005, pp 506]

In coarse-grain multithreading, only one thread executes at any given instant in time. When a thread encounters a long-latency event, such as a cache miss, the hardware swaps in a second thread to use the machine resources rather than letting it idle. By allowing other work to use what otherwise would have been idle cycles, overall system throughput is increased. To conserve chip area, both threads share many of the system resources, such as architected registers. Hence, to swap program control from one thread to another requires several cycles. IBM introduced coarse-grain threading on the IBM pSeries S85 [Borkenhagen et al. 2000].

Fine-grain multithreading switches between threads each cycle. In this class of machines [Alverson et al. 1990], a different thread is executed in a round-robin fashion. As in coarse-grain multithreading, the architected states of multiple threads are all maintained in the processor. Fine-grain multithreading allows overlap of short pipeline latencies by letting another thread fill in execution gaps that would otherwise exist. With a larger number of threads, longer latencies can be successfully overlapped. For long-latency events in a single thread, if the number of threads is less than the number of latency cycles, there will be empty execution cycles for that thread. To accommodate this design, hardware facilities are duplicated. When a thread encounters a long-latency event, its cycles remain unused.

Simultaneous multithreading maintains the architected states of multiple threads. This type of multithreading is distinguished by having the ability to schedule instructions from all threads concurrently [Tullsen et al. 1995]. On any given cycle, instructions from one or more threads may be executing on different execution units. With SMT, the system adjusts dynamically to the environment, allowing instructions to execute from each thread if possible while allowing instructions from one thread to utilise all of the execution units if the other thread(s) cannot make use of them. This allows the system to dynamically adjust to the environment. The POWER5 system implements two threads per processor core. Both threads share execution units if both have work to do. If one thread is waiting for a long-latency event, the other thread can achieve a greater share of execution unit time.

#### **3.2 POWER5**

The IBM POWER5 Microprocessor is a two-way simultaneous multithreaded (SMT) dual core (CMP) chip. Each die includes;

- 64k, two way set associative L1 Instruction cache for each core

- 32k, four way set associative L1 Data for each core

- 1.875MB of 10 way set associative L2 cache shared between the two cores

- Directory and interface logic for the external L3 cache (36MB)

- DRAM controller

- Fabric interconnect

- I/O interconnect

- Power management, JTAG interfaces etc.

- Clock frequencies ≃1.65GHz and above (system dependent)

#### 3.2.1 Background

POWER5 is a descendant from the earlier POWER4 and POWER3 architectures which are nicely detailed in [Tendler et al. 2002] and [Papermaster et al. 1998] respectively.<sup>3</sup>

POWER5 is designed to allow effective scalability up to 64 physical processors (128 threads) at one extreme yet be a good fit for one and two way systems. Physically this achieved by having three building blocks.

- A Multi Chip Module (MCM) sees four POWER5 and four cache chips brought together on a single ceramic substrate 95mm on a side. Thus an MCM has eight complete cores (16 threads). MCMs are most commonly used in larger SMP configurations.

- A Quad Chip Module (QCM) sees two POWER5 CPUs and two cache chips on a single ceramic package for a total of four cores/eight threads. QCMs are used in more recent single rack unit designs.

<sup>&</sup>lt;sup>3</sup>If a longer historical view is sought, a brief but accurate history of POWER, PowerPC and associated technologies appears in "POWER to the people" [Mikes 2004]

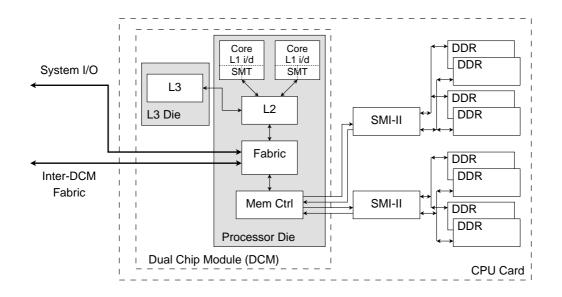

**Figure 3.1:** POWER5 Block Diagram. Two such cards are used in the 4-Way configuration of the OpenPower 720

• The Dual Chip Module (DCM) is shown with it's associated memory sub-system in Figure 3.1). The DCM comprises a single CPU and cache chip and provides a two core/four thread building block<sup>4</sup>. Two DCMs are used in the OpenPower 720.

The POWER5 is a complex part and a working knowledge will be important to our understanding.<sup>5</sup> Hence we will cover it's internals in more detail in the following sections.

#### 3.2.2 Threading Models

Sections 3.1.3 and 3.1.2 provide general descriptions of threading models. Using those definitions POWER5 is an CMP design where each core also supports SMT. POWER5 is also able to run in single-threaded (ST) mode - SMT disabled - as well as allowing one of the two cores on a chip to be disabled - CMP disabled.

From a software standpoint this allows a single chip to look like;

- A Uni-processor a single thread of execution no SMT or CMP

- A 2-Way SMP two threads of execution, each with an entire core to itself CMP

- A 2-Way SMP two threads of execution, both threads residing on a single core SMT

- A 4-Way SMP four threads of execution, two threads per core, two cores operating -CMP with SMT

These different modes of operation have some interesting side effects in relation to memory bandwidth and overall computational capability and are a focus of our work.

<sup>&</sup>lt;sup>4</sup>It is this combination of CPU and cache die that gives the "Dual" in DCM

<sup>&</sup>lt;sup>5</sup>[Kalla et al. 2004] and [Sinharoy et al. 2005] provide a detailed description of POWER5 written by key members of the POWER5 design team.

#### 3.2.3 Instruction Fetching on POWER5

It is useful for us to understand the details of instructions fetch/decode on the microprocessor, again we quote from [Sinharoy et al. 2005, pp 508];

In SMT mode, two separate program counters are used, one for each thread. Instruction fetches alternate between the two threads. Similarly, branch prediction alternates between threads. In Single Threaded (ST) mode, only one program counter is used, and instructions can be fetched for that thread every cycle.

[...]

Up to eight instructions can be fetched from the instruction cache (IC pipeline stage) every cycle.

Recall that this ability to run separate threads of execution simultaneously on different execution units is what makes POWER5 SMT rather than (say) Fine-grained Multithreaded.

IBM have an article available on instruction fetching and CPI analysis available on their Developer Works website <sup>6</sup> which treats this topic further.

#### 3.2.4 Thread Priority

In a multithreaded system, one thread may use a significant amount of system resources, potentially blocking other threads. [Sinharoy et al. 2005, pp 511] Accordingly the POWER5 design provides various mechanisms to optimise resource usage and balance between threads.

Each thread has eight software controlled priority levels, some levels can only be accessed when the processor is in privileged mode, the balance can be set from user space. When not running, a thread is at Level 0, Levels 1 (the lowest) through to 7 (the highest) apply when the thread is executing. While set by software, these priorities are enforced by hardware.

Electrical power is also conserved automatically by the POWER5 core. When both threads are at Level 1 instruction decode is throttled by hardware.

#### 3.2.4.1 Thread Priority in Linux

The Linux kernel makes use of thread priority, adjusting it up or down slightly when entering certain sections of code. In the kernel code the more generic abbreviation HMT (Hardware Multi Threading) is used. In spin loops for example, HMT\_low() is used. The kernel idle loop will call to HMT\_very\_low() while doing nothing and HMT\_medium() during normal operation. Linux does not currently force a priority above HMT\_medium() - recall these priorities are relative so the core still runs at full speed when it is able.

The macros defined in ./include/asm-powerpc/processor.hillustrate how special instances of the or instruction<sup>7</sup> are used to set thread priority

```

/* Macros for adjusting thread priority (hardware multi-threading) */

#define HMT_very_low() asm volatile("or 31,31,31 # very low priority")

#define HMT_low() asm volatile("or 1,1,1 # low priority")

#define HMT_medium_low() asm volatile("or 6,6,6 # medium low priority")

#define HMT_medium() asm volatile("or 2,2,2 # medium priority")

#define HMT_medium_high() asm volatile("or 5,5,5 # medium high priority")

#define HMT_high() asm volatile("or 3,3,3 # high priority")

```

<sup>6</sup>http://www-128.ibm.com/developerworks/power/library/pa-cpipower1

<sup>7</sup>as used this is effectively a nop

#### 3.2.5 Dynamic Resource Balancing

"Depending on the situation, the POWER5 microprocessor employs one of three mechanisms to throttle threads to perform dynamic resource balancing." [Sinharoy et al. 2005, pp 511]

Firstly, in addition to the software control over priority level mentioned above, the POWER5 core can temporarily adjust the level of a thread to throttle its execution. Such a decision is based on instruction completion statistics gathered from the instruction completion logic on the core.

Secondly, the L2 miss rate for each thread is monitored and when it rises above a specified value, instruction decode for that thread is temporarily disabled.

The final mechanism is employed when an instruction is decoded which will take a long time to complete. For example, sync instructions or an instruction that will cause a stall due to resource contention. Under such situations the core will flush all of the instructions for that thread and inhibit further decodes until the instruction completes.

#### 3.2.6 Single-threaded Operation

While designed to be used in an SMT configuration, the POWER5 cores can be placed in a ST mode. [Sinharoy et al. 2005, pp 514] provides a cogent description of this feature of POWER5;

Not all applications benefit from SMT. Applications whose performance is executionunit-limited or which are consuming all of the POWER5 chip memory bandwidth will not see additional performance by having two such threads executing on the same processor. For this reason, POWER5 systems support single-threaded execution mode. In single-threaded mode, a POWER5 system makes all of the rename registers, issue queues, the Load Reorder Queue, and the Store Reorder Queue available to the active thread. This gives the single active thread more rename registers to use, allowing it to achieve higher performance levels than a POWER4 system at equivalent frequencies. Software can dynamically change a processor between single-threaded and SMT modes.

#### 3.2.7 Memory Subsystem on POWER5

The memory subsystem plays a significant role in determining the computers performance characteristics.

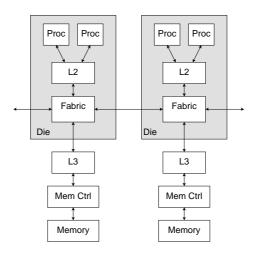

In examining the POWER5 memory system, it is useful to contrast it with that of POWER4 (Figure 3.2) that preceded it. Table 3.1 shows this evolution and is drawn from information in [Papermaster et al. 1998], [Tendler et al. 2002], [Sinharoy et al. 2005] and [DeMone 2004].

In examining the information in Table 3.1 and Figures 3.1 and 3.2 it can be seen that in POWER5 cache has been moved closer to the core. Further main memory is now accessed through a separate channel to L3, these two changes along with other tweaks have brought a significant reduction in latency and increase in bandwidth.

We now examine the memory subsystem in a more detail, the reader may wish to refer to Figure 3.1 as we proceed. Note that where bandwidths or latencies are quoted as absolute figures they assume a 1.65GHz core frequency.

#### 3.2.7.1 Cache on POWER5

There are three levels of cache on a POWER5 system, L1, L2 and L3. On systems with multiple DCMs, cross fabric reads of cache are possible which are referred to as L2.75 and L3.75 accesses.

|           | POWER4                         | POWER5                         |  |  |  |  |

|-----------|--------------------------------|--------------------------------|--|--|--|--|

| L1 ICache | 64kB Direct Mapped             | 64kB 2-way associative         |  |  |  |  |

| L1 DCache | 32kB 2-way associative         | 32kB 4-way associative         |  |  |  |  |

| L2 Cache  | 1.44MB 8-way associative       | 1.92MB 10-way associative      |  |  |  |  |

|           | 12 cycle latency               | 13 cycle latency               |  |  |  |  |

| L3 Cache  | 32MB 8-way associative         | 36MB 12-way associative        |  |  |  |  |

|           | 123 cycle latency              | 87 cycle latency               |  |  |  |  |

|           | Clocked at $1/3$ CPU frequency | Clocked at $1/2$ CPU frequency |  |  |  |  |

| Memory    | $\simeq 4$ GB per die          | $\simeq 16$ GB per die         |  |  |  |  |

|           | 351 cycle latency              | 220 cycle latency              |  |  |  |  |

Table 3.1: POWER4 / POWER5 Memory characteristics

Figure 3.2: POWER4 Block Diagram

Each core has its own L1 cache, hence there are a pair per DCM. They operate at the processor frequency and have hardware coherency. The L1 Instruction cache is 32kB in size, 128 byte lines with two way associativity and a FIFO replacement policy. The L1 Data cache is 32kB in size, 128 byte lines, four way set associative with LRU, store through. Latency is two cycles, bandwidth  $\simeq$  26GB/s.

There is a single L2 cache per DCM of 1.92MB comprised of three slices of 640kB each. L2 is 10 way set-associative with an LRU replacement policy and 128B line size.

Each core on the DCM has a separate port to each of the three L2 slices with a latency of 13 cycles and a theoretical peak bandwidth of  $\simeq$  52GB/s. Additionally each slice has independent access to the fabric, other cores in the system can read/write data to the L2 directly. These L2.75 operations have a latency of around 140 cycles and a peak theoretical bandwidth of  $\simeq$  39GB/s L2 to Fabric and  $\simeq$  79GB/s Fabric to L2.

Each DCM has it's own L3 comprised of three slices of 12MB each for a total of 36MB. The L3 is 12 way set-associative, LRU replacement and has a 256 byte line size. The L3 acts as a victim cache of L2 and has one read and one write port to each L2 slice and a port to the fabric. Latency to the local CPUs is some 87 cycles, 140 cycles for an L3.75 access from another DCM. Peak bandwidth is  $\simeq$  13GB/s read and write.

#### 3.2.7.2 Main Memory on POWER5

Main memory on POWER5 systems is DDR or DDR2 based depending on the model in question. Here we confine ourselves to the arrangement on the OpenPOWER 720.

Each processor card contains half the system memory, thus a 32GB system has 16GB attached to each DCM. Referring to Figure 3.1 it can be seen that each card has eight 266MHz DDR ECC memory modules installed in pairs, two pairs per memory controller.

The SMI-II memory controllers straddle two asynchronous clock domains, the processors' on one side, DDR memory on the other. The interface to the core itself has an eight byte wide read port and a two byte wide write port and operates at half the core frequency. The interface on the memory side is eight bytes wide and operates at the DRAM frequency<sup>8</sup>

On the OpenPOWER720 the SMI-II's are configured to share the physical address space, thus sequential reads and writes are interleaved across the available DIMMs yielding a theoretical per DCM bandwidth of 10.41GB/s.

The memory controllers also perform background operations related to ECC and reliability functions on the system.

<sup>&</sup>lt;sup>8</sup>the internal logic in this side of the SMI-II operates at twice the DRAM clock

## **Experimental Setup**

## 4.1 Systems Used

Except where noted otherwise, all results discussed in the following sections were produced on an IBM OpenPOWER 720 system. While DCS have two such systems of their own our work primarily utilised a system made available at IBM's OzLabs facility. This avoided inconvenience to other students using the DCS machines as well as providing a relatively known "background" workload for our measurements.

The machine in question *jago* has two CPU cards as shown in Figure 3.1, each with a 1.65GHz CPU and 16GB of RAM. This provides a total of four POWER5 CPUs and 32GB of RAM in a single system image<sup>1</sup>.

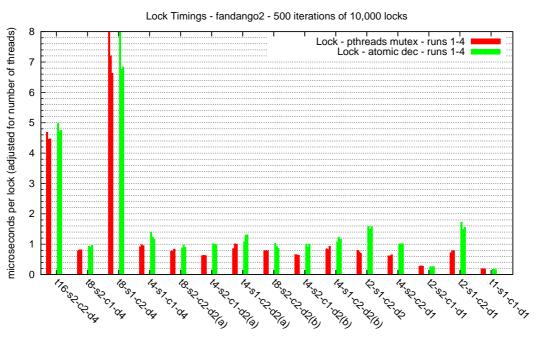

For our barrier/locking experiments a larger machine was used to give a greater range of processor options. This machine, *fandango2*<sup>2</sup>, is an eight POWER5 processor IBM pSeries 570 with 16GB RAM.

Architecturally the two systems are all but identical, built as they are from DCM building blocks as shown in Figure 3.1.

## 4.2 Processor & Memory Affinity under Linux

Linux has well thought out support for both processor and memory affinity both of which we rely on in our work.

| SMP:     |      | DC   | M1    |      | DCM0  |      |       |      |  |  |

|----------|------|------|-------|------|-------|------|-------|------|--|--|

| CMT:     | Co   | re1  | Core0 |      | Core1 |      | Core0 |      |  |  |

| SMT:     | SMT1 | SMT0 | SMT1  | SMT0 | SMT1  | SMT0 | SMT1  | SMT0 |  |  |

| Bitmask: | 0x80 | 0x40 | 0x20  | 0x10 | 0x08  | 0x04 | 0x02  | 0x01 |  |  |

| CPU ID:  | 7    | 6    | 5     | 4    | 3     | 2    | 1     | 0    |  |  |

Table 4.1: Layout of CPU bitmask for four way OpenPOWER720

<sup>&</sup>lt;sup>1</sup>These systems support *partitioning* into multiple system images, something we did not make use of in our work

<sup>&</sup>lt;sup>2</sup>It is an OzLabs tradition to name PowerPC machines with names ending in "go"

#### 4.2.1 Processor Affinity

From the user or application standpoint Linux takes a simple approach to dealing with different combinations of SMT, CMP and SMP - everything is considered a CPU. Internally of course the scheduler is aware of the subtleties of both SMT and CMP and endeavours to assign work accordingly.

Processors are numbered based on an underlying bitmask structure, that is to say a system can have CPU0, CPU1, CPU4 and CPU5. This bitmask gives some recognition to the underlying layout of CPU cards, dies, cpus and threads. In the case of the OpenPOWER720 however it is pretty straightforward as seen in Table 4.1.

#### 4.2.2 Setting Processor Affinity

There are two approaches to setting processor affinity under Linux that we used in our work.

The first is to use the taskset utility from the command line. Part of the sched-utils<sup>3</sup> package, it allows the user to run a command and limit it to a particular set of CPUs. Thus on *jago*, running taskset 0x55 foo would invoke the command foo and confine it to using the SMT0 threads on each of the four cores.

While taskset is useful for quick tests it doesn't implicitly bind a thread of execution within the target application to a particular CPU. The scheduler or internal actions of the called application could cause a thread to migrate to different CPUs within the mask.

The second approach, the use of implicit calls to the setaffiniy() and getaffinity() functions, mitigates this problem by tying the calling thread to the CPU specified. For our work the procedure in Figure 4.1was used.

```

/* Master Thread */

for each thread {

/* Create and start threads */

create_thread(thread_id, cpu_mask);

}

/* Now wait for worker threads to finish */

join();

/* Within each thread */

create_thread(thread_it, cpu_mask) {

/* Bind thread to required CPU, quit on failure */

setaffinity(cpu_mask);

/* Allocate and touch memory to ensure affinity */

allocate_memory();

touch_memory();

/* Run codes */

do_work();

}

```

Figure 4.1: Pseudo code for setting processor affinity

<sup>&</sup>lt;sup>3</sup>http://freshmeat.net/projects/sched-utils

#### 4.2.3 Memory Affinity

By default memory affinity is handled automatically - memory requested by a thread of execution will be allocated from the node closest the CPU on which it is running when the page is first touched. In recent kernels<sup>4</sup> this can be over-ridden but the interfaces to handle this, particularly to user space, are still somewhat in flux.

## 4.3 Threads, Cores, Dies, Oh My!

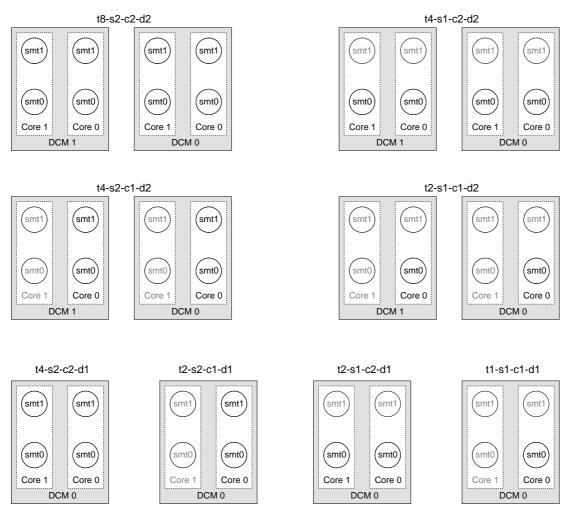

As discussed in §1.1 our work focussed on investigating the different combinations of SMP, CMP and SMT. In practice this meant we had one combination of SMP/CMP/SMT when utilising eight processor threads, three combinations of SMP/CMP/SMT when utilising four threads, three when utilising two threads and one for a single processor thread of execution.

We refer to a single core as being either in SMT mode (two threads) or non-SMT mode (one thread). This latter case we will refer to as ST for Single Threaded mode in most cases for grammatical simplicity.

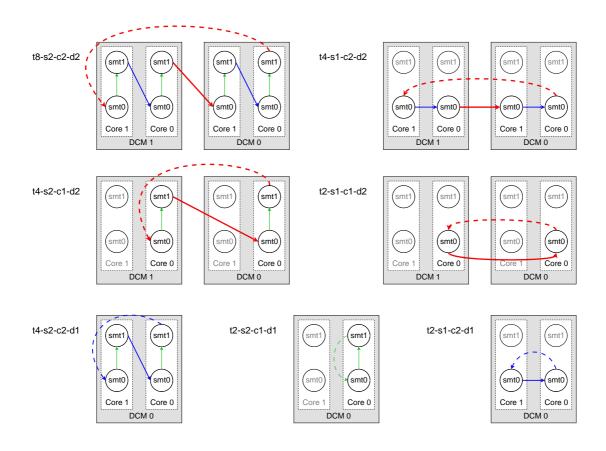

We arrived at the following naming scheme to (hopefully!) make the configuration in use clear. The reader may wish to refer back to Section 3.2.1 and the diagram at Figure 4.2 as they proceed through the following.

The four pieces of information we needed to convey were;

- 1. Total number of threads denoted **t** for the OpenPOWER 720 this is between one and eight

- 2. Number of SMT threads per CPU denoted **s** either one (SMT disabled ST) or two (SMT enabled) for POWER5

- 3. Number of CPU cores in use for each die denoted c either one or two for POWER5

- Number of dies/DCMs in use denoted d for the OpenPOWER 720 this is also one or two

Thus for the OpenPOWER 720 we arrived at eight different combinations;

- t8-s2-c2-d2 Eight CPU threads active using both DCMs, both CPUs within each DCM enabled and SMT enabled on all four CPUs. This is essentially the "full" configuration for the OpenPOWER 720

- t4-s1-c2-d2 Four CPU threads active using both DCMs, both CPUs within each DCM in use, SMT disabled on both CPUs (ST). This is nominally the most balanced four thread configuration.

- **t4-s2-c1-d2** Four CPU threads active using both DCMs, only one CPU within each DCM in use, SMT enabled on each active CPUs (ST). This is a less balanced four thread configuration than the one above.

- t4-s2-c2-d1 Four CPU threads active using one DCM, both CPUs within that DCM enabled, SMT enabled on both CPUs. This is the "pathological" four thread configuration the threads of one entire DCM remains idle.

- t2-s1-c1-d2 Two CPU threads active utilising two DCMs, only one CPUs within each DCM enabled and SMT disabled (ST). This is most balanced two thread configuration.

<sup>&</sup>lt;sup>4</sup>linux-2.6.17 or so onwards

- **t2-s1-c2-d1** Two CPU threads active utilising one DCM, both CPUs within that DCM enabled but SMT disabled. This configuration leaves the second DCM largely unused.

- t2-s2-c1-d1 Two CPU threads active utilising one DCM, one CPU within the DCM enabled, SMT enabled. This configuration leaves both the second CPU on the active DCM unused as well as the the second DCM largely unused.

- t1-s1-c1-d1 One CPU thread active utilising one DCM, one CPU within that DCM enabled, SMT disabled. This configuration leaves both the second CPU on the active DCM unused as well as the the second DCM largely unused.

Figure 4.2 illustrates these different combinations.

The naming scheme assumes that there is no difference between cores and threads on a particular CPU. That is to say that Core 0 and Core 1 will perform identically if run in isolation and similarly that SMT0 and SMT1 within a core will perform identically if run with the other SMT thread inactive.

**Figure 4.2:** The eight different threading combinations described in §4.3 shown diagrammatically

## 4.4 Comparing SMT and ST - "SMT vs ST pairs"

It should now be evident that on an eight way system like *jago* we have four combinations that will show the difference between SMT and non-SMT (ST) operation.

- t8-s2-c2-d2 vs t4-s1-c2-d2

- t4-s2-c1-d2 vs t2-s1-c1-d2

- t4-s2-c2-d1 vs t2-s1-c2-d1

- t2-s2-c1-d1 vs t1-s1-c1-d1

We will refer to these as our "SMT vs ST pairs" in coming sections and use these comparisons to assess the impact, positive or otherwise, of SMT for the trial in question.

## 4.5 **Operating System**

The systems in use ran the PowerPC64 "Etch" release of Debian GNU/Linux. Except where noted, we built our own Linux 2.6.18 kernel and made use of it for all runs.

No particular effort was made to quiesce the system in use other than to ensure that no other users were logged in.

## 4.6 Compiler

In consultation with colleagues it was decided to run a recent though pre-release version of gcc in order to ensure we had the most recent OpenMP support available. In practice this meant all our work with the exception of NAS was built with gcc (GCC) 4.2.0 20060816 (experimental) with the NAS work (which required FORTRAN) being compiled with gcc (GCC) 4.2.0 20061024 (prerelease)

While both versions were not production versions it was known that they had passed sufficient regression testing for us to proceed with a high degree of confidence.

The only flags used with the compiler of significance were -O3 and -Wall to enable optimisation and show all compilation warnings respectively.

### 4.7 Automation

Some effort was made to automate the process of running benchmarks, collecting and analysing data and ensuring results were backed up across several locations.

For the most part this consisted of bash scripts that would run the jobs required, pipe the resultant output and errors to log files with defined names and generally allow us to do other things while the trials were completed. As some sequences of experiments took over six hours to complete, this was a significant issue.

These scripts will be made available along with the other files from this research on the eScience projects website.

## 4.8 Thread to CPU affinity

For both the modified STREAM benchmarks (§4.9.2) and our Barrier/Locking tests (§4.10) some effort was put into ensuring that a thread of execution within the benchmark was tied to a particular CPU. Our code was structured such that a particular thread would always map to the same CPU for subsequent trials.

This became particularly important in the context of the round-robin lock benchmarks (§4.10.3) as it meant that a consistent pattern of CPU use was established.

When the benchmark was invoked a bit mask as described in  $\S4.2$  was passed that determined the CPU(s) to use and hence the total number of threads.

### 4.9 STREAM Benchmark

#### 4.9.1 Baseline Setup

Our initial tests with STREAM used a completely unmodified version run multiple times in lieu of using OpenMP to give us a feel for the opreation of the benchmark. The taskset utility was used to provide processor affinity for each instance. This method was used to gather the data presented in Table 6.1

STREAM was then built with OpenMP support using the gcc compiler and a similar set of tests run. taskset was again used to set overall affinity for the instance of STREAM run, multiple threads being created by the OpenMP parallel for directives in the code.

While this approach worked satisfactionally we were left at the mercy of OpenMP's memory and processor affinity decisions. To give finer grained control over same we elected to modify STREAM as detailed in the following section.

#### 4.9.2 Details of changes

Broadly, our changes to STREAM were as follows

- Addition of command line options to allow processor affinity to be specified, the size of the arrays and the number of repeats.

- Make use of the pthread threading library for parallelism.

- Implicit use of Linux's low level setaffinity() function. This provided for a consistent match between thread number and the underlying CPU.

- Modifications to the memory allocation code to evenly allocate memory across the processors in use.

- The output from a successful run was expanded to report:

- 1. Number of threads and CPU bitmask

- 2. Size of array in elements and MB

- 3. Number of repeats ('N')

- 4. One and Five minute load average for system

- 5. Start and End time of runs (seconds since epoch)

- 6. For each of the four codes (copy, scalar, add and triad) the maximum, average and minimum bandwidth and times measured

• Synchronisation between threads to ensure that a run was completed by all threads before starting the next. This reduced the "noise" on our data by preventing any single thread to suddenly see more of the available machine capacity because other threads had completed early.

In total this was some 600+ lines of code all told, about 50% more than the standard version. This modified source will be made available on the ANU eScience projects website.

#### 4.9.3 Main Memory & Cache Runs

The scripts used to automate the collection of data from STREAM would perform all the runs of a particular memory size for each thread combination before moving on to the next memory size.

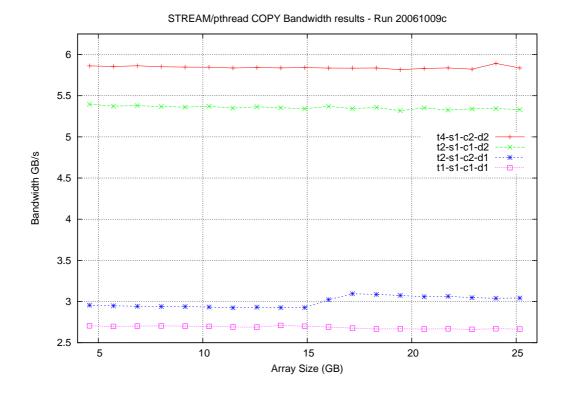

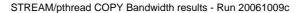

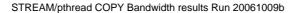

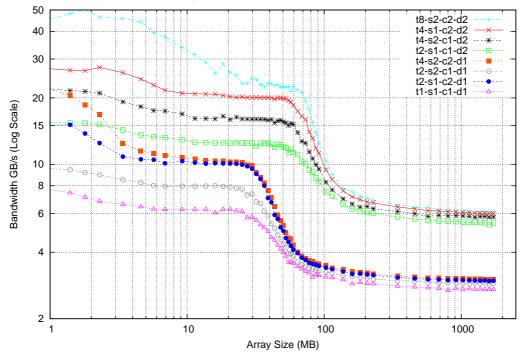

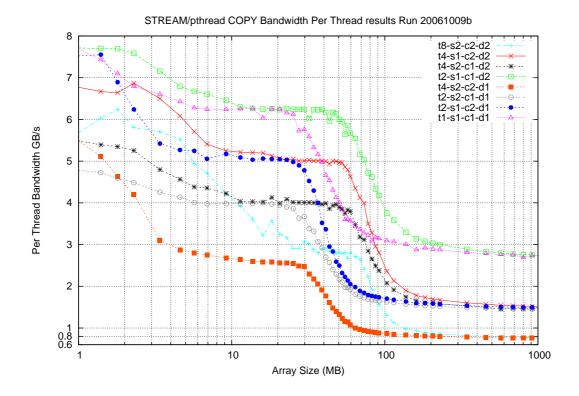

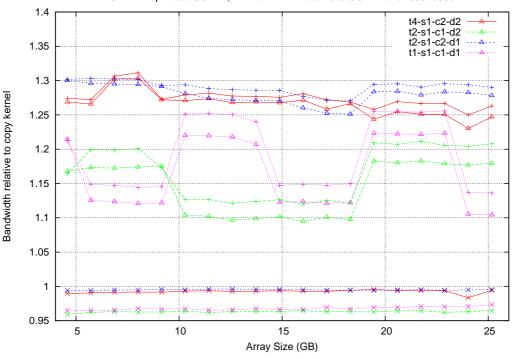

Hence when referring to graphs such as Figure 6.1, time proceeds down the page (most threads to least threads) then across the page left to right (smaller data sets first)

This approach was chosen to minimise the impact any short term loads on the system would have on a the results for a particular thread combination.

### 4.10 Barrier & Lock Benchmarks

To allow us to benchmark low level lock and barrier primitives we wrote a modest test suite. The basic framework for this code was the modified STREAM source modified as described in Section 4.9). This avoided having to re-write the command line parsing, collection, processor affinity and summary/output codes.

We tested two primitives, an execution barrier and a mutex style round-robin lock. For each we coded up a version using relevant pthreads functions and a version using the low level atomic instructions directly in assembler. We examine these codes in more detail in 4.10.2 and 4.10.3.

#### 4.10.1 Time Keeping

```

volatile inline u64 readtb(void)

{

u64 tb;

asm volatile ("mftb %0" : "=r" (tb) : );

return tb;

}

double mysecond()

{

/* Constant shown is correct for fandango2 */

return ((double)readtb() * 5.31793260052222e-09);

}

```

Figure 4.3: Time keeping functions used for barrier and lock experiments

While our modified STREAM source provided an overall starting point we required a very lightweight timekeeping function as the conventional approach of a call to gettimeofday() would take longer than the code being measured.

The PowerPC Architecture defines a 64 bit Time Base register available in each CPU which on SMP configurations is guaranteed to be synchronised. In the case of POWER5 these are clocked at around 200MHz giving a resolution of  $\simeq$ 5ns. We made use of it as shown in Figure 4.3.

While crude, the code seemed to work quite well. A further optimisation step would be to simply store direct timebase values and do the final floating point calculation once at the end of the runs.

We note that there has been some recent work on improving the availability of highresolution timing as part of the standard GNU glibc library. It may be that custom code isn't required in future work which will also reduce platform dependence.

#### 4.10.2 Barrier Codes

Two barrier codes were implemented and benchmarked.

The first, shown in Figure 4.4 used a shared counter locked by pthread\_mutex\_lock and pthread\_mutex\_unlock calls. While more efficient schemes exist, such as the atomic decrement approach, this code was thought to be representative of pthread based barrier implementations in real world applications.

In the closing days of our work it was realised that a return statement should have been added after the call to pthread\_mutex\_unlock() in the if statement. As shown there is a slim chance that the second call to pthread\_mutex\_unlock() could result in the mutex being unlocked when it was owned by a second thread of execution. We did not have time to repeat our trials but would not expect any great difference, as it will merely mean the counter misses an increment on very rare occasions.

```

void thread_sync(int t_id)

{

pthread_mutex_lock(&thread_sync_count_mutex);

thread_sync_counter++;

if (thread_sync_counter == threads_requested) {

if (pthread_cond_broadcast(&thread_sync_count_cv) != 0) {

fprintf(stderr, "cond_broadcasts failed!!");

}

thread_sync_counter = 0;

pthread_mutex_unlock(&thread_sync_count_mutex);

}

else {

pthread_cond_wait(&thread_sync_count_cv,

&thread_sync_count_mutex);

pthread_mutex_unlock(&thread_sync_count_mutex);

}

```

Figure 4.4: thread\_sync function

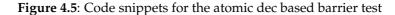

The second barrier implementation is based on a shared counter scheme. It utilises an atomic decrement function hand coded in assembler as shown in Figure 4.5.

It is based on code developed as part of the ANU SPARC-Sulima project.

#### 4.10.3 Round-Robin Lock Codes

The two locking benchmarks followed the same basic model. A global variable was declared that was incremented by each thread of execution in term - hence the lock was passed round robin style between each thread.

Each thread would spin until the the global variable was equal to its ID whereupon it would try and acquire the lock (waiting if necessary), increment the counter, check for wrapping (via a modulo operation) then free the lock. The two high level functions differed only in which locking function was called and global variables used. They are shown in Figure 4.6.

We reiterate that the round-robin codes were written in a manner that ensured that the lock passed from CPU thread to CPU thread in a consistent pattern.

While the pthread version (obviously) used the pthread libraries pthread\_mutex\_lock and pthread\_mutex\_unlock functions, the assembler version used our own implementations as shown in Figure 4.7. Note that in the interests of clarity this code is edited slightly, mostly to remove the GNU compiler specific semantics for register selection and such like.

### 4.10.4 Overall Benchmark

The code that was then used to run each of the four tests was straightforward.

Referring to Figure 4.8 we have t\_id as the thread ID, counting from zero to number of threads. C was set to to 0, 1, 2 or 3 depending on which code was being run. N was the number of locks or barriers to time, this value is given in the results section. Finally, NTIMES was the number of times the codes were run and hence averaged over, the relevant value is also provided with the results. function\_under\_test(t\_id) was the lock or benchmark being evaluated.

After the codes were run, the times stored in start\_times[] and end\_times[] were processed to arrive at a minimum, maximum and average for each code. The times calculated and output were per thread not the total runtime for that code.

These times were then processed further when plotted, in most cases being divided by the number of threads in operation to arrive at a figure that was normalised by the number of threads in use. This removed the bias that would have otherwise occurred from a barrier or lock naturally taking longer when more threads are in operation.

# 4.11 NAS Parallel Benchmarks

By comparison to the effort involved with STREAM and our Barrier/Locking benchmarks, running NAS was an exercise in relative simplicity.

## 4.11.1 Basic Setup

The NAS benchmarks were configured to use a mixture of "Class A" and "Class B" benchmarks, the latter being chosen when the runtime of the "Class A" version was too short to provide reasonable data. All benchmarks were Version 3.2.1

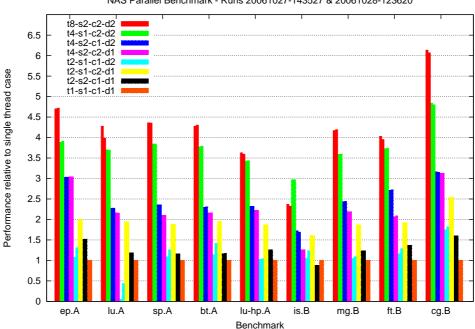

Nine benchmarks were used - ep.A, lu.A, sp.A, bt.A, lu-hp.A, is.B, mg.B, ft.B and cg.B. These were built with gcc as described in §4.6.

Six runs of the nine benchmarks were completed using scripts to automate the process. Figure 4.9 shows the basic arrangement used<sup>5</sup>. This process was then repeated a second time to give a total of twelve runs.

<sup>&</sup>lt;sup>5</sup>This approach and that used for data parsing inspired by the method used by Tony Breeds [Breeds 2006] in his COMP6702 work

```

#define NUM_PBAR (4)

void pbarrier_init(void)

int i;

for (i=0; i < NUM_PBAR; i++) {</pre>

pbarrier_at_barrier[i] = threads_requested;

}

for (i = 0; i < MAX_CPUS; i++) {</pre>

pbarrier_n_barrier_calls[i][0] = 0;

}

}

void userspace_atomic_dec(long *var)

{

asm volatile (

ldarx r1, 0, var

/* Get current value of var */

loop:

/* with address reservation */

addic r1, r1, -1

/* Decrement */

stdcx. r1, 0, var

/* Attempt to store back

with address reservation */

bne-

loop

/* Retry if we lost reservation */

);

}

void pbarrier(int t_id)

{

int nbarrier;

int spin_catch = 100000000;

nbarrier = pbarrier_n_barrier_calls[t_id][0] % NUM_PBAR;

/* Only thread 0 gets to set up counter for next barrier */

if (t_id == 0) {

pbarrier_at_barrier[(nbarrier + 1) %NUM_PBAR] =

threads_requested;

}

userspace_atomic_dec(&pbarrier_at_barrier[nbarrier]);

pbarrier_n_barrier_calls[t_id][0]++;

/* spinlock */

while (pbarrier_at_barrier[nbarrier]) {

if (spin_catch -- == 0) {

fprintf(stderr, "thread %d lockedup\n", t_id);

pbarrier_at_barrier[nbarrier] = 0;

return;

}

}

}

```

```

void mylock_do_lock_asm(int t_id)

{

while(mylock_asm_current_thread != t_id) {}

set_lock(&mylock_atomic_int);

mylock_asm_current_thread += 1;

mylock_asm_current_thread %= threads_requested;

clear_lock(&mylock_atomic_int);

}

void mylock_do_lock_pthread(int t_id)

{

while(mylock_pthread_current_thread != t_id) {}

pthread_mutex_lock(&mylock_mutex);

mylock_pthread_current_thread += 1;

mylock_pthread_current_thread %= threads_requested;

pthread_mutex_unlock(&mylock_mutex);

}

```

```

Figure 4.6: Code snippets for the two lock functions tested

```

```

void set_lock(int *lock)

{

asm volatile (

lwarx r1, 0, lock /* Load lock value into r1 */

loop:

/* with addr. reservation */

cmpwi r1, 0

/* See if it's zero

*/

/* If not, spin

loop

bne-

*/

r1, 1

/* Want to set lock to 1

li

*/

stwcx. r1, 0, lock /* Do store with addr.

*/

/* reservation check

*/

loop

/* Retry if we lost the

bne-

*/

/* reservation

*/

/* Lightweight sync

isync

*/

);

}

void clear_lock(int *lock)

{

asm volatile (

/* Heavyweight memory sync */

r1, 0 /* Get a zero */

sync

li

r1, 0, lock /* And store in the lock

stwx

*/

);

}

```

Figure 4.7: Assembler for our low level lock functions set\_lock and clear\_lock

```

for (k = 0; k < NTIMES; k++) {

start_times[0][t_id][k] = mysecond();

for (i = 0; i < N; i++) {

function_under_test(t_id);

}

end_times[0][t_id][k] = mysecond();

}</pre>

```

```

Figure 4.8: Typical wrapper code used to run each barrier or lock test

```

Figure 4.9: Pseudo wrapper code used for NAS runs

Experimental Setup

# A Performance Model for Round-Robin Locking

# 5.1 Background

Section 4.3 describes the different thread combinations available to us on *jago*. Section 4.10.3 details the benchmark written to allow us to evaluate round-robin locking performance.

The choice of round-robin locking and the known relationship between a thread of execution in the benchmark and a particular thread on the CPU allows us to put model the likely behaviour of the benchmark.

# 5.2 Description of model

The operation of the round-robin lock is heavily dependent on the efficiency of shared memory operations, in particular the transfer of cache lines containing the locking variable. The characteristic of the lock is each thread updating the counter in turn while the remaining threads read the counter in a spin loop.

We can reasonably argue that the dominant time factor in the process of passing the lock is passing the cache line containing the shared counter (c.f. §4.10.3) between threads of execution. For the system under test, this process of passing the counter can occur over three different paths, each with increasing latency characteristics. In Figure 5.1 the three different paths are shown as a thin green line, a thicker blue line and a still thicker red line.

We assign each of these transfers or latencies a different weight. The thin green line represents the time delay for the lock to be transferred between SMT threads on the same core,  $l_s$ . The blue line indicates an inter-core transfer between threads on the same DCM/die,  $l_c$ . Finally the red line denotes a transfer between threads on two different DCM/die,  $l_f$ .

Figure 5.1 illustrates the seven different thread combinations that can occur (the single thread case is irrelevant in this case) and the "path" taken by the lock from thread to thread. The dashed line indicates the "path" taken by the lock at the start of the next iteration.