### American University in Cairo

### **AUC Knowledge Fountain**

Theses and Dissertations

Student Research

2-1-2016

### Nano-scale TG-FinFET: Simulation and Analysis

Ahmed Taha Elthakeb Naguib Youssef

Follow this and additional works at: https://fount.aucegypt.edu/etds

### **Recommended Citation**

### **APA Citation**

Youssef, A. (2016). *Nano-scale TG-FinFET: Simulation and Analysis* [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/110

### **MLA Citation**

Youssef, Ahmed Taha Elthakeb Naguib. *Nano-scale TG-FinFET: Simulation and Analysis*. 2016. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*.

https://fount.aucegypt.edu/etds/110

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

# The American University in Cairo School of Science and Engineering (SSE)

Nano-scale TG-FinFET: Simulation and Analysis

A Thesis Submitted to

Electronics and Communications Engineering Department

in partial fulfillment of the requirements for the degree of Master of Science

By Ahmed Taha El-Thakeb Naguib Youssef

Under the supervision of:

Prof. Yehea Ismail

Prof. Hamdy Abd Elhamid

July/2015

Cairo, Egypt

### The American University in Cairo

### School of Science and Engineering (SSE)

### Nano-scale TG-FINFET: SIMULATION AND ANALYSIS

# A Thesis Submitted by Ahmed Taha El-Thakeb Naguib Youssef

To the Electronics and Communications Engineering Department July/2015

In partial fulfillment of the requirements for

The degree of Master of Science

### has been approved by

| Thesis Committee Supe |      |             | -    |

|-----------------------|------|-------------|------|

| Thesis Committee Read | der  |             |      |

| Affiliation           |      |             |      |

| Thesis Committee Read | der  |             |      |

| Affiliation           |      | <del></del> |      |

|                       |      |             |      |

| <del></del>           |      |             |      |

| Dept. Chair /Director | Date | Dean        | Date |

### **DEDICATION**

To my beloved family ...

My father,

My mother,

and my brother.

### **ACKNOWLEDGMENT**

### Praise be to Allah, Lord of the Worlds

This work has been accomplished thanks to many persons. First, I would like to thank my supervisors Prof. Yehea Ismail and Prof. Hamdy Abd Elhamid for giving me the opportunity to carry out this work under their supervision.

I would like to thank Prof. Yehea Ismail for his trust and giving me the chance to join his center of nano-electronics and devices (CND) among a talented group of students and faculty. I appreciate his tremendous efforts to afford the most advanced research facilities including most recent T/CAD tools, PDKs and access to material experimental labs that greatly impacted the quality of this research. In addition to his insightful lectures and discussions that inspired me a lot in my research.

I would like to show my sincerest appreciation and gratitude to Prof. Hamdy Abd Elhamid. I would like to thank him for his sincere advising during which I have learnt a lot on both the technical and personal levels, for his fruitful discussions and continuous support and encouragement over two years of work. I also would like to thank him for giving me the opportunity to join the center of microelectronics, ICTEAM, UCL, Belgium, over the summer period which influenced both my research and life experiences.

I am greatly indebted to Prof. Hassan Mostafa for giving me the wonderful opportunity to investigate the FinFET on the circuit level. I would like to thank him for his precious time and valuable discussions and introducing me to the SRAM fundamentals.

I also would like to thank Prof. David Bol, UCL for his great advising and cooperation and nice hosting for me within his lab that helped me to make full use of my short stay. Also for providing me an access to the 28nm FDSOI PDK and carrying out very interesting study. I am also very grateful to Prof. Denis Flandre for his welcoming and insightful discussion that inspired me and was indispensable for our work.

I am obliged to my friend Taher Essam for his continuous assistance in installing the TCAD tools and his great help in the IT issues that saved a lot of time for me.

Finally, I would like to express my gratitude to my mother for her support and keeping my morals high in moments where desperation seemed to be the only choice. Also to all my friends in CND for their support and encouragement.

### **ABSTRACT**

#### OF THE THESIS OF

Ahmed Taha El-Thakeb Naguib Youssef

for Master of Science

Major: Electronics and Communications Engineering

The American University in Cairo

Title: Nano-scale TG-FinFET: Simulation and Analysis

Supervisor: <u>Prof. Yehea Ismail</u> Co-Supervisor: <u>Prof. Hamdy Abd Elhamid</u>

Transistor has been designed and fabricated in the same way since its invention more than four decades ago enabling exponential shrinking in the channel length. However, hitting fundamental limits imposed the need for introducing disruptive technology to take over. FinFET "3-D transistor" has been emerged as the first successor to MOSFET to continue the technology scaling roadmap.

In this thesis, scaling of nano-meter FinFET has been investigated on both the device and circuit levels. The studies, primarily, consider FinFET in its tri-gate (TG) structure.

On the device level, first, the main TCAD models used in simulating electron transport are benchmarked against the most accurate results on the semi-classical level using Monte Carlo techniques. Different models and modifications are investigated in a trial to extended one of the conventional models to the nano-scale simulations. Second, a numerical study for scaling TG-FinFET according to the most recent International Technology Roadmap of Semiconductors is carried out by means of quantum corrected 3-D Monte Carlo simulations in the ballistic and quasi-ballistic regimes, to assess its ultimate performance and scaling behavior for the next generations. Ballisticity ratio (BR) is extracted and discussed over different channel lengths. The electron velocity along the channel is analyzed showing the physical significance of the off-equilibrium transport with scaling the channel length.

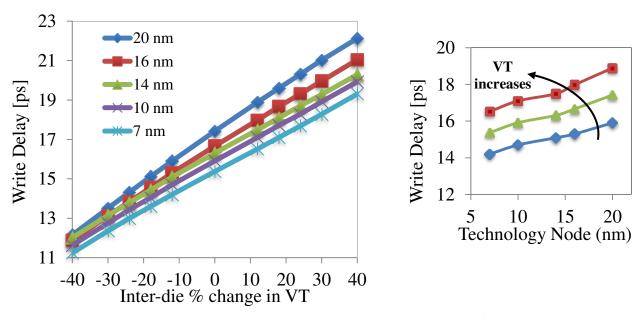

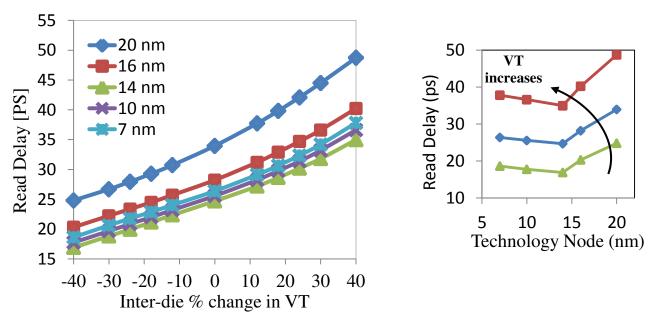

On the circuit level, first, the impact of FinFET scaling on basic circuit blocks is investigated based on the PTM models. 256-bit (6T) SRAM is evaluated for channel lengths of 20nm down to 7nm showing the scaling trends of basic performance metrics. In addition, the impact of  $V_T$  variations on the delay, power, and stability is reported considering die-to-die variations. Second, we move to another peer-technology which is 28nm FD-SOI as a comparative study, keeping the SRAM cell as the test block, more advanced study is carried out considering the cell's stability and the evolution from dynamic to static metrics.

## List of publications

- **Ahmed T. El-Thakeb**, Thomas Haine, Denis Flandre, Yehea Ismail, Hamdy Abd El Hamid, David Bol, "Analysis and Optimization for Dynamic Read Stability in 28nm SRAM Bitcells" in *IEEE ISCAS*, P. 1414-1417, May 2015.

- Ahmed T. El-Thakeb, Hamdy Abd El-Hamid, Yehea Ismail, "Scaling of TG-FinFETs: 3-D Monte Carlo Simulations in the Ballistic and Quasi-Ballistic Regimes," *IEEE Trans. Electron Devices*, vol. 62, no. 06, p.1796-1802, April 2015.

- Ahmed T. El-Thakeb, Hassan Mostafa, Hamdy Abd El-Hamid, Yehea Ismail, "Performance Evaluation of FinFET-Based SRAM Cell with Technology Scaling Under Statistical VT Variability," in *Proc. 26th Int. Conf. on Microelectronics* (*ICM*), pp. 88–91, Dec. 2014.

In The Name of Allah, the Most Beneficent, the Most Merciful

### **Table of Contents**

| 1. | Introduction                                                                                                 | 1    |

|----|--------------------------------------------------------------------------------------------------------------|------|

|    | 1.1. Short channel effects (SCEs)                                                                            | 3    |

|    | 1.2. Tri-gate "FinFET" structure                                                                             | 4    |

|    | 1.3. Reduction of short-channel effects                                                                      | 5    |

|    | 1.4. Overview of the Thesis                                                                                  | 8    |

| 2. | Benchmarking Semi-Classical Electron Transport Models for Nano-scale FinFET in TCAD                          | . 10 |

|    | 2.1. Introduction                                                                                            | . 10 |

|    | 2.2. Computational electronics                                                                               | . 11 |

|    | 2.3. Electron Transport models                                                                               | . 13 |

|    | 2.3.1. Drift-Diffusion (DD) Transport Model                                                                  | . 15 |

|    | 2.3.2. Thermodynamic (TD) Transport Model                                                                    | . 16 |

|    | 2.3.3. Hydrodynamic (HD) Transport Model                                                                     | . 17 |

|    | 2.4. Benchmarking semi-classical transport models in TCAD                                                    | . 19 |

|    | 2.4.1. Problem statement                                                                                     | . 19 |

|    | 2.4.2. Objective of the study                                                                                | . 21 |

|    | 2.4.3. Device Structure and Simulation Methodology                                                           | . 21 |

|    | 2.4.4. Simulation Results and discussion                                                                     | . 25 |

|    | A numerical study of Nano-scale TG-FinFET: 3D Monte Carlo Simulations in the Ballistic and ballistic regimes |      |

|    | 3.1. Introduction                                                                                            | . 28 |

|    | 3.2. Device Design and Simulation Methodology                                                                | . 31 |

|    | 3.3. Simulations Results                                                                                     | . 33 |

|    | 3.3.1. Performance metrics with scaling                                                                      | . 33 |

|    | 3.3.2. Ballisticity Ratio (BR): How close to the ballistic limit?                                            | . 36 |

|    | 3.3.3. Electron Velocity Evolution along the Channel                                                         | . 40 |

|    | 3.3.4. Discussion                                                                                            | . 46 |

|    | 3.4. Conclusion                                                                                              | . 48 |

| 4. | Evaluation of TG-FinFET Scaling Roadmap in Circuit Design                                                    | . 50 |

|    | 4.1 Introduction                                                                                             | 50   |

| 4.2. Performance Evaluation of FinFET based SRAM under Statistical VT Variability | 52 |

|-----------------------------------------------------------------------------------|----|

| 4.2.1. Simulation Methodology                                                     | 54 |

| 4.2.2. Simulation Results and Discussions                                         | 55 |

| 4.2.3. Conclusion                                                                 | 62 |

| 4.3. Analysis and Optimization for Dynamic Read Stability in 28nm SRAM Bit-cells  | 62 |

| 4.3.1. Quantitative analysis of Dynamic Read Noise Margin                         | 64 |

| 4.3.2. Effect of parasitic capacitances on R/W dynamic noise margin:              | 68 |

| 4.3.3. Sizing for DNM: Design Perspective                                         | 71 |

| 4.3.4. Conclusion                                                                 | 72 |

| 5. Conclusion and Outlook                                                         | 73 |

| 5.1. Summary                                                                      | 73 |

| 5.2. Outlook                                                                      | 76 |

| 5.2.1. On the device level                                                        | 76 |

| 5.2.2. On the circuit level                                                       | 76 |

| Bibliography                                                                      | 77 |

| Annendix                                                                          | 83 |

# **List of Figures**

| Figure 1-1: Illustration of short-channel effects                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Different flavors of MG structures5                                                                                                                                                                                                                                                     |

| Figure 1-3: Different Electric Field components on elemental volume inside the channel 6                                                                                                                                                                                                            |

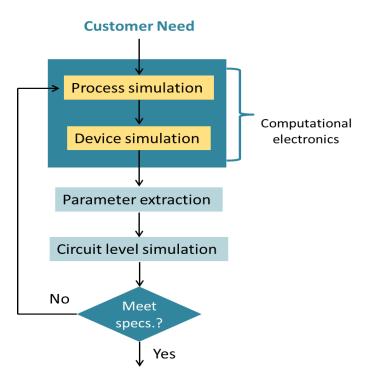

| Figure 2-1: Design sequence to achieve desired customer need                                                                                                                                                                                                                                        |

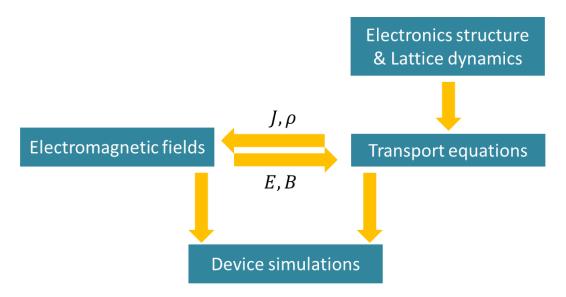

| Figure 2-2: Sequence of main device simulation                                                                                                                                                                                                                                                      |

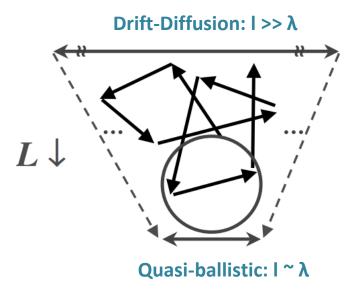

| Figure 2-3: Illustration of carriers' motion inside a semiconductor. Each arrow represents a deterministic path until an abrupt change or scattering event happens so the carrier changes its momentum randomly and go through another deterministic path represented by different arrow, and so on |

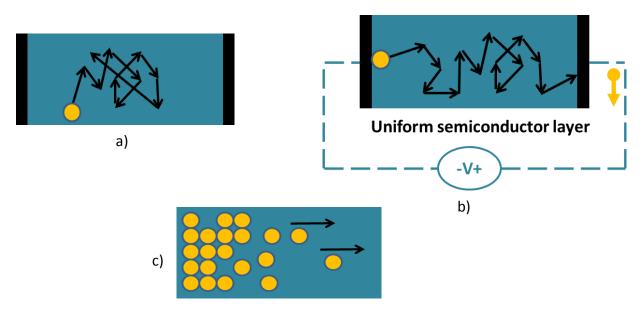

| Figure 2-4: Drift Diffusion transport mechanisms: a) random walk under therma equilibrium, b) Drift under applied electric field, c) Diffusion under concentration gradient.                                                                                                                        |

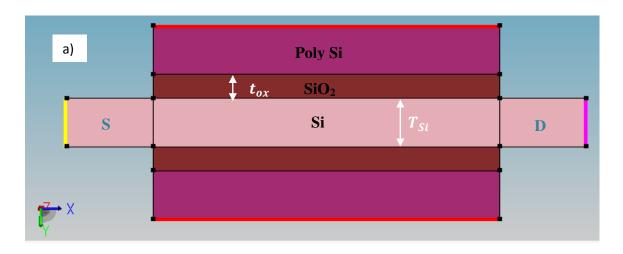

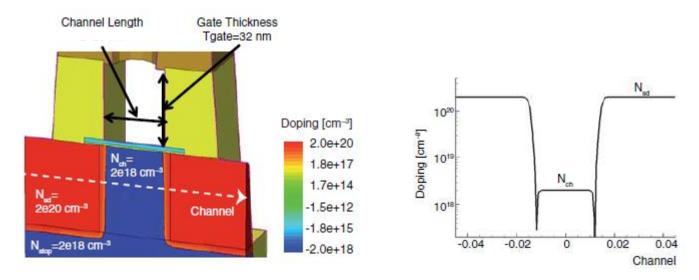

| Figure 2-5: Simulated double gate (DG) structure, (a) Structure's geometry by Sentaurus structure editor, (b) Doping profile                                                                                                                                                                        |

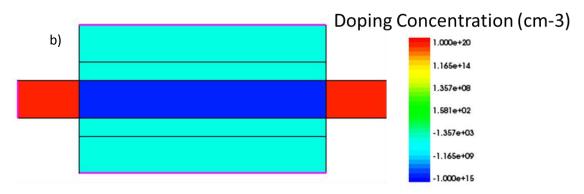

| Figure 2-6: Transfer characteristics with Monte Carlo (MC), and classical drift-diffusion (DD): (a) long channel $Leff = 50nm$ , (b) short channel, $Leff = 20nm$                                                                                                                                   |

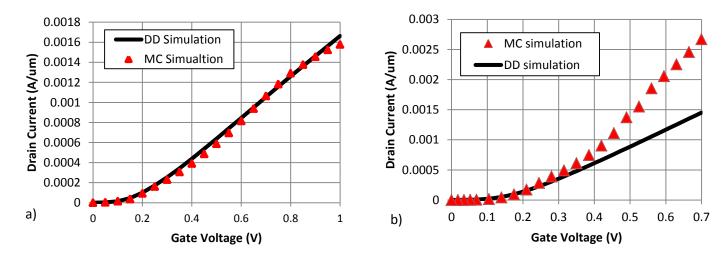

| Figure 2-7: Process Formation Flow of simulated device [Sentaurus Template, [60]] 22                                                                                                                                                                                                                |

| Figure 2-8: Doping Profile across the simulated structure, [Sentaurus Template] 22                                                                                                                                                                                                                  |

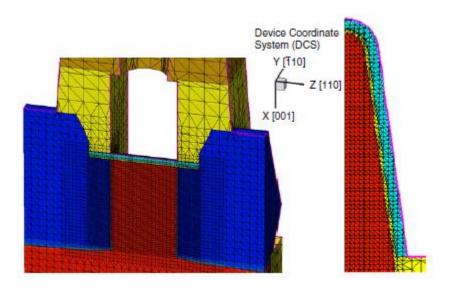

| Figure 2-9: Meshing and Orientation of the simulated FinFET structure, [Sentaurus 23]                                                                                                                                                                                                               |

| Figure 2-10: Output characteristics of Triple-gate FinFET simulated with Monte Carlo (MC), Modified drift-diffusion (MDD), Drift-diffusion with ballistic mobility model (BDD), and the classical drift-diffusion (CDD); (a) $L=17\ nm$ , $Tsi=11\ nm$ , $Hfin=27\ nm$ , (b) $L=15.3\ nm$ , $Tsi=10\ nm$ , $Hfin=27\ nm$                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

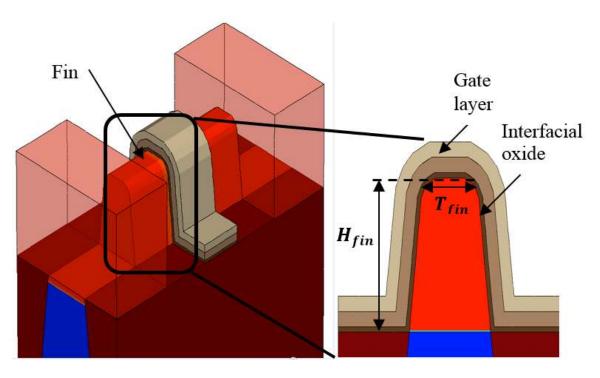

| Figure 3-1: 3-D and 2-D representations of Tri-gate FinFET structure under study 32                                                                                                                                                                                                                                                                                                                                                                                     |

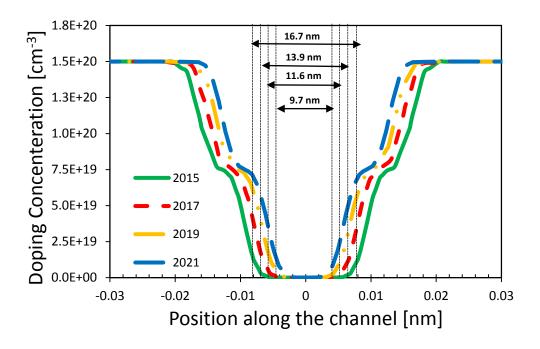

| Figure 3-2: Doping profiles in cross sections of the simulated Tri-gate FinFET for channel lengths of 16.7, 13.9, 11.6, and 9.7 nm as projected to the years 2015, 2017, 2019, and 2021 respectively                                                                                                                                                                                                                                                                    |

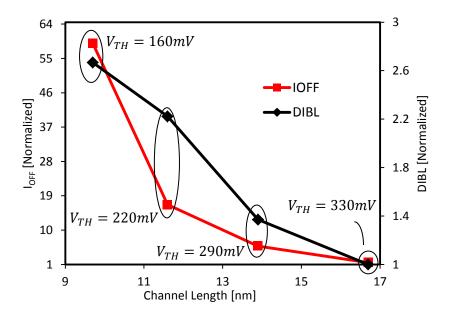

| Figure 3-3: SCEs behavior of Tri-gate FinFET at different channel lengths showing the threshold voltage roll-off and the degradation of both DIBL and leakage current (IOFF) based on the adopted scaling strategy normalized to values at 16.7nm                                                                                                                                                                                                                       |

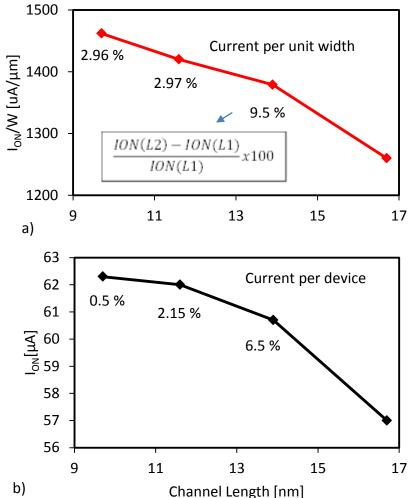

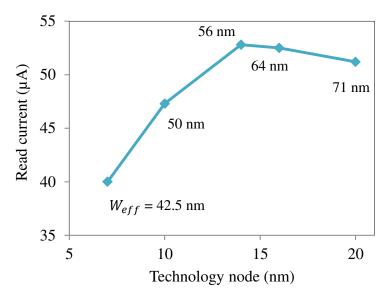

| Figure 3-4: The behavior of the output current at VGS=VDS=VDD showing the relative improvement with technology scaling a) The current per device (corresponding to a device effective width; $Weff = 2Hfin + Tfin$ ), b) The device current per unit width. 35                                                                                                                                                                                                          |

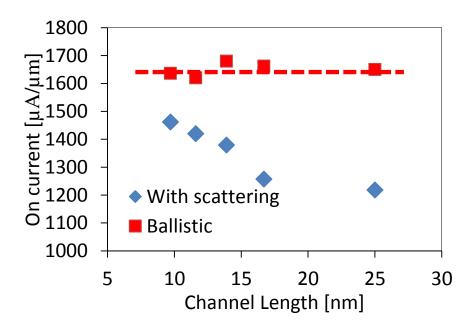

| Figure 3-5: Drain current at VD=VG=Supply Voltage, normalized to the effective channel width, $Weff=2Hfin+Tfin$ , at scaled channel lengths, body thicknesses, supply voltages, and oxide thicknesses projected by the 2013 ITRS as reported in Table 1                                                                                                                                                                                                                 |

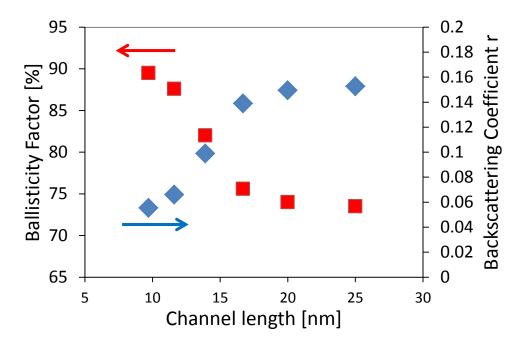

| Figure 3-6: Ballisticity factor in the left y-axis and corresponding backscattering coefficient in the right y-axis, with scaling the channel length as reported in table 1, at body thickness = 4 nm, supply voltage = 0.78 V                                                                                                                                                                                                                                          |

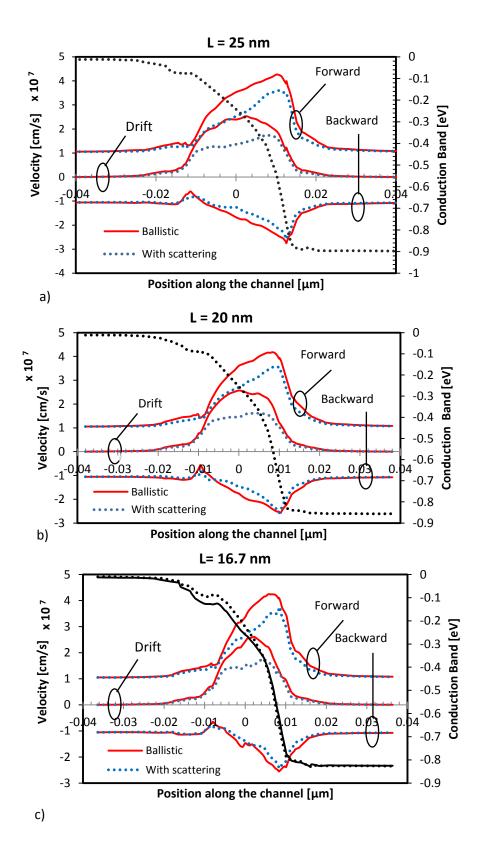

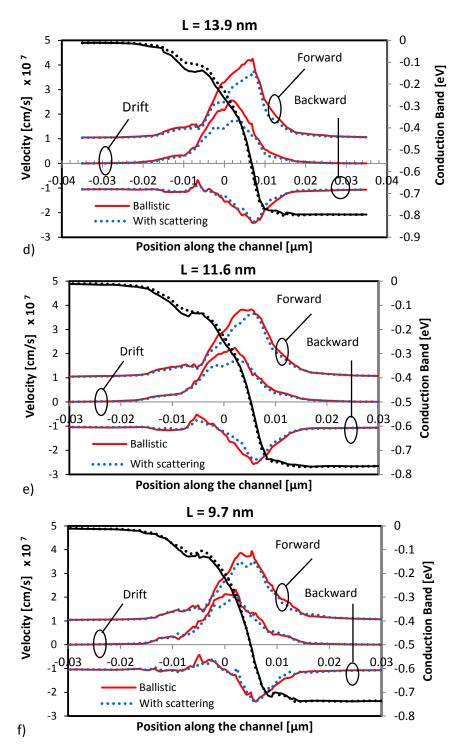

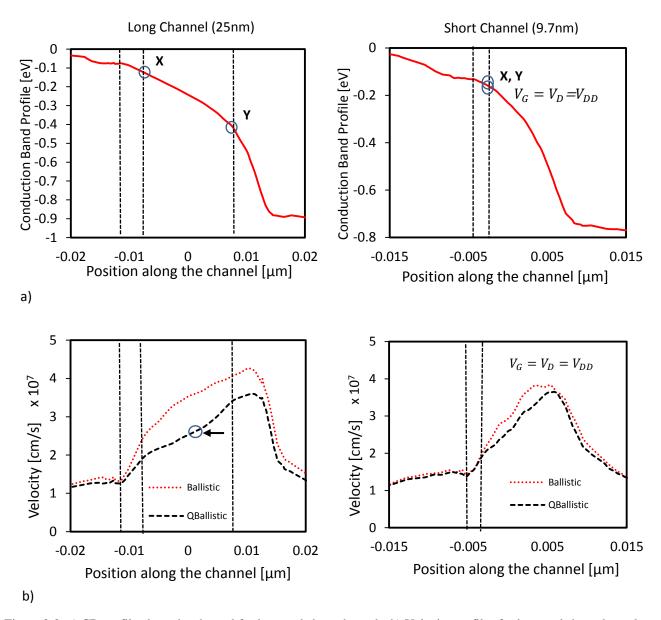

| Figure 3-7: Different average electron velocity components: drift, forward, and backward; and the conduction band profile along the channel 15 $A^{\circ}$ below the Si-SiO <sub>2</sub> interface at various channel lenghts: a) L=25 nm, b) L=20 nm, c) L=16.7 nm, d) L=13.9 nm, e) L=11.6 nm, f) L=9.7 nm. Solid lines: indicating the ballistic case, dotted lines: including all scattering mechanisims. All simulations are done for the on-state ( $VG = VDD$ ). |

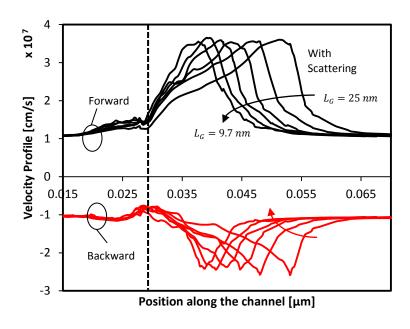

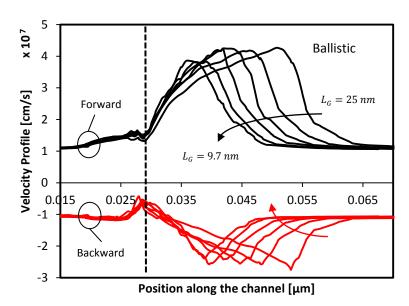

| Figure 3-8: Forward and backward components of the electron velocity for Tri-gate FinFET 15 A° below the Si-SiO2 interface at various channel lengths 25, 20, 16.7, 13.9,                                                                                                                                                                                                                                                                                               |

| 11.6, 9.7 nm; a) For the Quasi-ballistic case (including scattering), b) For the ballistic case                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-9: a) CB profile along the channel for long and short channels, b) Velocity profiles for long and short channels                                                                                    |

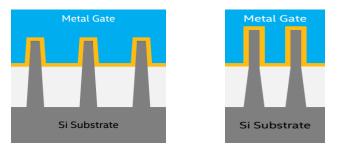

| Figure 4-1: TG-FinFET a) 22 nm 1st Generation, b) 14 nm 2nd Generation Tri-gate Transistor [INTEL]                                                                                                           |

| Figure 4-2: FinFET demonstration road map                                                                                                                                                                    |

| Figure 4-3: Transistor scaling guidelines for circuit design [Intel]                                                                                                                                         |

| Figure 4-4: SRAM Write delay sensitivity to threshold voltage inter-die variations range of +/-40 % at various technology nodes from 20nm down to 7nm node                                                   |

| Figure 4-5: SRAM Read delay sensitivity to threshold voltage inter-die variations range of +/-40 % at various technology nodes from 20nm down to 7nm node                                                    |

| Figure 4-6: Device current per bit-cell with technology scaling from 20nm to 7nm node, where Weff = 2Hfin+Tfin, and Wtot = Nfin Weff                                                                         |

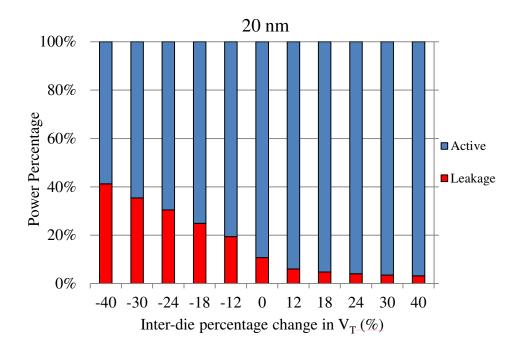

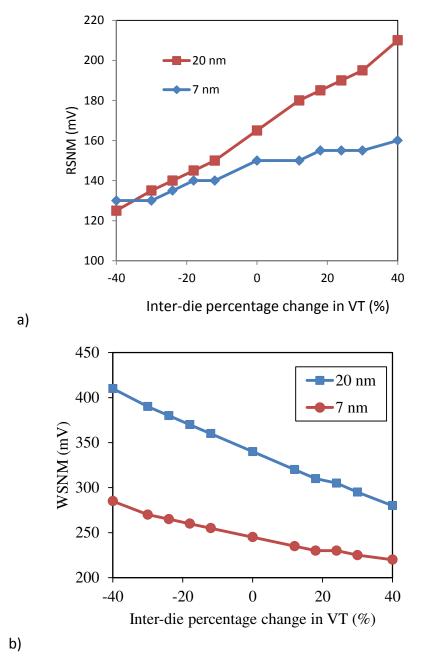

| Figure 4-7: Sensitivity of the percentage leakage power to the active power with threshold voltage variations; a) 20nm node, b) 7nm node                                                                     |

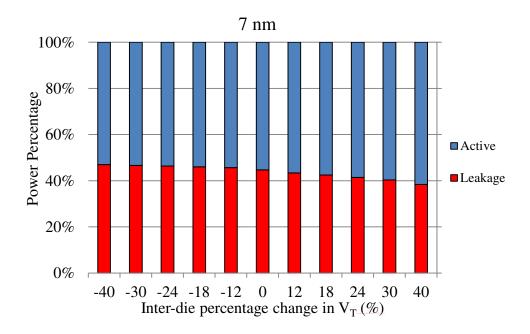

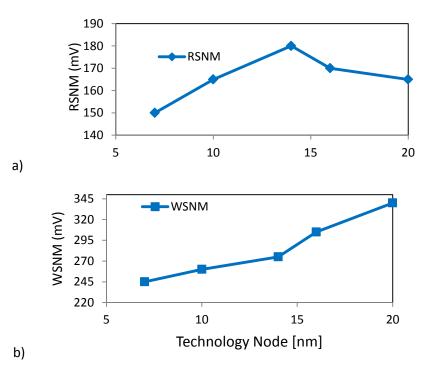

| Figure 4-8: Read and write static noise margins with technology scaling                                                                                                                                      |

| Figure 4-9: Sensitivity of the read and write noise margins to the threshold voltage variations for 20nm and 7nm technology nodes; a) RSNM, b) WSNM                                                          |

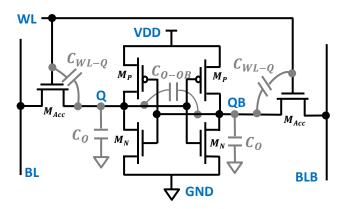

| Figure 4-10: Conventional 6T SRAM cell with the main parasitic capacitances, under study, contributing to the dynamic effects                                                                                |

| Figure 4-11: Equivalent circuit for DNM characterization setup                                                                                                                                               |

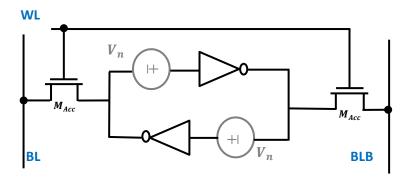

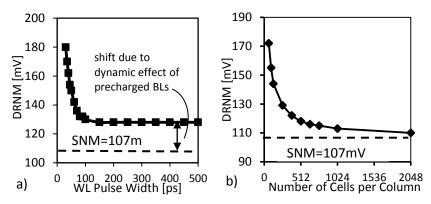

| Figure 4-12: Evolution of noise margin from SNM to DNM with cumulative dynamic effects The BL discharge time for 100mV of differential voltage is 22ps, which allows sufficient margin for a 50-ps WL pulse. |

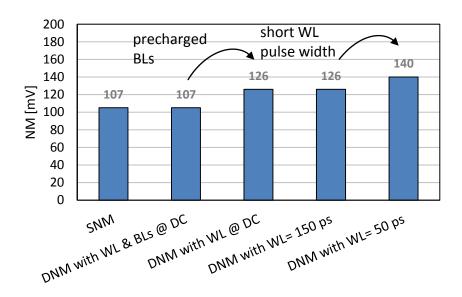

| Figure 4-13: Behavior of DNM with a) increasing WL pulse width an density of SRAM cell array                                                                                                                                                                                                         | ,                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

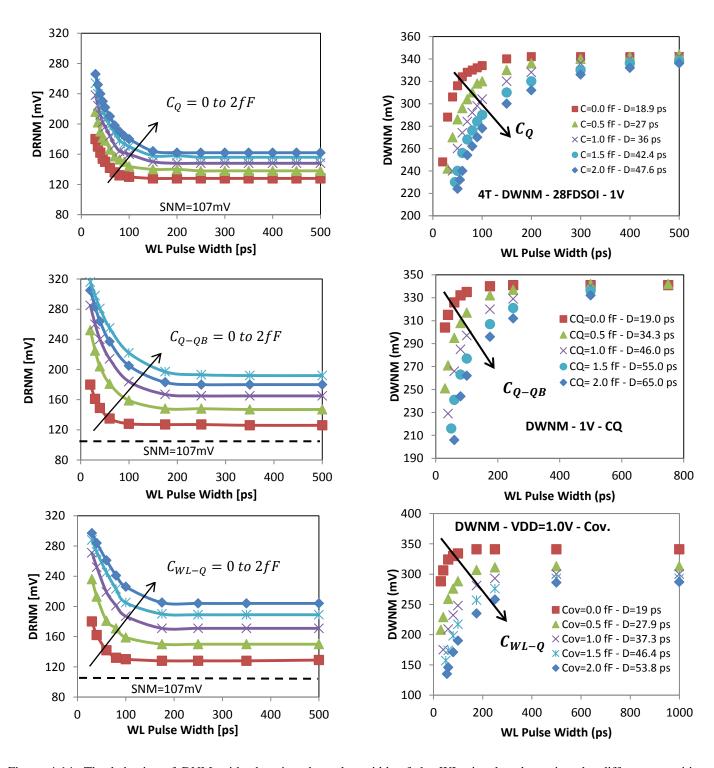

| Figure 4-14: The behavior of DNM ( with changing the pulse width of the varying the different parasitic capacitance components from 0 to 2fF: a) of the storage nodes $(C_Q)$ ; b) coupling capacitance between the storage rand c) coupling capacitance between the WL signal and the storage nodes | self-capacitance nodes ( $C_{(Q-QB)}$ ); |

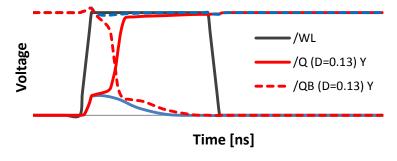

| Figure 4-15: Transient waveforms for Q, QB at different noise levels (Vr. which it flips its data, along with WL signal, a) intrinsic case (cell parasi at the used sizing), b) added CQ, c) added CQ-QB, d) added CWL-Q                                                                             | tic capacitances                         |

| Figure 4-16: Dependence of read noise margins on the beta ratio conditions                                                                                                                                                                                                                           |                                          |

# **List of Tables**

| Table 2-1: Device parameters of the simulated structure | . 20 |

|---------------------------------------------------------|------|

| Table 3-1: The main parameters of the simulated device  |      |

| Table 4-1: The simulated device parameters              | . 54 |

# **List of Abbreviations**

MOSFET Metal Oxide Semiconductor Field Effect Transistor

FinFET Fin Field Effect Transistor

TG Tri-gate

MG Multi-gate

ITRS International Technology Roadmap for Semiconductors.

DD Drift-diffusion

HD Hydro-dynamic

TD Thermo-dynamic

MC Monte Carlo

VT Threshold voltage

SRAM Static Random Access Memory

BTE Boltzmann Transport Equation

BSIM-CMG Standard compact models for multi-gate structures

PTM Predictive technology models

# 1. Introduction

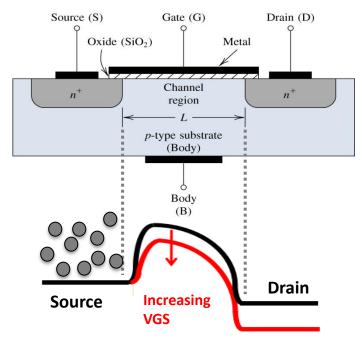

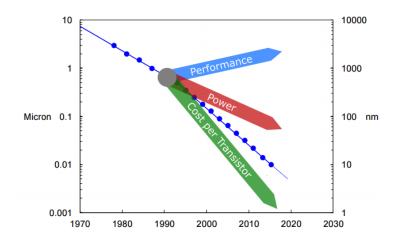

Transistors forming microprocessors, memory chips and telecommunications microcircuits have been designed in the same way since its invention at late 1950-1960's — what is called conventionally MOSFETs Figure 1-1. Basically, we may define transistors based on three design characteristics or metrics: a) the core design *material* involved in the fabrication process, b) the geometrical *structure*, and c) the physical *theory of operation* describing its switching mechanisms between ON/OFF states, charge transport, and device electrostatics. Therefore, nano-electronics research centers and giant industry companies need to identify new materials, structures, and/or novel working principle in order to move forward.

Regarding the material, "Entire eras are named after materials — the Stone Age, the Iron Age and now we have the silicon age" said Shoucheng Zhang, a Stanford University physicist. The core material for fabricating mainstream transistors is Silicon so far, which has the ability to behave as both electrical conductor and insulator. However with the continuous miniaturization and looking forward to below 7nm channel lengths, moving to non-silicon CMOS may be prominent in the immediate future. There is a great interest in III-V high mobility materials for increased performance and higher switching speeds. In addition, a lot of efforts to integrate III-V materials with Silicon aiming to continue the scaling beyond the Silicon's capabilities alone. IMEC has already demonstrated world's first III-V FinFET devices monolithically with traditional Silicon substrate in late 2013 [1]. Also moving to the Carbon era is very likely with the great advances in Graphene materials [2].

Regarding the working principle, transistors are built on intrinsic substrate with two highly oppositely doped sides that are the source and drain. A channel in between connects the highly doped sides with a wide gate on top which controls the device

operation. Applying the right gate voltage, an inversion layer is formed in between that creates a conductive pathway that allows current to flow from source to drain.

Under this scenario the transistor is switched to be in the ON-state, while without forming such inversion layer, no current can flow hence the device is called to be in the OFF-state. In the OFF-state, what blocks the electrons flow is energy barrier across the channel, **Figure 1-1** and transistors are all about modulating these energy barriers through the gate and drain voltages. One of the fundamental problems impeding MOSFET scaling is the short channel effects (SCEs), where the energy barrier gets modulated not only by the gate but from the drain side as well, which compromise the idea working principle.

Extensive efforts are going on everywhere to identify new theories the switching mechanisms to take over [3]. Graphene bi-layers, which are simply two sheets of graphene in close proximity, are predicted to have special transport characteristics [4]. Another direction of interest is about spintronics and what is called spin-FET that basically makes use of the electron's spin to represent and process information [5].

Figure 1-1: Illustrating the MOSFET structure and its thwory of operation

### 1.1. Short channel effects (SCEs)

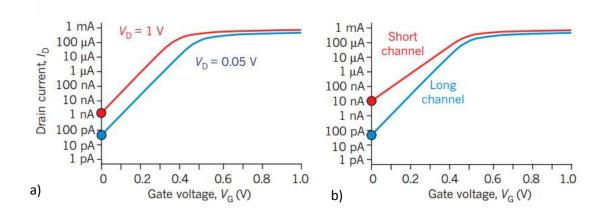

The most fundamental impediment associated with scaling down the channel length is what is called Short-channel effects (SCEs). SCEs are as a result of getting the source and drain closer to each other which result in undesired sharing of the electrical charges over the channel between the gate from one hand, and the source (S) and the drain (D) from the other side. The S and D junctions create a depletion region into the channel from each side, which effectively shorten the actual channel length under the gate control. As the drain voltage increases, more electric fields lines penetrates into the channel region and compromise the full control of the gate over the channel. The effect gets amplified as the distance between the S and the D gets shorter. As a resultant of losing the full gate control over the channel, two serious phenomena are observed that undermine the overall device performance, **Figure 1-2**:

- a) Drain-induced barrier lowering (DIBL); which causes the threshold voltage to decrease with increasing the drain voltage.

- b) Degradation in the sub-threshold slope (SS).

Both of them contribute to increase the overall leakage current of the transistors forming a serious challenge for further technology scaling.

Figure 1-2: Illustration of short-channel effects. a) DIBL effect, b) Sub-threshold swing degradation

### 1.2. Tri-gate "FinFET" structure

In the conventional MOSFET structure, the source, the drain, and the channel connecting them (with the gate on top) lie flat in the same plane. In such configuration the device is called planar and can essentially be treated as a 2-D device especially on the simulation level. In this case, the electrostatic control is achieved through a capacitive coupling between the top gate and the channel region though the gate oxide layer. SCEs can be reduced by improving the gate control over the channel which can be achieved through two approaches. First, increasing the gate control by enhancing the capacitive coupling between the gate and the channel through the reduction of the gate oxide thickness or using high-k oxides. Second, reducing the impact of the drain by decreasing the depth of the source and drain regions with scaling the channel length.

On the other side, device's electrostatics can also be improved by modifying the shape of the device. For long channel MOSFETs, the device's electrostatics are considered as a one dimensional problem and the gradual channel approximation was commonly employed in the old days in solving 1-D Poisson equation (that govern the relationship between the electric fields and the charges in the vertical direction. Having SCEs when electric fields from both sides (S/D) penetrate laterally (in the horizontal direction) into the channel, extends the problem into a 2-D problem.

Multi-gate (MG) structures (also called FinFETs) make use of the third dimension to mitigate SCEs by increasing the gate control over the channel region. MG structures come in different flavors as shown in Figure 1-3, in the next section we will explain the effect of increasing the gate area on the natural screening length. Basically the name comes from the shape of the gate and how many sides it wraps around [6]. Also the substrate can be SOI or Bulk.

Figure 1-3: Different flavors of MG structures

#### 1.3. Reduction of short-channel effects

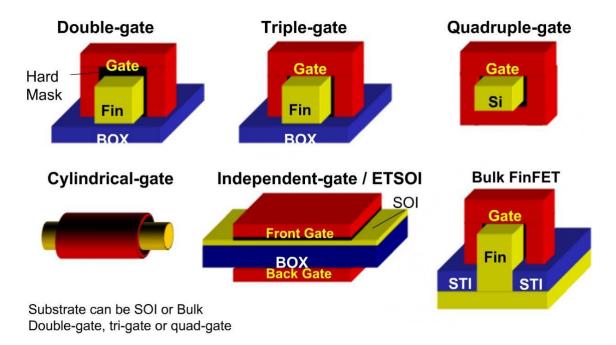

SCEs, DIBL and SS degradation, are mainly a result of the penetration of the electric field lines from the drain end into the channel hence competing the gate in modulating the energy barrier and consequently becomes more difficult to turn the device off by reducing the threshold voltage. Maxwell's equation describes the distribution of the electric potential along the channel [7]:

$$\nabla \cdot D = \rho \tag{1-1}$$

where  $D = \varepsilon E$  is the electrical displacement field,  $\varepsilon$  is the permittivity of the material, and E is the electric field and  $\rho$  is the local density of electrical charge. In 3-D, the electric field components are shown in Figure 1-4, and Poisson equation is written as:

$$\frac{dE_x}{dx} + \frac{dE_y}{dy} + \frac{dE_z}{dz} = -\frac{\rho}{\varepsilon}$$

= consant value

Figure 1-4: Different Electric Field components on elemental volume inside the channel

The superiority of the multi-gate structures over the planar is that the gate control (in the MG case) is exerted in the y and z directions and competes with the undesired variation in the electric field in the x direction coming from the source and the drain.

The sum of three components in x, y, and z of the Poisson equation is a constant, therefore any increase in the control by the top and bottom gates  $(dE_y/dy)$ , or by the side gates  $(dE_z/dz)$  will counteract the SCEs by reducing the penetration of the electric field component coming from the S and D  $(dE_x/dx)$ .

Using simplifying assumptions and few approximations, it is possible to deduce from solving the Poisson equation a parameter called the geometric screening length (or the natural length) which represents the extension of the electric field lines from the source and the drain into the channel region [6]. For example, to quantify such parameter, it is possible to get a device free of SCEs if its gate length is times larger than the natural length (L>6  $\lambda$ ).

For a device with a square cross section having width of W and thickness of T, the natural length is given by:

$$\lambda_1 = \sqrt{\frac{\varepsilon_{si}}{\varepsilon_{ox}}} t_{ox} t_{si}$$

For single gate MOSFET (1-2)

$$\lambda_2 = \sqrt{\frac{\varepsilon_{si}}{2\varepsilon_{ox}}} t_{ox} t_{si}$$

For double gate MOSFET (1-3)

$$\lambda_2 = \sqrt{\frac{\varepsilon_{si}}{2\varepsilon_{ox}}} t_{ox} t_{si} \qquad \text{For double gate MOSFET}$$

(1-3)

$$\lambda_4 = \sqrt{\frac{\varepsilon_{si}}{4\varepsilon_{ox}}} t_{ox} t_{si} \qquad \text{For quadruple gate MOSFET (GAA)} \tag{1-4}$$

where  $\varepsilon_{ox}$  is the electrical permittivity of the gate oxide,  $\varepsilon_{Si}$  is the electrical permittivity of the silicon,  $t_{ox}$  is the gate oxide thickness, and  $t_{Si}$  is the silicon film thickness. These expressions indicate that the SCEs can be minimized by decreasing the gate oxide thickness, by decreasing the silicon film thickness, and by increasing the dielectric constant of the gate oxide material.

Looking at the natural lengths of different MG structures, equations (1-3), interesting concept can be defined as the effective gate number (N), and a generalized natural length expression can be written in terms of N as follows:

$$\lambda_N = \sqrt{\frac{\varepsilon_{si}}{N\varepsilon_{ox}}} t_{ox} t_{si} \tag{1-5}$$

This expression clearly shows the benefits of the MG structures in improving the device electrostatics by reducing the SCEs.

#### 1.4. Overview of the Thesis

As it is clear from the above introduction, the focus of this research is multi-gate structures and specifically Tri-gate (TG) FinFET. The thesis is composed of two main parts: A) Device Level [Ch.2, 3], B) Circuit Level [Ch.4].

On the device level; the main focus is about the electron transport in nano-scale TG-FinFET and is divided into two parts [Ch.2, Ch3].

In Chapter 2, the basic electron transport models are discussed starting from the most classical drift-diffusion model to most sophisticated Monte Carlo techniques. A case study of double-gate FinFET structure is used to show the failure of the conventional DD model in simulating nano-scale channels. Then, the main transport models are benchmarked against the most accurate results on the semi-classical level from Monte Carlo techniques. Different models and modifications are investigated in a trial to extended one of the conventional models to the nano-scale simulations, since they are relatively simple and computationally efficient compared to the Monte Carlo ones.

In Chapter 3, using the conclusions from the previous chapter, a numerical study for scaling nano-scale TG-FinFET according to the most recent International Technology Roadmap of Semiconductors (ITRS 2013) is carried out by means of 3-D Monte Carlo simulations in the ballistic and quasi-ballistic regimes. Ballisticity ratio (BR) is extracted and discussed over different channel lengths. The electron velocity along the channel is analyzed showing the impact of spatial portions of the channel on the transport behavior.

In Chapter 4, we start by benchmarking the basic performance of TG-FinFET SRAM cell (256-array) with technology scaling starting at 20nm and down to 7nm channel length. In this study, predictive technology models (PTM-models) are used as the model cards for the simulations with BSIM-CMG models (the standard compact models for MG-FETs developed by BSIM group).

Next, we move to another peer technology which is 28nm FD-SOI as the most advanced available commercial PDK, keeping the SRAM cell as the test block, but more advanced study is carried out about the cell stability and the evolution from the dynamic to the static metric.

Finally, in Chapter 5, we conclude the overall results of this research and propose future work.

# 2. BENCHMARKING SEMI-CLASSICAL ELECTRON TRANSPORT MODELS FOR NANO-SCALE FINFET IN TCAD

#### 2.1. Introduction

Device models can be categorized under one of three different types of models: a) TCAD models, b) empirical models, and c) compact models. The first type, TCAD, are based on numerical solving techniques solve for the carrier transport and electrostatics of different devices in exact manner; however its computational burden increases especially after the technology advances brought new device architectures such as the FinFET which requires three-dimensional simulations making them impractical for fast circuit simulation, yet, they are of extreme importance for rigorous device physics analysis, so some techniques need to be implemented to turn them to be more efficient. On the other side, the second and third types of models have much less computational burden so they are more practical for fast circuit simulation, however, for the second type, as the dimensions shrink, the complexity of having novel geometries and new physics of carrier transport such as hot electrons phenomena, velocity overshoot, ballistic/quasi-ballistic transport, and quantum effects, impose an enormous number of empirical parameters to be used in the model that drives them far from physical and consequently reduce the amount of insights out of them. All these complexities underlying technology scaling imply the need for more understanding and analyses for the physics involving the transport at the nano-scale dimensions, which consequently can yield more physics-based compact models that can predict the device performance properly and are computationally efficient at the same time [8]. In the following section, we discuss the computational electronics which enables combining sophisticated numerical techniques along with physical models and incorporating them efficiently into TCAD tools for advanced simulations of semiconductor devices.

### 2.2. Computational electronics

Modeling and even simulation of nano-scale FinFET is a formidable challenge due to several factors. At such extremely scaled dimensions it becomes more and more complicated to understand the actual operation of such devices specifically from the electron transport point of view, since peculiar effects start to show up at these extremely scaled dimensions such as hot electrons, velocity overshoot, ballistic and quasi-ballistic transport [9], [10], [11]. Therefore careful treatment for the electronic transport must be considered. These facts imply that relying on fully experimental approach that encounters trial and error will be impossible in terms of both time consumption and cost.

Relying on the technology advancements enabled by the electronics so far, computers are considered cheaper and more practical resources to address the analysis and simulation of further technology nodes and practically become an indispensable tool for all device engineers.

Computational Electronics is devoted to state of the art numerical techniques and physical models used in the simulation of semiconductor devices from a semi-classical perspective and can be extended to include more advanced physics such as quantum transport which is the base of Technology Computer Aided Design (TCAD) tools. In fact its importance mainly stems from two points: a) offering the possibility to investigate physical phenomena that cannot be measured in real life experiments which offers much insight into the real theory of operation of the device under test, b) it enables examining novel devices or even hypothetical devices which have not been manufactured yet [12]. In addition, this kind of simulations can include process simulation that consider various device fabrication processes such as oxidation, etching, material deposition and growth, impurity diffusion, contact deposition. TCAD provides the basis for device modeling as the SPICE simulators provide the basis for circuit design.

The main design flow steps to achieve specific customer need are shown in Figure 2-1. The basic components for general semiconductor device simulation are shown in Figure 2-2.

The basic methodology can be described in terms of two coupled kernels that need to be solved self-consistently with each other, a) the transport equations that govern the flow of charge carriers, b) the electrostatics which describes the modulation of energy barriers and essentially drives the charge flow. Both of them are coupled to each other therefore they require simultaneous solution. Initially, with the beginning of the semiconductor industry, the electrical device characteristics were estimated using pure simple analytical models, for example, the gradual channel approximation for MOSFETs based on the drift-diffusion model which encountered several approximations to yield closed form expressions. The resulting formulas, however, were able to capture the basic device behavior and features [13]. Examples of such approximations are using simplified doping profiles and structure geometries. However, with the advancement in the semiconductor industry and the continuous shrinking of the channel length, these approximations can no longer be applied and start to lose its validity. Hence there was a need for more accurate models.

Figure 2-1: Design sequence to achieve desired customer need

Figure 2-2: Sequence of main device simulation

Numerical simulation was the base for developing such advanced models by solving the carrier transport of semiconductor devices using discretization as was demonstrated by the work of scharfetter and Gummel [14] who proposed a robust discretization of the DD equations that are still in use till today. In the next section, we move to describe the main carrier transport models used in simulating transistors and their evolution over the past decades till today.

### 2.3. Electron Transport models

Modeling of carriers under equilibrium (rest state) conditions is necessary since it establishes the initial frame of reference. However, under equilibrium the net current flow is zero which is uninteresting for practical performance demonstration. Therefore, from a device performance point of view, when the semiconductor is excited, this gives rise to carrier action or a net carrier response and essentially current can flow. So the most interesting question, what controls the operation of the semiconductor devices, is how the charge carriers (electrons/holes) respond to applied, built—in, and or scattering potentials.

In fact, with shrinking the channel length, the clear understanding of carrier transport remains the most tedious issue for proper device modeling [15].

In semiconductor devices, there are two types of carrier motion as shown in Figure 2-3, A) deterministic motion where electrons can be considered as a classical particles hence the Newton's law can be applied, and B) random motion; since after some time, the electron encounter a scattering event which essentially changes its direction and momentum, these random scatterings events follow Fermi's golden rule. As it can be noticed in the same figure, when I (denoting the effective channel length) is much longer than the mean free path  $(\lambda)$ , the transport is mainly described as drift and diffusion components. As I scales down, the transport becomes more deterministic due to the reduction of the number of the scattering events that induce this randomness since the device becomes shorter. Therefore, the transport goes from drift-diffusion to quasi-ballistic  $(1 \sim \lambda)$  and eventually to ballistic at  $(1 < \lambda)$  as will be described in the subsequent sections.

Figure 2-3: Illustration of carriers' motion inside a semiconductor. Each arrow represents a deterministic path until an abrupt change or scattering event happens so the carrier changes its momentum randomly and goes through another deterministic path represented by different arrow, and so on.

### 2.3.1. Drift-Diffusion (DD) Transport Model

The most popular transport model that has been used over long period and all device engineers rely on is called the drift-diffusion model (DD). DD represents one of the semi-classical approaches of treating carrier transport in semiconductors and is based on macroscopic theory in a sense that it considers the electrons as particles.

In the normal case, under equilibrium, electrons execute random thermal motion, where they move in a direction for a while until they encounter a scattering event which essentially changes their direction. Examples for such scattering events could be due lattice vibrations or impurity scatterings and many others. This scattering process might result-in a change in the momentum and/or the energy of the charge carrier.

Since this is under equilibrium, the net current flow is zero, however the electrons have thermal kinetic energy (KT) and average thermal velocity ( $v_{th} \sim 10^7 \ cm/s$ ). Having particles exhibiting a random walk, statistical approaches are used to characterize their behavior such as Fermi and Boltzmann statistics.

Figure 2-4: Drift Diffusion transport mechanisms: a) random walk under thermal equilibrium, b) Drift under applied electric field, c) Diffusion under concentration gradient.

DD model considers the carriers' motion consists of basically two components: i) Drift; where the current carriers drift under the influence of electric field, Figure 2-4, b).ii) Diffusion; where charge carriers diffuse down under concentration gradient, Figure 2-4 c). In general, we have both concentration gradient and electric fields. Hence DD model can be described by this general equation:

$$J_n = n_s q \mu_n E + q D_n \frac{dn_s}{dx} \tag{2-1}$$

$$\frac{D_n}{\mu_n} = \frac{KT}{q} \tag{2-2}$$

where  $J_n$  is the electron current density, q is the electron charge,  $n_s$  the electron charge density,  $\mu_n$  is the electron mobility, E is the electric field,  $D_n$  is the electrons diffusion coefficient,  $\frac{dn_s}{dx}$  is the electrons concentration gradient, T is the temperature, and K is the Boltzmann constant. DD model is based on the first moment of the BTE, and is strictly valid for low field near equilibrium conditions found in long channel transistors [16]. But, with scaling the channel length, the DD model starts to lose its validity since some of the assumptions of this macroscopic model that are implemented in the TCAD tools start to break down. The first is assuming collision dominated transport, and the second is neglecting the quantum effects and the degenerate carrier statistics [17].

In addition, it was found that he DD model underestimates the ballistic on-current [18] due to its incorrect limit on the carrier velocity and shows no velocity overshoot due to its local transport assumption.

### 2.3.2. Thermodynamic (TD) Transport Model

The thermodynamic transport model extends the drift-diffusion approach to account for electro-thermal effects, under the assumption that charge carriers are in thermal equilibrium with the lattice.

Therefore, the carrier temperatures and the lattice temperature are described by a single temperature. The thermodynamic model is required for simulations with high current levels, where considerable self-heating effects might occur. Examples for such cases can include power devices and MOSFETs with high gate or drain voltages, and open bipolar transistors.

The reason behind this model is that high currents can produce Joule heat in the device's regions, which may raise the lattice temperature significantly.

Since many models used in the simulations, including the carrier mobility models, the SRH generation-recombination models, and the avalanche generation model, are functions of the lattice temperature, solving the heat flow equation (thereby obtaining the lattice temperature distribution) is necessary to improve the accuracy of the simulation under such conditions.

The thermodynamic model can be used independently or combined with other advanced transport models [19].

In practice it solves the lattice temperature (heat flow) equation in addition to Poisson equation and carrier continuity equation.

The thermodynamic model is defined by the basic set of differential equations after adding the temperature gradient [19]:

$$J_N = qn\mu_n E + qD_N \nabla n - qn\mu_n P_n \nabla T$$

(2-3)

$$J_P = qp\mu_p E - qD_P \nabla p - qp\mu_p P_p \nabla T$$

(2-4)

where  $P_p$  and  $P_n$  are the absolute thermoelectric powers, and  $\nabla T$  is the temperature gradient.

### 2.3.3. Hydrodynamic (HD) Transport Model

In relatively small channel lengths, the carriers move through the device with velocity larger than the saturation velocity which induce a non-stationary kind of transport and non-local effects where the mobility becomes field dependent.

In Si devices non-stationary transport occurs because of the different order of magnitude of the carrier momentum and energy relaxation times.

Hydrodynamic model was developed mainly to investigate such non-stationary and non-equilibrium electron transport in sub-micrometer channel transistors and semiconductor device [20].

The HD model gained its popularity in electron transport theory due to the physical features of this approach in addition to its practical attributes. In Hydrodynamic/Energy balance modeling the velocity overshoot effect is accounted for through the addition of:

- Energy conservation equation, in addition to:

- Particle Conservation (Continuity Equation)

- Momentum (mass) Conservation Equation

which is the superiority of the HD over the classical DD model. [20].

Another model called Energy transport model (ET) which is usually mentioned when discussing HD models. The basic difference between the HD and ET models is the neglect of the drift energy in the energy transport equation [21].

However, with the continuous scaling of channel length approaching the near ballistic regime, it was found that both ET/HD may substantially overestimate the on-current [21]. One justification for the failure of such macroscopic transport models in the near ballistic can be attributed to the assumption of their derivation. The kinetic energy of carriers is composed of two terms, the first is the thermal energy due scattering events, and the second is the drift energy associated with average motion of the carriers. In such models, it is common to neglect the second term. However, at the ballistic limit, there is no scattering to rise the temperature, hence the second term dominates the total kinetic energy. Neglecting the drift energy term in such models is most probably the cause of the un-physically high velocities observed in the HD/ET simulations [21].

### 2.4. Benchmarking semi-classical transport models in TCAD

### 2.4.1. Problem statement

As discussed above about the complexity associated with scaling down the channel length and the evolution of new carrier transport physics, conventional models can no longer be used to simulate such nano-scale devices. Therefore special care should be devoted to choosing the proper transport model of simulation. To give an idea about the importance of this point, a double gate (DG) structure, as shown in Figure 2-5 a), was simulated with two different channel lengths: a) L=50 nm, b) L=20 nm, representing long and short channels respectively. The doping profile is shown in Figure 2-5 b), and the main device parameters and dimensions are summarized in Table 2-1. The simulation was done two times using different transport model in each run:

- i) Conventional Drift-diffusion,

- ii) Monte Carlo technique (will be discussed in more details in the following sections).

to assess validity of the used carrier transport model with scaling the channel length.

Figure 2-6 a), b) show the transfer characteristics of the simulated device in the saturation regime ( $V_d = V_{DD}$ ), at each channel length for both DD and MC.

It is clear that for quite long channels (L=50 nm), as shown in Figure 2-6 a), the MC and DD models quite match each other and yields almost the same results while scaling the channel length down to 20 nm, Figure 2-6 b), the DD model clearly underestimates the oncurrent and a big mismatch is found with respect to the characteristic obtained using the MC model. These results are consistent with previous studies [18].

Figure 2-5: Simulated double gate (DG) structure, (a) Structure's geometry by Sentaurus structure editor, (b) Doping profile.

Table 2-1: Device parameters of the simulated structure

| Parameter                  | Value             |  |  |

|----------------------------|-------------------|--|--|

| Channel length (L)         | a) 50 nm b) 20 nm |  |  |

| Body Thickness (T)         | 3 nm              |  |  |

| Oxide Thickness $(t_{ox})$ | 1.5 nm            |  |  |

| Body Doping (NA)           | -1e15             |  |  |

| S/D Doping (ND)            | 1e20              |  |  |

Figure 2-6: Transfer characteristics with Monte Carlo (MC), and classical drift-diffusion (DD): (a) long channel  $L_{eff} = 50nm$ , (b) short channel,  $L_{eff} = 20nm$

# 2.4.2. Objective of the study

The purpose of this study is to investigate and assess the applicability of the common electron transport models used in commercial TCAD device simulator (Sentaurus) to describe the behavior of nano-scale channel lengths, where the quasi-ballistic regime is dominant [2 - Bude], with novel structural geometries such as triple-gate (TG) FinFETs at the dimensions projected by the international technology roadmap for semiconductors (ITRS).

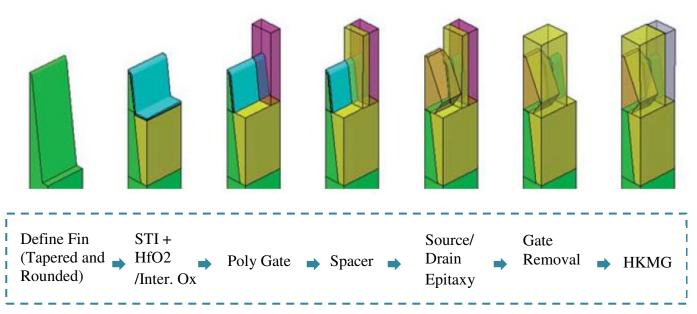

# 2.4.3. Device Structure and Simulation Methodology

As a case study, TG FinFET structure is used according to the process in [22] for two channel lengths: a) L=17 nm, b) L=15nm. The main process formation flow is shown in Figure 2-7, and the doping profile is shown in Figure 2-8, and finally Figure 2-9, shows the structure after meshing (representing the geometrical object as a set of finite elements for computational analysis). Different versions and modifications of conventional Drift-

Diffusion (DD) model are investigated. Classical Monte Carlo simulations were taken as a reference since they are considered the most accurate results on the semi-classical level.

Figure 2-7: Process Formation Flow of simulated device [Sentaurus Template, [81]]

Figure 2-8: Doping Profile across the simulated structure, [Sentaurus Template, [81]]

Figure 2-9: Meshing and Orientation of the simulated FinFET structure, [Sentaurus Template, [81]]

We briefly describe the basic device models incorporated in the TCAD tool (Synopsys, Sentaurus). These models, except the MC, are based on considering the mobility and the saturation velocity of the drift diffusion model as fitting parameters, yet they can yield quite accurate results for nano-scale device simulation [23].

#### A. Monte Carlo method (MC)

Monte Carlo (MC) simulation technique is considered the most accurate technique for simulating the carrier transport phenomena in semiconductor devices on the semi-classical level [24]. The main idea of the MC simulation is tracking large number of particles each one represents an electron through its journey along the device, trajectory, under the influence of electric field and subject to random scattering events. These trajectories are governed by classical newton's law and the carrier dispersion relation. The duration of the electron's free flight before getting interrupted by a scattering event, the type of the scattering event, and the final state after the scattering event are all chosen

based on probabilistic distributions. Simulating large number of these trajectories can yield very good average values for important physical quantities that can describe the average behavior of the carrier through the device and results a carrier distribution satisfies the Boltzmann Transport equation (BTE) [25]. Since the main MC algorithm is based on real physics, usually MC simulations are viewed as simulated experiments. In this investigation we take the MC results as the reference results when comparing the different models.

# B. Modified drift-diffusion model (MDD)

Classical drift—diffusion (CDD) model works pretty well for long channel devices, where the transport is collision-dominated, however for short channel devices, the approximation of the transport as collision-dominated breaks down and near ballistic effects and strong velocity overshoot show up consequently the classical drift-diffusion model loses its validity. Due to the fact that the DD model is based on physics that can be derived from first moment of the Boltzmann transport equation (BTE) [24], it is not completely off what the actual model should be. So instead of going to sophisticated, time-consuming MC simulations, to some limits the classical DD model can be adjusted through modifying some parameters to fit the transport model in such small devices. To account for the velocity saturation effect, the mobility modeling is divided into two parts: a) low field mobility model, b) high field mobility model, which accounts for the velocity saturation effects. DD model incorporates a field dependent mobility model that provides smooth transition between low-field and high-field behavior. This model is called Caughey-Thomas (CT) field dependent mobility model and is expressed as:

$$\mu(E) = \frac{\mu_o}{\left[1 + (\frac{\mu_o E}{\nu_{SAT}})^{\beta}\right]^{1/\beta}}$$

(2-5)

Where E is the lateral electric field (parallel to the oxide interface), vsat is the saturation velocity,  $\beta$  is the low field inversion layer mobility and  $\beta$  a constant.

The suitability of the DD model to simulate the short channel transistors through adjusting some parameters in the CT high filed velocity saturation model was first introduced in [16].

Then it was extended for the double-gate structures [26] through a fitting formula to define a length-dependent velocity saturation.

$$v_{sat}(L) = \frac{aL+b}{L+c} \tag{2-6}$$

where a=1.5, b=21.6, and c=2.7 are fitting parameters to adjust the DD model for short channels simulations. For the triple-gate, we use this formula for the channel lengths of 17 nm and 15 nm to yield a velocity saturation values of  $2.39 \times 10^7$  and  $2.47 \times 10^7$  cm/s respectively.

# C. Drift-diffusion with Ballistic mobility model (BDD)

Adding more physically sounded adjustment to the traditional model can improve the results further. DD model is characterized by the mobility and the diffusion coefficient terms, consequently once one of these collision dominated transport related quantities loses its significance, the whole model fails. By re-examining the mobility term, according to [27], and [28], looking into the scattering current model expressed by the Landauer formula, a ballistic mobility like model was deduced which has a channel length dependence causing degradation of the mobility at short channel lengths. Then, a generic mobility model called apparent mobility was mathematically demonstrated taking the effect of the ballistic mobility into account and extends the mobility concept to very short channel lengths.

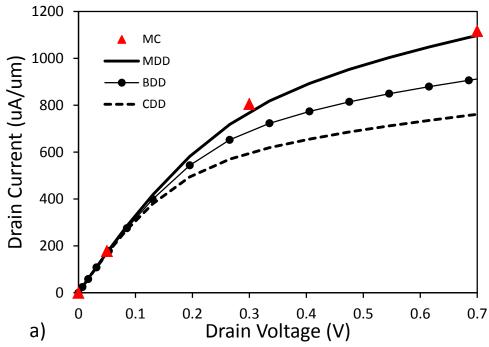

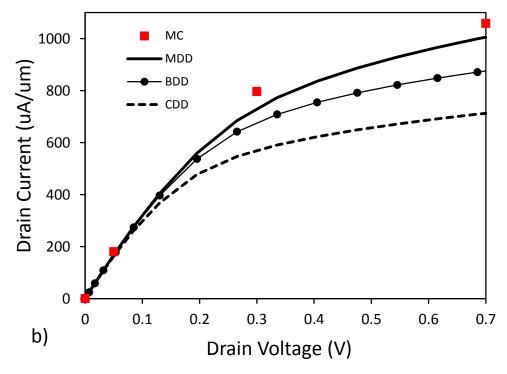

#### 2.4.4. Simulation Results and discussion

As shown in Figure 2-10, output characteristics of two triple-gate structures; (a) for gate length of 17 nm, silicon fin thickness of 11 nm, (b) for gate length of 15 nm and silicon

fin thickness of 10 nm as projected by the ITRS for the years of 2015 and 2016, are simulated with all above mentioned models.

Figure 2-10: Output characteristics of Triple-gate FinFET simulated with Monte Carlo (MC), Modified drift-diffusion (MDD), Drift-diffusion with ballistic mobility model (BDD), and the classical drift-diffusion (CDD); (a)  $L=17~nm, T_{si}=11~nm, H_{fin}=27~nm$ , (b)  $L=15.3~nm, T_{si}=10~nm, H_{fin}=27~nm$ .

It is noteworthy to mention that realistic considerations are taken into account in these simulations such as a parasitic source/drain series resistance, strain effects, and high-k metal gate stack.

#### 2.5. Conclusions

It is clear that the classical DD model underestimates the current characteristics as expected, and for the DD with ballistic mobility (BDD), it predicts the current in the linear region however the error increase as it goes deep into saturation, and it is clear that the modified DD model (MDD) is the most viable model and regenerated the MC results quite well, however it relies on non-physical fitting parameters formula to adjust for the length scaling effects which might vary from one structure to another. Accordingly we conclude that there is a need to conduct all the simulations based on MC approach to be able to draw appropriate conclusions.

# 3. A NUMERICAL STUDY OF NANO-SCALE TG-FINFET: 3D MONTE CARLO SIMULATIONS IN THE BALLISTIC AND Q-BALLISTIC REGIMES

In this chapter, nano-scale tri-gate (TG) FinFET with channel lengths down to 9.7 nm as projected by the 2013 International Technology Roadmap of Semiconductors (ITRS-2013) are simulated by means of quantum corrected 3-D Monte Carlo technique in the ballistic and quasi-ballistic regimes. Ballisticity ratio (BR) is extracted and found to reach values as high as 90% at LG = 9.7 nm. The impact of the ITRS-2013 scaling strategy on the BR, and ON-/OFF-states is discussed. Forward and backward electron velocity components are extracted along the channel to analyze the electron transport in detail. Velocity profile is found to be characterized by two critical points along the channel; each is associated with a change in the electron acceleration showing the physical significance of the off-equilibrium transport with scaling the channel length.

#### 3.1. Introduction

Modeling and even simulation of nano-scale FinFET is a formidable challenge due to several factors. First, peculiar effects start to show up at these extremely scaled dimensions on the transport level such as hot electrons, velocity overshoot, ballistic and quasi-ballistic transport [29], [10], [11], [30] hence a careful treatment for the electronic transport must be considered. Second, with scaling the fin thickness, incorporation of quantum effects in the transport model is essential, hence quantum corrections are inevitable for proper accounting of the device electrostatics [31]. Third, the 3-D geometry of such non-planar multi-gate devices imposes new challenges especially on the computational level.

Therefore, choosing the correct transport model is considered the most serious challenge in the simulation of nano-scale transistors.

Several approaches have been proposed to account for such ballistic effects and strong off-equilibrium transport and even to determine the ultimate ballistic limit which is set by thermal injection from the source end [11], [30].

However, due to the lack of well-selected experiments which can appropriately discriminate between the various physical effects that interact with each other and suits such inextricable nature of electron transport on the nano-scale, they are still in need for more rigorous verification [32]. Therefore, more computationally intensive device models are required to study the transport in nano-scale devices such as Monte Carlo (MC) technique [33]. MC is considered the most efficient technique for simulating the carrier transport that involves hot electron phenomena and ballistic effects in semiconductor devices on the semi-classical level [34].

Previous works have been done based on 2-D MC simulations to study the ballistic and quasi-ballistic transport theories for nano-scale bulk and double gate (DG) SOI MOSFETs [35], [36], [37], [38], in addition to assessing the validity of the well-known analytical models developed in [11], [30]. In [39], MC simulations were used to verify newly developed backscattering models for Bulk MOSFETs within the Landauer theory. In [40], the same technique was used to study the scattering effects along the channel in DG MOSFETs, and further to get more insight about the main behavior of quasi-ballistic transport and determine the crucial parts of the channel that have the most contribution in limiting the ballistic transport. The scattering was turned on along some portions of the channel, and off in other parts and the different cases were compared. Some of the electron transport quantities have been discussed also by means of 2-D self-consistent MC simulations, where the evolution of the velocity distribution along the channel was analyzed [36].

Most of these computational studies confirm the general framework proposed in [11], [30], while others suggest additional complexities [41], [42], [43], e.g. the non-equivalence of the forward and backward velocities at the top of the barrier. However, due to the complexity of the 3-D nature of the tri-gate FinFET in addition to the

sophistication of the MC technique in 3-D, most of the work done for tri-gate FinFETs was for relatively long channels and based on conventional transport theories to develop analytical models [44], [45]. Little studies have been done for the tri-gate structure on the nano-scale based on 3-D Monte Carlo simulations [46], [47], and none of them provided a detailed study for the ballistic and quasi-ballistic transport in such devices, which is targeted in this work.

To keep short channel effects (SCEs) under control ( $I_{OFF} = 100 \ nA/\mu m$ ), ITRS implies scaling of the supply voltage  $V_{DD}$ , gate oxide thickness  $t_{ox}$ , and the fin thickness  $T_{fin}$ . For all the simulated devices, the same scaling strategy is mostly adopted as reported in Table.1.

Table 3-1: The main parameters of the simulated device

| Year                                         | 2013                      | 2015 | 2017 | 2019 | 2021 |  |

|----------------------------------------------|---------------------------|------|------|------|------|--|

| Physical Gate<br>Length (nm)                 | 20                        | 16.7 | 13.9 | 11.6 | 9.7  |  |

| Body<br>Thickness (nm)                       | 6.4                       | 5.3  | 4.4  | 3.7  | 3.1  |  |

| Fin Height (nm)                              | 20.0                      |      |      |      |      |  |

| Supply<br>Voltage (V)                        | 0.86                      | 0.83 | 0.80 | 0.77 | 0.74 |  |

| EOT (nm)                                     | 0.7                       | 0.67 | 0.64 | 0.61 | 0.56 |  |

| EPS_HIGH-K                                   | 22.0                      |      |      |      |      |  |

| $t_{ox,ph}$ (nm)                             | 2.56                      | 2.53 | 2.46 | 2.42 | 2.37 |  |

| Work<br>Function (eV)                        | 4.25                      |      |      |      |      |  |

| Wafer/Channel<br>Direction                   | 001/100                   |      |      |      |      |  |

| Channel Doping (cm <sup>-3</sup> )           | $1x10^{15}$               |      |      |      |      |  |

| S/D Doping / S/D<br>Ext. (cm <sup>-3</sup> ) | $1.5x10^{20}/1.5x10^{20}$ |      |      |      |      |  |

| S/D Extension (nm)                           | 8.0                       |      |      |      |      |  |

# 3.2. Device Design and Simulation Methodology

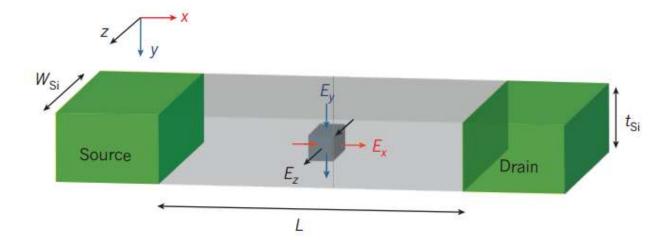

Figure 3-1 shows the simulated structure under study, the channel length varies from 15.2 nm down to 9.7 nm, as projected by the 2013 ITRS. The work function is set to 4.25 eV. The fin top corners are rounded, close to the industry standard. Also the gate stack with nitride spacer formation is used. Source/drain (S/D) extensions are employed and set to 8 nm for all the simulated devices. In this work, we didn't consider the series resistance effect. The overlap distance between the gate and the S/D extensions (where S/D doping drops to 1×10<sup>19</sup> cm<sup>-3</sup>) is 1 nm. The mechanical stress is considered through all the simulation results. The scaling strategies as specified by the ITRS are mostly adopted in all the simulated devices. The main device parameters are reported in Table I and the corresponding doping profiles are shown in Figure 3-2.

The simulation methodology is based on 3-D Monte Carlo simulation [48], incorporating quantum corrections using modified permittivity and work function taking into account the orientation dependence of the surface mobility [47], for both the ballistic and quasiballistic transport regimes. For the quasi-ballistic regime, scattering mechanisms include ionized impurity scattering, phonon scattering, and surface roughness scattering. For the ballistic regime, all the scattering mechanisms are switched off inside the channel volume such that the electrons have the full opportunity to transit from the source to the drain without encountering a single scattering event. Forward and backward components of average transport quantities such as the electron velocity are analyzed in the ballistic and quasi-ballistic transport. To do that, scalar product between the group velocity (with which the electron is directed) and a vector in the system coordinates directed towards the direction of transport [48] is evaluated (assuming the forward direction to be from the source to the drain). All Monte Carlo simulations are performed at 300K temperature.

Figure 3-1: 3-D and 2-D representations of Tri-gate FinFET structure under study

Figure 3-2: Doping profiles in cross sections of the simulated Tri-gate FinFET for channel lengths of 16.7, 13.9, 11.6, and 9.7 nm as projected to the years 2015, 2017, 2019, and 2021 respectively.

#### 3.3. Simulations Results

# 3.3.1. Performance metrics with scaling

#### A. Off-state behavior:

The fundamental challenge in shrinking the transistor's gate length is to control the SCEs. Indeed, this problem is exacerbated in a nonlinear sense with approaching the 10-nm length. Figure 3-3 shows the behavior of the SCEs with length scaling normalized to the values at  $L_{ch} = 16.7$  nm (130-mV/V drain induced barrier lowering (DIBL) and 130-nA/ $\mu$ m IOFF). The OFF-state behavior is studied by MC method, however, the Drift diffusion (DD) can be also used as an approximation. It can be noticed that scaling beyond the 13.9nm channel length yields a significant increase in  $I_{OFF}$  (exponential increase with scaling) and DIBL. Although the ITRS scaling strategy manages to keep the  $N_{inv}$  and  $V_{inj}$  almost independent of  $L_{ch}$  keeping the necessary assumptions of the ballistic theory.

Figure 3-3: SCEs behavior of Tri-gate FinFET at different channel lengths showing the threshold voltage roll-off and the degradation of both DIBL and leakage current (IOFF) based on the adopted scaling strategy normalized to values at 16.7nm

According to our simulations, Fig. 3-3, it fails in keeping control of the SCEs, as shown in Figure 3-3. This from one side elucidates the severe degradation of the performance of such devices with down scaling and raises the need for other quick viable alternatives to extend the technology scaling. On the other side, such non-ideal effects raise additional complexities to the performance evaluation and require careful treatment in parameters extraction. For example, having a substantial DIBL leads to differentiation between the virtual source point and the top of the barrier (ToB) point, as discussed in [49], which used to refer to the same point interchangeably for an electrostatically well-tempered device.

#### B. ON-State Behavior

ON-current  $(I_{ON})$  is considered the most indicative factor in evaluating the transistor's performance. This can be approached in two ways. First,  $I_{ON}$  per unit width, which is the most widely used metric to compare different devices. Second, we can still be concerned about the  $I_{ON}$  per device.

In this section, we consider both metrics separately. Approaching the ballistic transport has been considered to be the peak performance a device could ever achieve in terms of ION. Since operating in ballistic regime improves scaling benefits in a sense that:

- 1) Speed increases as a result of the transport in shorter channels, and

- 2) For these shorter channels being ballistic, i.e., comparable with the mean free path, is even better for the performance, since the electron transport would encounter less amount of scatterings yielding enhanced mobility, hence higher I<sub>ON</sub>.

However, as a result of the necessity to adopt a scaling strategy to compensate the increase of the SCEs that involves scaling of other geometrical parameters besides the channel length, leading to reduced effective channel width, these benefits start to be undermined.

As shown in Figure 3-4, although a consistent improvement in ballistic ratios might be achieved with scaling (as discussed in Section IV), the devices are not able to attain similar performance improvements. Figure 3-4 (a) shows ION per unit width with technology scaling. The relative improvement (with respect to the preceding node) is decreasing with  $L_{ch}$  and almost saturates at 11.6 nm. Figure 3-4 (b) shows the corresponding ION per device with technology scaling. The relative improvement is also decreasing with the channel length. It does not saturate, but it diminishes instead, which means that the current itself saturates but not the improvement.

Figure 3-4: The behavior of the output current at VGS=VDS=VDD showing the relative improvement with technology scaling a) The current per device (corresponding to a device effective width;  $W_{eff} = 2H_{fin} + T_{fin}$ ), b) The device current per unit width.

Therefore, whether the relative improvement or the current itself saturates, this represents a serious slowdown in TG-FinFET scaling performance. In the latest ITRS edition, similar analogy has been pointed out. Along the roadmap, ION per unit width has been noticed for the first time to drop with technology scaling keeping fixed IOFF (controlled SCEs). This can have serious implications on advanced circuit design, as discussed in [50].

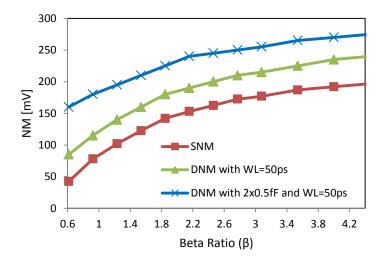

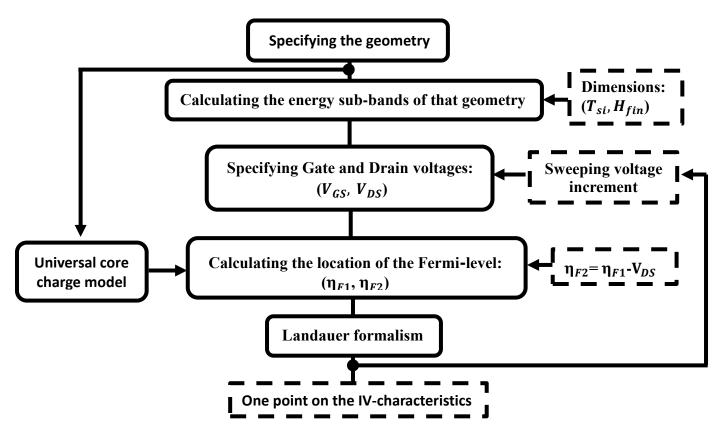

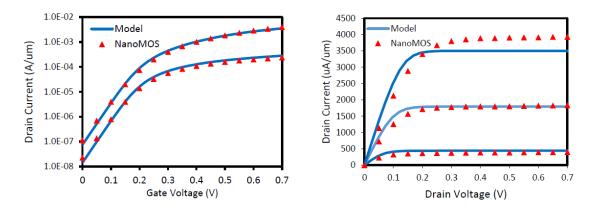

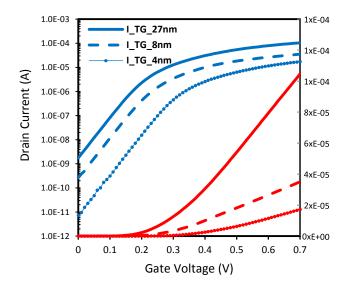

# 3.3.2. Ballisticity Ratio (BR): How close to the ballistic limit?